(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4057990号

(P4057990)

(45) 発行日 平成20年3月5日(2008.3.5)

(24) 登録日 平成19年12月21日(2007.12.21)

(51) Int.Cl.

F 1

H03K 5/1252 (2006.01)

H03K 5/01

G

H03K 5/08 (2006.01)

H03K 5/08

E

H03K 19/0175 (2006.01)

H03K 19/00

1 O 1 F

請求項の数 4 (全 11 頁)

(21) 出願番号

特願2003-363461 (P2003-363461)

(22) 出願日

平成15年10月23日(2003.10.23)

(65) 公開番号

特開2005-130185 (P2005-130185A)

(43) 公開日

平成17年5月19日(2005.5.19)

審査請求日

平成17年10月7日(2005.10.7)

(73) 特許権者 000221199

東芝マイクロエレクトロニクス株式会社

神奈川県川崎市川崎区駅前本町25番地1

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100092820

弁理士 伊丹 勝

(72) 発明者 大川 浩一

神奈川県川崎市川崎区駅前本町25番地1

東芝マイクロエレクトロニクス株式会社

内

審査官 石田 勝

最終頁に続く

(54) 【発明の名称】半導体集積回路装置

(57) 【特許請求の範囲】

【請求項 1】

論理信号に含まれるグリッチを除去するフィルタ回路を備えた半導体集積回路装置において、

前記フィルタ回路は、

入力論理信号の各立ち上がりエッジのタイミング後一定時間活性化されてその立ち上がりエッジを遅延させる第1の遅延回路と、

前記入力論理信号の各立ち下がりエッジのタイミング後一定時間活性化されてその立ち下がりエッジを遅延させる第2の遅延回路と、

前記第1及び第2の遅延回路の出力により制御されて前記入力論理信号の遅延出力を出す出力ドライバとを有し、

前記第1及び第2の遅延回路はそれぞれ、

前記入力論理信号に基づいて生成された相補的レベルを持つ二系統の信号の一方が入力される、ゲートに参照電圧が与えられて出力の放電電流を制限する電流源トランジスタを備えた第1のインバータと、

前記第1のインバータの出力に接続されたキャパシタと、

前記第1のインバータの出力電圧を前記参照電圧と比較して検知するための、前記二系統の信号の一方の立ち上がりエッジから一定時間活性化されるカレントミラー型差動増幅器とを有する

ことを特徴とする半導体集積回路装置。

10

20

**【請求項 2】**

前記差動増幅器は、

一方のゲートが前記第1のインバータの出力に接続され、他方のゲートに前記参照電圧が与えられる一対のドライバN M O Sトランジスタと、

前記ドライバN M O Sトランジスタのドレインにそれぞれドレインが接続されてカレントミラー回路を構成する一対の負荷P M O Sトランジスタと、

前記ドライバN M O Sトランジスタの共通ソースと接地端子の間に介在する活性化用N M O Sトランジスタと、

前記負荷P M O Sトランジスタの共通ソースと電源端子の間に介在する活性化用P M O Sトランジスタとを有する

ことを特徴とする請求項1記載の半導体集積回路装置。

**【請求項 3】**

前記第1及び第2の遅延回路はそれぞれ、

前記差動増幅の出力と前記出力ドライバの間に介在させた第2及び第3のインバータと、

前記差動増幅器の出力レベルをそれが非活性化された後にも保持するためのラッチ回路と、

前記第2及び第3のインバータの接続ノードの電圧レベルを電源投入時に初期設定する初期設定回路とを更に備えた

ことを特徴とする請求項1記載の半導体集積回路装置。

**【請求項 4】**

前記出力ドライバは、

ソースが電源端子に接続されドレインが前記出力ノードに接続されて、前記第1の遅延回路の出力によりゲートが駆動されるP M O Sトランジスタと、

ソースが接地端子に接続されドレインが前記出力ノードに接続されて、前記第2の遅延回路の出力によりゲートが駆動されるN M O Sトランジスタと、

前記出力ノードに接続されてその電圧レベルを正帰還制御する帰還回路とを有する

ことを特徴とする請求項1記載の半導体集積回路装置。

**【発明の詳細な説明】****【技術分野】**

30

**【0 0 0 1】**

この発明は、論理信号に含まれるグリッヂを除去するためのフィルタ回路を備えた半導体集積回路装置に関する。

**【背景技術】****【0 0 0 2】**

半導体集積回路において、しばしば論理信号を内部回路に転送する際に、その論理信号に重畳されているグリッヂを除去乃至抑圧することが必要になる。グリッヂは、狭いパルス幅の電圧スパイクノイズであるから、これを除去するためには一般にフィルタ回路が用いられる。グリッヂ除去のためのフィルタ回路としては例えば、積分回路が用いられる（例えば、特許文献1参照）。

40

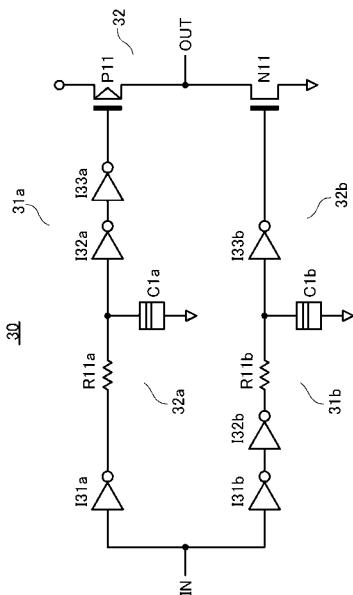

**【0 0 0 3】**

図5は従来のフィルタ回路30の構成例を示している。このフィルタ回路30は、二系統の遅延回路31a, 31bと、それらの遅延出力で交互に駆動されるP M O SトランジスタP11とN M O SトランジスタN11からなる出力ドライバ32とを有する。一方の遅延回路31aは、入力ノードINに接続されたインバータI31a, I32a, I33aの列を有し、そのインバータI31aとI32aの間には抵抗R11aとキャパシタC1aからなる積分回路32aが配置されている。他方の遅延回路31bは、同様に入力ノードINに接続されたインバータI31b, I32b, I33bの列を有し、そのインバータI32bとI33bの間に抵抗R11bとキャパシタC1bからなる積分回路32bが配置されている。

50

**【0004】**

各遅延回路31a, 31b内に配置された積分回路32a, 32bが内部回路に転送すべき入力論理信号のグリッヂを除去するための低域通過フィルタ(LPF)の働きをする。即ち、入力ノードINが“L”から“H”或いは“H”から“L”に遷移する論理信号が入力されると、遅延回路31a, 31bによりそれぞれ一定の遅延を受けて、PMOSトランジスタP11, NMOSトランジスタN11の一方がオン、他方がオフになり、出力ノードOUTに遅延された論理信号が出力される。入力論理信号に重畠している正、負のグリッヂパルスは、遅延回路31b, 31bの積分回路32b, 32bにより除去される。

【特許文献1】特開平7-336201号公報

10

**【発明の開示】****【発明が解決しようとする課題】****【0005】**

インバータと積分回路を組み合わせた従来のグリッヂ除去フィルタ回路は、電源電圧依存性があり、またインバータを構成するトランジスタのしきい値電圧のばらつきの影響を受ける。

**【0006】**

この発明は、消費電力を増大させることなく特性改善を図ったグリッヂ除去フィルタを備えた半導体集積回路装置を提供することを目的とする。

**【課題を解決するための手段】**

20

**【0007】**

この発明の一態様によれば、論理信号に含まれるグリッヂを除去するフィルタ回路を備えた半導体集積回路装置において、前記フィルタ回路は、入力論理信号の各立ち上がりエッジのタイミング後一定時間活性化されてその立ち上がりエッジを遅延させる第1の遅延回路と、前記入力論理信号の各立ち下がりエッジのタイミング後一定時間活性化されてその立ち下がりエッジを遅延させる第2の遅延回路と、前記第1及び第2の遅延回路の出力により制御されて前記入力論理信号の遅延出力を出す出力ドライバとを有し、前記第1及び第2の遅延回路はそれぞれ、前記入力論理信号に基づいて生成された相補的レベルを持つ二系統の信号の一方が入力される、ゲートに参照電圧が与えられて出力の放電電流を制限する電流源トランジスタを備えた第1のインバータと、前記第1のインバータの出力に接続されたキャパシタと、前記第1のインバータの出力電圧を前記参照電圧と比較して検知するための、前記二系統の信号の一方の立ち上がりエッジから一定時間活性化されるカレントミラー型差動増幅器とを有する。

30

**【発明の効果】****【0008】**

この発明によれば、消費電力を増大させることなく特性改善を図ったフィルタ回路を備えた半導体集積回路装置が得られる。

**【発明を実施するための最良の形態】****【0009】**

以下、図面を参照して、この発明の実施の形態を説明する。

40

**【0010】**

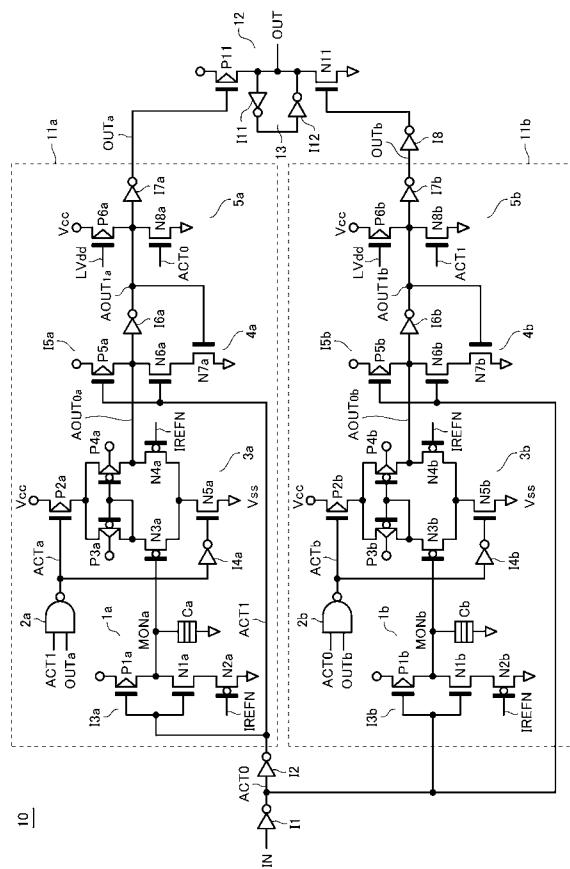

図1は、この発明の実施の形態による半導体集積回路に搭載されるフィルタ回路10の構成を示している。フィルタ回路10は、二つの遅延回路11a, 11bこれらの遅延出力により駆動される出力ドライバ12を有する。二つの遅延回路11a, 11bは同じ構成を有するから、図では対応する回路要素に対してサフィックス“a”, “b”により区別した同じ符号を付してある。

**【0011】**

第1の遅延回路11aは、入力ノードINに供給される論理信号の各立ち上がりエッジのタイミング後一定時間活性化されてその立ち上がりエッジを遅延させて、出力ドライバ12のPMOSトランジスタP11をオン駆動するためのものである。その遅延処理のな

50

かでグリッチ除去が行われる。入力ノードINが“H”レベルを保つ間、第2の遅延回路11bは非活性に保たれる。

#### 【0012】

第2の遅延回路11bは、入力ノードINの論理信号の各立ち下がりエッジのタイミング後一定時間活性化されてその立ち下がりエッジを遅延させて、出力ドライバ12のNMOSトランジスタN11をオン駆動するためのものである。その遅延処理のなかで、グリッチ除去が行われる。入力ノードINが“L”レベルを保つ間、第1の遅延回路11aは非活性に保たれる。

#### 【0013】

二つの遅延回路11a, 11bを入力論理信号に基づいて相補的に動作させるために、

10

入力ノードINには2段のインバータI1, I2が接続されている。これらのインバータの出力ノードACT0, ACT1には、入力論理信号に対応して相補的レベルを持つ二系統の信号が得られる。これらの二系統の信号がそれぞれ、第1の遅延回路11aと第2の遅延回路11bに入力される。

#### 【0014】

以下、第1の遅延回路11aに着目してその構成を説明する。ノードACT1に接続されたインバータI3aのNMOSトランジスタN1aと接地端子の間には、電源電圧Vccより低くかつ電源電圧に依存しない参照電圧IREFNにより駆動される電流源NMOSトランジスタN2aが設けられている。電流源NMOSトランジスタN2aには、チャネルドーピングが行われていないイントリンシック(I)型NMOSトランジスタを用いている。インバータI3aの出力ノードMONaにキャパシタCaが接続されている。キャパシタCaは、DタイプMOSトランジスタを用いたMOSキャパシタである。

20

#### 【0015】

このインバータI3aとキャパシタCaは、グリッチ除去のための低域通過フィルタ(LPF)1aを構成している。即ち、ノードMONaの“H”から“L”への遷移(立ち下がり)波形は、参照電圧IREFNにより駆動される電流源NMOSトランジスタN2aのオン抵抗(R)とキャパシタCaの容量(C)によるCR時定数により遅延される。この時定数を最適設定することによって、一定パルス幅以下のグリッチ除去が可能となる。

。

#### 【0016】

インバータI3aの出力ノードMONaには、カレントミラー型差動増幅器3aが接続されている。差動増幅器3aは、ドライバNMOSトランジスタN3a, N4aと、それらのドレインにそれぞれドレインが接続されたカレントミラー負荷を構成するPMOSトランジスタP3a, P4aを有する。差動トランジスタN3a, N4aのうち、一方N3aのゲートがノードMONaに接続され、他方N4aのゲートには電源電圧に依存しない参照電圧IREFNが与えられている。これらのPMOSトランジスタP3a, P4a及びNMOSトランジスタN3a, N4aとしてもI型トランジスタが用いられている。

30

#### 【0017】

差動アンプ3aのPMOSトランジスタ対P3a, P4aの共通ソースと電源端子Vccとの間、NMOSトランジスタ対N3a, N4aの共通ソースと接地端子Vssとの間にはそれぞれ、活性化用PMOSトランジスタP2a, NMOSトランジスタN5aが接続されている。これらの活性化用トランジスタP2a, N5aを一定時間オン駆動するために、NANDゲート2aが用意されている。

40

#### 【0018】

NANDゲート2aの二入力には、この遅延回路11aの入力ノードACT1と出力ノードOUTaが接続されている。従って、ノードACT1が“H”になった後、一定時間遅れて出力ノードOUTaが“L”になるまでの間、NANDゲート2aの出力ノードACTaは“L”となる。このノードACTaの“L”レベル電圧により、活性化PMOSトランジスタP2a及びNMOSトランジスタN5aがオンになり、差動アンプ3aが活性状態になる。

50

## 【0019】

差動アンプ3aの出力ノードAOUT0aは、インバータI6aを介してノードAOUT1aに、更にノードAOUT1aはインバータI7aを介して出力ノードOUTaに接続される。出力ノードAOUT0aには、ノードACT1により制御されるインバータI5aの出力も接続されている。このインバータI5aのNMOSトランジスタN6aには、ノードAOUT1aによりゲートが制御されるNMOSトランジスタN7aが直列接続されている。

## 【0020】

即ちインバータI5aとI6aとは、逆並列接続されて、ノードACT1の信号をラッチ信号とするラッチ回路4aを構成している。ノードACT1が“H”になると、NMOSトランジスタN6a, N7aがオンになって、差動アンプ3aの出力ノードAOUT0aを“L”レベルに設定する。差動アンプ3aは、ノードACTaが“L”の間のみ活性でその後は非活性になるが、その後も、ACT1 = “H”的間、これとAOUT1a = “H”とによって、ラッチ回路4aが出力ノードAOUT0aを安定に“L”に保持する働きをする。

10

## 【0021】

出力ドライバ12は、ソースがそれぞれ電源端子Vcc, 接地端子Vssに接続され、ドレインが出力ノードOUTに共通接続されたPMOSトランジスタP11とNMOSトランジスタN11を有する。第1の遅延回路11aの出力ノードOUTaは、PMOSトランジスタP11のゲートに接続される。第2の遅延回路11bの出力ノードOUTbは、インバータI8を介してNMOSトランジスタN11のゲートに接続される。この出力ドライバ12の出力ノードOUTがフィルタ出力ノードである。この出力ノードOUTに、以下に具体的に説明するように、入力ノードINに入る論理信号のグリッチが抑圧乃至除去されて、一定の遅延を受けた論理パルス信号が得られる。

20

## 【0022】

インバータI6a, I7aの接続ノードAOUT1aには、電源投入時にこのノードAOUT1aをプリチャージするためのPMOSトランジスタP6aが設けられている。即ちPMOSトランジスタP6aは、電源電圧Vccに遅れて立ち上がる内部電源電圧LVdにによりゲートが駆動されており、電源投入後一定時間オンになる。ノードAOUT1aにはまた、ノードACT0により制御されるプルダウン用NMOSトランジスタN8aが接続されている。このPMOSトランジスタP6aとプルダウン用NMOSトランジスタN8aは、ノードAOUT1a、従って出力ノードOUTaの電圧レベルを電源投入時に初期設定する初期設定回路5aを構成している。

30

## 【0023】

即ち電源投入時、ノードACT0が“L”であれば、ノードAOUT1aはPMOSトランジスタP6aにより充電されて、“H”となり、出力ノードOUTaは“L”になる。ノードACT0が“H”であれば、ノードAOUT1aはNMOSトランジスタN8aにより放電されて“L”になる。

## 【0024】

第2の遅延回路11b側でも対応するノードAOUT1bには同様に、プリチャージ用PMOSトランジスタP6bと、ノードACT1により逝去されるプルダウン用NMOSトランジスタN8bによる初期設定回路5bが接続されている。従って、電源投入時、ノードACT1の“L”, “H”に応じて、出力ノードOUTbは“L”, “H”になる。

40

## 【0025】

これにより電源投入初期に、出力ドライバ12は、遅延回路11a, 11bに遅延出力が得られる前に、入力ノードINの論理信号レベルに応じた出力レベルに初期設定されることになる。具体的に入力ノードINが“H”であれば、PMOSトランジスタP11がオン、NMOSトランジスタN11がオフとなり、出力ノードOUTは“H”となる。入力ノードINが“L”であれば、出力ノードOUTは“L”となる。

## 【0026】

50

出力ノードOUTには、2段のインバータI11, I12によりその電位を正帰還制御する帰還回路13が構成されている。第1の遅延回路11aの出力ノードOUTaと第2の遅延回路11bの出力ノードOUTbは、基本的には一方が“H”のとき他方が“L”になるという相補的な変化を示すが、共に“H”となる期間が存在する。この期間出力ノードOUTは、高インピーダンス(HiZ)のフローティング状態となる。帰還回路13は、出力ノードOUTがフローティングになるときに、そのレベルを安定に保つための働きをする。

#### 【0027】

第2の遅延回路11bは、前述のようにインバータI1の出力ノードACT0を入力ノードとする(言い換えれば、第1の遅延回路11aとは論理反転した信号が入る)他、その構成は第1の遅延回路11aと同様である。従ってその構成の詳細説明は省く。10

#### 【0028】

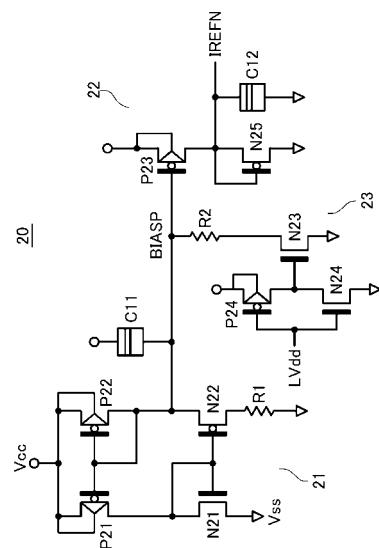

図1のインバータI3a, I3b及び差動アンプ3a, 3bに与えられる参照電圧IREFNは、図2に示すような公知の参照電圧発生回路20により発生される。この参照電圧発生回路20は、ウィルソン型カレントミラー回路を用いた参照電流源回路21を有する。この参照電流源回路21の出力BIASPにより駆動されるPMOSトランジスタP23と、ダイオード接続されたNMOSトランジスタN25の部分が定電圧出力回路22を構成している。

#### 【0029】

参照電流源回路21の出力BIASPには、起動回路23が接続されている。起動回路23のPMOSトランジスタP24とNMOSトランジスタN24からなるインバータは、電源電圧Vccの立ち上がりに遅れて立ち上がる内部電源電圧LVddにより駆動される。従って電源投入初期、このインバータ出力によりNMOSトランジスタN23がオン駆動されて、ノードBIASPが低レベルに初期設定される。20

#### 【0030】

定電圧出力回路22は、ノードBIASPにより制御されるPMOSトランジスタP23の負荷曲線とNMOSトランジスタN25のI-V曲線の交点位置により決まる定電圧を出力する。参照電流源回路21のPMOSトランジスタP22と定電圧発生回路22のPMOSトランジスタP23はカレントミラー回路を構成しているから、定電圧出力回路22の出力電圧は、電源電圧に依存しない参照電圧IREFNとなる。これが遅延回路11a, 11bに共通に供給される。30

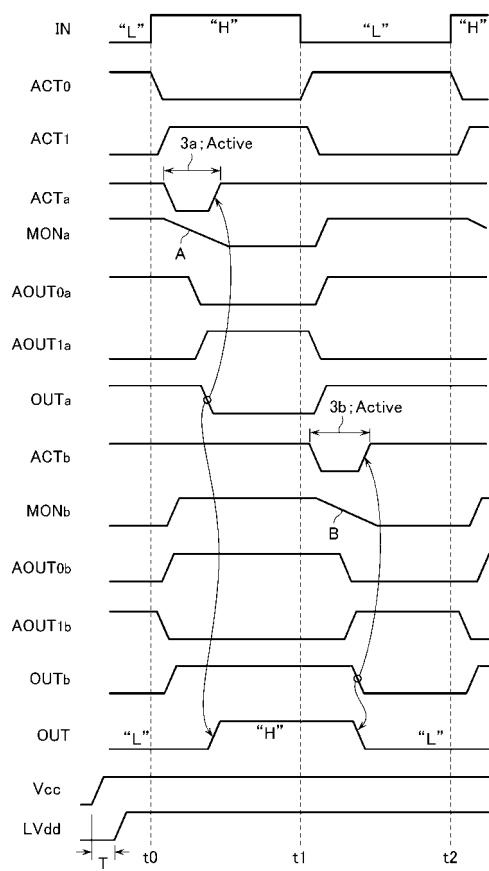

#### 【0031】

次にフィルタ回路10の動作を、図4のタイミング図を参照して具体的に説明する。図4では、入力ノードINの論理信号が“L”, “H”, “L”, “H”とレベル変化する場合について、各部動作波形を示している。例えば、“L”, “H”レベルはそれぞれ、論理“0”, “1”データに対応する。この実施の形態では前述のように、遅延回路を構成する初段インバータI3a, I3bとそれらの出力ノードMONa, MONbに接続されたキャパシタCa, Cbにより、出力ノードMONa, MONbの“H”レベルからの立ち下がり波形に一定の遅延を与えることで、グリッチ除去を行う。このために、入力ノードINの“L”から“H”への立ち上がりに対する遅延処理とグリッチ除去を行う第1の遅延回路11aと、入力ノードINの“H”から“L”への立ち下がりに対する遅延処理とグリッチ除去を行う第2の遅延回路11bの二系統を併設している。40

#### 【0032】

図4には、電源投入時、電源電圧Vccに一定時間Tだけ遅れて内部電源電圧LVddが立ち上がる様子を示している。その遅延時間Tの間、遅延回路11a, 11bでは、PMOSトランジスタP6a, P6bがオンになる。また、ノードACT0, ACT1に応じて、NMOSトランジスタN8a, N8bの一方がオンになる。即ち初期設定回路5a, 5bにより、ノードAOUT1a, AOUT1bのレベルが初期設定される。

#### 【0033】

図4の例では、タイミングt0以前、入力ノードINが“L”的間、ノードACT0が50

“H”，ノードA C T 1が“L”である。従って、第1の遅延回路11aのノードA O U T 1 aが“L”、第2の遅延回路11bのノードA O U T 1 bが“H”になる。これを受け、出力ノードO U Tは、入力ノードI Nの“L”レベルに対応して“L”レベルに設定される。

#### 【0034】

タイミングt0で入力ノードI Nが“L”から“H”にレベル遷移すると、これを受け第1の遅延回路11aでは、N A N Dゲート2aの出力ノードA C T aが“L”レベルになる。これにより、差動アンプ3aが活性化される。また、A C T 1 = “H”を受けて、インバータI 3 aの出力ノードM O N aが“H”から“L”に遷移する。その立ち下がり波形Aは、放電電流が制限されるインバータI 3 aにより、緩やかになる。このレベル遷移による一定の遅延時間をもって、差動アンプ3aの出力ノードA O U T 0 aが“L”レベルになる。10

#### 【0035】

出力ノードA O U T 0 aの“L”レベルは、A C T 1 = “H”とA O U T 1 a = “H”により制御されるN M O SトランジスタN 6 a, N 7 aがオンになることで、その後差動アンプ3aが非活性になっても保持される。

#### 【0036】

差動アンプ3aの出力ノードA O U T 0 aの“L”を受けて、出力ノードO U T aが“L”になると、これを受けて出力ドライバ12のP M O SトランジスタP 1 1がオンになる。この間、第2の遅延回路11bでは、N A N Dゲート2bの出力ノードA C T bは“H”であり、差動アンプ3bは非活性に保たれる。また、N M O SトランジスタN 8 bがノードA C T 1の“H”レベルを受けてオンであり、出力ノードO U T bは、入力ノードI Nのレベル遷移から早いタイミングで“H”になっている。20

#### 【0037】

従って、フィルタ出力ノードO U Tは、第1の遅延回路11aのノードA O U T aの“L”レベルへの遷移を受けて、“H”になる。言い換えば、出力ノードO U Tは、タイミングt0から一定の遅延時間をもって立ち上がる。同時に、出力ノードO U T aの“L”を受けて、N A N Dゲート2aの出力ノードA C T aは“H”になり、以後差動アンプ3aは非活性になる。

#### 【0038】

この様にして、入力ノードI Nの信号レベルが立ち上がると、第1の遅延回路11aが活性になって、インバータI 3 aとキャパシタC aによりグリッチが抑圧乃至除去される。そして、出力ノードO U Tには、入力ノードI Nの立ち上がりエッジから一定の遅延を受けて立ち上がる“H”レベルが得られる。入力ノードI Nが“H”的間、第2の遅延回路11bは非活性である。30

#### 【0039】

次に、入力ノードI Nがタイミングt1で“H”から“L”に遷移すると、第2の遅延回路11bにおいて差動アンプ3bが活性になる。また、第2の遅延回路11bにおいて、インバータ1bの出力ノードM O N bの“H”から“L”への立ち下がり波形Bは、電流源トランジスタN 2 bとキャパシタC bにより決まる緩やかな放電波形となる。40

#### 【0040】

そして、先の第1の遅延回路11aでの動作と同様に、一定の時間遅延を受けて、出力ノードO U T bが“L”になる。これを受け、差動アンプ11bは非活性になり、またフィルタ出力ノードO U Tが“L”になる。即ち入力ノードI Nの信号レベルが立ち下がると、第2の遅延回路11bが活性になって、そのインバータI 3 bとキャパシタC bによりグリッチが抑圧乃至除去される。

#### 【0041】

以上のようにこの実施の形態のフィルタ回路10では、二系統の遅延回路11a, 11bは、入力論理信号の各レベル遷移に応答して、その一方のみが動作状態になる。具体的に、差動増幅器3a, 3bは、入力ノードI Nのレベル遷移に応じて、遅延回路11a, 50

11 b の出力ノード OUT a , OUT b のレベルが確定するまでの間のみ活性化され、それ以外は非活性に保たれる。従ってこれらの差動アンプ 3 a , 3 b での貫通電流は必要最小限に抑えられており、無駄な消費電力のないフィルタ回路が得られる。

#### 【0042】

また入力ノード IN のレベル変化を受けるインバータ I 3 a , I 3 b において、それらの出力ノード MON a , MON b の “H” から “L” への、大きい放電時定数による立ち下がり遅延を利用して、グリッヂ除去を行っている。この出力ノード MON a , MON b の放電動作は、電源電圧に依存しない参照電圧 IREFN により駆動される電流源 NMOS トランジスタ N 2 a , N 2 b の定電流による放電波形を利用している。またノード MON a , MON b のレベル遷移を検出するカレントミラー型差動アンプ 3 a , 3 b にも、電源電圧に依存しない参照電圧 IREFN が用いられている。更に、インバータ I 3 a , I 3 b の電流源 NMOS トランジスタ N 2 a , N 2 b 及び差動アンプ 3 a , 3 b には、しきい値のばらつきの小さい I 型トランジスタを用いている。これらの理由でこの実施の形態のフィルタ回路 10 では、インバータチェーンと積分回路を組み合わせる従来のフィルタ回路と比べて、電源電圧依存性が少なく、しきい値のばらつきの影響が小さい特性が得られる。10

#### 【0043】

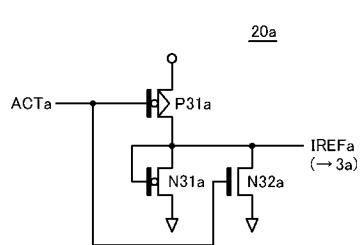

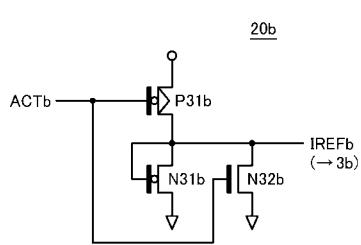

上記実施の形態では、各遅延回路 11 a , 11 b に対して図 2 に示す共通の参照電圧発生回路 20 が常時参照電圧 IREFN を供給している。これに対して、差動アンプ 3 a , 3 b の活性化と同期して、これらに参照電圧を与えるようにすることができる。例えば、差動アンプ 3 a 及び 3 b に対してそれぞれ、図 3 A 及び図 3 B に示す参照電圧発生回路 20 a 及び 20 b を用意すればよい。20

#### 【0044】

これらの参照電圧発生回路 20 a , 20 b はそれぞれ、ノード ACT a , ACT b により制御される I 型 PMOS トランジスタ P 31 a , P 31 b の負荷と、ダイオード接続された I 型 NMOS トランジスタ N 31 a , N 31 b を有する。それらの出力ノードにはリセット用 NMOS トランジスタ N 32 a , N 32 b が接続されている。

#### 【0045】

図 3 A の参照電圧発生回路 20 a は、ノード ACT a が “L” の間、PMOS トランジスタ P 31 a がオンになり、参照電圧 IREFa を出力する。即ち遅延回路 11 a の差動アンプ 3 a が活性化される間のみ活性化されて、参照電圧 IREFa が差動アンプ 3 a に与えられる。図 3 B の参照電圧発生回路 20 b は、ノード ACT b が “L” の間、PMOS トランジスタ P 31 b がオンになり、参照電圧 IREFb を出力する。即ち遅延回路 11 b の差動アンプ 3 b が活性化される間のみ活性化されて、参照電圧 IREFb が差動アンプ 3 b に与えられる。また差動アンプ 3 a , 3 b が非活性の間は、リセットトランジスタ N 32 a , N 32 b がオンして、参照電圧発生回路 20 a , 20 b の出力は “L” を保つ。30

#### 【0046】

このような参照電圧発生回路 20 a , 20 b を用いると、これらはスタンバイ時に貫通電流を流さないから、一層消費電力の削減が図られる。40

#### 【図面の簡単な説明】

#### 【0047】

【図 1】この発明の一実施の形態によるフィルタ回路の構成を示す図である。

【図 2】同フィルタ回路に用いられる参照電圧発生回路の構成を示す図である。

【図 3 A】他の実施の形態によるフィルタ回路の一方の差動アンプに用いられる参照電圧発生回路の構成を示す図である。

【図 3 B】同フィルタ回路の他方の差動アンプに用いられる参照電圧発生回路の構成を示す図である。

【図 4】実施の形態によるフィルタ回路の動作タイミング図である。

【図 5】従来のフィルタ回路の構成例を示す図である。50

## 【符号の説明】

## 【0048】

10... フィルタ回路、11a, 11b... 遅延回路、12... 出力ドライバ、13... 帰還回路、1a, 1b... LPF、2a, 2b... NANDゲート、3a, 3b... カレントミラー型差動増幅器、4a, 4b... ラッチ回路、5a, 5b... 初期設定回路、I3a, I3b~I7a, I7b... インバータ、Ca, Cb... キャパシタ、IN... 入力ノード、OUT... 出力ノード。

【図1】

【図2】

【図3A】

【図3B】

【図4】

【図5】

---

フロントページの続き

(56)参考文献 特開平05-225782(JP,A)

特開平07-098983(JP,A)

特開昭62-220026(JP,A)

特開昭63-010913(JP,A)

特表2003-518865(JP,A)

特開平05-002893(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03K 5/00 - 5/02 ; 5/08 - 5/12 ; 5/15 - 5/26

H03K 19/00 - 19/00、103 ; 19/01 - 19/082 ; 19/092 - 19

/096