(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2016년08월05일

(11) 등록번호 10-1645552

(24) 등록일자 2016년07월29일

- (51) 국제특허분류(Int. Cl.)

*G11C 7/10* (2015.01)

- (52) CPC특허분류

*G11C 7/1045* (2013.01)

*G11C 7/1051* (2013.01)

- (21) 출원번호 10-2015-7009592(분할)

- (22) 출원일자(국제) 2011년06월27일

심사청구일자 2015년04월20일

- (85) 번역문제출일자 2015년04월14일

- (65) 공개번호 10-2015-0047635

- (43) 공개일자 2015년05월04일

- (62) 원출원 특허 10-2012-7034084

원출원일자(국제) 2011년06월27일

심사청구일자 2012년12월27일

- (86) 국제출원번호 PCT/US2011/042029

- (87) 국제공개번호 WO 2012/006025

국제공개일자 2012년01월12일

- (30) 우선권주장

12/824,698 2010년06월28일 미국(US)

- (56) 선행기술조사문헌

US07342411 B2\*

T. Farrell, 'Core Architecture Doubles MEM Data Rate', Electronic Engineering Times Asia, December 16, 2005.\*

\*는 심사관에 의하여 인용된 문헌

전체 청구항 수 : 총 28 항

심사관 : 손윤식

(54) 발명의 명칭 동적 메모리 종단을 위한 방법 및 장치

**(57) 요약**

종단 신호 레벨에 응답하여 메모리의 메모리 입-출력(I/O) 인터페이스로의 하나 이상의 유한 종단 임피던스 값 설정들을 동적으로 전환하기 위한 방법 및 장치가 여기에 설명된다. 이 방법은: 메모리의 입-출력(I/O) 인터페이스의 종단 유닛을 위한 제1 종단 임피던스 값 설정을 설정하는 단계; 메모리가 액세스되어 있지 않을 때 종단 (뒷면에 계속)

**대 표 도 - 도1**

유닛에 제1 종단 임피던스 값 설정을 할당하는 단계; 및 종단 신호 레벨에 응답하여 제1 종단 임피던스 값 설정으로부터 제2 종단 임피던스 값 설정으로 전환하는 단계를 포함한다.

(52) CPC특허분류

*G11C 7/1057* (2013.01)

*G11C 7/1078* (2013.01)

*G11C 7/1084* (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

메모리의 입-출력(I/O) 인터페이스의 종단 유닛을 위한 제1 종단 임피던스 값 설정(termination impedance value setting)을 설정하는 단계;

상기 메모리가 액세스되지 않고, 종단을 활성화시킬 종단 신호가 디-어서트될 때 상기 종단 유닛에 상기 제1 종단 임피던스 값 설정을 디폴트 값 설정(default value setting)으로서 할당하는 단계; 및

연관된 메모리 제어기에 의한 상기 종단 신호의 어서션에 응답하여 상기 제1 종단 임피던스 값 설정으로부터 제2 종단 임피던스 값 설정으로 전환하는 단계 - 제1 및 제2 종단 임피던스 값들은 항상 유한한 값들이고, 상기 제1 종단 임피던스 값은 상기 제2 종단 임피던스 값보다 크며, 상기 제1 및 제2 종단 임피던스 값 설정들은 상기 메모리의 레지스터에 저장됨 -

를 포함하는 방법.

#### 청구항 2

제1항에 있어서, 상기 제1 종단 임피던스 값 설정을 설정하는 단계는, 운영 체제를 통해 상기 메모리에 있는 랜저스터를 상기 제1 종단 임피던스 값으로 설정하는 단계를 포함하는 방법.

#### 청구항 3

제1항에 있어서, 상기 종단 신호는 상기 메모리의 ODT(on-die termination) 신호인 방법.

#### 청구항 4

제3항에 있어서, 상기 제1 종단 임피던스 값 설정으로부터 제2 종단 임피던스 값 설정으로 전환하는 단계는 상기 ODT 신호가 어서트될 때 발생하는 방법.

#### 청구항 5

제3항에 있어서, 상기 종단 유닛에 상기 제1 종단 임피던스 값 설정을 할당하는 단계는 상기 ODT 신호가 디-어서트될 때 발생하는 방법.

#### 청구항 6

제1항에 있어서, 상기 종단 유닛은 켜지거나 꺼지도록 동작할 수 있는 복수의 풀-업 저항기들을 포함하고, 상기 종단 유닛에 상기 제1 종단 임피던스 값 설정을 할당하는 단계는 상기 복수의 저항기들 중의 저항기들을 켜거나 끄는 단계를 포함하는 방법.

#### 청구항 7

제1항에 있어서, 상기 메모리의 상기 I/O 인터페이스는 상기 메모리의 DDR4(Double Data Rate 4) 인터페이스인 방법.

#### 청구항 8

제1항에 있어서, 상기 메모리는, 하나 이상의 DRAM(Dynamic Random Access Memory)을 갖는 DIMM(Dual In-Line Memory Module)인 메모리 모듈에 있는 방법.

#### 청구항 9

제1항에 있어서, 상기 메모리는 DRAM인 방법.

#### 청구항 10

메모리에 액세스하도록 동작할 수 있는 인터페이스 - 상기 메모리는, 상기 메모리의 입-출력(I/O) 인터페이스의 종단 유닛을 위한 제1 종단 임피던스 값 설정을 갖는 레지스터를 구비함 -;

상기 메모리가 액세스되지 않고, 종단을 활성화시킬 종단 신호가 디-어서트될 때, 상기 종단 유닛에 상기 제1 종단 임피던스 값 설정을 디폴트 값 설정으로서 할당하도록 동작할 수 있는 제1 논리 유닛; 및

연관된 메모리 제어기에 의한 상기 종단 신호의 어서션에 응답하여 상기 제1 종단 임피던스 값 설정으로부터 제2 종단 임피던스 값 설정으로 전환하도록 동작할 수 있는 제2 논리 유닛 - 제1 및 제2 종단 임피던스 값들은 항상 유한한 값들이고, 상기 제1 종단 임피던스 값은 상기 제2 종단 임피던스 값보다 크며, 상기 제1 및 제2 종단 임피던스 값 설정들은 상기 메모리의 레지스터에 저장됨 -

을 포함하는 장치.

#### **청구항 11**

제10항에 있어서, 상기 메모리의 상기 I/O 인터페이스는 상기 메모리의 DDR4 인터페이스인 장치.

#### **청구항 12**

제10항에 있어서, 상기 메모리는 DRAM인 장치.

#### **청구항 13**

제10항에 있어서, 상기 메모리는, 하나 이상의 DRAM을 갖는 DIMM인 메모리 모듈에 있는 장치.

#### **청구항 14**

제10항에 있어서, 상기 종단 유닛은 상기 종단 신호의 어서션에 응답하여 켜거나 꺼도록 동작할 수 있는 복수의 풀-업 저항기들을 포함하는 장치.

#### **청구항 15**

제14항에 있어서, 상기 제1 및 제2 논리 유닛은, 상기 종단 유닛의 임피던스를 상기 제1 및 제2 종단 임피던스 값 설정으로 각각 설정하기 위해, 상기 복수의 저항기들 중의 저항기들을 켜거나 끄도록 동작할 수 있는 장치.

#### **청구항 16**

제10항에 있어서, 상기 레지스터는 운영 체제를 통해 상기 제1 및 제2 종단 임피던스 값으로 설정되도록 동작할 수 있는 장치.

#### **청구항 17**

제10항에 있어서, 상기 종단 신호는 상기 메모리의 ODT 신호인 장치.

#### **청구항 18**

제17항에 있어서, 상기 제2 논리 유닛은, 상기 ODT 신호가 어서트될 때, 상기 제1 종단 임피던스 값 설정으로부터 상기 제2 종단 임피던스 값 설정으로 전환하도록 동작할 수 있는 장치.

#### **청구항 19**

제17항에 있어서, 상기 제1 논리 유닛은, 상기 ODT 신호가 디-어서트될 때, 상기 종단 유닛에 상기 제1 종단 임피던스 값 설정을 할당하도록 동작할 수 있는 장치.

#### **청구항 20**

메모리 - 상기 메모리는, 상기 메모리의 I/O 인터페이스의 종단 유닛을 위한 제1 종단 임피던스 값 설정을 저장하도록 동작할 수 있는 레지스터를 구비함 -; 및

상기 메모리에 결합되고, 상기 메모리의 상기 I/O 인터페이스의 종단 임피던스 설정을 조정하도록 동작할 수 있는 메모리 제어기

를 포함하고,

상기 메모리 제어기는,

상기 메모리가 액세스되지 않고, 종단을 활성화시킬 종단 신호가 디-어서트될 때, 상기 종단 유닛에 상기 제1 종단 임피던스 값 설정을 디풀트 값 설정으로서 할당하도록 동작할 수 있는 제1 논리 유닛; 및

상기 메모리 제어기에 의한 상기 종단 신호의 어서션에 응답하여 상기 제1 종단 임피던스 값 설정으로부터 제2 종단 임피던스 값 설정으로 전환하도록 동작할 수 있는 제2 논리 유닛 - 제1 및 제2 종단 임피던스 값들은 항상 유한한 값들이고, 상기 제1 종단 임피던스 값은 상기 제2 종단 임피던스 값보다 큼 -;

을 포함하는 시스템.

### 청구항 21

제20항에 있어서, 상기 메모리의 상기 I/O 인터페이스는 상기 메모리의 DDR4 인터페이스인 시스템.

### 청구항 22

제20항에 있어서, 상기 메모리는 DRAM인 시스템.

### 청구항 23

제20항에 있어서, 상기 메모리는, 하나 이상의 DRAM을 갖는 DIMM인 메모리 모듈에 있는 시스템.

### 청구항 24

제20항에 있어서, 상기 종단 유닛은 상기 종단 신호의 어서션에 응답하여 켜지거나 꺼지도록 동작할 수 있는 복수의 풀-업 저항기들을 포함하는 시스템.

### 청구항 25

제24항에 있어서, 상기 제1 및 제2 논리 유닛은, 상기 종단 유닛의 임피던스를 상기 제1 및 제2 종단 임피던스 값 설정들로 각각 설정하기 위해, 상기 복수의 저항기들 중의 저항기들을 켜거나 끄도록 동작할 수 있는 시스템.

### 청구항 26

제20항에 있어서, 상기 레지스터는 운영 체제 또는 상기 메모리 제어기에 의해 상기 제1 및 제2 종단 임피던스 값들로 설정되도록 동작할 수 있는 시스템.

### 청구항 27

제20항에 있어서, 상기 종단 신호는 상기 메모리의 ODT 신호인 시스템.

### 청구항 28

제27항에 있어서, 상기 제2 논리 유닛은, 상기 ODT 신호가 어서트될 때, 상기 제1 종단 임피던스 값 설정으로부터 상기 제2 종단 임피던스 값 설정으로 전환하도록 동작할 수 있고, 상기 제1 논리 유닛은, 상기 ODT 신호가 디-어서트될 때, 상기 종단 유닛에 상기 제1 종단 임피던스 값 설정을 할당하도록 동작할 수 있는 시스템.

## 발명의 설명

### 기술 분야

[0001] 본 발명의 실시예들은 일반적으로 메모리의 분야에 관한 것이다. 보다 구체적으로, 본 발명의 실시예들은 종단 신호 레벨에 응답하여 메모리의 메모리 입-출력(I/O) 인터페이스로의 하나 이상의 유한 종단 임피던스 값 설정들을 동적으로 전환하기 위한 방법 및 장치에 관한 것이다.

### 배경 기술

[0002] 컴퓨터 시스템의 전형적인 메모리 시스템에서, 메모리 제어기는 컴퓨터 시스템에서 메모리 모듈의 액세스를 용

이하게 한다. 메모리 모듈은 랭크로서 지칭되는 하나 이상의 메모리를 포함할 수 있다. 메모리 제어기는 입-출력(I/O) 인터페이스 및 전송선(transmission lines)을 통해 메모리 모듈의 랭크들과 통신한다. I/O 인터페이스는 메모리 제어기 단부 및 메모리 모듈 단부 양측에 존재한다. 메모리 제어기는, 그것의 I/O 인터페이스를 통해, 어드레스 신호, 제어 신호, 클록 신호 등을 포함하는 다수의 신호들(a host of signals)을 랭크들로 전송하여, 랭크들로부터의 데이터에 액세스하거나 랭크들에게 데이터를 전송한다.

[0003] 랭크들과 메모리 제어기 사이의 정확한 통신을 위해, 메모리 제어기 및/또는 랭크들의 I/O 인터페이스들에 종단 임피던스가 설정된다. 여기에서 정확한 통신(correct communication)이라는 용어는 메모리 모듈과 메모리 제어기 사이에서 예상되는 데이터를 전송 및/또는 수신하는 것을 지칭하고, 예상되는 데이터는 성능 사양들, 예컨대, 타이밍, 전압 마진, 신호 무결성 등을 충족한다. 종단 임피던스의 값은 메모리 제어기와 랭크들 사이에서 통신되는 신호의 품질을 결정한다.

[0004] 일반적으로, 메모리 제어기에 의해 개시된 메모리 액세스(예컨대, 메모리 판독) 동안, 랭크들에서 I/O 인터페이스의 종단 임피던스는 랭크와 메모리 제어기 사이에서 통신되는 신호에 대한 노이즈를 감소시키기 위한 값으로 설정된다. DDR3(Double Data Rate 3) I/O 인터페이스에 대해, 메모리 제어기는 단지 단일 유한 종단 값에 액세스되는 랭크들의 DDR3 I/O 인터페이스에 종단 임피던스를 설정하도록 동작할 수 있다. 액세스되어 있지 않은 랭크들의 DDR3 I/O 인터페이스에 대한 종단 임피던스는 디폴트 종단 임피던스 값으로서 고 임피던스 값(종단 디바이스들을 3 상태로 하여 야기된 무한 임피던스)이 설정된다.

[0005] 고 임피던스 값인 DDR3 I/O 인터페이스에 대한 디폴트 종단 임피던스 값을 갖는 하나의 이유는 전력 소비를 절약하기 위한 것이다. DDR3 I/O 인터페이스는 파워 서플라이 노드(power supply node)에 접속된 풀-업 종단 저항기(pull-up termination resistor) 및 그라운드 서플라이 노드(ground supply node)에 접속된 풀-다운 종단 저항기(pull-down termination resistor)를 구비하는 중간-탭 종단 체계(center-tap termination scheme)를 갖는 사양에 의해 요구된다. 이러한 중간-탭 종단 체계는 풀-다운 종단 저항기와 풀-다운 종단 저항기를 통해 파워 서플라이 노드로부터 그라운드 노드로 전기적 경로를 제공한다. 전기적 경로는 중간-탭 종단 체계가 인에이블될 때 전력 소비의 소스이다.

[0006] 랭크에 대한 메모리 액세스가 존재하지 않을 때 DDR3 I/O 인터페이스에서의 전력 소비를 줄이기 위해, 랭크의 종단 임피던스는 고 임피던스의 디폴트 값으로 유지된다. 이러한 고 종단 임피던스(즉, 무한 임피던스)는 메모리 제어기와 다른 활성 랭크들 사이에서 통신되는 판독 신호들에 대한 타이밍 및 전압 마진을 줄인다. 메모리 I/O 인터페이스의 더 높은 속도, 예컨대, 초당 1600-3200 메가 트랜스퍼(MT/s)의 DDR3 I/O 인터페이스 속도 대(vs.) DDR4(Double Data Rate 4) I/O는 인터페이스에 대한 800-1600 MT/s에 대한 요구가 증가함에 따라, 고 종단 임피던스의 디폴트 값은 메모리 시스템 성능을 감소시킨다.

### 도면의 간단한 설명

[0007] 본 발명의 실시예들은 아래에 주어진 상세한 설명으로부터 및 본 발명의 다양한 실시예들의 첨부 도면들로부터 더 충분히 이해될 것이지만, 본 발명을 특정 실시예들로 제한하기 위해 취해진 것이 아니고, 단지 설명 및 이해를 위한 것이다.

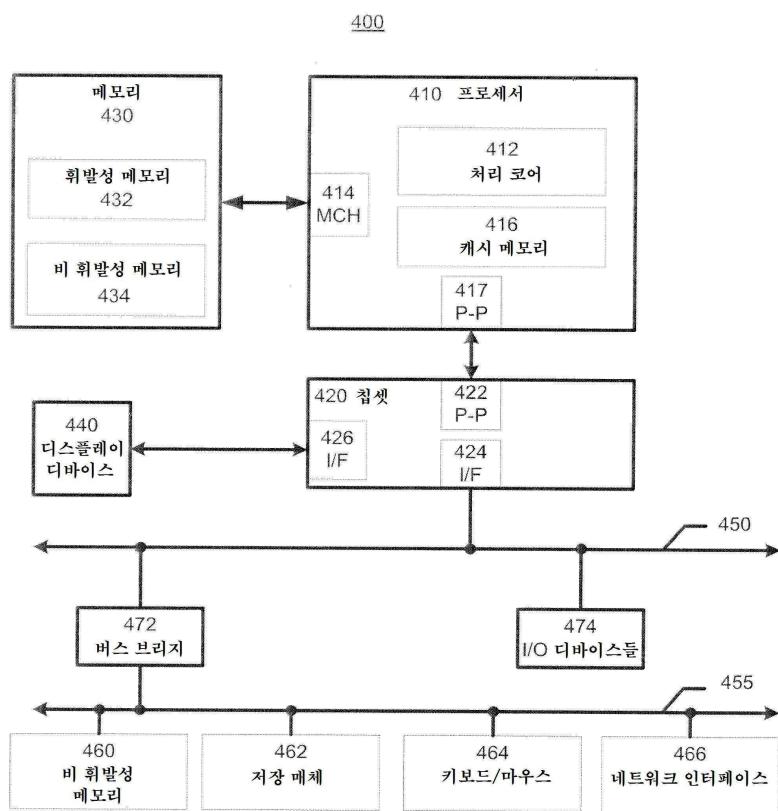

도 1은, 본 발명의 하나의 실시예에 따라, 메모리 모듈들 내에 있는 랭크들에 유한 종단 임피던스 설정들을 동적으로 제공하기 위한 메모리 제어기와 메모리 모듈들을 포함하는 메모리 시스템이다.

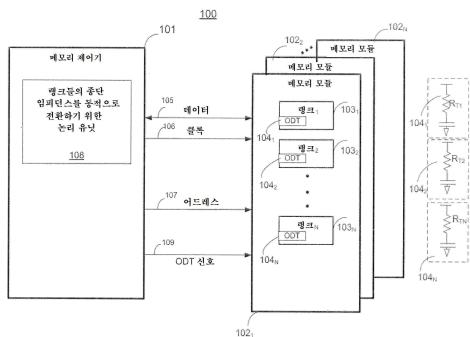

도 2a는, 본 발명의 하나의 실시예에 따라, 랭크들에 유한 종단 임피던스 설정들을 동적으로 제공하기 위한 메모리 제어기이다.

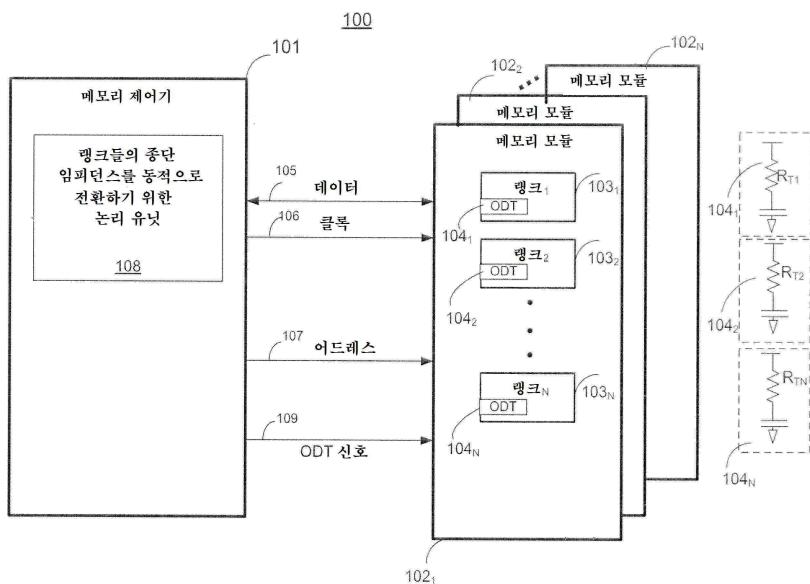

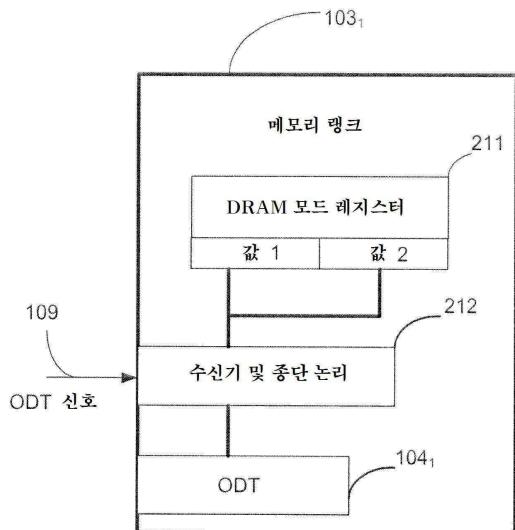

도 2b는, 본 발명의 하나의 실시예에 따라, 메모리 랭크의 ODT(on-die termination) 유닛에 유한 종단 임피던스 설정들을 동적으로 제공하기 위한 메모리 랭크이다.

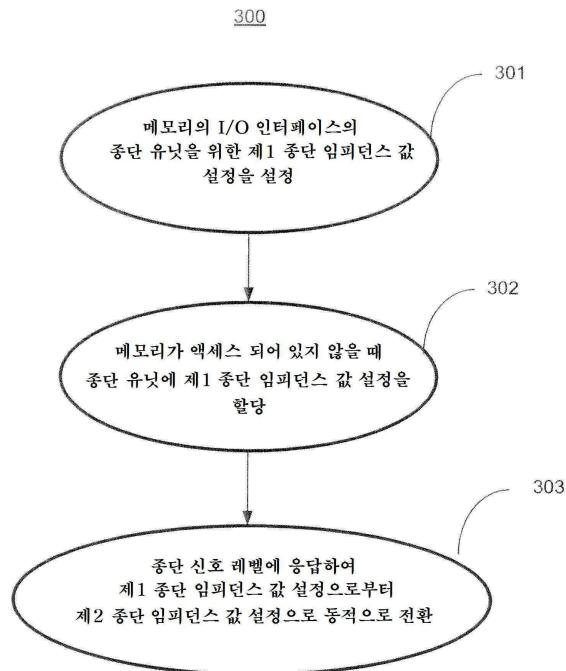

도 3은, 본 발명의 하나의 실시예에 따라, 메모리 랭크들에 유한 종단 임피던스 설정들을 동적으로 제공하기 위한 순서도이다.

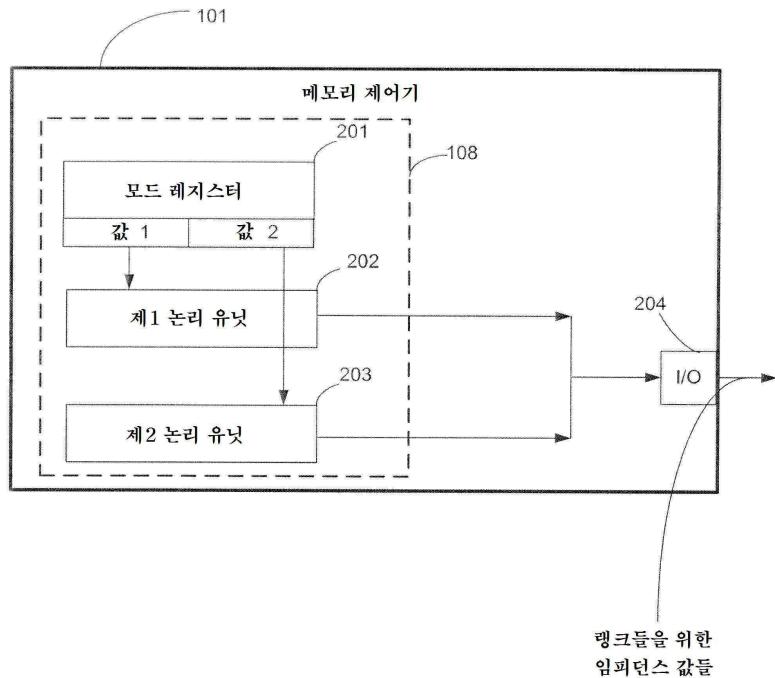

도 4는, 본 발명의 하나의 실시예에 따라, 메모리 랭크들에 동적 메모리 종단 임피던스 설정들을 제공하기 위한 방법을 구현하는 컴퓨터 시스템이다.

### 발명을 실시하기 위한 구체적인 내용

[0008] 본 발명의 실시예들은 종단 신호 레벨에 응답하여 메모리의 메모리 입-출력(I/O) 인터페이스로의 하나 이상의

유한 종단 임피던스 값 설정들을 동적으로 전환하기 위한 방법 및 장치에 관한 것이다.

[0009] 하나의 실시예에서, 메모리 제어기는 레지스터로부터 제1 유한 임피던스 값 설정을 판독하고, 그 값 설정을, 액세스되어 있지 않은 메모리 랭크들 중 하나의 종단 유닛에 할당한다. 메모리 액세스가 존재하지 않을 때 디폴트 값으로서 랭크들에 대해 고 임피던스 종단 값을 갖는 것과 반대로, DDR3(Double Data Rate 3) I/O 인터페이스에 대한 경우와 같이, 여기의 실시예에서는, 제1 프로그래밍할 수 있는 유한 임피던스 값 설정이 액세스되어 있지 않은 랭크들의 종단 유닛에 할당된다. 하나의 실시예에서, 제2 종단 임피던스 값 설정은, 종단 신호 레벨이 어서트할 때 액세스되는 랭크들에 할당된다. 여기에서 논의된 실시예들에서, 제1 및 제2 종단 임피던스 값들 다 프로그래밍할 수 있다.

[0010] 하나의 실시예에서, 메모리 제어기가 랭크들 중 하나로부터의 메모리 액세스를 개시할 때, 데이터가 액세스되는 랭크의 종단 유닛은 제2 종단 임피던스 값을 갖도록 구성된다. 이러한 실시예에서, 액세스되는 랭크의 종단 유닛은, 종단 신호 레벨이 어서트될 때, 제1 유한 프로그래밍할 수 있는 종단 임피던스 값 설정으로부터 제2 종단 임피던스 값 설정으로 그의 종단 임피던스 값 설정을 전이하도록 동작할 수 있다. 아래 논의된 바와 같이, 종단 신호는 ODT(on-die termination) 신호이다.

[0011] 여기에서 실시예들은, 랭크의 메모리 액세스 동안 고 임피던스 종단 값 설정으로부터 유한 임피던스 종단 값 설정으로 전이하도록 구성되는 종래의 아키텍처에 비해, 랭크들의 메모리 액세스에 대한 타이밍 및 전압 마진에 있어서 20-30% 향상을 야기한다. 결과적으로, 여기에서의 실시예들은, 종단 유닛들에 대한 종단 임피던스 값 설정들의 동적 전환을 허용하지 않는 메모리 시스템들에 비해 타이밍 마진이 향상하므로, 메모리 시스템들의 더 높은 수율(즉, 더 적은 고장 부품들)을 야기한다.

[0012] 여기에서 동적 전환(dynamic switching)이라는 용어는, 종단 유닛들이 고 임피던스 상태 또는 임의의 다른 중간 임피던스 상태로 전이하도록 하지 않고, 랭크들의 종단 유닛들에 대한 유한 임피던스 값 설정들을 전환하는 것을 지칭한다. 이러한 전환은, 종단 신호 레벨이 하나의 논리 레벨에서 또 다른 논리 레벨로 바뀔 때 메모리 액세스에 응답하여 하나의 종단 임피던스 값 설정으로부터 또 다른 종단 임피던스 값 설정으로 바로 발생한다.

[0013] 여기에서 고 임피던스(high impedance)라는 용어는, 종단 유닛 단부(termination unit end)에서 전송선 상의 신호들의 풀 반사(full reflection)를 야기하는 종단 유닛을 끄는 것(즉, 종단 유닛을 3 상태로 설정하는 것)에 의해 야기된 무한 임피던스를 지칭한다. 하나의 실시예에서, I/O 인터페이스는 풀-업 저항기들을 포함하고 풀-다운 저항기들을 포함하지 않는 종단 유닛을 갖는 DDR4(Double Data Rate 4) 인터페이스이다. 하나의 실시예에서, I/O 인터페이스는 풀-다운 저항기들을 갖고 풀-업 저항기들을 갖지 않는 종단 유닛을 포함한다.

[0014] 본 발명의 하나의 실시예에서, 하나 이상의 랭크들은 SDRAM(Synchronous Dynamic Random Access Memory), DRAM(Dynamic Random Access Memory), RDRAM(RAMBUS Dynamic Random Access Memory), DDR4 SDRAM, 및 임의의 다른 유형의 랜덤 액세스 메모리 디바이스를 포함한다. 하나의 실시예에서, 랭크들은 메모리 모듈에 있다.

[0015] 본 발명의 실시예들을 모호하게 하지 않기 위해, 여기에서의 실시예들은, 랭크들로도 불리는, 하나 이상의 SDRAM들을 갖는 DIMM(Dual In-Line Memory Module)을 참조하여 논의되고, 여기에서 DIMM은 DDR4 I/O 인터페이스를 통해 메모리 모듈에 통신가능하게 결합된다. 그러나, 상기 실시예들이 실시예들을 제한하는 것은 아니다. 다른 메모리 모듈들(DIMM 외의), 메모리 모듈들이 없는 메모리들, 및 다른 I/O 인터페이스들(예컨대, DDR4 I/O 인터페이스보다 더 최신의 I/O 인터페이스들)을 갖는 다른 실시예들이 본 발명의 본질을 바꾸지 않고 사용될 수 있다.

[0016] 다음 설명에서, 본 발명의 실시예들에 대한 보다 철저한 설명을 제공하기 위해 많은 상세들이 논의된다. 그러나, 본 발명의 실시예들은 이러한 구체적인 상세 없이 실행될 수 있다는 것이 당업자에게는 명백할 것이다. 본 발명의 실시예들을 모호하게 하는 것을 피하기 위해, 경우에 따라, 잘-알려진 구조들 및 디바이스들은 자세하기 보다 블록도 형태로 도시된다.

[0017] 실시예들의 해당 도면들에서, 신호들은 라인들로 표현된다는 것에 주의한다. 일부 라인들은, 더 많은 구성 요소 신호 경로들을 나타내기 위해 더 두꺼울 수 있고, 및/또는 주요 정보 흐름 방향을 나타내기 위해 하나 이상의 단부에 화살표들을 구비할 수 있다. 이러한 표시들은 한정하기 위한 것이 아니다. 오히려, 라인들은 회로 또는 논리 유닛에 대한 이해를 더 용이하게 하기 위해 하나 이상의 예시적인 실시예와 관련하여 사용된다. 설계 요구나 선호에 의해 지시되는 것으로서, 임의의 표현 신호는 실제로 어느 하나의 방향으로 이동할 수 있는 하나 이상의 신호를 포함할 수 있고, 임의의 적절한 유형의 신호 체계, 예컨대, 차동 쌍, 싱글-엔드 등으로 구현될 수 있다.

- [0018] 도 1은, 본 발명의 하나의 실시예에 따라, 메모리 모듈들( $102_{1-N}$ )에 대해 프로그래밍할 수 있는 유한 종단 임피던스 값을 동적으로 설정하도록 동작할 수 있는 메모리 제어기(101)를 포함하는 메모리 시스템(100)이다. 하나의 실시예에서, 메모리 제어기(101)는 마이크로프로세서(CPU) 내에 통합된다. 다른 실시예들에서, 메모리 제어기(101)는 마더보드 상의 별도의 집적 회로(IC)이고, 마더보드 라우팅(도시되지 않음) 및 커넥터들(도시되지 않음)을 통해 CPU(도시되지 않음) 및 메모리 모듈들( $102_{1-N}$ )에 결합된다.

- [0019] 본 발명의 하나의 실시예에서, 메모리 모듈( $102_1$ )은 하나 이상의 메모리들, 레지스터 디바이스들, 버퍼 디바이스들 등을 포함한다. 하나 이상의 메모리들은 또한 여기에서는 랭크들로서 지칭된다. 하나의 실시예에서, 랭크들( $103_{1-N}$ )은 SDRAM들이다. 하나의 실시예에서, 랭크들( $103_{1-N}$ )은 동일한 어드레스, 명령 및 제어 버스들을 공유한다. 하나의 실시예에서, 랭크들( $103_{1-N}$ )은 메모리 모듈에 존재하지 않는다. 하나의 실시예에서, 메모리 제어기(101)는, 메모리 제어기(101)와 메모리 모듈들( $102_{1-N}$ ) 사이의 통신을 야기하기 위해, 데이터 신호(105), 클록 신호(106), 어드레스 신호(107), ODT(on-die termination) 신호(109), 및 임의의 다른 신호들을 포함하는 신호들을 통해 메모리 모듈( $102_1$ )과 통신한다.

- [0020] 하나의 실시예에서, 랭크들( $103_{1-N}$ )의 각각의 I/O 핀/패드(도시되지 않음)는 종단 유닛( $104_{1-N}$ )을 갖는다. 하나의 실시예에서, 종단 유닛( $104_{1-N}$ )은 랭크( $103_{1-N}$ )의 다이 내(within the die)에 구현되는, 즉, ODT 유닛이다. 다른 실시예들에서, 종단 유닛( $104_{1-N}$ )은 다이에서 떨어져(off-die) 구현된다.

- [0021] 본 발명의 실시예들을 보호하게 하지 않기 위해, 각각의 랭크의 I/O 핀/패드는 도시되지 않는다. 또한, 여기에서의 실시예들에 대해 논의된 종단 유닛( $104_{1-N}$ )은 메모리 액세스 동안 전송선들에서의 신호 반사들을 캔슬하는 ODT 유닛이다. 당업자는 실시예들의 본질을 바꾸지 않고 ODT 유닛들을 다이에서 떨어진 종단 유닛들로 대체할 수 있다.

- [0022] 하나의 실시예에서, 메모리 제어기(101)가 ODT 신호(109)를 어서트할 때, 액세스되는 랭크들은 그들의 ODT 유닛들이 제2 종단 임피던스 값을 갖도록 설정한다. 하나의 실시예에서, ODT 신호(109)는 제어 신호이다. 하나의 실시예에서, 메모리 제어기(101)로부터 ODT 신호(109)를 수신하도록 동작할 수 있는, 랭크당 하나의 ODT 핀이 존재한다. 하나의 실시예에서, 제2 종단 임피던스 값을 모드 레지스터(mode register)에서 프로그래밍되고, 어서트되는 ODT 신호(109)에 응답하여 액세스된다. 하나의 실시예에서, 모드 레지스터는 메모리 제어기(101)에 있다. 또 다른 실시예에서, 모드 레지스터는 메모리 모드 레지스터(예컨대, DRAM 모드 레지스터)이고, 각각의 메모리 랭크에 있다.

- [0023] 하나의 실시예에서, ODT 유닛( $104_1$ )은 I/O 핀에 결합된 풀-업 저항기( $R_{T1}$ ) 및 풀-다운 커패시터를 포함한다. 하나의 실시예에서, 저항기( $R_{T1}$ )의 값은 DDR4 I/O 인터페이스의 사양에 따라 구성/설정된다. 위에서 언급된 바와 같이, DDR3 I/O 인터페이스 및 이전의 DDR I/O 인터페이스의 종단 유닛들과는 반대로, 본 발명의 실시예들의 ODT 유닛들( $104_{1-N}$ )은 종단 유닛들 내에 파워 서플라이로부터 그라운드까지의 전기적 경로를 갖지 않는다. 그 결과, ODT 유닛들( $104_{1-N}$ )은, ODT 신호(109)가 디-어서트될 때 ODT 유닛들( $104_{1-N}$ )에 결합된 전송선들에서의 신호 레벨들을 메모리 제어기(101)가 풀-업하므로, DDR3 I/O 인터페이스 및 이전의 DDR I/O 인터페이스의 종단 유닛들보다 적은 전력을 소모한다.

- [0024] ODT 유닛들( $104_{1-N}$ )이 하나의 풀-업 저항기를 갖는 것으로 도시되지만, 임의의 수의 풀-업 저항기들의 풀-업 저항기들을 포함할 수 있고, 여기에서, 풀-업 저항기들은 제1 및/또는 제2 종단 임피던스 값을 달성하기 위해 논리(도시되지 않음)를 통해 켜지거나 꺼지도록 동작할 수 있다. 하나의 실시예에서, 제1 임피던스 값을 180 옴인 한편 제2 임피던스 값을 60 옴이다.

- [0025] 하나의 실시예에서, 메모리 제어기(101)는 ODT 유닛들( $104_{1-N}$ )의 종단 임피던스를 동적으로 구성하기 위한 논리 유닛( $108$ )을 포함한다. 하나의 실시예에서, 논리 유닛( $108$ )은, 메모리 제어기(101)가 랭크들로부터의 메모리에 액세스하지 않을 때, ODT 유닛들( $104_{1-N}$ )의 임피던스를, 제1 유한 종단 임피던스 값 설정으로 설정하도록 동작할 수 있다. 이러한 실시예에서, ODT 신호(109)의 레벨은 디-어서트된다. 하나의 실시예에서, 논리 유닛은, ODT 신호(109)의 어서션(assertion)에 응답하여, ODT 유닛들( $104_{1-N}$ ) 중 임의의 것의 임피던스 값을 설정을, 제1 종단

임피던스 값 설정으로부터 제2 종단 임피던스 값 설정으로 동적으로 전환한다.

[0026] 여기에서 어서션(assertion)이라는 용어는 논리적 저 레벨(logical low level)에서 논리적 고 레벨(logical high level)로의 전이(transition)를 지칭한다. 유사하게, 여기에서 디-어서션(de-assertion)이라는 용어는 논리적 고 레벨에서 논리적 저 레벨로의 전이를 지칭한다. 따라서, 디-어서트된 신호는 논리적 저 레벨 신호인 한편 어서트된 신호는 논리적 고 레벨 신호이다.

[0027] 도 2a는, 본 발명의 하나의 실시예에 따라, 메모리 모듈들의 랭크들에 유한 종단 임피던스 설정들을 동적으로 제공하기 위한 메모리 제어기(200)(도 1의 101과 동일함)이다. 하나의 실시예에서, 메모리 제어기(101)는 각각 제1 및 제2 종단 임피던스 값(값 1 및 값 2)을 갖는 레지스터(201)를 포함한다. 하나의 실시예에서, 제1 및 제2 종단 임피던스 값은 프로그래밍할 수 있는 값들이다. 하나의 실시예에서, 제1 및 제2 종단 임피던스 값은, 메모리 시스템 부팅시에 설정된 미리 결정된 값들이다. 하나의 실시예에서, 레지스터(201)는 운영 체제를 통해 프로그래밍할 수 있다. 하나의 실시예에서, 제1 및 제2 종단 임피던스 값은 유한 값들이다.

[0028] 도 2b를 참조하여 논의된 하나의 실시예에서, 레지스터(201)는 랭크들(103<sub>1-N</sub>)에 있는 DRAM 모드 레지스터이고, 프로그래밍할 수 있는 제1 및 제2 종단 임피던스 값을 저장하도록 동작할 수 있다. 하나의 실시예에서, 복수의 랭크들(103<sub>1-N</sub>)의 각각의 랭크의 DRAM 모드 레지스터는 운영 체제 및/또는 메모리 제어기(101)를 통해 액세스 할 수 있다. 하나의 실시예에서, 메모리 제어기(101) 및/또는 BIOS(Basic Input-Output System)는 시스템 메모리에 기초한 모든 랭크의 DRAM 모드 레지스터들을 프로그래밍하도록 동작할 수 있다.

[0029] 도 2b는, 본 발명의 하나의 실시예에 따라, ODT 유닛(104<sub>1</sub>)에 대해 프로그래밍할 수 있는 제1 및 제2 종단 임피던스 값을 저장하도록 동작할 수 있는 DRAM 모드 레지스터(211)를 포함하는 메모리 랭크(103<sub>1</sub>)의 고 레벨 논리 블록도(210)이다. 본 발명의 실시예들을 모호하게 하지 않기 위해, 단일 메모리 랭크(103<sub>1</sub>)는 단일 I/O 펀/패드에 대해 단일 ODT 유닛(104<sub>1</sub>)을 갖도록 도시되고 있다. 그러나, 메모리 랭크(103<sub>1</sub>)는 각각의 펀/패드에 대해 다수의 ODT 유닛들을 갖고, 동일한 설명은 본 발명의 실시예에 따른 모든 메모리 랭크들(103<sub>1-N</sub>) 적용할 수 있다. 하나의 실시예에서, 메모리 랭크(103<sub>1</sub>)는 메모리 모듈에 있다. 다른 실시예들에서, 메모리 랭크(103<sub>1</sub>)는 메모리 모듈에 없다. 하나의 실시예에서, 메모리 랭크(103<sub>1</sub>)는 수신기(212)를 통해 메모리 제어기(101)로부터의 ODT 신호(109)를 수신한다.

[0030] 하나의 실시예에서, ODT 신호(109)의 논리 레벨에 따라, 수신기(212)에 결합된 종단 논리 유닛(212)(간단하게 할 목적으로 단일 블록으로 도시됨)은 ODT 유닛(104<sub>1</sub>)에게 제1 또는 제2 종단 임피던스 값을 할당한다. 하나의 실시예에서, 종단 논리 유닛(212)은 도 2a를 참조하여 논의된 제1 및 제2 논리 유닛(202 및 203)을 포함한다. 하나의 실시예에서, 종단 유닛(212)은 도 2a를 참조하여 아래 논의된 제1 및 제2 논리 유닛(202 및 203)으로부터 신호를 수신하여, DRAM 모드 레지스터(211)로부터 ODT 유닛(104<sub>1</sub>)에 제1 및 제2 종단 임피던스 값을 제공한다.

[0031] 하나의 실시예에서, ODT 신호(109)가 디-어서트될 때, ODT 유닛(104<sub>1</sub>)에 대한 디폴트 종단 임피던스 값인, 제1 종단 임피던스 값(값 1)이 DRAM 모드 레지스터(211)로부터 ODT 유닛(104<sub>1</sub>)에 할당된다. 하나의 실시예에서, ODT 신호(109)가 어서트될 때, 제2 종단 임피던스 값(값 2)이 DRAM 모드 레지스터(211)로부터 ODT 유닛(104<sub>1</sub>)에 할당된다. 하나의 실시예에서, DRAM 모드 레지스터(211)에서 종단 임피던스 값을(값 1 및 값 2)은 하드웨어나 소프트웨어를 통해 프로그래밍할 수 있다.

[0032] 도 2a를 다시 참조하면, 하나의 실시예에서, 메모리 제어기(101)는 제1 논리 유닛(202) 및 제2 논리 유닛(203)을 더 포함한다. 하나의 실시예에서, 제1 논리 유닛(202)은, 메모리 제어기(101)에 의해 액세스되어 있지 않는 랭크들(103<sub>1-N</sub>)에 대응하는 ODT 유닛들(104<sub>1-N</sub>) 중 임의의 것에, 레지스터(201)로부터의 제1 종단 임피던스 값을 설정을 할당하도록 동작할 수 있다. 이러한 실시예에서, ODT 신호(109)의 레벨은 디-어서트된다. 하나의 실시예에서, 제1 논리 유닛(202)은 랭크의 DRAM 모드 레지스터에 저장된 제1 종단 임피던스 값을 설정을 랭크의 ODT 유닛에 할당하도록 동작할 수 있다. 하나의 실시예에서, 제1 논리 유닛(202)은 제1 종단 임피던스 값을 설정을 갖도록 그들을 구성하기 위해, ODT 유닛들(104<sub>1-N</sub>)의 폴-업 저항기들을 켜거나 꺼서 제1 종단 임피던스 값을 설정을 할당하도록 동작할 수 있다.

- [0033] 위에서 언급된 바와 같이, ODT 신호(109)의 레벨은, 메모리 제어기(101)에 의해 액세스되어 있지 않은 랭크들의 ODT 유닛들(104<sub>1-N</sub>)에 대해 제1 종단 임피던스 값을 설정할 때 디-어서트된다. 하나의 실시예에서, 제2 논리 유닛(203)은, 어서트되는 ODT 신호(109)의 레벨에 응답하여 평가되는 랭크들의 ODT 유닛들(104<sub>1-N</sub>)에 대해 제1 종단 임피던스 값을 설정을 제2 종단 임피던스 값을 설정들로 동적으로 전환하도록 동작할 수 있다.

- [0034] 이러한 실시예에서, 제2 논리 유닛(203)은 메모리 제어기(101)에 의해 액세스되는 랭크들의 I/O 핀/패드에 대응하는 종단 유닛들(104<sub>1-N</sub>)의 복수의 저항기로부터의 저항기들을 켜거나 끄도록 동작할 수 있다. 하나의 실시예에서, 제1 및 제2 논리 유닛들은 메모리 제어기(101)의 I/O 송신기(204)를 통해 ODT 유닛들(104<sub>1-N</sub>)에 제1 및 제2 종단 값을 설정들을 할당한다. 하나의 실시예에서, 제1 및 제2 논리 유닛들은 각각의 랭크(103<sub>1-N</sub>)의 DRAM 모드 레지스터에 저장된 값을로부터 각각의 랭크의 ODT 유닛들(104<sub>1-N</sub>)에 제1 및 제2 종단 값을 설정들을 할당하도록 동작할 수 있다.

- [0035] 도 3은, 본 발명의 하나의 실시예에 따라, 랭크들에 유한 종단 임피던스 설정들을 동적으로 제공하기 위한 순서도(300)이다. 순서도는 도 1 및 도 2a-b의 실시예들에 대하여 논의된다.

- [0036] 블록 301에서, 제1 임피던스 값을 메모리 제어기(101)의 레지스터(201)에 또는 하나 이상의 랭크들(103<sub>1-N</sub>)에 설정된다. 위에서 언급된 바와 같이, 제1 임피던스 값(값 1)은 메모리 제어기(101)에 의해 액세스되어 있지 않은 랭크들에 대응하는 I/O 핀/패드의 ODT 유닛들(104<sub>1-N</sub>) 중 임의의 것에 대한 유한 임피던스 값이다. 블록 301에서, 제2 임피던스 값(값 2)은 또한 메모리 제어기(101)의 레지스터(201)에 또는 하나 이상의 랭크들(103<sub>1-N</sub>)에 설정된다. 위에서 논의된 바와 같이, 하나의 실시예에서, 레지스터(201)는 개개의 랭크들(103<sub>1-N</sub>)에 있다(도 2b의 DRAM 모드 레지스터(211)를 참조). 제2 임피던스 값을 또한 메모리 제어기(101)에 의해 액세스되는 랭크들에 대응하는 I/O 핀/패드의 ODT 유닛들(104<sub>1-N</sub>) 중 임의의 것에 대한 유한 임피던스 값이다. 하나의 실시예에서, 메모리 제어기(101)는 운영 체제를 통해 제1 및 제2 임피던스 값을 설정하도록 동작할 수 있다.

- [0037] 블록 302에서, 제1 종단 임피던스 값을 설정은, 제1 논리 유닛(202)을 통해 및/또는 도 2b의 논리 유닛(212)을 통해, 메모리 제어기(101)에 의해 액세스되어 있지 않은 랭크들에 대응하는 I/O 핀의 ODT 유닛들(104<sub>1-N</sub>) 중 임의의 것에 할당된다. 하나의 실시예에서, 제1 종단 임피던스 값을 메모리 제어기(101)에 의해 액세스되어 있지 않은 랭크들에 대응하는 I/O 핀/패드의 ODT 유닛들(104<sub>1-N</sub>)에 대한 디폴트 임피던스 값이다. 하나의 실시예에서, 제1 종단 임피던스 값을 액세스되어 있지 않은 ODT 유닛들(104<sub>1-N</sub>)에 할당된다. 이러한 실시예에서, ODT 신호(109)의 레벨은 디-어서트된다.

- [0038] 블록 303에서, 제2 논리 유닛(203) 및/또는 도 2b의 논리 유닛(212)은 ODT 신호(109)의 어서션에 응답하여 제1 종단 임피던스 값을 설정을 제2 종단 임피던스 값을 설정으로 동적으로 전환한다. 블록 303에서, 제2 임피던스 값을 설정은 메모리 제어기(101)에 의해 액세스되는 랭크들에 대응하는 I/O 핀/패드의 ODT 유닛들(104<sub>1-N</sub>) 중 임의의 것에 할당된다. 이러한 실시예에서, ODT 신호(109)의 레벨은 어서트한다.

- [0039] 상기 실시예들은, 하나 이상의 메모리 모듈(102<sub>1-N</sub>)의 랭크들(103<sub>1-N</sub>)에서 메모리 시스템의 상이한 랭크들이, ODT 신호(109)의 논리 레벨 및 액세스되는 랭크에 의존하는, 상이한 프로그래밍할 수 있는 유한 종단 임피던스 값을 설정들을 갖도록 허용한다. 유한 임피던스 종단 값을, ODT 신호(109)의 레벨 및 액세스되는 랭크들에 응답하여, 제1 유한 종단 임피던스 값을 설정으로부터 제2 유한 종단 임피던스 값을 설정으로 및 그 반대로 동적으로 전환한다.

- [0040] 상기 실시예들은, 고 임피던스(무한 임피던스) 값을 설정과 유한 임피던스 값을 설정 사이의 전환 만을 허용하는 메모리 시스템에 비해 전체 메모리 시스템에 대해 향상된 타이밍 및 전압 마진을 야기한다. 타이밍 및 전압 마진이 향상되는 하나의 이유는, 메모리들이 액세스될 때와 그들이 액세스되어 있지 않을 때의, ODT 유닛들에 대한 상이한 유한 종단 임피던스 값을 설정들으로 인해 메모리 제어기와 랭크들 사이의 전송선들에서 신호 반사의 감소이다. 본 발명의 실시예들은 따라서 DDR4 I/O 인터페이스를 갖는 메모리 시스템이 그의 디폴트 임피던스 값을 으로서 유한 프로그래밍할 수 있는 종단 임피던스를 갖도록 허용한다.

- [0041] 본 발명의 실시예들은 또한 기계-판독가능한 저장 매체에 저장된 프로그래밍할 수 있는 컴퓨터-실행가능한 명령어들을 통해 구현된다. 예를 들어, 도 3의 방법은 컴퓨터에 의해 프로그래밍할 수 있고 실행할 수 있다. 기계

-판독가능한 저장 매체는, 이에 한정되는 것은 아니지만, 플래시 메모리, 광 디스크, CD-ROM, DVD ROM, RAM, EPROM, EEPROM, 자기 또는 광 카드, 또는 전자적 또는 컴퓨터-실행가능한 명령어들을 저장하기에 적합한 다른 유형의 기계-판독가능한 저장 매체를 포함할 수 있다. 예를 들어, 본 발명의 실시예들은 통신 링크(예컨대, 모뎀이나 네트워크 접속)를 통해 데이터 신호에 의해 원격 컴퓨터(예컨대, 서버)로부터 요청 컴퓨터(예컨대, 클라이언트)로 전송될 수 있는 컴퓨터 프로그램으로서 다운로드될 수 있다.

[0042] 도 4는, 본 발명의 하나의 실시예에 따라, 여기에 개시된 방법들을 구현하는 시스템(400)을 도시한다. 하나의 실시예에서, 시스템(400)은, 이에 한정되는 것은 아니지만, 데스크톱 컴퓨터, 랩톱 컴퓨터, 넷북, 노트북 컴퓨터, PDA(personal digital assistant), 서버, 워크스테이션, 휴대 전화, 모바일 컴퓨팅 디바이스, 인터넷 어플라이언스 또는 임의 다른 유형의 컴퓨팅 디바이스를 포함한다. 또 다른 실시예에서, 여기에 개시된 방법들을 구현하기 위해 사용된 시스템(400)은 SOC(system on chip) 시스템일 수 있다.

[0043] 하나의 실시예에서, 프로세서(410)는 시스템(400)의 명령어들을 실행하는 처리 코어(412)를 갖는다. 하나의 실시예에서, 처리 코어(412)는, 이에 한정되는 것은 아니지만, 명령어들을 인출하는 사전-인출 논리(pre-fetch logic), 명령어들을 디코드하는 디코드 논리, 명령어들을 실행하는 실행 논리 등을 포함한다. 하나의 실시예에서, 프로세서(410)는 시스템(400)의 명령어들 및/또는 데이터를 캐시하는 캐시 메모리(416)를 갖는다. 하나의 실시예에서, 캐시는 도 3의 방법을 실행하는 명령어들을 저장한다. 본 발명의 또 다른 실시예에서, 캐시 메모리(416)는 레벨 1, 레벨 2 및 레벨 3 캐시 메모리, 또는 프로세서(410) 내에 있는 임의의 다른 구성의 캐시 메모리를 포함한다.

[0044] MCH(memory control hub)(414)로도 지칭되는, 메모리 제어기(101)는, 프로세서(410)가, 휘발성 메모리(432) 및/또는 비휘발성 메모리(434)를 포함하는 메모리(430)에 액세스 및 그와 통신하도록 인에이블하는 기능들을 수행하도록 동작할 수 있다. 휘발성 메모리(432)는, 이에 한정되는 것은 아니지만, SDRAM, DRAM, RDRAM, 및/또는 임의의 다른 유형의 랜덤 액세스 메모리 디바이스를 포함한다. 비 휘발성 메모리(434)는, 이에 한정되는 것은 아니지만, 플래시 메모리, PCM(phase change memory), ROM, EEPROM, 또는 임의의 다른 유형의 비 휘발성 메모리 디바이스를 포함한다.

[0045] 메모리(430)는 정보 및 프로세서(410)에 의해 실행될 명령어들을 저장한다. 하나의 실시예에서, 프로세서(410)가 명령어들을 실행하고 있는 동안 메모리(430)는 또한 일시적인 변수들(temporary variables) 또는 다른 중간 정보(intermediate information)를 저장할 수 있다. 하나의 실시예에서, 칩셋(420)은 PtP 또는 PP(Point-to-Point) 인터페이스(417 및 422)를 통해 프로세서(410)와 접속한다. 하나의 실시예에서, 칩셋(420)은 프로세서(410)가 시스템(400)에서 다른 모듈들에 접속하도록 인에이블한다. 본 발명의 하나의 실시예에서, 인터페이스(417 및 422)는 Intel® QPI(QuickPath Interconnect) 등과 같은 PtP 통신 프로토콜에 따라 동작한다.

[0046] 하나의 실시예에서, 칩셋(420)은 인터페이스(426)를 통해 디스플레이 디바이스(440)에 접속한다. 하나의 실시예에서, 디스플레이(440)는, 이에 한정되는 것은 아니지만, LCD(liquid crystal display), CRT(cathode ray tube) 디스플레이, 또는 임의의 다른 형태의 시각적 디스플레이 디바이스를 포함한다. 본 발명의 하나의 실시예에서, 프로세서(410) 및 칩셋(420)은 SOC에 병합된다. 또한, 칩셋(420)은 다양한 모듈들(474, 460, 462, 464 및 466)을 상호접속하는 하나 이상의 버스(450 및 455)에 접속한다. 하나의 실시예에서, 버스들(450 및 455)은, 버스 속도 또는 통신 프로토콜에서 불일치가 존재하는 경우, 버스 브리지(472)를 통해 서로 상호접속될 수 있다. 하나의 실시예에서, 칩셋(420)은, 이에 한정되는 것은 아니지만, 인터페이스(424)를 통해, 비 휘발성 메모리(460), 대용량 저장 디바이스(들)(462), 키보드/마우스(464), 및 네트워크 인터페이스(466)와 결합한다.

[0047] 하나의 실시예에서, 대용량 저장 디바이스(462)는, 이에 한정되는 것은 아니지만, 고체 상태 드라이브, 하드 디스크 드라이브, 범용 직렬 버스 플래시 메모리 드라이브, 또는 임의의 다른 형태의 컴퓨터 데이터 저장 매체를 포함한다. 하나의 실시예에서, 네트워크 인터페이스(466)는, 이에 한정되는 것은 아니지만, 이더넷 인터페이스, 범용 직렬 버스(USB) 인터페이스, 주변 컴포넌트 상호접속(PCI) 익스프레스 인터페이스, 무선 인터페이스 및/또는 임의의 다른 적절한 유형의 인터페이스를 포함하는 임의의 유형의 잘 알려진 네트워크 인터페이스 표준에 의해 구현된다. 하나의 실시예에서, 무선 인터페이스는, 이에 한정되는 것은 아니지만, IEEE 802.11 표준 및 그의 관련된 패밀리, 홈 플러그 AV(HPAV), 울트라 와이드 밴드(UWB), 블루투스, 와이맥스, 또는 임의의 형태의 무선 통신 프로토콜에 따라 동작한다.

[0048] 도 4에 도시된 모듈들은 시스템(400) 내에서 별도의 블록들로 묘사되지만, 이러한 블록들의 일부에 의해 수행되는 기능들은 단일 반도체 회로 내에 통합될 수 있고 또는 둘 이상의 별도의 접적 회로를 사용하여 구현될 수 있다. 예를 들어, 캐시 메모리(416)는 프로세서(410) 내에 있는 별도의 블록으로 묘사되지만, 캐시 메모리(416)

는 각각 프로세서 코어(412)에 통합될 수 있다. 하나의 실시예에서, 시스템(400)은 본 발명의 또 다른 실시예에서 하나보다 많은 프로세서/처리 코어를 포함할 수 있다.

[0049] 여기에서 사용된 동작할 수 있는(operable)이라는 용어는, 디바이스, 모듈, 시스템, 또는 논리 유닛이 외부 전원이 공급되는 상태(off-powered state)에 있을 때 그의 원하는 기능을 위해, 디바이스, 모듈, 시스템, 논리 유닛, 프로토콜 등이 동작하는 것이 가능하거나, 동작하도록 구성된다는 것을 의미한다.

[0050] 명세서에서, "일 실시예", "하나의 실시예", "일부 실시예," 또는 "다른 실시예"라는 지칭은, 실시예와 관련하여 설명된 특정한 특징, 구조, 또는 특성이 적어도 일부 실시예들에 포함되지만, 반드시 모든 실시예에 포함될 필요는 없다는 것을 의미한다. "일 실시예", "하나의 실시예" 또는 "일부 실시예"의 다양한 등장이 반드시 모두 동일한 실시예를 지칭하는 것일 필요는 없다. 명세서에서 컴포넌트, 특징, 구조 또는 특성이 포함될 "수 있다"(may, might, could)"고 진술되는 경우, 그 특정한 컴포넌트, 특징, 구조, 또는 특성이 포함되도록 요구되는 것은 아니다. 명세서 또는 청구항에서 "하나(a, an)"의 요소가 지칭되는 경우에, 그것이 단지 하나의 요소가 존재한다는 것을 의미하는 것은 아니다. 명세서 또는 청구항에서 "추가적인" 요소를 지칭하는 경우에, 그것이 하나 보다 많은 추가적인 요소가 존재하는 것을 배제하는 것은 아니다.

[0051] 본 발명은 그의 특정 실시예들과 관련하여 설명되었지만, 그러한 실시예들의 많은 대안들, 수정들 및 변형이 전술한 설명에 비추어 당업자에게 명백할 것이다. 예를 들어, 제1 임피던스 값으로부터 제2 임피던스 값으로의 종단 임피던스 값들의 동적 전환은, ODT 신호(109)가 어서트 대신 디-어스트할 때 발생할 수 있다. 이러한 실시예에서, ODT 신호(109)는 랙크로부터의 메모리 액세스에 응답하여 디-어서트된다. 하나의 실시예에서, 메모리 제어기(101)에 결합된 메모리는 독립형 DRAM이다.

[0052] 본 발명의 실시예들은, 이러한 대안들, 수정들, 및 변형들 모두가, 첨부된 청구항들의 넓은 범위 내에 있도록 포괄하도록 의도된다.

## 도면

### 도면1

## 도면2a

200

## 도면2b

210

## 도면3

## 도면4