(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-88721

(P2004-88721A)

(43) 公開日 平成16年3月18日(2004.3.18)

(51) Int.C1.<sup>7</sup>

H03L 7/14

H03L 7/093

F 1

H03L 7/14

H03L 7/08

A

E

テーマコード(参考)

5J106

審査請求 未請求 請求項の数 20 O L (全 30 頁)

(21) 出願番号 特願2003-18844 (P2003-18844)

(22) 出願日 平成15年1月28日 (2003.1.28)

(31) 優先権主張番号 特願2002-186949 (P2002-186949)

(32) 優先日 平成14年6月26日 (2002.6.26)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 390010179

埼玉日本電気株式会社

埼玉県児玉郡神川町大字元原字豊原300

番18

(74) 代理人 100109313

弁理士 机 昌彦

(74) 代理人 100085268

弁理士 河合 信明

(74) 代理人 100111637

弁理士 谷澤 靖久

(72) 発明者 小杉 淳一

埼玉県児玉郡神川町大字元原字豊原300

番18

埼玉日本電

気株式会社内

最終頁に続く

(54) 【発明の名称】位相同期方法及び位相同期回路

## (57) 【要約】

【課題】リファレンスクロック ( $f_i$ ) の入力が断になったときにこの  $f_i$  と出力クロック ( $f_o$ ) との周波数にわずかな差があっても、再び  $f_i$  の入力が復帰したときに、同期の具合が悪化しないようにする。

【解決手段】位相比較器 1 は、 $f_i$  と  $f_o$  の位相差を比較し位相差信号 (PD) を出力する。ループフィルタ 2 は、予め出力していた第 1 の制御電圧 ( $V_{ca}$ ) を PD に応じて処理をする。電圧制御手段 3 は、ループフィルタ 2 が処理した  $V_{ca}$  を入力し、 $f_i$  の入力があるときには、この  $V_{ca}$  を第 2 の制御電圧 ( $V_c$ ) として出力し、 $f_i$  の入力が断になってからは、 $V_c$  を、 $f_i$  の入力が断になったときの  $V_{ca}$  の平均値を中心に振動させて出力する。電圧制御発振器 4 は、 $V_c$  を入力しこの電圧値に応じた周波数の  $f_o$  を出力する。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

出力クロックと外部から入力するリファレンスクロックとの位相を比較しこの比較結果に基づき制御用の電圧を変化させこの変化させた前記制御用の電圧に応じた前記出力クロックを出力して前記リファレンスクロックに前記出力クロックの位相を同期させるようにした位相同期方法において、

外部からの前記リファレンスクロックの入力が断のときに、前記制御用の電圧を、前記リファレンスクロックの入力が断になるまでの前記制御用の電圧より求めた演算値を中心に振動させるようにしたことを特徴とする位相同期方法。

**【請求項 2】**

前記リファレンスクロックの入力が断になるまでの前記制御用の電圧より求めた前記演算値を、前記リファレンスクロックの入力が断になるまでの前記制御用の電圧の平均値としたことを特徴とする請求項 1 記載の位相同期方法。

**【請求項 3】**

前記制御用の電圧の変動の幅が予め定めた値より小さくなることを示す周波数の引き込み過程が終了したときに、前記変動の中心の値を前記制御用の電圧の平均値とし、その後、前記制御用の電圧がこの平均値より大又は小になった後に小又は大になる毎に、前記制御用の電圧が前記平均値より大又は小になった後に小又は大になるまでの前記制御用の電圧の平均を前記平均値に置き換えて前記平均値を更新し、この平均値を前記リファレンスクロックの入力が断になるまでの前記制御用の電圧より求めた前記演算値としたことを特徴とする請求項 1 記載の位相同期方法。

**【請求項 4】**

外部からの前記リファレンスクロックの入力があるときに、前記制御用の電圧の前記平均値と、振動用パラメータとを演算しておき、前記リファレンスクロックの入力が断になってから、この演算した前記制御用の電圧の前記平均値と前記振動用パラメータとを使用して、前記制御用の電圧を、前記制御用の電圧の前記平均値を中心に振動させるようにしたことを特徴とする請求項 2 又は 3 記載の位相同期方法。

**【請求項 5】**

前記制御用の電圧を、前記制御用の電圧の前記平均値を中心に収束させながら振動させるようにしたことを特徴とする請求項 2、3 又は 4 記載の位相同期方法。

**【請求項 6】**

自位相同期回路が出力する出力クロックと外部から入力するリファレンスクロックとの位相を比較しこの比較結果に基づき制御用の電圧を変化させこの変化させた前記制御用の電圧に応じた前記出力クロックを出力して前記リファレンスクロックに前記出力クロックの位相を同期させる位相同期回路であって、

前記リファレンスクロックと前記出力クロックとを入力して位相を比較し位相差信号を出力する位相比較器と、

前記位相差信号を入力し予め出力していた第 1 の制御電圧を前記位相差信号に応じて処理しこの処理した前記第 1 の制御電圧を出力するループフィルタと、

前記ループフィルタが出力した前記第 1 の制御電圧を入力し、前記リファレンスクロックの入力があるときには、この第 1 の制御電圧を第 2 の制御電圧として出力し、前記リファレンスクロックの入力が断になってからは、前記第 2 の制御電圧を、前記リファレンスクロックの入力が断になるまでの前記第 1 の制御電圧より求めた演算値を中心に振動する波として出力する電圧制御手段と、

前記第 2 の制御電圧を入力しこの電圧値に応じた周波数の前記出力クロックを出力する電圧制御発振器と、

を備えたことを特徴とする位相同期回路。

**【請求項 7】**

前記電圧制御手段は、前記リファレンスクロックの入力が断になってからは、前記第 2 の制御電圧を、前記リファレンスクロックの入力が断になるまでの前記第 1 の制御電圧の平

10

20

30

40

50

均値を中心に振動する波として出力するようにしたことを特徴とする請求項 6 記載の位相同期回路。

【請求項 8】

前記電圧制御手段は、前記第 1 の制御電圧の変動の幅が予め定めた値より小さくなることを示す周波数の引き込み過程が終了したときに、前記変動の中心の値を前記第 1 の制御電圧の平均値とし、その後、前記第 1 の制御電圧がこの平均値より大又は小になった後に小又は大になる毎に、前記第 1 の制御電圧が前記平均値より大又は小になった後に小又は大になるまでの前記第 1 の制御電圧の平均を前記平均値に置き換えて前記平均値を更新し、この平均値を前記リファレンスロックの入力が断になるまでの前記第 1 の制御電圧より求めた前記演算値としたことを特徴とする請求項 6 記載の位相同期回路。

10

【請求項 9】

前記電圧制御手段は、前記リファレンスロックの入力があるときに前記第 1 の制御電圧の前記平均値と振動用パラメータとを演算しておき、前記リファレンスロックの入力が断になってから、この演算した前記第 1 の制御電圧の前記平均値と前記振動用パラメータとを使用して、前記第 2 の制御電圧を前記第 1 の制御電圧の前記平均値を中心に振動する波として出力するようにしたことを特徴とする請求項 7 又は 8 記載の位相同期回路。

【請求項 10】

前記振動用パラメータとは、前記第 2 の制御電圧の変化量 (  $V$  ) , 前記第 2 の制御電圧の前記変化量の変化の量 (  $V$  ) , 前記第 2 の制御電圧が前記第 1 の制御電圧の前記平均値より大になったときから小になるまでの前記  $V$  の平均及び前記第 2 の制御電圧が前記第 1 の制御電圧の前記平均値より小になったときから大になるまでの前記  $V$  の平均を含むことを特徴とする請求項 9 記載の位相同期回路。

20

【請求項 11】

前記電圧制御手段は、前記第 2 の制御電圧を前記第 1 の制御電圧の前記平均値を中心に収束させながら振動する波として出力するようにしたことを特徴とする請求項 7 、 8 、 9 又は 10 記載の位相同期回路。

【請求項 12】

自位相同期回路が出力する出力クロックと外部から入力するリファレンスロックとの位相を比較しこの比較結果に基づき制御用の電圧を変化させこの変化させた前記制御用の電圧に応じた前記出力クロックを出力して前記リファレンスロックに前記出力クロックの位相を同期させる位相同期回路であって、

30

前記リファレンスロックと前記出力クロックとを入力して位相を比較し位相差信号を出力する位相比較器と、

前記位相差信号を入力し予め出力していた第 1 の制御電圧 (  $V_{c a}$  ) を前記位相差信号に応じて処理しこの処理した前記第 1 の制御電圧 (  $V_{c a}$  ) を出力するループフィルタと、前記リファレンスロックを入力し断検出信号を出力する断検出回路と、

前記ループフィルタが出力した前記第 1 の制御電圧 (  $V_{c a}$  ) を入力しこの第 1 の制御電圧 (  $V_{c a}$  ) を予め定めた周期で第 1 のデジタル制御電圧 (  $V_{c a d}$  ) に変換し変換する毎に出力する A / D コンバータと、

前記断検出回路が出力した前記断検出信号を受けるとともに、前記 A / D コンバータが出力した前記第 1 のデジタル制御電圧 (  $V_{c a d}$  ) を前記予め定めた周期毎に受け、前記断検出信号が前記リファレンスロックの入力があることを示す入力状態を示すときに、第 1 の切り替え指示を示す切り替え信号を出力し、前記第 1 のデジタル制御電圧 (  $V_{c a d}$  ) の平均値 (  $R E F V D$  ) と振動用パラメータとを前記予め定めた周期毎に演算して最新結果を格納しておき、前記断検出信号が前記リファレンスロックの入力がないことを示す断状態を示すときから、第 2 の切り替え指示を示す前記切り替え信号を出力し、前記格納しておいた前記第 1 のデジタル制御電圧 (  $V_{c a d}$  ) の前記平均値 (  $R E F V D$  ) と前記振動用パラメータとを使用して第 2 のデジタル制御電圧 (  $V D$  ) を前記予め定めた周期で作成しこの作成した第 2 のデジタル制御電圧 (  $V D$  ) を前記予め定めた周期で出力する演算部と、

40

50

前記演算部が出力した前記第2のデジタル制御電圧(  $V_D$  )を受けこの第2のデジタル制御電圧(  $V_D$  )をアナログ電圧の第3の制御電圧(  $V_{cd}$  )に変換するD/Aコンバータと、

前記ループフィルタが出力した前記第1の制御電圧(  $V_{ca}$  )と前記D/Aコンバータが出力した前記第3の制御電圧(  $V_{cd}$  )と前記演算部が出力した前記切り替え信号とを受け、前記切り替え信号が前記第1の切り替え指示を示すときに前記第1の制御電圧(  $V_{ca}$  )を前記第2の制御信号(  $V_c$  )として出力し、前記切り替え信号が前記第2の切り替え指示を示すときに前記第3の制御電圧(  $V_{cd}$  )を前記第2の制御信号(  $V_c$  )として出力する切り替え回路と、

前記切り替え回路が出力した前記第2の制御電圧(  $V_c$  )を入力しこの第2の制御電圧(  $V_c$  )の示す電圧値に応じた周波数の前記出力クロックを出力する電圧制御発振器と、

を備えたことを特徴とする位相同期回路。

【請求項13】

自位相同期回路が出力する出力クロックと外部から入力するリファレンスクロックとの位相を比較しこの比較結果に基づき制御用の電圧を変化させこの変化させた前記制御用の電圧に応じた前記出力クロックを出力して前記リファレンスクロックに前記出力クロックの位相を同期させる位相同期回路であって、

前記リファレンスクロックと前記出力クロックとを入力して位相を比較し位相差信号を出力する位相比較器と、

前記位相差信号を入力し予め出力していた第1の制御電圧(  $V_{ca}$  )を前記位相差信号に応じて処理しこの処理した前記第1の制御電圧(  $V_{ca}$  )を出力するループフィルタと、前記リファレンスクロックを入力し断検出信号を出力する断検出回路と、

前記ループフィルタが出力した前記第1の制御電圧(  $V_{ca}$  )を入力しこの第1の制御電圧(  $V_{ca}$  )を予め定めた周期で第1のデジタル制御電圧(  $V_{cad}$  )に変換し変換する毎に出力するA/Dコンバータと、

前記断検出回路が出力した前記断検出信号を受けるとともに、前記A/Dコンバータが出力した前記第1のデジタル制御電圧(  $V_{cad}$  )を前記予め定めた周期毎に受け、前記断検出信号が前記リファレンスクロックの入力があることを示す入力状態を示すときに、前記第1のデジタル制御電圧(  $V_{cad}$  )を前記第2のデジタル制御電圧(  $V_D$  )として出力し、前記第1のデジタル制御電圧(  $V_{cad}$  )の平均値(  $REFVD$  )と振動用パラメータとを前記予め定めた周期毎に演算して最新結果を格納しておき、前記断検出信号が前記リファレンスクロックの入力がないことを示す断状態を示すときから、前記格納しておいた前記第1のデジタル制御電圧(  $V_{cad}$  )の前記平均値(  $REFVD$  )と前記振動用パラメータとを使用して第2のデジタル制御電圧(  $V_D$  )を前記予め定めた周期で作成しこの作成した第2のデジタル制御電圧(  $V_D$  )を前記予め定めた周期で出力する演算部と、

前記演算部が出力した前記第2のデジタル制御電圧(  $V_D$  )を受けこの第2のデジタル制御電圧(  $V_D$  )をアナログ電圧の第3の制御電圧(  $V_{cd}$  )に変換し前記第2の制御電圧(  $V_c$  )として出力するD/Aコンバータと、

前記D/Aコンバータが出力した前記第2の制御電圧(  $V_c$  )を入力しこの第2の制御電圧(  $V_c$  )の示す電圧値に応じた周波数の前記出力クロックを出力する電圧制御発振器と、

を備えたことを特徴とする位相同期回路。

【請求項14】

前記演算部は、前記第2のデジタル制御電圧(  $V_D$  )を出力するときに、前記予め定めた周期で作成して出力する前記第2のデジタル制御電圧(  $V_D$  )の各出力電圧値による外観を、前記第1のデジタル制御電圧(  $V_{cad}$  )の前記平均値(  $REFVD$  )を中心に前記予め定めた周期より大きな周期の波として振動させて出力するようにしたことを特徴とする請求項12又は13記載の位相同期回路。

【請求項15】

10

20

30

40

50

前記演算部は、前記第2のデジタル制御電圧(  $V_D$  )を出力するときに、前記予め定めた周期より大きな周期の波として収束させながら振動させて出力するようにしたことを特徴とする請求項14記載の位相同期回路。

【請求項16】

前記振動用パラメータとは、前記第2のデジタル制御電圧(  $V_D$  )の変化量(  $\Delta V_D$  )、この変化量(  $\Delta V_D$  )の変化量(  $\Delta \Delta V_D$  )、前記第2のデジタル制御電圧(  $V_D$  )が前記第1のデジタル制御電圧(  $V_{cad}$  )の前記平均値より大になったときから小になるまでの前記  $V_D$  の平均(  $V_D_P$  )及び前記第2のデジタル制御電圧(  $V_D$  )が前記第1のデジタル制御電圧(  $V_{cad}$  )の前記平均値より小になったときから大になるまでの前記  $V_D$  の平均(  $V_D_M$  )を含むことを特徴とする請求項12又は13記載の位相同期回路。

10

20

30

【請求項17】

前記演算部は、前記第2のデジタル制御電圧(  $V_D$  )を出力するときに、この第2のデジタル制御電圧(  $V_D$  )を前記第1のデジタル制御電圧(  $V_{cad}$  )の前記平均値(  $R_E F V_D$  )を中心に振動させるために、前記予め定めた周期で、前回出力した前記第2のデジタル制御電圧(  $V_D$  )に前記格納した前記  $V_D$  と前記  $V_D_P$  又は前記  $V_D_M$  を加えて新たな前記第2のデジタル制御電圧(  $V_D$  )を作成し、この作成した新たな前記第2のデジタル制御電圧(  $V_D$  )を今回出力するようにしたことを特徴とする請求項16記載の位相同期回路。

20

【請求項18】

前記振動用パラメータは、前記  $V_D_P$  の平均(  $A V_E_P$  )及び前記  $V_D_M$  の平均(  $A V_E_M$  )含むことを特徴とする請求項16記載の位相同期回路。

20

【請求項19】

前記演算部は、前記第2のデジタル制御電圧(  $V_D$  )を出力するときに、この第2のデジタル制御電圧(  $V_D$  )を前記第1のデジタル制御電圧(  $V_{cad}$  )の前記平均値(  $R_E F V_D$  )を中心に振動させるために、前記予め定めた周期で、前回出力した前記第2のデジタル制御電圧(  $V_D$  )に前記格納した前記  $V_D$  と前記  $A V_E_P$  又は前記  $A V_E_M$  を加えて新たな前記第2のデジタル制御電圧(  $V_D$  )を作成し、この作成した新たな前記第2のデジタル制御電圧(  $V_D$  )を今回出力するようにしたことを特徴とする請求項18記載の位相同期回路。

30

【請求項20】

前記演算部は、前記予め定めた周期で、前記  $V_D_P$  と前記  $V_D_M$  とに係数  $k$  ( $0 < k < 1$ ) を掛けて新たな前記  $V_D_P$  と前記  $V_D_M$  とにすることにより、前記第2のデジタル制御電圧(  $V_D$  )を前記第1のデジタル制御電圧(  $V_{cad}$  )の前記平均値(  $R_E F V_D$  )を中心に収束させて振動させるようにしたことを特徴とする請求項17又は19記載の位相同期回路。

40

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は位相同期方法及び位相同期回路に関し、特に外部から入力するリファレンスクロックの位相に同期した出力クロックを出力する位相同期方法及び位相同期回路に関する。

40

【0002】

【従来の技術】

従来、この種の位相同期回路は、たとえば特許文献1に開示されているように、自位相同期回路が出力する出力クロックと外部から入力するリファレンスクロックとの位相を比較しこの比較結果に基づいて変化させた制御用の電圧に応じて出力クロックを出力してリファレンスクロックにこの出力クロックの位相を同期させるために用いられている。

【0003】

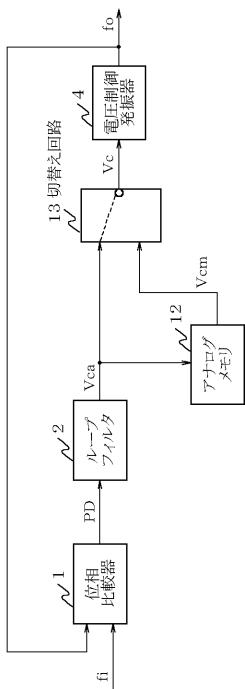

この従来の位相同期回路は、図17に示すように、外部からのリファレンスクロック(  $f_i$  )と電圧制御発振器4より出力される出力クロック(  $f_o$  )との位相差を比較し位相差

50

信号 (P D) を出力する位相比較器 1 と、位相差信号を入力しアナログ電圧 (V c a) を出力するループフィルタ 2 と、ループフィルタ 2 からのアナログ電圧の電圧値を記憶しこの電圧値の電圧 (V c m) を出力するアナログメモリ 1 2 と、ループフィルタ 2 からのアナログ電圧 (V c a) とアナログメモリ 1 2 からの電圧 (V c m) とを受け、リファレンスクロックの入力があるときにはループフィルタ 2 からのアナログ電圧 (V c a) を制御電圧 (V c) として出力し、リファレンスクロックの入力が断になったときにアナログメモリ 1 2 からの電圧 (V c m) を制御電圧 (V c) として出力する切替え回路と、切替え回路が出力した制御電圧 (V c) を入力しその電圧値に対応する周波数の出力クロック (f o) を出力する電圧制御発振器 4 とにより構成する。

【0004】

10

この従来の位相同期回路は、位相比較器 1 からループフィルタ 2 を通して得られる電圧 (V c a) をアナログメモリ 1 2 に記憶しておき、リファレンスクロックの入力が断になったときに、切り替え回路 1 3 が電圧制御発振器 4 へ出力する制御電圧 (V c) をループフィルタ 2 を通して得られる電圧 (V c a) からアナログメモリ 1 2 に記憶した電圧 (V c m) に切り替え、リファレンスクロックの入力が断になったときから、リファレンスクロックの入力が断になる直前にアナログメモリ 1 2 に記憶した電圧 (V c m) で電圧制御発振器 4 を動作させ、出力クロックの周波数をリファレンスクロックの入力が断になる直前の周波数に維持するようにしている。

【0005】

20

【特許文献 1】

特開平 04-107011 号公報 (特許請求の範囲、第 1 図)

【0006】

【発明が解決しようとする課題】

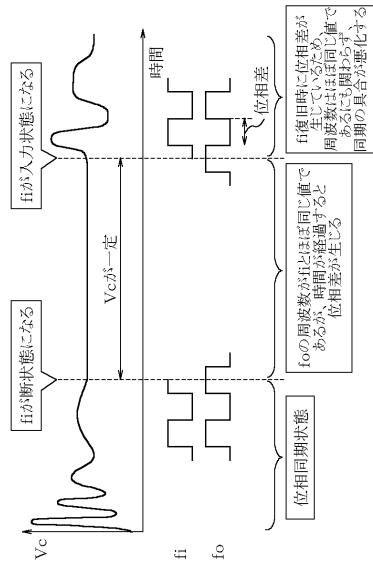

上述した従来の位相同期回路は、位相比較器からループフィルタを通して得られる電圧 (V c a) をアナログメモリに記憶しておき、リファレンスクロックの入力が断になったときに、切り替え回路が電圧制御発振器へ出力する電圧 (V c) をループフィルタを通して得られる電圧 (V c a) からアナログメモリに記憶した電圧 (V c m) に切り替えて、リファレンスクロックの入力が断になったときから、電圧制御発振器の出力クロックの周波数をリファレンスクロックの入力が断になる直前の周波数に維持するようにしているため、図 18 に示すように、リファレンスクロック (f i) の入力が断になったとき、リファレンスクロック (f i) と出力クロック (f o) との周波数にわずかな差があった場合 (ほぼ一致している場合)、時間が経つにつれてこの f i と f o とに位相差が生じてしまうので、この位相差が生じている状態で、再びリファレンスクロック (f i) の入力が復帰すると、リファレンスクロック (f i) と出力クロック (f o) との周波数がほぼ一致しているにもかかわらず、位相比較器から f i と f o との位相差に応じた位相差信号 (P D) が出力され、電圧制御発振器は、この位相差信号 (P D) に応じて出力されるループフィルタからの電圧を制御電圧 V c として入力しリファレンスクロック (f i) の周波数からかけ離れた周波数の出力クロック (f o) を出力してしまい同期の具合が悪化するという問題点がある。

30

【0007】

40

本発明の目的はこのような従来の欠点を除去するため、リファレンスクロック (f i) の入力が断になったときにリファレンスクロック (f i) と出力クロック (f o) との周波数にわずかな差があっても、その後、時間が経過後に、再びリファレンスクロック (f i) の入力が復帰したときに、リファレンスクロック (f i) の周波数からかけ離れた周波数の出力クロック (f o) が出力されず同期の具合が悪化しない位相同期方法及び位相同期回路を提供することにある。

【0008】

50

【課題を解決するための手段】

本発明の位相同期方法は、出力クロックと外部から入力するリファレンスクロックとの位相を比較しこの比較結果に基づき制御用の電圧を変化させた前記制御用の電

圧に応じた前記出力クロックを出力して前記リファレンスクロックに前記出力クロックの位相を同期させるようにした位相同期方法において、

外部からの前記リファレンスクロックの入力が断のときに、前記制御用の電圧を、前記リファレンスクロックの入力が断になるまでの前記制御用の電圧より求めた演算値を中心に振動させるようにしている。

【0009】

また、本発明の位相同期方法は、前記リファレンスクロックの入力が断になるまでの前記制御用の電圧より求めた前記演算値を、前記リファレンスクロックの入力が断になるまでの前記制御用の電圧の平均値としている。

【0010】

更に、本発明の位相同期方法は、前記制御用の電圧の変動の幅が予め定めた値より小さくなることを示す周波数の引き込み過程が終了したときに、前記変動の中心の値を前記制御用の電圧の平均値とし、その後、前記制御用の電圧がこの平均値より大又は小になった後に小又は大になる毎に、前記制御用の電圧が前記平均値より大又は小になった後に小又は大になるまでの前記制御用の電圧の平均を前記平均値に置き換えて前記平均値を更新し、この平均値を前記リファレンスクロックの入力が断になるまでの前記制御用の電圧より求めた前記演算値としている。

【0011】

また、本発明の位相同期方法は、外部からの前記リファレンスクロックの入力があるときに、前記制御用の電圧の前記平均値と、振動用パラメータとを演算しておき、前記リファレンスクロックの入力が断になってから、この演算した前記制御用の電圧の前記平均値と前記振動用パラメータとを使用して、前記制御用の電圧を、前記制御用の電圧の前記平均値を中心に振動させるようにしている。

【0012】

更に、本発明の位相同期方法は、前記制御用の電圧を、前記制御用の電圧の前記平均値を中心に収束させながら振動させるようにしている。

【0013】

本発明の第1の位相同期回路は、自位相同期回路が出力する出力クロックと外部から入力するリファレンスクロックとの位相を比較しこの比較結果に基づき制御用の電圧を変化させこの変化させた前記制御用の電圧に応じた前記出力クロックを出力して前記リファレンスクロックに前記出力クロックの位相を同期させる位相同期回路であって、

前記リファレンスクロックと前記出力クロックとを入力して位相を比較し位相差信号を出力する位相比較器と、

前記位相差信号を入力し予め出力していた第1の制御電圧を前記位相差信号に応じて処理しこの処理した前記第1の制御電圧を出力するループフィルタと、

前記ループフィルタが出力した前記第1の制御電圧を入力し、前記リファレンスクロックの入力があるときには、この第1の制御電圧を第2の制御電圧として出力し、前記リファレンスクロックの入力が断になってからは、前記第2の制御電圧を、前記リファレンスクロックの入力が断になるまでの前記第1の制御電圧より求めた演算値を中心に振動する波として出力する電圧制御手段と、

前記第2の制御電圧を入力しこの電圧値に応じた周波数の前記出力クロックを出力する電圧制御発振器と、

を備えて構成されている。

【0014】

また、本発明の第1の位相同期回路の前記電圧制御手段は、前記リファレンスクロックの入力が断になってからは、前記第2の制御電圧を、前記リファレンスクロックの入力が断になるまでの前記第1の制御電圧の平均値を中心に振動する波として出力するようにしている。

【0015】

更に、本発明の第1の位相同期回路の前記電圧制御手段は、前記第1の制御電圧の変動の

10

20

30

40

50

幅が予め定めた値より小さくなることを示す周波数の引き込み過程が終了したときに、前記変動の中心の値を前記第1の制御電圧の平均値とし、その後、前記第1の制御電圧がこの平均値より大又は小になった後に小又は大になる毎に、前記第1の制御電圧が前記平均値より大又は小になった後に小又は大になるまでの前記第1の制御電圧の平均を前記平均値に置き換えて前記平均値を更新し、この平均値を前記リファレンスロックの入力が断になるまでの前記第1の制御電圧より求めた前記演算値としている。

## 【0016】

また、本発明の第1の位相同期回路の前記電圧制御手段は、前記リファレンスロックの入力があるときに前記第1の制御電圧の前記平均値と振動用パラメータとを演算しておき、前記リファレンスロックの入力が断になってから、この演算した前記第1の制御電圧の前記平均値と前記振動用パラメータとを使用して、前記第2の制御電圧を前記第1の制御電圧の前記平均値を中心に振動する波として出力するようにしている。10

## 【0017】

更に、本発明の第1の位相同期回路の前記電圧制御手段は、前記第2の制御電圧を前記第1の制御電圧の前記平均値を中心に収束させながら振動する波として出力するようにしている。

## 【0018】

本発明の第2の位相同期回路は、自位相同期回路が出力する出力クロックと外部から入力するリファレンスロックとの位相を比較しこの比較結果に基づき制御用の電圧を変化させこの変化させた前記制御用の電圧に応じた前記出力クロックを出力して前記リファレンスロックに前記出力クロックの位相を同期させる位相同期回路であって、20

前記リファレンスロックと前記出力クロックとを入力して位相を比較し位相差信号を出力する位相比較器と、

前記位相差信号を入力し予め出力していた第1の制御電圧( $V_{c a}$ )を前記位相差信号に応じて処理しこの処理した前記第1の制御電圧( $V_{c a}$ )を出力するループフィルタと、前記リファレンスロックを入力し断検出信号を出力する断検出回路と、

前記ループフィルタが出力した前記第1の制御電圧( $V_{c a}$ )を入力しこの第1の制御電圧( $V_{c a}$ )を予め定めた周期で第1のデジタル制御電圧( $V_{c a d}$ )に変換し変換する毎に出力するA/Dコンバータと、

前記断検出回路が出力した前記断検出信号を受けるとともに、前記A/Dコンバータが出力した前記第1のデジタル制御電圧( $V_{c a d}$ )を前記予め定めた周期毎に受け、前記断検出信号が前記リファレンスロックの入力があることを示す入力状態を示すときに、第1の切り替え指示を示す切り替え信号を出力し、前記第1のデジタル制御電圧( $V_{c a d}$ )の平均値( $R E F V D$ )と振動用パラメータとを前記予め定めた周期毎に演算して最新結果を格納しておき、前記断検出信号が前記リファレンスロックの入力がないことを示す断状態を示すときから、第2の切り替え指示を示す前記切り替え信号を出力し、前記格納しておいた前記第1のデジタル制御電圧( $V_{c a d}$ )の前記平均値( $R E F V D$ )と前記振動用パラメータとを使用して第2のデジタル制御電圧( $V D$ )を前記予め定めた周期で作成しこの作成した第2のデジタル制御電圧( $V D$ )を前記予め定めた周期で出力する演算部と、30

前記演算部が出力した前記第2のデジタル制御電圧( $V D$ )を受けこの第2のデジタル制御電圧( $V D$ )をアナログ電圧の第3の制御電圧( $V_{c d}$ )に変換するD/Aコンバータと、

前記ループフィルタが出力した前記第1の制御電圧( $V_{c a}$ )と前記D/Aコンバータが出力した前記第3の制御電圧( $V_{c d}$ )と前記演算部が出力した前記切り替え信号とを受け、前記切り替え信号が前記第1の切り替え指示を示すときに前記第1の制御電圧( $V_{c a}$ )を前記第2の制御信号( $V c$ )として出力し、前記切り替え信号が前記第2の切り替え指示を示すときに前記第3の制御電圧( $V_{c d}$ )を前記第2の制御信号( $V c$ )として出力する切り替え回路と、

前記切り替え回路が出力した前記第2の制御電圧( $V c$ )を入力しこの第2の制御電圧(40

10

20

30

40

50

$V_c$ ) の示す電圧値に応じた周波数の前記出力クロックを出力する電圧制御発振器と、を備えて構成されている。

【0019】

本発明の第3の位相同期回路は、自位相同期回路が出力する出力クロックと外部から入力するリファレンスクロックとの位相を比較しこの比較結果に基づき制御用の電圧を変化させこの変化させた前記制御用の電圧に応じた前記出力クロックを出力して前記リファレンスクロックに前記出力クロックの位相を同期させる位相同期回路であって、前記リファレンスクロックと前記出力クロックとを入力して位相を比較し位相差信号を出力する位相比較器と、

前記位相差信号を入力し予め出力していた第1の制御電圧( $V_{c a}$ )を前記位相差信号に応じて処理しこの処理した前記第1の制御電圧( $V_{c a}$ )を出力するループフィルタと、前記リファレンスクロックを入力し断検出信号を出力する断検出回路と、

前記ループフィルタが出力した前記第1の制御電圧( $V_{c a}$ )を入力しこの第1の制御電圧( $V_{c a}$ )を予め定めた周期で第1のデジタル制御電圧( $V_{c a d}$ )に変換し変換する毎に出力するA/Dコンバータと、

前記断検出回路が出力した前記断検出信号を受けるとともに、前記A/Dコンバータが出力した前記第1のデジタル制御電圧( $V_{c a d}$ )を前記予め定めた周期毎に受け、前記断検出信号が前記リファレンスクロックの入力があることを示す入力状態を示すときに、前記第1のデジタル制御電圧( $V_{c a d}$ )を前記第2のデジタル制御電圧( $V_D$ )として出力し、前記第1のデジタル制御電圧( $V_{c a d}$ )の平均値( $REFVD$ )と振動用パラメータとを前記予め定めた周期毎に演算して最新結果を格納しておき、前記断検出信号が前記リファレンスクロックの入力がないことを示す断状態を示すときから、前記格納しておいた前記第1のデジタル制御電圧( $V_{c a d}$ )の前記平均値( $REFVD$ )と前記振動用パラメータとを使用して第2のデジタル制御電圧( $V_D$ )を前記予め定めた周期で作成しこの作成した第2のデジタル制御電圧( $V_D$ )を前記予め定めた周期で出力する演算部と、

前記演算部が出力した前記第2のデジタル制御電圧( $V_D$ )を受けこの第2のデジタル制御電圧( $V_D$ )をアナログ電圧の第3の制御電圧( $V_{c d}$ )に変換し前記第2の制御電圧( $V_c$ )として出力するD/Aコンバータと、

前記D/Aコンバータが出力した前記第2の制御電圧( $V_c$ )を入力しこの第2の制御電圧( $V_c$ )の示す電圧値に応じた周波数の前記出力クロックを出力する電圧制御発振器と、を備えて構成されている。

【0020】

また、本発明の第2と第3の位相同期回路の前記演算部は、前記第2のデジタル制御電圧( $V_D$ )を出力するときに、前記予め定めた周期で作成して出力する前記第2のデジタル制御電圧( $V_D$ )の各出力電圧値による外観を、前記第1のデジタル制御電圧( $V_{c a d}$ )の前記平均値( $REFVD$ )を中心に前記予め定めた周期より大きな周期の波として振動させて出力するようにしている。

【0021】

更に、本発明の第2と第3の位相同期回路の前記演算部は、前記第2のデジタル制御電圧( $V_D$ )を出力するときに、前記予め定めた周期より大きな周期の波として収束させながら振動させて出力するようにしている。

【0022】

【発明の実施の形態】

次に、本発明の実施の形態について図面を参照して説明する。

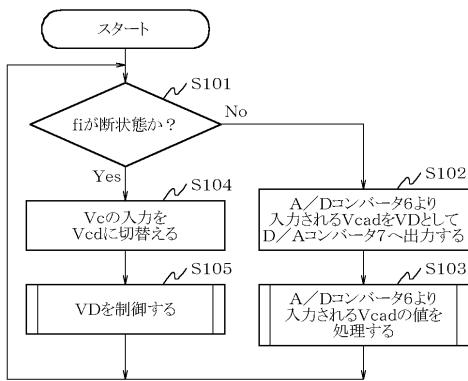

【0023】

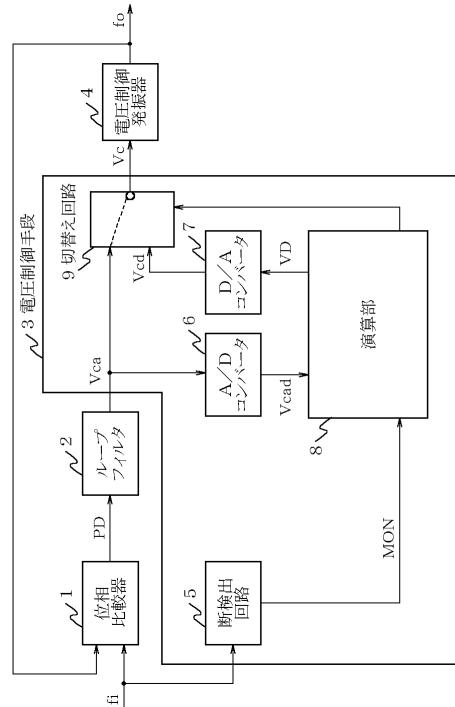

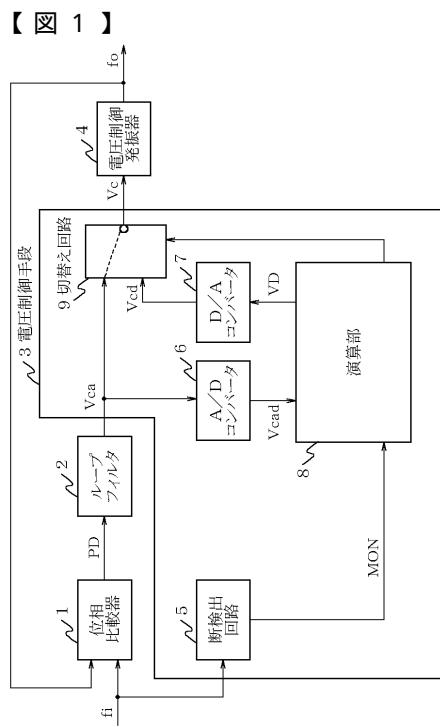

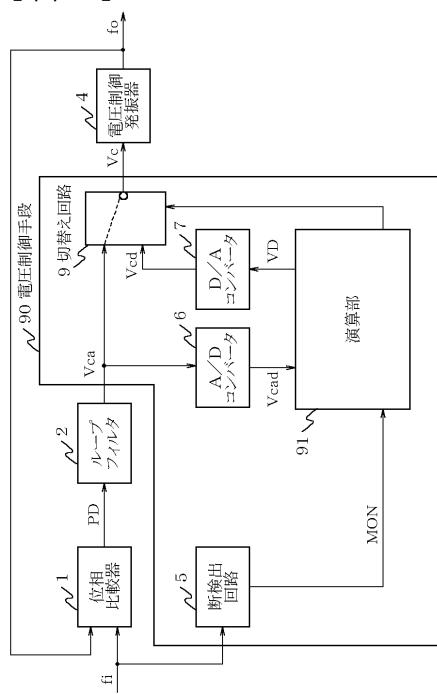

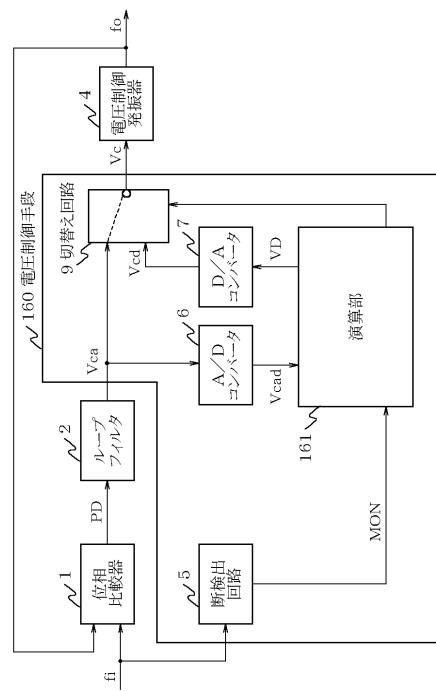

図1は、本発明の位相同期回路の第1の実施の形態を示すブロック図である。

【0024】

図1に示す本実施の形態は、位相比較器1と、ループフィルタ2と、電圧制御手段3と、

電圧制御発振器 4 とにより構成する。

【 0 0 2 5 】

位相比較器 1 は、外部から入力するリファレンスクロック (  $f_i$  ) と電圧制御発振器 4 より出力する出力クロック (  $f_o$  ) とを入力して位相を比較し位相差信号 (  $P_D$  ) を出力する。位相差信号 (  $P_D$  ) は、出力クロック (  $f_o$  ) の位相がリファレンスクロック (  $f_i$  ) の位相より遅れているときにはプラスの値、進んでいるときにはマイナスの値とし、また、位相が一致しているときにはハイインピーダンス状態にする。

【 0 0 2 6 】

ループフィルタ 2 は、位相差信号 (  $P_D$  ) を入力し、この位相差信号がプラスの値のときには第 1 の制御電圧 (  $V_{ca}$  ) を増加させ、この位相差信号がマイナスの値のときには第 1 の制御電圧 (  $V_{ca}$  ) を減少させる。また、この位相差信号がハイインピーダンス状態のときには第 1 の制御電圧 (  $V_{ca}$  ) を保持する。

【 0 0 2 7 】

電圧制御手段 3 は、ループフィルタ 2 が output した第 1 の制御電圧 (  $V_{ca}$  ) を入力し、リファレンスクロック (  $f_i$  ) の入力があるときには、この第 1 の制御電圧 (  $V_{ca}$  ) を第 2 の制御電圧 (  $V_c$  ) として出力し、リファレンスクロック (  $f_i$  ) の入力が断になってからは、第 2 の制御電圧 (  $V_c$  ) を、リファレンスクロック (  $f_i$  ) の入力が断になったときの第 1 の制御電圧 (  $V_{ca}$  ) の平均値を中心に振動する波として出力する。

【 0 0 2 8 】

電圧制御発振器 4 は、第 2 の制御電圧 (  $V_c$  ) を入力しこの電圧値に応じた周波数の出力クロック (  $f_o$  ) を出力する。例えば、第 2 の制御電圧 (  $V_c$  ) が高いときには高い周波数の出力クロック (  $f_o$  ) を出力する。第 2 の制御電圧 (  $V_c$  ) が低いときには低い周波数の出力クロック (  $f_o$  ) を出力する。

【 0 0 2 9 】

また、電圧制御手段 3 は、断検出回路 5 と、A / D コンバータ 6 と、演算部 8 と、D / A コンバータ 7 と、切り替え回路 9 とにより構成する。

【 0 0 3 0 】

断検出回路 5 は、リファレンスクロック (  $f_i$  ) を入力し断検出信号 (  $MON$  ) を出力する。

【 0 0 3 1 】

A / D コンバータ 6 は、ループフィルタ 2 が output した第 1 の制御電圧 (  $V_{ca}$  ) を入力し、この第 1 の制御電圧 (  $V_{ca}$  ) を予め定めた周期で第 1 のデジタル制御電圧 (  $V_{cad}$  ) に変換し変換する毎に出力する。

【 0 0 3 2 】

演算部 8 は、断検出回路 5 が output した断検出信号 (  $MON$  ) を受けるとともに、A / D コンバータ 6 が output した第 1 のデジタル制御電圧 (  $V_{cad}$  ) を予め定めた周期毎に受け、断検出信号 (  $MON$  ) がリファレンスクロックの入力があることを示す入力状態を示すときに、第 1 の切り替え指示を示す切り替え信号を出力し、第 1 のデジタル制御電圧 (  $V_{cad}$  ) の平均値 (  $REFVD$  ) と振動用パラメータとを予め定めた周期毎に演算して最新結果を格納しておき、断検出信号 (  $MON$  ) がリファレンスクロック (  $f_i$  ) の入力がないことを示す断状態を示すときから、第 2 の切り替え指示を示す切り替え信号を出力し、格納しておいた第 1 のデジタル制御電圧 (  $V_{cad}$  ) の平均値 (  $REFVD$  ) と振動用パラメータとを使用して第 2 のデジタル制御電圧 (  $VD$  ) を予め定めた周期で作成しこの作成した第 2 のデジタル制御電圧 (  $VD$  ) を予め定めた周期で出力する。

【 0 0 3 3 】

D / A コンバータ 7 は、演算部 8 が output した第 2 のデジタル制御電圧 (  $VD$  ) を受けこの第 2 のデジタル制御電圧 (  $VD$  ) をアナログ電圧の第 3 の制御電圧 (  $V_{cd}$  ) に変換する。

【 0 0 3 4 】

切り替え回路 9 は、ループフィルタ 2 が output した第 1 の制御電圧 (  $V_{ca}$  ) と D / A コン

10

20

30

40

50

バータ7が出力した第3の制御電圧( $V_{cd}$ )と演算部8が出力した切り替え信号とを受け、切り替え信号が第1の切り替え指示を示すときに第1の制御電圧( $V_{ca}$ )を第2の制御信号( $V_c$ )として出力し、切り替え信号が第2の切り替え指示を示すときに第3の制御電圧( $V_{cd}$ )を第2の制御信号( $V_c$ )として出力する。

【0035】

ここで、振動用パラメータとは、第2のデジタル制御電圧( $V_D$ )の変化量( $\Delta V_D$ )、この変化量( $\Delta V_D$ )の変化量( $\Delta \Delta V_D$ )、第2のデジタル制御電圧( $V_D$ )が第1のデジタル制御電圧( $V_{cad}$ )の平均値より大になったときから小になるまでの $V_D$ の平均( $\bar{V}_D_P$ )及び第2のデジタル制御電圧( $V_D$ )が第1のデジタル制御電圧( $V_{cad}$ )の平均値より小になったときから大になるまでの $V_D$ の平均( $\bar{V}_D_M$ )を含んでいる。10

【0036】

そして、演算部8は、第2のデジタル制御電圧( $V_D$ )を出力するときに、この第2のデジタル制御電圧( $V_D$ )を第1のデジタル制御電圧( $V_{cad}$ )の平均値( $REFV_D$ )を中心に振動させるために、この振動用パラメータを使用する。すなわち、予め定めた周期で、前回出力した第2のデジタル制御電圧( $V_D$ )に格納した $V_D$ と $\bar{V}_D_P$ 又は $\bar{V}_D_M$ を加えて新たな第2のデジタル制御電圧( $V_D$ )を作成し、この作成した新たな第2のデジタル制御電圧( $V_D$ )を今回出力する。

【0037】

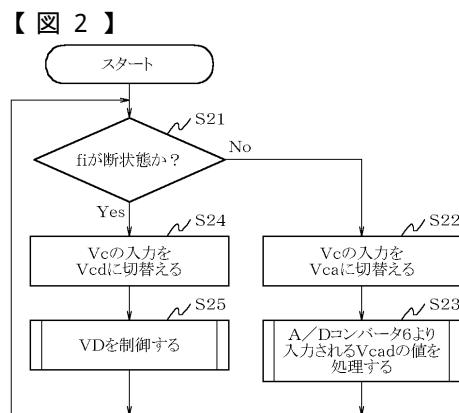

次に、本実施の形態の位相同期回路の動作を図2から図8を参照して詳細に説明する。20

【0038】

図2は、第1の実施の形態での演算部の概要動作の一例を示すフローチャートである。ステップ21で、断検出回路5からの断検出信号( $MON$ )が入力状態を示す信号か断状態を示す信号か調べ、断検出信号( $MON$ )が入力状態を示す信号のときはステップ22へ進む。ステップ22では、演算部8は第1の切り替え指示を示す切り替え信号を切り替え回路9に出力し、切り替え回路9に第1の制御電圧( $V_{ca}$ )を第2の制御信号( $V_c$ )として出力させ、ステップ23では、A/Dコンバータ6より入力する第1のデジタル制御電圧( $V_{ca}$ )の平均値( $REFV_D$ )と振動用パラメータとを演算し格納する。一方、ステップ21で調べた結果が、断検出信号( $MON$ )が断状態を示す信号のときにはステップ24へ進む。ステップ24では、演算部8は第2の切り替え指示を示す切り替え信号を切り替え回路9に出力し、切り替え回路9に第3の制御電圧( $V_{cd}$ )を第2の制御信号( $V_c$ )として出力させ、ステップ25では、ステップ23で格納しておいた第1のデジタル制御電圧( $V_{cad}$ )の平均値( $REFV_D$ )と振動用パラメータとを使用して第2のデジタル制御電圧( $V_D$ )を作成し出力する。以上の動作を予め定めた周期毎に行う。30

【0039】

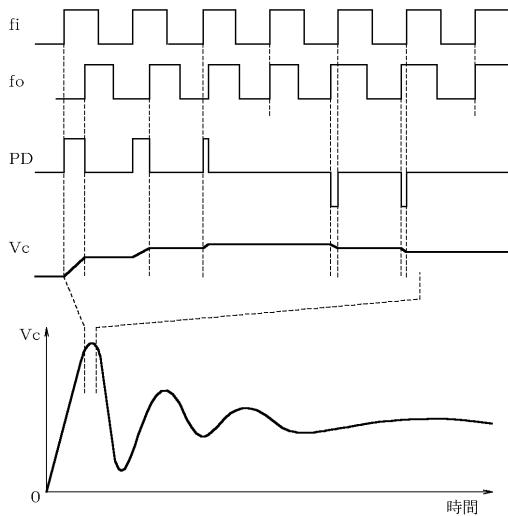

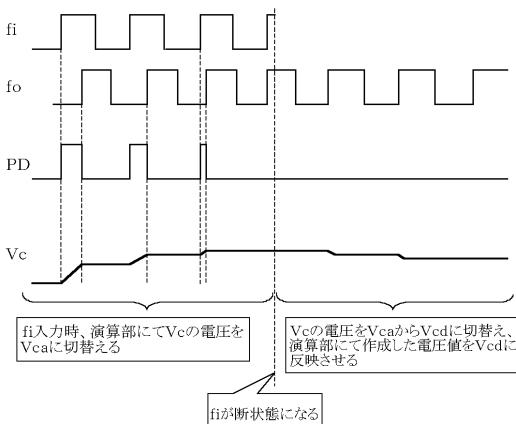

図3は、リファレンスクロック( $f_i$ )が入力状態のときの各信号の関係を示す図であり、リファレンスクロック( $f_i$ )が入力状態のときのリファレンスクロック( $f_i$ )と出力クロック( $f_o$ )と位相差信号( $PD$ )と第2の制御電圧( $V_c$ )との関係を示している。40

【0040】

図4は、リファレンスクロック( $f_i$ )が断状態のときの各信号の関係を示す図であり、リファレンスクロック( $f_i$ )が断状態のときのリファレンスクロック( $f_i$ )と出力クロック( $f_o$ )と位相差信号( $PD$ )と第2の制御電圧( $V_c$ )との関係を示している。

【0041】

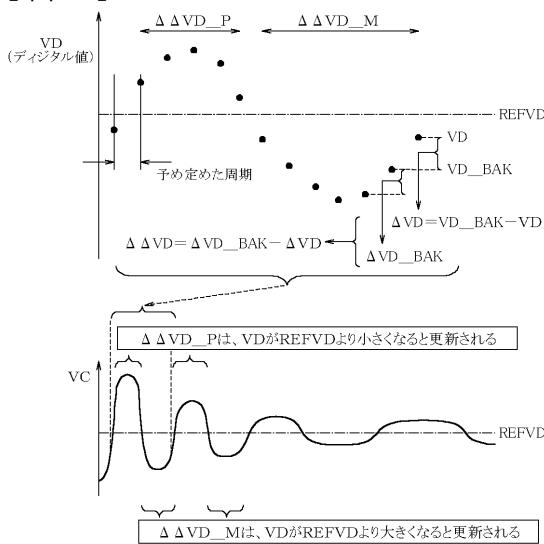

図5は、演算部で使用する変数の定義を説明する図である。

【0042】

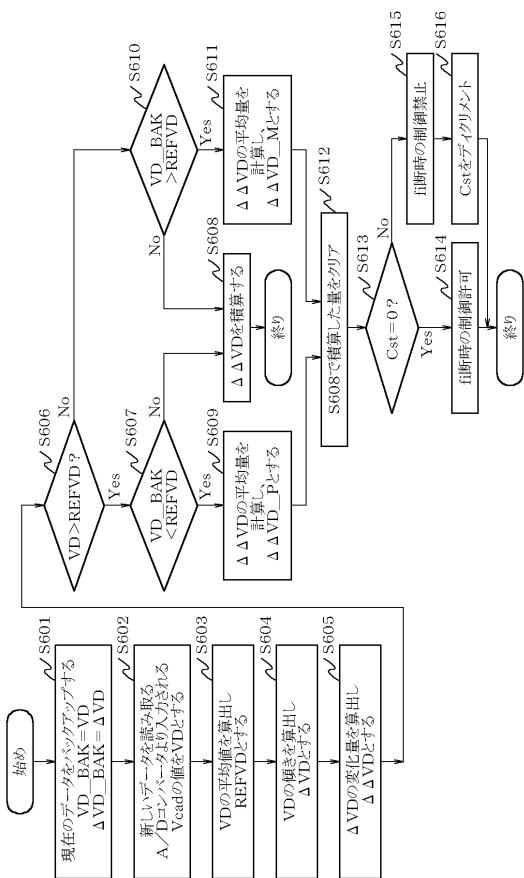

図6は、リファレンスクロック( $f_i$ )が入力状態のときの演算部の動作の一例を示すフローチャートである。

【0043】

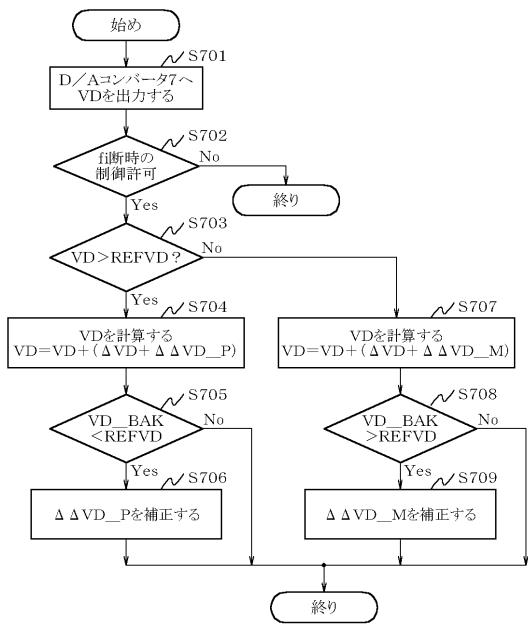

図7は、リファレンスクロック( $f_i$ )が断状態のときの演算部の動作の一例を示すフローチャートである。

【0044】

図8は、リファレンスクロック( $f_i$ )が断状態のときの第2のデジタル制御電圧( $V_D$ )の計算例を示す図である。

【0045】

図1において、初めに、リファレンスクロック( $f_i$ )が入力状態のときの動作を説明する。リファレンスクロック( $f_i$ )が入力状態のときは、断検出回路5はリファレンスクロック( $f_i$ )が入力状態であることを示す断検出信号( $M_{ON}$ )を演算部8に出力する。

10

【0046】

演算部8はこの断検出信号( $M_{ON}$ )を受け第1の切り替え指示を示す切り替え信号を切り替え回路9に出力し、切り替え回路9に第1の制御電圧( $V_{ca}$ )を第2の制御信号( $V_c$ )として出力させる(図2のステップ21とステップ22)。

【0047】

制御電圧発振器が入力する第2の制御電圧( $V_c$ )が第1の制御電圧( $V_{ca}$ )に切り替わると、位相比較器1とループフィルタ2と電圧制御発振器4とのループが構成される。

【0048】

この場合、位相比較器1は、電圧制御発振器4より出力される出力クロック( $f_o$ )と、リファレンスクロック( $f_i$ )の位相を比較し、出力クロック( $f_o$ )の位相がリファレンスクロック( $f_i$ )の位相よりも遅れている場合プラスの値の位相差信号( $P_D$ )を出力し、進んでいる場合マイナスの値の位相差信号( $P_D$ )を出力する。また、位相が一致しているときには、位相差信号( $P_D$ )をハイインピーダンス状態にする。

20

【0049】

ループフィルタ2は、入力される位相差信号( $P_D$ )がプラスの値の場合第1の制御電圧( $V_{ca}$ )を増加させ、マイナスの値の場合第1の制御電圧( $V_{ca}$ )を減少させる。また、位相差信号( $P_D$ )がハイインピーダンス状態の場合、第1の制御電圧( $V_{ca}$ )の電圧を保持する。

【0050】

電圧制御発振器4は、入力される第2の制御電圧( $V_c$ )の値が増加すると、出力クロック( $f_o$ )の周波数を増加させ、第2の制御電圧( $V_c$ )の値が減少すると、出力クロック( $f_o$ )の周波数を減少させる。

30

【0051】

このため、リファレンスクロック( $f_i$ )が入力状態の時は、図3に示すように、出力クロック( $f_o$ )、位相差信号( $P_D$ )、第2の制御電圧( $V_c$ )が制御され、この結果リファレンスクロック( $f_i$ )と出力クロック( $f_o$ )の周波数が一致する。通常、第2の制御電圧( $V_c$ )は位相が同期したときの第2の制御電圧( $V_c$ )を中心に振動しやがて収束する。

【0052】

このときA/Dコンバータ6は、第1の制御電圧( $V_{ca}$ )の値をデジタル値に変換し第1のデジタル制御電圧( $V_{cad}$ )として出力する。

40

【0053】

演算部8は、第1のデジタル制御電圧( $V_{cad}$ )を入力し内部にて処理し、第1のデジタル制御電圧( $V_{ca}$ )の平均値( $REFVD$ )と振動用パラメータとを演算し格納する(図2のステップ23)。

【0054】

次に、リファレンスクロック( $f_i$ )が断状態のときの動作を説明する。

【0055】

リファレンスクロック( $f_i$ )が断状態のときは、断検出回路5はリファレンスクロック( $f_i$ )が断状態であることを示す断検出信号( $M_{ON}$ )を演算部8に出力する。

50

## 【0056】

演算部8はこの断検出信号(MON)を受け第2の切り替え指示を示す切り替え信号を切り替え回路9に出力し、切り替え回路9に第3の制御電圧(Vcd)を第2の制御信号(Vc)として出力させる(図2のステップ21とステップ24)。

## 【0057】

制御電圧発振器が入力する第2の制御電圧(Vc)が第3の制御電圧(Vcd)に切り替わると、位相比較器1とループフィルタ2とA/Dコンバータ6と演算部8とD/Aコンバータ7と電圧制御発振器4とのループが構成される。

## 【0058】

演算部8は、図2のステップ23で格納した第1のデジタル制御電圧(Vca)の平均値(REFVD)と振動用パラメータとを使用して第2のデジタル制御電圧(VD)の値を作成し出力する(図2のステップ25)。

## 【0059】

D/Aコンバータ7は、第2のデジタル制御電圧(VD)を入力しこの値に対応するアナログ電圧である第3の制御電圧(Vcd)を出力する。これにより、電圧制御発振器4に入力される第2の制御電圧(Vc)は、演算部8にて制御される。

## 【0060】

このため、リファレンスロック(f1)が入力状態の時は、図4に示すように、出力クロック(f0)、第2の制御電圧(Vc)が制御される。

## 【0061】

ここで、演算部8の詳細な動作について図5から図8を参照して説明する。

## 【0062】

初めに、演算部8にて使用する変数の定義について、図5を使用して説明する。

## 【0063】

A/Dコンバータ6より入力される第1のデジタル制御電圧(Vcad)を一定周期(例えば、1MHz~0.2Hz程度であるが、この値はシステムにより異なり適宜決定する。)でサンプリングし、その平均を計算した値を第1のデジタル制御電圧(Vcad)の平均値(REFVD)とする。この一定周期を予め定めた周期とし、この周期で他の計算も行う。

## 【0064】

ある時間にて演算部8が第2のデジタル制御電圧(VD)を設定した場合に、前回設定した第2のデジタル制御電圧(VD)をVD\_BAKとする。

## 【0065】

第2のデジタル制御電圧(VD)の傾き(変化量)をVD\_BAKと第2のデジタル制御電圧(VD)の差で計算し VDとする。

## 【0066】

ある時間にて演算部8が VDを計算した場合に、前回計算した VDを VD\_BAKとする。

## 【0067】

VDの変化量を VD\_BAKと VDの差で計算し、 VDとする。

## 【0068】

第2のデジタル制御電圧(VD)が平均値(REFVD)より小さい場合から大きい場合になったときから、平均値(REFVD)より大きい場合から小さい場合になったときまでの VDの平均を VD\_Pとする。 VD\_Pは、第2のデジタル制御電圧(VD)が平均値(REFVD)より小さくなったときに更新される。

## 【0069】

第2のデジタル制御電圧(VD)が平均値(REFVD)より大きい場合から小さい場合になったときから、平均値(REFVD)より小さい場合から大きい場合になったときまでの VDの平均を VD\_Mとする。 VD\_Mは、第2のデジタル制御電圧(VD)が平均値(REFVD)より大きくなったときに更新される。

10

20

30

40

50

## 【0070】

$k$  はリファレンスロック ( $f_i$ ) が断状態のときに  $VD\_P$  及び  $VD\_M$  を減少させる係数であり、その値は  $0 < k < 1$  である。

## 【0071】

$Cst$  は、リファレンスロック ( $f_i$ ) が入力状態にあるときデクリメントする変数であり、 $Cst$  が 0 になったとき、リファレンスロック ( $f_i$ ) が断状態のときに演算部 8 にて第 2 のデジタル制御電圧 ( $VD$ ) の制御を行い、0 ではない場合第 2 のデジタル制御電圧 ( $VD$ ) の制御を行わない。これは、リファレンスロック ( $f_i$ ) が入力されている時間が短い場合に誤制御を行わないようにするためである。

## 【0072】

次に、リファレンスロック ( $f_i$ ) が入力状態のときの演算部 8 の動作 (図 2 のステップ 23) について、図 6 を参照して説明する。

## 【0073】

ステップ 601 では、現在の第 2 のデジタル制御電圧 ( $VD$ ) を  $VD\_BAK$  とし、 $VD$  を  $VD\_BAK$  とする。

## 【0074】

ステップ 602 では、A/D コンバータ 6 より入力される第 1 のデジタル制御電圧 ( $Vc$ ) を読み取り第 2 のデジタル制御電圧 ( $VD$ ) とする。

## 【0075】

ステップ 603 では、第 2 のデジタル制御電圧 ( $VD$ ) の平均値 ( $REFVD$ ) を算出 ( $VD$  を積算し、積算回数で割る) する。

## 【0076】

ステップ 604 では、第 2 のデジタル制御電圧 ( $VD$ ) の傾きを算出 ( $VD\_BAK - VD$ ) し  $VD$  とする。

## 【0077】

ステップ 605 では、 $VD$  の変化量を計算 ( $VD\_BAK - VD$ ) し  $VD$  とする。

## 【0078】

ステップ 606 では、第 2 のデジタル制御電圧 ( $VD$ ) が平均値 ( $REFVD$ ) より大きいか否かを判断する。

## 【0079】

ステップ 607 では、ステップ 606 で行った判断にて、第 2 のデジタル制御電圧 ( $VD$ ) が平均値 ( $REFVD$ ) よりも大きい場合、 $VD\_BAK$  が平均値 ( $REFVD$ ) より小さいか否かを判断する。

## 【0080】

ステップ 608 では、ステップ 607 で行った判断にて、 $VD\_BAK$  が平均値 ( $REFVD$ ) よりも大きい場合、 $VD$  を積算し終了する。

## 【0081】

ステップ 609 では、ステップ 607 で行った判断にて、 $VD\_BAK$  が平均値 ( $REFVD$ ) よりも小さい場合、ステップ 608 にて積算した値を積算回数で割ることで  $VD$  の平均値を計算し  $VD\_P$  とし、ステップ 612 へ進む。

## 【0082】

ステップ 610 では、ステップ 606 で行った判断にて、第 2 のデジタル制御電圧 ( $VD$ ) が平均値 ( $REFVD$ ) より小さい場合、 $VD\_BAK$  が平均値 ( $REFVD$ ) より大きいか否かを判断し、 $VD\_BAK$  が平均値 ( $REFVD$ ) よりも小さい場合、ステップ 608 へ進む。

## 【0083】

ステップ 611 では、ステップ 610 で行った判断にて、 $VD\_BAK$  が平均値 ( $REFVD$ ) よりも大きい場合、ステップ 608 にて積算した値を積算回数で割ることで  $VD$  の平均値を計算し  $VD\_M$  としステップ 612 へ進む。

10

30

40

50

## 【0084】

ステップ612では、ステップ608にて積算した値をクリアする。

## 【0085】

ステップ613では、Cstが0であるか否かを判断し、Cstが0であるかときには、ステップ614で、リファレンスロック(f\_i)が断状態のときの制御を許可し、終了する。

## 【0086】

また、Cstが0ないときには、ステップ615で、リファレンスロック(f\_i)が断状態のときの制御を禁止し、ステップ616で、Cstをデクリメントし終了する。

## 【0087】

次に、リファレンスロック(f\_i)が断状態のときの演算部8の動作(図2のステップ25)について、図7を参照して説明する。

## 【0088】

初めに、ステップ701で、D/Aコンバータ7へ第2のデジタル制御電圧(VD)を出力し、

ステップ702で、図6のステップ614でリファレンスロック(f\_i)が断状態のときの制御を許可されているか否かを判断し、リファレンスロック(f\_i)が断状態のときの制御を許可されていないときには終了し、許可されているときには、ステップ703へ進む。

## 【0089】

ステップ703では、第2のデジタル制御電圧(VD)が平均値(REFVD)より大きいか否かを判断し、大きいと判断したときにはステップ704へ進み、大きくないと判断したときにはステップ707へ進む。

## 【0090】

ステップ704では、VDとVD\_Pとを使用して第2のデジタル制御電圧(VD)を計算する。計算式は、今回の $VD = \text{前回の} VD + (VD + VD_P)$ である。

## 【0091】

ステップ705では、VD\_BAKが平均値(REFVD)より小さいか否かを判断し、小さいと判断したときにはステップ706へ進み、小さくないと判断したときには終了する。

## 【0092】

ステップ706では、計算式 $VD_P = VD_P \times k$ により、VD\_Pの値を補正し終了する。

## 【0093】

ステップ703で、第2のデジタル制御電圧(VD)が平均値(REFVD)より大きくないと判断したとき、ステップ707へ進み、ステップ707では、VDとVD\_Mとを使用して第2のデジタル制御電圧(VD)を計算する。計算式は、今回の $VD = \text{前回の} VD + (VD + VD_M)$ である。

## 【0094】

ステップ708では、VD\_BAKが平均値(REFVD)より大きいか否かを判断し、大きいと判断したときにはステップ709へ進み、大きくないと判断したときには終了する。

## 【0095】

ステップ709では、計算式 $VD_M = VD_M \times k$ により、VD\_Mの値を補正し終了する。

## 【0096】

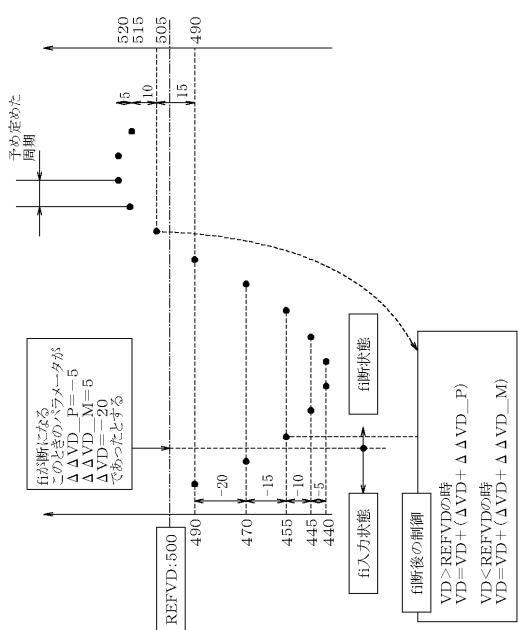

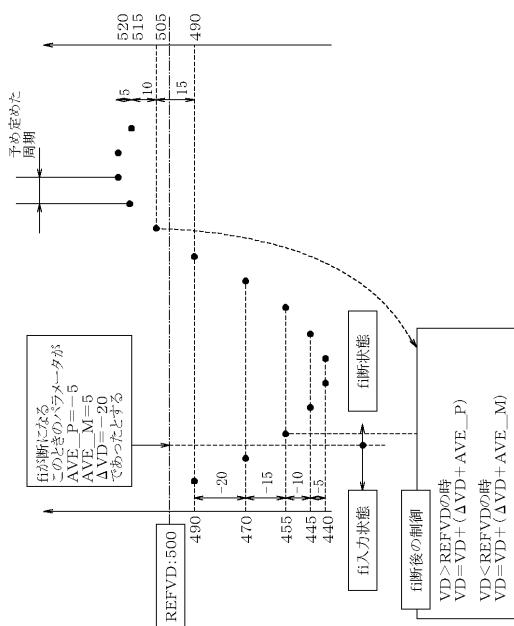

ここで、図8を参照して、リファレンスロック(f\_i)が断状態のときの第2のデジタル制御電圧(VD)の計算例を示す(計算方法は図7に示すフローチャートに従って行う)。

## 【0097】

10

20

30

40

50

図8では、リファレンスクロック( $f_i$ )が断状態になったときの、第2のデジタル制御電圧( $V_D$ )を455、 $V_D_P = -5$ 、 $V_D_M = 5$ 、 $V_D = -20$ 、平均値( $REFVD$ )=500とし、予め定めた周期毎の第2のデジタル制御電圧( $V_D$ )を黒丸で示している。

【0098】

図8に示すように、予め定めた周期毎の各第2デジタル制御電圧( $V_D$ )の値による外観が、この予め定めた周期よりも大きな周期(例えば、10倍から10000倍程度の周期)であるが、この値はシステムにより異なり適宜決定する。)で平均値( $REFVD$ )を中心にして振動している。また、傾きの変化量の平均値である $V_D_P$ と $V_D_M$ を係数kにて補正しているため、その制御量は時間が経つにつれて小さくなる。これにより、電圧制御発振器4の第3の制御電圧( $V_c$ )をその平均値を中心として収束させながら振動させることができ、リファレンスクロック( $f_i$ )が入力されている状態の位相同期回路の制御電圧の変化を実現できるため、リファレンスクロック( $f_i$ )が断状態のときでも、位相同期を保つための制御を持続することが可能になる。

10

【0099】

図9は、本発明の位相同期回路の第2の実施の形態を示すブロック図である。

【0100】

図9に示す第2の実施の形態は、位相比較器1と、ループフィルタ2と、電圧制御手段90と、電圧制御発振器4とにより構成する。

20

【0101】

図1に示す第1の実施の形態とは、電圧制御手段90の中の演算部91のみが異なり、演算部91以外の構成の機能は第1の実施の形態と同じである。

【0102】

ここでは、演算部91の機能を説明する。

【0103】

演算部91は、断検出回路5が output した断検出信号( $MON$ )を受けるとともに、A/Dコンバータ6が output した第1のデジタル制御電圧( $V_{cad}$ )を予め定めた周期毎に受け、断検出信号( $MON$ )がリファレンスクロックの入力があることを示す入力状態を示すときに、第1の切り替え指示を示す切り替え信号を出力し、第1のデジタル制御電圧( $V_{cad}$ )の平均値( $REFVD$ )と振動用パラメータとを予め定めた周期毎に演算しておく。

30

【0104】

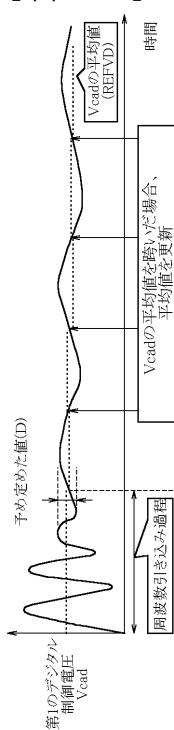

このとき、第1のデジタル制御電圧( $V_{cad}$ )の平均値( $REFVD$ )の演算は、次のように行う。すなわち、図10で示すように、第1のデジタル制御電圧( $V_{cad}$ )の変動の幅が予め定めた値D(例えば、1mV程度の値。この値はシステムにより適宜変えて良い。)より小さくなることを示す周波数の引き込み過程が終了したときに、この変動の中心の値を第1のデジタル制御電圧( $V_{cad}$ )の平均値( $REFVD$ )とし、その後、第1のデジタル制御電圧( $V_{cad}$ )がこの平均値より大又は小になった後に小又は大になる毎に、第1のデジタル制御電圧( $V_{cad}$ )がこの平均値より大又は小になった後に小又は大になるまでの第1のデジタル制御電圧( $V_{cad}$ )の平均をこの平均値( $REFVD$ )に置き換えて平均値( $REFVD$ )を更新する。

40

【0105】

そして、断検出信号( $MON$ )がリファレンスクロック( $f_i$ )の入力がないことを示す断状態を示すときから、第2の切り替え指示を示す切り替え信号を出力し、格納しておいた第1のデジタル制御電圧( $V_{cad}$ )の平均値( $REFVD$ )と振動用パラメータとを使用して第2のデジタル制御電圧( $V_D$ )を予め定めた周期で作成しこの作成した第2のデジタル制御電圧( $V_D$ )を予め定めた周期で出力する。

【0106】

そして、演算部91は、第2のデジタル制御電圧( $V_D$ )を出力するときに、この第2のデジタル制御電圧( $V_D$ )を第1のデジタル制御電圧( $V_{cad}$ )の平均値( $REFVD$ )

50

)を中心いて振動させるために、この振動用パラメータを使用する。すなわち、 $V_D_P$ の平均を演算して $AVE\_P$ とし、 $V_D_M$ の平均を演算して $AVE\_M$ とし、予め定めた周期で、前回出力した第2のデジタル制御電圧( $V_D$ )に $V_D$ と $AVE\_P$ 又は $AVE\_M$ を加えて新たな第2のデジタル制御電圧( $V_D$ )を作成し、この作成した新たな第2のデジタル制御電圧( $V_D$ )を今回出力する。

【0107】

次に、第2の実施の形態の位相同期回路の動作を図2、図3、図4、図5、図11、図12から図13を参照して詳細に説明する。

【0108】

図2は、第1の実施の形態での演算部の概要動作の一例を示すフローチャートであるとともに第2の実施の形態での演算部の概要動作の一例を示すフローチャートである。

【0109】

図11は、リファレンスクロック( $f_i$ )が入力状態のときの演算部の動作の一例を示すフローチャートである。

【0110】

図12は、リファレンスクロック( $f_i$ )が断状態のときの演算部の動作の一例を示すフローチャートである。

【0111】

図13は、リファレンスクロック( $f_i$ )が断状態のときの第2のデジタル制御電圧( $V_D$ )の計算例を示す図である。

【0112】

図9において、初めに、リファレンスクロック( $f_i$ )が入力状態のときの動作を説明する。リファレンスクロック( $f_i$ )が入力状態のときは、断検出回路5はリファレンスクロック( $f_i$ )が入力状態であることを示す断検出信号( $MON$ )を演算部91に出力する。

【0113】

演算部91はこの断検出信号( $MON$ )を受け第1の切り替え指示を示す切り替え信号を切り替え回路9に出力し、切り替え回路9に第1の制御電圧( $V_{ca}$ )を第2の制御信号( $V_c$ )として出力させる(図2のステップ21とステップ22)。

【0114】

制御電圧発振器が入力する第2の制御電圧( $V_c$ )が第1の制御電圧( $V_{ca}$ )に切り替わると、位相比較器1とループフィルタ2と電圧制御発振器4とのループが構成される。

【0115】

この場合、位相比較器1は、電圧制御発振器4より出力される出力クロック( $f_o$ )と、リファレンスクロック( $f_i$ )の位相を比較し、出力クロック( $f_o$ )の位相がリファレンスクロック( $f_i$ )の位相よりも遅れている場合プラスの値の位相差信号( $PD$ )を出力し、進んでいる場合マイナスの値の位相差信号( $PD$ )を出力する。また、位相が一致しているときには、位相差信号( $PD$ )をハイインピーダンス状態にする。

【0116】

ループフィルタ2は、入力される位相差信号( $PD$ )がプラスの値の場合第1の制御電圧( $V_{ca}$ )を増加させ、マイナスの値の場合第1の制御電圧( $V_{ca}$ )を減少させる。また、位相差信号( $PD$ )がハイインピーダンス状態の場合、第1の制御電圧( $V_{ca}$ )の電圧を保持する。

【0117】

電圧制御発振器4は、入力される第2の制御電圧( $V_c$ )の値が増加すると、出力クロック( $f_o$ )の周波数を増加させ、第2の制御電圧( $V_c$ )の値が減少すると、出力クロック( $f_o$ )の周波数を減少させる。

【0118】

このため、リファレンスクロック( $f_i$ )が入力状態の時は、図3に示すように、出力クロック( $f_o$ )、位相差信号( $PD$ )、第2の制御電圧( $V_c$ )が制御され、この結果リ

10

20

30

40

50

ファレンスクロック (f<sub>i</sub>) と出力クロック (f<sub>o</sub>) の周波数が一致する。通常、第2の制御電圧 (V<sub>c</sub>) は位相が同期したときの第2の制御電圧 (V<sub>c</sub>) を中心に振動しやがて収束する。

【0119】

このとき A/D コンバータ 6 は、第1の制御電圧 (V<sub>c a</sub>) の値をデジタル値に変換し第1のデジタル制御電圧 (V<sub>c a d</sub>) として出力する。

【0120】

演算部 91 は、第1のデジタル制御電圧 (V<sub>c a d</sub>) を入力し内部にて処理し、第1のデジタル制御電圧 (V<sub>c a</sub>) の平均値 (REFVD) と振動用パラメータとを演算し格納する (図2のステップ23)。

10

【0121】

次に、リファレンスクロック (f<sub>i</sub>) が断状態のときの動作を説明する。

【0122】

リファレンスクロック (f<sub>i</sub>) が断状態のときは、断検出回路 5 はリファレンスクロック (f<sub>i</sub>) が断状態であることを示す断検出信号 (MON) を演算部 91 に出力する。

【0123】

演算部 91 はこの断検出信号 (MON) を受け第2の切り替え指示を示す切り替え信号を切り替え回路 9 に出力し、切り替え回路 9 に第3の制御電圧 (V<sub>c d</sub>) を第2の制御信号 (V<sub>c</sub>) として出力させる (図2のステップ21とステップ24)。

20

【0124】

制御電圧発振器が入力する第2の制御電圧 (V<sub>c</sub>) が第3の制御電圧 (V<sub>c d</sub>) に切り替わると、位相比較器 1 とループフィルタ 2 と A/D コンバータ 6 と演算部 91 と D/A コンバータ 7 と電圧制御発振器 4 とのループが構成される。

【0125】

演算部 91 は、図2のステップ23で格納した第1のデジタル制御電圧 (V<sub>c a</sub>) の平均値 (REFVD) と振動用パラメータとを使用して第2のデジタル制御電圧 (VD) の値を作成し出力する (図2のステップ25)。

【0126】

D/A コンバータ 7 は、第2のデジタル制御電圧 (VD) を入力しこの値に対応するアナログ電圧である第3の制御電圧 (V<sub>c d</sub>) を出力する。これにより、電圧制御発振器 4 に入力される第2の制御電圧 (V<sub>c</sub>) は、演算部 91 にて制御される。

30

【0127】

このため、リファレンスクロック (f<sub>i</sub>) が入力状態の時は、図4に示すように、出力クロック (f<sub>o</sub>)、第2の制御電圧 (V<sub>c</sub>) が制御される。

【0128】

ここで、演算部 91 の詳細な動作について図5、図11から図13を参照して説明する。

【0129】

初めに、演算部 91 にて使用する変数の定義について、図5を使用して説明する。

【0130】

A/D コンバータ 6 より入力される第1のデジタル制御電圧 (V<sub>c a d</sub>) を一定周期 (例えば、1MHz ~ 0.2Hz 程度であるが、この値はシステムにより異なり適宜決定する。) でサンプリングし、このサンプリング値を使用して第1のデジタル制御電圧 (V<sub>c a d</sub>) の平均値 (REFVD) の演算を行う。すなわち、新図4で示すように、第1のデジタル制御電圧 (V<sub>c a d</sub>) の変動の幅が予め定めた値 D より小さくなることを示す周波数の引き込み過程が終了したときに、この変動の中心の値を第1のデジタル制御電圧 (V<sub>c a d</sub>) の平均値 (REFVD) とし、その後、第1のデジタル制御電圧 (V<sub>c a d</sub>) がこの平均値より大又は小になった後に小又は大になる毎に、第1のデジタル制御電圧 (V<sub>c a d</sub>) がこの平均値より大又は小になった後に小又は大になるまでの第1のデジタル制御電圧 (V<sub>c a d</sub>) の平均をこの平均値 (REFVD) として更新する。この一定周期を予め定めた周期とし、この周期で他の計算も行う。

40

50

## 【0131】

ある時間にて演算部91が第2のデジタル制御電圧(VD)を設定した場合に、前回設定した第2のデジタル制御電圧(VD)をVD\_BAKとする。

## 【0132】

第2のデジタル制御電圧(VD)の傾き(変化量)をVD\_BAKと第2のデジタル制御電圧(VD)の差で計算し VDとする。

## 【0133】

ある時間にて演算部91が VDを計算した場合に、前回計算した VDを VD\_BAKとする。

## 【0134】

VDの変化量を VD\_BAKと VDの差で計算し、 VDとする。 10

## 【0135】

第2のデジタル制御電圧(VD)が平均値(REFVD)より小さい場合から大きい場合になったときから、平均値(REFVD)より大きい場合から小さい場合になったときまでの VDの平均を VD\_Pとする。 VD\_Pは、第2のデジタル制御電圧(VD)が平均値(REFVD)より小さくなったとき、平均値(REFVD)より小さくなる毎に次々と格納していく。

## 【0136】

第2のデジタル制御電圧(VD)が平均値(REFVD)より大きい場合から小さい場合になったときから、平均値(REFVD)より小さい場合から大きい場合になったときまでの VDの平均を VD\_Mとする。 VD\_Mは、第2のデジタル制御電圧(VD)が平均値(REFVD)より大きくなったとき、平均値(REFVD)より大きくなる毎に次々と格納していく。 20

## 【0137】

Cstは、リファレンスクロック(f\_i)が入力状態にあるときデクリメントする変数であり、Cstが0になったとき、リファレンスクロック(f\_i)が断状態のときに演算部91にて第2のデジタル制御電圧(VD)の制御を行い、0ではない場合第2のデジタル制御電圧(VD)の制御を行わない。これは、リファレンスクロック(f\_i)が入力されている時間が短い場合に誤制御を行わないようにするためである。

## 【0138】

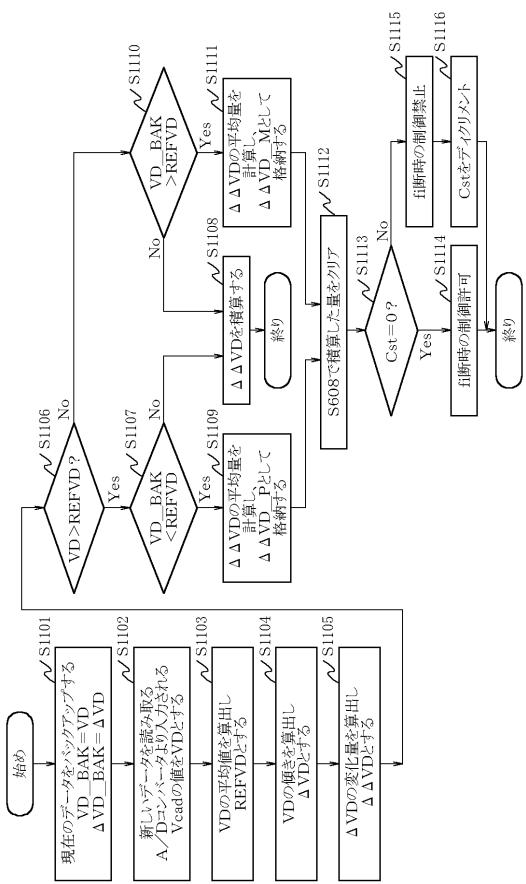

次に、リファレンスクロック(f\_i)が入力状態のときの演算部91の動作(図2のステップ23)について、図11を参照して説明する。 30

## 【0139】

ステップ1101では、現在の第2のデジタル制御電圧(VD)をVD\_BAKとし、VDを VD\_BAKとする。

## 【0140】

ステップ1102では、A/Dコンバータ6より入力される第1のデジタル制御電圧(Vcad)を読み取り第2のデジタル制御電圧(VD)とする。

## 【0141】

ステップ1103では、図10で示すように、第1のデジタル制御電圧(Vcad)の変動の幅が予め定めた値Dより小さくなることを示す周波数の引き込み過程が終了したときに、この変動の中心の値を第1のデジタル制御電圧(Vcad)及び第2のデジタル制御電圧(VD)の平均値(REFVD)とし、その後、第1のデジタル制御電圧(Vcad)又は第2のデジタル制御電圧(VD)がこの平均値より大又は小になった後に小又は大になる毎に、第1のデジタル制御電圧(Vcad)又は第2のデジタル制御電圧(VD)がこの平均値より大又は小になった後に小又は大になるまでの第1のデジタル制御電圧(Vcad)及び第2のデジタル制御電圧(VD)の平均をこの平均値(REFVD)に置き換えて平均値を更新する。 40

## 【0142】

ステップ1104では、第2のデジタル制御電圧(VD)の傾きを算出( VD\_BAK - 50

V D ) し V D とする。

【 0 1 4 3 】

ステップ 1 1 0 5 では、 V D の変化量を計算 ( V D \_ B A K - V D ) し V D とする。

【 0 1 4 4 】

ステップ 1 1 0 6 では、第 2 のデジタル制御電圧 ( V D ) が平均値 ( R E F V D ) より大きいか否かを判断する。

【 0 1 4 5 】

ステップ 1 1 0 7 では、ステップ 1 1 0 6 で行った判断にて、第 2 のデジタル制御電圧 ( V D ) が平均値 ( R E F V D ) よりも大きい場合、 V D \_ B A K が平均値 ( R E F V D ) 10 より小さいか否かを判断する。

【 0 1 4 6 】

ステップ 1 1 0 8 では、ステップ 1 1 0 7 で行った判断にて、 V D \_ B A K が平均値 ( R E F V D ) よりも大きい場合、 V D を積算し終了する。

【 0 1 4 7 】

ステップ 1 1 0 9 では、ステップ 1 1 0 7 で行った判断にて、 V D \_ B A K が平均値 ( R E F V D ) よりも小さい場合、ステップ 1 1 0 8 にて積算した値を積算回数で割ることで V D の平均値を計算し V D \_ P としこれを格納し、ステップ 1 1 1 2 へ進む。

【 0 1 4 8 】

ステップ 1 1 1 0 では、ステップ 1 1 0 6 で行った判断にて、第 2 のデジタル制御電圧 ( V D ) が平均値 ( R E F V D ) より小さい場合、 V D \_ B A K が平均値 ( R E F V D ) より大きいか否かを判断し、 V D \_ B A K が平均値 ( R E F V D ) よりも小さい場合、ステップ 1 1 0 8 へ進む。

【 0 1 4 9 】

ステップ 1 1 1 1 では、ステップ 1 1 1 0 で行った判断にて、 V D \_ B A K が平均値 ( R E F V D ) よりも大きい場合、ステップ 1 1 0 8 にて積算した値を積算回数で割ることで V D の平均値を計算し V D \_ M としこれを格納しステップ 1 1 1 2 へ進む。

【 0 1 5 0 】

ステップ 1 1 1 2 では、ステップ 1 1 0 8 にて積算した値をクリアする。

【 0 1 5 1 】

ステップ 1 1 1 3 では、 C s t が 0 であるか否かを判断し、 C s t が 0 であるかときには、ステップ 1 1 1 4 で、リファレンスクロック ( f i ) が断状態のときの制御を許可し、終了する。

【 0 1 5 2 】

また、 C s t が 0 ないときには、ステップ 1 1 1 5 で、リファレンスクロック ( f i ) が断状態のときの制御を禁止し、ステップ 1 1 1 6 で、 C s t をデクリメントし終了する。

【 0 1 5 3 】

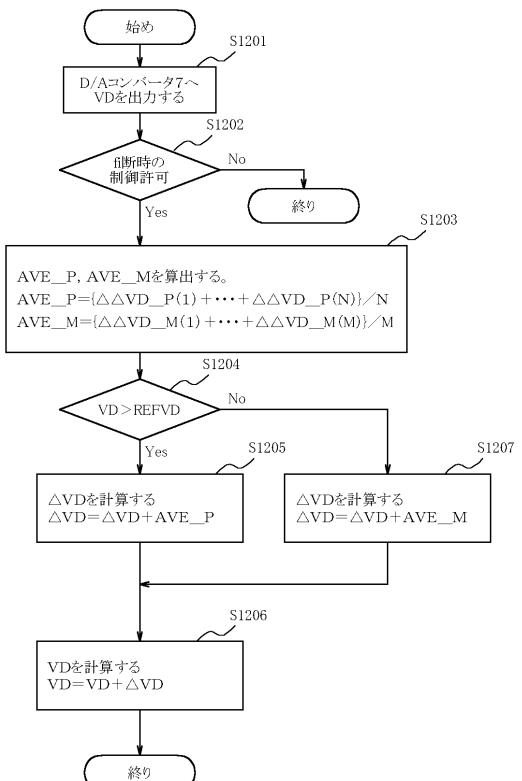

次に、リファレンスクロック ( f i ) が断状態のときの演算部 9 1 の動作 ( 図 2 のステップ 2 5 ) について、図 1 2 を参照して説明する。

【 0 1 5 4 】

初めに、ステップ 1 2 0 1 で、 D / A コンバータ 7 へ第 2 のデジタル制御電圧 ( V D ) を出力し、

ステップ 1 2 0 2 で、図 1 1 のステップ 1 1 1 4 でリファレンスクロック ( f i ) が断状態のときの制御を許可されているか否かを判断し、リファレンスクロック ( f i ) が断状態のときの制御を許可されていないときには終了し、許可されているときには、ステップ 1 2 0 3 へ進む。

【 0 1 5 5 】

ステップ 1 2 0 3 では、図 1 1 のステップ 1 1 0 9 で格納した V D \_ P を格納時間の少ない順に予め定めた個数 ( N : N はシステムにより適宜決めて良い ) 取り出してこの平均を取り A V E \_ P とする。同様に、図 1 1 のステップ 1 1 1 1 で格納した V D \_ M 50

を格納時間の少ない順に予め定めた個数 (M : M はシステムにより適宜決めて良い) 取り出してこの平均を取り  $A V E\_M$  とする。

【0156】

ステップ 1204 では、第 2 のデジタル制御電圧 (V D) が平均値 (REFVD) より大きいか否かを判断し、大きいと判断したときにはステップ 1205 へ進み、大きくないと判断したときにはステップ 1207 へ進む。

【0157】

ステップ 1205 では、V D と  $A V E\_P$  とを使用して第 2 のデジタル制御電圧 (V D) の傾き ( $\Delta V D$ ) を計算する。計算式は、今回の  $V D = \text{前回の } V D + A V E\_P$  である。計算後ステップ 1206 へ進む。

10

【0158】

ステップ 1206 では、V D を使用して第 2 のデジタル制御電圧 (V D) を計算する。計算式は、今回の  $V D = \text{前回の } V D + \text{今回の } V D$  である。計算後終了する。

【0159】

一方、ステップ 1207 では、V D と  $A V E\_M$  とを使用して第 2 のデジタル制御電圧 (V D) の傾き ( $\Delta V D$ ) を計算する。計算式は、今回の  $V D = \text{前回の } V D + A V E\_M$  である。計算後ステップ 1206 へ進む。

【0160】

ここで、図 13 を参照して、リファレンスクロック ( $f_i$ ) が断状態のときの第 2 のデジタル制御電圧 (V D) の計算例を示す (計算方法は図 12 に示すフロー チャートに従って行う)。

【0161】

図 13 では、リファレンスクロック ( $f_i$ ) が断状態になったときの、第 2 のデジタル制御電圧 (V D) を 455、 $A V E\_P = -5$ 、 $A V E\_M = 5$ 、 $V D = -20$ 、平均値 (REFVD) = 500 とし、予め定めた周期毎の第 2 のデジタル制御電圧 (V D) を黒丸で示している。

【0162】

図 13 に示すように、予め定めた周期毎の各第 2 デジタル制御電圧 (V D) の値による外観が、この予め定めた周期よりも大きな周期 (例えば、10 倍から 10000 倍程度の周期であるが、この値はシステムにより異なり適宜決定する。) で平均値 (REFVD) を中心にして振動している。

20

【0163】

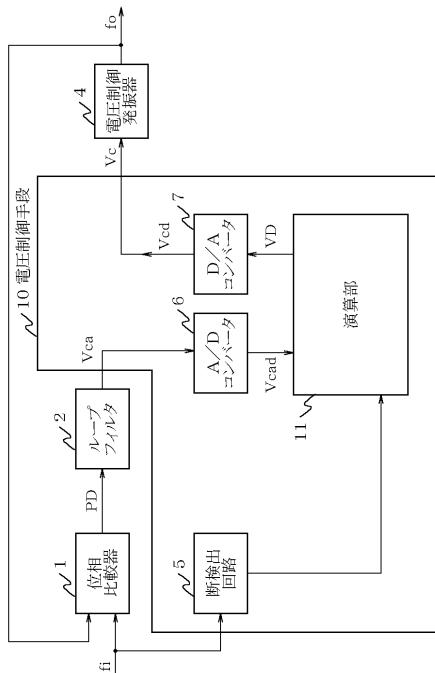

図 14 は、本発明の位相同期回路の第 3 の実施の形態を示すブロック図である。

【0164】

図 14 に示す本実施の形態は、位相比較器 1 と、ループフィルタ 2 と、電圧制御手段 10 と、電圧制御発振器 4 とにより構成し、位相比較器 1、ループフィルタ 2、電圧制御手段 10 及び電圧制御発振器 4 の動作は、図 1 に示した本発明の位相同期回路の第 1 の実施の形態と同様であるが、第 1 の実施の形態とは、電圧制御手段 10 内の構成と動作が異なる。

30

【0165】

電圧制御手段 10 は、断検出回路 5 と A / D コンバータ 6 と D / A コンバータ 7 とは、第 1 の実施の形態で示したものと同様であり、演算部 11 が第 1 の実施の形態で示したものと異なる。

【0166】

演算部 11 は、断検出回路 5 が output した断検出信号 (MON) を受けるとともに、A / D コンバータ 6 が output した第 1 のデジタル制御電圧 (Vcad) を予め定めた周期毎に受け、断検出信号 (MON) がリファレンスクロックの入力があることを示す入力状態を示すときに、第 1 のデジタル制御電圧 (Vcad) を第 2 のデジタル制御電圧 (V D) として出力し、第 1 のデジタル制御電圧 (Vcad) の平均値 (REFVD) と振動用パラメータとを予め定めた周期毎に演算して最新結果を格納しておき、断検出信号 (MON) が前

40

50

記リファレンスクロックの入力がないことを示す断状態を示すときから、格納しておいた第1のデジタル制御電圧( $V_{cad}$ )の平均値( $REFVD$ )と振動用パラメータとを使用して第2のデジタル制御電圧( $VD$ )を予め定めた周期で作成しこの作成した第2のデジタル制御電圧( $VD$ )を予め定めた周期で出力する。

【0167】

ここで、図2に示した第1の実施の形態での演算部8の概要動作に対応させて、第3の実施の形態での演算部の概要動作の一例を示すフローチャートである図15を参照して、第3の実施の形態での演算部11の動作の概要を説明する。

【0168】

ステップ101は、図2のステップ21と同様であり、断検出回路5からの断検出信号( $MON$ )が入力状態を示す信号か断状態を示す信号か調べ、断検出信号( $MON$ )が入力状態を示す信号のときはステップ102へ進み、断検出信号( $MON$ )が断状態を示す信号のときにはステップ104へ進む。 10

【0169】

図2のステップ22では、第1の切り替え指示を示す切り替え信号を切り替え回路9に出力し、切り替え回路9に第1の制御電圧( $V_{ca}$ )を第2の制御信号( $V_c$ )として出力させるのに対し、図15のステップ102では、A/Dコンバータ6より入力する第1のデジタル制御電圧( $V_{cad}$ )を第2のデジタル制御電圧( $VD$ )としてD/Aコンバータ7に出力する。これにより、D/Aコンバータ7はこの第2のデジタル制御電圧( $VD$ )を第3の制御電圧( $V_{cd}$ )に変換しこの変換した第3の制御電圧( $V_{cd}$ )を第2の制御電圧( $V_c$ )として電圧制御部に出力する。 20

【0170】

ステップ103は、図2のステップ23と同様であり、A/Dコンバータ6より入力する第1のデジタル制御電圧( $V_{ca}$ )の平均値( $REFVD$ )と振動用パラメータとを演算し格納する。

【0171】

図2のステップ24では、第2の切り替え指示を示す切り替え信号を切り替え回路9に出力し、切り替え回路9に第3の制御電圧( $V_{cd}$ )を第2の制御信号( $V_c$ )として出力させるのに対し、図15のステップ104では、D/Aコンバータ7への出力を、A/Dコンバータ6から入力した第1のデジタル制御電圧( $V_{cad}$ )から演算部11内部で計算した第2のデジタル制御電圧( $VD$ )へ切り替える。 30

【0172】

ステップ105は、図2のステップ25と同様であり、ステップ103で格納しておいた第1のデジタル制御電圧( $V_{cad}$ )の平均値( $REFVD$ )と振動用パラメータとを使用して第2のデジタル制御電圧( $VD$ )を作成し出力する。

【0173】

図16は、本発明の位相同期回路の第4の実施の形態を示すブロック図である。

【0174】

図16に示す本実施の形態は、位相比較器1と、ループフィルタ2と、電圧制御手段160と、電圧制御発振器4とにより構成し、位相比較器1、ループフィルタ2、電圧制御手段160及び電圧制御発振器4の動作は、図14に示した本発明の位相同期回路の第3の実施の形態と同様であるが、第3の実施の形態とは、電圧制御手段160内の動作が異なる。 40

【0175】

電圧制御手段160は、断検出回路5とA/Dコンバータ6とD/Aコンバータ7とは、第3の実施の形態で示したものと同様であり、演算部161が第3の実施の形態で示したものと異なる。

【0176】

演算部161は、断検出回路5が出力した断検出信号( $MON$ )を受けるとともに、A/Dコンバータ6が出力した第1のデジタル制御電圧( $V_{cad}$ )を予め定めた周期毎に受 50

け、断検出信号（M O N）がリファレンスクロックの入力があることを示す入力状態を示すとき、第1のデジタル制御電圧（V c a d）を第2のデジタル制御電圧（V D）として出力し、第1のデジタル制御電圧（V c a d）の平均値（R E F V D）と振動用パラメータとを予め定めた周期毎に演算して最新結果を格納しておく。

【0177】

このとき、第1のデジタル制御電圧（V c a d）の平均値（R E F V D）の演算は、次のように行う。すなわち、図10で示すように、第1のデジタル制御電圧（V c a d）の変動の幅が予め定めた値Dより小さくなることを示す周波数の引き込み過程が終了したときに、この変動の中心の値を第1のデジタル制御電圧（V c a d）の平均値（R E F V D）とし、その後、第1のデジタル制御電圧（V c a d）がこの平均値より大又は小になった後に小又は大になる毎に、第1のデジタル制御電圧（V c a d）がこの平均値より大又は小になった後に小又は大になるまでの第1のデジタル制御電圧（V c a d）の平均をこの平均値（R E F V D）に置き換えて平均値（R E F V D）を更新する。

【0178】

そして、断検出信号（M O N）が前記リファレンスクロックの入力がないことを示す断状態を示すときから、格納しておいた第1のデジタル制御電圧（V c a d）の平均値（R E F V D）と振動用パラメータとを使用して第2のデジタル制御電圧（V D）を予め定めた周期で作成しこの作成した第2のデジタル制御電圧（V D）を予め定めた周期で出力する。

【0179】

ここで、第3の実施の形態での演算部の概要動作の一例を示すフローチャートであるとともに第4の実施の形態での演算部の概要動作の一例を示すフローチャートである図15を参照して、第4の実施の形態での演算部161の動作の概要を説明する。

【0180】

ステップ101は、断検出回路5からの断検出信号（M O N）が入力状態を示す信号か断状態を示す信号か調べ、断検出信号（M O N）が入力状態を示す信号のときはステップ102へ進み、断検出信号（M O N）が断状態を示す信号のときにはステップ104へ進む。

【0181】

ステップ102では、A / Dコンバータ6より入力する第1のデジタル制御電圧（V c a d）を第2のデジタル制御電圧（V D）としてD / Aコンバータ7に出力する。これにより、D / Aコンバータ7はこの第2のデジタル制御電圧（V D）を第3の制御電圧（V c d）に変換しこの変換した第3の制御電圧（V c d）を第2の制御電圧（V c）として電圧制御部に出力する。

【0182】

ステップ103は、A / Dコンバータ6より入力する第1のデジタル制御電圧（V c a）の平均値（R E F V D）と振動用パラメータとを演算し格納する。

【0183】

ステップ104では、D / Aコンバータ7への出力を、A / Dコンバータ6から入力した第1のデジタル制御電圧（V c a d）から演算部161内部で計算した第2のデジタル制御電圧（V D）へ切り替える。

【0184】

ステップ105は、ステップ103で格納しておいた第1のデジタル制御電圧（V c a d）の平均値（R E F V D）と振動用パラメータとを使用して第2のデジタル制御電圧（V D）を作成し出力する。

【0185】

【発明の効果】

以上説明したように、本発明によれば、外部からのリファレンスクロックの入力が断のときに、出力クロックを制御する制御用の電圧を、リファレンスクロックの入力が断になるまでの制御用の電圧より求めた演算値（例えば、平均値）を中心に振動させるようにした

10

20

30

40

50

ため、リファレンスクロックが断状態のときに、リファレンスクロックが入力されている状態での制御用の電圧の変化を実現するので、リファレンスクロックが断のときでも、位相同期を保つための制御を持続することが可能になる。このため、リファレンスクロックの入力が断になったときにリファレンスクロックと出力クロックとの周波数にわずかな差があっても、その後、時間が経過後に、再びリファレンスクロックの入力が復帰したときに、リファレンスクロックの周波数からかけ離れた周波数の出力クロックが出力されず同期の具合が悪化しない。

【0186】

また、本発明によれば、外部からのリファレンスクロックの入力が断のときに、制御用の電圧をある中心値（演算値）を中心に振動させるようにしたが、この振動の中心値（演算値）を、外部からのリファレンスクロックの入力があるときの制御用の電圧の変動の幅が予め定めた値Dより小さくなることを示す周波数の引き込み過程が終了した後からの制御用の電圧より求めたので、電圧制御発振器に入力する制御電圧の制御誤差が少なくなる。

10

【図面の簡単な説明】

【図1】本発明の位相同期回路の第1の実施の形態を示すブロック図である。

【図2】第1の実施の形態及び第2の実施の形態での演算部の概要動作の一例を示すフローチャートである。

【図3】リファレンスクロックが入力状態のときの各信号の関係の一例を示す図である。

【図4】リファレンスクロックが断状態のときの各信号の関係の一例を示す図である。

20

【図5】演算部で使用する変数の定義を説明する図である。

【図6】リファレンスクロックが入力状態のときの演算部の動作の一例を示すフローチャートである。

【図7】リファレンスクロックが断状態のときの演算部の動作の一例を示すフローチャートである。

【図8】リファレンスクロックが断状態のときの第2のデジタル制御電圧の計算例を示す図である。

【図9】本発明の位相同期回路の第2の実施の形態を示すブロック図である。

【図10】リファレンスクロックが断状態のときの各信号の関係の一例を示す図である。

【図11】リファレンスクロックが入力状態のときの演算部の動作の一例を示すフローチャートである。

30

【図12】リファレンスクロックが断状態のときの演算部の動作の一例を示すフローチャートである。

【図13】リファレンスクロックが断状態のときの第2のデジタル制御電圧の計算例を示す図である。

【図14】本発明の位相同期回路の第3の実施の形態を示すブロック図である。

【図15】第3の実施の形態及び第4の実施の形態での演算部の概要動作の一例を示すフローチャートである。

【図16】本発明の位相同期回路の第4の実施の形態を示すブロック図である。

【図17】従来の位相同期回路のブロック図である。

【図18】従来の技術の問題点を説明する図である。

40

【符号の説明】

- 1 位相比較器

- 2 ループフィルタ

- 3 電圧制御手段

- 4 電圧制御発振器

- 5 断検出回路

- 6 A / D コンバータ

- 7 D / A コンバータ

- 8 演算部

- 9 切り替え回路

50

1 0 電圧制御手段

1 1 演算部

1 2 アナログメモリ

1 3 切り替え回路

9 0 電圧制御手段

9 1 演算部

1 6 0 電圧制御手段

1 6 1 演算部

【図3】

【 四 4 】

【 図 5 】

【 図 6 】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 3】

【図 1 2】

【図 1 4】

【 図 1 5 】

【 図 1 6 】

【 図 1 7 】

【 図 1 8 】

---

フロントページの続き

F ターム(参考) 5J106 AA04 CC01 CC21 CC41 DD09 DD33 DD35 DD36 DD44 EE06

HH03 HH10 KK03 KK18