(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2013-511894

(P2013-511894A)

(43) 公表日 平成25年4月4日(2013.4.4)

| (51) Int.Cl.                 | F 1        | テーマコード (参考) |

|------------------------------|------------|-------------|

| <b>H03H 17/02</b> (2006.01)  | H03H 17/02 | 621Z        |

| <b>H04B 15/00</b> (2006.01)  | H04B 15/00 | 5K052       |

| <b>G10K 11/178</b> (2006.01) | G10K 11/16 | H           |

| <b>H03H 17/00</b> (2006.01)  | H03H 17/00 | 621D        |

| <b>H03H 17/08</b> (2006.01)  | H03H 17/08 | A           |

審査請求 有 予備審査請求 有 (全 48 頁) 最終頁に続く

|               |                              |          |                                                                                                                |

|---------------|------------------------------|----------|----------------------------------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2012-539919 (P2012-539919) | (71) 出願人 | 595020643<br>クアアルコム・インコーポレイテッド<br>QUALCOMM INCORPORATED<br>アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775 |

| (86) (22) 出願日 | 平成22年10月26日 (2010.10.26)     | (74) 代理人 | 100108855<br>弁理士 蔵田 昌俊                                                                                         |

| (85) 翻訳文提出日   | 平成24年7月18日 (2012.7.18)       | (74) 代理人 | 100159651<br>弁理士 高倉 成男                                                                                         |

| (86) 國際出願番号   | PCT/US2010/054147            | (74) 代理人 | 100088683<br>弁理士 中村 誠                                                                                          |

| (87) 國際公開番号   | W02011/062734                | (74) 代理人 | 100109830<br>弁理士 福原 淑弘                                                                                         |

| (87) 國際公開日    | 平成23年5月26日 (2011.5.26)       |          |                                                                                                                |

| (31) 優先権主張番号  | 12/621,156                   |          |                                                                                                                |

| (32) 優先日      | 平成21年11月18日 (2009.11.18)     |          |                                                                                                                |

| (33) 優先権主張国   | 米国(US)                       |          |                                                                                                                |

最終頁に続く

(54) 【発明の名称】デシメートされた係数 (decimated coefficients) のフィルタリングを実行する他の回路またはアクティヴ雑音相殺回路における遅延技術

## (57) 【要約】

【解決手段】本開示はデジタル・ドメインのアクティヴ雑音相殺について用いられ得る回路構成が記載されている。特に、本開示は、信号処理についての遅延を用いる他の回路、またはデジタル適応雑音相殺回路の一つまたはそれ以上の望ましい遅延を達成するために、メモリ・ベース遅延回路というよりむしろダウン・サンプル・ユニット及びアップ・サンプル・ユニットの使用を提案する。ダウン・サンプル・ユニット及びアップ・サンプル・ユニットによって達成される遅延は、種々のアクティヴ雑音相殺回路構成について必要な遅延を自由に生成するよう調整され得る。多くの適応アクティヴ雑音相殺回路構成が議論され、技術は、低レーテンシー平衡回路のような他のタイプの回路について有効であり得る。

【選択図】図5

FIG. 5

## 【特許請求の範囲】

## 【請求項 1】

装置は、

ダウン・サンプル・ユニットと、

アップ・サンプル・ユニットと、

を備え、

前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットは、前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットを介して、サンプルを処理することに関連する合成遅延 (combined delay) が、前記装置について選択される予め定義された (pre-defined) 遅延と一致するようにそれぞれ調整される

10

装置。

## 【請求項 2】

前記合成遅延は、前記装置の調整可能パラメータ (tunable parameter) である

請求項 1 の装置。

## 【請求項 3】

アクティヴ雑音相殺 (active noise cancellation) を実行するように構成されたアク

ティヴ雑音相殺回路

を更に備え、

前記予め定義された遅延は、前記アクティヴ雑音相殺を促進するように選択される

請求項 1 の装置。

20

## 【請求項 4】

前記アップ・サンプル・ユニットは、前記サンプルについて、前記予め定義された遅延

を提供するために、前記ダウン・サンプル・ユニットのすぐ後に続く

請求項 1 の装置。

## 【請求項 5】

前記ダウン・サンプル・ユニットは、カスケード積分櫛形 (C I C : cascaded integration combiner) デシメータを備え、前記アップ・サンプル・ユニットは、C I C 補間器

(interpolator) を備える

請求項 1 の装置。

## 【請求項 6】

前記合成遅延は、前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットのサンプリング・レシオに基づいて、調整可能である

請求項 5 の装置。

30

## 【請求項 7】

前記合成遅延は、また、ステージ数 (N) についての固定数、及び前記ダウン・サンプ

ル・ユニット及び前記アップ・サンプル・ユニットについての差動遅延 (differential d

elay) (M) に基づく

請求項 6 の装置。

## 【請求項 8】

前記ダウン・サンプル・ユニットの出力をフィルタリングし、前記アップ・サンプル・

ユニットへ入力を提供するフィルタのセットを定義する遅延素子、加算器及び増幅器のセ

ットを更に含み、

前記予め定義された遅延に一致する前記合成遅延は、前記フィルタのセットに関連する

遅延と一致する

請求項 3 の装置。

## 【請求項 9】

前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットは、それぞれ、

前記合成遅延の半分 (one-half) を生成するように調整される

請求項 1 の装置。

40

## 【請求項 10】

50

前記装置は、前記予め定義された遅延を生成するために、前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットを含むアクティヴ雑音相殺回路 (active noise cancellation circuit) を備え、

前記予め定義された遅延は、前記アクティヴ雑音相殺を促進するように選択され、

前記装置は、オーディオ情報を捉えるマイクロフォンと、前記捉えられたオーディオ情報をサンプルに変換するデジタル・アナログ変換器 (digital-to-analog converter) と、前記アクティヴ雑音相殺回路によって生成される反雑音を出力するスピーカと、を更に備える

請求項 1 の装置。

【請求項 1 1】

アクティヴ雑音相殺 (active noise cancellation) を実行する方法であって、前記方法は、

ダウン・サンプル・ユニット及びアップ・サンプル・ユニットを介してサンプルを処理することを備え、

前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットを介してサンプルを処理することに関する合成された遅延は、アクティヴ雑音相殺を促進するように選択される予め定義された (pre-defined) 遅延と一致する

アクティヴ雑音相殺を実行する方法。

【請求項 1 2】

前記合成遅延は、前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットを含む回路の調整可能パラメータ (tunable parameter) である

請求項 1 1 の方法。

【請求項 1 3】

前記回路は、アクティヴ雑音回路を含む

請求項 1 2 の方法。

【請求項 1 4】

前記アップ・サンプル・ユニットは、前記サンプルについて、前記サンプルについて前記予め定義された遅延を提供するために、前記ダウン・サンプル・ユニットのすぐ後に続く

請求項 1 1 の方法。

【請求項 1 5】

前記ダウン・サンプル・ユニットは、カスケード積分櫛形 (C I C : cascaded integration combiner) デシメータを備え、前記アップ・サンプル・ユニットは、C I C 補間器 (interpolator) を備える

請求項 1 1 の方法。

【請求項 1 6】

前記合成遅延は、前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットのサンプリング・レシオに基づいて、調整可能であり

前記方法は、前記サンプリング・レシオに基づいて、前記合成遅延を調整することを更に備える

請求項 1 5 の方法。

【請求項 1 7】

前記合成遅延は、また、ステージ数 N についての固定値、及び前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットについての差動遅延 (differential delay) M に基づく

請求項 1 6 の方法。

【請求項 1 8】

前記ダウン・サンプル・ユニットの出力をフィルタリングし、前記アップ・サンプル・ユニットへ入力を提供するフィルタのセットを定義する遅延素子、加算器及び増幅器のセットを介して、前記サンプルを処理することを更に備え、

10

20

30

40

50

前記予め定義された遅延に一致する前記合成遅延は、前記フィルタのセットに関連する遅延と一致する

請求項 1 1 の方法。

【請求項 1 9】

前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットは、それぞれ、前記合成遅延の半分 (one-half) を生成するように調整される

請求項 1 1 の方法。

【請求項 2 0】

前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットは、反雑音を生成するアクティヴ雑音相殺回路の一部を形成し、

10

前記方法は更に、

オーディオ情報を捉えることと、

前記捉えられたオーディオ情報をサンプルに変換することと、

前記反雑音を生成するために、前記アクティヴ雑音相殺回路を介して前記サンプルを処理することと、

前記アクティヴ雑音相殺回路によって生成された前記反雑音を出力することと、

を備える

請求項 1 1 の方法。

【請求項 2 1】

ダウン・サンプリング手段と、

アップ・サンプリング手段と、

を備え、前記ダウン・サンプリング手段、及び前記アップ・サンプリング手段は、ダウン・サンプリング及びアップ・サンプリングに関する合成された遅延が、予め定義された遅延と一致するように、それぞれ調整される

装置。

20

【請求項 2 2】

前記合成遅延は、前記装置の調整可能パラメータ (tunable parameter) である

請求項 2 1 の装置。

【請求項 2 3】

アクティヴ雑音相殺 (active noise cancellation) を実行するように構成されたアクティヴ雑音相殺回路

を備え、

30

前記予め定義された遅延は、前記アクティヴ雑音相殺を促進するように予め選択される

請求項 2 1 の装置。

【請求項 2 4】

前記アップ・サンプリング手段は、前記サンプルについて、前記予め定義された遅延を

提供するために、前記ダウン・サンプリング手段のすぐ後に続く

請求項 2 1 の装置。

【請求項 2 5】

前記ダウン・サンプリング手段は、カスケード積分樹形 (C I C : cascaded integration combiner) デシメータを備え、前記アップ・サンプリング手段は、C I C 補間器 (interpolator) を備える

40

請求項 2 1 の装置。

【請求項 2 6】

前記合成遅延は、前記ダウン・サンプリング手段及び前記アップ・サンプリング手段の

サンプリング・レシオに基づいて、調整可能である

請求項 2 5 の装置。

【請求項 2 7】

前記合成遅延は、また、ステージ数 (N) についての固定数、及び前記ダウン・サンプリング手段及び前記アップ・サンプリング手段についての差動遅延 (differential delay

50

) (M) に基づく

請求項 2 6 の装置。

【請求項 2 8】

前記ダウン・サンプリング手段の出力をフィルタリングし、前記アップ・サンプリング手段へ入力を提供するフィルタのセットを定義する遅延素子、加算器及び増幅器のセットを更に含み、

前記予め定義された遅延に一致する前記合成遅延は、前記フィルタのセットに関連する遅延と一致する

請求項 2 3 の装置。

【請求項 2 9】

前記ダウン・サンプリング手段及び前記アップ・サンプリング手段は、それぞれ、前記合成遅延の半分 (one-half) を生成するように調整される

請求項 2 1 の装置。

【請求項 3 0】

前記装置は、前記予め定義された遅延を生成するために、前記ダウン・サンプリング手段及び前記アップ・サンプリング手段を含むアクティヴ雑音相殺回路 (active noise cancellation circuits) を備え、

前記予め定義された遅延は、前記アクティヴ雑音相殺を促進するように選択され、

前記装置は、オーディオ情報を捉えるマイクロフォンと、前記捉えられたオーディオ情報をサンプルに変換するデジタル・アナログ変換器 (digital-to-analog converter) と、前記アクティヴ雑音相殺回路によって生成される反雑音を出力するスピーカと、を更に備える

請求項 2 1 の装置。

【請求項 3 1】

プロセッサ内での実行で前記プロセッサに、アクティヴ雑音相殺 (active noise cancellation) を実行させる、命令を含むコンピュータ読み出し可能な記憶媒体であって、

前記命令は、前記プロセッサに、

前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットを介してサンプルを処理させ、

前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットを介してサンプルを処理することに関する合成された遅延は、アクティヴ雑音相殺を促進するように選択される予め定義された (pre-defined) 遅延と一致する

コンピュータ読み出し可能な記憶媒体。

【請求項 3 2】

前記合成遅延は、前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットを含む前記装置の調整可能パラメータ (tunable parameter) であり、

前記命令は、前記プロセッサに、前記調整可能パラメータを選択させる

請求項 3 1 のコンピュータ読み出し可能な記憶媒体。

【請求項 3 3】

前記回路はアクティヴ雑音相殺回路を備え、

前記プロセッサは、前記回路についての前記予め定義された遅延を選択する

請求項 3 1 のコンピュータ読み出し可能な記憶媒体。

【請求項 3 4】

前記アップ・サンプル・ユニットは、前記サンプルについて、前記予め定義された遅延を生成するために、前記ダウン・サンプル・ユニットのすぐ後に続く

請求項 3 1 のコンピュータ読み出し可能な記憶媒体。

【請求項 3 5】

前記ダウン・サンプル・ユニットは、カスケード積分櫛形 (C I C : cascaded integration combiner) デシメータを備え、前記アップ・サンプル・ユニットは、C I C 補間器 (interpolator) を備える

10

20

30

40

50

請求項 3 1 のコンピュータ読み出し可能な記憶媒体。

【請求項 3 6】

前記合成遅延は、前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットのサンプリング・レシオに基づいて、調整可能であり、

前記命令は、前記プロセッサに、前記サンプリング・レシオに基づいて、前記合成遅延を調整させる

請求項 3 5 のコンピュータ読み出し可能な記憶媒体。

【請求項 3 7】

前記合成遅延は、また、ステージ数  $N$  についての固定数、及び前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットについての差動遅延 (differential delay)  $M$  に基づき、

前記命令は、前記プロセッサに、 $N$  及び  $M$  に基づいて前記合成遅延を調整させる

請求項 3 6 のコンピュータ読み出し可能な記憶媒体。

【請求項 3 8】

前記命令は、前記装置に、前記ダウン・サンプル・ユニットの出力をフィルタリングし、前記アップ・サンプル・ユニットへ入力を提供するフィルタのセットを定義する遅延素子、加算器及び増幅器のセットを介して、前記サンプルを処理させ、

前記予め定義された遅延に一致する前記合成遅延は、前記フィルタのセットに関連する遅延と一致する

請求項 3 1 のコンピュータ読み出し可能な記憶媒体。

【請求項 3 9】

前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットは、それぞれ、前記合成遅延の半分 (one-half) を生成するように調整される

請求項 3 1 のコンピュータ読み出し可能な記憶媒体。

【請求項 4 0】

前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットは、反雑音を生成するアクティヴ雑音相殺回路の一部を形成し、

前記命令は、前記プロセッサに、

オーディオ情報を捉えさせ、

前記捉えられたオーディオ情報をサンプルに変換させ、

前記反雑音を生成するために、前記アクティヴ雑音相殺回路を介して前記サンプルを処理させ、

前記アクティヴ雑音相殺回路によって生成された前記反雑音を出力させる

請求項 3 1 のコンピュータ読み出し可能な記憶媒体。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本開示は、概して信号処理技術、特に P D M ドメイン信号処理 (P D M domain signal processing) に関する。より具体的には、本開示は、オーディオ・アプリケーションについてのデジタル・ドメインのアクティヴ雑音相殺 (active noise cancellation) に限定されない。

【背景技術】

【0 0 0 2】

アクティヴ雑音相殺回路 (active noise cancellation circuits) は、ヘッドフォンのようなオーディオ出力デバイス、デジタル・メディア・プレイヤ、ワイヤレス通信デバイス、個人通信システムのような種々のアプリケーションで用いられ得る。アクティヴ雑音相殺システムは、いわゆる “反雑音 (anti-noise) ” を生成することによって、周囲のアコースティック雑音 (acoustic noise) を活発的に減少する。アクティヴ雑音相殺システムは、環境雑音信号 (environmental noise signals) を捉える一つまたはそれ以上のマイクロフォン、反雑音を生成する回路、及び環境雑音を相殺するために反雑音を再生する

10

20

30

40

50

一つまたはそれ以上のスピーカを一般的に含む。反雑音は、周囲の環境雑音を破壊的に妨害し、それによって、ユーザーの耳に届く雑音信号を減少させる。

#### 【0003】

従来のアクティヴ雑音相殺回路は、アナログ信号処理を介してしばしば改善される。これは、アナログ回路が、デジタル回路に関連するとしても短い処理遅延を有しているからである。しかしながら、アナログ信号処理は、構造化可能な、または適応可能なアナログ信号処理を実行することが困難であるという欠点がある。

#### 【0004】

アクティヴ雑音相殺は、信号フィルタリングを介してデジタル・ドメインで実行される。信号フィルタリングは、種々のレベルのフィルタリングを導入するステージで生じ得る。デジタル・アクティヴ雑音相殺回路の従来のフィルタリングは、フィルタ・ステージ間でメモリ・ベースの (memory based) 遅延回路を要求し得る。これらのメモリ・ベースの (memory based) 遅延回路は、特に信号がオーバーサンプルされる (oversampled) 場合、回路のメモリ空間がとても大きくなることがある。

10

#### 【発明の概要】

#### 【0005】

本開示は、デジタル・ドメインのアクティヴ雑音相殺について用いられ得る回路構成を記載している。本開示は、デジタル適応雑音相殺回路 (digital adaptive noise cancellation circuits) の一つまたはそれ以上の望ましい遅延を達成するために、メモリ・ベース遅延回路というよりは、むしろダウン・サンプル・ユニット及びアップ・サンプル・ユニットの使用を記載している。ダウン・サンプル・ユニット及びアップ・サンプル・ユニットによって達成される遅延は、異なる適応アクティヴ雑音相殺回路構成について必要な遅延を生成することにおいて、自由度を許可するように調整され得る。多くの異なる適応アクティヴ雑音相殺回路構成は、二つまたはそれ以上の種々のサンプル・レート・ドメイン内のサンプルをフィルタリングするハイブリッド回路を含んで議論される。遅延技術は、他の回路 (すなわち、アクティヴ雑音相殺を行わない) で用いられる。例えば、メモリ・ベース遅延回路というよりは、むしろダウン・サンプル・ユニット及びアップ・サンプル・ユニットを用いる遅延技術は、また、低レーテンシー平衡回路 (low-latency equalization circuits) または他の回路で用いられ得る。

20

#### 【0006】

一例において、本開示は、ダウン・サンプル・ユニット及びアップ・サンプル・ユニットを含んでいる装置を記載している。このダウン・サンプル・ユニット及びアップ・サンプル・ユニットは、ダウン・サンプル・ユニット及びアップ・サンプル・ユニットを介してサンプルを処理することに関連する合成遅延が、予め決められた遅延と一致するようにそれぞれ調整される。いくつかのケースにおいて、予め決められた遅延は、アクティヴ雑音相殺を促進するように選択されうる。

30

#### 【0007】

他の例において、本開示は、ダウン・サンプル・ユニット及びアップ・サンプル・ユニットを介してサンプルを処理することを含む方法を示している。予め決められた遅延は、アクティヴ雑音相殺を促進するように選択されるように、ダウン・サンプル・ユニット及びアップ・サンプル・ユニットを介してサンプルを処理することに関連する合成遅延が、予め決められた遅延と一致する。

40

#### 【0008】

他の例において、本開示は、ダウン・サンプリング手段及びアップ・サンプリング手段を含む装置を記載している。ダウン・サンプリング手段及びアップ・サンプリング手段はそれぞれ、ダウン・サンプリング及びアップ・サンプリングを介してサンプルを処理することに関連する合成遅延が、予め決められた遅延と一致するようにそれぞれ調整される。いくつかのケースにおいて、予め決められた遅延は、アクティヴ雑音相殺を促進するように選択されうる。

#### 【0009】

50

本開示の技際の技術の態様は、ハードウェア、ソフトウェア、ファームウェア、またはそれらの組み合わせで実施され得る。ソフトウェアで実施される場合、ソフトウェアは、マイクロプロセッサ、特定用途向け集積回路（A S I C）、フィールド・プログラマブル・ゲート・アレイ（F P G A）、デジタル信号プロセッサ（D S P）のような一つまたはそれ以上のプロセッサで実行され得る。技術を実行するソフトウェアは、コンピュータ読み取り可能な媒体に最初に記憶され、プロセッサで読み出され、実行される。

【0 0 1 0】

従って、本開示は、本開示はまた、プロセッサに、プロセッサでアクティヴ雑音相殺を実行させる命令を含むコンピュータ読み取り可能な記憶媒体を検討している。命令は、プロセッサに、ダウン・サンプル・ユニット及びアップ・サンプル・ユニットを介してサンプルを処理させ、ダウン・サンプル・ユニット及びアップ・サンプル・ユニットを介してサンプルを処理することに関連する合成遅延が、アクティヴ雑音相殺を促進するように選択する予め決められた遅延と一致する。合成遅延は、ダウン・サンプル・ユニット及びアップ・サンプル・ユニットを含む回路の調整可能パラメータを含み得る。命令は、プロセッサに、調整可能パラメータを選択させる。

10

【0 0 1 1】

本開示の一つ又はそれ以上の態様の詳細は、図面及び下記の詳細と結びつけられて示される。本開示に記載の技術の利点、目的、他の特徴は、明細書、図面、特許請求の範囲から明白である。

20

【図面の簡単な説明】

【0 0 1 2】

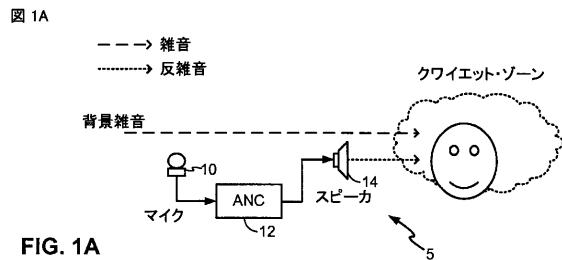

【図1 A】図1 Aは、アクティヴ雑音相殺システムのアプリケーションを示す概念的な図である。

【図1 B】図1 Bは、図1 Aのアクティヴ雑音相殺回路の例を示すブロック図である。

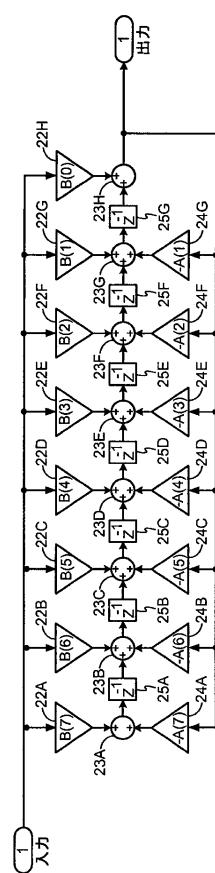

【図2】図2は、メモリ・ベース遅延要素を用いるアクティヴ雑音相殺回路の回路図である。

【図3】図3は、メモリ・ベース遅延要素を用いるアクティヴ雑音相殺回路の他の回路図である。

【図4】図4は、図3のメモリ・ベース遅延回路の一つを示すブロック図である。

30

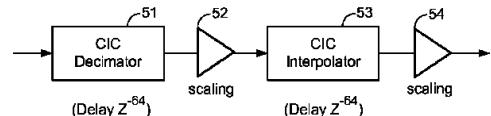

【図5】図5は、本開示と整合性が取れたメモリ・ベース遅延回路に代わるもの示したブロック図である。

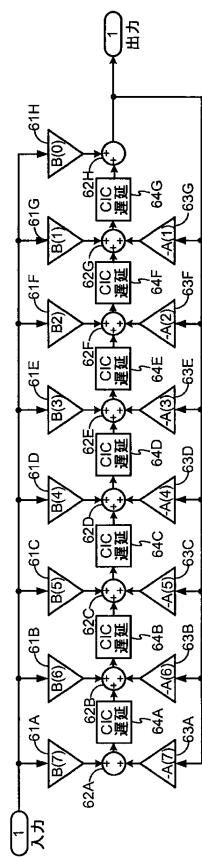

【図6】図6は、従来のメモリ・ベース遅延素子に代わるために、ダウン・サンプル（down sample）及びアップ・サンプル（up sample）ユニットを用いるアクティヴ雑音相殺回路の回路図である。

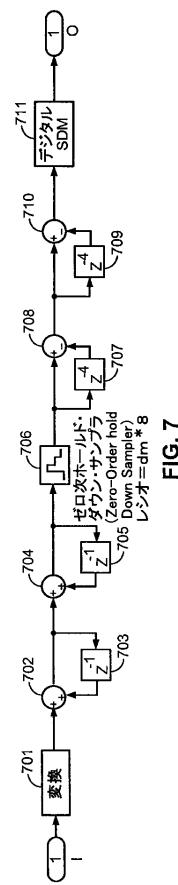

【図7】図7は、例示的なカスケード積分櫛形（C I C : cascaded integration combiner）デシメータのブロック図である。

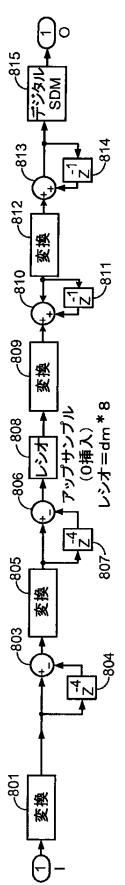

【図8】図8は、例示的なC I C補間器のブロック図である。

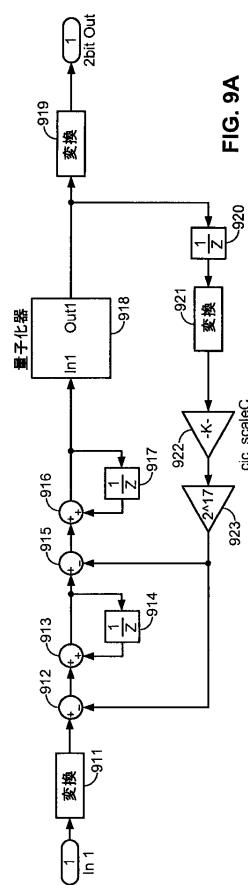

【図9 A】図9 Aは、例示的な2次シグマーデルタ・モジュレータ（second order sigma-delta modulator）のブロック図である。

40

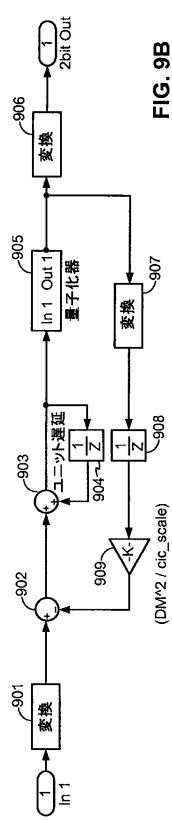

【図9 B】図9 Bは、例示的な1次シグマーデルタ・モジュレータ（first order sigma-delta modulator）のブロック図である。

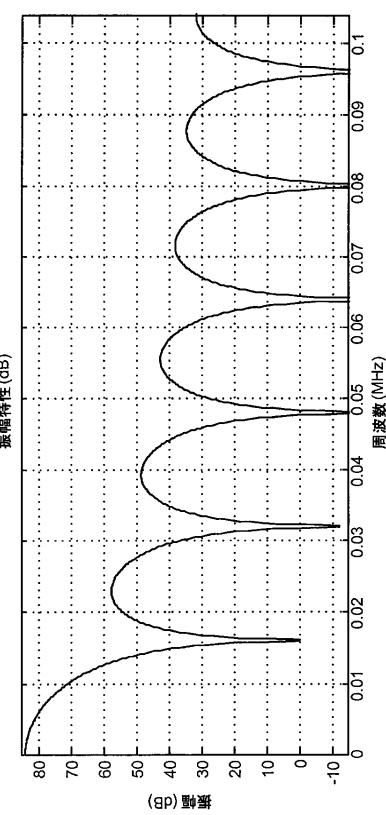

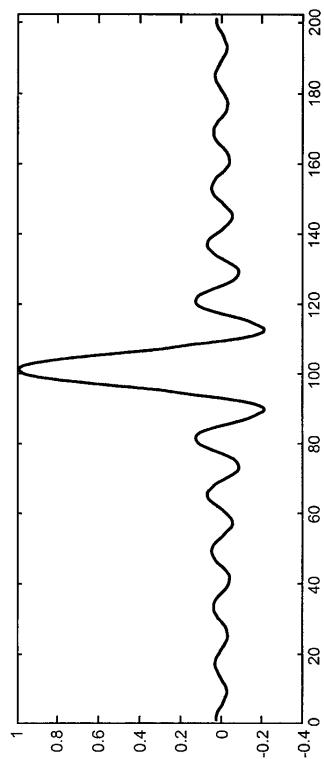

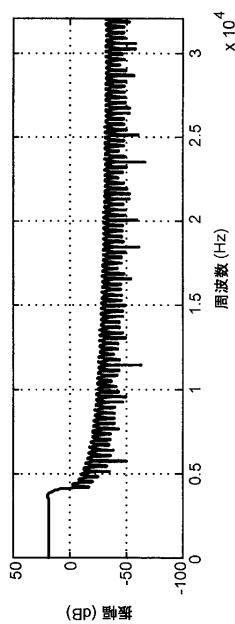

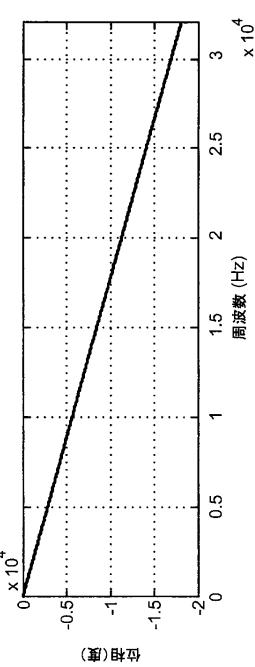

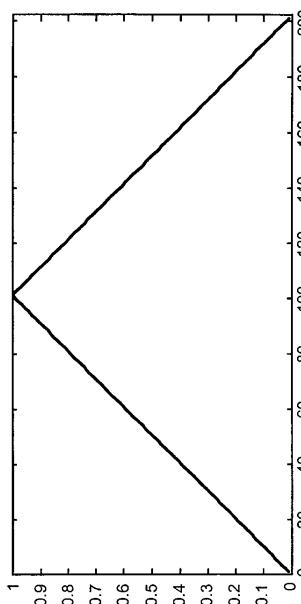

【図1 0】図1 0は、C I Cデシメータ及びC I C補間器を含むC I Cフィルタの振幅特性を示すグラフである。

【図1 1】図1 1は、従来のメモリ・ベース遅延素子を用いるアクティヴ雑音相殺回路の回路図である。

【図1 2】図1 2は、従来のメモリ・ベース遅延素子に代わるために、ダウン・サンプル（down sample）及びアップ・サンプル（up sample）ユニットを用いるアクティヴ雑音相殺回路の回路図である。

【図1 3】図1 3は、二つの異なるサンプル・レート・ドメインのフィルタリングを実行し、少なくともある程度必要な遅延を達成するためにダウン・サンプル（down sample）

50

及びアップ・サンプル (up sample) ユニットを用いるハイブリッド・アクティヴ雑音相殺回路の回路図である。

【図 14】図 14 は、二つの異なるサンプル・レート・ドメインのフィルタリングを実行し、少なくともある程度必要な遅延を達成するためにダウン・サンプル (down sample) 及びアップ・サンプル (up sample) ユニットを用いるハイブリッド・アクティヴ雑音相殺回路の他の回路図である。

【図 15】図 15 は、二つの異なるサンプル・レート・ドメインのフィルタリングを実行し、少なくともある程度必要な遅延を達成するためにダウン・サンプル (down sample) 及びアップ・サンプル (up sample) ユニットを用いるハイブリッド・アクティヴ雑音相殺回路の他の回路図である。

【図 16】図 16 は、本開示と整合性が取れた C I C デシメータに代わるものと示したブロック図である。

【図 17】図 17 は、本開示と整合性が取れた図 16 に示される回路の F I R フィルタの証明動作 (demonstrating operation) のグラフである。

【図 18 A】図 18 A は、本開示と整合性が取れた図 16 に示される回路の F I R フィルタの証明動作 (demonstrating operation) のグラフである。

【図 18 B】図 18 B は、本開示と整合性が取れた図 16 に示される回路の F I R フィルタの証明動作 (demonstrating operation) のグラフである。

【図 19】図 19 は、本開示と整合性が取れた図 16 に示される回路の他の例示的な F I R フィルタの証明動作 (demonstrating operation) のグラフである。

【図 20 A】図 20 A は、本開示と整合性が取れた図 16 に示される回路の他の例示的な F I R フィルタの証明動作 (demonstrating operation) のグラフである。

【図 20 B】図 20 B は、本開示と整合性が取れた図 16 に示される回路の他の例示的な F I R フィルタの証明動作 (demonstrating operation) のグラフである。

【図 21】図 21 は、本開示と整合性が取れた C I C デシメータに代わるものであり得る F I R フィルタ及びダウン・サンプラーのカスケード (cascade) を示すブロック図である。

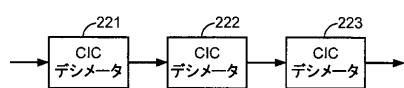

【図 22】図 22 は、本開示と整合性が取れ、本開示の例である直列の三つのカスケードされた C I C デシメータを示している。

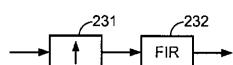

【図 23】図 23 は、本開示と整合性が取れた C I C 補間器に代わるものと示したブロック図である。

【図 24】図 24 は、本開示と整合性が取れた図 23 に示される回路の F I R フィルタの証明動作 (demonstrating operation) のグラフである。

【図 25】図 25 は、本開示と整合性が取れた図 23 に示される回路の F I R フィルタの証明動作 (demonstrating operation) のグラフである。

【図 26】図 26 は、本開示と整合性が取れた C I C 補間器に代わるものであり得るアップ・サンプラー及び F I R フィルタのカスケードを示したブロック図である。

【図 27】図 27 は、本開示と整合性が取れ、本開示の例である直列の三つのカスケードされた C I C 補間器を示している。

【発明を実施するための形態】

【0013】

本開示は、デジタル・ドメインのアクティヴ雑音相殺のために用いられ得る回路構成を記載している。記載されている回路は、ヘッドフォンのようなオーディオ出力デバイス、ワイヤレス通信デバイス、デジタル・メディア・プレイヤ、個人通信システムのような幅広いアクティヴ雑音相殺設定またはアプリケーションで用いられる。アクティヴ雑音相殺は、周囲の環境の雑音の反対の形態であるオーディオ信号を含む“反雑音”と呼ばれるものを生成することによって、環境のアコースティック雑音を積極的に減少させる。アクティヴ雑音相殺システムは、外部雑音信号を拾う為の一つまたはそれ以上のマイクロフォン、反雑音を生成するためのアクティヴ雑音相殺回路、及び環境雑音を相殺する反雑音を再生する一つまたはそれ以上のスピーカ、を一般的に含む。アクティヴ雑音相殺回路

によって生成された反雑音は、破壊的に周囲の環境雑音を妨害し、それゆえに、ユーザーの耳に届く雑音信号を減少する。

【0014】

たとえ、本開示の遅延技術が、アクティヴ雑音相殺の文脈で主に記載されていても、遅延技術は、他の回路（すなわち、アクティヴ雑音相殺を実行しない回路）で用いられ得る。例えば、メモリ・ベース遅延回路というよりむしろダウン・サンプル・ユニット（down sample unit）及びアップ・サンプル・ユニット（up sample unit）を用いる遅延技術は、低レーテンシー平衡回路（low-latency equalization circuits）または他の回路で用いられ得る。

【0015】

デジタル・ドメインの従来のアクティヴ雑音相殺は、アクティヴ雑音相殺回路の一つまたはそれ以上のステージ間のメモリ・ベース遅延回路を用い得る。本開示は、デジタル適応雑音相殺回路の一つまたはそれ以上の望ましい遅延を得るために、メモリ・ベース遅延回路というより、むしろ、ダウン・サンプル・ユニット（down sample unit）及びアップ・サンプル・ユニット（up sample unit）の使用を記載している。ダウン・サンプル・ユニット（down sample unit）及びアップ・サンプル・ユニット（up sample unit）によって達成された遅延は、種々のアクティヴ雑音相殺回路構成について、必要な遅延の生成の柔軟性を許可するために、調整され得る。多くの種々の適応雑音相殺回路構成（adaptive noise cancellation circuit configurations）は、二つまたはそれ以上の異なるサンプル・レート・ドメイン内でフィルタ・サンプリングするハイブリッド回路を含んでいると議論される。ダウン・サンプル・ユニット（down sample unit）及びアップ・サンプル・ユニット（up sample unit）がそれら自身でメモリ遅延素子を含む限り、ダウン・サンプル・ユニット（down sample unit）及びアップ・サンプル・ユニット（up sample unit）のメモリ遅延素子は、従来のメモリ・ベース遅延回路について要求されるメモリよりも遙かに少ない。

10

20

30

40

50

【0016】

図1Aは、アクティヴ雑音相殺システム5のアプリケーションを示す概念的な図である。アクティヴ雑音相殺システム5は、背景雑音（background noise）を捉える一つまたはそれ以上のマイクロフォン10、反雑音を生成するアクティヴ雑音相殺（ANC）回路12、及び反雑音を出力するスピーカ・デバイス14を含み得る。スピーカ14は、実質的に、破壊的な方法の背景雑音を妨害する反雑音の範囲で背景雑音の逆である。周囲の環境の背景雑音と、スピーカ・デバイス14によって出力される反雑音の組み合わせは、図1Aのユーザー、すなわち人間のリスナーの周囲の“クワイエット・ゾーン”と概念的に記載されているようなクワイエット・ゾーンを明確にし得る。

【0017】

図1Bは、より詳細な例示的なANC回路12の例を示すブロック図である。図1Bに示すように、ANC回路12は、デジタル・ドメインで動作し、アナログ・デジタル変換器（ADC：analog-to-digital converter）16、デジタルANC回路17、及びデジタル・アナログ変換器（DAC：digital-to-analog converter）18を含む。本開示の技術は、ANC回路12のデジタルANC回路17に適用可能である。マイクロフォンがパルス・コード・モジュレーション（PCM：pulse code modulation）サンプルを出力するデジタル・マイクロフォンとして言及され得るケースにおいて、ADC16は、マイクロフォン10の部分を代替的に形成することができる。また、デジタル・ドメイン内にANC12の出力が存在するケースにおいて、DAC18は、スピーカ・デバイス14の部分を形成することができる。

【0018】

図1Bに示すような例において、ADC16の出力は、PCMサンプルを含み得る。オーディオ・コーディングの文脈において、PCMサンプルは、一連の振幅として時間ドメインのオーディオ波形を現すデジタル・サンプルを含み得る。アクティヴ雑音相殺について有用な反雑音を生成するために、デジタルANC17は、背景雑音のデジタル・サンプ

ルをフィルタリングする。特に、デジタルA N C 1 7は、反雑音を生成するために、受信した背景雑音を、フィルタリングする。

【0019】

通常のP C Mサンプルについてのデジタルフィルタは、連続的なフィルタ・ステージ (successive filter stages) (フィルタ・タップ・ステージとも呼ばれる) 間の1サンプル遅延 (one-sample delay) を典型的に必要とする。各フィルタ・ステージは、フィルタリングの増加量 (an incremental amount of filtering) を実行し、フィードバック信号へのそのようなフィルタリングを合成 (combine) し得る。フィルタ・ステージ間のーサンプル遅延 (one-sample delays) を達成するために、メモリ遅延回路が用いられ得る。図2は、連続的なフィルタ・ステージ間のメモリ遅延回路を用いる例示的なA N C回路を示している。P C Mサンプルの場合は、入力サンプルは、増幅器2 2 A ~ 2 2 Hによって受信される。回路の出力サンプルは、増幅器2 4 A ~ 2 4 Gにフィードバックされ得る。増幅器2 2 A ~ 2 2 H及び増幅器2 4 A ~ 2 4 Gは、サンプルに対するフィルタ・タップのアプリケーション (application) を規定し得る。例えば、増幅器2 2 A ~ 2 2 H及び増幅器2 4 A ~ 2 4 Gは、利得ファクタ (gain factor) によって入力信号を乗算するデジタル乗算回路を含み得る。アクティヴ雑音相殺に必要な望ましい信号増幅を達成するために、利得ファクタ (gain factor) は、選択され得る。

10

【0020】

アドレス2 3 A ~ 2 3 Hは、増幅器2 2 A ~ 2 2 Hの出力を、増幅器2 4 A ~ 2 2 Gの出力と、メモリ・ベース遅延回路2 5 A ~ 2 5 Gとを図示するようにそれぞれ合成する。メモリ・ベース遅延回路2 5 A ~ 2 5 Gは、サンプルが処理されるように、回路の各連続するステージ間のーサンプル遅延 (one-sample delays) を提供する。従って、回路の種々のステージは、メモリ・ベース遅延回路2 5 A ~ 2 5 Gによって分割される。入力サンプルは、各フィルタ・ステージによってフィルタリングされる。しかしながら、与えられたサンプルは、メモリ・ベース遅延回路2 5 A ~ 2 5 Gに渡って進むので、出力において望ましい反雑音効果を提供するために、フィルタリングが累積される (accumulates)。

20

【0021】

ここに記すように、そのようなメモリ・ベース遅延回路2 5 A ~ 2 5 Gは、実施の観点から望まれない。任意のケースにおいて、P C Mサンプルは、更に、P C Mサンプルよりもより小さいビット幅を典型的に有するパルス・デンシティ・モジュレーション (P D M : pulse density modulation) にアップ・サンプルされ得る。典型的なアプリケーションにおいて、アナログ・デジタル変換器からのP D Mサンプルは、1 ~ 4ビットのビット幅を有し得る。信号のP D Mサンプル表示は、典型的に、信号バンド幅より高いサンプリング・レートを用い、典型的なオーバーサンプリング・レシオ (例えば、オーバー・サンプリング・レート及びベース・バンド信号のサンプリング・レート間のレシオ) は、およそ6 4及び2 5 6の間に分布し得る。いくつかのケースにおいて、アナログ・デジタル変換の後のP D Mサンプルは、信号処理についての、P C Mサンプル・ビットよりも大きなビット幅を有することがある。

30

【0022】

図2のアプローチは、フィルタ・タップの数がとても大きくなつた場合、望ましくなくなることがある。それ故に、そのようなフィルタ・タップ間にK個の遅延を挿入するので、N個のフィルタ・タップが望まれている図3に示されるように、デシメートされたフィルタ構造を用いることが良い場合がある。図3のデシメートされたフィルタ構造は、ベースバンド周波数に至るまで、同等のフィルタリング動作 (equivalent filtering operation) を達成し、ベースバンド周波数の後、より高い周波数において、応答パターン (response pattern) を繰り替えすことを有し得る。

40

【0023】

図2のような図3の回路は、入力サンプルを受信する増幅器3 2 A ~ 3 2 Hの第1のセット、及びフィードバックのような回路の出力を受信する増幅器3 4 A ~ 3 4 Gの第2のセットを含む。アドレス3 3 A ~ 3 3 Hは、図3に示すようにフィルタリングされたサン

50

プルを合成し、メモリ・ベース遅延回路 35A～35G は、PDMドメインのアクティヴ雑音相殺を達成するために、フィルタ・ステージ間で必要とされている遅延を提供する。ここに記載されている回路は、例示的な数のステージ及び増幅器を有し、異なるフィルタ・ステージ及び増幅器の数は、本開示に整合性が取れる他の構成で用いられ得る。

#### 【0024】

オーバーサンプリング・レシオは、PDM信号サンプリング・レート及びベース・バンド信号サンプリング・レート間のレシオとして言及され得る。例えば 8 kHz ベース・バンド信号の典型的な PDM 表示 (representation) は、オーバーサンプリング・レシオが 256 である 2048 kHz サンプリング・レートを用いる。そのようなケースにおいて、インタレストの信号 (signal of interest) は、ただ 4 kHz まで及ぶ (spans) ので、タップ間の 1 サンプル遅延を含むデジタルフィルタは、1024 kHz バンド幅全域に渡って効果を有することがある。フィルタ・タップ間のマルチ・サンプル遅延を用いるデシメートされたフィルタ構造を用いることが望ましいことが有る。タップ間の 256 遅延を用いることで、フィルタは、フル信号バンド幅 (4 kHz) まで完全な制御を未だに有し、フィルタは、乗算器の数及び 1～256 の因子によるアドレスを減少する。メモリ・ベース遅延回路 35A～35G による、信号について必要な遅延は、オーバーサンプリング・レシオ及びベース・バンド・サンプリング周波数の関数であり得る。従って、オーディオ・サンプリング周波数及びオーバーサンプリング周波数が高い場合、要求されたメモリ・サイズは、とても大きくなることがある。加えて、そのようなメモリ・ベース遅延回路 35A～35G を用いるフィルタリング回路は、入力データ及び増幅器 32A～32H 及び 34A～34G に関連するフィルタリング係数の限定されたワード長 (limited word length) に起因する持続的な問題を有し得る。限定されたワード長は、実際には十分に大きくない係数のバンド幅を意味する。係数またはデータのバンド幅 (すなわちビット深度) は、チップ内の回路を製造するために必要なシリコン領域を比例的に増加する。従って、実際のアプリケーションでとても大きなビット幅を用いることは望ましくないことがある。しかしながら、ビット幅が十分に大きくない場合、係数またはデータは、データに多くの量子化エラー (quantization error) または量子化雑音 (quantization noise) を加えることがある、比較的低い分解能を有することがある。

#### 【0025】

図 2 及び図 3 の両方における回路は、PCMドメイン及びPDMドメインで動作することができる。図 2 の回路は、入力信号の全バンド幅に渡って、フィルタリング効果を有し得る。図 3 の回路は、入力信号バンド幅の  $1 / 128^{t/h}$  のフィルタリング効果を有し得る。図 3 のケースにおいて、同じフィルタリング効果は、残りのバンド幅に渡って、127 回繰り返されることがある。図 3 の回路は、入力信号バンド幅がサンプリング周波数の小さい分数 (1/128) である場合、有用であり得る。例えば、サンプリング周波数によるバンド幅が 512 kHz であり、信号バンド幅が 4 kHz しかない場合、128 個のサンプルの遅延は、図 3 に示されるフィルタ・タップ間に挿入されることがある。これぞいて、一つは、フィルタ回路に 128 倍以上の乗算器、及び加算器を必要とし得る。

#### 【0026】

本開示は、ダウン・サンプル・ユニット及びアップ・サンプル・ユニットのペアの調整可能なグループ遅延特性を利用することによって、代替的な遅延構造を提供する。一例として、本開示は、ダウン・サンプル・ユニット及びアップ・サンプル・ユニットのペアを含む図 4 の回路 41 のような一つまたはそれ以上のメモリ・ベース遅延回路の代わりを用意する。ダウン・サンプル・ユニット及びアップ・サンプル・ユニットのペアは、ユニット・ペアに関連する固有の遅延を有し得る。しかし、ダウン・サンプル・ユニット及びアップ・サンプル・ユニットのペアで用いられるメモリは、もしメモリ・ベース遅延回路が用いられる必要があれば、メモリの断片を含み得る。ダウン・サンプル・ユニット及びアップ・サンプル・ユニットのペアによって提供される遅延の量は、下記で詳細に説明するように、ユニットのパラメータを選択することによって調整され得る。

#### 【0027】

10

20

30

40

50

本開示が、ほかのタイプのダウン・サンプル・ユニット及びアップ・サンプル・ユニットのペアを予期していても、ダウン・サンプル・ユニット及びアップ・サンプル・ユニットのペアは、カスケード積分櫛形 (C I C:cascaded integration combiner) デシメータ、及び C I C 補間器を含み得る。図 5 に示すように、例えば、C I C 補間器 5 3 に続く C I C デシメータ 5 1 は、図 4 のメモリ・ベース遅延回路 4 1 への均等な遅延量を提供するように調整され得る。この遅延量は、反雑音生成を促進するために、明確に選択され得る。図 5 の例において、C I C デシメータ 5 1 および C I C 補間器 5 3 のそれぞれは、異なる遅延量を提供するように調整されることができるとはいえ、C I C デシメータ 5 1 および C I C 補間器 5 3 のそれぞれは、望ましい遅延の半分 (one-half) を提供する。重要なことに、図 5 の回路に関連する遅延量は、図 4 のメモリ・ベース遅延回路 4 1 の遅延に実質的に等しいスケーリング増幅器 5 2 及び 5 4 はまた、トランケーション関連オーディオ・ディフェクト (truncation-related audio defects) を避けるために、含まれ得る。図 5 に示される回路素子は、図 4 のメモリ・ベース遅延回路 4 1 に関連するアクティヴ雑音相殺回路の信号遅延を達成するために、より効果的な方法を明確にする。

10

## 【0028】

図 5 に表される C I C デシメータ / 補間器ペアは、可変遅延を含むロー・パス・フィルタとして示される。C I C デシメータ 5 1 は、ロー・パス・フィルタ及びダウン・サンプルのパラメータによって決定される遅延を含むダウン・サンプル及びロー・パス・フィルタを含み得る。C I C 補間器 5 3 は、ロー・パス・フィルタ及びアップ・サンプルのパラメータによって決定される遅延を含むアップ・サンプル及びロー・パス・フィルタを含み得る。C I C パラメータを選択することによって、一つは、C I C デシメータ 5 1 に望ましい遅延の半分、そして C I C 補間器 5 3 によってもう一方の望ましい遅延の半分を達成することができる。C I C デシメータ 5 1 及び C I C 補間器 5 3 についての同じダウン・サンプリング及びアップ・サンプリング・レシオを選択することによって、回路は、ロー・パス・フィルタリング及び望ましい遅延効果を達成するので、同じ入力及び出力サンプリング周波数を規定し得る。

20

## 【0029】

C I C 回路のビット進展特性 (bit growth characteristics) に起因して、ユニット利得を達成するために、適切なスケーリングが必要とされる。スケーリング増幅器 5 2 及び 5 4 は、この目的で用いられ得る。C I C 回路のロー・パス周波数応答は、高周波数量子化雑音を抑制することによって、安定アクティヴ雑音相殺を手助けし得る。C I C 回路を用いることの欠点 (draw back) は、C I C デシメータ 5 1 及び / または C I C 補間器 5 3 の小さいエイリアシング効果、あるいはインバンド信号ドロップ (in-band signal drop) を含み得る。しかし、エイリアシング効果、及びインバンド信号ドロップを最小化する C I C パラメータを選択することによって、エイリアシング効果、及びインバンド信号ドロップは、ごくわずかになる。種々の C I C パラメータは、下記に議論される。

30

## 【0030】

図 6 は、本開示と整合性のとれた回路図である。このケースにおいて、C I C 遅延回路 6 4 A ~ 6 4 G は、望ましい遅延を提供するために、従来のメモリ回路ととて変わる。遅延回路 6 4 A ~ 6 4 G のそれぞれは、ダウン・サンプル・ユニット及びアップ・サンプル・ユニットを含み、ダウン・サンプル・ユニット及びアップ・サンプル・ユニットのペアは、ダウン・サンプル・ユニット及びアップ・サンプル・ユニットを介して、サンプルを処理することを関連付けられ、合成遅延は、アクティヴ雑音相殺を促進するために、選択された予め定義された遅延 (pre-defined delay) に対応するように、それぞれ調整され得る。C I C 遅延回路 6 4 A ~ 6 4 G は、少ないハードウェアと、メモリ・ベース遅延回路に関連する改善された安定性を含み得る。図 6 の回路において、本明細書に記載されるほかの回路と同様に、入力サンプルは、背景雑音に関連するオーディオ・サンプルを表し、出力サンプルは、実質的に背景雑音を破壊的に妨害する反雑音を表すオーディオ・サンプルを含み得る。

40

## 【0031】

50

図6の回路は、入力サンプルを受信する増幅器61A～61Hの第1のセットと、フィードバックとして回路の出力を受信する増幅器63A～63Gの第2のセットを含む。アドレス62A～62Hは、図3に示すようにフィルタリングされたサンプルを合成し、CIC遅延回路64A～64Gは、アクティヴ雑音相殺を達成するために、フィルタ・ステージ間で必要とされる遅延を提供する。

#### 【0032】

再び、本開示は、ダウン・サンプリング・ファクタRに比例する遅延を生成する可変遅延としてCICデシメータ／補間器ペアの使用を提案する。このケースにおいて、一は、弟子メーション・ファクタ(K)進展(growth)に関連するダウン・サンプリング・ファクタRを増加させることによって、遅延を増加することができる。総合的に、デジタル特定用途向け集積回路(ASIC)において改善された場合、CICベース遅延は、従来のメモリ・ベース遅延回路と比較して、ハードウェア領域を減少し得る。また、CICデシメータ／補間器ペアは、無限インパルス応答(IIR)フィルタリングの安定性を高めることができるロー・パス・フィルタリングのサイド効果(side effect)を達成し得る。

10

#### 【0033】

ダウン・サンプル・ユニット及びアップ・サンプル・ユニット・ペア(例えばCICデシメータ／補間器ペア)は、直列に配置される。図6の回路において、CIC遅延回路64A～64Gのそれぞれは、直列に配列されたCICデシメータ／補間器ペアを含み得る。下記により詳細に記載されたほかのケースにおいて、ダウン・サンプル・ユニット及びアップ・サンプル・ユニット・ペアは、直列に配列され、またダウン・サンプル・ユニット及びアップ・サンプル・ユニット間のほかの要素も含み得る。

20

#### 【0034】

図5に示すように、CICフィルタは、CICデシメータ51(ダウン・サンプラの一例)及びCIC補間器(アップ・サンプラの一例)を含み得る。カスケード積分器(cascaded integrators)及び結合器(combiners)は、CICデシメータ51及びCIC補間器53を形成するように用いられ得る。

20

#### 【0035】

図7は、図5のCICデシメータ51のようなCICデシメータの一例を示している。図7のCICデシメータは、入ってくるサンプルを21ビットのような特定のビット深度に変換する変換ユニット701を含み得る。加算器702及び遅延素子703は、第1の積分器を形成し、加算器704及び遅延素子705は、第2の積分器を形成する。したがって、素子702、703、704、及び705は、2ステージ積分器を形成する。ゼロ次ホールド素子(zero order hold elements)706は、例えば32、64、128、または256のファクタで、データ・レートを抑制するダウン・サンプラを含む。ダウン・サンプラ・レシオは、 $R = d_m \times 8$ に相当し得る。このケースにおいて、512KHzは、すべてのサンプリング周波数の最大公約数(GCF:greatest common denominator)であるので、 $d_m$ は、512KHzへのオーバー・サンプリング周波数(OSF)のレシオである。可変の“ $d_m$ ”は、典型的に自然数である。Rはオーバー・サンプリング周波数(64KHzのような)を表す。上述で $d_m$ を定義したように、一は、ダウン・サンプルされたドメインは、入力オーバー・サンプリング周波数から独立した64KHzへマッピングされるということを確実にする。ゼロ次ホールド素子706のデータ・レート出力は、たとえ他のデータ・レートが用いられることができても、64キロヘルツであり得る。遅延素子(705及び707のような)比較的小さく、メモリ・ベース遅延回路は、多くの複雑さ無しで用いられることができる。図7において(図9においてもまた)、可変 $d_m$ は、上で言及したような $d_m$ と同じ、すなわち、オーバー・サンプリング周波数であり得る。

30

#### 【0036】

遅延素子707及び加算器708は、第1の結合器を形成し、遅延素子709及び加算器710は、第2の結合器を形成する。したがって、素子707、708、709、及び710は、2ステージ結合器を形成する。素子711は、シグマ・デルタ・モジュレータ

40

50

を含む。シグマ・デルタ・モジュレータのさらなる詳細は、図9に関連して下で議論する。図7において、素子701、702、703、704、及び705は、アップ・サンプリングされた周波数で動作し、素子707、708、709、及び710は、ダウン・サンプリングされた周波数で動作する。アップ・サンプリングされた周波数は、ファクタによってダウン・サンプリングされた周波数よりも大きい。例えば、アップ・サンプリングされた周波数は、8、16、32、64、128、256のファクタ、またはnが正の整数である他の $2^n$ の倍数によってダウン・サンプリングされた周波数よりも大きい。

#### 【0037】

図8は、図5のCIC補間器53のようなCIC補間器の一例を示している。図8に示すCIC補間器は、24ビット～23ビットのような特定のビット深度に入ってきたサンプルを変換する変換ユニット801を含み得る。このビット深度拡張は、可変することができ、CIC補間器デザインの公正なスタンダード部分(fairly standard part)であり得る。遅延素子804及び加算器803は、第1の結合器を形成する。変換ユニット805は、加算器806についての入力データのビット幅を変換する。図8に示されるCIC補間器は、内面的に、データ・ストリーム・ステージのビット幅を拡張し、この方法は、CIC補間器が用いられる場合に、データ・ラインのビット幅を拡張するように実行される。遅延素子807及び加算器806は、第2の結合器を形成する。素子803、804、805、806及び807は、2ステージ結合器を形成する。

#### 【0038】

素子808は、32のファクタのようなファクタでデータ・レートをアップ・サンプリングするアップ・サンプラを含む。変換ユニット809は、加算器810についての入力データ・バンド幅を変換する。加算器810及び遅延素子811は、第1の積分器を形成し、加算器813及び遅延素子814は、第2の積分器を形成する。変換ユニット812は、加算器813についての第1の積分器の出力を調整するために、第1及び第2の積分器の間に配置される。したがって、素子810、811、812、813及び814は、2ステージ積分器を形成する。素子815は、シグマ・デルタ・モジュレータを含む。シグマ・デルタ・モジュレータのさらなる詳細は、図9に関連して下で議論する。図8において、素子801、802、803、804、805及び806は、ダウン・サンプリングされた周波数で動作し、素子809、810、811、812、813、814及び815は、ダウン・サンプリングされた周波数で動作する。アップ・サンプリングされた周波数は、ファクタによってダウン・サンプリングされた周波数よりも大きい。例えば、アップ・サンプリングされた周波数は、8、16、32、64、128、256のファクタ、またはnが正の整数である他の $2^n$ の倍数によってダウン・サンプリングされた周波数よりも大きい。

#### 【0039】

より一般的には、CIC積分器53は、高オーバー・サンプリング周波数(OSF)レートで動作する、Nは整数であるN個のデジタル積分器ステージを含み得る。各ステージは、ユニット・フィードバック係数(unit feedback coefficient)を含む1ポール・フィルタ(one-pole filter)として実施され得る。図8に示される回路の結合部(803～806の部分)は、Rは整数レート変化ファクタ(integer rate change factor)であり、低サンプリング・レートOSF/R(64KHz)で動作する。結合部は、入力及び遅延入力間(例えば素子803～806)の差を計算するCIC補間器またはデシメータのステージである。この結合部は、ステージにつきM個のサンプルの差動遅延を含むN個の結合ステージ(comb stage)を含み得る。アクティヴ雑音相殺実施において、差動遅延は、M=4であり、ステージの数は、N=2にセットされ得る。

#### 【0040】

OSFサンプリング・レートと言及される本明細書に記載のCIC遅延回路(例えば、CICデシメータ及びCIC補間器ペア)と同等の伝達関数は、以下のように与えられる。

10

20

30

40

## 【数1】

$$H(Z) = H_l(Z)H_c(Z) = \frac{(1 - Z^{-RM})^N}{(1 - Z^{-1})^N} = \left( \sum_{k=0}^{RM-1} Z^{-k} \right)^N$$

## 【0041】

10

$H(z)$  は、 CIC 遅延回路の伝達関数であり、

$H_l(z)$  は、 CIC 遅延回路の補間器部の伝達関数であり、

$H_c(z)$  は、 CIC 遅延回路の結合部の伝達関数であり、

$z$  は、  $z$  トランスマニア変数 ( $z$ -transform variable) であり、

$R$  は、 CIC 遅延回路のダウン・サンプリング及びアップ・サンプリング・レシオであり、

$M$  は、 CIC 遅延回路の結合部の差動遅延数 (differential delay number) であり、

$N$  は、 CIC 遅延回路の整数遅延回路ステージ / 微分ステージの数である。

20

CIC 回路の周波数応答は、一定のグループ遅延を見せる  $N$  個のステージ有限インパルス応答 (FIR) フィルタのカスケードに機能的に均等である。

## 【0042】

20

CIC 回路のパラメータは、遅延を制御するために調整され得る。 FIR フィルタ・アップ遅延は、 CIC フィルタ・デシメータ及び補間器の合計から生じる。 CIC デシメータ及び補間器からの遅延は、それぞれ以下のように表され得る。

$$\text{遅延} = M R N / 2, R = 8 \times d m, d m = F s \times O S F / (8 \times 64000)$$

$N$  は、積分器ステージの数であり、  $R$  はダウン・サンプリング・レートであり、  $M$  は、差動遅延であり、  $F s$  は、ベースバンド・サンプリング周波数である。

したがって、 CIC ペアの遅延は、以下のように与えられ得る。

$$\text{CIC ペアの遅延} = M R N$$

30

したがって、 CIC 回路の遅延は、三つのパラメータ、積分器ステージ  $N$ 、ダウン・サンプリング・レシオ  $R$ 、差動遅延  $M$ 、を制御することによって、調整され得る。差動遅延  $M$  は、 CIC 回路のスペクトルのヌル・ロケーション (spectral null location) を制御し得る。スペクトルのヌル・ロケーションは、零に近づくフィルタ利得 (filter gain approaches zero) である周波数である。

## 【0043】

30

従って、 CIC デシメータ / 補間器ペアの合計遅延は、  $M$ 、  $R$  及び  $N$  の関数である。ハードウェア・デザインについて、  $R$  を可変しているので、  $M$  及び  $N$  について固定された数を用いるということは簡単である。このケースにおいて、 CIC デシメータ及び補間器の両方についてダウン / アップ・サンプリング・レシオ  $R$  を制御することによって、 CIC ペアの遅延は、望ましい遅延適正に調整することができる。特に弟子メートされた FIR / IIR フィルタとともに用いられる場合、 CIC ペアは、複数のサンプリング・レートをサポートするために、有用であり得る。オーバー・サンプリング・レートが変化する場合、遅延は、 CIC 回路遅延は、一定のベース・バンド・フィルタ構造の遅延と同等であるように、増加する、または減少され得る。

40

## 【0044】

CIC 回路は、ビット幅が増えるように、ビット幅スケーリングを提供するために、ユニットを必要とし得る。多くの CIC フィルタは、DC 利得を示す。したがって、スケーリング・ファクタは、 CIC 回路のすべてのユニット利得を達成するために、デシメータ及び補間器の出力で適用され得る。

このケースにおいて、デシメータについて、

50

$$G = (RM)^2 = (8 \times dm \times M)^2 = dm^2 \times 2^{10}, B_{max} = B_{in} + N(10 \log_2 RM) - 1$$

従って、このようなケースにおいて、デシメータのビット幅は、

$$3 + (2(10 \log_2 192 \times 4) - 1) = 21$$

このケースにおいて、補間器について、

【数2】

$$G_j = \begin{cases} 2^j, j = 1, 2, \dots, N \\ \frac{2^{2N-j}(RM)^{j-N}}{R}, j = N+1, \dots, 2N \end{cases}$$

10

【0045】

最後のステージにおいて、利得は以下のように得る。

【0046】

$$G = RM^2 = (8 \times dm) \times M^2 = dm \times 2^7$$

例えばCICデシメータの出力のような、アクティヴ雑音相殺デシメータ出力ビットは、雑音レベルのすべてを維持するので、ハードウェア領域をセーブするように切り捨てられることができる。CICデシメータ出力は、下記によってスケール・ダウンされ得る。

20

$$(dm)^2 / CIC_{scale}$$

同様に、CIC補間器出力は、以下によってスケール・ダウンされる。

$$dm \times CIC_{scale} \times 2^{17} / CIC_{scale}$$

。

【数3】

$$CIC_{scale} = \begin{cases} 1, dm = 1 の場合 \\ 3, dm = 3 の場合 \\ 4, 他の場合 \end{cases}$$

30

【0047】

このスケーリングは、図5に示す増幅器52及び54をスケーリングすることによって、実行され、図7及び図8の素子711及び815によってそれぞれ示されるCICデシメータ及びCIC補間器のデジタル・シグマ・デルタ・モジュレータとして実施され得る。

【0048】

図9A及び9Bは、CIC補間及びCICデシメーションの状況でオーディオ・ディフェクトに関する切り捨てを避けるために、スケーリングするために用いられ得る1次及び2次シグマ・デルタ・モジュレータのブロック・ダイアグラムである。図9A及び9Bのブロック・ダイアグラムは、図5のスケーリング増幅器52及び54に対応し、または、図7及び図8の素子711及び815にそれぞれ示されるようなCICデシメータ及びCIC補間器部を形成し得る。

40

【0049】

図9Bは、1次シグマ・デルタ・モジュレータを示している。図9Bに示すように、1次シグマ・デルタ・モジュレータは、入力サンプルを、加算器902についてのより広いビット深度に変換する変換ユニット901を含み得る。加算器902は、フィードバック・ループのフィードバック・サンプルから入力サンプルを減算することによって、サンプ

50

ルを合成する。加算器 903 及び遅延素子 904 は、積分器を定義し、ユニット 905 は、サンプルをスケーリングするために、ラウンディング (rounding) 動作及びライト・シフト (right shift) を実行する。変換ユニット 906 は、ビット深度を、望ましい出力ビット深度に変換し、変換ユニット 907、遅延素子 908、及び増幅器 909 は、加算器 902 へのフィードバック・パスを定義する。

【0050】

図 9A は、2 次シグマ・デルタ・モジュレータを示している。図 9A に示すように、2 次シグマ・デルタ・モジュレータは、二つの信号積分器を用いるという点を除いて、1 次シグマ・デルタ・モジュレータに似ている。特に、図 9B の 1 次シグマ・デルタ・モジュレータは、図 9A に示すような素子 903 及び 904 を含み得るので、図 9A の 2 次シグマ・デルタ・モジュレータは、素子 913 及び 914 と、素子 916 及び 917 とにそれ 10 ぞれ対応する二つの積分器を有している。

【0051】

一般的に、図 9A に示される 2 次シグマ・デルタ・モジュレータは、変換ユニット 911、加算器 912、913、915、及び 916、遅延素子 914、917、量子化器 918 及びビット深度を望ましい出力ビット深度に変換する変換ユニット 919 を含んでいる。フィードバック・パスにおいて、図 9A の 2 次シグマ・デルタ・モジュレータは、遅延素子 920、変換ユニット 921、増幅器 922、及び 923 を含んでいる。簡単に言うと、2 次シグマ・デルタ・モジュレータは、素子 913 及び 914 と、素子 916 及び 917 とにそれぞれ対応する二つの信号積分器を用いるという点を除いて、1 次シグマ・デルタ・モジュレータに似ている。また、2 次シグマ・デルタ・モジュレータは、フィードバック・パスにおいて、二つの異なる増幅器を含んでいる。

【0052】

変数  $dm$  は、上で言及された 512 kHz へのOSF のレシオである。 $dm^2 / CIC\_scale$  の値は、図 9B の下の増幅器 909 及び下のユニット 905 に表される。ユニット 905 は、 $K = dm^2 / CIC\_scale$  である利得  $1 / K$  を、入力信号へ適用する。CIC\_scale の値は、下の表 1 のシード・コード (pseudo code) に示されるルールによって決定される。スケーリングは、任意のあらかじめ決められた限界内の信号動的範囲 (signal dynamic range) をキープするように実行される。ユニット 905 の出力は、フィードバック・ループで用いられ、変換ユニット 907 は、加算器 902 についてのデータ・ビット幅を変換し、遅延素子 908 は、1 サンプル遅延を提供し、増幅器 909 は、利得  $K$  に従ったサンプルへ利得を適応する。

【表 1】

TABLE1

```

if(dm >= 2)

if(dm == 3)

cic_scale = 3;

else

cic_scale = 2^2;

end

else

cic_scale = 1;

end

```

【0053】

したがって、本開示は、フィルタリングする CIC 回路、及びオーディオ・バス内のス

10

20

30

40

50

ケーリングについての 1 次シグマ・デルタ・モジュレータを定義する。 C I C 回路は、 C I C デシメータ及び C I C 補間器の両方についてヌル周辺のエイリアシング・エラー (aliasing errors) を引き起こすことができる。 C I C フィルタのダウン・サンプリングされた周波数 (F\_s / R) に比例する電力応答は、以下のように与えられる。

【数 4】

$$P(f) = \left[ \frac{\sin \pi Mf}{\sin \left( \frac{\pi f}{R} \right)} \right]^{2N} \approx [RM \frac{\sin \pi Mf}{\pi Mf}]^{2N} \text{ for } 0 \leq f < \frac{1}{M}$$

10

【0054】

このケースにおいて、  $F_s$  は、 C I C 補間器の出力サンプリング周波数と同様である C I C デシメータの入力サンプリング周波数であり、

Rは、 C I C 補間器のアップ・サンプリング・レシオと同様である C I C デシメータのダウン・サンプリング・レシオであり、

$P(f)$  は、電力スペクトル (power spectrum) (周波数  $f$  の関数であり得る)

Mは、 C I C 結合部の差動遅延数 (differential delay number) であり、

$f$  は、ダウン・サンプリングされたクロック・ドメインの周波数であり、

Nは、 C I C フィルタのステージの数である。

20

【0055】

スペクトラムにおけるヌルは、差動遅延Mによって制御され得る。 C I C デシメータについて、あらゆるヌルの周辺の領域は、パス・バンドに折り重ねられることが可能である、すなわち、パス・バンドの後の周波数を含む信号は、パス・バンドの中の信号に戻って加算ができる。 C I C 補間器について、イメージングは、あらゆるヌルの周辺で生じ得る。ステージ数Nを増加させることによって、回路は、合計のフィルタ遅延と、パス・バンド・ドローピング (drooping) の増加という犠牲を払ってエイリアシング・エラー (aliasing errors) を抑制し得る。変形された C I C フィルタ構造は、さらにエイリアシング・インデュースド・エラー (aliasing induced errors) を抑制するための回路応答を形成するために、用いられ得る。

30

【0056】

図 10 は、本明細書に含むように、 C I C デシメータ及び C I C 補間器を含む C I C 回路の例示的な振幅特性 (magnitude response) を示している。このケースにおいて、 C I C 回路のパラメータは、 2048 KHz から 64 KHz にダウン・サンプリングする、  $N = 2$  、  $M = 4$  、  $R = 32$  であり得る。N、M及びRパラメータは、任意の与えられた実施についてのフィルタ遅延、周波数応答、及びエイリアシング要求を保つために正確に選択され得る。 C I C 回路の周波数要求は、 1 KHz 以下の信号をよく通し、高周波数のダウン信号を抑制するということを示す。このプロパティは、ダウン・サンプリングを十分に達成するための鍵である。

30

【0057】

再び、1次シグマ・デルタ・モジュレータは、オーディオ・ディフェクトに関連する切り捨てを避けるために、スケーリングについて用いられ得る。シグマ・デルタ・モジュレータは、リミット・サイクルを生成することによって、またはdcまたは0入力を含む音の振る舞い (tonal behaviors) を示すことなどによって、オーディオ品質にわずかに作用し得る。正確な計測は、より高次のシグマ・デルタ・モジュレータを用いること、量子化器または入力への小さな擾動 (perturbations) またはディザーリング (dithering) を加えること、及び/またはローカル・カオティック振る舞い (local chaotic behavior) を示す積分器を用いることのような、シグマ・デルタ・モジュレータの安定性を改善するために用いられことができる。

40

【0058】

50

図 11～14 は、本開示の種々の例と整合性がとれたアクティヴ雑音相殺回路の回路図である。これらのケースにおいて、回路への入力サンプルは、背景雑音に関するオーディオ・サンプルを示し、回路の出力サンプルは、背景雑音を実質的に破壊的に妨害する反雑音を示すオーディオ・サンプルを含み得る。遅延素子のぞれぞれについて、入力 “i” 及び出力 “o” がラベルされている。

#### 【0059】

本開示にしたがって、オーディオ雑音相殺についての信号処理は、デジタル・ドメインで実行される。アナログ信号は、一つまたはそれ以上のアナログによるデジタル・フォーマット内のアナログから、デジタル変換器 (D A C) に転送され得る。このケースにおいて、信号の振幅は、サンプリング・レートとして言及され得るレギュラー・レートでサンプリングされる。信号振幅 (signal amplitude) は、量子化され、記憶され得る。オーディオ信号変換のこの形式は、パルス・コード・モジュレーション (P C M) として通常知られている。P C Mにおいて、信号は、12またはそれ以上のビットの典型的な分解能を含むレコードされたバイナリ・コード (binary code) である。他方で、シグマ・デルタ・モジュレータは、アナログ信号を、低分解能 (例えば 1～4 ビット)、しかし通常オーバー・サンプリングと呼ばれる高サンプリング・レートの不連続の時間信号に変換し得る。オーバー・サンプリング・レート (O S R) は、大抵、ファクタ (オーバー・サンプリング・ファクタまたは O S F と呼ばれる) によって乗算されたサンプリング・レートである。

10

#### 【0060】

オーバー・サンプリングされたフォーマットの信号は、パルス・デンシティ・モジュレーション (P D M) サンプルとして通常知られている。P C M ドメインの信号処理は、実施の単純な利点を有している。しかしながら、P C M データ生産のデジタル変換ステップへのアナログは、典型的に、少なくともいくつかのサンプルの遅延を処理することを有している。この遅延は、アクティヴ雑音相殺のようないくつかのタイム・クリティカル・アプリケーション (some time critical applications) について、長すぎることがある。他方で、P D M ドメインの信号を処理することは、その高サンプリング・レートに起因するとても低い処理レーテンシーの利点を提示する。

20

#### 【0061】

$x_t$  を P C M の信号にすると、係数 ( $B_0, B_1, \dots, B_n, A_0, A_1, \dots, A_n$ ) ( $A_0 = 1$ ) を含むフィルタは、出力  $y_t$  を与えるために、信号  $x_t$  に適用される。このケースでは、

$$y_t = B_0 x_t + B_1 x_{t-1} + B_2 x_{t-2} + \dots + B_n x_{t-n} - A_1 y_{t-1} - A_2 y_{t-2} - \dots - A_n y_{t-n}$$

30

$z$  変換 ( $z$ -transform) が適用された場合、上述したこの式は、以下のように  $z$  ドメイン ( $z$ -domain) で表されることができる。

#### 【数5】

$$Y(z) = \frac{B_0 + B_1 z^{-1} + B_2 z^{-2} + \dots + B_n z^{-n}}{1 + A_1 z^{-1} + A_2 z^{-2} + \dots + A_n z^{-n}} X(z)$$

40

#### 【0062】

$X(z)$  及び  $Y(z)$  は、それぞれ  $x_t$  及び  $y_t$  の  $z$  変換 ( $z$ -transform) である。

#### 【0063】

$u_t$  及び  $v_t$  を、オーバー・サンプリング・ファクタ R を含む P D M ドメインの入力及び出力信号にする。動作のみが、下の S R / 2 周波数の変形であり、フィルタリングは、同じフィルタ係数で実行されることができる。したがって、P D M サンプルについての  $Z$  ドメインの上の表現は下記のように表され得る。

50

【数6】

$$V(z) = \frac{B_0 + B_1 z^{-R} + B_2 z^{-2R} + \cdots + B_n z^{-nR}}{1 + A_1 z^{-R} + A_2 z^{-2R} + \cdots + A_n z^{-nR}} U(z)$$

【0064】

10

$U(z)$ 及び $V(z)$ は、それぞれ $u_t$ 及び $v_t$ の $z$ 変換であり、 $R$ は、オーバー・サンプリング・ファクタを表す。したがって、 $R$ は、どのくらいの時間、PCMドメインの信号と比較して、PDMドメインで信号がオーバー・サンプリングされているかを表す。ANCにおいて、 $x_t$ は、計測されたPCMドメイン雑音信号(ANC制御の入力)であり、 $y_t$ は、ANC制御回路は、によって計算された反雑音信号である。 $X(z)$ 及び $Y(z)$ は、 $z$ 変換ドメインの入力雑音及び反雑音信号に一致する。PDMドメインにおいて、 $z$ 変換入力及び出力信号は、 $U(z)$ 及び $V(z)$ によって表される。出力信号を生成するために、入力信号の変形は、 $B$ 's及び $A$ 'sを含む商(quotients)によって、表される。

【0065】

20

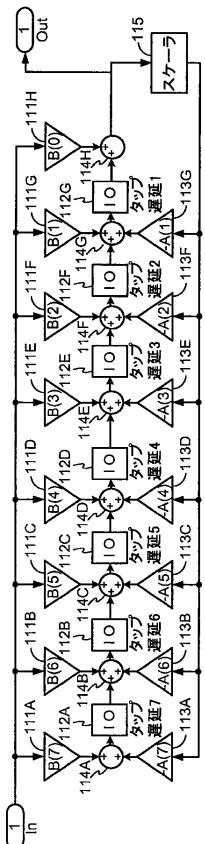

図11は、PDMサンプルのような、アップ・サンプリングされたサンプルと整合性がとれた従来のメモリ・ベース遅延素子を用いるアクティヴ雑音相殺回路の回路図である。このPDMサンプルのケースにおいて、入力サンプルは、増幅器111A～111Hによって受信される。回路の出力サンプルは、出力サンプルを正確なビット深度にスケーリングするスケーラ・ユニット115を通った後、増幅器113A～113Gにフィードバックされる。増幅器111～111H及び増幅器113A～113Hは、サンプルへのフィルタ・タップのアプリケーションを定義し得る。例えば、増幅器111A～111H及び増幅器113A～113Hは、利得ファクタによって、入力信号を乗算するデジタル乗算回路を含み得る。利得ファクタは、アクティヴ雑音相殺について必要とされる望ましい信号増幅を達成するために、選択され得る。

【0066】

30

加算器114A～114Hは、増幅器111A～111Hの出力を、図示するように増幅器113A～113H及びメモリ・ベース遅延回路112A～112Gの出力を合成する。メモリ・ベース遅延回路112A～112Gは、サンプルが処理されるように、回路の連続するステージのそれぞれの間に1サンプル遅延を提供する。したがって、回路の種々のステージは、メモリ・ベース遅延回路112A～112Gによって分割される。入力サンプルは、各フィルタ・ステージによってフィルタリングされる。しかし、与えられたサンプルが、メモリ・ベース遅延回路112A～112Gに渡ってステージを移動するので、フィルタリングは、出力で望ましい反雑音効果を提供するために、蓄積する。

【0067】

40

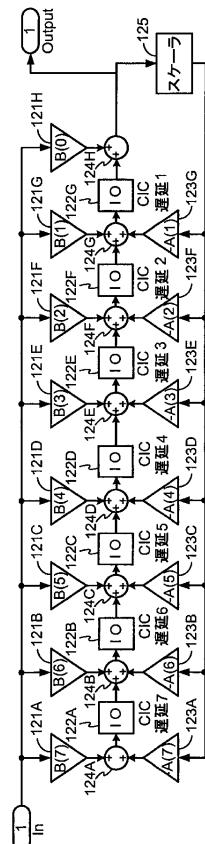

本明細書に記載するように、そのようなメモリ・ベース遅延回路112A～112Gは、実施の観点から望ましくないことがある。各フィルタ・タップから中間の出力を記憶するためのタップ遅延ライン(tap delay lines)を用いる代わりに、本開示の代替は、正確に望ましい遅延を有するCICデシメータ/補間器ペアを用いることである。図12は、図11と比較した本コンセプトを示している。

【0068】

50

特に、図12は、従来のメモリ・ベース遅延の代わりにCIC遅延回路122A～122Gを用いるアクティヴ雑音相殺回路の回路図である。PDMサンプルのこのケースにおいて、入力サンプルは、増幅器121A～121Hによって受信され得る。回路の出力サンプルは、出力サンプルを正確なビット深度にスケーリングするスケーラ・ユニット125を通った後に、増幅器123A～123Gにフィードバックされる。増幅器121A～121H及び増幅器123A～123Gは、サンプルでのフィルタ・タップのアプリケー

ションを明確にし得る。例えば、増幅器 121A～121H 及び増幅器 123A～123G は、利得ファクタによって、入力信号を乗算するデジタル乗算回路を含み得る。利得ファクタは、アクティヴ雑音相殺に必要な望ましい信号増幅を達成するために、選択され得る。

#### 【0069】

加算器 124A～124H は、図示するように、増幅器 121A～121H の出力と、増幅器 123A～123G 及び CIC 遅延回路 122A～122G の出力とを合成する。CIC 遅延回路 122A～122G は、サンプルが処理されるように、連続するステージの回路のそれぞれの間に提供される。従って、回路の異なるステージは、メモリ・ベース遅延回路というよりもむしろ CIC 遅延回路 122A～122G 遅延回路 122A～122G によって、分割され得る。入力サンプルは、各フィルタ・ステージによってフィルタリングされ、しかし、所定のサンプルは、CIC 遅延回路 122A～122G に渡って移動するので、フィルタリングは、出力で、望ましい反雑音効果を提供するために、累積する。

10

#### 【0070】

再び、PDM ドメインのフィルタリングが、とても低い処理レーテンシーの利点を提示するとはいえ、一つの欠点は、時間遅延ライン (time delay line) において、オーバー・サンプリングされたデータを記憶するために要求されるメモリ素子が大量であるということである。低いレーテンシー要求は、 $B_1$  係数にただ適用され、他に全ての係数は、いくつかのアルゴリズム遅延に関連づけられ、他の係数は、OSR よりも低いサンプリング・レートで信号を適用することができる。図 13～15 に図示するように、これは、PCM 及び PDM ドメインの両方のハイブリッド・フィルタリングのスキームによって達成されることができる。これらのスキームにおいて、入力及び出力信号は、PDM ドメイン内にある。係数  $B_0$  は、PDM 入力信号に適用される。CIC ダウン・サンプリング・フィルタは、サンプルの PCM ストリームを生成するために、入力及び出力信号の両方を適用し得る。係数  $B_1$ ～ $B_7$  は、係数  $A_1$ ～ $A_7$  が、PCM 出力信号に適用されるので、PCM 入力信号へ適用される。これらの係数からの最終的な出力は、アップ・サンプリング・フィルタを通って、アップ・サンプリングされ、 $B_0$  に関連する PDM ストリームへ加算される。典型的に、CIC 遅延回路 122A～122G 回路からの反エイリアシング要求 (anti-aliasing requirement) 及び係数  $B_0$  と  $B_1$  との間で許可される限定された遅延に基づいて、PCM は、ベース・サンプリング・レートよりも大きい中間サンプリング・レートであり得る。本明細書の他の例において、図 13～15 の例は、増幅器及びステージの不連続数を示し、しかし、増幅器及びステージの数は、本開示と整合性のとれた他の例について異なり得る。

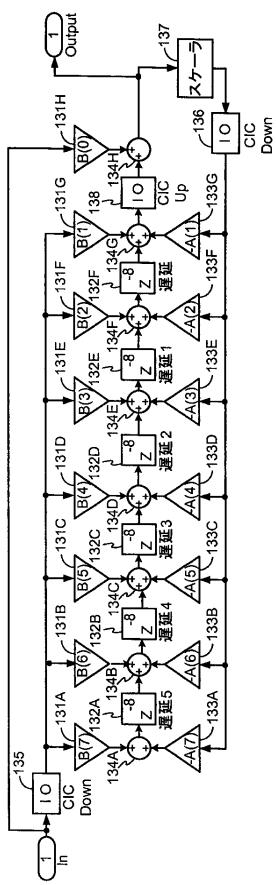

20

#### 【0071】

図 13 の例において、中間サンプリング・レートは、ベース・サンプリング・レートの 8 倍であり得る。本開示の遅延技術と整合性のとれた、図 13 のアクティヴ雑音相殺回路において、CIC ダウン・サンプリング及び CIC アップ・サンプリング・フィルタは、係数  $B_0$  及び  $B_1$  間の遅延を達成するために、方法を提供する。特に、CIC ダウン・サンプラ 135 及び CIC アップ・サンプラ 138 は、係数  $B_0$  及び  $B_1$  のアプリケーション間で必要とされている遅延を提供する CIC デシメータ / 補間器ペアを形成する。CIC ダウン・サンプラ 136 は、出力がフィードバック・ループにおいて、適切なドメインにダウン・サンプリングされるということを確かにし、スケーラ・ユニット 137 は、適切なビット深度を確実にするために、サンプルをスケーリングする。

30

#### 【0072】

図 13 は、PDM 及び PCM ドメインでサンプルをフィルタリングし、フィルタ・タップ間の遅延の目的でダウン・サンプラ及びアップ・サンプラ・ペアを用いるハイブリッド・アクティヴ雑音相殺回路の回路図である。PDM サンプルのケースにおいて、入力サンプルは、PDM ドメインの回路及び増幅器 131H フィルタによって受信される。CIC ダウン・サンプラ 135 は、PCM ドメインへの入力サンプルをダウン・サンプリングす

40

50

る。P S M ドメインにおけるサンプルは、増幅器 1 3 1 A ~ 1 3 1 G によってフィルタリングされる。回路の出力サンプルは、出力サンプルを、適切なビット深度にスケーリングするスケーラ・ユニット 1 3 7、及び P D M ドメインから P C M ドメインに変換する他の C I C ダウン・サンプラー 1 3 6 を通った後、増幅器 1 3 3 A ~ 1 3 3 G にフィードバックされる。増幅器 1 3 1 A ~ 1 3 1 H、及び増幅器 1 3 3 A ~ 1 3 3 H は、サンプルへのフィルタ・タップのアプリケーションを定義し得る。例えば、増幅器 1 3 1 A ~ 1 3 1 H、及び増幅器 1 3 3 A ~ 1 3 3 H は、利得ファクタによって、入力信号を乗算するデジタル乗算回路を含み得る。利得ファクタは、アクティヴ雑音相殺について、必要とされる望ましい信号増幅を達成するために、選択され得る。とりわけ、他の増幅器が P C M ドメインのサンプルで動作する間、増幅器 1 3 1 H は、P D M ドメインのサンプルで動作する。素子 1 3 5 及び 1 3 6 は、C I C デシメータを含み、素子 1 3 8 は、C I C 補間器を含み、これらの素子 1 3 5、1 3 6、及び 1 3 8 は、P D M ドメインのサンプルのフィルタ 1 3 1 H のアプリケーションと、P C M ドメインのサンプルのフィルタ増幅器 1 3 1 A ~ 1 3 1 G のアプリケーションと、の間の望ましい遅延を達成するように、調整され得る。

10

20

30

40

## 【0073】

加算器 1 3 4 A ~ 1 3 4 G は、図示するように、増幅器 1 3 1 A ~ 1 3 1 G の出力と、増幅器 1 3 3 A ~ 1 3 3 G 及びメモリ・ベース遅延回路 1 3 2 A ~ 1 3 2 G の出力を合成する。メモリ・ベース遅延回路 1 3 2 A ~ 1 3 2 G は、サンプルが処理されるように、回路の連続するステージ間毎に、8 個のサンプル遅延を提供する。一度、加算器 1 3 4 G の出力が、C I C アップ・サンプラー 1 3 8 を介して P D M ドメインへ、アップ・コンバートされて戻る場合、C I C アップ・サンプラー 1 3 8 の出力は、反雑音を含み得る回路出力を生成するために、増幅器 1 3 1 H の出力と合成される。

## 【0074】

ハイブリッド・フィルタリング（例えば、P C M 及び P D M ドメインのフィルタリング）の代替的なスキームは、図 14 に示されるように可能である。このスキームにおいて、P C M 出力フィードバックへ C I C アップ・サンプリングを適用する代わりに、B<sub>1</sub> は、P C M ストリームに適用され、係数 B<sub>2</sub> ~ B<sub>8</sub> 及び A<sub>2</sub> ~ A<sub>8</sub> へ出力が合成される。この信号は、フィードバック係数 A<sub>2</sub> ~ A<sub>8</sub> について要求される P C M 出力信号である。

## 【0075】

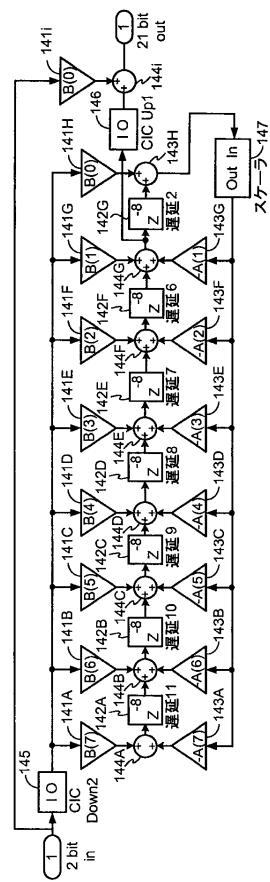

特に、図 14 は、P D M 及び P C M ドメインのサンプルをフィルタリングし、フィルタ・タップ間の遅延の目的で、ダウン・サンプラー及びアップ・サンプラー・ペアを用いるハイブリッド・アクティヴ雑音相殺回路の回路図である。P D M サンプルのケースにおいて、入力サンプルは、P D M 度名の増幅器 1 4 1 i フィルタ及び回路によって受信される。C I C ダウン・サンプラー 1 4 5 は、入力サンプルを P C M ドメインにダウン・サンプリングする。P C M ドメインのサンプルは、増幅器 1 4 1 A ~ 1 4 1 H によってフィルタリングされる。加算器 1 4 3 H の出力は、サンプルを適切なビット深度にスケーリングするスケーラ・ユニット 1 4 7 を通った後、増幅器 1 4 3 A ~ 1 4 3 G にフィードバックされる。

## 【0076】

増幅器 1 4 1 A ~ 1 4 1 i、及び増幅器 1 4 3 A ~ 1 4 3 G は、サンプルへのフィルタ・タップのアプリケーションを定義し得る。例えば、増幅器 1 4 1 A ~ 1 4 1 i、及び増幅器 1 4 3 A ~ 1 4 3 G は、利得ファクタによって、入力信号を乗算するデジタル乗算回路を含み得る。利得ファクタは、アクティヴ雑音相殺について、必要とされる望ましい信号増幅を達成するために、選択され得る。とりわけ、他の増幅器が P C M ドメインのサンプルで動作する間、増幅器 1 3 1 H は、P D M ドメインのサンプルで動作する。素子 1 4 5 は、C I C デシメータを含み、素子 1 4 6 は、C I C 補間器を含み、これらの素子 1 4 5、及び 1 4 6 は、P D M ドメインのサンプルのフィルタ 1 4 1 i のアプリケーションと、P C M ドメインのサンプルのフィルタ増幅器 1 4 1 A ~ 1 4 1 G のアプリケーションと、の間の望ましい遅延を達成するように、調整され得る。

## 【0077】

加算器 1 4 4 A ~ 1 4 4 G は、図示するように、増幅器 1 4 1 A ~ 1 4 1 G の出力と、

50

増幅器 1 4 3 A ~ 1 4 3 G 及びメモリ・ベース遅延回路 1 4 2 A ~ 1 4 2 G の出力とを合成する。同様に、加算器 1 4 3 H は、増幅器 1 4 1 H の出力と、遅延回路 1 4 2 G の出力とを合成する。メモリ・ベース遅延回路 1 4 2 A ~ 1 4 2 G は、サンプルが処理されるように、回路の連続するステージ間毎に、8 個のサンプル遅延を提供する。一度、加算器 1 4 4 G の出力が、C I C アップ・サンプラ 1 4 6 を介して P D M ドメインへ、アップ・コンバートされて戻る場合、C I C アップ・サンプラ 1 4 6 の出力は、反雑音を含み得る回路出力を生成するために、加算器 1 4 4 i を介して、増幅器 1 4 1 i の出力と合成される。

#### 【 0 0 7 8 】

図 15 は、更なる他の回路構成を示している。図 15 の回路構成と整合性をとって、出力  $y_t$  は、二つのフィルタの合計として表され得る。 10

$$y_t = B_0 x_t + s_t$$

$B_0$  は、図 15 の増幅器 1 5 1 H である。値  $x_t$  は、上述で説明したように入力信号である。値  $s_t$  は、ターゲット信号  $y_t$  及び  $B_0 x_t$  間の差である。従って、 $s_t = y_t - B_0 x_t$ 。または、 $z$  ドメインにおいて、

$$Y(z) = B_0 X(z) + S(z)$$

$Y(z)$ 、 $X(z)$  は、上で定義したように、同じ意味であり、出力信号  $y_t$  及び入力信号  $x_t$  の  $z$  変換を表す。 $S(z)$  は、信号  $s_t$  の  $z$  変換である。 20

#### 【 0 0 7 9 】

従って、

#### 【 数 7 】

$$Y(z) = B_0 X(z) + S(z)$$

$$S(z) = Y(z) - B_0 X(z)$$

$$= \frac{B_0 + B_1 z^{-1} + B_2 z^{-2} + \cdots + B_n z^{-n}}{1 + A_1 z^{-1} + A_2 z^{-2} + \cdots + A_n z^{-n}} X(z) - B_0 X(z)$$

$$= \frac{(B_1 - B_0 A_1) + (B_2 - B_0 A_2) z^{-1} + \cdots + (B_n - B_0 A_n) z^{-(n-1)}}{1 + A_1 z^{-1} + A_2 z^{-2} + \cdots + A_n z^{-n}} z^{-1} X(z) \quad 30$$

$$= \frac{C_0 + C_1 z^{-1} + \cdots + C_{n-1} z^{-(n-1)}}{1 + A_1 z^{-1} + A_2 z^{-2} + \cdots + A_n z^{-n}} z^{-1} X(z)$$

#### 【 0 0 8 0 】

ここで、 $Y(z)$ 、 $X(z)$ 、 $B_0$ 、 $B_1$ 、 $B_2$ 、 $A_0$ 、 $A_1$ 、 $A_2$ 、は、上で定義したことと同じ意味を有する。新たに導入された変数は、以下のように表される。 40

$$C_0 = B_1 - B_0 A_1$$

$$C_1 = (B_2 - B_0 A_2)$$

$$C_2 = (B_3 - B_0 A_3)$$

このスキームの実施は、図 15 に示されている。

#### 【 0 0 8 1 】

図 15 の回路において、係数  $C_0 \sim C_6$  及び  $A_1 \sim A_7$  を経由するフィルタリングは、完全に P C M ドメイン内で実施される。これは、高次の循環フィルタ (high-order recursive filter) に、カスケード・バイカッド・フィルタ (cascade biquad filters)、並列フィルタの加算 (summation) 等になることを許可するこのフィルタが実施される形式の中で自由を与える。カスケード・バイカッド実施 (cascade biquad implementation) は、フィルタのこのタイプが、量子化された係数であっても安定であるので望ましいこと 50

がある。

【0082】

$Y(z) = B_0 X(z) + S(z)$  の式は、 $S(z)$ について、以下のように繰り返されることがある。

$$S(z) = z^{-1} (C_0 X(z) + S_1(z))$$

これは、いくつかの理由で有用である。第1に、信号は、中間サンプリング・レートからベース・サンプリング・レートにさらにダウン・サンプリングされ、メモリ抑制 (memory saving) は、このダウン・サンプリングを介して達成されることができる。第2に、10 入力信号は、小さいファクタによって毎回、サンプリング・レートに達するまで中間サンプリング・レートを乗算するようにダウン・サンプリングされることができる。より小さいファクタで、ダウン・サンプリングすることによって、良い反エイリアシング性能が保証され得る。更に、オーバー・サンプリング・レート (例えば PDM ドメインで) で  $B_0$  を含む信号をフィルタリングすることは、最小の処理レーテンシーを保証し得る。オーバー・サンプリング・レートの  $1/4$  である中間サンプリング・レートの  $C_0$  を含む信号を処理することは、係数  $B_1$  に関する処理レーテンシーは、まだ利用されているということを保証する。 $B_2$  及び  $B_3$  に関する処理レーテンシーは、 $ISR_2 = ISR/4$  及び  $ISR_3 = ISR_2/4$  でフィルタリングされる場合、達成され、利用され得る。 $ISR$  は、中間サンプリング・レートを意味する。最終的に、式をくり返すことで、無限インパルス応答 (IIR) フィルタは、更なる安定性を提示する有限インパルス応答 (FIR) フィルタに効果的に変換される。20

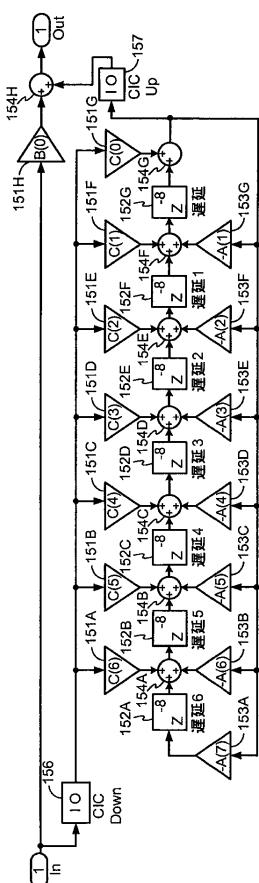

【0083】

図15は、PDM及びPCMドメインでサンプルをフィルタリングし、フィルタ・タップ間の遅延の目的でダウン・サンプラ及びアップ・サンプラ・ペアを用いるハイブリッド・アクティヴ雑音相殺回路の回路図である。PDMサンプルのケースにおいて、入力サンプルは、PDMドメインの回路及び増幅器151Hフィルタによって受信される。30 CICダウン・サンプラ156は、PCMドメインへの入力サンプルをダウン・サンプリングする。PSMドメインにおけるサンプルは、増幅器151A～151Gによってフィルタリングされる。加算器154Gの出力は、増幅器153A～153Gにフィードバックされる。増幅器151A～151H、及び増幅器153A～153Gは、サンプルへのフィルタ・タップのアプリケーションを定義し得る。例えば、増幅器151A～151H、及び増幅器153A～153Gは、利得ファクタによって、入力信号を乗算するデジタル乗算回路を含み得る。利得ファクタは、アクティヴ雑音相殺について、必要とされる望ましい信号増幅を達成するために、選択され得る。とりわけ、他の増幅器がPCMドメインのサンプルで動作する間、増幅器151Hは、PDMドメインのサンプルで動作する。素子156は、CICデシメータを含み、素子157は、CIC補間器を含み、これらの素子156、及び157は、PDMドメインのサンプルのフィルタ151Hのアプリケーションと、PCMドメインのサンプルのフィルタ増幅器151A～151Gのアプリケーションとの間の望ましい遅延を達成するように、調整され得る。

【0084】

加算器154A～154Gは、図示するように、増幅器151A～151Fの出力と、増幅器153A～153G及びメモリ・ベース遅延回路152A～152Gの出力とを合成する。同様に、加算器154Gは、遅延回路152A～152Gの出力を、増幅器151Gの出力と合成する。メモリ・ベース遅延回路152A～152Gは、サンプルが処理されるように、回路の連続するステージ間に、8個のサンプル遅延を提供する。一度、加算器154Gの出力が、CICアップ・サンプラ157を介してPDMドメインへ、アップ・コンバートされて戻る場合、CICアップ・サンプラ157の出力は、反雑音を含み得る回路出力を生成するために、増幅器151Hの出力と合成される。40

【0085】

概して、CICダウン・サンプラは、従来のFIRフィルタ、及び従来のダウン・サンプラと取って代わり得る。更に、CICアップ・サンプラは、従来のアップ・サンプラ及

10

20

30

40

50

び従来のFIRフィルタと取って代わり得る。

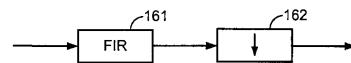

【0086】

本開示と整合性のとれた他の例において、本明細書に記載のCICデシメータは、望ましい遅延の部分を達成するために、他の種類のダウン・サンプル・ユニットと取って代わり、または追加のフィルタと合成され得る。ダウン・サンプル構造のような一つは、FIRフィルタ161及びダウン・サンプラー162を含む図16に示される。このケースにおいて、FIRフィルタ161は、ダウン・サンプリングしている間の出力内の高周波数信号帯域外のエイリアシングを抑制するために、ローパス・フィルタリングが実行され得る。ダウン・サンプラー162は、入力信号の全てのR個のサンプルから、R-1個のサンプルを除去することで、デジタル信号のサンプリング・レートを抑制し得る。

10

【0087】

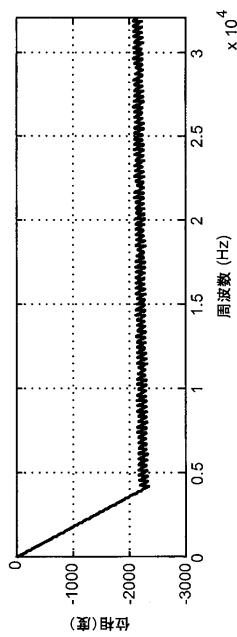

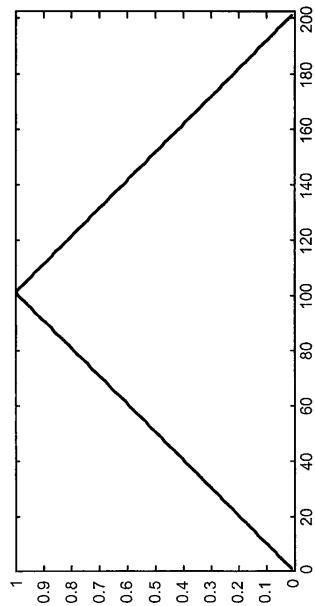

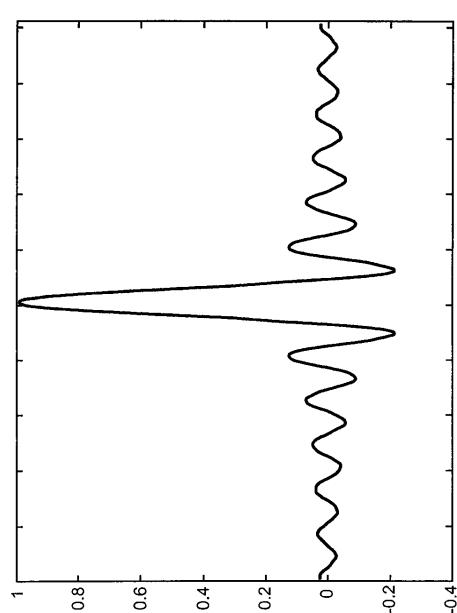

FIRフィルタ161は、FIRフィルタ161が、全ての周波数について一定のグループ遅延を提供するように、シンメトリック(symmetric)であり得る。FIRフィルタ161の長さは、望ましい遅延を提供するようにセットされ得る。大抵、N個のタップの遅延が、要求される場合、フィルタの長さは $2N-1$ 個のタップである。実現可能なFIRフィルタ応答の一例は、図17、18A、及び18Bのグラフで示される。図17は、図16のFIR+ダウン・サンプラーの組み合わせで用いられるFIR+ダウン・サンプラーの組み合わせフィルタの一例を示すグラフである。ここで、x軸は、フィルタ・タップ・インデックスであり、y軸は、フィルタ・タップ係数を表している。

20

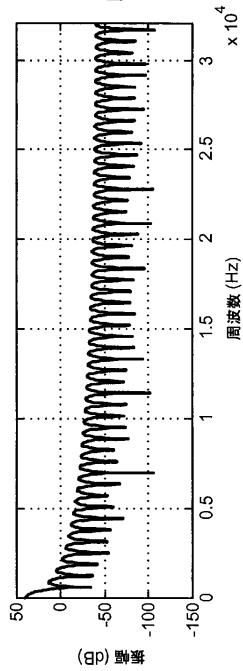

【0088】

図18A及び18Bは、入力周波数の関数として、それぞれ出力振幅及び出力位相を示す二つのグラフである。図18A及び18Bは、64kHzから8kHzサンプリング・レートの信号のダウン・サンプリングの一例で用いられる、FIRフィルタの例示的な応答を示している。入力信号周波数の関数として、図18Aは、dBの振幅応答(amplitude respond)であり、図18Bは、度(degree)の位相応答(phase respond)である。首尾良く信号のダウン・サンプリングするために、FIRフィルタは、ダウン・サンプリング後のバンド内の信号を保護すべきである。現在の例において、これは $8\text{kHz}/2 = 4\text{kHz}$ であり、振幅応答プロットは、FIRフィルタは、0Hz~4kHzで一定の信号レベルを維持するということを示している。また、FIRは、エイリアシングを防止するために、帯域外信号(out of band signal)(すなわち、信号 $> 4\text{kHz}$ )を抑制すべきである。プロットは、FIRフィルタは、このベース・バンド信号、信号 $> 4\text{kHz}$ の約40dBだけダウンを抑制することができるということを示している。また、帯域内信号への位相歪み(phase distortion)を抑制するために、FIRは、図18Bに示すように、位相が、周波数增加として負に向かす直線であるように、線形位相を有し得る。FIRフィルタ161は、そのようなフィルタリングを達成するように設計され得る。図17、18A及び18Bのグラフで実証されるFIRフィルタ出力は、エイリアス信号の約50dBの抑制で64kHzから8kHzへとダウン・サンプリングすることについて、許可し得る。

30

【0089】

図19、20A及び20Bは、本開示と整合性のとれた、FIRフィルタ161について用いられる他の実現可能なFIRフィルタの例を示している。図19は、FIRフィルタ応答を示す他のグラフであり、図20A及び20Bは、入力周波数の関数として、それぞれ、出力振幅及び出力位相を示す二つのグラフである。FIRフィルタ161は、そのようなフィルタリングを有するように設計され得る。

40

【0090】

更に他の例において、上述したCICデシメータは、図21に示すようなFIRフィルタ及びダウン・サンプラーのカスケードと取って代わることが有る。このケースにおいて、FIRフィルタ211、ダウン・サンプラー212、FIRフィルタ213、ダウン・サンプラー214、FIRフィルタ215、ダウン・サンプラー216は、必要な遅延を達成するために、本明細書で議論されたCICデシメータととって代わり得る。ダウン・サンプラー

50

、及びカスケードされたFIRフィルタの各ステージの遅延及びダウン・サンプル・レシオは、望ましい全ての遅延及びダウン・サンプル・レシオを正しく達成するために、選択され得る。例えば、各FIRが、N個のタップの遅延を有し、ダウン・サンプラが、ダウン・サンプル・レシオまたはRを有する場合、図21に示すように、FIRダウン・サンプラ・ペアの3つのステージのチェインについて、全ての遅延は、 $N + N \times R + N \times R^2$ であり、全てのダウン・サンプル・レシオは、 $R^3$ である。

#### 【0091】

更に他の例において、本明細書に記載のCICデシメータは、所定のアクティヴ雑音相殺回路構成に必要とされている遅延の量を明確にするために、CICデシメータのカスケードによって、交換され得る。任意の数のCICデシメータ回路が用いられるとはいえ、図22は、三つのカスケードされたCICデシメータ221、222及び223を示している。CICデシメータ221、222及び223のパラメータは、CICデシメータ221、222、及び223についての異なる遅延量、または同じ遅延量を提供するように調整されることができる。各CICの遅延及びダウン・サンプル・レシオは、望ましい全ての遅延及びダウン・サンプル・レシオを達成するように定義され得る。例えば、各CICデシメータが、N個のタップ遅延及びダウン・サンプル・レシオRを有するかもしれない。全てのダウン・サンプル・レシオは、 $R^3$ であり、全ての遅延は、三つのCICデシメータについてのチェインについての、 $N + N \times R + N \times R^2$ である。

10

#### 【0092】

CICデシメータのように、本明細書に開示されるCIC補間器は、追加のフィルタと合成され、望ましい遅延の一部を達成するために、他の種類のアップ・サンプル・ユニットと交換され得る。アップ・サンプル構成のような一つは、FIRフィルタ232に続くアップ・サンプル231を含む図23に示される。FIRフィルタ232は、全ての周波数について一定のグループ遅延を提供するように、シンメトリック(symmetric)であり得る。上述したダウン・サンプリングで用いられる同一、または似ているFIRフィルタは、アップ・サンプリングで用いられることができる。

20

#### 【0093】

このケースにおいて、FIR + ダウン・サンプラの組み合わせフィルタ232は、アップ・サンプリングの間、出力の帯域外高周波数信号に対する、帯域内信号の任意のイメージング効果を除去または防止するように、ローパス・フィルタリングを実行し得る。アップ・サンプラ231は、出力信号が、入力信号のサンプリング・レートR時間有するように、各サンプル間にR-1個のゼロを挿入し得る。

30

#### 【0094】

FIR232の長さは、望ましい遅延を提供するように設定されうる。大抵、N個のタップの遅延が要求された場合、フィルタの長さは、フィルタの長さは $2N - 1$ 個のタップである。フィルタ232の実現可能なFIRフィルタの一例は、図24及び25のグラフによって示される。図24及び25は、図17と同様の意味を持っている。二つのグラフは、FIRフィルタの形を描画する。従って、x軸は、フィルタ・タップに対するインデックスであり、y軸は、フィルタ・タップ係数の値である。FIRフィルタ232は、そのようなフィルタリングを達成するように設計され得る。図24及び25のグラフで実証されるFIRフィルタ出力は、イメージング信号の抑制を含む8kHzから64kHzへのアップ・サンプリングについて許可得る。

40

#### 【0095】

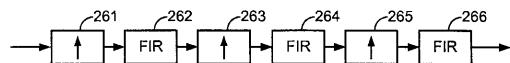

CICデシメータと同様に、上述したCIC補間器は、図26に示すようなFIRフィルタ及びアップ・サンプラと取って代わることが有る。このケースにおいて、アップ・サンプラ261、FIRフィルタ262、アップ・サンプラ263、FIRフィルタ264、アップ・サンプラ265及びFIRフィルタ266は、必要な遅延を達成するために、本明細書で議論されたCIC補間器ととって代わり得る。カスケードされたアップ・サンプラ、及びFIRフィルタの各ステージの遅延及びアップ・サンプル・レシオは、望ましい全ての遅延及びダウン・サンプル・レシオを正しく達成するために、選択され得る。例

50

えば、各 F I R が、N 個のタップの遅延を有し、アップ・サンプルが、アップ・サンプル・レシオまたは R を有する場合、図 26 に示すように、F I R アップ・サンプル・ペアの 3 つのステージのチェインについて、全ての遅延は、 $N + N \times R + N \times R^2$  であり、全てのダウン・サンプル・レシオは、 $R^3$  である。任意の数のアップ・サンプル及び F I R フィルタのペアが用いられ得る。

【0096】

更に他の例において、本明細書に記載の C I C 補間器は、所定のアクティヴ雑音相殺回路構成に必要とされている遅延の量を明確にするために、C I C 補間器のカスケードによって、交換され得る。任意の数の C I C 補間器が用いられるとはいえ、図 27 は、三つのカスケードされた C I C 補間器 271, 272 及び 273 を示している。C I C 補間器 271, 272 及び 273 のパラメータは、C I C 補間器 271, 272, 及び 273 についての異なる遅延量、または同じ遅延量を提供するように調整されることができる。各 C I C 補間器の遅延及びアップ・サンプル・レシオは、望ましい全ての遅延及びアップ・サンプル・レシオを達成するように定義され得る。例えば、各 C I C 補間器が、N 個のタップ遅延及びアップ・サンプル・レシオ R を有する場合、全てのアップ・サンプル・レシオは、 $R^3$  であり、全ての遅延は、三つの C I C 補間器についてのチェインについての、 $N + N \times R + N \times R^2$  である。

10

【0097】

本開示の技術は、携帯電話、集積回路 (I C)、または I C のセット (すなわちチップ・セット) のような、ワイヤレス通信装置ハンドセットを含む装置、またはある目的に必要な器具一式の広い取り合わせで実施され得る。任意の要素、モジュール、またはユニットは、機能的な態様を重視し、種々のハードウェア・ユニットによる認識を必ずしも要求しないということを提供することが記載されている。本明細書に記載の技術は、ハードウェア、ソフトウェア、ファームウェア、またはこれらの任意の組み合わせで実施され得る。モジュール、ユニット、または要素として記載されている任意の特徴は、集積論理装置、または別々のディスクリート、しかし共同利用できる論理装置で共に実施され得る。いくつかのケースにおいて、種々の特徴は、集積回路チップまたはチップセットのような集積回路装置として実施され得る。

20

【0098】

ソフトウェアで実施される場合、技術は、プロセッサで実施される場合、上述した一つまたはそれ以上の方法を実行するという命令を含むコンピュータ読み取り可能な媒体で少なくとも在る程度実現され得る。コンピュータ読み取り可能な媒体は、コンピュータ読み取り可能な記憶媒体を備え、パッケージング材料を含み得るコンピュータ・プログラム製品の一部を形成する。コンピュータ読み取り可能な記憶媒体は、シンクロナスダイナミックランダムアクセスメモリ (S D R A M)、読み出し専用メモリ (R O M)、不揮発性ランダムアクセスメモリ (N V R A M)、電気的に消去及び書き込み可能な読み出し専用メモリ (E E P R O M)、F L A S H メモリ、磁気的、または光学データ記憶媒体等のようなランダム・アクセス・メモリ (R A M) を含み得る。技術は、更に、または代替的に、命令またはデータ構造の携帯で、コードを通信または運び、コンピュータによってアクセスされ、読み出され、及び / または実行されるコンピュータ読み取り可能な媒体で少なくとも在る程度実現され得る。

30

40

【0099】

本明細書に記載の任意の回路は、上述したようなコンピュータ読み取り可能な記憶媒体に記憶された命令を実行するプロセッサで少なくとも在る程度実現され得る。従って、本開示は、プロセッサにアクティヴ雑音相殺を実行させる実行という命令を含むコンピュータ読み取り可能な記憶媒体を予期する。命令は、プロセッサに、ダウン・サンプル・ユニット及びアップ・サンプル・ユニットを介してサンプルを処理させ、ダウン・サンプル・ユニット及びアップ・サンプル・ユニットを介してサンプルを処理することに関する合成遅延は、アクティヴ雑音相殺を促進させるために選択される予め決定された遅延と一致する。合成遅延は、ダウン・サンプル・ユニット及びアップ・サンプル・ユニットを含む回

50

路の調整可能パラメータを含み得る。命令は、プロセッサに、調整可能パラメータを選択させる。

#### 【0100】

コードまたは命令は、一つまたはそれ以上のデジタル信号プロセッサ（D S P）、汎用目的マイクロプロセッサ、特定用途向け集積回路（A S I C）、フィールド・プログラマブル・ロジック・アレイ（F P G A）、または他の平衡集積またはディスクリート論理回路のよう一つまたはそれ以上のプロセッサによって実行され得る。従って、本明細書で用いられている“プロセッサ”という用語は、任意の先の構造、または本明細書に記載の技術を適切に実施できる任意の他の構造に言及され得る。更に、任意の態様において、本明細書に記載の機能は、合成されたビデオ・コーデックの組み込み、デコーディング、エンコーディング、について構成される献身的なハードウェア・モジュールまたはソフトウェア・モジュール内に提供され得る。また、技術は、一つまたはそれ以上の回路または論理素子で完全に実施され得ることができる。

10

#### 【0101】

本開示は、また、本開示に記載された一つまたはそれ以上の技術を実施する回路を含む任意の種類の集積回路装置を予期している。そのような回路は、単一の集積回路チップ内、または、チップセットと呼ばれる複数の共同利用できる集積回路チップ内に提供され得る。そのような集積回路装置は、携帯電話ハンドセットのようなワイヤレス通信デバイスで用いられる種々のアプリケーションで用いられ得る。

20

#### 【0102】

種々の例は、本開示に記載されている。本明細書に記載の回路は、図示された、ダウン・サンプリング及びアップ・サンプリング・レシオ、増幅器、ステージの例示的な数を有し、他のダウン・サンプリング及びアップ・サンプリング・レシオ、増幅器、ステージの例示的な数は、本開示と整合性がとれる他の構成で用いられ得ることができる。

30

#### 【0103】

更に、本開示の遅延技術が、アクティヴ雑音相殺の文脈で記載されているとしても、遅延技術は、他の回路（すなわち、アクティヴ雑音相殺を実行しない回路）でも用いられ得る。例えば、メモリ・ベース遅延回路というよりむしろダウン・サンプル・ユニット及びアップ・サンプル・ユニットを備える遅延技術は、低レーテンシー平衡回路または他の回路で用いられ得る。

#### 【0104】

これら及び他の例は、添付した特許請求の範囲の範囲内である。

【図 1 A】

【図 1 B】

【図 2】

【 図 6 】

图 6

FIG. 6

【 四 7 】

四

FIG. 7

【 义 8 】

图 8

FIG. 8

【図9A】

図 9A

FIG. 9A

【図 9B】

図 9B

FIG. 9B

【図 10】

図 10

FIG. 10

【図 11】

図 11

FIG. 11

【図 12】

図 12

FIG. 12

【図 13】

図 13

FIG. 13

【図 14】

図 14

FIG. 14

【図 15】

図 15

FIG. 15

【図 16】

図 16

FIG. 16

【図 17】

図 17

FIG. 17

【図 18 A】

図 18A

FIG. 18A

【図 18 B】

図 18B

FIG. 18B

【図 19】

図 19

FIG. 19

【図 20A】

図 20A

FIG. 20A

【図 20B】

図 20B

FIG. 20B

【図 21】

図 21

FIG. 21

【図 22】

図 22

FIG. 22

【図 23】

図 23

FIG. 23

【図 24】

図 24

FIG. 24

【図 25】

図 25

FIG. 25

【図 26】

図 26

FIG. 26

【図 27】

図 27

FIG. 27

## 【手続補正書】

【提出日】平成24年8月20日(2012.8.20)

## 【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

## 【補正の内容】

【特許請求の範囲】

## 【請求項1】

装置は、

ダウン・サンプル・ユニットと、

アップ・サンプル・ユニットと、

を備え、

前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットは、前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットを介して、サンプルを処理することに関連する合成遅延(combined delay)が、前記装置について選択される予め定義された(pre-defined)遅延と一致するようにそれぞれ調整され、

前記合成遅延は前記装置の調整可能パラメータ(tunable parameter)であり、

前記合成遅延は、前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットのサンプリング・レシオに基づいて、調整可能である

装置。

## 【請求項2】

アクティヴ雑音相殺(active noise cancellation)を実行するように構成されたアク

ティヴ雑音相殺回路

を更に備え、

前記予め定義された遅延は、前記アクティヴ雑音相殺を促進するように選択される請求項1の装置。

【請求項3】

前記アップ・サンプル・ユニットは、前記サンプルについて、前記予め定義された遅延を提供するために、前記ダウン・サンプル・ユニットのすぐ後に続く請求項1の装置。

【請求項4】

前記ダウン・サンプル・ユニットは、カスケード積分櫛形(C I C:cascaded integration combiner)デシメータを備え、前記アップ・サンプル・ユニットは、C I C補間器(interpolator)を備える

請求項1の装置。

【請求項5】

前記合成遅延は、また、ステージ数(N)についての固定数、及び前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットについての差動遅延(differential delay)(M)に基づく

請求項1の装置。

【請求項6】

前記ダウン・サンプル・ユニットの出力をフィルタリングし、前記アップ・サンプル・ユニットへ入力を提供するフィルタのセットを定義する遅延素子、加算器及び増幅器のセットを更に含み、

前記予め定義された遅延に一致する前記合成遅延は、前記フィルタのセットに関連する遅延と一致する

請求項1の装置。

【請求項7】

前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットは、それぞれ、前記合成遅延の半分(one-half)を生成するように調整される

請求項1の装置。

【請求項8】

前記装置は、前記予め定義された遅延を生成するために、前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットを含むアクティヴ雑音相殺回路(active noise cancellation circuit)を備え、

前記予め定義された遅延は、前記アクティヴ雑音相殺を促進するように選択され、

前記装置は、オーディオ情報を捉えるマイクロフォンと、前記捉えられたオーディオ情報をサンプルに変換するデジタル・アナログ変換器(digital-to-analog converter)と、前記アクティヴ雑音相殺回路によって生成される反雑音を出力するスピーカと、を更に備える

請求項1の装置。

【請求項9】

アクティヴ雑音相殺(active noise cancellation)を実行する方法であって、前記方法は、

ダウン・サンプル・ユニット及びアップ・サンプル・ユニットを介してサンプルを処理することを備え、

前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットを介してサンプルを処理することに関する合成された遅延は、アクティヴ雑音相殺を促進するように選択される予め定義された(pre-defined)遅延と一致し、

前記合成遅延は、前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットを含む回路の調整可能パラメータ(tunable parameter)であり、

前記合成遅延は、前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットのサンプリング・レシオに基づいて、調整可能である

アクティヴ雑音相殺を実行する方法。

## 【請求項 10】

前記回路は、アクティヴ雑音回路を含む

請求項 9 の方法。

## 【請求項 11】

前記アップ・サンプル・ユニットは、前記サンプルについて、前記サンプルについて前記予め定義された遅延を提供するために、前記ダウン・サンプル・ユニットのすぐ後に続く

請求項 9 の方法。

## 【請求項 12】

前記ダウン・サンプル・ユニットは、カスケード積分櫛形 ( C I C : cascaded integration combiner ) デシメータを備え、前記アップ・サンプル・ユニットは、C I C 補間器 ( interpolator ) を備える

請求項 9 の方法。

## 【請求項 13】

前記合成遅延は、また、ステージ数 N についての固定値、及び前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットについての差動遅延 ( differential delay ) M に基づく

請求項 9 の方法。

## 【請求項 14】

前記ダウン・サンプル・ユニットの出力をフィルタリングし、前記アップ・サンプル・ユニットへ入力を提供するフィルタのセットを定義する遅延素子、加算器及び増幅器のセットを介して、前記サンプルを処理することを更に備え、

前記予め定義された遅延に一致する前記合成遅延は、前記フィルタのセットに関連する遅延と一致する

請求項 9 の方法。

## 【請求項 15】

前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットは、それぞれ、前記合成遅延の半分 ( one-half ) を生成するように調整される

請求項 9 の方法。

## 【請求項 16】

前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットは、反雑音を生成するアクティヴ雑音相殺回路の一部を形成し、

前記方法は更に、

オーディオ情報を捉えることと、

前記捉えられたオーディオ情報をサンプルに変換することと、

前記反雑音を生成するために、前記アクティヴ雑音相殺回路を介して前記サンプルを処理することと、

前記アクティヴ雑音相殺回路によって生成された前記反雑音を出力することと、

を備える

請求項 9 の方法。

## 【請求項 17】

ダウン・サンプリング手段と、

アップ・サンプリング手段と、

を備え、前記ダウン・サンプリング手段、及び前記アップ・サンプリング手段は、ダウン・サンプリング及びアップ・サンプリングに関する合成された遅延が、予め定義された遅延と一致するように、それぞれ調整され、

前記合成遅延は、前記装置の調整可能パラメータ ( tunable parameter ) であり、

前記合成遅延は、前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットのサンプリング・レシオに基づいて、調整可能である

装置。

**【請求項 18】**

アクティヴ雑音相殺 (active noise cancellation) を実行するように構成されたアクティヴ雑音相殺回路

を備え、

前記予め定義された遅延は、前記アクティヴ雑音相殺を促進するように予め選択される

請求項 17 の装置。

**【請求項 19】**

前記アップ・サンプリング手段は、前記サンプルについて、前記予め定義された遅延を

提供するために、前記ダウン・サンプリング手段のすぐ後に続く

請求項 17 の装置。

**【請求項 20】**

前記ダウン・サンプリング手段は、カスケード積分櫛形 (CIC : cascaded integration combiner) デシメータを備え、前記アップ・サンプリング手段は、CIC 補間器 (interpolator) を備える

請求項 17 の装置。

**【請求項 21】**

前記合成遅延は、また、ステージ数 (N) についての固定数、及び前記ダウン・サンプリング手段及び前記アップ・サンプリング手段についての差動遅延 (differential delay) (M) に基づく

請求項 17 の装置。

**【請求項 22】**

前記ダウン・サンプリング手段の出力をフィルタリングし、前記アップ・サンプリング手段へ入力を提供するフィルタのセットを定義する遅延素子、加算器及び増幅器のセット

を更に含み、

前記予め定義された遅延に一致する前記合成遅延は、前記フィルタのセットに関連する

遅延と一致する

請求項 17 の装置。

**【請求項 23】**

前記ダウン・サンプリング手段及び前記アップ・サンプリング手段は、それぞれ、前記

合成遅延の半分 (one-half) を生成するように調整される

請求項 17 の装置。

**【請求項 24】**

前記装置は、前記予め定義された遅延を生成するために、前記ダウン・サンプリング手段及び前記アップ・サンプリング手段を含むアクティヴ雑音相殺回路 (active noise cancellation circuits) を備え、

前記予め定義された遅延は、前記アクティヴ雑音相殺を促進するように選択され、

前記装置は、オーディオ情報を捉えるマイクロフォンと、前記捉えられたオーディオ情報

をサンプルに変換するデジタル・アナログ変換器 (digital-to-analog converter) と

、前記アクティヴ雑音相殺回路によって生成される反雑音を出力するスピーカと、を更に

備える

請求項 17 の装置。

**【請求項 25】**

プロセッサ内での実行で前記プロセッサに、アクティヴ雑音相殺 (active noise cancellation) を実行させる、命令を含むコンピュータ読み出し可能な記憶媒体であって、

前記命令は、前記プロセッサに、

前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットを介してサンプル

を処理させ、

前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットを介してサンプル

を処理することに関する合成された遅延は、アクティヴ雑音相殺を促進するように選択

される予め定義された (pre-defined) 遅延と一致し、

前記合成遅延は、前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットを含む前記装置の調整可能パラメータ ( tunable parameter ) であり、

前記命令は、前記プロセッサに、前記調整可能パラメータを選択させ、

前記合成遅延は、前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットのサンプリング・レシオに基づいて、調整可能である

コンピュータ読み出し可能な記憶媒体。

【請求項 26】

前記回路はアクティヴ雑音相殺回路を備え、

前記プロセッサは、前記回路についての前記予め定義された遅延を選択する

請求項 25 のコンピュータ読み出し可能な記憶媒体。

【請求項 27】

前記アップ・サンプル・ユニットは、前記サンプルについて、前記予め定義された遅延を生成するために、前記ダウン・サンプル・ユニットのすぐ後に続く

請求項 25 のコンピュータ読み出し可能な記憶媒体。

【請求項 28】

前記ダウン・サンプル・ユニットは、カスケード積分櫛形 ( C I C : cascaded integration combiner ) デシメータを備え、前記アップ・サンプル・ユニットは、C I C 補間器 ( interpolator ) を備える

請求項 25 のコンピュータ読み出し可能な記憶媒体。

【請求項 29】

前記合成遅延は、また、ステージ数 N についての固定数、及び前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットについての差動遅延 ( differential delay ) M に基づき、

前記命令は、前記プロセッサに、N 及び M に基づいて前記合成遅延を調整させる

請求項 25 のコンピュータ読み出し可能な記憶媒体。

【請求項 30】

前記命令は、前記装置に、前記ダウン・サンプル・ユニットの出力をフィルタリングし、前記アップ・サンプル・ユニットへ入力を提供するフィルタのセットを定義する遅延素子、加算器及び増幅器のセットを介して、前記サンプルを処理させ、

前記予め定義された遅延に一致する前記合成遅延は、前記フィルタのセットに関連する遅延と一致する

請求項 25 のコンピュータ読み出し可能な記憶媒体。

【請求項 31】

前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットは、それぞれ、前記合成遅延の半分 ( one-half ) を生成するように調整される

請求項 25 のコンピュータ読み出し可能な記憶媒体。

【請求項 32】

前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットは、反雑音を生成するアクティヴ雑音相殺回路の一部を形成し、

前記命令は、前記プロセッサに、

オーディオ情報を捉えさせ、

前記捉えられたオーディオ情報をサンプルに変換させ、

前記反雑音を生成するために、前記アクティヴ雑音相殺回路を介して前記サンプルを処理させ、

前記アクティヴ雑音相殺回路によって生成された前記反雑音を出力させる

請求項 25 のコンピュータ読み出し可能な記憶媒体。

【手続補正 2】

【補正対象書類名】明細書

【補正対象項目名】0 1 0 4

【補正方法】変更

## 【補正の内容】

## 【0104】

これら及び他の例は、添付した特許請求の範囲の範囲内である。

以下に、本願出願の当初の特許請求の範囲に記載された発明を付記する。

1. 装置は、

ダウン・サンプル・ユニットと、

アップ・サンプル・ユニットと、

を備え、

前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットは、前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットを介して、サンプルを処理することに関連する合成遅延 (combined delay) が、前記装置について選択される予め定義された (pre-defined) 遅延と一致するようにそれぞれ調整される

装置。

2. 前記合成遅延は、前記装置の調整可能パラメータ (tunable parameter) である

1の装置。

3. アクティヴ雑音相殺 (active noise cancellation) を実行するように構成されたアクティヴ雑音相殺回路

を更に備え、

前記予め定義された遅延は、前記アクティヴ雑音相殺を促進するように選択される1の装置。

4. 前記アップ・サンプル・ユニットは、前記サンプルについて、前記予め定義された遅延を提供するために、前記ダウン・サンプル・ユニットのすぐ後に続く

1の装置。

5. 前記ダウン・サンプル・ユニットは、カスケード積分櫛形 (CIC : cascaded integration combiner) デシメータを備え、前記アップ・サンプル・ユニットは、CIC補間器 (interpolator) を備える

1の装置。

6. 前記合成遅延は、前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットのサンプリング・レシオに基づいて、調整可能である

5の装置。

7. 前記合成遅延は、また、ステージ数 (N) についての固定数、及び前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットについての差動遅延 (differential delay) (M) に基づく

6の装置。

8. 前記ダウン・サンプル・ユニットの出力をフィルタリングし、前記アップ・サンプル・ユニットへ入力を提供するフィルタのセットを定義する遅延素子、加算器及び増幅器のセットを更に含み、

前記予め定義された遅延に一致する前記合成遅延は、前記フィルタのセットに関連する遅延と一致する

3の装置。

9. 前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットは、それぞれ、前記合成遅延の半分 (one-half) を生成するように調整される

1の装置。

10. 前記装置は、前記予め定義された遅延を生成するために、前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットを含むアクティヴ雑音相殺回路 (active noise cancellation circuit) を備え、

前記予め定義された遅延は、前記アクティヴ雑音相殺を促進するように選択され、

前記装置は、オーディオ情報を捉えるマイクロフォンと、前記捉えられたオーディオ情報をサンプルに変換するデジタル・アナログ変換器 (digital-to-analog converter) と、前記アクティヴ雑音相殺回路によって生成される反雑音を出力するスピーカと、を更に

備える1 の装置。11. アクティヴ雑音相殺 (active noise cancellation) を実行する方法であって、前記方法は、ダウン・サンプル・ユニット及びアップ・サンプル・ユニットを介してサンプルを処理することを備え、前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットを介してサンプルを処理することに関する合成された遅延は、アクティヴ雑音相殺を促進するように選択される予め定義された (pre-defined) 遅延と一致するアクティヴ雑音相殺を実行する方法。12. 前記合成遅延は、前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットを含む回路の調整可能パラメータ (tunable parameter) である11 の方法。13. 前記回路は、アクティヴ雑音回路を含む12 の方法。14. 前記アップ・サンプル・ユニットは、前記サンプルについて、前記サンプルについて前記予め定義された遅延を提供するために、前記ダウン・サンプル・ユニットのすぐ後に続く11 の方法。15. 前記ダウン・サンプル・ユニットは、カスケード積分櫛形 (CIC : cascaded integration combiner) デシメータを備え、前記アップ・サンプル・ユニットは、CIC補間器 (interpolator) を備える11 の方法。16. 前記合成遅延は、前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットのサンプリング・レシオに基づいて、調整可能であり前記方法は、前記サンプリング・レシオに基づいて、前記合成遅延を調整することを更に備える15 の方法。17. 前記合成遅延は、また、ステージ数 N についての固定値、及び前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットについての差動遅延 (differential delay) M に基づく16 の方法。18. 前記ダウン・サンプル・ユニットの出力をフィルタリングし、前記アップ・サンプル・ユニットへ入力を提供するフィルタのセットを定義する遅延素子、加算器及び増幅器のセットを介して、前記サンプルを処理することを更に備え、前記予め定義された遅延に一致する前記合成遅延は、前記フィルタのセットに関連する遅延と一致する11 の方法。19. 前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットは、それぞれ、前記合成遅延の半分 (one-half) を生成するように調整される11 の方法。20. 前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットは、反雑音を生成するアクティヴ雑音相殺回路の一部を形成し、前記方法は更に、オーディオ情報を捉えることと、前記捉えられたオーディオ情報をサンプルに変換することと、前記反雑音を生成するために、前記アクティヴ雑音相殺回路を介して前記サンプルを処理することと、前記アクティヴ雑音相殺回路によって生成された前記反雑音を出力することと、

を備える

11の方法。

21. ダウン・サンプリング手段と、

アップ・サンプリング手段と、

を備え、前記ダウン・サンプリング手段、及び前記アップ・サンプリング手段は、ダウン・サンプリング及びアップ・サンプリングに関する合成された遅延が、予め定義された遅延と一致するように、それぞれ調整される

装置。

22. 前記合成遅延は、前記装置の調整可能パラメータ (tunable parameter) である

21の装置。

23. アクティヴ雑音相殺 (active noise cancellation) を実行するように構成されたアクティヴ雑音相殺回路

を備え、

前記予め定義された遅延は、前記アクティヴ雑音相殺を促進するように予め選択される21の装置。

24. 前記アップ・サンプリング手段は、前記サンプルについて、前記予め定義された遅延を提供するために、前記ダウン・サンプリング手段のすぐ後に続く

21の装置。

25. 前記ダウン・サンプリング手段は、カスケード積分櫛形 (CIC : cascaded integration combiner) デシメータを備え、前記アップ・サンプリング手段は、CIC補間器 (interpolator) を備える

21の装置。

26. 前記合成遅延は、前記ダウン・サンプリング手段及び前記アップ・サンプリング手段のサンプリング・レシオに基づいて、調整可能である

25の装置。

27. 前記合成遅延は、また、ステージ数 (N) についての固定数、及び前記ダウン・サンプリング手段及び前記アップ・サンプリング手段についての差動遅延 (differential delay) (M) に基づく

26の装置。

28. 前記ダウン・サンプリング手段の出力をフィルタリングし、前記アップ・サンプリング手段へ入力を提供するフィルタのセットを定義する遅延素子、加算器及び増幅器のセットを更に含み、

前記予め定義された遅延に一致する前記合成遅延は、前記フィルタのセットに関連する遅延と一致する

23の装置。

29. 前記ダウン・サンプリング手段及び前記アップ・サンプリング手段は、それぞれ、前記合成遅延の半分 (one-half) を生成するように調整される

21の装置。

30. 前記装置は、前記予め定義された遅延を生成するために、前記ダウン・サンプリング手段及び前記アップ・サンプリング手段を含むアクティヴ雑音相殺回路 (active noise cancellation circuits) を備え、

前記予め定義された遅延は、前記アクティヴ雑音相殺を促進するように選択され、

前記装置は、オーディオ情報を捉えるマイクロフォンと、前記捉えられたオーディオ情報をサンプルに変換するデジタル・アナログ変換器 (digital-to-analog converter) と、前記アクティヴ雑音相殺回路によって生成される反雑音を出力するスピーカと、を更に備える

21の装置。

31. プロセッサ内の実行で前記プロセッサに、アクティヴ雑音相殺 (active noise cancellation) を実行させる、命令を含むコンピュータ読み出し可能な記憶媒体であって

、前記命令は、前記プロセッサに、

前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットを介してサンプルを処理させ、

前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットを介してサンプルを処理することに関する合成された遅延は、アクティヴ雑音相殺を促進するように選択される予め定義された( pre-defined )遅延と一致する

コンピュータ読み出し可能な記憶媒体。

3 2 . 前記合成遅延は、前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットを含む前記装置の調整可能パラメータ( tunable parameter )であり、

前記命令は、前記プロセッサに、前記調整可能パラメータを選択させる

3 1 のコンピュータ読み出し可能な記憶媒体。

3 3 . 前記回路はアクティヴ雑音相殺回路を備え、

前記プロセッサは、前記回路についての前記予め定義された遅延を選択する

3 1 のコンピュータ読み出し可能な記憶媒体。

3 4 . 前記アップ・サンプル・ユニットは、前記サンプルについて、前記予め定義された遅延を生成するために、前記ダウン・サンプル・ユニットのすぐ後に続く

3 1 のコンピュータ読み出し可能な記憶媒体。

3 5 . 前記ダウン・サンプル・ユニットは、カスケード積分櫛形( C I C : cascaded integration combiner )デシメータを備え、前記アップ・サンプル・ユニットは、C I C補間器( interpolator )を備える

3 1 のコンピュータ読み出し可能な記憶媒体。

3 6 . 前記合成遅延は、前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットのサンプリング・レシオに基づいて、調整可能であり、

前記命令は、前記プロセッサに、前記サンプリング・レシオに基づいて、前記合成遅延を調整させる

3 5 のコンピュータ読み出し可能な記憶媒体。

3 7 . 前記合成遅延は、また、ステージ数 N についての固定数、及び前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットについての差動遅延( differential delay ) M に基づき、

前記命令は、前記プロセッサに、 N 及び M に基づいて前記合成遅延を調整させる

3 6 のコンピュータ読み出し可能な記憶媒体。

3 8 . 前記命令は、前記装置に、前記ダウン・サンプル・ユニットの出力をフィルタリングし、前記アップ・サンプル・ユニットへ入力を提供するフィルタのセットを定義する遅延素子、加算器及び増幅器のセットを介して、前記サンプルを処理させ、

前記予め定義された遅延に一致する前記合成遅延は、前記フィルタのセットに関連する遅延と一致する

3 1 のコンピュータ読み出し可能な記憶媒体。

3 9 . 前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットは、それぞれ、前記合成遅延の半分( one-half )を生成するように調整される

3 1 のコンピュータ読み出し可能な記憶媒体。

4 0 . 前記ダウン・サンプル・ユニット及び前記アップ・サンプル・ユニットは、反雑音を生成するアクティヴ雑音相殺回路の一部を形成し、

前記命令は、前記プロセッサに、

オーディオ情報を捉えさせ、

前記捉えられたオーディオ情報をサンプルに変換させ、

前記反雑音を生成するために、前記アクティヴ雑音相殺回路を介して前記サンプルを処理させ、

前記アクティヴ雑音相殺回路によって生成された前記反雑音を出力させる

3 1 のコンピュータ読み出し可能な記憶媒体。

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

|                                                   |

|---------------------------------------------------|

| International application No<br>PCT/US2010/054147 |

|---------------------------------------------------|

|                                                                |

|----------------------------------------------------------------|

| A. CLASSIFICATION OF SUBJECT MATTER<br>INV. G10K11/178<br>ADD. |

|----------------------------------------------------------------|

|                                                                                                   |

|---------------------------------------------------------------------------------------------------|

| According to International Patent Classification (IPC) or to both national classification and IPC |

|---------------------------------------------------------------------------------------------------|

|                    |

|--------------------|

| B. FIELDS SEARCHED |

|--------------------|

|                                                                                                   |

|---------------------------------------------------------------------------------------------------|

| Minimum documentation searched (classification system followed by classification symbols)<br>G10K |

|---------------------------------------------------------------------------------------------------|

|                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------|

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched |

|-------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------|

| Electronic data base consulted during the international search (name of data base and, where practical, search terms used) |

|----------------------------------------------------------------------------------------------------------------------------|

|                      |

|----------------------|

| EPO-Internal, INSPEC |

|----------------------|

|                                        |

|----------------------------------------|

| C. DOCUMENTS CONSIDERED TO BE RELEVANT |

|----------------------------------------|

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                                                                                                                                                                         | Relevant to claim No.                                                          |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| X         | EP 1 970 902 A2 (SONY CORP [JP])<br>17 September 2008 (2008-09-17)<br><br>paragraph [0002]<br>paragraph [0054]<br>paragraph [0090] - paragraph [0115]<br>paragraph [0192] - paragraph [0193]<br>paragraph [0247] - paragraph [0271]<br>claims 1-4<br>figures 4,5<br>-----<br>US 7 454 353 B2 (FRAUNHOFER GESELLSCHAFT<br>ZUR FÖRDERUNG DER ANGEWANDTEN FORSCHUNG<br>E.V.) 18 November 2008 (2008-11-18)<br><br>column 1, line 43 - line 54<br>-----<br>-/- | 1,3,<br>7-11,13,<br>16-31,<br>33,37-40<br><br>1,2,<br>7-12,<br>16-32,<br>37-40 |

| X         |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                |

|                                                                                                |                                                              |

|------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| <input checked="" type="checkbox"/> Further documents are listed in the continuation of Box C. | <input checked="" type="checkbox"/> See patent family annex. |

|------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

\* Special categories of cited documents :

- "A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier document but published on or after the international filing date

- "L" document which may throw doubts on priority, claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- "O" document referring to an oral disclosure, use, exhibition or other means

- "P" document published prior to the international filing date but later than the priority date claimed

"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

"&" document member of the same patent family

|                                                           |                                                    |

|-----------------------------------------------------------|----------------------------------------------------|

| Date of the actual completion of the international search | Date of mailing of the international search report |

|-----------------------------------------------------------|----------------------------------------------------|

|                 |            |

|-----------------|------------|

| 3 February 2011 | 18/02/2011 |

|-----------------|------------|

|                                                                                                                                                                    |                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Name and mailing address of the ISA/<br>European Patent Office, P.O. 5818 Patentlaan 2<br>NL-2280 HV Rijswijk<br>Tel. (+31-70) 340-2040,<br>Fax: (+31-70) 340-3016 | Authorized officer |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

|             |

|-------------|

| Marquart, N |

|-------------|

## INTERNATIONAL SEARCH REPORT

|                              |

|------------------------------|

| International application No |

| PCT/US2010/054147            |

## C(Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                   | Relevant to claim No.                  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| X         | JP 2005 128175 A (KOBÉ STEEL LTD)<br>19 May 2005 (2005-05-19)<br><br>the whole document<br>-----                                                                                                                                                                                                     | 1,4,<br>7-11,14,<br>16-31,<br>34,37-40 |

| X         | MEHR A. S.: "Alias-component matrices of<br>multirate systems",<br>IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS<br>II: EXPRESS BRIEFS,<br>12 May 2009 (2009-05-12), pages 489-493,<br>XP002620290,<br>ISSN: 1549-7747, DOI:<br>10.1109/TCSII.2009.2020927<br>* abstract<br>page 489 - page 490<br>----- | 1,5,<br>7-11,<br>15-31,<br>35,37-40    |

| X         | EP 2 101 506 A2 (FUJITSU LTD [JP])<br>16 September 2009 (2009-09-16)<br><br>the whole document<br>-----                                                                                                                                                                                              | 1,6-11,<br>16-31,<br>36-40             |

| X         | WO 2007/095664 A1 (DYNAMIC HEARING PTY LTD<br>[AU]; DICKSON BONAR [AU]; STEELE BRENTON<br>ROBER) 30 August 2007 (2007-08-30)<br>page 3, line 7 - page 4, line 12<br>-----                                                                                                                            | 1,11,21,<br>31                         |

## INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No

PCT/US2010/054147

| Patent document cited in search report |    | Publication date |    | Patent family member(s) |  | Publication date |