(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-235860

(P2005-235860A)

(43) 公開日 平成17年9月2日(2005.9.2)

(51) Int.Cl.<sup>7</sup>

H01L 21/3205

F 1

H01L 21/88

テーマコード(参考)

H01L 21/60

H01L 23/12

T

5 F O 3 3

H01L 23/12

H01L 21/92

6 O 3 D

H01L 21/92

6 O 4 C

H01L 21/88

J

審査請求 未請求 請求項の数 16 O L (全 10 頁)

(21) 出願番号

特願2004-40409 (P2004-40409)

(22) 出願日

平成16年2月17日 (2004.2.17)

(出願人による申告) 国等の委託研究の成果に係る特許出願(平成13年度新エネルギー・産業技術総合開発機構からの委託研究「超高密度電子S-I技術の研究開発(エネルギー使用合理化技術開発)」)、産業活力再生特別措置法30条の適用を受けるもの

(71) 出願人 000001889

三洋電機株式会社

大阪府守口市京阪本通2丁目5番5号

(74) 代理人 100107906

弁理士 須藤 克彦

(72) 発明者 亀山 工次郎

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

(72) 発明者 鈴木 彰

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

(72) 発明者 岡山 芳央

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

最終頁に続く

(54) 【発明の名称】 半導体装置及びその製造方法

## (57) 【要約】

【課題】 エッチング工程の増加を抑えつつ、半導体装置の電気的特性の劣化を極力抑止可能な半導体装置及びその製造方法を提供する。

【解決手段】 本発明の半導体装置は、半導体基板10の表面に、第1のバリア層12とアルミニウム層が積層されて成るパッド電極層14が形成されていることを特徴とする。また、半導体基板10の表面には支持基板16が接着されている。半導体基板10の裏面、及び半導体基板10の裏面から第1のバリア層12に到達するビアホール18内に、第2のバリア層19が形成されている。さらに、ビアホール18内を完全もしくは不完全に埋め込むようにして、再配線層21が形成されている。再配線層21上には、ボール状端子22が形成されている。

【選択図】 図4

**【特許請求の範囲】****【請求項 1】**

半導体チップの表面に形成され、かつ、第1のバリア層とアルミニウム層又はアルミニウム合金層が積層されて成るパッド電極層と、

前記半導体チップの表面に接着された支持基板と、

前記半導体チップの裏面から前記第1のバリア層に到達するピアホールと、

前記ピアホール内を含む前記半導体チップの裏面に形成され、かつ前記第1のバリア層と接続された再配線層と、

を有することを特徴とする半導体装置。

**【請求項 2】**

前記再配線層は、前記ピアホール内を完全に埋め込むようにして形成されていることを特徴とする請求項1記載の半導体装置。 10

**【請求項 3】**

前記再配線層は、前記ピアホール内を不完全に埋め込むようにして形成されていることを特徴とする請求項1記載の半導体装置。

**【請求項 4】**

前記再配線層は、メッキ処理またはスパッタ処理により形成されていることを特徴とする請求項1, 2, 3のうちいずれか1項に記載の半導体装置。

**【請求項 5】**

前記再配線層上に導電端子が形成されていることを特徴とする請求項1, 2, 3, 4のうちいずれか1項に記載の半導体装置。 20

**【請求項 6】**

前記第1のバリア層は、チタンナイトライド層、チタンタングステン層、タンタルナイトライド層、高融点金属層及びその化合物層のいずれかから成ることを特徴とする請求項1, 2, 3, 4, 5のうちいずれか1項に記載の半導体装置。

**【請求項 7】**

前記ピアホール内を含む前記半導体チップの裏面と前記再配線層との間に、第2のバリア層が形成されていることを特徴とする請求項1, 2, 3, 4, 5, 6のうちいずれか1項に記載の半導体装置。

**【請求項 8】**

前記第2のバリア層は、チタンナイトライド層、チタンタングステン層、タンタルナイトライド層、高融点金属層及びその化合物層のいずれかから成ることを特徴とする請求項7記載の半導体装置。 30

**【請求項 9】**

第1のバリア層とアルミニウム層又はアルミニウム合金層が積層されて成るパッド電極層を有する半導体基板を準備し、

前記半導体基板の表面に支持基板を接着する工程と、

前記半導体基板に、当該半導体基板の裏面から前記第1のバリア層に到達するピアホールを形成する工程と、

前記ピアホール内を含む前記半導体基板の裏面に、前記第1のバリア層と接続する再配線層を形成する工程と、 40

を有することを特徴とする半導体装置の製造方法。

**【請求項 10】**

前記再配線層を形成する工程において、前記再配線層は、前記ピアホール内を完全に埋め込むようにして形成されることを特徴とする請求項9記載の半導体装置の製造方法。

**【請求項 11】**

前記再配線層を形成する工程において、前記再配線層は、前記ピアホール内を不完全に埋め込むようにして形成されることを特徴とする請求項10記載の半導体装置の製造方法。

**【請求項 12】**

前記再配線層を形成する工程において、前記再配線層は、メッキ処理またはスパッタ処理 50

により形成されることを特徴とする請求項 9, 10, 11 のうちいずれか 1 項に記載の半導体装置。

【請求項 13】

前記再配線層上に導電端子を形成する工程を含むことを特徴とする請求項 9, 10, 11, 12 のうちいずれか 1 項に記載の半導体装置の製造方法。

【請求項 14】

前記第 1 のバリア層は、チタンナイトライド層、チタンタングステン層、タンタルナイトライド層、高融点金属層及びその化合物層のいずれかから成ることを特徴とする請求項 9, 10, 11, 12, 13 のうちいずれか 1 項に記載の半導体装置の製造方法。

【請求項 15】

前記ビアホール内を含む前記半導体基板の裏面と前記再配線層との間に、第 2 のバリア層を形成する工程を含むことを特徴とする請求項 9, 10, 11, 12, 13, 14 のうちいずれか 1 項に記載の半導体装置の製造方法。

【請求項 16】

前記第 2 のバリア層は、チタンナイトライド層、チタンタングステン層、タンタルナイトライド層、高融点金属層及びその化合物層のいずれかから成ることを特徴とする請求項 15 記載の半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関し、特に、半導体基板に貫通ビアホールが形成されて成る半導体装置及びその製造方法に関する。

【背景技術】

【0002】

従来より、半導体チップの外形寸法と略同サイズの外形寸法を有するチップサイズパッケージの一種として、BGA (Ball Grip Array) 型の半導体装置が知られている。この BGA 型の半導体装置は、この BGA 型の半導体装置は、半田等の金属部材からなるボール状端子をパッケージの一主面上に格子状に複数配列し、パッケージの他方の面上に形成される半導体チップと電気的に接続したものである。

【0003】

そして、この BGA 型の半導体装置を電子機器に組み込む際には、各ボール状端子をプリント基板上の配線パターンに圧着することで、半導体チップとプリント基板に搭載される外部回路とを電気的に接続している。

【0004】

このような BGA 型の半導体装置は、側部に突出したリードピンを有する SOP (Small Outline Package) や QFP (Quad Flat Package) 等の他の型のチップサイズパッケージに比して、多数のボール状端子を設けることが出来、しかも小型化できるという長所を有する。BGA 型の半導体装置は、例えば携帯電話機に搭載されるデジタルカメラのイメージセンサチップとしての用途がある。この例では、半導体チップの一主面上もしくは両主面上に、例えばガラスから成る支持基板が接着される。なお、関連する技術文献としては、以下の特許文献 1 が挙げられる。

【0005】

次に、半導体チップに 1 枚の支持基板が接着されて成る場合の従来例に係る BGA 型の半導体装置及びその製造方法について、図面を参照して説明する。

【0006】

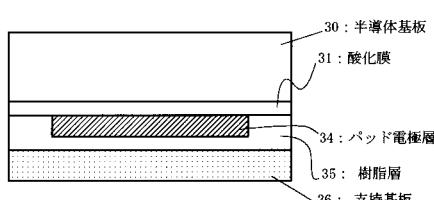

図 5 乃至図 7 は、イメージセンサチップに適用可能な従来例に係る BGA 型の半導体装置及びその製造方法を示す断面図である。最初に、図 5 に示すように、半導体基板 30 上の表面に、絶縁膜、例えば酸化膜 31 を介してアルミニウム層またはアルミニウム合金層から成るパッド電極層 34 を形成する。そしてパッド電極層 34 を含む半導体基板 30 の表面に、樹脂層 35 を介して例えばガラスから成る支持基板 36 を接着する。

10

20

30

40

50

**【 0 0 0 7 】**

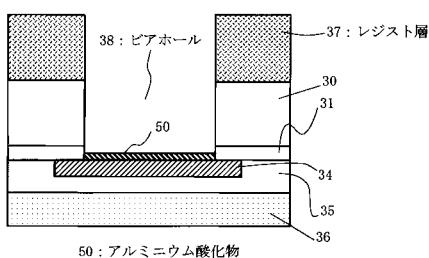

次に、図6に示すように、パッド電極層34に対応する半導体基板30の裏面に開口部を有したレジスト層37を形成し、これをマスクとして、ドライエッティングを半導体基板30に対して行い、半導体基板30の裏面からパッド電極層34に到達するビアホール38を形成する。ここで、上記エッティングにより形成したビアホール38底部のパッド電極層34の一部上には、エッティングの際に生成されるアルミニウム酸化物50（例えばAl<sub>2</sub>O<sub>3</sub>化合物）が形成される。

**【 0 0 0 8 】**

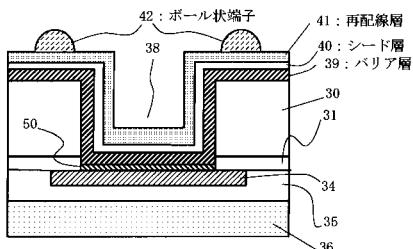

そして、図7に示すように、ビアホール38内を含む半導体基板30の裏面にバリア層39を形成する。さらに、バリア層39上にメッキ用のシード層40を形成し、そのシード層40上でメッキ処理を行って、例えば銅(Cu)から成る再配線層41を形成する。さらに、再配線層41上に保護層(図示せず)を形成し、保護層の所定位置に開口を設けて再配線層41とコンタクトするボール状端子42を形成する。

**【 0 0 0 9 】**

その後、図示しないが、半導体基板及びそれに積層された上記各層を切断して、個々の半導体チップに分離する。こうして、パッド電極層34とボール状端子42とが電気的に接続されたBGA型の半導体装置が形成される。

**【特許文献1】特許公表2002-512436号公報****【発明の開示】****【発明が解決しようとする課題】****【 0 0 1 0 】**

しかしながら、上記エッティングによりビアホール38を形成した際に、その底部に形成されたアルミニウム酸化物50は、パッド電極層34の一部上に形成されるため、パッド電極層34と再配線層41との間の抵抗を高抵抗に至らしめていた。また、アルミニウム酸化物50は、再配線層41に対するパッド電極層34の被覆性を劣化させるため、再配線層41に断線等の損傷を生じ易くさせていた。従って、半導体装置の特性が劣化するという問題が生じていた。

**【 0 0 1 1 】**

そこで、このアルミニウム酸化物50を再度エッティング等により除去することが考えられるが、この場合、エッティング工程が増すことにより製造プロセスが煩雑になるという問題が生じていた。

**【 0 0 1 2 】**

そこで、本発明は、エッティング工程を増加させることなく、電気的特性の劣化を極力抑止し得る半導体装置及びその製造方法を提供するものである。

**【課題を解決するための手段】****【 0 0 1 3 】**

本発明の半導体装置は、上記課題に鑑みて為されたものであり、半導体チップの表面に形成され、かつ、第1のバリア層とアルミニウム層又はアルミニウム合金層が積層されて成るパッド電極層と、半導体チップの表面に接着された支持基板と、半導体チップの裏面から第1のバリア層に到達するビアホールと、ビアホール内を含む半導体チップの裏面に形成され、かつ第1のバリア層と接続された再配線層と、を有することを特徴とする。

**【 0 0 1 4 】**

また、本発明の半導体装置は、上記構成に加えて、再配線層は、ビアホール内を完全に、もしくは不完全に埋め込むようにして形成されていることを特徴とする。

**【 0 0 1 5 】**

また、本発明の半導体装置は、上記再配線層は、メッキ処理またはスパッタ処理により形成されている。

**【 0 0 1 6 】**

また、本発明の半導体装置は、再配線層上に導電端子が形成されていることを特徴とする。

**【 0 0 1 7 】**

また、本発明の半導体装置は、ピアホール内を含む半導体チップの裏面と再配線層との間に、第2のバリア層が形成されていることを特徴とする。

**【 0 0 1 8 】**

また、本発明の半導体装置の製造方法は、第1のバリア層とアルミニウム層又はアルミニウム合金層が積層されて成るパッド電極層を有する半導体基板を準備し、半導体基板の表面に支持基板を接着する工程と、半導体基板に当該半導体基板の裏面から第1のバリア層に到達するピアホールを形成する工程と、ピアホール内を含む半導体基板の裏面に、第1のバリア層と接続する再配線層を形成する工程と、を有することを特徴とする。

**【 0 0 1 9 】**

また、本発明の半導体装置の製造方法は、上記再配線層を形成する工程において、再配線層は、ピアホール内を完全に、もしくは不完全に埋め込むようにして形成されることを特徴とする。

**【 0 0 2 0 】**

また、本発明の半導体装置の製造方法は、再配線層を形成する工程において、前記再配線層はメッキ処理またはスパッタ処理により形成されることを特徴とする。

**【 0 0 2 1 】**

また、本発明の半導体装置の製造方法は、上記工程に加え、再配線層上に導電端子を形成する工程を含むことを特徴とする。

**【 0 0 2 2 】**

また、本発明の半導体装置の製造方法は、上記工程に加え、ピアホール内を含む半導体基板の裏面と再配線層との間に、第2のバリア層を形成する工程を含むことを特徴とする。

**【 発明の効果 】****【 0 0 2 3 】**

本発明の半導体装置及びその製造方法によれば、アルミニウム層又はアルミニウム合金層と第1のバリア層を積層することにより、パッド電極層を形成した。これにより、エッチングによりピアホールを形成する際に、従来のようなピアホールの底部に位置するパッド電極層上に、アルミニウム酸化物が形成されることが回避される。従って、パッド電極層と再配線層との間が高抵抗となることがなくなり、再配線層に断線等の損傷の発生を極力抑止することができる。その結果、上記ピアホールの形成による半導体装置の電気的特性の劣化を極力抑止することが可能となる。また、アルミニウム酸化物を除去するためのエッチング工程が必要なくなる。

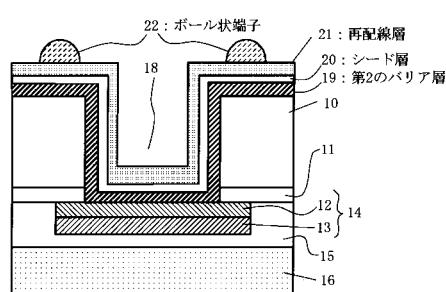

**【 発明を実施するための最良の形態 】****【 0 0 2 4 】**

次に、本実施形態に係る半導体装置の構造について、図面を参照して説明する。図4は、本実施形態に係る半導体装置のうち、後述するパッド電極層が存在する領域の断面を示しており、個々の半導体チップに分離する以前の状態を示している。

**【 0 0 2 5 】**

図4に示すように、S1から成る半導体基板10（後に分離されて個々の半導体チップとなる）の表面上に、絶縁膜、例えば酸化膜11を介して第1のバリア層12上にアルミニウム層13（もしくはアルミニウム合金層）が積層されて成るパッド電極層14が形成されている。即ち、第1のバリア層12は、半導体チップ10に近い方の層として形成されている。

**【 0 0 2 6 】**

なお、半導体基板10には、不図示の回路が形成されており、パッド電極層14は、上記回路と電気的に接続されている。上記不図示の回路は、例えばCCD（Charge Coupled Device）イメージセンサとして形成されている。この場合、CCDイメージ（画像）の基準点となるオプティカル・ブラック領域が必要となるため、パッド電極層14を構成するアルミニウム層13は、光（赤外線）を遮光し得るピュア・アル

ミニウムから成ることが好ましく、Al-Cu層でも良い。もしくは、赤外線を透過するするシリコン(Si)を含む合金(例えばAl-Si, Al-Si-Cu等)以外の金属であることが好ましい。

#### 【0027】

また、第1のバリア層12は、例えばチタンナイトライド(TiN)層であることが好ましい。もしくは、第1のバリア層12は、高融点金属層やその化合物層であれば、チタンナイトライド層以外の金属から成るものであっても良く、タンタル(Ta)層、チタンタングステン(TiW)層、タンタルナイトライド(TaN)層等でも良い。

#### 【0028】

さらに、半導体基板10の表面上に、樹脂層15(接着剤として機能する)を介して、

10 例えば所定の波長帯の光を透過し得るガラスから成る支持基板16が接着されている。そして、半導体基板10のうち、パッド電極層14が存在する領域には、半導体基板10の裏面から、パッド電極層14の第1のバリア層12に到達するピアホール18が形成されている。そして、このピアホール18内を含む半導体基板10の裏面上に、ピアホール18から露出する半導体基板10の側壁を絶縁するために形成した絶縁層を介してそれらを覆うようにして、第2のバリア層19が形成されている。この第2のバリア層19は、例えばチタンナイトライド層であることが好ましい。もしくは、第2のバリア層19は、第1のバリア層と同様にチタンナイトライド層以外の金属から成るものであってもよい。

#### 【0029】

そして、第2のバリア層19上には、メッキ用のシード層20と、メッキ処理により成膜された再配線層21が形成されている。さらに、再線層21上に保護層(図示せず)を形成し、保護層の所定位置に開口を設けて再配線21とコンタクトするボール状端子22が形成されている。即ち、このボール状端子22は、再配線層21、シード層20、第2のバリア層19を介して、パッド電極層14と電気的に接続されている。

#### 【0030】

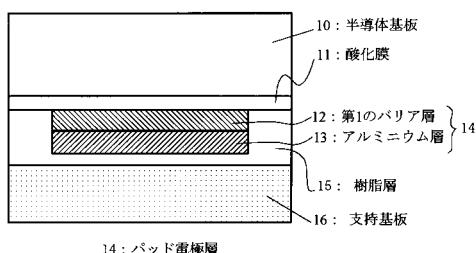

次に、上述した本実施形態に係る半導体装置の製造方法について、図面を参照して説明する。図1乃至図4は、本実施形態に係る半導体装置の製造方法を示す断面図である。図1乃至図4は、パッド電極層14が存在する領域の断面を示しており、個々の半導体チップに分離する以前の状態を示している。

#### 【0031】

最初に、図1に示すように、不図示の回路が形成された半導体基板10(後に分離され個々の半導体チップとなる)の表面上に、絶縁層、例えば酸化膜11を介して、第1のバリア層12上にアルミニウム層13もしくはアルミニウム合金層が積層されて成るパッド電極層14が形成される。即ち、第1のバリア層12は、半導体チップ10に近い方の層として形成される。

#### 【0032】

ここで、上記不図示の回路が、例えばCCDイメージセンサである場合、パッド電極層14を構成するアルミニウム層13は、ピュア・アルミニウムから成ることが好ましい。そして、アルミニウム層13は、光(赤外線)を遮光し得るような厚さ(例えば2μm)で形成されることが好ましい。また、第1のバリア層12は、例えばチタンナイトライド(TiN)層であることが好ましく、本実施形態では250の設定温度のスパッタ装置を用いてチタンナイトライド(TiN)層をスパッタ形成している。もしくは、第1のバリア層12は、前述したように高融点金属やその化合物であれば、チタンナイトライド以外の金属から成るものであってもよい。

#### 【0033】

そして、半導体基板10の表面上に、樹脂層15(接着剤として機能する)を介して、

40 例えばガラスから成る支持基板16が接着される。

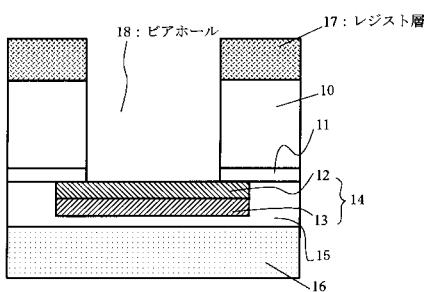

#### 【0034】

次に、図2に示すように、半導体基板10の裏面上において、パッド電極層14が存在する位置の一部上を開口するレジスト層17を形成する。そして、レジスト層17をマス

クとして半導体基板 10 対してエッティングを行うことにより、半導体基板 10 の裏面から、パッド電極層 14 の第 1 のバリア層 12 に到達するビアホール 18 が形成される。その際のエッティングは、半導体基板 10 がシリコン (Si) から成る場合、例えば SF<sub>6</sub> もしくは O<sub>2</sub> もしくは C<sub>4</sub>F<sub>8</sub> 等を含むエッティングガスを用いてドライエッティングにより行われることが好ましい。

#### 【0035】

ここで、ビアホール 18 の底部に位置するパッド電極層 14 の面は第 1 のバリア層 12 となっているため、上記エッティングはアルミニウム層 13 にまで及ばない。従って、従来例の半導体装置を示す図 6 にみられたようなアルミニウム酸化物 50 (例えば Al<sub>2</sub>O<sub>3</sub> 化合物) などの酸化物が形成されることはない。

10

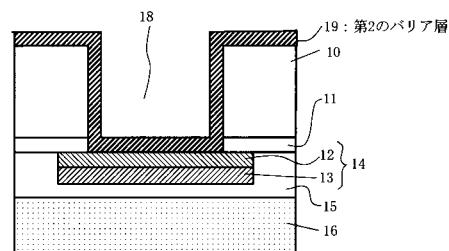

#### 【0036】

次に、レジスト層 17 を除去した後、図 3 に示すように、ビアホール 18 内を含む半導体基板 10 の裏面上に、それらを覆うようにして酸化膜等から成る絶縁層を形成し、第 1 のバリア層 12 上の絶縁層を除去した後に、全面に第 2 のバリア層 19 が形成される。この第 2 のバリア層 19 は、例えばチタンナイトライド層であることが好ましく、本実施形態では 200 以下の CVD 装置内で CVD 法でチタンナイトライド層を形成している。もしくは、前述したように第 2 のバリア層 19 は、高融点金属やその化合物であれば、チタンナイトライド層以外の金属から成るものであってもよい。なお、第 2 のバリア層 19 の形成前もしくは形成後に、半導体基板 10 もしくは第 2 のバリア層 19 上に、ボール状端子 22 に加わる力を緩和するための不図示の緩衝部材を形成してもよい。ここで、第 1 のバリア層 12 上の絶縁層 (例えば酸化膜) をエッティング除去する際に第 1 のバリア層 12 によりアルミニウム層 13 は露出しないため、アルミニウム酸化物は形成されない。

20

#### 【0037】

次に、図 4 に示すように、第 2 のバリア層 19 上の全面に再配線層 21 が形成される。その際、まず、第 2 のバリア層 19 上の全面に、例えば銅 (Cu) から成るメッキ用のシード層 20 を電界メッキにより形成し、その後、そのシード層 20 に対して無電界メッキ処理を行うことで、例えば銅 (Cu) から成る再配線層 21 を形成する。ここで、再配線層 21 は、ビアホール 18 内を不完全に埋め込むようにして形成される。もしくは、再配線層 21 は、ビアホール 18 内を完全に埋め込むように形成されてもよい。

30

#### 【0038】

さらに、再配線層 21 上に保護層 (図示せず) を形成し、保護層の所定位置に開口を設けた後にスクリーン印刷法によりハンダを印刷してリフローさせることで、前記開口上にボール状端子 22 を形成する。そして、図示しないが、ダイシングラインに沿って、半導体基板 10 及びそれに積層された各層を切断することにより、個々の半導体チップ、即ち本実施形態の半導体装置が完成される。

#### 【0039】

上述したように、本発明の半導体装置及びその製造方法によれば、半導体基板 10 の表面に、第 1 のバリア層 12 (例えばチタンナイトライド層から成る) 上にアルミニウム層 13 もしくはアルミニウム合金層が積層されて成るパッド電極層 14 を形成した。

40

#### 【0040】

これにより、エッティングによりビアホール 18 を形成する際に、第 1 のバリア層 12 の存在によりビアホール 18 の底部に位置するパッド電極層 14 上に、アルミニウム酸化物が形成されることが回避される。従って、パッド電極層 14 と再配線層 21 との間が高抵抗となることが極力回避される。また、再配線層 21 に断線等の損傷の発生を極力抑止することができる。その結果、上記ビアホール 18 の形成による半導体装置の特性の劣化を極力抑止することができる。また、アルミニウム酸化物 50 を除去する必要がなくなるため、エッティング工程を増やす必要がなくなる。

#### 【0041】

なお、本実施形態では、ビアホール 18 を含む半導体基板 10 の裏面に第 2 のバリア層 19 を形成したが、本発明はこれに制限されるものではない。即ち、本発明は、ビアホー

50

ル18を含む半導体基板10の裏面に、第2のバリア層19が形成されずに、前記絶縁層を介して再配線層21が形成されるものであってもよい。

【0042】

また、本実施形態では、再配線層21は、メッキ処理により形成されるものとしたが、本発明はこれに制限されるものではない。即ち、本発明は、メッキ用のシード層20は形成されず、メッキ処理以外の方法により再配線層21が形成されるものであってもよく、例えばアルミニウム(A1)等の金属をスパッタ形成するものでも良い。

【0043】

また、本発明は、ボール状端子22が形成された半導体装置に適用されるものとしたが、本発明はこれに制限されるものではない。即ち、本発明は、半導体基板を貫通するピアホールが形成されて成るものであれば、ボール状端子が形成されない半導体装置にも適用されるものである。例えば、LGA(Land Grid Array)型の半導体装置にも適用される。

【0044】

更に言えば、本発明ではピアホール18を形成する側のアルミニウム層13上に第1のバリア層12を形成しているため、ピアホール開口時のエッチング処理時にアルミニウム層13の表面がオーバーエッチングによりエッチングされることが抑制される。従って、オーバーエッチングにより削られてしまう量を考慮してアルミニウム層13の膜厚を多くする必要がなくなる。

【図面の簡単な説明】

【0045】

【図1】本発明の実施形態に係る半導体装置の製造方法を説明する断面図である。

【図2】本発明の実施形態に係る半導体装置の製造方法を説明する断面図である。

【図3】本発明の実施形態に係る半導体装置の製造方法を説明する断面図である。

【図4】本発明の実施形態に係る半導体装置及びその製造方法を説明する断面図である。

【図5】従来例に係る半導体装置及びその製造方法を説明する断面図である。

【図6】従来例に係る半導体装置及びその製造方法を説明する断面図である。

【図7】従来例に係る半導体装置及びその製造方法を説明する断面図である。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

F ターム(参考) 5F033 HH08 HH10 HH21 HH23 HH32 HH33 JJ11 JJ21 JJ23 JJ32

JJ33 KK11 KK21 KK23 KK32 KK33 MM05 MM13 MM30 NN05

NN07 PP06 PP15 PP27 PP28 QQ07 QQ09 QQ11 QQ37 RR04

TT07 VV07