(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6838829号

(P6838829)

(45) 発行日 令和3年3月3日(2021.3.3)

(24) 登録日 令和3年2月16日(2021.2.16)

(51) Int.Cl.

F 1

|             |           |             |      |

|-------------|-----------|-------------|------|

| HO1L 21/28  | (2006.01) | HO1L 21/28  | Z    |

| HO1L 21/265 | (2006.01) | HO1L 21/265 | F    |

| HO1L 21/822 | (2006.01) | HO1L 21/265 | V    |

| HO1L 27/04  | (2006.01) | HO1L 21/265 | R    |

|             |           | HO1L 21/28  | 301A |

請求項の数 20 (全 15 頁) 最終頁に続く

(21) 出願番号 特願2017-528424 (P2017-528424)

(86) (22) 出願日 平成27年11月24日 (2015.11.24)

(65) 公表番号 特表2018-503976 (P2018-503976A)

(43) 公表日 平成30年2月8日 (2018.2.8)

(86) 國際出願番号 PCT/US2015/062265

(87) 國際公開番号 WO2016/085900

(87) 國際公開日 平成28年6月2日 (2016.6.2)

審査請求日 平成30年11月12日 (2018.11.12)

(31) 優先権主張番号 14/555,300

(32) 優先日 平成26年11月26日 (2014.11.26)

(33) 優先権主張国・地域又は機関

米国(US)

(73) 特許権者 390020248

日本テキサス・インスツルメンツ合同会社

東京都新宿区西新宿六丁目24番1号

(73) 特許権者 507107291

テキサス インスツルメンツ インコーポ

レイテッド

アメリカ合衆国 テキサス州 75265

-5474 ダラス メイル ステイショ

ン 3999 ピーオーボックス 655

474

(74) 上記1名の代理人 100098497

弁理士 片寄 恒三

前置審査

最終頁に続く

(54) 【発明の名称】ディープトレンチ充填のためのポリサンドイッチ

## (57) 【特許請求の範囲】

## 【請求項1】

半導体デバイスであって、

半導体材料と前記半導体材料の上の埋め込み層と前記埋め込み層の上の上側層とを含む基板であって、前記半導体材料と前記上側層とが第1の導電型を有し、前記埋め込み層が第2の導電型を有する、前記基板と、

前記基板におけるディープトレンチ構造であって、

前記基板における少なくとも10ミクロンの深さのディープトレンチであって、前記上側層と前記埋め込み層とを通じて前記半導体材料まで延在する、前記ディープトレンチと、

前記ディープトレンチの側壁上に配置される誘電体ライナーと、

前記誘電体ライナー上に配置され、前記ディープトレンチの底部まで延在する、ポリシリコンの第1の層と、

前記ポリシリコンの第1の層上に配置され、前記ディープトレンチ内に延在する、ポリシリコンの第2の層と、

を含み、

ドーパントが、少なくとも $1 \times 10^{18} \text{ cm}^{-3}$ の平均ドーピング濃度で、前記ポリシリコンの第1の層と前記ポリシリコンの第2の層とにわたって分配され、前記ディープトレンチ構造の幅が、1.5ミクロン～3.5ミクロンである、前記ディープトレンチ構造と、

前記基板における第2の導電型のシンカー領域であって、前記ディープトレンチ構造に隣接して前記埋め込み層まで前記上側層を通じて延在する、前記シンカー領域と、

を含む、半導体デバイス。

【請求項2】

請求項1に記載の半導体デバイスであって、

前記誘電体ライナーが、前記側壁上の熱酸化物の層と前記熱酸化物の層上の堆積された二酸化シリコンの層とを含む、半導体デバイス。

【請求項3】

請求項1に記載の半導体デバイスであって、

前記ディープトレンチ構造が前記基板において20ミクロン～35ミクロンの深さである、半導体デバイス。 10

【請求項4】

請求項1に記載の半導体デバイスであって、

前記ポリシリコンの第1の層が150ナノメートル～200ナノメートルの厚みを有する、半導体デバイス。

【請求項5】

請求項1に記載の半導体デバイスであって、

前記ポリシリコンの第1の層が前記基板の半導体材料への電気的コンタクトを成すよう前記ディープトレンチ構造の底部に前記誘電体ライナーがない、半導体デバイス。 20

【請求項6】

請求項5に記載の半導体デバイスであって、

前記第1の導電型がp型であり、前記第2の導電型がn型であり、前記上側層がエピタキシャル層である、半導体デバイス。

【請求項7】

請求項1に記載の半導体デバイスであって、

前記ポリシリコンの第1の層が、前記ディープトレンチ構造の底部における前記誘電体ライナーにより前記基板から隔離される、半導体デバイス。

【請求項8】

半導体デバイスを形成する方法であって、

半導体材料と前記半導体材料の上の埋め込み層と前記埋め込み層の上の上側層とを含む基板を提供することであって、前記半導体材料と前記上側層とが第1の導電型を有し、前記埋め込み層が第2の導電型を有する、前記基板を提供することと、 30

前記基板にディープトレンチを少なくとも10ミクロンの深さで形成する工程であって、前記ディープトレンチが、前記上側層と前記埋め込み層を通じて前記半導体材料まで延在し、1.5ミクロン～3.5ミクロンの幅を有する、前記ディープトレンチを形成することと、

前記ディープトレンチの側壁上に誘電体ライナーを形成することと、

前記誘電体ライナー上に、前記ディープトレンチ内に延在するようにポリシリコンの第1の層を形成する工程であって、前記ポリシリコンの第1の層がドープされていない層として形成される、前記ポリシリコンの第1の層を形成することと、 40

前記ポリシリコンの第1の層にドーパントを注入することと、

前記ポリシリコンの第1の層上に、前記ディープトレンチ内に延在するようにポリシリコンの第2の層を形成する工程であって、前記ポリシリコンの第2の層がドープされていない層として形成される、前記ポリシリコンの第2の層を形成することと、

前記ポリシリコンの第1の層と前記ポリシリコンの第2の層とにおける平均ドーピング濃度が少なくとも $1 \times 10^{18} \text{ cm}^{-3}$ であるように、前記注入されたドーパントを活性化及び拡散するように、前記基板をアニールすることと、

前記基板に第2の導電型のシンカー領域を形成することであって、前記シンカー領域が前記ディープトレンチに隣接して前記埋め込み層まで前記上側層を通じて延在する、前記シンカー領域を形成することと、 50

を含む、方法。

【請求項 9】

請求項 8 に記載の方法であって、

前記ドーパントが、 $2 \times 10^{15} \text{ cm}^{-2} \sim 1 \times 10^{16} \text{ cm}^{-2}$  のドーズ量で注入される、方法。

【請求項 10】

請求項 8 に記載の方法であって、

前記ドーパントが、1度～2度の傾き角度と約ゼロ度の捩れ角度での4サブドーズで注入される、方法。

【請求項 11】

請求項 8 に記載の方法であって、

前記ポリシリコンの第1の層が150ナノメートル～200ナノメートルの厚みを有する、方法。

【請求項 12】

請求項 8 に記載の方法であって、

前記基板をアニールすることが、窒素雰囲気における100分～150分間の1000～1100でのファーネスアニールを含む、方法。

【請求項 13】

請求項 8 に記載の方法であって、

前記第1の導電型がp型であり、前記第2の導電型がn型である、方法。

10

【請求項 14】

請求項 8 に記載の方法であって、

前記誘電体ライナーを形成することが、前記側壁上に熱酸化物の層を形成することと、熱酸化物の前記層上に堆積された二酸化シリコンの層を形成することとを含む、方法。

【請求項 15】

請求項 8 に記載の方法であって、

前記ポリシリコンの第1の層を形成する前に前記ディープトレンチの底部における前記誘電体ライナーを取り除くことを更に含み、前記ポリシリコンの第1の層が前記ディープトレンチの底部において前記基板への電気的コンタクトを成すように、前記ディープトレンチの底部まで延在するように、前記ポリシリコンの第1の層を形成する、方法。

30

【請求項 16】

請求項 15 に記載の方法であって、

前記ディープトレンチの底部における前記誘電体ライナーを取り除いた後であり、前記ポリシリコンの第1の層を形成する前に、前記ディープトレンチの底部における前記基板の半導体材料内にドーパントを注入することを更に含む、方法。

【請求項 17】

請求項 8 に記載の方法であって、

前記誘電体ライナーが前記ポリシリコンの第1の層を前記基板から隔離するように、前記ポリシリコンの第1の層が前記ディープトレンチの底部まで延在して形成される、方法。

40

【請求項 18】

半導体デバイスを形成する方法であって、

半導体材料と前記半導体材料の上の埋め込み層と前記埋め込み層の上の上側層とを含む基板を提供することであって、前記半導体材料と前記上側層とが第1の導電型を有し、前記埋め込み層が第2の導電型を有する、前記基板を提供することと、

ディープトレンチを前記基板に少なくとも10ミクロンの深さで形成することであって、前記ディープトレンチが、前記上側層と前記埋め込み層とを通じて前記半導体材料まで延在し、1.5ミクロン～3.5ミクロンの幅を有する、前記ディープトレンチを形成することと、

前記ディープトレンチの側壁上に誘電体ライナーを形成することと、

50

前記ディープトレンチの底部における前記誘電体ライナーを取り除くことと、

前記ディープトレンチの底部における前記基板の半導体材料にドーパントを注入することと、

ポリシリコンの第1の層が前記ディープトレンチの底部において前記基板への電気的コンタクトを成すように、前記誘電体ライナー上に前記ディープトレンチの底部まで延在する前記ポリシリコンの第1の層を形成することであって、前記ポリシリコンの第1の層がドープされていない層として形成される、前記ポリシリコンの第1の層を形成することと、

ポリシリコンの前記第1の層にドーパントを注入することと、

ポリシリコンの第2の層が前記ディープトレンチ内に延在するように、前記ポリシリコンの第1の層上に前記ポリシリコンの第2の層を形成することであって、前記ポリシリコンの第2の層がドープされていない層として形成される、前記ポリシリコンの第2の層を形成することと、

前記ポリシリコンの第1の層と前記ポリシリコンの第2の層とにおける平均ドーピング濃度が少なくとも  $1 \times 10^{18} \text{ cm}^{-3}$  であるように、前記注入されたドーパントを活性化及び拡散するように、前記基板をアニールすることと、

前記基板に第2の導電型のシンカー領域を形成することであって、前記シンカー領域が前記ディープトレンチに隣接して前記埋め込み層まで前記上側層を通じて延在する、前記シンカー領域を形成することと、

を含む、方法。

#### 【請求項 19】

請求項18に記載の方法であって、

前記誘電体ライナーを形成することが、前記側壁上に熱酸化物の層を形成することと、熱酸化物の前記層上に堆積された二酸化シリコンの層を形成することとを含む、方法。

#### 【請求項 20】

請求項18に記載の方法であって、

前記第1の導電型がp型であり、前記第2の導電型がn型である、方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本願は、概して半導体デバイスに関し、更に特定して言えば、半導体デバイスにおけるディープトレンチ構造に関連する。

##### 【背景技術】

##### 【0002】

半導体デバイスが、ディープトレンチの側壁上の誘電体ライナーを備えたディープトレンチ構造、及びディープトレンチを充填する誘電体ライナー上のドープされた多結晶シリコン（ポリシリコン）を有する。ディープトレンチにおけるポリシリコンにおいて望ましく低いシート抵抗を得ることは、ポリシリコンが堆積される際のインサイチュド・ピングを必要とし、これは、望ましくないことに、半導体デバイスの基板の裏側のドーパント汚染、及び堆積されたポリシリコンがアニーリングされた後の半導体デバイスにおける応力を生じさせる。これらの望ましくない影響はいずれも、半導体デバイスの性能及び信頼性を劣化させ得る。代替として、ドープされていないポリシリコンが、半導体デバイスの頂部表面において堆積及び注入され得、20ミクロン深さを超えるディープトレンチにおけるドーパント分布の所望の均一性を得るために長い熱駆動が必要とされる。この長い熱駆動は、埋め込み層など、基板におけるドープされた構造に悪影響を与える。

##### 【発明の概要】

##### 【0003】

半導体デバイスが、半導体デバイスの基板においてディープトレンチを形成することにより形成される。ディープトレンチの側壁上に誘電体ライナーが形成される。第1のドープされていないポリシリコン層が、誘電体ライナー上のディープトレンチ内に延在するが

10

20

30

40

50

、ディープトレンチを充填せずに、半導体デバイス上に形成される。第1のポリシリコン層にドーパントが注入される。ポリシリコンの第1の層上にポリシリコンの第2の層が形成される。熱駆動アニールが、ドーパントを活性化及び拡散する。ポリシリコンの第1の層及びポリシリコンの第2の層のポリシリコンは、基板の頂部表面の上から取り除かれる。

【図面の簡単な説明】

【0004】

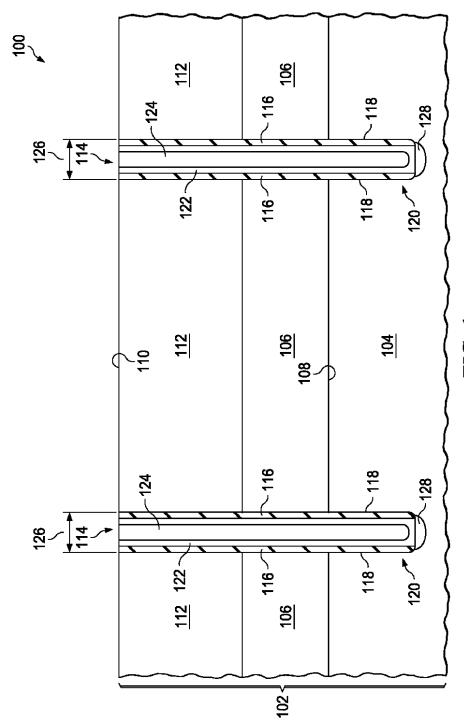

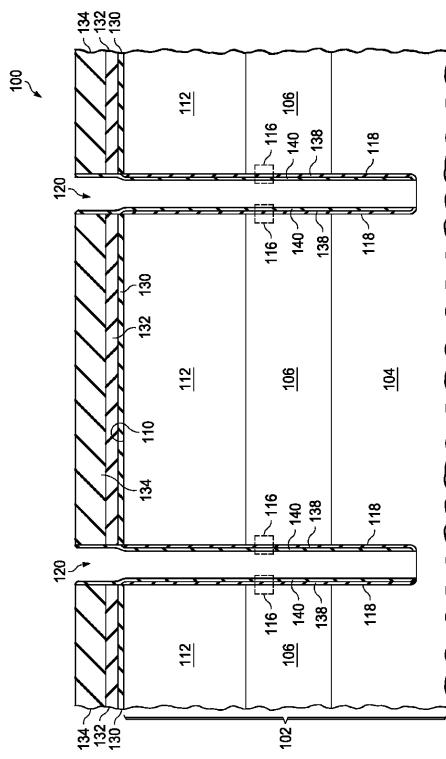

【図1】例示の半導体デバイスの断面である。

【0005】

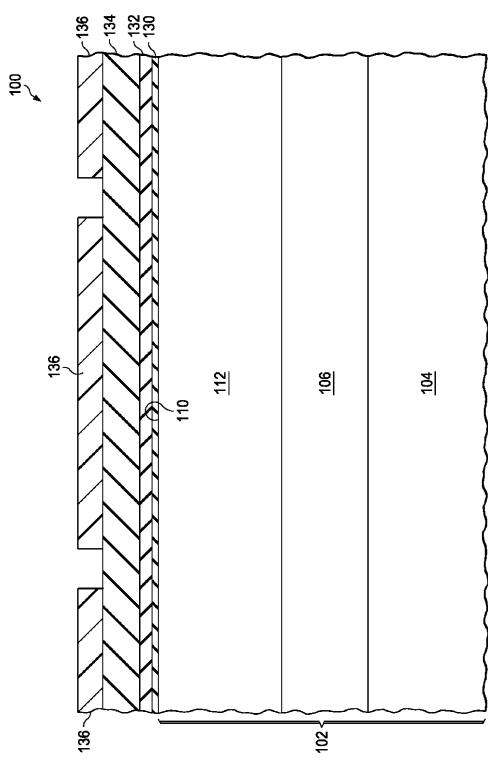

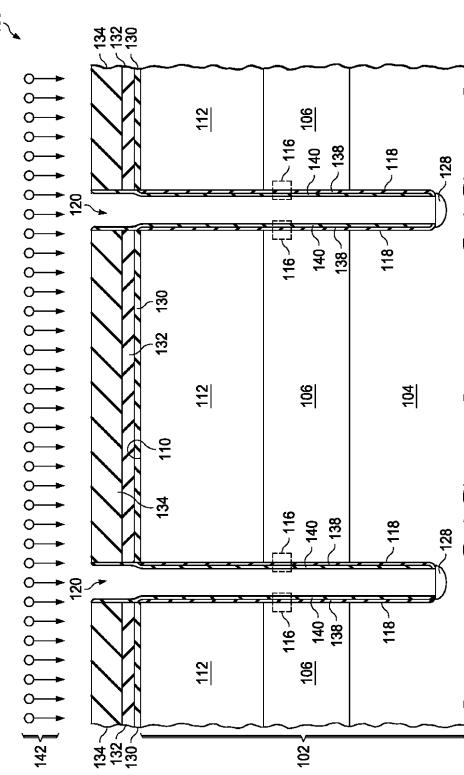

【図2A】製造の連続的段階で示した、図1の半導体デバイスの断面図である。

10

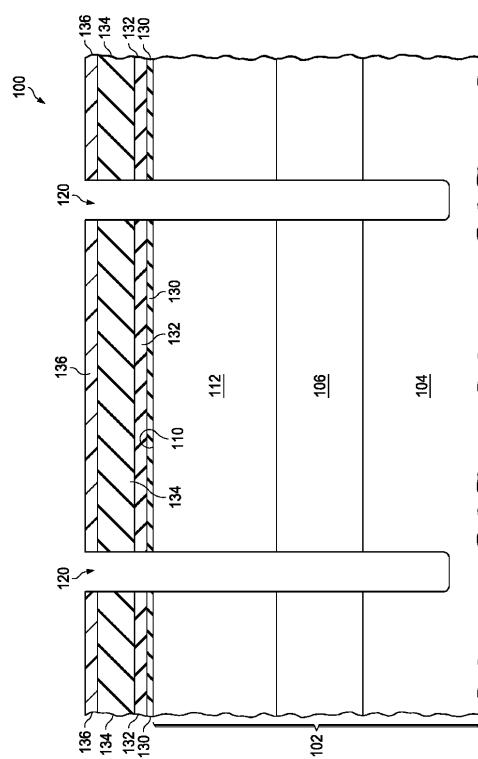

【図2B】製造の連続的段階で示した、図1の半導体デバイスの断面図である。

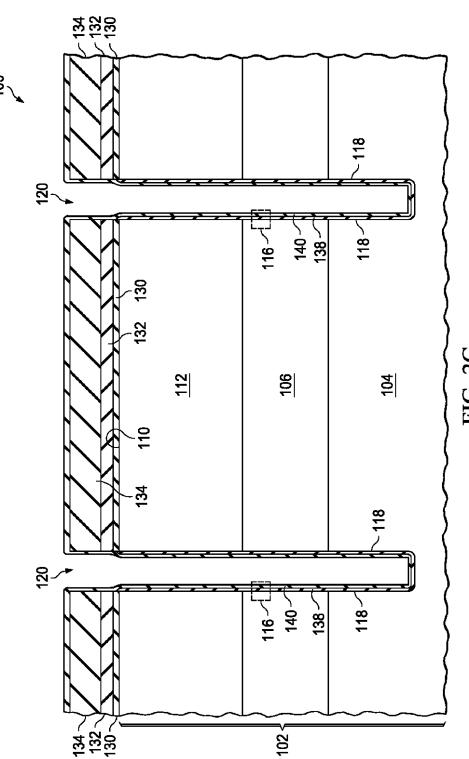

【図2C】製造の連続的段階で示した、図1の半導体デバイスの断面図である。

【図2D】製造の連続的段階で示した、図1の半導体デバイスの断面図である。

【図2E】製造の連続的段階で示した、図1の半導体デバイスの断面図である。

【図2F】製造の連続的段階で示した、図1の半導体デバイスの断面図である。

【図2G】製造の連続的段階で示した、図1の半導体デバイスの断面図である。

【図2H】製造の連続的段階で示した、図1の半導体デバイスの断面図である。

【図2I】製造の連続的段階で示した、図1の半導体デバイスの断面図である。

【図2J】製造の連続的段階で示した、図1の半導体デバイスの断面図である。

【0006】

20

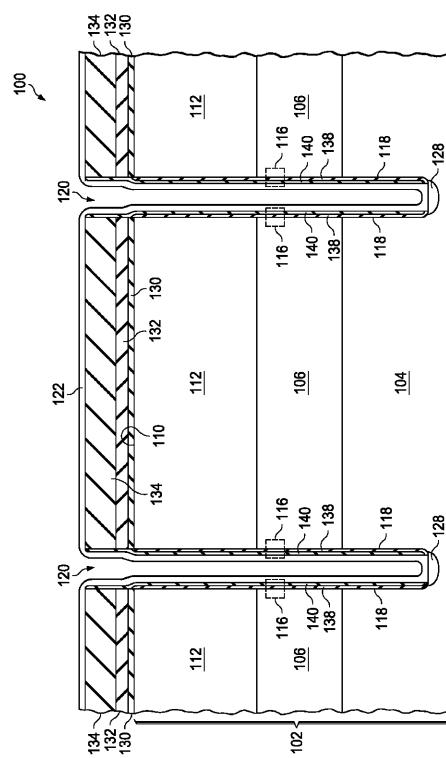

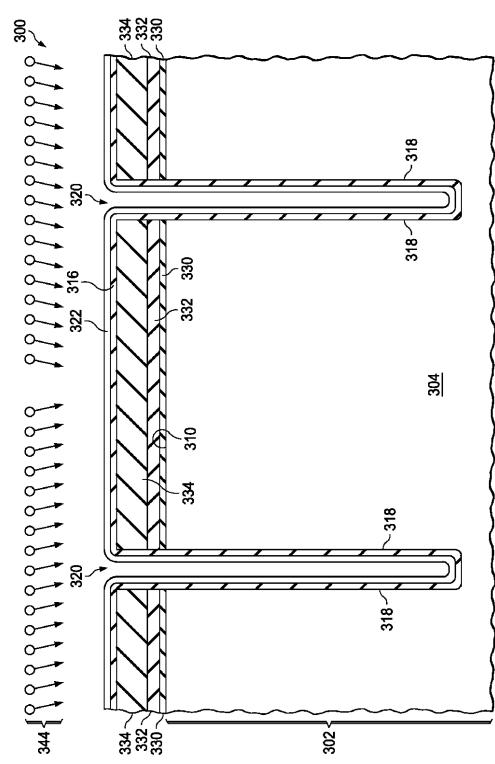

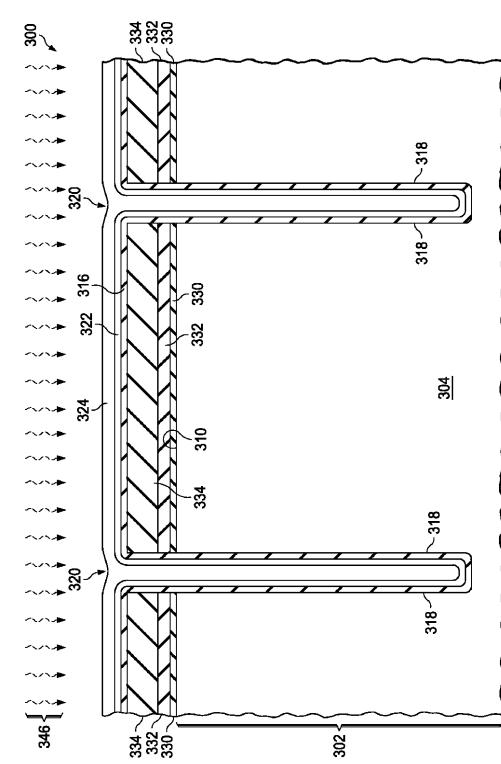

【図3】別の例示の半導体デバイスの断面である。

【0007】

【図4】製造の連続的段階で示した、図3の半導体デバイスの断面図である。

【0008】

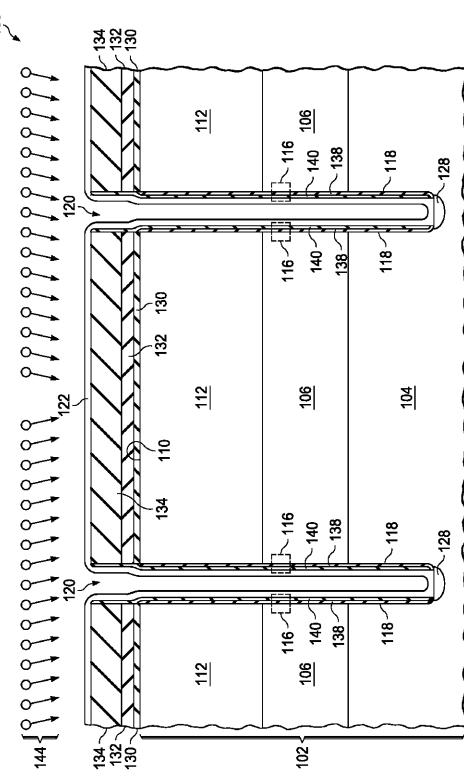

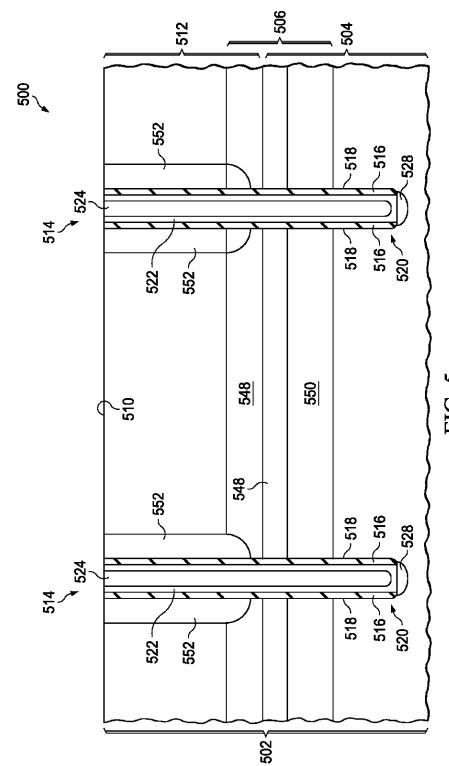

【図5】埋め込み層、及び埋め込み層に対する自己整合シンカーを備えたディープトレンチ構造を含む代替の半導体デバイスの断面である。

【発明を実施するための形態】

【0009】

下記の同時係属中の特許出願が関連しており、参照により本願に組み込まれる。

【特許文献1】米国特許出願番号U.S.14/555,209

30

【特許文献2】米国特許出願番号U.S.14/555,330

【特許文献3】米国特許出願番号U.S.14/555,359

【0010】

図面は一定の縮尺で描いてはいない。幾つかの動作が、異なる順で、及び／又は他の動作又は事象と同時に成され得る。また、例示の実施例に従った方法を実装するために、図示した全ての動作又は事象が必要とされるわけではない。

【0011】

半導体デバイスが、半導体デバイスの基板においてディープトレンチを少なくとも10ミクロンの深さ形成することによって、形成される。ディープトレンチの側壁上に誘電体ライナーが形成される。ポリシリコンの第1のドープされていない層が、半導体デバイス上に形成され、誘電体ライナー上のディープトレンチ内に延在するが、ディープトレンチを充填しない。第1のポリシリコン層にドーパントが注入される。ポリシリコンの第2のドープされていない層が、ポリシリコンの第1の層上に形成される。熱駆動アニールが、ドーパントを活性化し、ドーパントを第1及び第2のポリシリコン層にわたって拡散する。ポリシリコンの第1の層及びポリシリコンの第2の層のポリシリコンは、基板の頂部表面の上から取り除かれる。一例において、誘電体ライナーの誘電性材料が、基板を露出させるように、ディープトレンチの底部において取り除かれ得る。その後、ポリシリコンの第1の層は、埋め込み層の下の領域へなど、ディープトレンチの底部において基板への電気的接続を成す。別の例において、ポリシリコンの第1の層は、誘電体ライナーにより、ディープトレンチの底部において基板から電気的に隔離される。ディープトレンチにおける

40

50

る隔離されたポリシリコンは、半導体デバイスのレジスタ又はキャパシタを提供し得る。

【0012】

本開示の目的のため、半導体デバイス上のポリシリコンの層の形成に適用される際のドープされていないという用語は、ポリシリコン層を形成するために反応性ガスに含まれるドーパントの量が、有意でない量に過ぎないことを意味する。半導体デバイスに既に存在する幾つかのドーパントは、ポリシリコン層が形成されるにつれてポリシリコン層に拡散し得るが、これは、ポリシリコン層の形成のドープされていない性質を打ち消さない。

【0013】

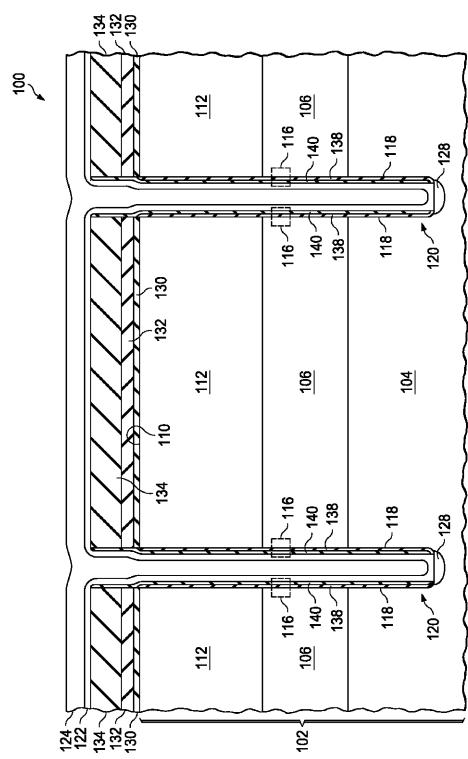

図1は例示の半導体デバイス100の断面であり、半導体デバイス100は、p型シリコンなどの半導体材料104を含む基板102において形成される。n型埋め込み層106などの埋め込み層106が、埋め込み層106の底部表面108が、基板102の頂部表面110よりも10ミクロン以上、下にあるように、基板102に配置され得る。基板102は、p型エピタキシャル層112など、埋め込み層106の上の上側層112を含み得る。この例では、埋め込み層106の下の半導体材料104は、埋め込み層106により上側層112から電気的に隔離され得る。

【0014】

半導体デバイス100は、一つ又は複数のディープトレンチ構造114を含み、ディープトレンチ構造114は、基板102において少なくとも10ミクロンの深さ延在する。各ディープトレンチ構造114は、ディープトレンチ構造114のディープトレンチ120の側壁118上の誘電体ライナー116を含む。ポリシリコンの第1の層122が、誘電体ライナー116上に配置され、ディープトレンチ構造114の底部まで延在する。ポリシリコンの第2の層124が、ポリシリコンの第1の層122上に配置され、ディープトレンチ120内に延在する。ドーパントが、少なくとも $1 \times 10^{18} \text{ cm}^{-3}$ の平均ドーピング濃度で、ポリシリコンの第1の層122及びポリシリコンの第2の層124において分布する。ディープトレンチ構造114の幅126は、1.5ミクロン～3.5ミクロンである。

【0015】

この例では、誘電体ライナー116の誘電性材料がディープトレンチ構造114の底部において取り除かれ、ディープトレンチ構造114の底部において基板102にコンタクト領域128が配置され、そのため、ポリシリコンの第1の層122がコンタクト領域128を介して基板102への電気的接続を成すようにする。コンタクト領域128は、少なくとも $5 \times 10^{18} \text{ cm}^{-3}$ の平均ドーピング濃度を有し得る。そのため、ディープトレンチ構造114は、少なくとも $5 \times 10^{18} \text{ cm}^{-3}$ の平均ドーピング濃度に起因して有利に低い抵抗で、基板102の頂部表面110から埋め込み層106の下の半導体材料104への電気的接続を提供する。ディープトレンチ構造114は、上側層112の一部と上側層112部分における半導体デバイス100の構成要素を囲むように、及びそのためそれらを隔離するように、閉ループ構成を有し得る。

【0016】

図2A～図2Jは、製造の連続的段階で示した、図1の半導体デバイスの断面図である。図2Aを参照すると、半導体材料104上に、埋め込み層106及び上側層112が形成される。埋め込み層106及び上側層112は、n型ドーパントをp型半導体材料104に注入することにより形成され得、その後、注入されたn型ドーパントの拡散及び活性化によって埋め込み層106が形成されるように、p型上側層112を成長させるための熱駆動アニール及び後続のエピタキシャルプロセスが続く。

【0017】

熱酸化などにより、基板の頂部表面110においてパッド酸化物130の層が形成される。パッド酸化物130の層は、5ナノメートル～30ナノメートルの二酸化シリコンを含み得る。アンモニア及びシランを用いる低圧化学気相成長(LPCVD)などにより、パッド酸化物130の層上にパッド窒化物132の層が形成される。パッド窒化物132の層は、100ナノメートル～300ナノメートルのシリコン窒化物を含み得る。テトラ

10

20

30

40

50

エトキシシラン(TEOS)と呼ぶこともあるオルトけい酸テトラエチルを用いるプラズマエンハンスト化学気相成長(PECVD)などにより、又は高密度プラズマ(HDP)プロセスを用いて、パッド窒化物132の層の上にハードマスク酸化物134の層が形成される。ハードマスク酸化物134の層は、500ナノメートル~2ミクロンの二酸化シリコンを含み得る。パッド窒化物132の層は、ハードマスク酸化物134の層の後続のエッティングのためのエッチ停止層を提供する。

【0018】

図1のディープトレンチ構造114のためのエリアを露出させるように、ハードマスク酸化物134の層の上にトレンチマスク136が形成される。トレンチマスク136は、フォトリソグラフィプロセスによって形成されるフォトレジストを含み得、更に、ハードマスク層及び/又は半反射層を含み得る。

10

【0019】

図2Bを参照すると、ハードマスクエッティングプロセスが、トレンチマスク136により露出されたエリアにおいてハードマスク酸化物134の層から材料を取り除く。続いて、停止層エッティングプロセスが、トレンチマスク136により露出されたエリアにおけるパッド窒化物132の層及びパッド酸化物130の層を取り除く。トレンチエッティングプロセスが、ディープトレンチ120を形成するためにトレンチマスク136により露出されたエリアにおいて基板102から材料を取り除き、ディープトレンチ120は、埋め込み層106の底部表面より下まで延在する。幾つかの例において、ディープトレンチ120は、12ミクロン~35ミクロンの深さであり得る。図2Bに示したように有意な部分、及び場合によってはトレンチマスク136の全て、及び場合によってはハードマスク酸化物134の層の一部が、トレンチエッティングプロセスにより腐食され得る。残りのトレンチマスク136がある場合、ディープトレンチ120が形成された後に取り除かれる。

20

【0020】

図2Cを参照すると、ディープトレンチ120の側壁118及び底部上に、熱酸化物138の層が形成される。幾つかの例において、熱酸化物138の層は、50ナノメートル~400ナノメートルの厚みであり得る。準大気圧化学気相成長(SACVD)プロセスなどにより、熱酸化物138の層上に二酸化シリコン140の層が形成される。幾つかの例において、二酸化シリコン140の層は、50ナノメートル~500ナノメートルの厚みであり得る。二酸化シリコン140の層と組み合わされた熱酸化物138の層は、誘電体ライナー116を提供する。

30

【0021】

図2Dを参照すると、誘電体ライナー116は、半導体材料104を露出させるように、ディープトレンチ120の底部において取り除かれる。誘電性材料は、側壁118上の誘電体ライナー116を実質的にそのまま残すフッ素ラジカルを用いる反応性イオンエッティング(RIE)プロセスなどにより取り除かれ得る。

【0022】

図2Eを参照すると、コンタクト領域128を形成するため、ディープトレンチ120の底部において露出された半導体材料104にp型ドーパント142が注入される。ドーパント142は、コンタクト領域128が半導体材料104と同じ導電型であるように選択される。この例では、半導体材料104はp型であり、ドーパント142はボロンを含む。ドーパント142は、実質的にゼロ度の傾き角度で、 $2 \times 10^{14} \text{ cm}^{-2} \sim 2 \times 10^{15} \text{ cm}^{-2}$ の例示のドーズ量で注入され得る。

40

【0023】

図2Fを参照すると、ポリシリコンの第1の層122が、既存の半導体デバイス100上に形成されて、ディープトレンチ120内に延在し、コンタクト領域128への電気的コンタクトを成す。ポリシリコンの第1の層122は、ディープトレンチ120を充填しないように、150ナノメートル~200ナノメートルの厚みを有し得る。幾つかの例において、ポリシリコンの第1の層122は、約200ミリトルの圧力で、500毎分標準立方センチメートル(sccm)~600sccmのシランガス(SiH<sub>4</sub>)を提供する

50

ことによって、約 620 の温度で形成され得る。ポリシリコンの第 1 の層 122 は、形成される際に実質的にドープされておらず、これは、ドープされたポリシリコンを用いるプロセスに比して、有利にも、基板 102 の裏側のドーピング汚染を低減する。

【0024】

図 2 G を参照すると、約ゼロ度の傾き角度及び約 45 度の捩れ (twist) 角度の 4 サブドーズで、 $1 \times 10^{15} \text{ cm}^{-2} \sim 1 \times 10^{16} \text{ cm}^{-2}$  の例示のドーズ量で、ポリシリコンの第 1 の層 122 に p 型ドーパント 144 が注入される。代替として、p 型ドーパント 144 は、約 1 度～2 度の傾き角度及び約ゼロ度の捩れ角度で 4 サブドーズで注入され得る。p 型ドーパント 144 はボロンを含み得、ボロンは有利にも、ガリウム及びインジウムなどの他の一般的な p 型ドーパントより高い拡散係数を有する。p 型ドーパント 144 の総ドーズは、ポリシリコンの第 1 の層 122 及び続いて形成されるポリシリコンの第 2 の層 124 における所望のシート抵抗値を提供するために、ディープトレンチ 120 の深さ及び幅に基づいて選択され得る。 10

【0025】

図 2 H を参照すると、ポリシリコンの第 2 の層 124 が、ポリシリコンの第 1 の層 122 上に形成され、ディープトレンチ 120 内に延在する。ポリシリコンの第 2 の層 124 は、800 ナノメートル～1.5 ミクロンの厚みを有し得、ディープトレンチ 120 を実質的に充填し得る。ポリシリコンの第 2 の層 124 は、図 2 F を参照してポリシリコンの第 1 の層 122 に対して説明されたものと同様のプロセス条件を用いて形成され得る。ポリシリコンの第 2 の層 124 は、形成される際に実質的にドープされておらず、これも、ドープされたシリコン層を用いるプロセスに比して、基板 102 の裏側のドーピング汚染を有利に低減する。 20

【0026】

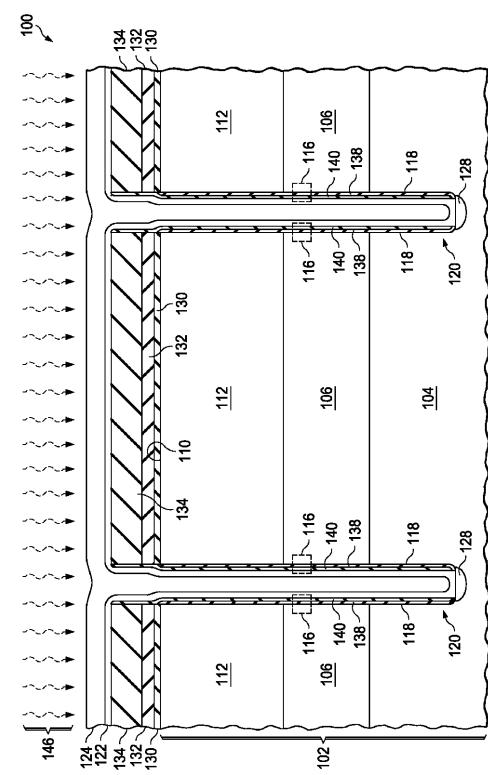

図 2 I を参照すると、図 2 G の注入されたドーパント 144 を活性化するため、及び注入されたドーパント 144 を、ポリシリコンの第 1 の層 122 及びポリシリコンの第 2 の層 124 にわたって拡散するために、熱駆動アニール 146 が基板 102 を加熱する。熱駆動アニールは、窒素雰囲気において 100 分～150 分間の 1000 ～1100 でのファーネスアニールであり得る。熱駆動アニールは有利にも、ポリシリコンの第 1 の層 122 及びポリシリコンの第 2 の層 124 における注入されたドーパント 144 の所望の均一性を提供する。 30

【0027】

図 2 J を参照すると、ポリシリコンの第 2 の層 124、ポリシリコンの第 1 の層 122 、図 2 I のハードマスク酸化物 134 の層、及びパッド窒化物 132 の層の一部が、図 2 J において CMP パッド 148 として示される化学機械研磨 (CMP) プロセス 148 を用いて取り除かれる。その後、パッド窒化物 132 の残りの層、及びパッド酸化物 130 の層が、図 1 の構造を提供するために取り除かれる。代替として、パッド酸化物 130 の層は、後続の注入及びアニールの間その場に残され得、その後、製造プロセスにおいて取り除かれ得る。

【0028】

この例の代替のバージョンにおいて、基板において n 型半導体材料を備える類似の半導体デバイスが、リンなどの n 型ドーパントを、ポリシリコンの第 1 の層に注入することによって形成され得る。結果のディープトレンチ構造は、半導体デバイスの頂部表面から、基板における n 型半導体材料までの、電気的接続を提供する。 40

【0029】

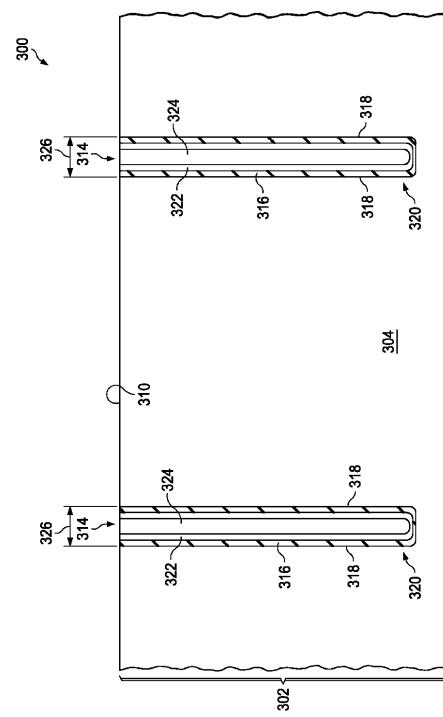

図 3 は、別の例示の半導体デバイス 300 の断面であり、これは、シリコンなどの半導体材料 304 を含む基板 302 において形成される。半導体デバイス 300 は、一つ又は複数のディープトレンチ構造 314 を含み、ディープトレンチ構造 314 は、基板 302 の頂部表面 310 より少なくとも 10 ミクロン下へ延在する。各ディープトレンチ構造 314 は、ディープトレンチ構造 314 のディープトレンチ 320 の側壁 318 及び底部上の誘電体ライナー 316 を含む。ポリシリコンの第 1 の層 322 が、誘電体ライナー 31 50

6 上に配置され、ディープトレンチ構造 314 の底部まで延在する。ポリシリコンの第 1 の層 322 上に、ポリシリコンの第 2 の層 324 が配置される。ドーパントが、少なくとも  $1 \times 10^{18} \text{ cm}^{-3}$  の平均ドーピング濃度で、ポリシリコンの第 1 の層 322 及びポリシリコンの第 2 の層 324 において分布する。ディープトレンチ構造 314 の幅 326 は、1.5 ミクロン～3.5 ミクロンである。

#### 【0030】

この例では、誘電体ライナー 316 は、ポリシリコンの第 1 の層 322 を基板 302 から隔離する。ディープトレンチ構造 314 は、レジスタ又はキャパシタを提供し得、これらは有利にも、半導体デバイス 300 の多くの表面空間を占有せず、低減されたサイズを、及びそのため一層低い製造コストを可能にする。

10

#### 【0031】

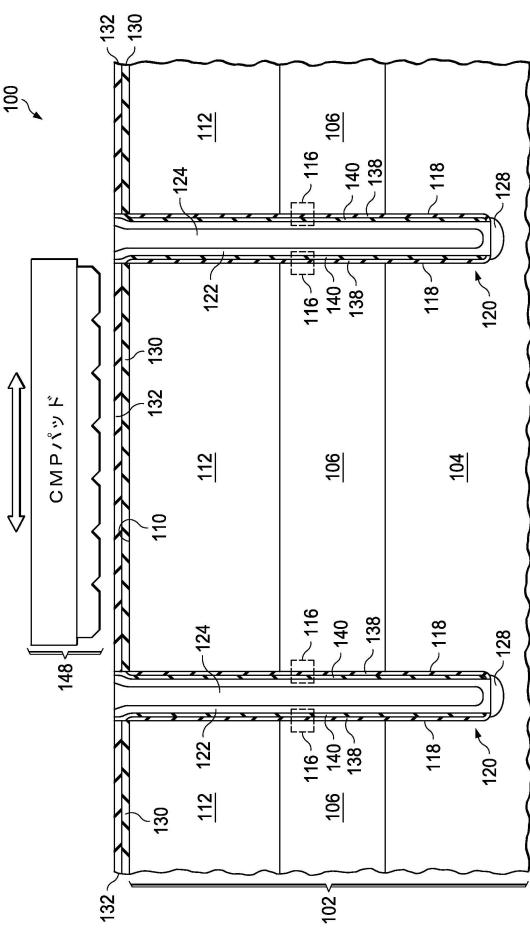

図 4A 及び図 4B は、製造の連続的段階で示した、図 3 の半導体デバイスの断面図である。図 4A を参照すると、パッド酸化物 330 の層が、基板の頂部表面 310 において形成される。パッド酸化物 330 の層上に、パッド窒化物 332 の層が形成される。パッド窒化物 332 の層の上に、ハードマスク酸化物 334 の層が形成される。ハードマスク酸化物 334 の層、パッド窒化物 332 の層、及びパッド酸化物 330 の層は、図 2A を参照して説明したように形成され得る。ディープトレンチ 320 は、ハードマスク酸化物 334 の層、パッド窒化物 332 の層、及びパッド酸化物 330 の層を介して、及び少なくとも 10 ミクロン基板 302 内に、形成される。幾つかの例において、ディープトレンチ 320 は、12 ミクロン～35 ミクロンの深さであり得る。ディープトレンチ 320 は、図 2B を参照して説明したように形成され得る。誘電体ライナー 316 が、ハードマスク酸化物 334 の層の上に形成され、ディープトレンチ 320 の側壁 318 上に延在する。誘電体ライナーは、図 2C を参照して説明したように、熱酸化物の層及び堆積された酸化物の層を含み得、又は他の方法により形成され得る。ポリシリコンの第 1 の層 322 は、誘電体ライナー 316 上に形成され、ディープトレンチ 320 内に延在する（がディープトレンチ 320 を充填はしない）。ポリシリコンの第 1 の層 322 は、150 ナノメートル～200 ナノメートルの厚みを有し得る。ポリシリコンの第 1 の層 322 は実質的にドープされておらず、図 2F を参照して説明した利点が得られ、及び図 2F を参照して説明したように形成され得る。ドーパント 344 が、1 度～2 度の傾き角度及び約ゼロ度の捩れ角度での 4 サブドーズで、 $2 \times 10^{15} \text{ cm}^{-2}$ ～ $1 \times 10^{16} \text{ cm}^{-2}$  の例示のドーズ量で、ポリシリコンの第 1 の層 322 に注入される。ドーパント 344 は、p 型ドーパントであり得、ボロンを含み得、又は、n 型ドーパントであり得、リン及び / 又は場合によってはヒ素を含み得る。ドーパント 344 の総ドーズは、ポリシリコンの第 1 の層 322 及び続いて形成されるポリシリコンの第 2 の層 324 において所望のシート抵抗値を提供するために、ディープトレンチ 320 の深さ及び幅に基づいて選択され得る。

20

#### 【0032】

図 4B を参照すると、ポリシリコンの第 2 の層 324 が、ポリシリコンの第 1 の層 322 上に形成され、ディープトレンチ 320 内に延在する。ポリシリコンの第 2 の層 324 は、800 ナノメートル～1.5 ミクロンの厚みを有し得、ディープトレンチ 320 を実質的に充填し得る。ポリシリコンの第 2 の層 324 は、図 2F を参照して説明したものと同様のプロセス条件を用いて形成され得る。ポリシリコンの第 2 の層 324 は、形成される際に実質的にドープされておらず、図 2H を参照して説明した利点が得られる。図 4A の注入されたドーパント 344 を活性化するように、及び注入されたドーパント 344 を、ポリシリコンの第 1 の層 322 及びポリシリコンの第 2 の層 324 にわたって拡散するように、熱駆動アニール 346 が基板 302 を加熱する。熱駆動アニールは、図 2I を参照して説明したものに類似し得、有利にも、ポリシリコンの第 1 の層 322 及びポリシリコンの第 2 の層 324 における注入されたドーパント 344 の所望の均一性を提供する。ドープされていない層としてのポリシリコンの第 1 の層 322 及びポリシリコンの第 2 の層 324 の形成により、図 2I を参照して説明した利点が得られる。ポリシリコンの第 2 の層 324、ポリシリコンの第 1 の層 322、ハードマスク酸化物 334 の層、及びパッ

30

40

50

ド窒化物 332 の層の一部が、C M P プロセスを用いて取り除かれる。パッド窒化物 332 の残りの層、及びパッド酸化物 330 の層はその後、図 3 の構造を提供するために取り除かれる。

【 0033 】

図 5 は、埋め込み層、及び埋め込み層に対する自己整合シンカーを備えたディープトレンチ構造を含む、代替の半導体デバイスの断面である。半導体デバイス 500 が基板 502 において形成され、基板 502 は、半導体材料の p 型ベース半導体層 504、半導体材料の n 型埋め込み層 506、及び基板 502 の頂部表面 510 まで延在する p 型上側半導体層 512 を含む。p 型ベース半導体層 504 は、5 cm ~ 10 cm の抵抗率を有するエピタキシャル半導体層であり得る。p 型上側半導体層 512 も、5 cm ~ 10 cm の抵抗率を有するエピタキシャル半導体層であり得る。n 型埋め込み層 506 はメイン層 548 を含み得、メイン層 548 は、ベース半導体層 504 と上側半導体層 512 との間の境界に跨り、ベース半導体層 504 内に少なくとも 1 ミクロン、及び上側半導体層 512 内に少なくとも 1 ミクロン延在する。n 型埋め込み層 506 はまた、軽くドープされた層 550 を含み得、軽くドープされた層 550 は、ベース半導体層 504 において配置され、メイン層 548 の下に少なくとも 2 ミクロン延在する。n 型埋め込み層 506 は、米国特許出願番号 U S 1 4 / 555, 330 に記載されるように形成され得る。

【 0034 】

半導体デバイス 500 は、一つ又は複数のディープトレンチ構造 514 を含み、ディープトレンチ構造 514 は、基板 502 において少なくとも 10 ミクロンの深さ延在する。各ディープトレンチ構造 514 は、ディープトレンチ構造 514 のディープトレンチ 520 の側壁 518 上の誘電体ライナー 516 を含む。ポリシリコンの第 1 の層 522 が、誘電体ライナー 516 上に配置され、ディープトレンチ構造 514 の底部まで延在する。ポリシリコンの第 2 の層 524 が、ポリシリコンの第 1 の層 522 上に配置され、ディープトレンチ 520 内に延在する。ドーパントが、少なくとも  $1 \times 10^{18} \text{ cm}^{-3}$  の平均ドーピング濃度で、ポリシリコンの第 1 の層 522 及びポリシリコンの第 2 の層 524 において分布する。トレンチ構造 514 は、本明細書における例の任意のものに記載されるように形成され得る。

【 0035 】

この例では、ポリシリコンの第 1 の層 522 がコンタクト領域 528 を介して基板 502 への電気的接続を成すように、誘電体ライナー 516 の誘電性材料が、ディープトレンチ構造 514 の底部において取り除かれ、コンタクト領域 528 が、ディープトレンチ構造 514 の底部における基板 502 において配置される。コンタクト領域 528、及び各ディープトレンチ構造 514 の底部における誘電体ライナー 516 を取り除く方法は、米国特許出願番号 U S 1 4 / 555, 359 に記載されるように成され得る。

【 0036 】

n 型自己整合シンカー 552 が、ディープトレンチ構造 514 に接し、埋め込み層 506 まで延在して、上側半導体層 512 に配置される。自己整合シンカー 552 は、埋め込み層 506 への電気的接続を提供する。自己整合シンカー 552 は、米国特許出願番号 U S 1 4 / 555, 209 に記載されるように形成され得る。

【 0037 】

本発明の特許請求の範囲内で、説明した例示の実施例に変形が成され得、他の実施例が可能である。

【図1】

FIG. 1

【図2A】

FIG. 2A

【図2B】

FIG. 2B

【図2C】

FIG. 2C

【図2D】

FIG. 2D

【図2E】

FIG. 2E

【図2F】

FIG. 2F

【図2G】

FIG. 2G

【図2H】

FIG. 2H

【図2I】

FIG. 2I

【図2J】

FIG. 2J

【図3】

FIG. 3

【図4A】

FIG. 4A

【図4B】

FIG. 4B

【図5】

FIG. 5

---

フロントページの続き

(51)Int.Cl.

F I

H 01 L 27/04

C

(72)発明者 ピンホワ フー

アメリカ合衆国 75024 テキサス州 プラノ, スターテン アイランド ドライブ 43

13

(72)発明者 サミール ピー ペンハルカル

アメリカ合衆国 75013 テキサス州 アレン, バーンサイド ドライブ 2032

(72)発明者 ジャーヴィス ベンジャミン ジェーコブス

アメリカ合衆国 75094 テキサス州 マーフィー, グレン リッジ ドライブ 433

審査官 宇多川 勉

(56)参考文献 特開平08-236614 (JP, A)

特開2010-062315 (JP, A)

特開2001-244328 (JP, A)

特開平05-144930 (JP, A)

特開平06-232149 (JP, A)

特表2006-521026 (JP, A)

特開平05-102298 (JP, A)

特開昭60-079737 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/28

H 01 L 21/265

H 01 L 21/822

H 01 L 27/04