(19) Weltorganisation für geistiges Eigentum

Internationales Büro

(43) Internationales Veröffentlichungsdatum 3. September 2015 (03.09.2015)

(10) Internationale Veröffentlichungsnummer WO 2015/127489 A1

(51) Internationale Patentklassifikation:

**H05K** 1/18 (2006.01) H01L 23/538 (2006.01) H05K 3/10 (2006.01)

(21) Internationales Aktenzeichen: PCT/AT2015/050052

(22) Internationales Anmeldedatum:

26. Februar 2015 (26.02.2015)

(25) Einreichungssprache: Deutsch

(26) Veröffentlichungssprache: Deutsch

(30) Angaben zur Priorität: A50152/2014 27. Februar 2014 (27.02.2014) AT

(71) Anmelder: AT&S AUSTRIA TECHNOLOGIE & SYSTEMTECHNIK AKTIENGESELLSCHAFT [AT/AT]; Fabriksgasse 13, A-8700 Leoben (AT).

(72) Erfinder: WEIDINGER, Gerald; Pebalstrasse 35, A-8700 Leoben (AT). ZLUC, Andreas; Im Tal 101, A-8700 Leoben (AT).

(74) Anwalt: PATENTANWALTSKANZLEI MATSCHNIG & FORSTHUBER OG; 36, Biberstrasse 22, A-1010 Wien (AT).

(81) Bestimmungsstaaten (soweit nicht anders angegeben, für jede verfügbare nationale Schutzrechtsart): AE, AG, AL,

AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Bestimmungsstaaten (soweit nicht anders angegeben, für jede verfügbare regionale Schutzrechtsart): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), eurasisches (AM, AZ, BY, KG, KZ, RU, TJ, TM), europäisches (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

#### Veröffentlicht:

— mit internationalem Recherchenbericht (Artikel 21 Absatz 3)

(54) Title: METHOD FOR MAKING CONTACT WITH A COMPONENT EMBEDDED IN A PRINTED CIRCUIT BOARD

(54) Bezeichnung : VERFAHREN ZUM KONTAKTIEREN EINES IN EINE LEITERPLATTE EINGEBETTETEN BAUELEMENTS SOWIE LEITERPLATTE

Fig. 5

(57) Abstract: The invention relates to a method for making contact with a component (6) embedded in a printed circuit board (13), which method has the following steps: a) providing a core (1) which has at least one insulating layer (2) and at least one conductor layer (3, 4) applied to the insulating layer (2), b) embedding at least one component (6) in a depression (5) in the insulating layer (2), wherein the contact pins (8) of the component (6) are located substantially in the plane of an outer surface of the core (1) having the at least one conductor layer (4), c) applying a varnish (9) that can be photo-structured to the one outer surface of the core (1) on which the component (6) is arranged, filling the spaces between the contact pins (8) of the component (6), d) exposing end faces of the contact pins (8) and the regions of the conductor layer (4) covered by the varnish (9) that can be photo-structured, by illuminating and developing the varnish (9) that can be photo-structured, e) by applying a semi-additive process, depositing a layer (10) of conductor material on the exposed end faces of the contact pins (8) and the exposed regions of the conductor layer (4), and forming a conductor structure (12-12), at least on the one outer surface of the core (1) on which the component (6) is arranged, and on the connecting lines (11) between the contact pins (8) and the conductor structure (12-12), and f) removing the regions of the conductor layer (4+10) that do not belong to the conductor structure (12-12).

(57) Zusammenfassung:

#

Die Erfindung betrifft ein Verfahren zum Kontaktieren eines in eine Leiterplatte (13) eingebetteten Bauelements (6), welches die folgenden Schritte aufweist: a) Bereitstellen eines Cores (1), das zumindest eine Isolierschicht (2) und zumindest eine auf der Isolierschicht (2) aufgebrachte Leiterschicht (3, 4) aufweist, b) Einbetten zumindest eines Bauelements (6) in eine Vertiefung (5) der Isolierschicht (2), wobei die Anschlüsse (8) des Bauelements (6) im Wesentlichen in der Ebene einer die zumindest eine Leiterschicht (4) aufweisenden Außenfläche des Cores (1) liegen, c) Aufbringen eines photostrukturierbaren Lacks (9) auf die eine Außenfläche des Cores (1), an der das Bauelement (6) angeordnet ist, unter Ausfüllen der Räume zwischen den Anschlüssen (8) des Bauelements (6), d) Freilegen von Stirnflächen der Anschlüsse (8) und der von dem photostrukturierbaren Lack (9) bedeckten Gebiete der Leiterschicht (4) durch Belichten und Entwickeln des photostrukturierbaren Lacks (9), e) durch Anwenden eines semi-additiven Prozesses Ablagern einer Schicht (10) von Leitermaterial auf den freigelegten Stirnflächen der Anschlüsse (8) sowie den freigelegten Gebieten der Leiterschicht (4) und Bilden einer Leiterstruktur (12-12) zumindest auf der einen Außenfläche des Cores (1), an der das Bauelement (6) angeordnet ist, sowie der Verbindungsleitungen (11) zwischen den Anschlüssen (8) und der Leiterstruktur (12-12) und f) Entfernen der nicht zur Leiterstruktur (12-12) gehörenden Bereiche der Leiterschicht (4+10).

# <u>Verfahren zum Kontaktieren eines in eine Leiterplatte eingebetteten Bauelements sowie</u> <u>Leiterplatte</u>

Die Erfindung bezieht sich auf ein Verfahren zum Kontaktieren eines in eine Leiterplatte eingebetteten Bauelements.

Weiters bezieht sich die Erfindung auf eine Leiterplatte mit zumindest einer Isolierschicht und zumindest einer strukturierten Leiterschicht mit Leiterbahnen, mit zumindest einem in die Isolierschicht unter Verwendung einer Kleberschicht in eine Vertiefung der Leiterplatte eingebetteten Bauelement, dessen Anschlüsse im Wesentlichen in der Ebene einer die zumindest eine Leiterschicht aufweisenden Außenfläche der Leiterplatte liegen und mit leitenden Verbindungen zwischen den Anschlüssen des Bauelements und Leiterbahnen der Leiterschicht

Das Einbetten von Bauteilen, wie insbesondere von Halbleiterchips, in Leiterplattenstrukturen ist dem Fachmann geläufig, wobei im Rahmen der Erfindung Strukturen betrachtet werden, bei welchen die Anschlüsse des Bauteils im Wesentlichen in einer Ebene an der Außenfläche der Leiterplatte liegen, wobei man auch von "surface embedded components" spricht. Die elektrischen Anschlüsse des Bauelements müssen mit einer Leiterstruktur kontaktiert werden, wozu verschiedene Wege beschritten wurden.

Beispielsweise zeigt die DE 10 2006 009 723 A1 ein Verfahren zum Einbetten eines Bauelements in eine Leiterplatte und zu dessen Kontakten, bei welchem auf ein metallisches Substrat eine erste Isolierschicht mit einer Leiterstruktur aufgebracht wird. Sodann wird ein Fenster bzw. ein Ausschnitt für den Chip in der ersten Schicht erzeugt und in dieses unter Belassen eines Spaltes ein Chip eingesetzt und mit Hilfe eines Klebstoffes auf dem Substrat fixiert. Die Anschlüsse des Chips befinden sich dabei an einer von dem Substrat abgewandten Kontaktseite. Darüber wird eine photostrukturierte zweite isolierende Schicht aufgetragen, welche die Kontaktstellen des Chips freilässt und dann erfolgt durch galvanisches Abscheiden eines Leitermaterials ein elektrisches Kontaktieren zwischen den Chipanschlüssen und der Leiterstruktur auf der ersten Schicht. Nachteilig an dem bekannten Verfahren bzw. dem erhaltenen Produkt ist die Tatsache, dass im Abstandsbereich zwischen Chip und angrenzenden Lagen ein Hohlraum verbleibt, der beim Aufbau weiterer Lagen zu Delaminationsproblemen führen kann.

Eine Aufgabe der Erfindung liegt in der Schaffung eines Verfahrens, mit dessen Hilfe einfach und kostengünstig eine Leiterstruktur in der Ebene der Anschlüsse samt entsprechenden Kontaktierungen erzeugt werden kann, ohne dass die Gefahr des Ablösens von Schichten besteht.

Diese Aufgabe wird mit einem Verfahren der eingangs genannten Art gelöst, welches erfindungsgemäß die folgenden Schritte aufweist:

a) Bereitstellen eines Cores, das zumindest eine Isolierschicht und zumindest eine auf der Isolierschicht aufgebrachte Leiterschicht aufweist,

b) Einbetten zumindest eines Bauelements in eine Vertiefung der Isolierschicht, wobei die Anschlüsse des Bauelements im Wesentlichen in der Ebene einer die zumindest eine Leiterschicht aufweisenden Außenfläche der Leiterplatte liegen,

- c) Aufbringen eines photostrukturierbaren Lacks auf die eine Außenfläche des Cores, an der das Bauelement angeordnet ist, unter Ausfüllen der Räume zwischen den Anschlüssen des Bauelements,

- d) Freilegen von Stirnflächen der Anschlüsse und der von dem photostrukturierbaren Lack bedeckten Gebiete der Leiterschicht durch Belichten und Entwickeln des photostrukturierbaren Lacks,

- e) durch Anwenden eines semi-additiven Prozesses Ablagern von Leitermaterial auf den freigelegten Stirnflächen der Anschlüsse sowie den freigelegten Gebieten der Leiterschicht und Bilden einer Leiterstruktur zumindest auf der einen Außenfläche des Cores, an der das Bauelement angeordnet ist, sowie der Verbindungsleitungen zwischen den Anschlüssen und der Leiterstruktur und

- f) Entfernen der nicht zur Leiterstruktur gehörenden Bereiche der Leiterschicht.

Dank der Erfindung kann die "Verdrahtung" von eingebetteten Bauteilen auf derselben Lage bzw. Ebene wie die Einbettung erfolgen, sodass die Leiterplatten dünner ausgebildet werden können und die oben genannten Probleme der Gefahr eines Ablösens ergeben sich nicht.

Dabei ist es empfehlenswert, wenn das Entfernen der Bereiche der Leiterschicht in Schritt f) durch Flash-Etching erfolgt.

In Hinblick auf die zusätzliche Funktion des photostrukturierbaren Lacks als Bestandteil der fertigen Leiterplatte ist es vorteilhaft, wenn der in Schritt c) verwendete photostrukturierbare Lack ein Epoxid basierter Lack ist.

Bei einer besonders günstigen Variante des erfindungsgemäßen Verfahrens kann vorgesehen sein, dass in Schritt b) das Bauelement unter Verwendung einer Kleberschicht in eine Vertiefung des Cores eingebettet wird, wobei die Kleberschicht sämtliche Flächen des Bauelements, ausgenommen jene mit den Anschlüssen, vollständig umgibt und im Wesentlichen bis zur Ebene der Oberfläche der Leiterplatte reicht, in welcher die Stirnflächen der Anschlüsse liegen.

Besonders zweckmäßig reicht dabei die Vertiefung des Cores durch die Leiterschicht hindurch in die Isolierschicht.

Die gestellten Aufgaben werden auch mit einer Leiterplatte der oben angegebenen Art gelöst, bei welcher erfindungsgemäß die Oberflächen der Verbindungen und der Leiterbahnen der Leiterschicht in einer Ebene liegen, die Kleberschicht sämtliche Flächen des Bauelements, ausgenommen jene mit den Anschlüssen, vollständig umgibt, die Räume zwischen den Anschlüssen des Bauelements mit einem ausgehärteten, photostrukturierbaren Lack gefüllt sind und auf den Stirnflächen der Anschlüsse sowie auf einer Leiterschicht der Leiterplatte im Bereich der Leiterbahnen eine zusätzliche Leiterschicht aufgebracht ist.

Bei einer bevorzugten Ausführungsform ist vorgesehen, dass der ausgehärtete, photostrukturierbare Lack die freien Stirnflächen der Kleberschicht zwischen der Außenwandung des Bauelements und der Innenwandung der Vertiefung der Leiterplatte bedeckt.

In einer Weiterbildung der Erfindung umfasst die Leiterplatte weiterhin ein Core, das zumindest eine Isolierschicht und zumindest eine auf der Isolierschicht aufgebrachte Leiterschicht aufweist, wobei eine mit zumindest einer Leiterschicht versehene Außenfläche des Cores eine Vertiefung aufweist, welche durch die Leiterschicht hindurch in die Isolierschicht reicht, wobei das Bauelement unter Verwendung einer Kleberschicht in der Vertiefung des Cores eingebettet ist und wobei die Anschlüsse des Bauelements im Wesentlichen in der Ebene der die zumindest eine Leiterschicht sowie die Vertiefung aufweisenden Außenfläche des Cores liegen.

Die Erfindung samt weiteren Vorteilen ist im Folgenden an Hand einer beispielsweisen Ausführungsform des Verfahrens bzw. der Leiterplatte näher beschrieben, was in der Zeichnung veranschaulicht ist. In dieser zeigen

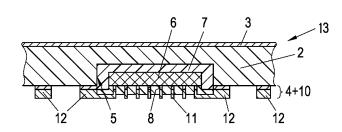

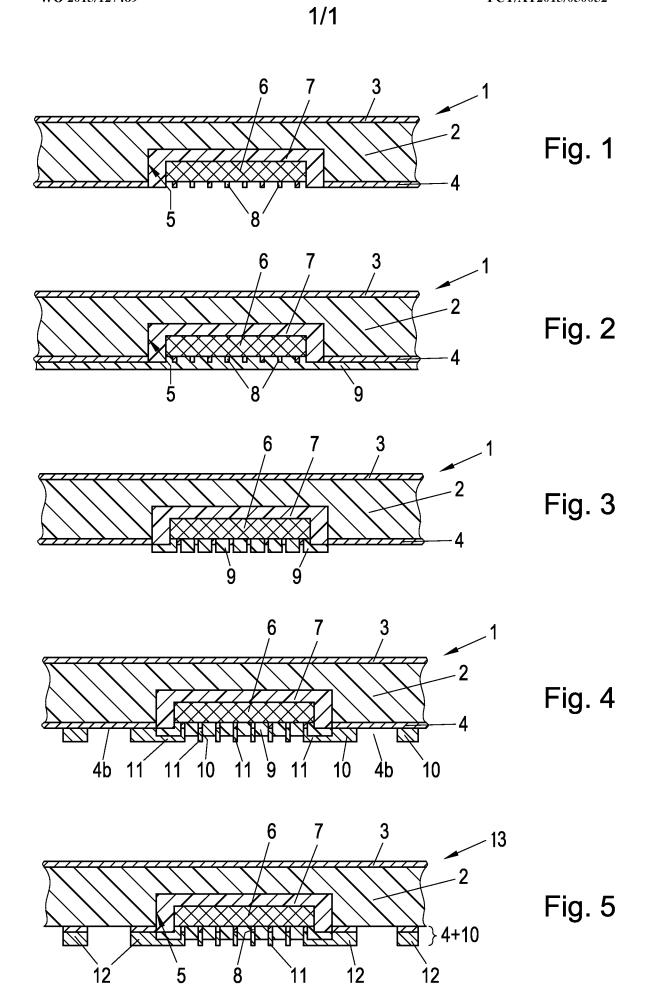

Fig. 1 in einem Schnitt durch einen Teilabschnitt ein in den ersten Schritten des Verfahrens hergestelltes Core mit einer eingebetteten Komponente,

Fig. 2 den Aufbau der Fig. 1 nach Aufbringen eines photostrukturierbaren Lacks,

Fig. 3 den Aufbau nach Belichten und Entwickeln des photostrukturierbaren Lacks,

Fig. 4 den Aufbau nach Ablagern von weiteren Leitermaterial durch Anwenden eines semi-additiven Prozesses und

Fig. 5 den Aufbau der fertigen Leiterplatte nach Wegätzen eines Teils der leitenden Beläge.

Unter Bezugnahme auf die Figuren werden nun das Verfahren nach der Erfindung sowie eine erfindungsgemäße Leiterplatte erläutert. Dabei ist unter dem im Folgenden verwendeten Begriff "Core" im Rahmen der gegenständlichen Beschreibung ein ausgehärtetes Prepreg mit einer Leiterschicht (Kupferlage) an zumindest einer Oberfläche zu verstehen.

**Fig. 1** zeigt einen Teil eines Cores 1, das aus einer Isolierschicht 2, beispielsweise bestehend aus einem in der Leiterplattenindustrie allgemein verwendeten Prepreg-Material, wie FR 4, und einer oberen Leiterschicht 3 sowie einer unteren Leiterschicht 4. An dieser Stelle sei angemerkt, dass sich die Begriffe "oben" und "unten" nur auf die Darstellungen in den Zeichnungen beziehen und zur Erleichterung der Beschreibung verwendet werden. Beispielsweise Schichtdicken sind 100  $\mu$ m für die Isolierschicht 2 und 1 bis 5  $\mu$ m, typisch 2  $\mu$ m, für die obere bzw. untere Leiterschicht 3 bzw. 4.

In dem Core 1 wird eine Vertiefung 5 ausgebildet, in welche ein Bauelement 6 unter Verwendung einer Kleberschicht 7 eingebettet wird, wobei die Schichtdicke dieser Kleberschicht beispielsweise 20 bis 200 µm beträgt. Das Bauelement 6, z.B. ein Halbleiter-Chip, trägt an einer Außenfläche Anschlüsse 8, z.B. Kupferpads, wobei die Kleberschicht 7 sämtliche Flächen des Bauelements 6, ausgenommen jene mit den Anschlüssen 8, vollständig umgibt und im Wesentlichen bis zur Ebene der Oberfläche des Cores 1 reicht, in welcher die Stirnflächen der Anschlüsse 8 liegen, somit hier der unteren Fläche. Als Kleber kommt beispielsweise ein lösungsmittelfreier bzw. lösungsmittelarmer Epoxidharzkleber mit einem Glaserweichungspunkt typisch von 120° bis 150°C in Frage, der in die

Vertiefung 5 gedruckt, eingefüllt oder eingespritzt wird. Nach der Bestückung mit dem Bauelement 6 wird dieser Kleber bei Temperaturen von 110° bis 150°C gehärtet.

In einem nächsten Schritt wird zumindest auf die Außenfläche des Cores 1 mit den Stirnflächen der Anschlüsse 8 ein Epoxid-basierter photostrukturierbarer Lack 9 aufgebracht, wobei auf **Fig. 2** Bezug genommen wird. Beispielsweise für diesen Zweck geeignete Produkte bzw. Materialien sind der Lack XB7081 mit dem Namen Probelec® der Fa. Huntsman oder der aus der lithographischen Galvanikabformung (LIGA) bekannte Fotolack SU-8 der Firma Microchem Corp. Wie man erkennt, füllt der Lack 9 sämtliche Räume zwischen den Anschlüssen 8 des Bauelements 6 aus und erstreckt sich auch über die untere Leiterschicht 4.

Sodann kann mit einem in der Leiterplattenherstellung üblichen fotolithographischen Prozess ein Strukturieren vorgenommen werden, wobei zunächst das Belichten mit einer Filmmaskierung oder durch LDI (Laser Direct Imaging) erfolgt. In der Folge wird entwickelt, nach Wegwaschen mit geeigneten Chemikalien die Strukturierung erhalten und das Material vollständig ausgehärtet. Das Härten erfolgt mit Hilfe üblicher Härtungsmethoden, wie z.B. thermisches Härten, UV- oder IR-Härten, Anwendung von Laserstrahlung etc. Das Strukturieren bzw. Belichten erfolgt in der Weise, dass die Anschlüsse 8, genauer gesagt deren Stirnflächen, freigelegt werden, wozu auf **Fig. 3** verwiesen wird. Dieser Strukturierungsvorgang wird so ausgeführt, dass der ausgehärtete, photostrukturierbare Lack 9 die freien Stirnflächen der Kleberschicht 7 zwischen der Außenwandung des Bauelements 6 und der Innenwandung der Vertiefung 5 des Core1 bedeckt und die untere Leiterschicht 4 wieder freigelegt wird.

Nach diesem Belichten und Entwickeln wird ein semi-additiver Prozess zum Auftragen von Leitermaterial, i.A. Kupfer, entsprechend der gewünschten Struktur vorgenommen. Dabei wird in den gewünschten Bereichen, insbesondere für Leiterzüge, eine Schicht 10 aus Leitermaterial aufgebracht, welche auch unter Bildung von Verbindungsleitungen 11 von den Stirnflächen der Anschlüsse 8 ausgehend zu der gewünschten Leiterstruktur abgelagert wird. Andererseits wird im Bereich der gewünschten Leiterzüge bzw. Leiterstruktur die untere Leiterschicht 4 verstärkt. Dieses Ergebnis ist in Fig. 4 ersichtlich.

Da zwischen den Verdickungen der unteren Leiterschicht 4 durch die Schicht 10, welche die Leiterzüge bilden sollen, noch Brücken 4b bestehen, erfolgt in einem weiteren Schritt das Entfernen dieser Brücken 4b und anderen unerwünschten Leitermaterials. Die erfolgt vorzugsweise durch sogenanntes "Flash-Etching", worunter man das Abätzen der Basiskupferfolie und einen geringen Abtrag der galvanisch aufgebrachten Kupferschichten versteht. Dieser Ätzvorgang erfolgt beispielsweise mit einem sauren Medium, z.B. HCl unter Zugabe H<sub>2</sub>O<sub>2</sub> und von Stabilisatoren, wobei die kleinen Kristallite der Basisfolie deutlich schneller aufgelöst werden als die galvanisch abgeschiedenen Schichten und eine selektive Ätzung erreicht wird. Nach diesem Vorgang des Abtragens bzw. Ätzens sind auch die Flächen bzw. Räume zwischen den Anschlüssen 9 gereinigt und die endgültigen Leiterbahnen 12 sind freigestellt und fertig gebildet, wozu auf **Fig. 5** verwiesen wird, welche die fertige Leiterplatte 13 mit dem eingebetteten und ankontaktierten Bauelement 6 zeigt.

Bei dem gezeigten Beispiel ist lediglich die Strukturierung der unteren Leiterschicht 4 beschrieben, doch sollte es klar sein, dass auch die obere Leiterschicht 3 in gleicher Weise strukturiert sein kann. Auch ist es möglich, Vias (leitende Durchkontaktierungen) zwischen den beiden Leiterschichten zu bilden, ebenso wie weitere Isolier- und Leiterschichten aufgebaut werden können.

Es sollte schließlich klar sein, dass die Darstellungen der Figuren 1 bis 5 im Allgemeinen nur Ausschnitte aus einer größeren Leiterplattenstruktur zeigen, und in der Praxis auf einer Leiterplatte mehrere Bauelemente an unterschiedlichen Stellen eingebettet und mit Leiterstrukturen verbunden sein können.

### Patentansprüche

1. Verfahren zum Kontaktieren eines in eine Leiterplatte (13) eingebetteten Bauelements (6), gekennzeichnet durch die folgenden Schritte:

- a) Bereitstellen eines Cores (1), das zumindest eine Isolierschicht (2) und zumindest eine auf der Isolierschicht (2) aufgebrachte Leiterschicht (3, 4) aufweist,

- b) Einbetten zumindest eines Bauelements (6) in eine Vertiefung (5) der Isolierschicht (2), wobei die Anschlüsse (8) des Bauelements (6) im Wesentlichen in der Ebene einer die zumindest eine Leiterschicht (4) aufweisenden Außenfläche des Cores (1) liegen,

- c) Aufbringen eines photostrukturierbaren Lacks (9) auf die eine Außenfläche des Cores (1), an der das Bauelement (6) angeordnet ist, unter Ausfüllen der Räume zwischen den Anschlüssen (8) des Bauelements (6),

- d) Freilegen von Stirnflächen der Anschlüsse (8) und der von dem photostrukturierbaren Lack (9) bedeckten Gebiete der Leiterschicht (4) durch Belichten und Entwickeln des photostrukturierbaren Lacks (9),

- e) durch Anwenden eines semi-additiven Prozesses Ablagern einer Schicht (10) von Leitermaterial auf den freigelegten Stirnflächen der Anschlüsse (8) sowie den freigelegten Gebieten der Leiterschicht (4) und Bilden einer Leiterstruktur (12-12) zumindest auf der einen Außenfläche des Cores (1), an der das Bauelement (6) angeordnet ist, sowie der Verbindungsleitungen (11) zwischen den Anschlüssen (8) und der Leiterstruktur (12-12) und

- f) Entfernen der nicht zur Leiterstruktur (12-12) gehörenden Bereiche der Leiterschicht (4+10).

- 2. Verfahren nach Anspruch 1, **dadurch gekennzeichnet**, **dass** das Entfernen der Bereiche der Leiterschicht (4+10) in Schritt f) durch Flash-Etching erfolgt.

- 3. Verfahren nach Anspruch 1 oder 2, **dadurch gekennzeichnet, dass** der in Schritt c) verwendete photostrukturierbare Lack (9) ein Epoxid basierter Lack ist.

- 4. Verfahren nach einem der Ansprüche 1 bis 3, **dadurch gekennzeichnet**, **dass** in Schritt b) das Bauelement (6) unter Verwendung einer Kleberschicht (7) in eine Vertiefung (5) des Cores (1) eingebettet wird, wobei die Kleberschicht (7) sämtliche Flächen des Bauelements (6), ausgenommen jene mit den Anschlüssen (8), vollständig umgibt und im Wesentlichen bis zur Ebene der Oberfläche der Leiterplatte (13) reicht, in welcher die Stirnflächen der Anschlüsse liegen.

- 5. Verfahren nach Anspruch 4, **dadurch gekennzeichnet**, **dass** die Vertiefung (5) des Cores (1) durch die Leiterschicht (4) hindurch in die Isolierschicht (2) reicht.

- 6. Leiterplatte (13) mit zumindest einer Isolierschicht (2) und zumindest einer strukturierten Leiterschicht (4+10) mit Leiterbahnen (12), mit zumindest einem in die Isolierschicht (2) unter Verwendung einer Kleberschicht (7) in eine Vertiefung (5) der Leiterplatte (13) eingebetteten Bauelement (6), dessen Anschlüsse (8) im Wesentlichen in der Ebene einer die zumindest eine Leiterschicht (4) sowie die Vertiefung (5) aufweisenden Außenfläche der Leiterplatte (13) liegen und

mit leitenden Verbindungen (11) zwischen den Anschlüssen (8) des Bauelements (6) und Leiterbahnen (12) der strukturierten Leiterschicht (4+10),

#### dadurch gekennzeichnet, dass

die Oberflächen der leitenden Verbindungen (11) und der Leiterbahnen (12) der strukturierten Leiterschicht (4+10) in einer Ebene liegen,

die Kleberschicht (9) sämtliche Flächen des Bauelements (6), ausgenommen jene mit den Anschlüssen (8), vollständig umgibt,

die Räume zwischen den Anschlüssen (8) des Bauelements (6) mit einem ausgehärteten, photostrukturierbaren Lack (9) gefüllt sind und

auf den Stirnflächen der Anschlüsse (8) sowie auf einer Leiterschicht (4) der Leiterplatte (13) im Bereich der Leiterbahnen (12) eine zusätzliche Leiterschicht (10) aufgebracht ist.

- 7. Leiterplatte (13) nach Anspruch 6, **dadurch gekennzeichnet**, **dass** der ausgehärtete, photostrukturierbare Lack (9) die freien Stirnflächen der Kleberschicht (7) zwischen der Außenwandung des Bauelements (6) und der Innenwandung der Vertiefung (5) bedeckt.

- 8. Leiterplatte (13) nach Anspruch 6 oder 7, weiterhin umfassend ein Core (1), das zumindest eine Isolierschicht (2) und zumindest eine auf der Isolierschicht (2) aufgebrachte Leiterschicht (3, 4) aufweist, wobei eine mit zumindest einer Leiterschicht (4) versehene Außenfläche des Cores (1) eine Vertiefung (5) aufweist, welche durch die Leiterschicht (4) hindurch in die Isolierschicht (2) reicht, dadurch gekennzeichnet, dass das Bauelement (6) unter Verwendung einer Kleberschicht (7) in der Vertiefung (5) des Cores (1) eingebettet ist, wobei die Anschlüsse (8) des Bauelements (6) im Wesentlichen in der Ebene der die zumindest eine Leiterschicht (4) sowie die Vertiefung (5) aufweisenden Außenfläche des Cores (1) liegen.

#### INTERNATIONAL SEARCH REPORT

International application No PCT/AT2015/050052

A. CLASSIFICATION OF SUBJECT MATTER INV. H05K1/18 ADD. H05K3/10 H01L23/538 According to International Patent Classification (IPC) or to both national classification and IPC **B. FIELDS SEARCHED** Minimum documentation searched (classification system followed by classification symbols) H05K Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched Electronic data base consulted during the international search (name of data base and, where practicable, search terms used) EPO-Internal, WPI Data C. DOCUMENTS CONSIDERED TO BE RELEVANT Relevant to claim No. Category' Citation of document, with indication, where appropriate, of the relevant passages γ WO 2013/029074 A1 (AUSTRIA TECH & SYSTEM 1-8 TECH [AT]; STAHR JOHANNES [AT]; ZLUC ANDREAS [AT) 7 March 2013 (2013-03-07) page 13, line 8 - page 14, line 16; figure US 2008/067666 A1 (HSU SHIH-PING [TW]) Υ 1-8 20 March 2008 (2008-03-20) figures 1,2 DE 196 42 488 A1 (KLOSE BERND [DE]) Α 1-8 16 April 1998 (1998-04-16) column 7, line 33 - column 8, paragraph 64; figures 1-7 DE 10 2010 042567 B3 (FRAUNHOFER GES 1-8 Α FORSCHUNG [DE]) 29 March 2012 (2012-03-29) figures 4A-4H Х Further documents are listed in the continuation of Box C. See patent family annex. Special categories of cited documents "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention "A" document defining the general state of the art which is not considered to be of particular relevance "E" earlier application or patent but published on or after the international "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive filing date "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other step when the document is taken alone "Y" document of particular relevance; the claimed invention cannot be special reason (as specified) considered to involve an inventive step when the document is combined with one or more other such documents, such combination "O" document referring to an oral disclosure, use, exhibition or other being obvious to a person skilled in the art "P" document published prior to the international filing date but later than the priority date claimed "&" document member of the same patent family Date of the actual completion of the international search Date of mailing of the international search report 26 May 2015 02/06/2015 Name and mailing address of the ISA/ Authorized officer European Patent Office, P.B. 5818 Patentlaan 2 NL - 2280 HV Rijswijk Tel. (+31-70) 340-2040, Fax: (+31-70) 340-3016 Degroote, Bart

## **INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No

PCT/AT2015/050052

| Patent document cited in search report | Public<br>dat |                       | Patent family<br>member(s)          |    | Publication<br>date                    |

|----------------------------------------|---------------|-----------------------|-------------------------------------|----|----------------------------------------|

| WO 2013029074                          | A1 07-0       | 3-2013 AT<br>DE<br>WO | 13436<br>112012003623<br>2013029074 | A5 | 15-12-2013<br>15-05-2014<br>07-03-2013 |

| US 2008067666                          | A1 20-0       | 3-2008 TW<br>US       | 200816443<br>2008067666             |    | 01-04-2008<br>20-03-2008               |

| DE 19642488                            | A1 16-0       | 4-1998 NO             | VE                                  |    |                                        |

| DE 102010042567                        | B3 29-0       | 3-2012 DE<br>US       | 102010042567<br>2012091594          |    | 29-03-2012<br>19-04-2012               |

#### INTERNATIONALER RECHERCHENBERICHT

Internationales Aktenzeichen PCT/AT2015/050052

A. KLASSIFIZIERUNG DES ANMELDUNGSGEGENSTANDES INV. H05K1/18 ADD. H05K3/10 H01L23/538 Nach der Internationalen Patentklassifikation (IPC) oder nach der nationalen Klassifikation und der IPC **B. RECHERCHIERTE GEBIETE** Recherchierter Mindestprüfstoff (Klassifikationssystem und Klassifikationssymbole) H05K Recherchierte, aber nicht zum Mindestprüfstoff gehörende Veröffentlichungen, soweit diese unter die recherchierten Gebiete fallen Während der internationalen Recherche konsultierte elektronische Datenbank (Name der Datenbank und evtl. verwendete Suchbegriffe) EPO-Internal, WPI Data C. ALS WESENTLICH ANGESEHENE UNTERLAGEN Bezeichnung der Veröffentlichung, soweit erforderlich unter Angabe der in Betracht kommenden Teile Betr. Anspruch Nr. Kategorie\* γ WO 2013/029074 A1 (AUSTRIA TECH & SYSTEM 1-8 TECH [AT]; STAHR JOHANNES [AT]; ZLUC ANDREĀS [AT) 7. März 2013 (2013-03-07) Seite 13, Zeile 8 - Seite 14, Zeile 16; Abbildung 3 US 2008/067666 A1 (HSU SHIH-PING [TW]) Υ 1-8 20. März 2008 (2008-03-20) Abbildungen 1,2 DE 196 42 488 A1 (KLOSE BERND [DE]) 1-8 Α 16. April 1998 (1998-04-16) Spalte 7, Zeile 33 - Spalte 8, Absatz 64; Abbildungen 1-7 DE 10 2010 042567 B3 (FRAUNHOFER GES 1-8 Α FORSCHUNG [DE]) 29. März 2012 (2012-03-29) Abbildungen 4A-4H Weitere Veröffentlichungen sind der Fortsetzung von Feld C zu entnehmen X Siehe Anhang Patentfamilie "T" Spätere Veröffentlichung, die nach dem internationalen Anmeldedatum oder dem Prioritätsdatum veröffentlicht worden ist und mit der Besondere Kategorien von angegebenen Veröffentlichungen "A" Veröffentlichung, die den allgemeinen Stand der Technik definiert, aber nicht als besonders bedeutsam anzusehen ist Anmeldung nicht kollidiert, sondern nur zum Verständnis des der Erfindung zugrundeliegenden Prinzips oder der ihr zugrundeliegenden "E" frühere Anmeldung oder Patent, die bzw. das jedoch erst am oder nach dem internationalen Anmeldedatum veröffentlicht worden ist Theorie angegeben ist "X" Veröffentlichung von besonderer Bedeutung; die beanspruchte Erfindung kann allein aufgrund dieser Veröffentlichung nicht als neu oder auf "L" Veröffentlichung, die geeignet ist, einen Prioritätsanspruch zweifelhaft erscheinen zu lassen, oder durch die das Veröffentlichungsdatum einer anderen im Recherchenbericht genannten Veröffentlichung belegt werden erfinderischer Tätigkeit beruhend betrachtet werden Veröffentlichung von besonderer Bedeutung; die beanspruchte Erfindung soll oder die aus einem anderen besonderen Grund angegeben ist (wie kann nicht als auf erfinderischer Tätigkeit beruhend betrachtet werden, wenn die Veröffentlichung mit einer oder mehreren Veröffentlichungen dieser Kategorie in Verbindung gebracht wird und diese Verbindung für einen Fachmann naheliegend ist ausgeführt) "O" Veröffentlichung, die sich auf eine mündliche Offenbarung, eine Benutzung, eine Ausstellung oder andere Maßnahmen bezieht "P" Veröffentlichung, die vor dem internationalen Anmeldedatum, aber nach "&" Veröffentlichung, die Mitglied derselben Patentfamilie ist dem beanspruchten Prioritätsdatum veröffentlicht worden ist Datum des Abschlusses der internationalen Recherche Absendedatum des internationalen Recherchenberichts 26. Mai 2015 02/06/2015 Name und Postanschrift der Internationalen Recherchenbehörde Bevollmächtigter Bediensteter Europäisches Patentamt, P.B. 5818 Patentlaan 2 NL - 2280 HV Rijswijk Tel. (+31-70) 340-2040,

Degroote, Bart

Fax: (+31-70) 340-3016

## INTERNATIONALER RECHERCHENBERICHT

Angaben zu Veröffentlichungen, die zur selben Patentfamilie gehören

Internationales Aktenzeichen

PCT/AT2015/050052

| Datum der<br>Veröffentlichung | Mitglied(er) der<br>Patentfamilie                          | Datum der<br>Veröffentlichung               |

|-------------------------------|------------------------------------------------------------|---------------------------------------------|

| 1 07-03-2013                  | AT 13436 U1<br>DE 112012003623 A5<br>WO 2013029074 A1      | 15-12-2013<br>15-05-2014<br>07-03-2013      |

| 1 20-03-2008                  | TW 200816443 A<br>US 2008067666 A1                         | 01-04-2008<br>20-03-2008                    |

| 1 16-04-1998                  | KEINE                                                      |                                             |

| 3 29-03-2012                  | DE 102010042567 B3<br>US 2012091594 A1                     | 29-03-2012<br>19-04-2012                    |

| - 4                           | Veröffentlichung A1 07-03-2013 A1 20-03-2008 A1 16-04-1998 | Veröffentlichung  A1 07-03-2013 AT 13436 U1 |