(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6493501号

(P6493501)

(45) 発行日 平成31年4月3日(2019.4.3)

(24) 登録日 平成31年3月15日(2019.3.15)

|                       |                  |

|-----------------------|------------------|

| (51) Int.Cl.          | F 1              |

| C04B 35/01 (2006.01)  | C04B 35/01       |

| C04B 35/495 (2006.01) | C04B 35/495      |

| C23C 14/34 (2006.01)  | C23C 14/34 A     |

| H01L 29/786 (2006.01) | H01L 29/78 618 B |

請求項の数 3 (全 16 頁)

|            |                                     |                                                          |

|------------|-------------------------------------|----------------------------------------------------------|

| (21) 出願番号  | 特願2017-233542 (P2017-233542)        | (73) 特許権者 000002130<br>住友電気工業株式会社<br>大阪府大阪市中央区北浜四丁目5番33号 |

| (22) 出願日   | 平成29年12月5日(2017.12.5)               | (74) 代理人 110001195<br>特許業務法人深見特許事務所                      |

| (62) 分割の表示 | 特願2013-185286 (P2013-185286)<br>の分割 | (72) 発明者 宮永 美紀<br>兵庫県伊丹市昆陽北一丁目1番1号 住友<br>電気工業株式会社 伊丹製作所内 |

| 原出願日       | 平成25年9月6日(2013.9.6)                 | (72) 発明者 綿谷 研一<br>兵庫県伊丹市昆陽北一丁目1番1号 住友<br>電気工業株式会社 伊丹製作所内 |

| (65) 公開番号  | 特開2018-62464 (P2018-62464A)         | (72) 発明者 栗巣 賢一<br>兵庫県伊丹市昆陽北一丁目1番1号 住友<br>電気工業株式会社 伊丹製作所内 |

| (43) 公開日   | 平成30年4月19日(2018.4.19)               |                                                          |

| 審査請求日      | 平成29年12月5日(2017.12.5)               |                                                          |

最終頁に続く

(54) 【発明の名称】酸化物焼結体の製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

酸化物焼結体に含まれる金属元素およびシリコンに対してインジウムおよびタンゲステンを80原子%以上の含有率で主成分として含み、スパッタ法のターゲットとして用いられる酸化物焼結体の製造方法であって、

I<sub>n</sub>W<sub>12</sub>O<sub>12</sub>型相を結晶相として含む粉末を用いる酸化物焼結体の製造方法。

## 【請求項2】

前記I<sub>n</sub>W<sub>12</sub>O<sub>12</sub>型相を結晶相として含む粉末は、酸化インジウム粉末および酸化タンゲステン粉末を混合して仮焼することにより得られる請求項1に記載の酸化物焼結体の製造方法。

10

## 【請求項3】

前記仮焼する際の温度は、800以上1200未満である請求項2に記載の酸化物焼結体の製造方法。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、酸化物焼結体の製造方法に関する。

## 【背景技術】

## 【0002】

液晶表示装置、薄膜EL(エレクトロルミネッセンス)表示装置、有機EL表示装置な

20

どにおいて、半導体デバイスであるTFT（薄膜トランジスタ）のチャネル層として機能する半導体膜として、従来では主として非晶質シリコン膜が使用されてきた。

#### 【0003】

しかし、近年では、そのような半導体膜として、In-Ga-Zn系複合酸化物（以下、IGZOともいう）を主成分とする酸化物半導体膜が、非晶質シリコン膜に比べてキャリアの移動度が大きいという利点から注目されている。

#### 【0004】

たとえば、特開2008-199005号公報（特許文献1）は、かかるIGZOを主成分とする酸化物半導体膜が、ターゲットを使用するスパッタ法によって形成されることを開示する。

10

#### 【0005】

また、特開2004-091265号公報（特許文献2）は、酸化物半導体膜をスパッタ法などにより形成する際に好適に用いられる材料として、主としてインジウムからなりタングステンを含む酸化物焼結体を開示する。

#### 【先行技術文献】

#### 【特許文献】

#### 【0006】

【特許文献1】特開2008-199005号公報

【特許文献2】特開2004-091265号公報

#### 【発明の概要】

20

#### 【発明が解決しようとする課題】

#### 【0007】

特開2008-199005号公報（特許文献1）に開示するIGZOを主成分とする酸化物半導体膜をチャネル層として含む半導体デバイスであるTFT（薄膜トランジスタ）には、市場価格が高い金属ガリウムを原料とする酸化ガリウムを原料として用いているため、製造コストが高いという問題点があった。

#### 【0008】

また、特開2004-091265号公報（特許文献2）に開示する主としてインジウムからなりタングステンを含む酸化物焼結体を用いて作製した酸化物半導体膜をチャネル層として含む半導体デバイスであるTFTには、OFF電流が $1 \times 10^{-11} A$ 程度と高く、駆動電圧を70V程度に高くしないとOFF電流に対するON電流の比を十分に大きくすることができないという問題点があった。

30

#### 【0009】

本発明は、上記問題点を解決し、特性の高い半導体デバイスの酸化物半導体膜を形成するのに好適な酸化物焼結体の製造方法を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0010】

本発明は、ある局面に従えば、少なくともインジウムおよびタングステンを含む酸化物焼結体の製造方法であって、In<sub>6</sub>WO<sub>12</sub>相を結晶相として含む粉末を用いる酸化物焼結体の製造方法である。

40

#### 【発明の効果】

#### 【0011】

本発明は、特性の高い半導体デバイスの酸化物半導体膜を形成するのに好適な酸化物焼結体の製造方法を提供できる。

#### 【図面の簡単な説明】

#### 【0012】

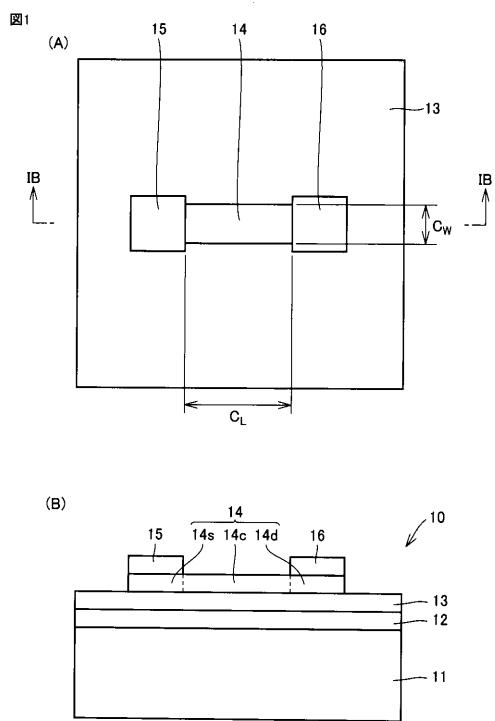

【図1】本発明にかかる半導体デバイスの一例を示す概略図である。ここで、(A)は概略平面図を、(B)はIB-IBにおける概略断面図を示す。

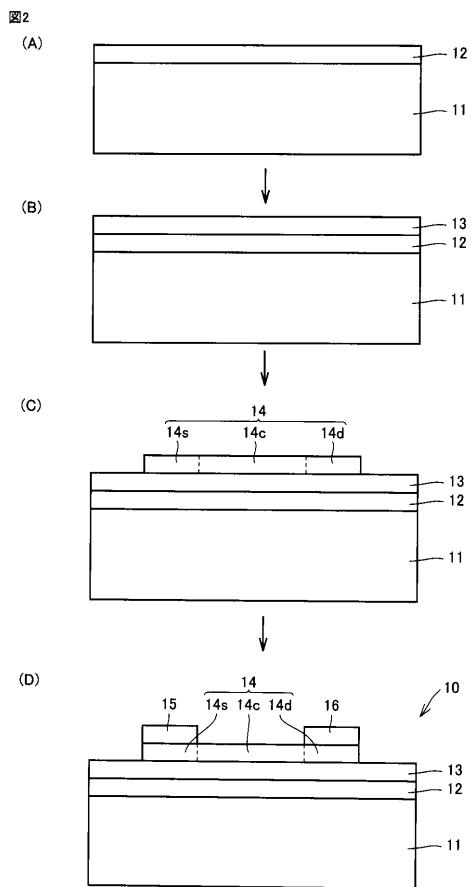

【図2】本発明にかかる半導体デバイスの製造方法の一例を示す概略断面図である。

#### 【発明を実施するための形態】

50

## 【0013】

<本願発明の実施形態の説明>

本発明のある実施形態である酸化物焼結体は、少なくともインジウムおよびタンゲステンを含む酸化物焼結体であって、結晶相として少なくとも $In_6WO_{12}$ 型相を含む。本実施形態の酸化物焼結体は、結晶相として少なくとも $In_6WO_{12}$ 型相を含むため、かかる酸化物焼結体を用いて形成された酸化物半導体膜をチャネル層として含む半導体デバイスであるTFT(薄膜トランジスタ)について、そのOFF電流を低下させるとともに、低い駆動電圧でOFF電流に対するON電流の比を高くすることができる。また、酸化物焼結体の熱伝導率を高くすることができる。

## 【0014】

10

本実施形態の酸化物焼結体においては、結晶相としてさらにピックスバイト型相を含むことができる。これにより、かかる酸化物焼結体を用いて形成された酸化物半導体膜をチャネル層として含む半導体デバイスであるTFTについて、そのOFF電流を低下させるとともに、低い駆動電圧でOFF電流に対するON電流の比を高くすることができる。また、酸化物焼結体の熱伝導率を高くすることができる。

## 【0015】

本実施形態の酸化物焼結体が結晶相として $In_6WO_{12}$ 型相およびピックスバイト型相を含む場合において、酸化物焼結体のある断面におけるその断面の面積に対する $In_6WO_{12}$ 型相およびピックスバイト型相の合計の面積の占有率であるダブル相占有率を、95%以上100%以下とすることができる。これにより、かかる酸化物焼結体を用いて形成された酸化物半導体膜をチャネル層として含む半導体デバイスであるTFTについて、そのOFF電流を低下させ、低い駆動電圧でOFF電流に対するON電流の比を高くするとともに、その特性の主面内のばらつきを低減することができる。また、酸化物焼結体の熱伝導率を高くすることができる。

20

## 【0016】

本実施形態の酸化物焼結体において、酸化物焼結体のある断面におけるその断面の面積に対する $In_6WO_{12}$ 型相の面積の占有率であるシングル相占有率を、20%以上100%以下とすることができる。これにより、かかる酸化物焼結体を用いて形成された酸化物半導体膜をチャネル層として含む半導体デバイスであるTFTについて、そのOFF電流を低下させ、低い駆動電圧でOFF電流に対するON電流の比を高くするとともに、その特性の主面内のばらつきを低減することができる。また、酸化物焼結体の熱伝導率を高くすることができる。

30

## 【0017】

本実施形態の酸化物焼結体において、酸化物焼結体に含まれるすべての金属元素およびシリコンに対するタンゲステンの含有率を、0.5原子%以上20原子%以下とすることができます。これにより、かかる酸化物焼結体を用いて形成された酸化物半導体膜をチャネル層として含む半導体デバイスであるTFTについて、低い駆動電圧でOFF電流に対するON電流の比を高くすることができる。また、酸化物半導体膜の成膜速度が高くなる。

## 【0018】

40

本実施形態の酸化物焼結体において、酸化物焼結体に含まれるすべての金属元素およびシリコンに対する、アルミニウム、スズ、チタン、クロム、ガリウム、ハフニウム、ジルコニウム、シリコン、モリブデン、バナジウム、ニオブ、タンタル、およびビスマスからなる群から選ばれる少なくとも1種の元素の含有率を0.1原子以上10原子%以下とすることができます。これにより、かかる酸化物焼結体を用いて形成された酸化物半導体膜をチャネル層として含む半導体デバイスであるTFTについて、そのOFF電流を低下させるとともに、低い駆動電圧でOFF電流に対するON電流の比を高くすることができる。

## 【0019】

本発明の別の実施形態である半導体デバイスは、上記実施形態の酸化物焼結体をターゲットとして用いてスパッタ法により形成した酸化物半導体膜を含む半導体デバイスである。本実施形態の半導体デバイスは、上記実施形態の酸化物焼結体をターゲットとして用い

50

てスパッタ法により形成した酸化物半導体膜を含むため、高い特性を有する。

#### 【0020】

<本願発明の実施形態の詳細>

##### [実施形態1：酸化物焼結体]

本発明のある実施形態である酸化物焼結体は、少なくともインジウムおよびタングステンを含む酸化物焼結体であって、結晶相として少なくとも $In_6WO_{12}$ 型相を含む。本実施形態の酸化物焼結体は、結晶相として少なくとも $In_6WO_{12}$ 型相を含むため、かかる酸化物焼結体を用いて形成された酸化物半導体膜をチャネル層として含む半導体デバイスであるTFT(薄膜トランジスタ)について、そのOFF電流を低下させるとともに、低い駆動電圧でOFF電流に対するON電流の比を高くすることができる。また、酸化物焼結体の熱伝導率を高くすることができる。10

#### 【0021】

##### (InおよびWの含有)

本実施形態の酸化物焼結体は、それを用いて形成された酸化物半導体膜をチャネル層として含む半導体デバイスであるTFT(薄膜トランジスタ)について、そのOFF電流を低下させ、低い駆動電圧でOFF電流に対するON電流の比を高くするとともに、酸化物焼結体の熱伝導率を高くする観点から、少なくともIn(インジウム)およびW(タングステン)を含み、InおよびWを主成分とすることが好ましい。ここで、主成分とは、本実施形態の酸化物焼結体に含まれる金属元素およびSi(シリコン)に対してInおよびWの含有率が80原子%以上であることをいい、95原子%以上が好ましい。20

#### 【0022】

##### ( $In_6WO_{12}$ 型相)

本実施形態の酸化物焼結体は、それを用いて形成された酸化物半導体膜をチャネル層として含む半導体デバイスであるTFT(薄膜トランジスタ)について、そのOFF電流を低下させ、低い駆動電圧でOFF電流に対するON電流の比を高くするとともに、酸化物焼結体の熱伝導率を高くする観点から、結晶相として少なくとも $In_6WO_{12}$ 型相を含む。。20

#### 【0023】

$In_6WO_{12}$ 型相は、 $In_6WO_{12}$ 相および $In_6WO_{12}$ 相の一部にInおよびW以外の金属元素およびSiが含まれる相、酸素が一部欠損している相、および/または酸素が過剰である相の総称をいい、 $In_6WO_{12}$ 相と同じ結晶構造を含む。 $In_6WO_{12}$ 型相は、X線回折測定により、同定される。30

#### 【0024】

ここで、 $In_6WO_{12}$ 相は、三方晶系の結晶構造を有し、JCPDSカードの01-074-1410に規定される結晶構造を有するタングステン酸インジウム化合物結晶相である。なお、特開2004-091265号公報(特許文献2)で開示されているタングステン酸インジウム化合物結晶相は、 $InW_3O_9$ 相であり、六方晶系の結晶構造を有し、JCPDSカードの33-627に規定される結晶構造を有するため、 $In_6WO_{12}$ 相とは結晶構造が異なる。40

#### 【0025】

また、 $In_6WO_{12}$ 相の一部にInおよびW以外の金属元素およびSiが含まれる相とは、 $In_6WO_{12}$ 相の一部にInおよびW以外の金属元素およびSiが固溶した結晶構造であってもよく、たとえば、InおよびW以外の金属元素およびSiが、 $In_6WO_{12}$ 相のInサイトおよび/またはWサイトの一部に固溶置換していてもよく、 $In_6WO_{12}$ 相の結晶格子間に侵入していてもよい。

#### 【0026】

##### (ビックスバイト型相)

本実施形態の酸化物焼結体においては、それを用いて形成された酸化物半導体膜をチャネル層として含む半導体デバイスであるTFTについて、そのOFF電流を低下させ、低い駆動電圧でOFF電流に対するON電流の比を高くするとともに、酸化物焼結体の熱伝50

導率を高くする観点から、結晶相としてさらにビックスバイト型相を含むことが好ましい。

#### 【0027】

ビックスバイト型相は、ビックスバイト相およびビックスバイト相の一部にInおよびW以外の金属元素およびSiが含まれる相の総称をいい、ビックスバイト相と同じ結晶構造を含む。ビックスバイト型相は、X線回折測定により、同定される。ここで、ビックスバイト相は、酸化インジウム( $In_2O_3$ )の結晶相のひとつであり、JCPDSカードの6-0416に規定される結晶構造をいい、希土類酸化物C型相(またはC-希土構造相)とも呼ばれる。また、ビックスバイト相の一部にInおよびW以外の金属元素およびSiが含まれる相は、ビックスバイト相の一部にInおよびW以外の金属元素およびSiが固溶した結晶構造であってもよい。10

#### 【0028】

##### ( $In_6WO_{12}$ 型相のシングル相占有率)

本実施形態の酸化物焼結体において、それを用いて形成された酸化物半導体膜をチャネル層として含む半導体デバイスであるTFT(薄膜トランジスタ)について、そのOFF電流を低下させ、低い駆動電圧でOFF電流に対するON電流の比を高くするとともに、酸化物焼結体の熱伝導率を高くする観点から、酸化物焼結体のある断面におけるその断面の面積に対する $In_6WO_{12}$ 型相の面積の占有率であるシングル相占有率は、20%以上100%以下が好ましく、20%以上85%以下がより好ましく、35%以上60%以下がさらに好ましい。20

#### 【0029】

かかる $In_6WO_{12}$ 型相のシングル相占有率は、以下のようにして算出する。まず、エネルギー分散型ケイ光X線分析計を付帯する走査型二次電子顕微鏡(SEM-EDX)を用いて、鏡面仕上げ加工をした酸化物焼結体の断面をSEMで観察し、各相の組成をEDXで分析する。各相の結晶構造をX線回折測定の-2法により同定する。X線回折測定により同定された各相は、InとWとの組成の比率が異なる。酸化物焼結体の相間のInとWとの組成の比率の違いは、上記EDXで分析された相間の組成の比率の違いと傾向が一致する。たとえば、X線回折測定において $In_6WO_{12}$ 型相および $InW_3O_9$ 型相の両方の存在が確認された場合、 $In_6WO_{12}$ 型相の方が高いIn比率のため、EDX分析においてIn比率が高い結晶相が $In_6WO_{12}$ 型相と同定される。30

#### 【0030】

##### ( $In_6WO_{12}$ 型相およびビックスバイト型相のダブル相占有率)

本実施形態の酸化物焼結体が結晶相として $In_6WO_{12}$ 型相およびビックスバイト型相を含む場合において、酸化物焼結体を用いて形成された酸化物半導体膜をチャネル層として含む半導体デバイスであるTFTについて、そのOFF電流を低下させ、低い駆動電圧でOFF電流に対するON電流の比を高くし、その特性の主面内のばらつきを低減するとともに、酸化物焼結体の熱伝導率を高くする観点から、酸化物焼結体のある断面におけるその断面の面積に対する $In_6WO_{12}$ 型相およびビックスバイト型相の合計の面積の占有率であるダブル相占有率は、95%以上100%以下が好ましく、98%以上100%以下がより好ましい。40

#### 【0031】

ここで、酸化物焼結体のビックスバイト型相の面積の占有率は、酸化物焼結体の断面の面積に対する $In_6WO_{12}$ 型相の面積の占有率であるシングル相占有率と同様の方法で算出されることから、断面の面積に対する $In_6WO_{12}$ 型相およびビックスバイト型相の合計の面積の占有率であるダブル相占有率は、酸化物焼結体の断面の面積に対する $In_6WO_{12}$ 型相の面積の占有率であるシングル相占有率と同様の方法で算出される。

#### 【0032】

##### (タンゲステン含有率)

本実施形態の酸化物焼結体において、それを用いて形成された酸化物半導体膜をチャネル層として含む半導体デバイスであるTFTについて、低い駆動電圧でOFF電流に対す50

るON電流の比を高くするとともに、酸化物半導体膜の成膜速度が高くなる観点から、酸化物焼結体に含まれるすべての金属元素およびSiに対するタンゲステンの含有率は、0.5原子%以上20原子%以下が好ましく、0.5原子%以上10原子%以下がより好ましく、7原子%以上10原子%以下がさらに好ましい。

#### 【0033】

ここで、酸化物焼結体中のWなどの金属元素またはSiの含有量は、ICP(誘導結合プラズマ)質量分析により測定される。タンゲステン含有率は、酸化物焼結体中のすべての金属元素またはSiの含有量に対するWの含有量の百分率である。

#### 【0034】

##### (金属元素およびSiの含有率)

10

本実施形態の酸化物焼結体において、それを用いて形成された酸化物半導体膜をチャネル層として含む半導体デバイスであるTFTについて、そのOFF電流を低下させるとともに、低い駆動電圧でOFF電流に対するON電流の比を高くする観点から、酸化物焼結体に含まれるすべての金属元素およびSi(シリコン)に対する、Al(アルミニウム)、Sn(スズ)、Ti(チタン)、Cr(クロム)、Ga(ガリウム)、Hf(ハフニウム)、Zr(ジルコニウム)、Si(シリコン)、Mo(モリブデン)、V(バナジウム)、Nb(ニオブ)、Ta(タンタル)、およびBi(ビスマス)からなる群から選ばれる少なくとも1種の元素の含有率は、0.1原子以上10原子%以下が好ましく、0.1原子%以上5原子%以下がより好ましく、0.1原子%以上1原子%以下がさらに好ましい。

20

#### 【0035】

ここで、Al、Ti、Cr、Ga、Hf、Si、V、およびNbの少なくとも1種類の元素の含有率が0.1原子%以上のとき、その酸化物焼結体を用いて得られる酸化物半導体を含む半導体デバイスのOFF電流が低くなる効果があるが、かかる元素の含有率が10原子%より大きくなると、半導体デバイスのON電流が低くなる傾向がある。

#### 【0036】

また、Sn、Zr、Mo、Ta、およびBiの少なくとも1種の元素の含有率が0.1原子%以上のとき、その酸化物焼結体を用いて得られる酸化物半導体を含む半導体デバイスのON電流が高くなる効果があるが、かかる元素の含有率が10原子%より大きくなると、半導体デバイスのOFF電流が高くなる傾向がある。

30

#### 【0037】

##### (酸化物焼結体の製造方法)

本実施形態の酸化物焼結体の製造方法は、特に制限はないが、効率よく製造する観点から、原料粉末の混合物を調製する工程と、混合物を仮焼する工程と、仮焼粉末を成形する工程と、成形体を焼結する工程と、を含む。

#### 【0038】

##### 1. 原料粉末の混合物を調製する工程

酸化物焼結体の原料粉末としては、In<sub>2</sub>O<sub>3</sub>(酸化インジウム)粉末、WO<sub>3</sub>(酸化タンゲステン)粉末など、酸化物焼結体を構成する金属元素およびSiの酸化物粉末が用いられる。原料粉末の純度は、酸化物焼結体への意図しない金属元素およびSiの混入を防止し安定した物性を得る観点から、99.9質量%以上の高純度であることが好ましい。

40

#### 【0039】

まず、In<sub>2</sub>O<sub>3</sub>粉末、WO<sub>3</sub>粉末などの酸化物粉末である原料粉末を、粉碎混合する。原料粉末を粉碎混合する方法には、特に制限はなく、乾式および湿式のいずれの方式であってもよく、具体的には、ボールミル、遊星ボールミル、ビーズミルなどを用いて粉碎混合される。このようにして、原料粉末の混合物が得られる。ここで、湿式の粉碎混合方式を用いて得られた混合物の乾燥には、自然乾燥やスプレードライヤなどの乾燥方法が好ましく用いられ得る。

#### 【0040】

##### 2. 混合物を仮焼する工程

50

次に、得られた混合物を仮焼する。混合物の仮焼温度は、特に制限はないが、仮焼物の粒径が大きくなりすぎて焼結密度が低下するないように 1200 未満であることが望ましく、仮焼物として結晶相である  $In_6WO_{12}$  相を得るためには 800 以上であることが望ましい。このため、800 以上 1200 未満であることが好ましく、900 以上 1000 以下がより好ましい。このようにして、仮焼物が得られる。得られた仮焼物は、上記と同様の粉碎混合する方法により、粉碎混合されて仮焼粉末が得られる。

#### 【0041】

##### 3. 仮焼粉末を成形する工程

次に、得られた仮焼粉末を成形する。仮焼粉末を成形する方法は、特に制限はないが、焼結密度を高くする点から、一軸プレス法、CIP（冷間静水圧処理）法、キャスティング法などが好ましい。このようにして、成形体が得られる。

10

#### 【0042】

##### 4. 成形体を焼結する工程

次に、得られた成形体を焼結する。成形体の焼結温度は、特に制限はないが、焼結密度（理論密度に対する実際の焼結密度の百分率をいう。）を 90% 以上として熱伝導率を高くする点から、1400 以上 1700 以下が好ましく、1450 以上 1550 以下がより好ましい。また、焼結雰囲気は、特に制限はないが、酸化物焼結体の構成結晶の粒径が大きくなることを防いでクラックの発生を防止する点および熱伝導率が高くなる点から、大気圧 - 大気雰囲気、酸素雰囲気、窒素 - 酸素混合雰囲気などが好ましく、大気圧 - 大気雰囲気が特に好ましい。このようにして、本実施形態の酸化物焼結体が得られる。

20

#### 【0043】

##### [実施形態 2：半導体デバイス]

図 1 を参照して、本発明の別の実施形態である半導体デバイス 10 は、実施形態 1 の酸化物焼結体をターゲットとして用いてスパッタ法により形成した酸化物半導体膜 14 を含む。本実施形態の半導体デバイスは、上記実施形態の酸化物焼結体をターゲットとして用いてスパッタ法により形成した酸化物半導体膜を含むため、高い特性を有する。

#### 【0044】

本実施形態の半導体デバイス 10 は、特に限定はされないが、たとえば、実施形態 1 の酸化物焼結体をターゲットとして用いてスパッタ法により形成した酸化物半導体膜 14 をチャネル層として含む半導体デバイスである TFT（薄膜トランジスタ）である。本実施形態の半導体デバイス 10 の一例である TFT は、上記実施形態の酸化物焼結体をターゲットとして用いてスパッタ法により形成した酸化物半導体膜 14 をチャネル層として含むため、その OFF 電流が低くなるとともに、低い駆動電圧で OFF 電流に対する ON 電流の比が高くなる。

30

#### 【0045】

本実施形態の半導体デバイス 10 である TFT は、より具体的には、図 1 に示すように、基板 11 と、基板 11 上に配置されたゲート電極 12 と、ゲート電極 12 上に絶縁層として配置されたゲート絶縁膜 13 と、ゲート絶縁膜 13 上にチャネル層として配置された酸化物半導体膜 14 と、酸化物半導体膜 14 上に互いに接触しないように配置されたソース電極 15 およびドレイン電極 16 と、を含む。

40

#### 【0046】

##### (半導体デバイスの製造方法)

図 2 を参照して、本実施形態の半導体デバイス 10 の製造方法は、特に制限はないが、効率よく高特性の半導体デバイスを製造する観点から、基板 11 上にゲート電極 12 を形成する工程（図 2 (A)）、ゲート電極 12 上に絶縁層としてゲート絶縁膜 13 を形成する工程（図 2 (B)）と、ゲート絶縁膜 13 上にチャネル層として酸化物半導体膜 14 を形成する工程（図 2 (C)）と、酸化物半導体膜 14 上にソース電極 15 およびドレイン電極 16 を互いに接触しないように形成する工程（図 2 (D)）と、を含むことが好ましい。

#### 【0047】

50

### 1. ゲート電極を形成する工程

図2(A)を参照して、基板11上にゲート電極12を形成する。基板11は、特に制限はないが、透明性、価格安定性、および表面平滑性を高くする点から、石英ガラス基板、無アルカリガラス基板、アルカリガラス基板などが好ましい。ゲート電極12は、特に制限はないが、耐酸化性が高くかつ電気抵抗が低い点から、Mo電極、Ti電極、W電極、Al電極、Cu電極などが好ましい。ゲート電極12の形成方法は、特に制限はないが、基板の主面上に大面積で均一に形成できる点から、真空蒸着法、スパッタ法などが好ましい。

#### 【0048】

### 2. ゲート絶縁膜を形成する工程

図2(B)を参照して、ゲート電極12上に絶縁層としてゲート絶縁膜13を形成する。ゲート絶縁膜13は、特に制限はないが、絶縁性が高い点から、SiO<sub>x</sub>膜、SiN<sub>x</sub>膜などが好ましい。ゲート絶縁膜13の形成方法は、特に制限はないが、ゲート電極が形成された基板の主面上に大面積で均一に形成できる点および絶縁性を確保する点から、プラズマCVD(化学気相堆積)法などが好ましい。

#### 【0049】

### 3. 酸化物半導体膜を形成する工程

図2(C)を参照して、ゲート絶縁膜13上にチャネル層として酸化物半導体膜14を形成する。酸化物半導体膜14は、特性の高い半導体デバイス10を製造する観点から、実施形態1の酸化物焼結体をターゲットとして用いてスパッタ法により形成する。ここでは、スパッタ法とは、成膜室内に、ターゲットと基板とを対向させて配置し、ターゲットに電圧を印加して、希ガスイオンでターゲットの表面をスパッタリングすることにより、ターゲットからターゲットを構成する原子を放出させて基板(上記のゲート電極およびゲート絶縁膜が形成された基板も含む。)上に堆積させることによりターゲットを構成する原子で構成される膜を形成する方法をいう。

#### 【0050】

### 4. ソース電極およびドレイン電極を形成する工程

図2(D)を参照して、酸化物半導体膜14上にソース電極15およびドレイン電極16を互いに接触しないように形成する。ソース電極15およびドレイン電極16は、特に制限はないが、耐酸化性が高く、電気抵抗が低く、かつ酸化物半導体膜との接触電気抵抗が低い点から、Mo電極、Ti電極、W電極、Al電極、Cu電極などが好ましい。ソース電極15およびドレイン電極16を形成する方法は、特に制限はないが、酸化物半導体膜が形成された基板の主面上に大面積で均一に形成できる点から、真空蒸着法、スパッタ法などが好ましい。ソース電極15およびドレイン電極16を互いに接触しないように形成する方法は、特に制限はないが、酸化物半導体膜が形成された基板の主面上に大面積で均一なソース電極とドレイン電極のパターンを形成できる点から、フォトレジストを使ったエッチング法による形成が好ましい。

#### 【実施例】

#### 【0051】

##### (実施例1～実施例9)

###### 1. 原料粉末の混合物の調製

まず、ボールミルに、WO<sub>3</sub>粉末(粒度0.5μm～1.2μm、純度99.9質量%)を入れて48時間粉碎混合し、次に、In<sub>2</sub>O<sub>3</sub>粉末(平均粒径1.0μm、純度99.9質量%)を入れて、さらに12時間粉碎混合することにより原料粉末の混合物を調製した。In<sub>2</sub>O<sub>3</sub>粉末とWO<sub>3</sub>粉末とのモル混合比率をIn<sub>2</sub>O<sub>3</sub>:WO<sub>3</sub>=40～40.5:0.1～1.0で変動させて、表1の実施例1～実施例9に示すIn<sub>2</sub>O<sub>3</sub>粉末とWO<sub>3</sub>粉末とのモル混合比率で混合して、9種類の原料粉末の混合物を調製した。上記の粉碎混合の際の分散媒としてエタノールを用いた。得られた原料粉末の混合物は大気中で乾燥させた。

#### 【0052】

10

20

30

40

50

## 2. 混合物の仮焼

次に、得られた9種類の原料粉末の混合物を、アルミナ製坩堝に入れて、大気雰囲気中で800～1000の温度で8時間仮焼した。仮焼温度は結晶相が形成される温度であれば仮焼物の粒径をなるべく小さくする点から低い方が好ましく、粉末原料の種類およびモル混合比率に応じて変えた。このようにして、実施例1においては結晶相として $In_6WO_{12}$ 型相を含む仮焼物が得られ、実施例2～実施例9においては結晶相として $In_6WO_{12}$ 型相とビックスバイト型相である $In_2O_3$ 型相とを含む仮焼物が得られた。

### 【0053】

次いで、得られた仮焼物を、ボールミルに入れて、12時間粉碎混合した。このようにして仮焼粉末が得られた。上記の粉碎混合の際の分散媒としてエタノールを用いた。得られた仮焼粉末はスプレードライで乾燥させた。10

### 【0054】

#### 3. 仮焼粉末の成形

次に、得られた仮焼粉末を、プレスにより成形し、さらにCIPにより室温(5～30)の静水中で190MPaの圧力で加圧成形して、直径100mmで厚さ約9mmの円板状の成形体を得た。

### 【0055】

#### 4. 成形体の焼結

次に、得られた成形体を大気雰囲気中にて表1の実施例1～実施例9に示す焼成温度で8時間焼結し、これによって酸化物焼結体が得られた。20

### 【0056】

#### 5. 酸化物焼結体の物性評価

得られた酸化物焼結体の結晶相の同定は、酸化物焼結体の一部からサンプルを採取して、粉末X線回折法による結晶解析により行なった。X線としてはCuのK線を用いて、結晶相の同定を行った。酸化物焼結体に存在する結晶相を表1にまとめた。

### 【0057】

得られた酸化物焼結体の上記断面における $In_6WO_{12}$ 型相およびビックスバイト型相である $In_2O_3$ 型相は以下のようにして同定した。

### 【0058】

酸化物焼結体の一部からサンプルを採取して、サンプルの表面を研磨して平滑にした。続いて、SEM-EDXを用いて、サンプルの表面をSEMで観察し、各結晶粒子の金属元素の組成比をEDXで分析した。結晶粒子をそれらの結晶粒子の金属元素の組成比の傾向でグループ分けを行ったところ、W含有率の多い結晶粒子のグループとW含有率が非常に少ない結晶粒子のグループに分けることができた。W含有率の多い結晶粒子のグループは $In_6WO_{12}$ 型相であり、W含有率が非常に少ない結晶粒子はビックスバイト型相である $In_2O_3$ 型相であると結論づけた。30

### 【0059】

酸化物焼結体の上記断面におけるその断面の面積に対する $In_6WO_{12}$ 型相の面積の占有率であるシングル相占有率(以下、 $In_6WO_{12}$ 型相のシングル相占有率という。)および酸化物焼結体の上記断面におけるその断面の面積に対する $In_6WO_{12}$ 型相およびビックスバイト型相である $In_2O_3$ 型相の合計の面積の占有率であるダブル相占有率(以下、 $In_6WO_{12}$ 型相およびビックスバイト型相である $In_2O_3$ 型相のダブル相占有率という。)を表1にまとめた。40

### 【0060】

得られた酸化物焼結体中の金属元素およびSiの含有量は、ICP質量分析法により測定した。これらの含有量に基づいて酸化物焼結体に含まれる金属元素およびSiに対するWの含有率を算出した。結果を表1にまとめた。

### 【0061】

得られた酸化物焼結体の熱伝導率は、レーザフラッシュ法により測定した。酸化物焼結体の一部からサンプルを採取して、直径20mm×厚さ1mmの円板状に加工した。熱の50

吸収及び輻射率をよくするために、サンプル表面にカーボンスプレーを塗布した後、サンプル表面にパルスレーザ光を照射した。レーザ光は波長が  $1.06 \mu\text{m}$  であり、パルス幅が  $0.4 \text{ ms}$  であった。実施例 1 の熱伝導率を 1 としたときの各実施例の相対熱伝導率を表 1 にまとめた。

#### 【0062】

##### 6. ターゲットの作製

得られた酸化物焼結体を、直径 3 インチ ( $76.2 \text{ mm}$ ) で厚さ  $5.0 \text{ mm}$  のターゲットに加工した。

#### 【0063】

##### 7. 半導体デバイスの作製

10

###### (1) ゲート電極の形成

図 2 (A) を参照して、まず、基板 11 として  $50 \text{ mm} \times 50 \text{ mm} \times$  厚さ  $0.6 \text{ mm}$  の合成石英ガラス基板を準備し、その基板 11 上にスパッタ法によりゲート電極 12 として厚さ  $100 \text{ nm}$  の Mo 電極を形成した。

#### 【0064】

###### (2) ゲート絶縁膜の形成

図 2 (B) を参照して、次に、ゲート電極 12 上にプラズマ CVD 法によりゲート絶縁膜 13 として厚さ  $200 \text{ nm}$  の非晶質の  $\text{SiO}_x$  膜を形成した。

#### 【0065】

###### (3) 酸化物半導体膜の形成

20

図 2 (C) を参照して、次に、ゲート絶縁膜 13 上に、実施例 1 ~ 実施例 9 のそれぞれの酸化物焼結体から加工されたターゲットを用いた RF (交流) マグнетロンスパッタ法により、厚さ  $35 \text{ nm}$  の酸化物半導体膜 14 を形成した。ここで、ターゲットの直径 3 インチ ( $76.2 \text{ mm}$ ) の平面がスパッタ面であった。

#### 【0066】

具体的には、スパッタリング装置 (図示せず) の成膜室内的水冷している基板ホルダ上に、上記ゲート電極 12 およびゲート絶縁膜 13 が形成された基板 11 をゲート絶縁膜 13 が露出されるように配置した。上記ターゲットをゲート絶縁膜 13 に対向するように  $90 \text{ mm}$  の距離で配置した。成膜室内を  $6 \times 10^{-5} \text{ Pa}$  程度の真空度として、ターゲットを以下のようにしてスパッタリングした。

30

#### 【0067】

まず、ゲート絶縁膜 13 とターゲットとの間にシャッターを入れた状態で、成膜室内へ Ar (アルゴン) ガスと  $\text{O}_2$  (酸素) ガスとの混合ガスを  $0.5 \text{ Pa}$  の圧力まで導入した。混合ガス中の  $\text{O}_2$  ガス含有率は 10 体積 % であった。ターゲットに  $120 \text{ W}$  の RF 電力を印加してスパッタリング放電を起こし、これによってターゲット表面のクリーニング (プレスパッタ) を 10 分間行なった。

#### 【0068】

次いで、同じターゲットに  $120 \text{ W}$  のスパッタ RF 電力を印加して、成膜室内の雰囲気をそのまま維持した状態で、上記シャッターを外すことにより、ゲート絶縁膜 13 上に酸化物半導体膜を成膜した。なお、基板ホルダに対しては、特にバイアス電圧は印加されておらず、水冷がされているのみであった。このとき、酸化物半導体膜 14 の厚さが  $35 \text{ nm}$  となるように成膜時間を設定した。このようにして、酸化物焼結体から加工されたターゲットを用いた RF (交流) マグネットロンスパッタ法により酸化物半導体膜 14 が形成された。かかる酸化物半導体膜 14 は、半導体デバイス 10 である TFT (薄膜トランジスタ) においてチャネル層として機能することになった。各実施例における酸化物半導体膜 14 の成膜速度を表 2 にまとめた。表 2 から、W の含有率が大きくなりすぎると成膜速度が低下することがわかった。

40

#### 【0069】

次に、形成された酸化物半導体膜 14 の一部をエッティングすることにより、ソース電極形成用部 14 s、ドレイン電極形成用部 14 d、およびチャネル部 14 c を形成した。こ

50

ここで、ソース電極形成用部 14 s およびドレイン電極形成用部 14 d の主面の大きさを  $100 \mu m \times 100 \mu m$ 、チャネル長さ  $C_L$  (図 1 (A) および (B) ならびに図 2 を参照して、チャネル長さ  $C_L$  とは、ソース電極とドレイン電極との間のチャネル部 14 c の距離をいう。) が  $60 \mu m$ 、チャネル幅  $C_W$  (図 1 (A) および (B) ならびに図 2 を参照して、チャネル幅  $C_W$  とは、チャネル部 14 c の幅をいう。) が  $30 \mu m$ 、とした。このとき、半導体デバイスである TFT (薄膜トランジスタ) が  $50 mm \times 50 mm$  の基板正面内に  $1 mm$  間隔で縦 48 個 × 横 48 個 (計 2304 個) が配置されるように図 1 および図 2 に記載されたチャネル部 14 c が  $50 mm \times 50 mm$  の基板正面内に  $1 mm$  間隔で縦 48 個 × 横 48 個 (計 2304 個) が配置された。

## 【0070】

10

具体的には、体積比でリン酸 : 酢酸 : 水 = 4 : 1 : 100 であるエッティング水溶液を調製し、ゲート電極 12、ゲート絶縁膜 13 および酸化物半導体膜 14 がこの順に形成された基板 11 を、そのエッティング水溶液に浸漬した。このとき、エッティング水溶液は、ホットバス内で 50 に昇温されていた。

## 【0071】

## (4) ソース電極およびドレイン電極の形成

図 2 (D) を参照して、次に、酸化物半導体膜 14 上にソース電極 15 およびドレイン電極 16 を互いに分離して形成した。

## 【0072】

20

具体的には、酸化物半導体膜 14 のソース電極形成用部 14 s およびドレイン電極形成用部 14 d の主面のみが露出するように、酸化物半導体膜 14 上にレジスト (図示せず) を塗布、露光および現像した。酸化物半導体膜 14 のソース電極形成用部 14 s およびドレイン電極形成用部 14 d のそれぞれの主面上に、スパッタ法により、ソース電極 15 である厚さが  $100 nm$  の Mo 電極とドレイン電極 16 である厚さが  $100 nm$  の Mo 電極とを互いに分離して形成した。その後、酸化物半導体膜 14 上のレジストを剥離した。このようなソース電極 15 およびドレイン電極 16 としての Mo 電極を、一つのチャネル部 14 c に対してそれぞれ 1 つ配置し、半導体デバイスである TFT (薄膜トランジスタ) が  $50 mm \times 50 mm$  の基板正面内に  $1 mm$  間隔で縦 48 個 × 横 48 個 (計 2304 個) が配置されるようにした。これにより、半導体デバイス 10 として、酸化物半導体膜 14 をチャネル層として備える TFT (薄膜トランジスタ) を製造した。

30

## 【0073】

次に、得られた半導体デバイス 10 である TFT を窒素雰囲気中 300 で 1 時間熱処理した。

## 【0074】

## 8. 半導体デバイスの特性評価

半導体デバイスである TFT の特性を以下のようにして評価した。まず、ゲート電極、ソース電極およびドレイン電極に測定針を接触した。ソース電極とドレイン電極との間に  $5 V$  のソース - ドレイン間電圧  $V_{ds}$  を印加し、ソース電極とゲート電極との間に印加するソース - ゲート間電圧  $V_{gs}$  を  $-10 V$  から  $10 V$  に変化させて、そのときのソース - ドレイン間電流  $I_{ds}$  を測定した。ソース - ゲート間電圧  $V_{gs}$  が  $-5 V$  のときのソース - ドレイン間電流  $I_{ds}$  を OFF 電流と定義した。各実施例における OFF 電流の値を表 2 にまとめた。ソース - ゲート間電圧  $V_{gs}$  が  $10 V$  のときのソース - ドレイン間電流  $I_{ds}$  を ON 電流と定義して、OFF 電流の値に対する ON 電流の値の比を表 2 にまとめた。

40

## 【0075】

次に、 $50 mm \times 50 mm$  の基板正面内に  $1 mm$  間隔で縦 48 個 × 横 48 個 (計 2304 個) 配置された半導体デバイスである TFT の全てについて、ソース - ドレイン間電流  $I_{ds}$  が  $1 \times 10^{-6} A$  のときのソース - ゲート間電圧  $V_{gs}$  を求め、 $50 mm \times 50 mm$  の半導体デバイス正面内でのソース - ゲート間電圧  $V_{gs}$  のばらつきを  $V_{gs}$  として表 2 にまとめた。ここで、ばらつき  $V_{gs}$  が小さければ、半導体デバイスである TFT の正面内の特性のばらつきが小さくなることを意味する。

50

【0076】

【表1】

|        | 原料粉末のモル混合比率 |          |          | 添加元素 | 焼結温度<br>(°C) | 結晶相   | シリカ相<br>占有率(%) | タフル相<br>占有率(%) | W含有率<br>(原子%) | 添加元素<br>の含有率<br>(原子%) | 相対<br>熱伝導率 |

|--------|-------------|----------|----------|------|--------------|-------|----------------|----------------|---------------|-----------------------|------------|

|        | I<br>(%)    | W<br>(%) | M<br>(%) |      |              |       |                |                |               |                       |            |

| 実施例 1  | 76.1        | 23.9     | —        | —    | 1400         | A     | 96             | 96             | 13.6          | 0                     | 1          |

| 実施例 2  | 80.0        | 20.0     | —        | —    | 1550         | A,B   | 82             | 98             | 11.1          | 0                     | 1.2        |

| 実施例 3  | 84.9        | 15.1     | —        | —    | 1450         | A,B   | 63             | 100            | 8.1           | 0                     | 1.2        |

| 実施例 4  | 87.7        | 12.3     | —        | —    | 1500         | A,B   | 52             | 100            | 6.5           | 0                     | 1.5        |

| 実施例 5  | 91.7        | 8.3      | —        | —    | 1450         | A,B   | 36             | 100            | 4.3           | 0                     | 1.2        |

| 実施例 6  | 94.8        | 5.2      | —        | —    | 1550         | A,B   | 23             | 98             | 2.7           | 0                     | 1.2        |

| 実施例 7  | 98.9        | 1.1      | —        | —    | 1400         | A,B   | 5              | 96             | 0.6           | 0                     | 1          |

| 実施例 8  | 82.1        | 17.9     | —        | —    | 1300         | A,B,C | 55             | 75             | 9.8           | 0                     | 0.9        |

| 実施例 9  | 79.3        | 20.7     | —        | —    | 1500         | A,B,D | 55             | 85             | 11.6          | 0                     | 0.9        |

| 実施例 10 | 86.0        | 13.1     | 0.9      | A    | 1500         | A,B   | 55             | 100            | 7.0           | 1                     | 1          |

| 実施例 11 | 81.9        | 12.6     | 5.5      | Ti   | 1500         | A,B   | 55             | 100            | 7.0           | 3                     | 1          |

| 実施例 12 | 85.0        | 13.1     | 1.9      | Cr   | 1500         | A,B   | 55             | 100            | 7.0           | 2                     | 1          |

| 実施例 13 | 82.3        | 13.0     | 4.7      | Ga   | 1500         | A,B   | 55             | 100            | 7.0           | 5                     | 1          |

| 実施例 14 | 78.6        | 12.5     | 8.9      | Hf   | 1500         | A,B   | 55             | 100            | 7.0           | 5                     | 1          |

| 実施例 15 | 85.3        | 12.8     | 1.9      | Si   | 1500         | A,B   | 55             | 100            | 7.0           | 1                     | 1          |

| 実施例 16 | 81.4        | 13.0     | 5.6      | V    | 1500         | A,B   | 55             | 100            | 7.0           | 6                     | 1          |

| 実施例 17 | 81.4        | 13.0     | 5.6      | Nb   | 1500         | A,B   | 55             | 100            | 7.0           | 6                     | 1          |

| 実施例 18 | 78.7        | 5.2      | 16.1     | Sn   | 1500         | A,B   | 25             | 100            | 2.9           | 9                     | 1          |

| 実施例 19 | 92.4        | 5.7      | 1.9      | Zr   | 1500         | A,B   | 25             | 100            | 2.9           | 9                     | 1          |

| 実施例 20 | 85.3        | 5.4      | 9.3      | Mo   | 1500         | A,B   | 25             | 100            | 2.9           | 5                     | 1          |

| 実施例 21 | 91.4        | 5.7      | 2.9      | Ta   | 1500         | A,B   | 25             | 100            | 2.9           | 3                     | 1          |

| 実施例 22 | 92.3        | 5.8      | 1.9      | Bi   | 1500         | A,B   | 25             | 100            | 2.9           | 2                     | 1          |

| 比較例 1  | 86.9        | 13.1     | —        | —    | 1500         | B,D   | —              | —              | 7.0           | 0                     | 0.7        |

| 比較例 2  | 90.5        | 9.5      | —        | —    | 1200         | B,C   | —              | —              | 5.0           | 0                     | 0.7        |

| 比較例 3  | 92.3        | 7.7      | —        | —    | 1300         | B,E   | —              | —              | 4.0           | 0                     | 0.7        |

原料欄において、Iは $In_2O_3$ 粉末を、Wは $WO_3$ 粉末を、Mは添加元素の酸化物粉末を、それぞれ示す。

結晶相欄において、Aは $In_6WO_{12}$ 型相を、Bは $In_2O_3$ 型相を、Cは $WO_3$ 型相を、Dは $In_2(WO_4)_3$ 型相を、Eは $InW_3O_9$ 型相を、それぞれ示す。

【0077】

【表2】

|        | 成膜速度<br>(nm/min) | OFF<br>電流<br>(A) | ON電流<br>/OFF電<br>流比(柵) | $\Delta V_{gs}$<br>(V) |

|--------|------------------|------------------|------------------------|------------------------|

| 実施例 1  | 26               | $10^{-13}$       | 8                      | 0.19                   |

| 実施例 2  | 28               | $10^{-13}$       | 8                      | 0.17                   |

| 実施例 3  | 28               | $10^{-13}$       | 8                      | 0.15                   |

| 実施例 4  | 28               | $10^{-13}$       | 8                      | 0.12                   |

| 実施例 5  | 29               | $10^{-13}$       | 8                      | 0.15                   |

| 実施例 6  | 30               | $10^{-13}$       | 8                      | 0.18                   |

| 実施例 7  | 30               | $10^{-12}$       | 8                      | 0.2                    |

| 実施例 8  | 28               | $10^{-12}$       | 8                      | 0.26                   |

| 実施例 9  | 27               | $10^{-12}$       | 8                      | 0.25                   |

| 実施例 10 | 28               | $10^{-13}$       | 8                      | 0.22                   |

| 実施例 11 | 28               | $10^{-13}$       | 8                      | 0.21                   |

| 実施例 12 | 28               | $10^{-13}$       | 8                      | 0.2                    |

| 実施例 13 | 28               | $10^{-13}$       | 8                      | 0.2                    |

| 実施例 14 | 28               | $10^{-13}$       | 8                      | 0.21                   |

| 実施例 15 | 28               | $10^{-13}$       | 8                      | 0.21                   |

| 実施例 16 | 28               | $10^{-13}$       | 8                      | 0.2                    |

| 実施例 17 | 28               | $10^{-13}$       | 8                      | 0.22                   |

| 実施例 18 | 27               | $10^{-12}$       | 9                      | 0.21                   |

| 実施例 19 | 27               | $10^{-12}$       | 9                      | 0.22                   |

| 実施例 20 | 27               | $10^{-12}$       | 9                      | 0.21                   |

| 実施例 21 | 27               | $10^{-12}$       | 9                      | 0.2                    |

| 実施例 22 | 27               | $10^{-12}$       | 9                      | 0.2                    |

| 比較例 1  | 20               | $10^{-11}$       | 5                      | 0.35                   |

| 比較例 2  | 23               | $10^{-11}$       | 5                      | 0.3                    |

| 比較例 3  | 24               | $10^{-11}$       | 5                      | 0.4                    |

10

20

30

## 【0078】

(実施例10～実施例22)

原料粉末の混合物の調製の際に、原料粉末として、 $In_2O_3$ 粉末および $WO_3$ 粉末の他に、表1の実施例10～実施例22に示すように、添加元素を含む酸化物粉末( $Al_2O_3$ 、 $TiO_2$ 、 $Cr_2O_3$ 、 $Ga_2O_3$ 、 $HfO_2$ 、 $SiO_2$ 、 $V_2O_5$ 、 $Nb_2O_3$ 、 $SnO_2$ 、 $ZrO_2$ 、 $MoO_2$ 、 $Ta_2O_3$ 、 $Bi_2O_3$ )を添加したこと以外は、実施例1～実施例9の場合と同様にして、酸化物焼結体を作製した。添加元素を含む酸化物粉末のモル混合比率を表1に示した。得られた酸化物焼結体をターゲットに加工して、かかるターゲットを用いたRFマグネットロンスパッタ法により形成された酸化物半導体膜を含む半導体デバイスであるTFTを作製した。

## 【0079】

得られた酸化物焼結体の物性および半導体デバイスであるTFTの特性を表1にまとめた。ここで、酸化物焼結体の添加元素を含む金属元素およびSiの含有量をICP質量分析法により測定し、金属元素およびSiの含有率に対する添加元素の含有量の百分率である添加元素の含有率を表1にまとめた。酸化物焼結体の物性を表1にまとめ、半導体デバイスであるTFTの特性を表2にまとめた。

## 【0080】

(比較例1～比較例3)

酸化物焼結体の作製の際、原料粉末の混合物を調製した後、仮焼をすることなく、原料粉末の混合物を成形し焼結したこと以外は、実施例1～実施例9の場合と同様にして、酸化物焼結体を作製してターゲットに加工して、かかるターゲットを用いたRFマグネットロンスパッタ法により形成された酸化物半導体膜を含む半導体デバイスであるTFTを作製した。比較例1～比較例3の間は、 $In_2O_3$ 粉末と $WO_3$ 粉末とのモル混合比率ならびに焼結温度が異なった。酸化物焼結体の物性を表1にまとめ、半導体デバイスであるTFT

40

50

の特性を表2にまとめた。

【0081】

表1を参照して、少なくともインジウムおよびタンゲステンを含み結晶相として少なくとも $In_6WO_{12}$ 型相を含む酸化物焼結体を用いて形成された酸化物半導体膜をチャネル層として含む半導体デバイスであるTFT(薄膜トランジスタ)は、そのOFF電流を $1 \times 10^{-11} A$ 未満に低下させるとともに、低い駆動電圧でOFF電流に対するON電流の比を8桁(8桁とは、 $1 \times 10^8$ 以上 $1 \times 10^9$ 未満を意味する。以下同じ。)と高くすることができた。また、酸化物焼結体の熱伝導率を高くすることができます。なお、表2におけるOFF電流に対するON電流の比の欄において、9桁とは $1 \times 10^9$ 以上 $1 \times 10^{10}$ 未満を意味し、5桁とは $1 \times 10^5$ 以上 $1 \times 10^6$ 未満を意味する。

10

【0082】

今回開示された実施の形態および実施例はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は、上記した説明でなく特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内のすべての変更が含まれることが意図される。

【符号の説明】

【0083】

10 半導体デバイス

20

11 基板

12 ゲート電極

13 ゲート絶縁膜

14 酸化物半導体膜

14c チャネル部

14d ドレイン電極形成用部

14s ソース電極形成用部

15 ソース電極

16 ドレイン電極

【図1】

【図2】

---

フロントページの続き

(72)発明者 曽我部 浩一

兵庫県伊丹市昆陽北一丁目1番1号 住友電気工業株式会社 伊丹製作所内

審査官 小川 武

(56)参考文献 国際公開第2012 / 105323 (WO, A1)

特開2004 - 091265 (JP, A)

Electronic structure and photocatalytic properties of In<sub>2</sub>W<sub>0</sub>12, Journal of Physics: Condensed Matter, 2007年

Charge transfer in In<sub>2</sub>W<sub>3</sub>O<sub>12</sub> and In<sub>6</sub>W<sub>0</sub>12 ceramics, Solid State Ionics, 2008年

(58)調査した分野(Int.Cl., DB名)

C 04 B 35 / 00 - 35 / 84

C 23 C 14 / 34