(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第5355006号

(P5355006)

(45) 発行日 平成25年11月27日(2013.11.27)

(24) 登録日 平成25年9月6日(2013.9.6)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 27/00  | (2006.01) | HO1L 27/00 | 301B |

| HO1L 21/336 | (2006.01) | HO1L 29/78 | 612D |

| HO1L 29/786 | (2006.01) | HO1L 29/78 | 613Z |

| HO1L 21/02  | (2006.01) | HO1L 29/78 | 627D |

| HO1L 27/12  | (2006.01) | HO1L 29/78 | 62O  |

請求項の数 5 (全 48 頁) 最終頁に続く

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2008-237282 (P2008-237282) |

| (22) 出願日     | 平成20年9月17日 (2008.9.17)       |

| (65) 公開番号    | 特開2009-94492 (P2009-94492A)  |

| (43) 公開日     | 平成21年4月30日 (2009.4.30)       |

| 審査請求日        | 平成23年6月23日 (2011.6.23)       |

| (31) 優先権主張番号 | 特願2007-243925 (P2007-243925) |

| (32) 優先日     | 平成19年9月20日 (2007.9.20)       |

| (33) 優先権主張国  | 日本国 (JP)                     |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 川俣 郁子<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 宮口 厚<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内    |

審査官 宇多川 勉

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の半導体層を有する第1の電界効果トランジスタと、第2の半導体層を有する第2の電界効果トランジスタと、表示素子と、を有し、

前記第1の電界効果トランジスタのソース又はドレインの一方は、前記表示素子と電気的に接続され、

前記第1の電界効果トランジスタのゲートは、前記第2の電界効果トランジスタのソース又はドレインの一方と電気的に接続された表示装置であって、

前記第1の電界効果トランジスタ上には第1の平坦化層が設けられ、

前記第1の平坦化層上には前記第2の電界効果トランジスタが設けられ、

10

前記第2の電界効果トランジスタ上には第2の平坦化層が設けられ、

前記第2の平坦化層上には配線が設けられ、

前記配線上には第3の平坦化層が設けられ、

前記第3の平坦化層上には前記表示素子が設けられ、

前記第1の電界効果トランジスタのゲートと、前記第2の電界効果トランジスタのソース又はドレインの一方と、は前記配線により電気的に接続されており、

前記配線は、前記第2の平坦化層、前記第2の半導体層、及び前記第1の平坦化層を貫通して形成されていることを特徴とする表示装置。

## 【請求項 2】

請求項1において、

20

前記第1の平坦化層上であって前記第2の平坦化層下には、第3の電界効果トランジスタが設けられ、

前記配線は前記第3の電界効果トランジスタのソース又はドレインの一方に電気的に接続されていることを特徴とする表示装置。

**【請求項3】**

請求項1又は請求項2において、

前記第1の半導体層と同一層の第3の半導体層を有する容量素子を有し、

前記容量素子は、前記第1の電界効果トランジスタのゲートと電気的に接続されていることを特徴とする表示装置。

**【請求項4】**

請求項1乃至請求項3のいずれか一項において、

前記第1の電界効果トランジスタはpチャネル型電界効果トランジスタであり、

前記第2の電界効果トランジスタはnチャネル型電界効果トランジスタであり、

前記第1の半導体層はチャネル長方向が<110>軸となるように形成されており、

前記第2の半導体層はチャネル長方向が<100>軸となるように形成されていることを特徴とする表示装置。

**【請求項5】**

請求項4において、

前記第1の半導体層は、{110}面の第1の半導体基板より分離して設けられたものであり、

前記第2の半導体層は、{100}面の第2の半導体基板より分離して設けられたものであることを特徴とする表示装置。

10

20

30

40

50

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は表示装置に関する。特に、本発明は絶縁表面に半導体層が設けられた電界効果トランジスタを用いて3次元的に画素回路が構成された表示装置に関する。

**【背景技術】**

**【0002】**

近年、絶縁表面に薄い単結晶半導体層を設けたシリコン・オン・インシュレータ（以下、「SOI」ともいう）と呼ばれる半導体基板を使った構造が注目されている。この構造は、バルク単結晶シリコンで形成されていた電界効果トランジスタ（FET；Field Effect Transistor、単にトランジスタと略記することもある）の活性領域（チャネル形成領域）を、単結晶シリコン薄膜とする技術である。

**【0003】**

SOI基板を製造する方法としては、水素イオン注入剥離法が知られている（例えば、特許文献1参照）。水素イオン注入剥離法は、シリコンウエハーに水素イオンを注入することによって表面から所定の深さに微小気泡層を形成し、該微小気泡層を劈開面として、別のシリコンウエハーに薄いシリコン層を接合する。さらにシリコン層を剥離する熱処理を行うことに加え、酸化性雰囲気下での熱処理によりシリコン層に酸化膜を形成した後に該酸化膜を除去し、次に1000から1300で熱処理を行って接合強度を高める必要があるとされている。そのため、ガラス基板のような高温熱処理に耐えることのできない基板上には、シリコン層の接合を所望の接合強度で貼り付けることは難しく、表示装置の画素を構成する電界効果トランジスタへの転用を単純に行うこととは技術的な障壁がある。

**【0004】**

一方、剥離技術及び転写技術を用いて作製されたトランジスタを含む薄膜回路と、当該薄膜回路に外部回路を接続するための接続電極を設け、3次元的に薄膜回路を積層する技術を用いて画素を構成するトランジスタを具備する表示装置について開示されている（特許

文献 2 参照)。

【特許文献 1】特開 2000-124092 号公報

【特許文献 2】特開 2004-349513 号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

表示装置の画素を構成する電界効果トランジスタ数は、表示装置の高性能化を図る上で増加する傾向にある。また、表示装置の画素のサイズを小さくすることで、同じサイズでの表示部の画素数を増やし、画素の高精細化を図る傾向にある。そのため、電界効果トランジスタ数の増加に伴い低下した画素の開口率を向上及び画素に占める電界効果トランジスタの面積を削減するため、電界効果トランジスタの微細化を行うことで対応することも考えられる。10

【0006】

また、表示装置の高性能化を図る上で、電界効果トランジスタの微細化と共に、表示装置の画素を構成する電界効果トランジスタの半導体層の高性能化を考えることも必要である。。

【0007】

しかしながら、表示装置の画素を構成する電界効果トランジスタの微細加工技術に依拠するのみで、表示装置の高性能化を図ることは限界がある。また、剥離技術及び転写技術を用いて、3次元的に画素を構成する電界効果トランジスタを積層し、電界効果トランジスタ数の増加に伴う低下した画素の開口率の向上及び画素に占める電界効果トランジスタの面積の削減を図ることができるもの、剥離した後に転写した薄膜回路同士の電気的な接続が困難であり、量産性の観点から好ましくない。そのため、SOI 技術のように簡便に高性能な電界効果トランジスタの半導体層が得られ、量産性に優れた技術により3次元的に薄膜回路を積層する技術が求められている。20

【0008】

そこで本発明は、表示装置の画素を構成する電界効果トランジスタの高性能化を実現し、且つ電界効果トランジスタの微細加工技術に依拠することなく、画素内の電界効果トランジスタ数を増やしても電界効果トランジスタ数の増加に伴い低下した画素の開口率を向上及び画素に占める電界効果トランジスタの面積の削減を図ることのできる表示装置を提供することを目的のとする。30

【課題を解決するための手段】

【0009】

半導体基板より分離され、絶縁表面を有する支持基板に接合された半導体層を有する電界効果トランジスタ等の半導体素子が、平坦化層を層間に設けて複数積層された画素を複数具備する表示装置とする。

【0010】

ゲート絶縁層、平坦化層、上層の絶縁層などを間に挟んで積層する下層の半導体層と上層の半導体層とは、該ゲート絶縁層、平坦化層、及び上層の絶縁層を貫通する配線層によって電気的に接続する。下層の半導体層と上層の半導体層とが重なって積層される場合、配線層は上層の半導体層を貫通して下層の半導体層と接して形成されてもよい。積層する半導体層が重なり合うように密に積層されることで、高集積化された電界効果トランジスタで構成される画素を有する表示装置とすることができる。40

【0011】

半導体基板より分離させ転置した半導体層で構成される高性能の半導体素子を積層構造とすることができるため、より高集積化された電界効果トランジスタで構成される画素を有する表示装置とすることができます。

【0012】

下層の半導体素子上に形成される上層の半導体素子の形成において、下層の半導体素子を覆う平坦化層を形成し、平坦化層上に半導体層と接合する絶縁層を形成する。よって上層50

の半導体素子の半導体層と絶縁層との接合を容易に行うことができ、表示装置の信頼性を向上させることができ、歩留まりも良くなる。

**【 0 0 1 3 】**

また、電界効果トランジスタを形成する半導体層をそれぞれ異なる絶縁層に接合して形成すると、電界効果トランジスタの半導体層間の寄生容量、又は電界効果トランジスタのゲート電極層間の寄生容量を低減することができる。

**【 0 0 1 4 】**

半導体基板より分離させ転置した半導体層を用いるため、半導体基板を選択することによって、電界効果トランジスタにおける結晶面方位及びチャネル長方向の結晶軸を制御することができる。

10

**【 0 0 1 5 】**

電界効果トランジスタのチャネルを流れるキャリアにとって移動度が高くなる結晶面方位又は結晶軸を適用することにより、表示装置を構成する画素の動作の高速化を図ることができる。また、低電圧で駆動することが可能となり、低消費電力化を図ることができる。すなわち、電界効果トランジスタのチャネルを流れるキャリアが原子で散乱される確率を低減することができ、それによって電子又はホールの受ける抵抗を減少させ、電界効果トランジスタの性能向上を図ることができる。

**【 0 0 1 6 】**

支持基板に、半導体層を接合するに際し、接合を形成する面の一方（半導体層側または支持基板側）若しくは双方（半導体層側及び支持基板側）に、好ましくは有機シランを原材料として成膜した酸化シリコン膜を形成し、半導体層と接合する絶縁層として用いることができる。有機シランガスとしては、珪酸エチル（T E O S：化学式 Si(O<sub>2</sub>H<sub>5</sub>)<sub>4</sub>）、トリメチルシラン（T M S：化学式 (C H<sub>3</sub>)<sub>3</sub>SiH）、テトラメチルシラン（化学式 Si(C H<sub>3</sub>)<sub>4</sub>）、テトラメチルシクロテトラシロキサン（T M C T S）、オクタメチルシクロテトラシロキサン（O M C T S）、ヘキサメチルジシラザン（H M D S）、トリエトキシシラン（SiH(O C<sub>2</sub>H<sub>5</sub>)<sub>3</sub>）、トリスジメチルアミノシラン（SiH(N(C H<sub>3</sub>)<sub>2</sub>)<sub>3</sub>）等のシリコン含有化合物が適用される。すなわち、支持基板に半導体層を接合する構造において、平滑面を有し親水性表面を形成する層を接合面として設ける。

20

**【 0 0 1 7 】**

なお、本明細書における化学気相成長（C V D；Chemical Vapor Deposition）法は、プラズマC V D法、熱C V D法、光C V D法を範疇に含むものとする。

30

**【 0 0 1 8 】**

また、半導体層と接合する絶縁層となる酸化シリコン膜は、モノシラン、ジシラン、又はトリシランを原料ガスに用いて化学気相成長法により形成することもできる。また、半導体層と接合する絶縁層となる酸化シリコン膜は熱酸化膜でもよく、塩素を含んでいると好適である。

**【 0 0 1 9 】**

支持基板に接合される半導体層は、半導体基板に形成された脆化層にて劈開し分離することにより得られる。脆化層は水素、ヘリウム若しくはフッ素に代表されるハロゲンのイオンを打ち込むことで形成することができる。この場合、一又は複数の同一の原子から成る質量の異なるイオンを打ち込んでもよい。水素イオンを打ち込む場合には、H<sup>+</sup>、H<sub>2</sub><sup>+</sup>、H<sub>3</sub><sup>+</sup>イオンを含ませると共に、H<sub>3</sub><sup>+</sup>イオンの割合を高めておくことが好ましい。

40

**【 0 0 2 0 】**

支持基板には、不純物元素の拡散を防止する窒化シリコン膜又は窒化酸化シリコン膜をブロッキング層（バリア層ともいう）として設けてもよい。さらに応力を緩和する作用のある絶縁膜として酸化窒化シリコン膜を組み合わせても良い。なお、酸化窒化シリコン膜とは、その組成として、窒素よりも酸素の含有量が多いものであって、ラザフォード後方散乱法（R B S：Rutherford Backscattering Spectro

50

metry) 及び水素前方散乱法 (HFS : Hydrogen Forward Scattering) を用いて測定した場合に、濃度範囲として酸素が 50 ~ 70 原子%、窒素が 0.5 ~ 15 原子%、Si が 25 ~ 35 原子%、水素が 0.1 ~ 10 原子% の範囲で含まれるものという。また、窒化酸化シリコン膜とは、その組成として、酸素よりも窒素の含有量が多いものであって、RBS 及び HFS を用いて測定した場合に、濃度範囲として酸素が 5 ~ 30 原子%、窒素が 20 ~ 55 原子%、Si が 25 ~ 35 原子%、水素が 10 ~ 30 原子% の範囲で含まれるものという。但し、酸化窒化シリコンまたは窒化酸化シリコンを構成する原子の合計を 100 原子%としたとき、窒素、酸素、Si 及び水素の含有比率が上記の範囲内に含まれるものとする。

## 【0021】

10

また、半導体基板と上記半導体層と接合する絶縁層との間に、保護層を形成してもよい。保護層は、窒化シリコン層、酸化シリコン層、窒化酸化シリコン層、又は酸化窒化シリコン層から選ばれた一層又は複数の層による積層構造により形成することができる。これらの層は、半導体基板に脆化層が形成される前に半導体基板上に形成することができる。また、半導体基板に脆化層を形成した後に半導体基板上に形成してもよい。

## 【0022】

本発明の表示装置の一形態は、絶縁表面を有する基板上に、第1の半導体層、第1のゲート絶縁層、第1のゲート電極層、第1のソース電極層及び第1のドレイン電極層を含む第1の電界効果トランジスタと、前記第1の電界効果トランジスタ上に平坦化層と、前記平坦化層上に、第2の半導体層、第2のゲート絶縁層、第2のゲート電極層、第2のソース電極層及び第2のドレイン電極層を含む第2の電界効果トランジスタと、を積層構造で有する画素を複数有し、第1の半導体層及び第2の半導体層は半導体基板より分離して設けられており、前記第1の電界効果トランジスタは、前記第1の半導体層と前記絶縁表面を有する基板との間に形成された第1の絶縁層と接合して前記絶縁表面を有する基板上に設けられ、前記第2の電界効果トランジスタは、前記平坦化層上に設けられた第2の絶縁層と接合して前記第1の電界効果トランジスタ上に設けられることを特徴とする。

20

## 【0023】

本発明の表示装置の一形態は、絶縁表面を有する基板上に、第1の半導体層、第1のゲート絶縁層、第1のゲート電極層、第1のソース電極層及び第1のドレイン電極層を含む第1の電界効果トランジスタと、前記第1の電界効果トランジスタ上に平坦化層と、前記平坦化層上に、第2の半導体層、第2のゲート絶縁層、第2のゲート電極層、第2のソース電極層及び第2のドレイン電極層を含む第2の電界効果トランジスタと、を積層構造で有する画素を複数有し、第1の半導体層及び第2の半導体層は半導体基板より分離して設けられており、前記第1の電界効果トランジスタは、前記第1の半導体層と前記絶縁表面を有する基板との間に形成された第1の絶縁層と接合して前記絶縁表面を有する基板上に設けられ、前記第2の電界効果トランジスタは、前記平坦化層上に設けられた第2の絶縁層と接合して前記第1の電界効果トランジスタ上に設けられ、前記第1の半導体層と、前記第2の半導体層の結晶面方位は互いに異なることを特徴とする。

30

## 【0024】

40

本発明の表示装置の一形態は、絶縁表面を有する基板上に、第1の半導体層、第1のゲート絶縁層、第1のゲート電極層、第1のソース電極層及び第1のドレイン電極層を含む第1の電界効果トランジスタと、前記第1の電界効果トランジスタ上に平坦化層と、前記平坦化層上に、第2の半導体層、第2のゲート絶縁層、第2のゲート電極層、第2のソース電極層及び第2のドレイン電極層を含む第2の電界効果トランジスタと、を積層構造で有する画素を複数有し、第1の半導体層及び第2の半導体層は半導体基板より分離して設けられており、前記第1の電界効果トランジスタは、前記第1の半導体層と前記絶縁表面を有する基板との間に形成された第1の絶縁層と接合して前記絶縁表面を有する基板上に設けられ、前記第2の電界効果トランジスタは、前記平坦化層上に設けられた第2の絶縁層と接合して前記第1の電界効果トランジスタ上に設けられ、前記第1の半導体層と、前記第2の半導体層の結晶面方位は同じであり、チャネル長方向の結晶軸は互いに異なること

50

を特徴とする。

【0025】

なお、本発明において、表示装置とは、液晶素子やEL素子などの表示素子を含む複数の画素やそれらの画素を駆動させる周辺駆動回路が同一基板上に形成された表示パネル本体のことをいう。また本発明における表示装置は、周辺駆動回路、いわゆるチップオングラス(COG)で接続されたICチップなどを含んでいても良い。さらに本発明における表示装置は、ICや抵抗素子や容量素子やインダクタやトランジスタなどが取り付けられたフレキシブルプリントサーキット(FPC)又はプリント配線基板(PWB)も含んでもよい。さらに、偏光板や位相差板などの光学シートを含んでいても良い。さらに、バックライトユニット(導光板やプリズムシートや拡散シートや反射シートや光源(LEDや冷陰極管など)を含んでいても良い)を含んでいても良い。なお、発光装置は、特にEL素子やFEDで用いる素子などの自発光型の表示素子を有している表示装置をいい、液晶表示装置とは、特に液晶素子を有している表示装置をいう。10

【発明の効果】

【0026】

電界効果トランジスタを構成する半導体層を半導体基板より分離して設ける構成とすることにより、表示装置の画素を構成する電界効果トランジスタの高性能化を実現することができる。また画素に設ける電界効果トランジスタを積層構造で設けることができるため、電界効果トランジスタの微細加工技術に依拠することなく、画素内の電界効果トランジスタ数を増やしても電界効果トランジスタ数の増加に伴い低下した画素の開口率を向上及び画素に占める電界効果トランジスタの面積の削減を図ることのできる表示装置を提供することができる。20

【発明を実施するための最良の形態】

【0027】

本発明の実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。30

(実施の形態1)

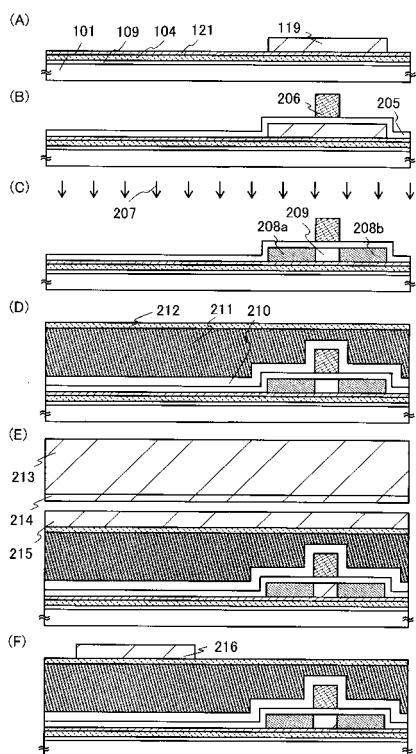

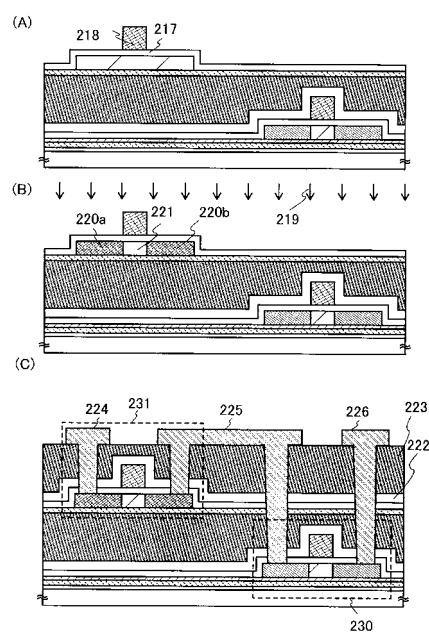

【0028】

本発明の表示装置の製造方法について、図1乃至図6を参照して説明する。本実施の形態では、表示装置の一例として電界効果トランジスタを具備する画素の構成に関して示し説明する。特に本実施の形態では、異なる平面上に形成された電界効果トランジスタの電気的な接続方法について断面図を用いて説明していく。

【0029】

本実施の形態では、半導体基板より分離され、絶縁表面を有する支持基板(または、絶縁表面を有する基板ともいう)に接合された半導体層を有する電界効果トランジスタ上に平坦化層を設けて積層していく。半導体基板として単結晶半導体基板を適用し、支持基板上に分離、接合される半導体層として単結晶半導体層を形成するのが好ましい。40

【0030】

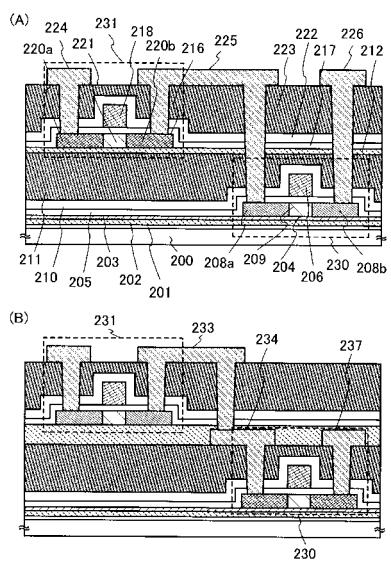

本実施の形態の表示装置の画素を構成する電界効果トランジスタの断面図について図1(A)に示す。絶縁表面を有する支持基板200上にプロッキング層201、絶縁層202、保護層203、電界効果トランジスタ230、絶縁層210、平坦化層211、絶縁層212、電界効果トランジスタ231、絶縁層222、平坦化層223が形成されている。電界効果トランジスタ230及び電界効果トランジスタ231は薄膜の半導体層を有する。電界効果トランジスタ230はソース領域又はドレイン領域である不純物領域208a、不純物領域208b、及びチャネル形成領域209を含む半導体層204、ゲート絶縁層205、ゲート電極層206を有しており、電界効果トランジスタ231はソース領50

域又はドレイン領域である不純物領域 220a、不純物領域 220b、及びチャネル形成領域 221を含む半導体層 216、ゲート絶縁層 217、ゲート電極層 218を有している。不純物領域 208bに接して配線層 226、不純物領域 220aに接して配線層 224が形成され、不純物領域 208aと不純物領域 220bとに接して形成された配線層 225によって、電界効果トランジスタ 230及び電界効果トランジスタ 231は電気的に接続している。

#### 【0031】

図 1 (A) に示した異なる平面上に形成された電界効果トランジスタの電気的な接続は、配線層 225 及び配線層 226 にて、ゲート絶縁層 205、絶縁層 210、平坦化層 211、絶縁層 212、ゲート絶縁層 217、絶縁層 222、及び平坦化層 223 を連続して貫通するように形成された開口 (コンタクトホール) で確保されている例である。電界効果トランジスタ 230 及び電界効果トランジスタ 231 の電気的接続の他の例を図 1 (B) に示す。

#### 【0032】

配線層 224、配線層 225、配線層 226 は、CVD 法やスパッタリング法を用いて、アルミニウム (Al)、タンクステン (W)、チタン (Ti)、タンタル (Ta)、モリブデン (Mo)、ニッケル (Ni)、白金 (Pt)、銅 (Cu)、金 (Au)、銀 (Ag)、マンガン (Mn)、ネオジム (Nd)、炭素 (C)、シリコン (Si) 等の金属元素、又は当該金属元素を含む合金材料若しくは化合物材料を用いて基板全面に導電膜を単層構造又は積層構造で形成した後、当該導電膜を選択的にエッチングして形成することもできる。アルミニウムを含む合金材料としては、例えば、アルミニウムを主成分としニッケルを含む材料、又は、アルミニウムを主成分とし、ニッケルと、炭素とシリコンの一方又は両方とを含む合金材料があげられる。また、タンクステンを含む化合物材料としては、例えばタンクステンシリサイドが挙げられる。例えば、配線層としては、バリア層とアルミニウムシリコン (Al-Si) 層とバリア層の積層構造、バリア層とアルミニウムシリコン (Al-Si) 層と窒化チタン層とバリア層の積層構造を採用することができる。なお、バリア層とは、チタン、チタンの窒化物、モリブデン、又はモリブデンの窒化物からなる薄膜に相当する。アルミニウムやアルミニウムシリコンは抵抗値が低く、安価であるため、配線層を形成する材料として好適である。また、配線層を、上層と下層にバリア層を設けた積層構造とすると、アルミニウムやアルミニウムシリコンのヒロックの発生を防止することができるため好適である。また配線層 224、配線層 225、配線層 226 は、コンタクトホールである開口を埋めるように埋込配線層を形成した後、埋込配線層上に引き回し配線層を形成した積層構造としてもよい。また配線層は、開口にバリアメタル膜やシード膜を形成しても良い。なお、図 1 (B)、図 2 (A)、及び図 2 (B) における配線層 233、配線層 234、配線層 235、配線層 236、及び配線層 237 も配線層 224、配線層 225、配線層 226 と同様に積層構造の配線層となっている。

#### 【0033】

図 1 (B) の表示装置の画素を構成する電界効果トランジスタの断面図は、電界効果トランジスタ 230 を覆う平坦化層 211 を形成後、ゲート絶縁層 205、絶縁層 210、及び平坦化層 211 に、不純物領域 208a、不純物領域 208b に達する開口を設け、不純物領域 208a、不純物領域 208b にそれぞれ接続する配線層 234、配線層 237 を形成する例である。電界効果トランジスタ 231 の不純物領域 220b 及び配線層 234 に接する配線層 233 によって、上層の電界効果トランジスタ 231 と下層の電界効果トランジスタ 230 とが電気的に接続する。図 1 (B) の場合、配線層 234、配線層 237 上にさらに平坦化層を形成し、配線層 234、配線層 237 によって生じる凹凸を平坦化した後、絶縁層 212 を形成してもよい。図 1 (B) では、絶縁層 212 を厚く設け、平坦化層としても機能させている。

#### 【0034】

なお本明細書において接続とは、特に記載のない限り電気的な接続を意味するものとする。

10

20

30

40

50

## 【0035】

また、異なる平面に積層する電界効果トランジスタの導電型はn型であってもp型であってもよく、図1(A)においては、下層の電界効果トランジスタ230が不純物領域208a、不純物領域208bとしてn型不純物領域を有するnチャネル型電界効果トランジスタ、上層の電界効果トランジスタ231が不純物領域220a、不純物領域220bとしてp型不純物領域を有するpチャネル型電界効果トランジスタの例である。一方、図1(B)においては、下層の電界効果トランジスタ230が不純物領域208a、不純物領域208bとしてpチャネル型不純物領域を有するp型電界効果トランジスタ、上層の電界効果トランジスタ231が不純物領域220a、不純物領域220bとしてn型不純物領域を有するnチャネル型電界効果トランジスタの例である。

10

## 【0036】

ゲート絶縁層、平坦化層、上層の絶縁層などを間に挟んで積層する下層の半導体層と上層の半導体層とは、該ゲート絶縁層、平坦化層、及び上層の絶縁層を貫通する配線層によって電気的に接続される。下層の半導体層と上層の半導体層とが重なって積層される場合、配線層は上層の半導体層を貫通して下層の半導体層と接して形成されてもよい。積層する半導体層が重なり合うように密に積層されると、より高集積化された電界効果トランジスタで構成された画素を有する表示装置とすることができる。

## 【0037】

下層の半導体層と上層の半導体層とが重なって積層する電界効果トランジスタで構成された表示装置の画素の例を図2(A)および図2(B)に示す。図2(A)において、下層の半導体素子である電界効果トランジスタ230の半導体層204(不純物領域208a)、及び上層の半導体素子である電界効果トランジスタ231の半導体層216(不純物領域220b)は一部重なって積層している。電界効果トランジスタ230及び電界効果トランジスタ231を電気的に接続する配線層235は、ゲート絶縁層205、絶縁層210、平坦化層211、絶縁層212、半導体層216(不純物領域220b)、ゲート絶縁層217、絶縁層222、及び平坦化層223を貫通し半導体層204(不純物領域208a)に達して形成されている。

20

## 【0038】

図2(A)の電界効果トランジスタ230の半導体層204と電界効果トランジスタ231の半導体層216とは一部重なるように形成する例であるが、図2(B)に示すように同じマスクなどを用いて、半導体層同士をほぼ重ねて形成してもよい。半導体層同士が重なる領域が大きいほどより高集積化することはできる。図2(B)においては、電界効果トランジスタ230と電界効果トランジスタ231とは平坦化層を介してほぼ同位置に重なるように積層している。電界効果トランジスタ230及び電界効果トランジスタ231を電気的に接続する配線層236は、ゲート絶縁層205、絶縁層210、平坦化層211、絶縁層212、半導体層216(不純物領域220b)、ゲート絶縁層217、絶縁層222、及び平坦化層223を貫通し半導体層204(不純物領域208b)に達して形成されている。

30

## 【0039】

本発明の表示装置は、3次元的に半導体層を積層し高集積化した構造の電界効果トランジスタで構成された画素を有するため、半導体層は同一絶縁層に接して隣接して配置されると、上下方向に平坦化層を介して異なる絶縁層に接して積層することができる。従って、画素内の電界効果トランジスタの配置の自由度が広く、より高集積化、高性能化を達成することができる。そして画素の開口率の向上及び画素に占める電界効果トランジスタの面積の削減を図ることができる。

40

## 【0040】

また、半導体基板より分離させた半導体層を有する半導体素子は、結晶化工程によって結晶化させた多結晶半導体層より結晶粒界によるリーク電流が少なく、表示装置として低消費電力化が達成できる。さらに結晶配向のばらつきによる半導体素子のしきい値ばらつきが少ない。レーザ結晶化によって生じる半導体層表面のリッジも軽減できるため、ゲート

50

絶縁層を薄膜化することができる。

【0041】

3次元的に積層される電界効果トランジスタは両方n型であってもよく、両方p型であってもよい。また同じ絶縁層に接して複数の電界効果トランジスタを設け、同一絶縁層に接して導電型の異なるnチャネル型電界効果トランジスタ及びpチャネル型電界効果トランジスタを両方設けてもよい。

【0042】

本実施の形態では2層の積層構造を示すが、より多層の積層構造としてもよい。複数の電界効果トランジスタは平坦化層上に設けられた絶縁層と半導体層上に設けられた絶縁層を接合することによって、積層することができる。

10

【0043】

本実施の形態の表示装置の画素を構成する電界効果トランジスタにおいては、半導体基板より分離させ転置した半導体層を用いるため、半導体基板を選択することによって、電界効果トランジスタにおける結晶面方位及びチャネル長方向の結晶軸を制御することができる。

【0044】

電界効果トランジスタのチャネルを流れるキャリアにとって移動度が高くなる結晶面方位又は結晶軸を適用することにより、表示装置の画素を構成する電界効果トランジスタの動作の高速化を図ることができる。また、画素を構成する電界効果トランジスタを低電圧で駆動することが可能となり、低消費電力化を図ることができる。すなわち、電界効果トランジスタのチャネルを流れるキャリアが原子で散乱される確率を低減することができ、それによって電子又はホールの受ける抵抗を減少させ、電界効果トランジスタの性能向上を図ることができる。

20

【0045】

以下、本実施の形態の表示装置の画素を構成する電界効果トランジスタの作製方法を図3乃至図6を用いて説明する。

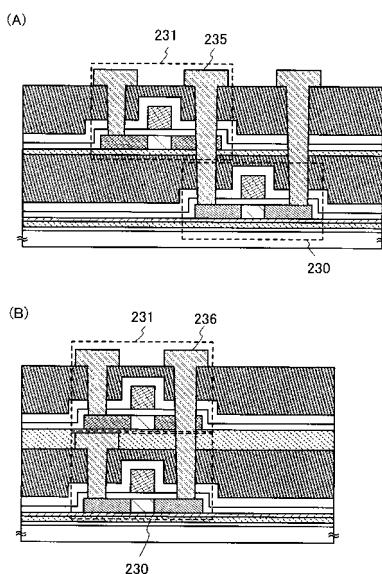

【0046】

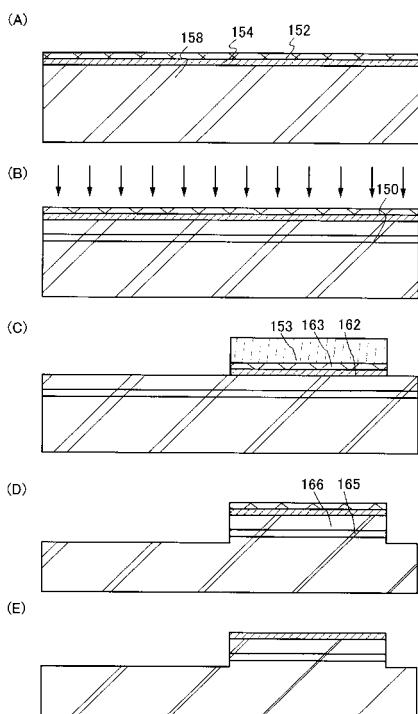

まず、絶縁表面を有する基板である支持基板上に、半導体基板より半導体層を設ける方法を図3(A)乃至(D)及び図4(A)乃至(D)を用いて説明する。

30

【0047】

図3(A)に示す半導体基板108は清浄化されており、その表面から電界で加速されたイオンを所定の深さに打ち込み、脆化層110を形成する。イオンの打ち込みは支持基板に転置する半導体層の厚さを考慮して行われる。イオンを打ち込む際の加速電圧はこのような厚さを考慮して、半導体基板108に打ち込まれるようにする。

【0048】

半導体基板108として、シリコン基板やゲルマニウム基板などの半導体基板、ガリウムヒ素やインジウムリンなどの化合物半導体基板を適用する。半導体基板108は単結晶半導体基板を適用するのが好ましいが、多結晶半導体基板を適用してもよい。結晶格子に歪みを有するシリコン、シリコンに対しゲルマニウムが添加されたシリコンゲルマニウムなどの半導体基板を用いていても良い。歪みを有するシリコンは、シリコンよりも格子定数の大きいシリコンゲルマニウムまたは窒化珪素上における成膜により、形成することができる。支持基板上に得られる半導体層は母体となる半導体基板を選択することによって決定することができる。

40

【0049】

また、半導体基板108は、作製する半導体素子(本実施の形態においては電界効果トランジスタ)によって、結晶面方位を選択すればよい。例えば、結晶面方位として{100}面、{110}面など有する半導体基板を用いることができる。

【0050】

本実施の形態は、半導体基板の所定の深さに水素、ヘリウム、又はフッ素のイオンを打ち込み、その後熱処理を行って表層の半導体層を分離するイオン打ち込み剥離法で形成する

50

が、ポーラスシリコン上に単結晶シリコンをエピタキシャル成長させた後、ポーラスシリコン層をウォータージェットで劈開して分離する方法を適用しても良い。

#### 【0051】

例えば、半導体基板108として単結晶シリコン基板を用い、希フッ酸で表面を処理し、自然酸化膜の除去と表面に付着するゴミ等の汚染物も除去して半導体基板108表面を清浄化する。

#### 【0052】

脆化層110は、イオンをイオンドーピング法やイオン注入法によって打ち込めばよい。脆化層110は水素、ヘリウム若しくはフッ素に代表されるハロゲンのイオンを打ち込むことで形成される。ハロゲン元素としてフッ素イオンを打ち込む場合にはソースガスとしてBF<sub>3</sub>を用いれば良い。なお、イオン注入法とはイオン化したガスを質量分離して半導体に打ち込む方式をいう。

10

#### 【0053】

単結晶シリコン基板にフッ素イオンのようなハロゲンイオンをイオン注入法で打ち込んだ場合、注入されたフッ素が、シリコン結晶格子内のシリコン原子をノックアウトする（追い出す）ことによって空白部分を効果的に作り出し、脆化層に微小な空洞を作る。この場合、比較的低温の熱処理によって脆化層に形成された微小な空洞の体積変化が起こり、脆化層に沿って分離することにより薄い単結晶半導体層を形成することができる。フッ素イオンを打ち込んだ後に、水素イオンを打ち込んで空洞内に水素を含ませるようにも良い。半導体基板から薄い半導体層を分離するために形成する脆化層は、脆化層に形成された微小な空洞の体積変化を利用して分離をするので、このようにフッ素イオンや水素イオンの作用を有効利用することが好ましい。

20

#### 【0054】

また、一又は複数の同一の原子から成る質量の異なるイオンを打ち込んでもよい。例えば、水素イオンを打ち込む場合には、H<sup>+</sup>、H<sub>2</sub><sup>+</sup>、H<sub>3</sub><sup>+</sup>イオンを含ませると共に、H<sub>3</sub><sup>+</sup>イオンの割合を高めておくことが好ましい。水素イオンを打ち込む場合には、H<sup>+</sup>、H<sub>2</sub><sup>+</sup>、H<sub>3</sub><sup>+</sup>イオンを含ませると共に、H<sub>3</sub><sup>+</sup>イオンの割合を高めておくと打ち込み効率を高めることができ、打ち込み時間を短縮することができる。このような構成とすることで、分離を容易に行うことができる。

30

#### 【0055】

脆化層の形成に当たってはイオンを高ドーズ条件で打ち込む必要があり、半導体基板108の表面が粗くなってしまう場合がある。そのためイオンが打ち込まれる表面に窒化シリコン膜、窒化酸化シリコン膜、若しくは酸化シリコン膜などによりイオン打ち込みに対する保護層を50nm乃至200nmの厚さで設けておいても良い。

#### 【0056】

例えば、半導体基板108上に保護層としてプラズマCVD法により酸化窒化シリコン膜（膜厚5nm～300nm、望ましくは30nm～150nm（例えば50nm））と窒化酸化シリコン膜（膜厚5nm～150nm、望ましくは10nm～100nm（例えば50nm））の積層を形成する。一例としては、半導体基板108上に酸化窒化シリコン膜を膜厚50nm形成し、該酸化窒化シリコン膜上に窒化酸化シリコン膜を膜厚50nm形成し、積層する。酸化窒化シリコン膜は有機シランガスを用いて化学気相成長法により作製される酸化シリコン膜でもよい。

40

#### 【0057】

また、半導体基板108を脱脂洗浄し、表面の酸化膜を除去して熱酸化を行ってもよい。熱酸化としては通常のドライ酸化でも良いが、酸化雰囲気中にハロゲンを添加した酸化を行うことが好ましい。例えば、酸素に対しHClを0.5～10体積%（好ましくは3体積%）の割合で含む雰囲気中で、700以上 の温度で熱処理を行う。好適には950～1100の温度で熱酸化を行うと良い。処理時間は0.1～6時間、好ましくは0.5～3.5時間とすれば良い。形成される酸化膜の膜厚としては、10nm～1000nm（好ましくは50nm～200nm）、例えば100nmの厚さとする。

50

## 【0058】

ハロゲンを含むものとしては HCl の他に、HF、NF<sub>3</sub>、HBr、Cl<sub>2</sub>、ClF<sub>3</sub>、BCl<sub>3</sub>、F<sub>2</sub>、Br<sub>2</sub> などから選ばれた一種又は複数種を適用することができる。

## 【0059】

このような温度範囲で熱処理を行うことで、ハロゲン元素によるゲッタリング効果を得ることができる。ゲッタリングとしては、特に金属不純物を除去する効果がある。すなわち、塩素の作用により、金属などの不純物が揮発性の塩化物となって気相中へ離脱して除去される。特に、半導体基板 108 の表面に化学的機械研磨 (CMP) 処理をしたものに対しては有効である。また、水素は半導体基板 108 と形成される酸化膜の界面の欠陥を補償して界面の局在準位密度を低減する作用を奏し、半導体基板 108 と酸化膜との界面が不活性化されて電気的特性が安定化する。10

## 【0060】

この熱処理により形成される酸化膜中にハロゲンを含ませることができる。ハロゲン元素は  $1 \times 10^{17} / \text{cm}^3 \sim 5 \times 10^{20} / \text{cm}^3$  の濃度で含まれることにより金属などの不純物を捕獲して半導体基板 108 の汚染を防止する保護層としての機能を発現させることができる。

## 【0061】

脆化層 110 を形成する際、加速電圧と全イオン数は、半導体基板上に堆積した膜の厚さと、目的とする半導体基板より分離して支持基板上に転置される半導体層の膜厚と、打ち込むイオン種によって調整することができる。20

## 【0062】

例えば、イオンドーピング法で原料として水素ガスを用い、加速電圧を 40 kV、全イオン数  $2 \times 10^{16} \text{ ions/cm}^2$  でイオンを打ち込んで脆化層を形成することができる。保護層の膜厚を厚くすれば、同一条件でイオンを打ち込み、脆化層を形成した場合、目的とする半導体基板より分離して支持基板上に転置される半導体層として、膜厚の薄い半導体層を形成することができる。例えば、イオン種 (H<sup>+</sup>、H<sub>2</sub><sup>+</sup>、H<sub>3</sub><sup>+</sup> イオン) の割合にもよるが、上記条件で脆化層を形成するとし、保護層として半導体基板上に酸化窒化シリコン膜（膜厚 50 nm）と窒化酸化シリコン膜（膜厚 50 nm）を保護層として積層する場合、支持基板に転置される半導体層の膜厚は約 120 nm となり、半導体基板上に酸化窒化シリコン膜（膜厚 100 nm）と窒化酸化シリコン膜（膜厚 50 nm）を保護層として積層する場合は、支持基板に転置される半導体層の膜厚は約 70 nm となる。30

## 【0063】

ヘリウム (He) や水素を原料ガスにする場合、加速電圧を 10 kV ~ 200 kV の範囲で、ドーズ量を  $1 \times 10^{16} \text{ ions/cm}^2 \sim 6 \times 10^{16} \text{ ions/cm}^2$  の範囲で打ち込み脆化層を形成することができる。ヘリウムを原料ガスにすると、質量分離を行わなくても He<sup>+</sup> イオンを主なイオンとして打ち込むことができる。また、水素を原料ガスとすると H<sub>3</sub><sup>+</sup> イオンや H<sub>2</sub><sup>+</sup> イオンを主なイオンとして打ち込むことができる。イオン種は、プラズマの生成方法、圧力、原料ガス供給量、加速電圧によっても変化する。

## 【0064】

脆化層形成の例としては、半導体基板上に酸化窒化シリコン膜（膜厚 50 nm）、窒化酸化シリコン膜（膜厚 50 nm）、及び酸化シリコン膜（膜厚 50 nm）を保護層として積層し、水素を加速電圧 40 kV、ドーズ量  $2 \times 10^{16} \text{ ions/cm}^2$  で打ち込み、半導体基板に脆化層を形成する。その後保護層の最上層である該酸化シリコン膜上に絶縁層として酸化シリコン膜（膜厚 50 nm）を形成する。脆化層形成の他の例としては、半導体基板上に酸化シリコン膜（膜厚 100 nm）、及び窒化酸化シリコン膜（膜厚 50 nm）を保護層として積層し、水素を加速電圧 40 kV、ドーズ量  $2 \times 10^{16} \text{ ions/cm}^2$  で打ち込み、半導体基板に脆化層を形成する。その後保護層の最上層である該窒化酸化シリコン膜上に絶縁層として酸化シリコン膜（膜厚 50 nm）を形成する。なお、上記酸化窒化シリコン膜及び窒化酸化シリコン膜はプラズマ CVD 法により形成すればよく、上記酸化シリコン膜は有機シランガスを用いて CVD 法により形成すればよい。4050

## 【0065】

支持基板101として、アルミニシリケートガラス、アルミニホウケイ酸ガラス、バリウムホウケイ酸ガラスのような電子工業用に使われるガラス基板を適用する場合、ガラス基板中にナトリウムなどのアルカリ金属が微量に含まれており、この微量の不純物によって電界効果トランジスタなど半導体素子の特性に悪影響を及ぼす恐れがある。このような不純物に対して、窒化酸化シリコン膜は支持基板101に含まれる金属不純物が半導体基板側に拡散するのを防止する効果がある。なお、窒化酸化シリコン膜の代わりに、窒化シリコン膜を形成してもよい。半導体基板と窒化酸化シリコン膜との間に酸化窒化シリコン膜や酸化シリコン膜などの応力緩和層を設けるとよい。窒化酸化シリコン膜と酸化窒化シリコン膜の積層構造を設けることで、半導体基板への不純物拡散を防止しつつ、応力歪みを緩和する構成とすることもできる。10

## 【0066】

次に、図3(B)で示すように支持基板と接合を形成する面に絶縁層104として酸化シリコン膜を形成する。なお脆化層形成の際に積層して形成した保護層は、除去して絶縁層104を形成しても良いし、保護層に積層して絶縁層104を形成してもよい。酸化シリコン膜としては有機シランガスを用いて化学気相成長法により作製される酸化シリコン膜が好ましい。その他に、シランガスを用いて化学気相成長法により作製される酸化シリコン膜を適用することもできる。化学気相成長法による成膜では、単結晶半導体基板に形成した脆化層110から脱ガスが起こらない温度として、例えば350℃以下(具体的な例としては300℃)の成膜温度が適用される。また、単結晶若しくは多結晶半導体基板から単結晶若しくは多結晶半導体層を分離する熱処理は、成膜温度よりも高い熱処理温度が適用される。20

## 【0067】

絶縁層104は平滑面を有し親水性表面を形成する。この絶縁層104として酸化シリコン膜が適している。特に有機シランガスを用いて化学気相成長法により作製される酸化シリコン膜が好ましい。有機シランガスとしては、珪酸エチル(TEOS:化学式Si(OCH<sub>3</sub>)<sub>4</sub>)、トリメチルシラン(TMS:(CH<sub>3</sub>)<sub>3</sub>SiH)、テトラメチルシラン(化学式Si(CH<sub>3</sub>)<sub>4</sub>)、テトラメチルシクロテトラシロキサン(TMCTS)、オクタメチルシクロテトラシロキサン(OMCTS)、ヘキサメチルジシラザン(HMDS)、トリエトキシシラン(SiH(OCH<sub>3</sub>)<sub>3</sub>)、トリスジメチルアミノシラン(SiH(N(CH<sub>3</sub>)<sub>2</sub>)<sub>3</sub>)等のシリコン含有化合物を用いることができる。なお、原料ガスに有機シランを用いて化学気相成長法により酸化シリコン層を形成する場合、酸素を付与するガスを混合させることができ。酸素を付与するガスとしては、酸素、亜酸化窒素、二酸化窒素等を用いることができる。さらに、アルゴン、ヘリウム、窒素又は水素等の不活性ガスを混合させてもよい。また、絶縁層104として、モノシラン、ジシラン、又はトリシラン等のシランを原料ガスに用いて化学気相成長法により形成される酸化シリコン層を適用することもできる。この場合も、酸素を付与するガスや不活性ガス等を混合させることができ。化学気相成長法による成膜では、半導体基板108に形成した脆化層110から脱ガスが起こらない温度として、例えば350℃以下の成膜温度が適用される。また、単結晶若しくは多結晶半導体基板から半導体層を分離する熱処理は、成膜温度よりも高い熱処理温度が適用される。なお、化学気相成長法は、プラズマCVD法、熱CVD法、光CVD法を範疇に含む。3040

## 【0068】

その他、絶縁層104として、酸化性雰囲気下において熱処理することにより形成される酸化シリコン、酸素ラジカルの反応により成長する酸化シリコン、酸化性の薬液により形成されるケミカルオキサイドなどを適用することもできる。絶縁層104として、シロキサン(Si-O-Si)結合を含む絶縁層を適用してもよい。また、前記有機シランガスと、酸素ラジカル又は窒素ラジカルとを反応させて絶縁層104を形成してもよい。

## 【0069】

上記平滑面を有し親水性表面を形成する絶縁層104は5nm～500nm、望ましくは50

10 nm ~ 200 nm の厚さで設けられる。この厚さであれば、被成膜表面の表面荒れを平滑化すると共に、当該膜の成長表面の平滑性を確保することが可能である。また、接合する支持基板と半導体基板 108 の歪みを緩和することができる。絶縁層 104 の表面は、算術平均粗さ Ra が 0.8 nm 未満、二乗平均平方根粗さ Rms が 0.9 nm 未満が望ましく、Ra が 0.4 nm 以下、Rms が 0.5 nm 以下がより望ましく、さらには Ra が 0.3 nm 以下、Rms が 0.4 nm 以下がより望ましい。例えば、Ra が 0.27 nm、Rms が 0.34 nm である。本明細書において Ra は算術平均粗さであり、Rms は二乗平均平方根粗さであり、測定面積は  $2 \mu\text{cm}^2$ 、又は  $10 \mu\text{m}^2$  である。

#### 【0070】

支持基板 101 にも絶縁層 104 と同様の酸化シリコン膜を設けておいても良い。すなわち、支持基板 101 に半導体層 102 を接合するに際し、接合を形成する面の一方若しくは双方に、好ましくは有機シランを原材料として成膜した酸化シリコン膜でなる絶縁層 104 設けることで強固な接合を形成することができる。

#### 【0071】

図 3 (C) は支持基板 101 と半導体基板 108 の絶縁層 104 が形成された面とを密接させ、この両者を接合させる態様を示す。接合を形成する面は、十分に清浄化しておく。支持基板 101 と半導体基板 108 の絶縁層 104 が形成された面は、メガソニック洗浄などによって清浄化すればよい。また、メガソニック洗浄後にオゾン水で洗浄し、有機物の除去と表面の親水性向上を行ってもよい。

#### 【0072】

支持基板 101 と絶縁層 104 を対向させて、一箇所を外部から押しつけると、局的に接合面同士の距離が縮まる事によるファン・デル・ワールス力の強まりや水素結合の寄与によって、お互いに引きつけ合う。更に、隣接した領域でも対向する支持基板 101 上と絶縁層 104 間の距離が縮まるので、ファン・デル・ワールス力が強く作用する領域や水素結合が関与する領域が広がる事によって、接合（ボンディングともいう）が進行し接合面全域に接合が広がる。例えば、押しつける圧力は、100 kPa ~ 5000 kPa 程度とすればよい。

#### 【0073】

そして、支持基板 101 と絶縁層 104 を密接させることにより接合が形成される。この接合はファン・デル・ワールス力が作用しており、支持基板 101 と半導体基板 108 とを圧接することで水素結合により強固な接合を形成することが可能である。

#### 【0074】

圧接する際に、基板四隅の一ヶ所を 100 kPa ~ 5000 kPa の圧力で抑えると、接合面同士が近づき、ファン・デル・ワールス力から水素結合へ移行することができる。基板内において一ヶ所の接合面が近接すると、隣接する接合面も近接し水素結合へ移行するため、接合面全域が水素結合へ移行することができる。

#### 【0075】

良好な接合を形成するために、表面を活性化しておいても良い。例えば、接合を形成する面に原子ビーム若しくはイオンビームを照射する。原子ビーム若しくはイオンビームを利用する場合には、アルゴン等の不活性ガス中性原子ビーム若しくは不活性ガスイオンビームを用いることができる。その他に、プラズマ照射若しくはラジカル処理を行う。このような表面処理により 200 乃至 400 の温度であっても異種材料間の接合を形成することが容易となる。

#### 【0076】

また、支持基板と絶縁層との接合界面の接合強度を向上させるために、加熱処理を行うと好ましい。例えば、オーブンや炉などで 70 ~ 350 （例えば 200 で 2 時間）の温度条件で熱処理を行う。

#### 【0077】

図 3 (D) において、支持基板 101 と半導体基板 108 を貼り合わせた後、加熱処理を行い、脆化層 110 を劈開面として半導体基板 108 を支持基板 101 から分離する。例

10

20

30

40

50

えば、400～700の熱処理を行うことにより、脆化層110に形成された微小な空洞の体積変化が起こり、脆化層110に沿って劈開することが可能となる。絶縁層104は支持基板101と接合しているので、支持基板101上には半導体基板108と同じ結晶性の半導体層102が残存することとなる。

#### 【0078】

400～700の温度域での熱処理は、前述の接合強度を向上させるための熱処理と同じ装置で連続して行ってもよいし、別の装置で行ってもよい。例えば炉で200～2時間熱処理した後に、600近傍まで昇温し2時間保持し、400から室温までの温度域に降温した後炉より取り出す。また、熱処理は室温から昇温してもよい。また、炉で200～2時間熱処理した後に、瞬間熱アニール(RTA)装置によって600～700の温度域で、1分間～30分間(例えば600～7分間、650～7分間)熱処理を行ってもよい。10

#### 【0079】

400～700の温度域での熱処理により、絶縁層と支持基板との接合は水素結合から共有結合に移行し、脆化層に打ち込まれた元素が析出して圧力が上昇し、半導体基板より半導体層を分離することができる。熱処理を行った後は支持基板と半導体基板は、一方が他方に載っている状態であり、大きな力を加えずに支持基板と半導体基板を離すことができる。例えば、上方に載っている基板を真空チャックで持ち上げることにより簡単に話すことができる。この際、下側の基板の真空チャックやメカニカルチャックで固定しておくと水平方向のずれがなく支持基板及び半導体基板の両基板を離すことができる。20

#### 【0080】

なお、図3、図4においては、半導体基板108が支持基板101より小さいサイズの例を示すが、本発明はそれに限定されず、半導体基板108と支持基板101が同じサイズであってもよいし、半導体基板108が支持基板101より大きいサイズであってもよい。。

#### 【0081】

図4は支持基板側に半導体層と接合する絶縁層を設けて半導体層を形成する工程を示す。図4(A)は保護層121として酸化シリコン膜が形成された半導体基板108に電界で加速されたイオンを所定の深さに打ち込み、脆化層110を形成する工程を示している。イオンの打ち込みは図3(A)の場合と同様である。半導体基板108の表面に保護層121を形成しておくことでイオン打ち込みによって表面がダメージを受け、平坦性が損なわれるのを防ぐことができる。また、保護層121によって、半導体基板108から形成される半導体層102に対する不純物の拡散防止効果を発現する。30

#### 【0082】

図4(B)は、ブロッキング層109及び絶縁層104が形成された支持基板101と半導体基板108の保護層121が形成された面を密接させて接合を形成する工程を示している。ブロッキング層109は支持基板101からナトリウムイオンなどの不純物が拡散して半導体層を汚染しないために設けられている。もっとも、支持基板101から半導体層に悪影響を与える不純物の拡散を心配する必要のない場合には、ブロッキング層109を省略することも可能である。支持基板101上の絶縁層104と半導体基板108の保護層121を密接させることにより接合が形成される。40

#### 【0083】

その後、図4(C)で示すように半導体基板108を分離する。半導体層を分離する熱処理は図3(D)の場合と同様にして行う。接合分離工程における加熱処理の温度は、支持基板101にあらかじめ行われた加熱処理以下とする。このようにして図4(C)で示す半導体基板を得ることができる。

#### 【0084】

支持基板101としては、絶縁性を有する基板、絶縁表面を有する基板を用いることができ、例えば、アルミニシリケートガラス、アルミニホウケイ酸ガラス、バリウムホウケイ酸ガラスの如き無アルカリガラスと呼ばれる電子工業用に使われる各種ガラス基板を適用50

することができる。また、石英基板、セラミック基板、サファイア基板、表面が絶縁層で被覆された金属基板などが適用可能である。

#### 【0085】

以上の工程により、図4(C)に示すように、絶縁表面を有する基板である支持基板101の上に絶縁層104が設けられ、半導体基板108より分離された半導体層102が形成される。

#### 【0086】

支持基板101上に設けられた半導体層102を島状の半導体層にエッチングにより加工する。半導体層102上にマスク117を形成し、マスク117を用いたエッチング処理により半導体層102を加工し、島状の半導体層119を形成する。図4では、半導体層下に形成される保護層及び絶縁層は半導体層119を形成するエッチング処理ではエッチングされない例を示すが、半導体層のエッチング処理と共に保護層及び絶縁層もエッチングしてもよい。このような場合、保護層及び絶縁層は島状の半導体層119の形状を反映し、半導体層119下のみに設けられる構造となる。

10

#### 【0087】

また、半導体基板より分離し、支持基板に転置された半導体層は、分離工程およびイオン打ち込み工程によって、結晶欠陥が生じ、また、その表面は平坦性が損なわれ、凹凸が形成されてしまう場合がある。半導体層を用いて電界効果トランジスタを作製する場合、このような凹凸のある半導体層の上面に薄く、絶縁耐圧性の高いゲート絶縁層を形成することは困難である。また、半導体層に結晶欠陥があると、ゲート絶縁層との局在界面準位密度が高くなるなど、電界効果トランジスタの性能および信頼性に影響を与える。

20

#### 【0088】

従って半導体層にレーザ光のような電磁波を照射し、結晶欠陥を低減させることができが好ましい。電磁波を照射することによって、半導体層の少なくとも一部の領域を溶融させ、半導体層中の結晶欠陥を低減させることができる。なお、電磁波の照射前に半導体層表面に形成された酸化膜(自然酸化膜、あるいはケミカル酸化膜)を希フッ酸で除去するとよい。

#### 【0089】

電磁波は半導体層に高いエネルギーを供給できるものであればよく、好適にはレーザ光を用いることができる。

#### 【0090】

30

またエネルギーの供給は、高エネルギーを有する粒子を照射などによって半導体層に衝突させ、主として熱伝導によって行うこともできる。高エネルギーを有する粒子を提供する熱源としては、プラズマを用いることができ、常圧プラズマ、高圧プラズマ、熱プラズマジェット、ガスバーナーなどの炎を用いることができる、又、他の熱源としては電子ビームなどを用いることができる。

#### 【0091】

電磁波の波長は、半導体層に吸収される波長とする。その波長は、電磁波の表皮深さ(skin depth)などを考慮して決定することができる。例えば、電磁波の波長は190nm～600nmを用いることができる。また、電磁波のエネルギーは、電磁波の波長、電磁波の表皮深さ、照射する半導体層の膜厚などを考慮して決定することができる。

40

#### 【0092】

レーザ光を発振するレーザは、連続発振レーザ、疑似連続発振レーザ及びパルス発振レーザを用いることができる。部分溶融させるためパルス発振レーザが好ましい。例えば、KrFレーザなどのエキシマレーザ、Arレーザ、Krレーザなどの気体レーザがある。その他、固体レーザとして、YAGレーザ、YVO<sub>4</sub>レーザ、YLFレーザ、YAlO<sub>3</sub>レーザ、GdVO<sub>4</sub>レーザ、KGWレーザ、KYWレーザ、アレキサンドライトレーザ、Ti:サファイアレーザ、Y<sub>2</sub>O<sub>3</sub>レーザなどがある。なお、エキシマレーザはパルス発振レーザであるが、YAGレーザなどの固体レーザには、連続発振レーザにも、疑似連続発振レーザにも、パルス発振レーザにもなるものがある。なお、固体レーザにおいては、基本波の第2高調波～第5高調波を適用するのが好ましい。また、GaN、GaAs、Ga

50

A<sub>1</sub>A<sub>s</sub>、InGaAsP等の半導体レーザも用いることができる。

【0093】

また、電磁波のエネルギーを半導体層に照射できるならば、ランプ光を用いてもよい。例えば、紫外線ランプ、ブラックライト、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、または高圧水銀ランプから射出された光を用いてもよい。上記ランプ光を用いたフラッシュアニールを用いてもよい。ハロゲンランプやキセノンランプなどを好適に用いて行うフラッシュアニールは極短時間の処理でよいため、支持基板の温度上昇を抑えることができる。

【0094】

電磁波の形状や電磁波の進路を調整するため、シャッター、ミラー又はハーフミラー等の反射体、シリンドリカルレンズや凸レンズなどによって構成される光学系がレーザ光の進路上に設置されていてもよい。

10

【0095】

なお、電磁波の照射方法は、選択的に電磁波を照射してもよいし、光（電磁波）をX Y軸方向に走査して光（電磁波）を照射することができる。この場合、光学系にポリゴンミラー やガルバノミラーを用いることが好ましい。

【0096】

電磁波の照射は、大気雰囲気のような酸素を含む雰囲気、または窒素雰囲気のような不活性雰囲気で行うことができる。不活性雰囲気中で電磁波を照射するには、気密性のあるチャンバー内で電磁波を照射し、このチャンバー内の雰囲気を制御すればよい。チャンバーを用いない場合は、電磁波の被照射面に窒素ガスなど不活性ガスを吹き付けることで、窒素雰囲気を形成することもできる。

20

【0097】

さらに、電磁波照射などの高エネルギーを供給され、結晶欠陥を低減された半導体層表面に研磨処理を行ってもよい。研磨処理によって半導体層表面の平坦性を高めることができる。

【0098】

研磨処理としては、化学的機械研磨（Chemical Mechanical Polishing : CMP）法や液体ジェット研磨法を用いることができる。なお、研磨処理前に半導体層表面を洗浄し、清浄化する。洗浄は、メガソニック洗浄や2流体ジェット洗浄等を用いればよく、洗浄により半導体層表面のゴミ等を除去する。また、希フッ酸を用いて半導体層表面上の自然酸化膜等を除去して半導体層を露出させると好適である。

30

【0099】

また、電磁波を照射する前にも半導体層表面に研磨処理（又はエッチング処理）を行ってもよい。

【0100】

本実施の形態において、半導体基板108として単結晶シリコン基板を適用した場合は、半導体層119として単結晶シリコン層を得ることが可能である。また、本実施の形態の表示装置の画素を構成する電界効果トランジスタの製造方法は、プロセス温度を700以下とすることができるため、支持基板101としてガラス基板を適用することができる。すなわち、従来の薄膜トランジスタと同様にガラス基板上に形成することができ、かつ単結晶シリコン層を半導体層に適用することが可能となる。これらのことにより、高速動作が可能で、サブスレッショルド値が低く、電界効果移動度が高く、低消費電圧で駆動可能など高性能、高信頼性の電界効果トランジスタをガラス基板等の支持基板上に作製することができる。

40

【0101】

次に上記図1(A)に示す表示装置の画素を構成する電界効果トランジスタの作製方法を図5及び図6を用いて説明する。

【0102】

図5(A)は、支持基板101上にプロッキング層109、絶縁層104、保護層121

50

、半導体層 119 が形成されている。支持基板 101、半導体層 119、プロッキング層 109、絶縁層 104、保護層 121 は上記図 4 と対応している。

#### 【0103】

半導体層 119 には、n チャネル型電界効果トランジスタ及び p チャネル型電界効果トランジスタの形成領域に合わせて、硼素、アルミニウム、ガリウムなどの p 型不純物、若しくはリン、砒素などの n 型不純物を添加することが好ましい。すなわち、n チャネル型電界効果トランジスタの形成領域に対応して p 型不純物を添加し、p チャネル型電界効果トランジスタの形成領域に対応して n 型不純物を添加して、所謂ウェル領域を形成する。不純物イオンのドーズ量は  $1 \times 10^{12} / \text{cm}^2$  から  $1 \times 10^{14} / \text{cm}^2$  程度で行えば良い。さらに、電界効果トランジスタのしきい値電圧を制御する場合には、これらのウェル領域に p 型若しくは n 型不純物を添加すれば良い。10

#### 【0104】

半導体層 119 をさらにエッチングして、半導体素子の配置に合わせて島状に加工してもよい。

#### 【0105】

半導体層上の酸化膜を除去し、半導体層 119 を覆うゲート絶縁層 205 を形成する。

#### 【0106】

ゲート絶縁層 205 は酸化珪素、若しくは酸化珪素と窒化珪素の積層構造で形成すればよい。ゲート絶縁層 205 は、プラズマ CVD 法や減圧 CVD 法により絶縁膜を堆積することで形成しても良いし、プラズマ処理による固相酸化若しくは固相窒化で形成すると良い。20 半導体層を、プラズマ処理により酸化又は窒化することにより形成するゲート絶縁層は、緻密で絶縁耐圧が高く信頼性に優れているためである。

#### 【0107】

また、ゲート絶縁層 205 として、二酸化ジルコニウム、酸化ハフニウム、二酸化チタン、五酸化タンタルなどの高誘電率材料を用いても良い。ゲート絶縁層 205 に高誘電率材料を用いることにより、ゲートリーコ電流を低減することができる。

#### 【0108】

ゲート絶縁層 205 上にゲート電極層 206 を形成する（図 5 (B) 参照。）。ゲート電極層 206 は、スパッタリング法、蒸着法、CVD 法等の手法により形成することができる。ゲート電極層 206 はタンタル (Ta)、タンクステン (W)、チタン (Ti)、モリブデン (Mo)、アルミニウム (Al)、銅 (Cu)、クロム (Cr)、ネオジム (Nd) から選ばれた元素、又は前記元素を主成分とする合金材料もしくは化合物材料で形成すればよい。また、ゲート電極層 206 としてリン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体層や、AgPdCu 合金を用いてもよい。30

#### 【0109】

ゲート電極層 206 をマスクとして、n 型を付与する不純物元素 207 を添加し、n 型不純物領域である不純物領域 208a、不純物領域 208b を形成する。本実施の形態では、不純物元素を含むドーピングガスとしてホスフィン ( $\text{PH}_3$ ) を用いる。ここでは、不純物領域 208a、208b に n 型を付与する不純物元素が  $5 \times 10^{19} \sim 5 \times 10^{20} / \text{cm}^3$  程度の濃度で含まれるように添加する。また、半導体層 119 にチャネル形成領域 209 が形成される（図 5 (C) 参照。）。40

#### 【0110】

不純物領域 208a、不純物領域 208b は高濃度 n 型不純物領域であり、ソース、ドレインとして機能する。

#### 【0111】

不純物元素を活性化するために加熱処理、強光の照射、又はレーザ光の照射を行ってもよい。活性化と同時にゲート絶縁層へのプラズマダメージやゲート絶縁層と半導体層との界面へのプラズマダメージを回復することができる。

#### 【0112】

次いで、ゲート電極層、ゲート絶縁層を覆う層間絶縁層を形成する。本実施の形態では、50

保護膜となる水素を含む絶縁層 210 と、平坦化層 211 との積層構造とする。

**【0113】**

さらに、窒素雰囲気中で、300～550 で1～12時間の熱処理を行い、半導体層を水素化する工程を行う。好ましくは、400～500 で行う。この工程は層間絶縁層である絶縁層 210 に含まれる水素により半導体層のダンギリングボンドを終端する工程である。本実施の形態では、410 度( )で1時間加熱処理を行う。

**【0114】**

本発明では、平坦化層 211 を形成し、半導体層、ゲート電極層などによって生じる表面の凹凸を軽減し、平坦化する。従って平坦化層 211 は、表面が平坦化するような膜厚で形成する。また、表面を化学的機械的研磨(CMP)することにより平坦化してもよい。

10

**【0115】**

絶縁層 210 と平坦化層 211 は、スパッタ法、またはプラズマ CVD を用いた窒化珪素膜、窒化酸化珪素膜、酸化窒化珪素膜、酸化珪素膜でもよく、他の珪素を含む絶縁膜を単層または3層以上の積層構造として用いても良い。

**【0116】**

絶縁層 210 、平坦化層 211 としては他に窒化アルミニウム(AlN)、酸化窒化アルミニウム(AlON)、窒素含有量が酸素含有量よりも多い窒化酸化アルミニウム(AlNO)または酸化アルミニウム、ダイアモンドライクカーボン(DLC)、窒素含有炭素(CN)その他の無機絶縁性材料を含む物質から選ばれた材料で形成することができる。また、シロキサン樹脂を用いてもよい。なお、シロキサン樹脂とは、Si-O-Si 結合を含む樹脂に相当する。シロキサンは、シリコン(Si)と酸素(O)との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基(例えばアルキル基、アリール基)が用いられる。有機基は、フルオロ基を含んでも良い。

20

**【0117】**

また、後工程で用いる加熱処理に耐えられる有機絶縁性材料を用いてもよく、有機材料としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、レジスト又はベンゾシクロブテン、ポリシラザンを用いることができる。平坦性のよい塗布法によってされる塗布膜を平坦化層 211 として用いてもよい。

**【0118】**

絶縁層 210 、平坦化層 211 は、ディップ、スプレー塗布、ドクターナイフ、ロールコーター、カーテンコーティング、ナイフコーティング、CVD 法、蒸着法等を採用することができる。液滴吐出法により絶縁層 210 、平坦化層 211 を形成してもよい。

30

**【0119】**

平坦化層 211 上に第 2 の半導体層と接合する絶縁層として絶縁層 212 を形成する(図 5 (D) 参照。)。絶縁層 212 は絶縁層 104 と同様の材料及び工程で形成すればよい。例えば、本実施の形態では絶縁層 212 として酸化シリコン膜を形成する。

**【0120】**

上記図 4 で説明したように、半導体層 102 を絶縁層 104 と接合させ、半導体基板 108 より分離したように、半導体層 215 を絶縁層 212 と接合させ、平坦化層 211 上に形成する(図 5 (E) 参照。)。半導体層 215 は、加熱処理によって脆化層 214 が形成された半導体基板 213 より分離し、絶縁層 212 と接合される。

40

**【0121】**

半導体層 215 の、結晶欠陥を低減するためにレーザ光を照射してもよい。また半導体層 215 表面に研磨処理を行ってもよい。研磨処理によって半導体層 215 表面の平坦性を高めることができる。

**【0122】**

なお、本実施の形態では、第 1 の半導体基板である半導体基板 108 として、結晶面方位が {100} の単結晶半導体基板が選択され、第 2 の半導体基板である半導体基板 213 として、結晶面方位が {110} の単結晶半導体基板が選択される。なお、第 1 の半導体基板の結晶面方位と第 2 の半導体基板の結晶面方位は本実施の形態の組み合わせに限定さ

50

れるものではなく、例えば第1の半導体基板として結晶面方位が{110}の基板を用い、第2の半導体基板として結晶面方位が{100}の基板を用いてもよい。その場合、第1の半導体基板を用いてpチャネル型電界効果トランジスタを作製し、第2の半導体基板を用いてnチャネル型電界効果トランジスタを作製することが好ましい。

#### 【0123】

その後、薄膜の半導体層215を選択的にエッティングして、絶縁層212上に島状の半導体層216を形成する(図5(F)参照)。

#### 【0124】

半導体層216上にゲート絶縁層217及びゲート電極層218を形成する(図6(A)参照)。

10

#### 【0125】

ゲート電極層218をマスクとして、p型を付与する不純物元素219を添加し、p型不純物領域である不純物領域220a、220bを形成する。不純物領域220a、220bにp型を付与する不純物元素が $1 \times 10^{20} \sim 5 \times 10^{21} / \text{cm}^3$ 程度の濃度で含まれるように添加する。また、半導体層216にチャネル形成領域221が形成される(図6(B)参照)。不純物領域220a、220bは高濃度p型不純物領域であり、ソース、ドレインとして機能する。

#### 【0126】

次いで、ゲート電極層、ゲート絶縁層を覆う層間絶縁層を形成する。本実施の形態では、保護膜となる水素を含む絶縁層222と、平坦化層223との積層構造とする。

20

#### 【0127】

さらに、窒素雰囲気中で、300～550で1～12時間の熱処理を行い、半導体層を水素化する工程を行う。好ましくは、400～500で行う。この工程は層間絶縁層である絶縁層222に含まれる水素により半導体層のダンギングボンドを終端する工程である。本実施の形態では、410度( )で1時間熱処理を行う。この熱処理の工程は、半導体層119及び絶縁層210に対する熱処理も兼ねてもよい。

#### 【0128】

本発明では、平坦化層223を形成し、半導体層、ゲート電極層などによって生じる表面の凹凸を軽減し、平坦化する。従って平坦化層223は、表面が平坦化するような膜厚で形成する。また、表面を化学的機械的研磨(CMP)することにより平坦化してもよい。

30

#### 【0129】

ゲート絶縁層217はゲート絶縁層205と、ゲート電極層218はゲート電極層206と、絶縁層222は絶縁層210と、平坦化層223は平坦化層211と対応しており、それぞれ同様な材料及び工程で形成することができる。

#### 【0130】

次いで、レジストからなるマスクを用いてゲート絶縁層205、絶縁層210、平坦化層211、絶縁層212、ゲート絶縁層217、絶縁層222、及び平坦化層223に半導体層119、216にそれぞれ達するコンタクトホール(開口)を形成する。エッティングは、用いる材料の選択比によって、一回で行っても複数回行っても良い。エッティングによって、ゲート絶縁層205、絶縁層210、平坦化層211、絶縁層212、ゲート絶縁層217、絶縁層222、及び平坦化層223を選択的に除去し、ソース領域又はドレイン領域である不純物領域208a、208b、不純物領域220a、220bに達する開口を形成する。

40

#### 【0131】

エッティング方法及び条件は、コンタクトホールを形成するゲート絶縁層205、絶縁層210、平坦化層211、絶縁層212、ゲート絶縁層217、絶縁層222、及び平坦化層223の材料によって適宜設定すればよい。ウェットエッティング、ドライエッティング、またはその両方を適宜用いることができる。本実施の形態ではドライエッティングを用いる。エッティング用ガスとしては、Cl<sub>2</sub>、BCl<sub>3</sub>、SiCl<sub>4</sub>もしくはCCl<sub>4</sub>などを代表とする塩素系ガス、CF<sub>4</sub>、SF<sub>6</sub>もしくはNF<sub>3</sub>などを代表とするフッ素系ガス又は

50

O<sub>2</sub>を適宜用いることができる。また用いるエッティング用ガスに不活性気体を添加してもよい。添加する不活性元素としては、He、Ne、Ar、Kr、Xeから選ばれた一種または複数種の元素を用いることができる。

#### 【0132】

ウェットエッティングのエッチャントは、フッ素水素アンモニウム及びフッ化アンモニウムを含む混合溶液のようなフッ酸系の溶液を用いるとよい。

#### 【0133】

開口を覆うように導電膜を形成し、導電膜をエッティングして各ソース領域又はドレイン領域の一部とそれぞれ電気的に接続するソース電極層又はドレイン電極層としても機能する配線層224、225、226を形成する。配線層は、PVD法、CVD法、蒸着法等により導電膜を成膜した後、所望の形状にエッティングして形成することができる。また、液滴吐出法、印刷法、電解メッキ法等により、所定の場所に選択的に導電膜を形成することができる。更にはリフロー法、ダマシン法を用いても良い。配線層の材料は、Ag、Au、Cu、Ni、Pt、Pd、Ir、Rh、W、Al、Ta、Mo、Cd、Zn、Fe、Ti、Zr、Ba等の金属、及びSi、Ge、又はその合金、若しくはその窒化物を用いて形成する。また、これらの積層構造としても良い。

10

#### 【0134】

本実施の形態では、ゲート絶縁層205、絶縁層210、平坦化層211、絶縁層212、ゲート絶縁層217、絶縁層222、及び平坦化層223に形成されたコンタクトホールを埋めるようにCVD法やスパッタリング法を用いて、アルミニウム(Al)、タンゲステン(W)、チタン(Ti)、タンタル(Ta)、モリブデン(Mo)、ニッケル(Ni)、白金(Pt)、銅(Cu)、金(Au)、銀(Ag)、マンガン(Mn)、ネオジム(Nd)、炭素(C)、シリコン(Si)等の金属元素、又は当該金属元素を含む合金材料若しくは化合物材料を用いて基板全面に導電膜を単層構造又は積層構造で形成した後、当該導電膜を選択的にエッティングして配線層224、225、226を形成する(図6(C)参照)。

20

#### 【0135】

以上の工程でnチャネル型電界効果トランジスタである電界効果トランジスタ230及びpチャネル型電界効果トランジスタである電界効果トランジスタ231を含む画素で構成された表示装置を作製することができる。なお、電界効果トランジスタ230及び電界効果トランジスタ231は配線層225によって電気的に接続されている。

30

#### 【0136】

電界効果トランジスタ230は、絶縁層104と接合して支持基板101上に設けられ、電界効果トランジスタ231は、電界効果トランジスタ230を覆う平坦化層211上に形成された絶縁層212と接合して平坦化層211上に設けられており、電界効果トランジスタ230及び電界効果トランジスタ231は積層されている。

#### 【0137】

本発明は高性能の半導体素子を積層構造とすることができるため、より高集積化された電界効果トランジスタで構成された画素を有する表示装置とすることができる。

#### 【0138】

また、支持基板上に半導体層を貼り合わせる際に、それぞれの半導体層はそれぞれ平坦な異なる絶縁層上に形成されるため、絶縁層と半導体層との接合を容易に行うことができる。

40

#### 【0139】

また本実施の形態のように、異なる導電型の電界効果トランジスタを形成する半導体層をそれぞれ異なる絶縁層上に形成すると、異なる導電型の電界効果トランジスタの半導体層間の寄生容量、又は異なる導電型の電界効果トランジスタのゲート電極層間の寄生容量を低減することができる。従って、性能のよい電界効果トランジスタで構成された画素を有する表示装置を作製することができる。

#### 【0140】

50

本実施の形態に限定されず、電界効果トランジスタはチャネル形成領域が一つ形成されるシングルゲート構造でも、二つ形成されるダブルゲート構造もしくは三つ形成されるトリプルゲート構造であっても良い。

【0141】

また、本実施の形態では、積層する電界効果トランジスタが異なる導電型のC M O S構造の場合を例として示すが、同導電型の電界効果トランジスタを積層させてもよい。

【0142】

以上のように本実施の形態において、より高集積化された高性能な電界効果トランジスタで構成された画素を有する表示装置を作製することができる。

(実施の形態2)

10

【0143】

本実施の形態では、実施の形態1において、半導体基板より支持基板へ半導体層を接合する工程の異なる例を示す。従って、実施の形態1と同一部分又は同様な機能を有する部分の繰り返しの説明は省略する。

【0144】

本実施の形態は、半導体基板より半導体層を転置する際、半導体基板を選択的にエッティング(溝加工ともいう)し、作製する半導体素子の大きさに複数に分割された複数の半導体層を、支持基板に転置する。従って、支持基板には、複数の島状の半導体層を形成することができる。予め、素子サイズの半導体層に加工して転置するために、半導体層単位で支持基板に転置することができ、半導体基板の大きさや形状に制限を受けない。そのためには大型の支持基板への半導体層の転置がより効率よく行うことができる。

20

【0145】

さらに、支持基板上に形成された半導体層に対して、エッティングを行い、半導体層の形状を加工、修正し精密に制御してもよい。これにより、レジストマスク形成時の露光の回り込みなどによるパターンズレや、転置時の貼り合わせ工程による位置ズレなどによる半導体層の形成位置の誤差や形状不良を修正することができる。

【0146】

従って、支持基板に所望の形状の複数の半導体層を、歩留まりよく形成することができる。よって、大面積基板により精密で高性能な半導体素子を用いて形成された電界効果トランジスタを積層して高集積化することで得られる画素を有する表示装置を高スループットで生産性よく作製することができる。

30

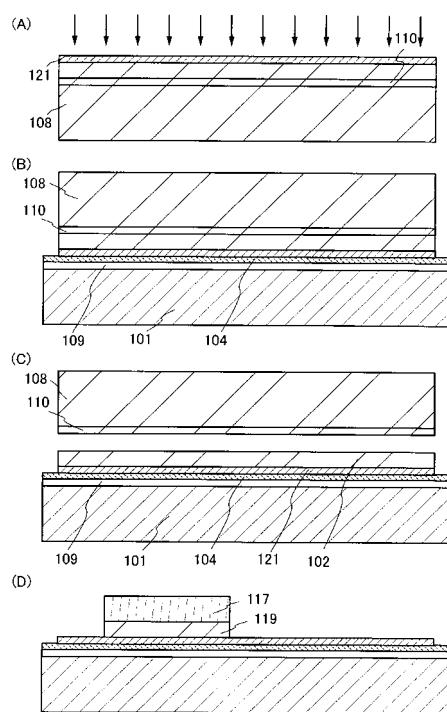

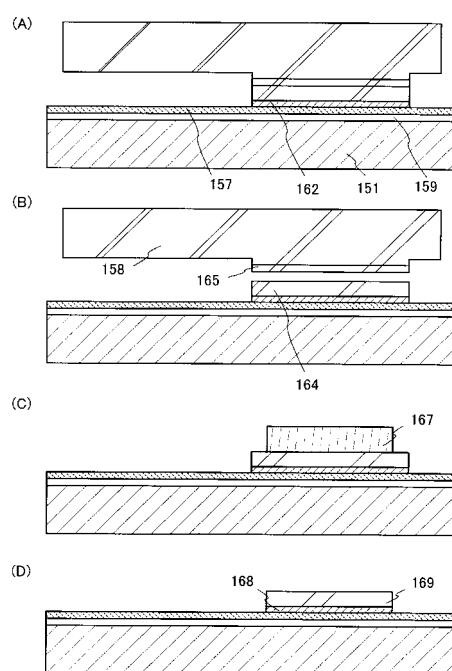

【0147】

図7(A)において、半導体基板158上に保護層154と窒化シリコン膜152が形成された状態を示している。窒化シリコン膜152は、半導体基板158を溝加工する際のハードマスクとして用いる。窒化シリコン膜152は、シランとアンモニアを用いて気相成長法により堆積させることで形成すれば良い。

【0148】

次に、イオンを打ち込み、半導体基板158の全面に脆化層150を形成する(図7(B)参照。)。イオンの打ち込みは支持基板に転置する半導体層の厚さを考慮して行われる。イオンを打ち込む際の加速電圧はこのような厚さを考慮して、半導体基板158の深部に打ち込まれるようにする。この処理によって半導体基板158の表面から一定の深さの領域に脆化層150が形成される。

40

【0149】

溝加工は、半導体層の形状を考慮して行われる。すなわち半導体素子の半導体層が支持基板に転置できるように、その部位が凸状部として残存するように半導体基板158に対して溝加工を行う。

【0150】

フォトレジストでマスク153を形成する。マスク153を用いて、窒化シリコン膜152及び保護層154をエッティングし、保護層162、及び窒化シリコン層163を形成する(図7(C)参照。)。

50

**【 0 1 5 1 】**

次いで、窒化シリコン層 163 をハードマスクとして半導体基板 158 のエッティングを行い、脆化層 165、半導体層 166 を有する半導体基板 158 を形成する（図 7（D）参照。）。本発明では、脆化層及び溝加工によって凸状に加工された半導体基板の一部である半導体領域を図 7（D）のように半導体層 166 という。

**【 0 1 5 2 】**

半導体基板 158 をエッティングする深さは、支持基板に転置する半導体層の厚さを考慮して適宜設定される。当該半導体層の厚さは水素イオンを打ち込む深さで設定することが可能である。半導体基板 158 に形成する溝の深さは、脆化層よりも深くなるように形成することが好ましい。この溝加工において、溝の深さを脆化層よりも深く加工することで、脆化層を分離すべき半導体層の領域のみに残すことができる。10

**【 0 1 5 3 】**

表面の窒化シリコン層 163 を除去する（図 7（E）参照。）。そして、半導体基板 158 における保護層 162 の表面と支持基板 151 を接合させる（図 8（A）参照。）。

**【 0 1 5 4 】**

支持基板 151 の表面には、プロッキング層 159 及び絶縁層 157 が形成されている。プロッキング層 159 は支持基板 151 からナトリウムイオンなどの不純物が拡散して半導体層を汚染しないために設けられている。もっとも、支持基板 151 から半導体層に悪影響を与える不純物の拡散を心配する必要のない場合には、プロッキング層 159 を省略することも可能である。一方、絶縁層 157 は、保護層 162 と接合を形成するために設けられている。20

**【 0 1 5 5 】**

接合は、表面が清浄化された半導体基板 158 側の保護層 162 と、支持基板側の絶縁層 157 が密接することにより形成される。接合の形成は室温で行うことが可能である。この接合は原子レベルで行われ、ファン・デル・ワールス力が作用して室温で強固な接合が形成される。半導体基板 158 には溝加工がされているので、半導体層を形成する凸状部が支持基板 151 と接すこととなる。

**【 0 1 5 6 】**

半導体基板 158 と支持基板 151 の間で接合を形成した後、熱処理を行うことにより、図 8（B）で示すように半導体基板 158 から半導体層 164 を分離して支持基板 151 に固定することができる。半導体層の分離は、脆化層 150 に形成された微小な空洞の体積変化が起こり、脆化層 150 に沿って破断面を発生させることにより行う。その後、接合をさらに強固なものとするために、熱処理を行うことが好ましい。このようにして、絶縁表面上に半導体層が形成される。図 8（B）では半導体層 164 が支持基板 151 上に接合された状態を示している。30

**【 0 1 5 7 】**

本実施の形態は、予め、素子サイズの半導体層に加工して転置するために、半導体層単位で支持基板に転置することができ、半導体基板の大きさや形状に制限を受けない。従って、半導体基板上で様々な形状の半導体層を形成することができる。例えば、エッティングの際に用いる露光装置のマスク毎、該マスクパターンを形成するための露光装置が有するステッパー毎、大型基板を用いた表示装置のパネルサイズに応じて、自由に半導体層を形成することができる。40

**【 0 1 5 8 】**

半導体層 164 をそのまま半導体素子の半導体層として用いてもよいし、さらにエッティングを行い、形状を加工してもよい。

**【 0 1 5 9 】**

図 8（C）、図 8（D）に転置された半導体層 164 にさらにエッティングを行い、形状を加工する例を示す。マスク 167 を、半導体層 164 の不要部分である周辺部分を露出して形成する。

**【 0 1 6 0 】**

10

20

30

40

50

マスク 167 を用いて、半導体層 164 をエッティングし、半導体層 169 を形成する。本実施の形態では、半導体層下の保護層 162 も半導体層と共にエッティングし、保護層 168 とする(図 8 (D) 参照)。このように、支持基板に転置した後さらに形状を加工することによって、作製工程で生じた形成領域のズレや、形状不良などを修正することができる。

#### 【0161】

図 7 及び図 8 では、支持基板上に設けられた絶縁層に半導体層を転置する例を示すが、もちろん上層に積層する半導体素子の半導体層として、平坦化層上に形成された絶縁層上に半導体層を形成する際にも本実施の形態を用いることができる。

#### 【0162】

本実施の形態は実施の形態 1 と適宜組み合わせて実施することが可能である。

#### (実施の形態 3)

#### 【0163】

本実施の形態では、実施の形態 1 において、半導体基板より支持基板へ半導体層を接合する工程の異なる例を示す。従って、実施の形態 1 と同一部分又は同様な機能を有する部分の繰り返しの説明は省略する。

#### 【0164】

本実施の形態では、半導体基板より半導体層を分離してから、支持基板に接合する例を示す。

#### 【0165】

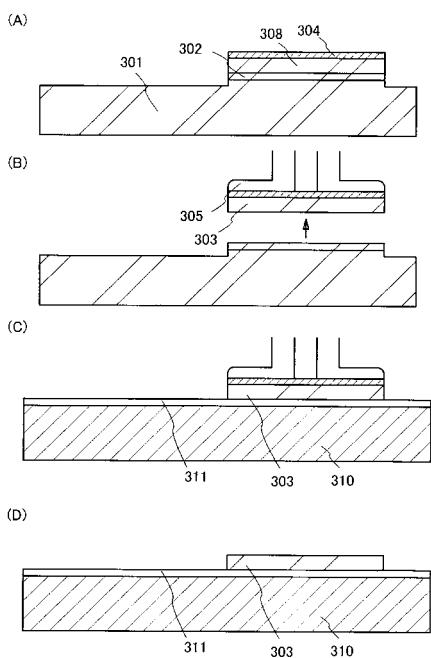

実施の形態 2 の図 7 で示したように、半導体基板に脆化層を形成し、溝を形成する。溝加工は、半導体素子の半導体層の形状を考慮して行われる。すなわち半導体素子の半導体層が支持基板に転置できるように、その部位が凸状部として残存するように半導体基板 301 に対して溝加工を行う。図 9 (A) において、半導体基板 301、脆化層 302、半導体基板の一部である半導体層 308、絶縁膜 304 が形成されている。本実施の形態では、酸化珪素を絶縁膜 304 として用いる。

#### 【0166】

次に、熱処理を行うことにより、脆化層 302 において隣接する微小ボイドどうしが結合して、微小ボイドの体積が増大する。その結果、脆化層 302 において半導体基板 301 が劈開し、半導体層 308 が、絶縁膜 304 と共に、半導体基板 301 から分離する。熱処理は、例えば 400 乃至 600 の温度範囲内で行えば良い。

#### 【0167】

なお、熱処理は、マイクロ波などの高周波による誘電加熱を用いて行っても良い。上記誘電加熱による熱処理は、高周波発生装置において生成された周波数 300 MHz 乃至 3 THz の高周波を半導体基板 301 に照射することで行うことができる。具体的には、例えば、2.45 GHz のマイクロ波を 900 W、14 分間照射することで、脆化層において隣接する微小ボイドどうしを結合させ、最終的に半導体基板 301 を劈開させることができる。

#### 【0168】

そして、図 9 (B) に示すように、コレット 305 を半導体層 308 上に形成された絶縁膜 304 に固着させ、半導体層 308 を半導体基板 301 から引き離す。上記熱処理による半導体基板 301 の劈開が不完全である場合でも、コレット 305 を用いて力を加えることで、半導体層 308 を半導体基板 301 から完全に分離させ、半導体層 303 を得ることができる。コレット 305 として、真空チャック、メカニカルチャックなどのチャック、先端に接着剤が付着したマイクロニードルなど、半導体層 308 の一つに選択的に固着させることができる手段を用いる。図 9 (B) では、コレット 305 として真空チャックを用いる場合を例示している。

#### 【0169】

また、マイクロニードルに付着させる接着剤として、エポキシ系接着剤、セラミック系接着剤、シリコーン系接着剤、低温凝固剤などを用いることができる。低温凝固剤は、例え

10

20

30

40

50

ば MW - 1 ( 株式会社エミネントサプライ製 ) を用いることができる。MW - 1 は、凝固点が 17 度であり、それ以下の温度 ( 好ましくは、10 度以下 ) で接着効果を有し、17 度以上 ( 好ましくは 25 度程度 ) では接着効果を有さない。

#### 【 0170 】

なお、半導体基板 301 を劈開させる前に、半導体基板 301 に水素化処理を行うようにしても良い。水素化処理は、例えば、水素雰囲気中において 350 、2 時間程度行う。

#### 【 0171 】

次に、図 9 ( C ) に示すように、半導体層 303 の分離により露出した面が支持基板 310 側を向くように、半導体層 303 と支持基板 310 とを貼り合わせる。本実施の形態では、支持基板 310 上に絶縁膜 311 が形成されており、絶縁膜 311 と半導体層 303 10 とが接合することで、半導体層 303 と支持基板 310 とを貼り合わせることができる。半導体層 303 と絶縁膜 311 とを接合させた後、該接合をさらに強固にするため、400 乃至 600 の熱処理を行うのが好ましい。

#### 【 0172 】

接合の形成はファン・デル・ワールス力を用いて行われているため、室温でも強固な接合が形成される。なお、上記接合は低温で行うことが可能であるため、支持基板 310 は様々なものを用いることが可能である。例えば支持基板 310 としては、アルミニノシリケートガラスバリウムホウケイ酸ガラス、アルミニノホウケイ酸ガラスなどのガラス基板の他、石英基板、サファイア基板などの基板を用いることが出来る。さらに支持基板 310 として、シリコン、ガリウムヒ素、インジウムリンなどの半導体基板などを用いることができる。或いは、ステンレス基板を含む金属基板を支持基板 310 として用いても良い。20

#### 【 0173 】

なお、支持基板 310 は、その表面に絶縁膜 311 が必ずしも形成されていなくとも良い。絶縁膜 311 が形成されていない場合でも、支持基板 310 と半導体層 303 とを接合させることは可能である。ただし、支持基板 310 の表面に絶縁膜 311 を形成しておくことで、支持基板 310 から半導体層 303 に、アルカリ金属やアルカリ土類金属などの不純物が入り込むのを防ぐことができる。

#### 【 0174 】

絶縁膜 311 を形成する場合、支持基板 310 ではなく絶縁膜 311 が半導体層 303 と接合するので、支持基板 310 として用いることができる基板の種類がさらに広がる。プラスチック等の可撓性を有する合成樹脂からなる基板は耐熱温度が一般的に低い傾向にあるが、作製工程における処理温度に耐え得るのであれば、絶縁膜 311 を形成する場合において、支持基板 310 として用いることが可能である。30

#### 【 0175 】

なお、半導体層 303 を支持基板 310 上に貼り合わせる前または貼り合わせた後に、半導体層 303 の分離により露出した面に、レーザ光の照射による熱アニールを施しても良い。半導体層 303 を支持基板 310 上に貼り合わせる前に熱アニールを施すと、分離により露出した面が平坦化され、接合の強度をより高めることができる。また、半導体層 303 を支持基板 310 上に貼り合わせた後に熱アニールを施すと、半導体層 303 が一部溶解し、接合の強度をより高めることができる。40

#### 【 0176 】

また、半導体層 303 を支持基板 310 上に接合のみによって貼り合わせるのではなく、半導体層 303 に 10 MHz ~ 1 THz 程度の高周波数の振動を加えることで、半導体層 303 と支持基板 310 の間に摩擦熱を生じさせ、該熱により半導体層 303 を部分的に溶解させ、半導体層 303 を支持基板 310 上に貼り合わせるようにしてても良い。

#### 【 0177 】

なお、MW - 1 を低温凝固剤として用いる場合、まず低温凝固剤が接着効果を有しない温度 ( 例えば 25 度程度 ) において、マイクロニードルの先端に付着した低温凝固剤を、絶縁膜 304 に接触させる。次に、低温凝固剤が接着効果を有する温度 ( 例えば 5 度程度 ) まで温度を下げて、低温凝固剤を凝固させることで、マイクロニードルと絶縁膜 304 と 50

を固着させる。そして、半導体基板 301 から引き離した半導体層 303 を、支持基板 310 上に貼り合わせた後、再び接着効果を有しない温度（例えば 25 度程度）まで低温凝固剤の温度を高めることで、マイクロニードルを半導体層 303 から引き離すことができる。

#### 【0178】

半導体層 303 上の絶縁膜 304 を除去し、支持基板 310 及び絶縁膜 311 上に島状の半導体層 303 が形成される（図 9 (D) 参照）。半導体層 303 にさらにエッチングをし、形状を加工してもよい。

#### 【0179】

図 9 (A) 乃至 (D) のように、劈開により露出される半導体層の表面を支持基板側に向けると、より平坦性の高い側の表面がゲート絶縁膜に接するため、半導体層とゲート絶縁膜の間の界面準位密度を低く、なおかつ均一にすることができる。よって、ゲート絶縁膜に接する半導体層の表面を平坦化するための研磨を省略、もしくは研磨時間を短縮化することができ、コストを抑えスループットを向上させることができる。10

#### 【0180】

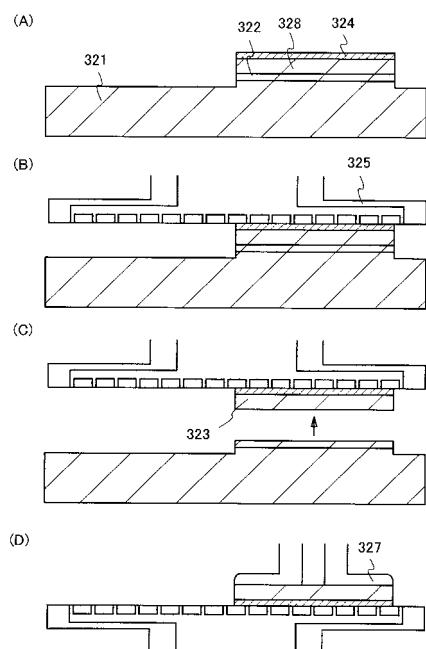

なお、劈開により露出される半導体層の表面と、半導体層上に形成するゲート絶縁膜とが接するように、半導体層を支持基板上に貼り合わせることもできる。この例を図 10 及び図 11 を用いて説明する。

#### 【0181】

図 10 (A) において、図 9 (A) と同様に、半導体基板 321、脆化層 322、半導体基板の一部である半導体層 328、絶縁膜 324 が形成されている。本実施の形態では、酸化珪素を絶縁膜 324 として用いる。20

#### 【0182】

次に、図 10 (B) に示すように半導体基板 321 を保持手段 325 に固着させる。半導体基板 321 の固着は、半導体層 328 が保持手段 325 側を向くように行う。保持手段 325 として、後の熱処理に耐えることができ、なおかつ複数の半導体層（図 10 では半導体層 328）と重なるように固着させることができる大型の真空チャックまたはメカニカルチャック、具体的には多孔質真空チャック、非接触式真空チャックなどを用いることができる。本実施の形態では、真空チャックを保持手段 325 として用いる例を示す。30

#### 【0183】

次に、熱処理を行うことにより、脆化層 322 において隣接する微小ボイドどうしが結合して、微小ボイドの体積が増大する。その結果、図 10 (C) に示すように、脆化層 322 において半導体基板 321 が劈開し、半導体基板 321 の一部であった半導体層 328 が、半導体層 323 となり、絶縁膜 324 と共に、半導体基板 321 から分離する。熱処理は、例えば 400 乃至 600 の温度範囲内で行えば良い。

#### 【0184】

なお、熱処理は、マイクロ波などの高周波による誘電加熱を用いて行っても良い。

#### 【0185】

また、半導体基板 321 を劈開させる前に、半導体基板 321 に水素化処理を行うようにしても良い。40

#### 【0186】

そして、図 10 (D) 及び図 11 (A) に示すように、コレット 327 を半導体層 323 の劈開により露出した面に固着させ、半導体層 323 を保持手段 325 から引き離す。コレット 327 として、真空チャック、メカニカルチャックなどのチャック、先端に接着剤が付着したマイクロニードルなど、半導体層 323 に選択的に固着させることができる手段を用いる。図 10 (D) 及び図 11 (A) では、コレット 327 として真空チャックを用いる場合を例示している。

#### 【0187】

なお、本実施の形態では、コレット 327 が半導体層 323 の劈開により露出した面に固着している例を示しているがコレット 327 により傷つくのを防ぐために、絶縁膜などの50

保護膜を形成しても良い。ただし、上記保護膜は、後に支持基板 330 に半導体層 323 を貼り合わせた後に、除去する。

【0188】

また、マイクロニードルに付着させる接着剤として、エポキシ系接着剤、セラミック系接着剤、シリコーン系接着剤、低温凝固剤などを用いることができる。

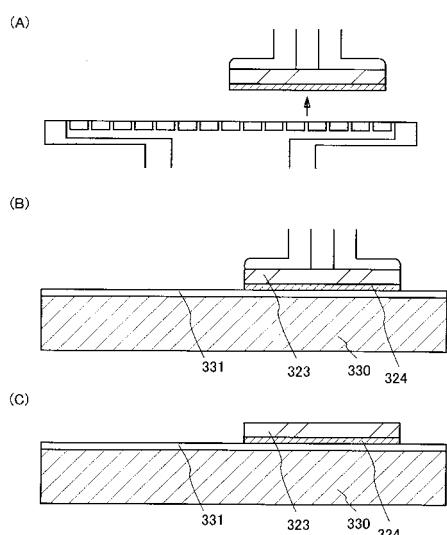

【0189】

次に、図 11 (B) に示すように、絶縁膜 324 が支持基板 330 側を向くように、すなわち劈開により露出した面の反対側の面が支持基板 330 側を向くように、半導体層 323 と支持基板 330 とを貼り合わせる。本実施の形態では、支持基板 330 上に絶縁膜 331 が形成されており、絶縁膜 324 と絶縁膜 331 とが接合することで、半導体層 323 と支持基板 330 とを貼り合わせることができる（図 11 (C) 参照。）。絶縁膜 324 と絶縁膜 331 とを接合させた後、該接合をさらに強固にするため、400 乃至 600 の熱処理を行うのが好ましい。10

【0190】

接合の形成はファン・デル・ワールス力を用いて行われているため、室温でも強固な接合が形成される。なお、上記接合は低温で行うことが可能であるため、支持基板 330 は様々なものを用いることが可能である。

【0191】

なお、支持基板 330 は、その表面に絶縁膜 331 が必ずしも形成されていなくとも良い。20

【0192】

なお、半導体基板は、反りや撓みを有している場合や、端部に丸みを帯びている場合がある。また、半導体基板から半導体層を分離するために水素又は希ガス、或いは水素イオン又は希ガスイオンを打ち込む際、半導体基板の端部において上記ガスまたはイオンの打ち込みを十分に行うことができない場合もある。そのため、半導体基板の端部に位置する部分は、半導体層を分離させるのが難しく、半導体基板を支持基板に貼り合わせた後に半導体基板を劈開して半導体層を形成する場合、半導体層間の間隔が数 mm ~ 数 cm となってしまう。しかし、本実施の形態では、半導体基板を支持基板に貼り合わせる前に、半導体基板を劈開させて半導体層を形成している。よって、半導体層を支持基板上に貼り合わせる際、半導体層間の間隔を、数十 μm 程度に小さく抑えることができ、半導体層間の隙間をまたぐように設けられた電界効果トランジスタで構成された画素を有する表示装置を作製することができる。30

【0193】

本実施の形態で説明した表示装置の画素を構成する電界効果トランジスタの作製方法は、複数の半導体基板を用いて一つの支持基板に複数の半導体層を貼り合わせることができるので、高スループットで処理を行うことができる。また、半導体素子の有する極性に合わせて半導体層の面方位を適宜選択することができる、半導体素子の移動度を高めることができ、より高速駆動が可能な電界効果トランジスタで構成される画素を有する表示装置を提供することができる。

【0194】

また、半導体基板の複数箇所において劈開することで複数の半導体層を形成し、該複数の半導体層を支持基板上に貼り合わせることができるので、表示装置を構成する画素の半導体素子の極性及びレイアウトに合わせて、複数の各半導体層を貼り合わせる位置を選択することができる。40

【0195】

本実施の形態は、実施の形態 1 と適宜組み合わせて実施することができる。

(実施の形態 4)

【0196】

本実施の形態では、本発明（特に実施の形態 3）に適用することができる表示装置の画素を構成する電界効果トランジスタを製造するための装置の構成について説明する。50

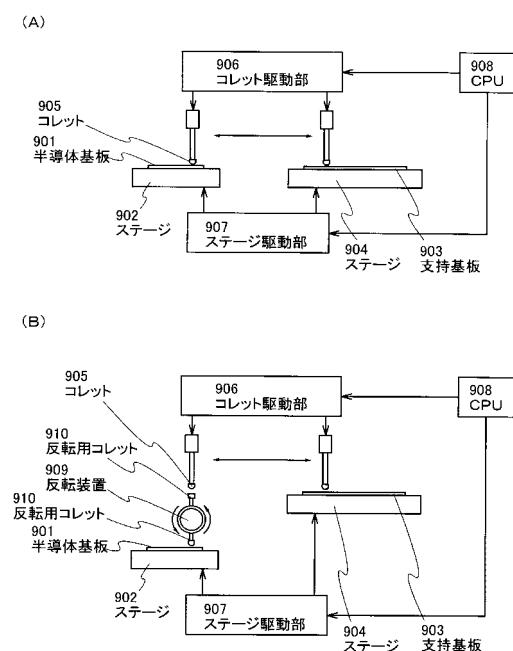

**【 0 1 9 7 】**

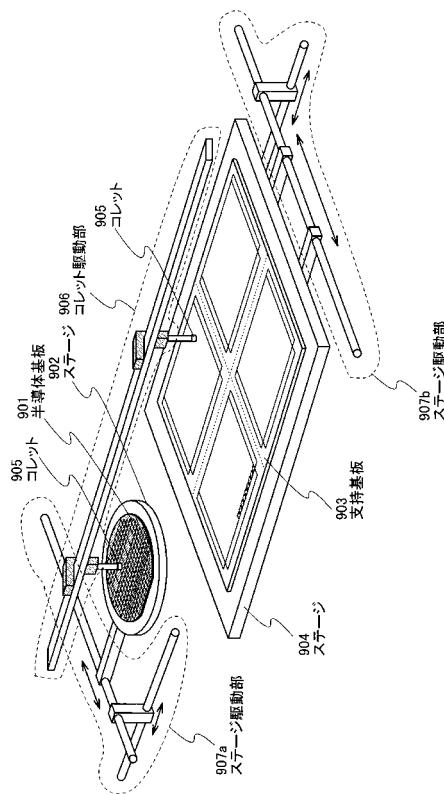

図12(A)に、本発明(特に実施の形態3)に適用できる製造装置の構成を一例として示す。図12(A)に示す製造装置は、半導体基板901を載置するステージ902と、支持基板903を載置するステージ904とを有する。なお図12(A)では、半導体基板901と支持基板903とを、互いに異なるステージに載置する例を示しているが、本発明はこの構成に限定されない。半導体基板901と支持基板903とを同一のステージに載置することも可能である。

**【 0 1 9 8 】**

また図12(A)では、1つの半導体基板901を載置するための1つのステージ902を示しているが、本発明はこの構成に限定されない。例えば本発明に適用できる製造装置は、一つの半導体基板901を載置するためのステージ902を複数有していても良いし、ステージ902上に複数の半導体基板901が載置できるようにしても良い。

10

**【 0 1 9 9 】**

さらに図12(A)に示す製造装置は、半導体基板901の劈開により形成される半導体層に固着し、なおかつ該半導体層を支持基板903の所定の位置に貼り合わせるコレット905を有する。コレット905として、真空チャック、メカニカルチャックなどのチャック、先端に接着剤が付着したマイクロニードルなど、半導体層の一つに選択的に固着させることができる手段を用いる。

**【 0 2 0 0 】**

また図12(A)に示す製造装置は、上記コレット905の位置を制御するコレット駆動部906と、ステージ902、ステージ904の位置を制御するステージ駆動部907と、コレットの位置情報またはステージの位置情報に従って、コレット駆動部906とステージ駆動部907の動作を制御するCPU908とを少なくとも有する。

20

**【 0 2 0 1 】**

コレットの位置情報またはステージの位置情報は、半導体基板901のどの位置に形成される半導体層を、支持基板903上のどの位置に貼り合わせるか、といった位置情報を元に作製することができる。なお、半導体基板901の位置合わせまたは支持基板903の位置合わせを行うために、図12(A)に示す製造装置に、CCD(電荷結合素子)などの撮像素子を有するカメラを設けても良い。

**【 0 2 0 2 】**

30

また、ステージ902上に、半導体基板901が有する熱を吸収または発散させるためのヒートシンクを設け、コレット905としてマイクロニードルの先端に低温凝固剤を付着させたものを用いる場合において、ヒートシンクを用いることで半導体基板901の温度を効率的に下げることができる。

**【 0 2 0 3 】**

また本発明に適用できる製造装置は、半導体基板901から半導体層を拾い上げた後に、上記半導体層を裏返すための反転装置を有していても良い。図12(B)に、図12(A)に示した製造装置に反転装置909を付加した形態を示す。反転装置909は、反転用コレット910を有しており、該反転用コレット910により半導体層を拾い上げて一時的に保持することができる。コレット905は、反転用コレット910に保持されている半導体層の、反転用コレット910が固着している面とは反対側の面に固着することで、反転用コレット910から半導体層を受け取ることができる。

40

**【 0 2 0 4 】**

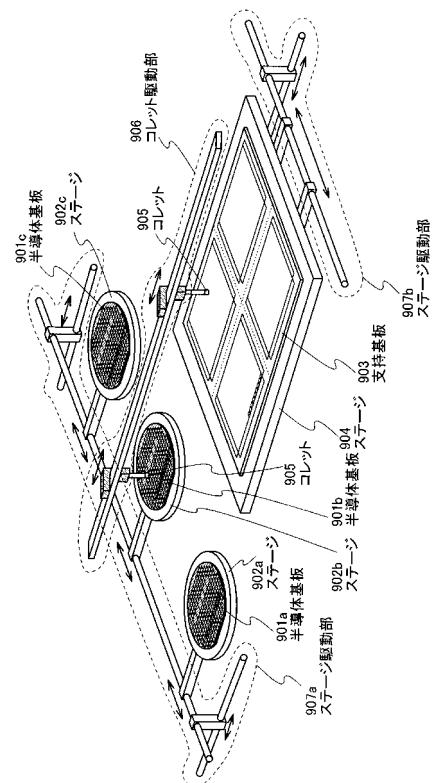

次に、図12(A)に示した半導体基板901、ステージ902、支持基板903、ステージ904、コレット905、コレット駆動部906、ステージ駆動部907の位置関係と具体的な構成を示すために、図13にそれらの斜視図を示す。なお図13では、ステージ902の動作を制御するステージ駆動部907aと、ステージ904の動作を制御するステージ駆動部907bとを用いている例を示している。

**【 0 2 0 5 】**

CPU908からの指示に従い、ステージ駆動部907aは、X方向またはY方向と交わ

50

るY方向にステージ902を移動させる。なおステージ駆動部907aが、X方向またはY方向に加え、X方向及びY方向によって形成される平面とは異なる平面に存在するZ方向に、ステージ902を移動させるようにしても良い。同様にステージ駆動部907bは、X方向またはX方向と交わるY方向にステージ904を移動させる。ステージ駆動部907bは、X方向またはY方向に加え、X方向及びY方向によって形成される平面とは異なる平面に存在するZ方向に、ステージ904を移動させるようにしても良い。

#### 【0206】

またコレット905は、半導体基板901の劈開によって形成される複数の半導体層の一つを拾い上げる。そしてコレット駆動部906は、半導体層を保持した状態のコレット905を、半導体基板901から支持基板903まで移送する。なお図13では、1つのコレット905が半導体基板901と支持基板903の間を行き来している例を示しているが、コレット905は複数用いられていても良い。複数のコレット905を用いる場合、各コレット905の動作を独立して制御するためにコレット駆動部906を複数用意しても良いし、全てのコレット905を1つのコレット駆動部906で制御しても良い。

10

#### 【0207】

次に、図13において複数のステージ902用いた場合の形態を、図14に示す。図14では、ステージ902a、ステージ902b、ステージ902cを用いている例を示しており、全てのステージ902a、ステージ902b、ステージ902cが、ステージ駆動部907aによって制御されている。なお、ステージ902a、ステージ902b、ステージ902cの動作を独立して制御するために、ステージ駆動部907aを複数用意しても良い。

20

#### 【0208】

また図14では、ステージ902a上に半導体基板901a、ステージ902b上に半導体基板901b、ステージ902c上に半導体基板901cが、それぞれ載置されている様子を示す。半導体基板901a、半導体基板901b、半導体基板901cの結晶面方位は、異なっていても、同じであっても良い。

#### 【0209】

また図14では、コレット905は、半導体基板901a、半導体基板901b、半導体基板901cの劈開によって形成される複数の半導体層の一つを拾い上げている。コレット駆動部906は、半導体層を保持した状態のコレット905を、半導体基板901a、半導体基板901b、半導体基板901cから支持基板903まで移送する。なお図14では、1つのコレット905が、半導体基板901a、半導体基板901b、半導体基板901cと支持基板903の間を行き来している例を示しているが、半導体基板901a、半導体基板901b、半導体基板901cのそれに、少なくとも1つのコレット905の対応するように、コレット905を複数用いても良い。

30

#### 【0210】

本発明に適用できる製造装置は、一つの半導体基板901から形成される複数の半導体層を、適宜支持基板903上の所望の位置に移送し、貼り合わせることができる。

#### 【0211】

本実施の形態は、実施の形態3と適宜組み合わせて実施することが可能である。

(実施の形態5)

40

#### 【0212】

本実施の形態では、半導体基板から、それぞれnチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタに適した半導体層を取り出す構成について示す。

#### 【0213】

実施の形態1乃至4で示すように、本発明の表示装置が有する画素を構成する電界効果トランジスタにおいては、半導体基板より分離させ転置した半導体層を用いるため、半導体基板を選択することによって、半導体層の結晶面方位を選択することができる。よって、その導電型の電界効果トランジスタにとって最適な半導体層の結晶面方位を有する半導体層をnチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタそれぞれ選

50

択することができる。

**【0214】**

結晶面方位の異なる半導体層を支持基板に接合する場合に、より好ましい態様として、半導体層のチャネル長方向の結晶軸を特定の方向とする。電界効果トランジスタにとって半導体層を流れる電子又はホールのキャリア移動度は、半導体層の結晶面方位での異方性と、キャリアの流れるチャネル長方向での異方性とを合わせることで、高めることができる。これは、結晶中でキャリアの有効質量が異方性を有するからである。

**【0215】**

例えば、結晶面方位が {100} 面の半導体基板から n チャネル型電界効果トランジスタ用の半導体層を取り出す場合には、チャネル長方向が <100> 軸となるようにすることが好ましい。また、半導体層面内に同じ <100> 軸の結晶軸が複数ある場合は、いずれかの <100> 軸の結晶軸をチャネル長方向として用いることができる。

10

**【0216】**

一方、p チャネル型電界効果トランジスタ用の半導体層を形成するには、{110} 面の半導体基板を用い、チャネル長方向が <110> 軸と平行な方向になるようにすることが好ましい。このように、n チャネル型電界効果トランジスタについて <100> 軸、p チャネル型電界効果トランジスタについて <110> 軸とすれば、チャネル形成領域を流れる電子とホールの移動度をより高めることができる。

**【0217】**

本実施の形態は、実施の形態 1 乃至 4 それぞれと適宜組み合わせて実施することが可能である。

20

(実施の形態 6)

**【0218】**

本実施の形態は、同一の結晶面を有する半導体基板から、それぞれ n チャネル型電界効果トランジスタと p チャネル型電界効果トランジスタに適した半導体層を取り出す構成について示す。

**【0219】**

{110} 面の半導体基板を用いる場合について示す。この場合、n チャネル型電界効果トランジスタ用の半導体層は、チャネル長方向が <100> 軸となるように形成する。一方、p チャネル型電界効果トランジスタ用の半導体層は、チャネル長方向が <110> 軸となるように形成する。

30

**【0220】**

本実施の形態によれば、支持基板上に、n チャネル型電界効果トランジスタとなる第 1 の半導体層と、p チャネル型電界効果トランジスタとなる第 2 の半導体層とを、同じ結晶面の半導体基板から取り出すことができ、かつチャネル長方向の結晶軸の向きが互いに異なる半導体集積回路等を得ることができる。n チャネル型電界効果トランジスタについて <100> 軸、p チャネル型電界効果トランジスタについて <110> 軸とすれば、チャネル形成領域を流れる電子とホールの移動度をより高めることができる。

**【0221】**

n チャネル型電界効果トランジスタの半導体層と p チャネル型電界効果トランジスタの半導体層とは、それぞれ支持基板に接合させるため、n チャネル型電界効果トランジスタと p チャネル型電界効果トランジスタの回路配置に設計の自由度が確保される。その結果、表示装置が有する画素の電界効果トランジスタの集積度を向上させることもできる。本発明の電界効果トランジスタを有する画素で構成された表示装置は、支持基板上に、移動度が高い電界効果トランジスタを形成したため動作の高速化を図ることができ、また低電圧で駆動することができとなり、低消費電力化を図ることができる。また、本実施の形態によれば素子分離を行うための構造を形成する必要がないので製造工程を簡略化できる。

40

**【0222】**

本実施の形態は、実施の形態 1 乃至 4 それぞれと適宜組み合わせて実施することが可能である。

50

(実施の形態 7 )

【 0 2 2 3 】

本実施の形態では、高性能、かつ高い信頼性を付与することを目的とした表示装置の電界効果トランジスタ（単にトランジスタと略記することもある）で構成される画素の一例について説明する。詳しくは電界効果トランジスタで構成される画素の一例として、EL（Electro Luminescence）素子を始めとする発光素子を用いたアクティブラマトリクス型の表示装置の画素の一例について説明する。

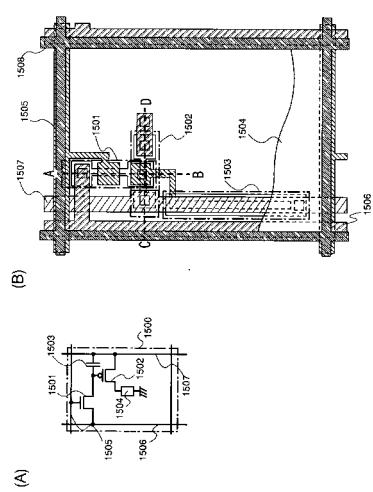

【 0 2 2 4 】

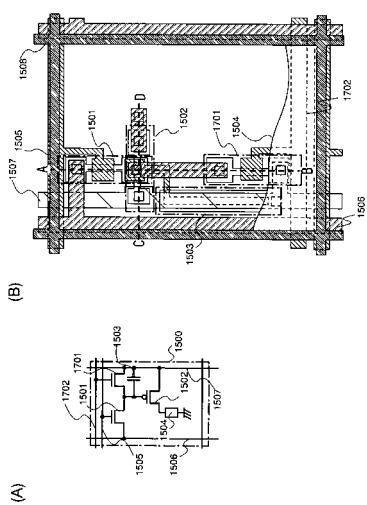

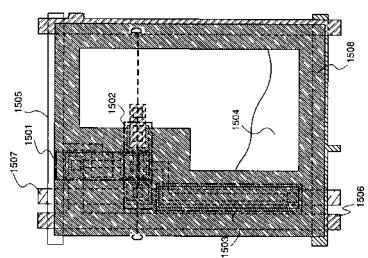

ここで発光素子を具備する表示装置における画素の回路図を図15(A)に、画素の上面構造を図15(B)に、図15(B)に示した上面構造の断面図に関して図16に示す。図15及び図16は共通の符号で表記できる箇所に関しては共通の符号を用い、互いに参考して説明するものとする。なお、本実施の形態で示す本発明の表示装置における画素の構成は一例であってこれに限定されるものではないことを付記する。

10

【 0 2 2 5 】

図15(A)、図15(B)において、画素1500は、選択用トランジスタ1501（第1の電界効果トランジスタともいう）と、駆動用トランジスタ1502（第2の電界効果トランジスタともいう）と、容量素子1503と、発光素子1504を有する。また選択用トランジスタ1501はnチャネル型電界効果トランジスタ、駆動用トランジスタ1502はpチャネル型電界効果トランジスタであるとするが、これに限定されるものではない。なお、本実施の形態でいう選択用トランジスタとは選択された画素に信号線からの信号を入力するための電界効果トランジスタであり、駆動用トランジスタとは選択された画素を点灯するための信号を発光素子に供給するための電界効果トランジスタである。また選択用トランジスタ1501のゲートには走査線1505が接続され、ソース又はドレインの一方の端子（第1端子ともいう）には信号線1506が接続され、ソース又はドレインの他方の端子（第2端子ともいう）には駆動用トランジスタ1502のゲート及び容量素子1503の一方の電極が接続される。また駆動用トランジスタの第1端子には電源線1507が接続され、第2端子には発光素子1504が接続される。また容量素子1503の第2の電極は電源線1507に接続されている。

20

【 0 2 2 6 】

なお本明細書にて用いる第1、第2、第3、乃至第N（Nは自然数）という用語は、構成要素の混同を避けるために付したものであり、数的に限定するものではないことを付記する。

30

【 0 2 2 7 】

選択用トランジスタ1501及び駆動用トランジスタ1502は、本実施の形態では、1つのゲートを有する構造としているが、複数のゲートを配して、複数の電界効果トランジスタが電気的に直列に接続される構造としてもよい。複数の電界効果トランジスタが電気的に直列に接続される構造とすることにより、オフ電流値を低減することができるという利点がある。

【 0 2 2 8 】

なお、駆動用トランジスタ1502は発光素子1504の点灯を制御するための素子であるため、多くの電流が流れ、熱による劣化やホットキャリアによる劣化の危険性が高い素子でもある。そのため、駆動用トランジスタ1502のドレイン側に、ゲート絶縁膜を介してゲート電極に重なるようにLDD（Light Doped Drain）領域を設ける構造は極めて有効である。

40

【 0 2 2 9 】

また、図15(B)に示すように、駆動用トランジスタ1502のゲートを含む配線は電源線1507と重畠する領域まで延在して容量素子1503が形成される。容量素子1503は、電源線1507と電気的に接続された半導体層（図示せず）、ゲート絶縁膜と同一層の絶縁膜（図示せず）及び駆動用トランジスタ1502のゲートを含む配線との間で形成される。この容量素子1503は駆動用トランジスタ1502のゲートとソースの

50

間に印加する電圧を保持する機能を有する。

#### 【0230】

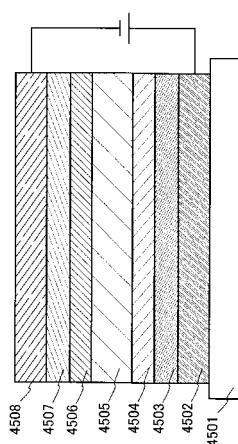

また、発光素子1504はR(赤)、G(緑)、B(青)の各色に対応した発光層を具備し、各画素に設けられる。なお発光素子1504の発光層として、イエロー、シアン、マゼンタ、または白の各色に対応した発光層を具備し、各画素に設けられてもよい。本実施の形態に適用可能な発光素子の例を図19に示す。

#### 【0231】

発光素子は、電界効果トランジスタ等の素子が形成された基板4501の上に、陽極4502、正孔注入材料からなる正孔注入層4503、その上に正孔輸送材料からなる正孔輸送層4504、発光層4505、電子輸送材料からなる電子輸送層4506、電子注入材料からなる電子注入層4507、そして陰極4508を積層させた素子構造である。ここで、発光層4505は、一種類の発光材料のみから形成されることもあるが、2種類以上の材料から形成されてもよい。また本実施の形態の素子の構造は、この構造に限定されない。

10

#### 【0232】

また、図19で示した各機能層を積層した積層構造の他、高分子化合物を用いた素子、発光層に三重項励起状態から発光する三重項発光材料を利用した高効率素子など、バリエーションは多岐にわたる。ホールブロック層によってキャリアの再結合領域を制御し、発光領域を2つの領域に分けることによって得られる白色発光素子などにも応用可能である。

20

#### 【0233】

次に、図19に示す素子の作製方法について説明する。まず、陽極4502(ITO(インジウム錫酸化物))を有する基板4501に正孔注入材料、正孔輸送材料、発光材料を順に蒸着する。次に電子輸送材料、電子注入材料を蒸着し、最後に陰極4508を蒸着で形成する。

20

#### 【0234】

次に、正孔注入材料、正孔輸送材料、電子輸送材料、電子注入材料、発光材料の材料に好適な材料を以下に列挙する。

#### 【0235】

正孔注入材料としては、有機化合物でればポルフィリン系の化合物や、フタロシアニン(以下「H<sub>2</sub>Pc」と記す)、銅フタロシアニン(以下「CuPc」と記す)などが有効である。また、使用する正孔輸送材料よりもイオン化ポテンシャルの値が小さく、かつ、正孔輸送機能をもつ材料であれば、これも正孔注入材料として使用できる。導電性高分子化合物に化学ドーピングを施した材料もあり、ポリスチレンスルホン酸(以下「PSS」と記す)をドープしたポリエチレンジオキシチオフェン(以下「PEDOT」と記す)や、ポリアニリンなどが挙げられる。また、絶縁体の高分子化合物も陽極の平坦化の点で有効であり、ポリイミド(以下「PI」と記す)がよく用いられる。さらに、無機化合物も用いられ、金や白金などの金属薄膜の他、酸化アルミニウム(以下「アルミナ」と記す)の超薄膜などがある。

30

#### 【0236】

正孔輸送材料として最も広く用いられているのは、芳香族アミン系(すなわち、ベンゼン環-窒素の結合を有するものの化合物である。広く用いられている材料として、4,4'-ビス(ジフェニルアミノ)-ビフェニル(以下、「TAD」と記す)や、その誘導体である4,4'-ビス[N-(3-メチルフェニル)-N-フェニル-アミノ]-ビフェニル(以下、「TPD」と記す)、4,4'-ビス[N-(1-ナフチル)-N-フェニル-アミノ]-ビフェニル(以下、「NPD」と記す)がある。4,4',4"-トリス(N,N-ジフェニル-アミノ)-トリフェニルアミン(以下、「TDATA」と記す)、4,4',4"-トリス(N,N-(3-メチルフェニル)-N-フェニル-アミノ)-トリフェニルアミン(以下、「MTDATA」と記す)などのスターバースト型芳香族アミン化合物が挙げられる。

40

#### 【0237】

50

電子輸送材料としては、金属錯体がよく用いられ、トリス(8-キノリノラト)アルミニウム(以下、「Alq<sub>3</sub>」と記す)、BA1q、トリス(4-メチル-8-キノリノラト)アルミニウム(以下、「Almq」と記す)、ビス(10-ヒドロキシベンゾ[h]-キノリナト)ベリリウム(以下、「Bebq」と記す)などのキノリン骨格またはベンゾキノリン骨格を有する金属錯体などがある。また、ビス[2-(2-ヒドロキシフェニル)-ベンゾオキサゾラト]亜鉛(以下、「Zn(BOX)<sub>2</sub>」と記す)、ビス[2-(2-ヒドロキシフェニル)-ベンゾチアゾラト]亜鉛(以下、「Zn(BTZ)<sub>2</sub>」と記す)などのオキサゾール系、チアゾール系配位子を有する金属錯体もある。さらに、金属錯体以外にも、2-(4-ビフェニリル)-5-(4-tert-ブチルフェニル)-1,3,4-オキサジアゾール(以下、「PBD」と記す)、OXD-7などのオキサジアゾール誘導体、TAZ、3-(4-tert-ブチルフェニル)-4-(4-エチルフェニル)-5-(4-ビフェニリル)-1,2,4-トリアゾール(以下、「p-EtTAZ」と記す)などのトリアゾール誘導体、バソフェナントロリン(以下、「BPhen」と記す)、BCPなどのフェナントロリン誘導体が電子輸送性を有する。

#### 【0238】

電子注入材料としては、上で述べた電子輸送材料を用いることができる。その他に、フッ化カルシウム、フッ化リチウム、フッ化セシウムなどの金属ハロゲン化物や、酸化リチウムなどのアルカリ金属酸化物のような絶縁体の、超薄膜がよく用いられる。また、リチウムアセチルアセトネット(以下、「Li(acac)」と記す)や8-キノリノラト-リチウム(以下、「Liq」と記す)などのアルカリ金属錯体も有効である。

#### 【0239】

発光材料としては、先に述べたAlq<sub>3</sub>、Almq、Bebq、BA1q、Zn(BOX)<sub>2</sub>、Zn(BTZ)<sub>2</sub>などの金属錯体の他、各種蛍光色素が有効である。蛍光色素としては、青色の4',4''-ビス(2,2'-ジフェニル-ビニル)-ビフェニルや、赤橙色の4-(ジシアノメチレン)-2-メチル-6-(p-ジメチルアミノスチリル)-4H-ピランなどがある。また、三重項発光材料も可能であり、白金ないしはイリジウムを中心金属とする錯体が主体である。三重項発光材料として、トリス(2-フェニルピリジン)イリジウム、ビス(2-(4'-トリル)ピリジナト-N,C<sup>2'</sup>)アセチルアセトナトイリジウム(以下「acacIrr(tpy)<sub>2</sub>」と記す)、2,3,7,8,12,13,17,18-オクタエチル-21H,23Hポルフィリン-白金などが知られている。

#### 【0240】

以上で述べたような各機能を有する材料を、各々組み合わせ、高信頼性の発光素子を作製することができる。

#### 【0241】

また、図19とは逆の順番に層を形成した発光素子を用いることもできる。つまり、基板4501の上に陰極4508、電子注入材料からなる電子注入層4507、その上に電子輸送材料からなる電子輸送層4506、発光層4505、正孔輸送材料からなる正孔輸送層4504、正孔注入材料からなる正孔注入層4503、そして陽極4502を積層させた素子構造である。

#### 【0242】

また、発光素子は発光を取り出すために少なくとも陽極又は陰極の一方が透明であればよい。そして、基板上に電界効果トランジスタ及び発光素子を形成し、基板とは逆側の面から発光を取り出す上面射出や、基板側の面から発光を取り出す下面射出や、基板側及び基板とは反対側の面から発光を取り出す両面射出構造の発光素子があり、画素構成はどの射出構造の発光素子にも適用することができる。本実施の形態においては、一例として、図15及び図16には、上面射出構造の発光素子を適用した画素の例を挙げて説明することにする。上面射出構造の発光素子を適用した画素の場合、発光素子は画素を構成する素子上に画素毎に形成された図15(B)に示す隔壁1508の内側に設けられる。また、上面射出構造の発光素子を適用した画素の場合、基板側の面に向けて射出される光を基板

10

20

30

40

50

とは逆側の面に向けて反射するための反射電極を設けることが好適である。反射電極としては、陽極としてITO(インジウム錫酸化物)を用いる場合、ITOの下層にAlとチタンとの合金層と、チタン層との積層構造を採用することで、抵抗値が低く且つ安価な材料であるアルミニウムを採用することができ、且つチタン層をITOとアルミニウムとの間の良好な接続を確保することができる。なお下面射出構造または両面射出構造の場合には、画素を構成する電界効果トランジスタ等の配置に応じて画素を構成する素子上に隔壁を設け、そして発光素子を設ければよい。

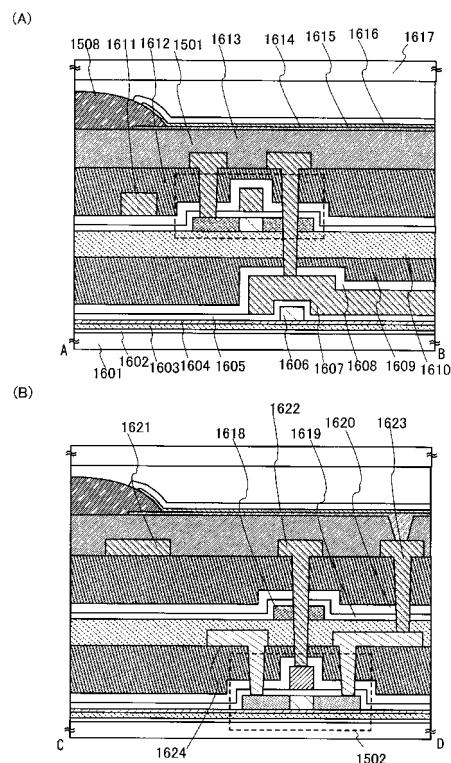

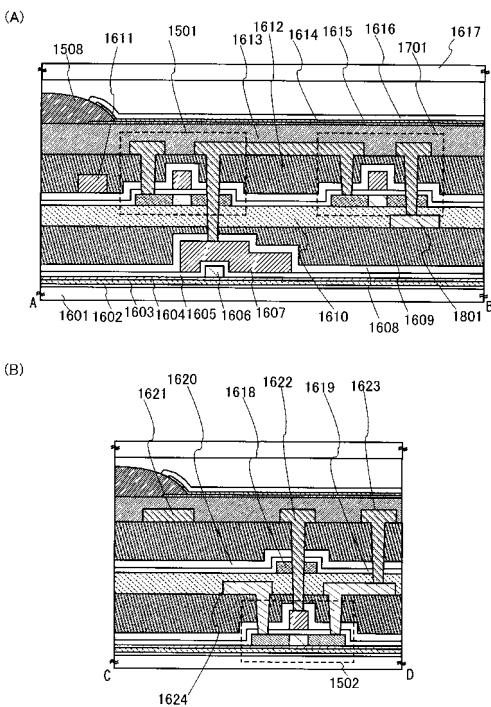

#### 【0243】

次に図15(B)に示した画素の上面図に対応する断面図について説明する。図16(A)は、図15(B)に示すA-Bの部分の断面図の一例である。また図16(B)は、図15(B)に示すC-Dの部分の断面図の一例である。なお本実施の形態における断面図に示す各素子は、断面構造を明確に記すために、誇張した縮尺により表記するものとする。

10

#### 【0244】

図16(A)では、支持基板1601上に、ブロッキング膜1602、絶縁層1603、保護層1604、絶縁層1605、半導体層1606、配線層1607、保護層1608、平坦化層1609、絶縁層1610、選択用トランジスタ1501、配線層1611、平坦化層1612、平坦化層1613、隔壁1508、画素電極1614、有機薄膜1615、有機導電体膜1616、及び対向基板1617が設けられた断面図について示している。なお、絶縁層1605は、駆動用トランジスタ1502のゲート絶縁膜として機能するものである。また、半導体層1606は駆動用トランジスタ1502の半導体層として機能するものである。また、配線層1607は駆動用トランジスタ1502のゲート電極として機能するものである。また配線層1611は、選択用トランジスタ1501のゲートに接続される走査線1505としての機能を有するものである。また画素電極1614、有機薄膜1615、及び有機導電体膜1616は積層して設けることにより、発光素子1504としての機能を有するものである。

20

#### 【0245】

また図16(B)では、支持基板上にブロッキング膜、絶縁層、及び保護層を介して配線層1624に接続された駆動用トランジスタ1502が設けられ、駆動用トランジスタ1502上に平坦化層、絶縁層を介して半導体層1618、絶縁層1619、保護層1620が設けられ、更に平坦化層上に、配線層1621、配線層1622、配線層1623が設けられた断面図を示している。なお配線層1624は駆動用トランジスタ1502のソースまたはドレインの一方に接続されており、電源線1507として機能するものである。また半導体層1618は選択用トランジスタ1501の半導体層におけるソースまたはドレインの一方として機能するものである。また、絶縁層1619は選択用トランジスタ1501におけるゲート絶縁膜として機能するものである。また、配線層1621は信号線1506として機能するものである。また、配線層1622は支持基板の垂直方向に対し、平坦化層及び絶縁層を貫通するように形成された開口により、選択用トランジスタ1501のソースまたはドレインの一方と駆動用トランジスタのゲートとを接続する機能を有する。また、配線層1623は、平坦化層、保護層1620、及び絶縁層1619を貫通するように形成された開口により、駆動用トランジスタのソースまたはドレインの他方と画素電極とを接続する機能を有する。

30

#### 【0246】

本実施の形態で示す画素で構成される発光素子を具備する表示装置は、上記実施の形態で示した半導体基板を用いて作製することができる。従って、ガラス基板等の透光性基板である支持基板1601上に3次元的に設けられた選択用トランジスタ1501、駆動用トランジスタ1502のチャネル領域を単結晶シリコンで作製することができる。そして、3次元的に半導体層を積層し高集積化した構造の電界効果トランジスタで構成された画素を有するため、半導体層は同一絶縁層に接して隣接して配置される他、上下方向に平坦化層を介して異なる絶縁層に接して積層することができる。従って、画素内の電界効果ト

40

50

ランジスタの配置の自由度が広く、より高集積化、高性能化を達成することができる。

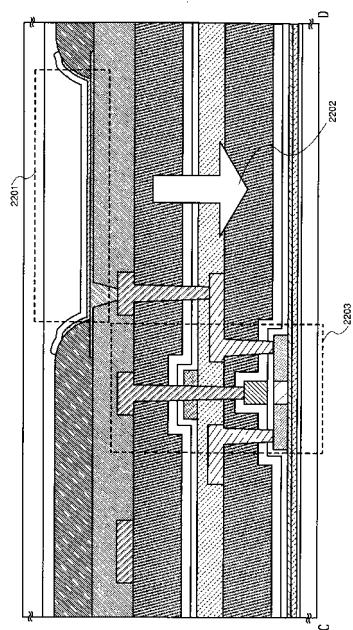

#### 【0247】

また、図15及び図16にて説明した表示装置の画素の上面図及び断面図の構成は、上面射出構造の発光素子を具備するものについて説明した。下面射出構造の発光素子を具備する構成について図21及び図22を用いて簡単に説明する。なお図21及び図22にて説明する上面図及びその断面図については、図15及び図16で示した回路図及び断面構造の積層構造に関する説明を援用するものとする。

#### 【0248】

図21において、図15(B)に示した上面図との違いは、支持基板が設けられる面から発光を取り出すために隔壁1508の内側に設けられる発光素子1504の占める領域が、電界効果トランジスタが設けられる領域とは重畠することなく設けられた点にある。

図21に示す上面図におけるC-Dの断面構造について、図22に示す。

10

#### 【0249】

図22に示す図21で示したC-Dの断面図は、上述したように発光素子が発光する領域2201より支持基板側の面となる矢印2202の方向に向けて発光が取り出されることとなる。発光素子が発光する領域2201は、電界効果トランジスタが設けられる領域2203と重畠することなく設けることで、発光素子の発光を効率よく外部に取り出すことができる。本発明の表示装置を構成する画素が有する電界効果トランジスタの構成においては、電界効果トランジスタ毎に3次元的に半導体層を積層し高集積化した構造の電界効果トランジスタで構成された画素を有するため、上下方向に平坦化層を介して異なる絶縁層に接して積層することができる。そのため、図21及び図22で説明したように、下面射出構造の発光素子を具備する表示装置においては、発光素子が発光する領域2201と電界効果トランジスタが設けられる領域2203とが重畠する面積を削減することができるため、画素の開口率の向上及び画素に占める電界効果トランジスタの面積の削減を図ることができ、好適である。

20

#### 【0250】

なお、本実施の形態で示した表示装置の画素の構成はこれに限られない。例えば、図17(A)、図17(B)に示したように、第2の走査線に接続された消去用トランジスタ(第3の電界効果トランジスタともいう)で構成された画素を有する表示装置としてもよい。図15及び図16で示した画素の構成とは異なる画素の回路図を図17(A)に、画素の上面構造を図17(B)に、図17(B)に示した上面構造の断面図に関して図18に示す。なお、図17及び図18は共通の符号で表記できる箇所に関しては共通の符号を用い、互いに参照して説明するものとする。また、図15で説明した画素と共に機能を有する構成については同じ符号を付して説明するものとする。

30

#### 【0251】

図17(A)、図17(B)において、画素1500は、選択用トランジスタ1501(第1の電界効果トランジスタともいう)と、駆動用トランジスタ1502(第2の電界効果トランジスタともいう)と、消去用トランジスタ1701(第3の電界効果トランジスタともいう)と、容量素子1503と、発光素子1504を有する。また選択用トランジスタ1501および消去用トランジスタ1701はNチャネル型電界効果トランジスタ、駆動用トランジスタ1502はPチャネル型電界効果トランジスタであるとするが、これに限定されるものではない。なお、本実施の形態でいう消去用トランジスタとは信号線から入力された信号を消去するための電界効果トランジスタである。また選択用トランジスタ1501のゲートには走査線1505(以下第1の走査線1505という)が接続され、ソース又はドレインの一方の端子(第1端子ともいう)には信号線1506が接続され、ソース又はドレインの他方の端子(第2端子ともいう)には駆動用トランジスタ1502のゲート、容量素子1503の一方の電極、及び消去用トランジスタ1701の第1端子が接続される。また駆動用トランジスタの第1端子には電源線1507が接続され、第2端子には発光素子1504は接続される。また消去用トランジスタ1701のゲートには、第2の走査線1702が接続され、第2端子には電源線1507が接続される。ま

40

50

た容量素子 1503 の第 2 の電極は電源線 1507 に接続されている。

**【0252】**

消去用トランジスタ 1701 は、本実施の形態では、1 つのゲートを有する構造としているが、複数のゲートを配して、複数の電界効果トランジスタが電気的に直列に接続される構造としてもよい。複数の電界効果トランジスタが電気的に直列に接続される構造とすることにより、オフ電流値を低減することができるという利点がある。

**【0253】**

また、図 17 (B) に示すように、消去用トランジスタ 1701 は、第 2 端子が電源線 1507 に接続され、第 2 の走査線 1702 による制御により、容量素子 1503 に保持された駆動用トランジスタ 1502 のゲートとソースの間にかかる電圧を消去する機能を有する。

10

**【0254】**

次に図 17 (B) に示した画素の上面図に対応する断面図について説明する。図 18 (A) は、図 17 (B) に示す A - B の部分の断面図の一例である。また図 18 (B) は、図 17 (B) に示す C - D の部分の断面図の一例である。なお本実施の形態における断面図に示す各素子は、断面構造を明確に記すために、誇張した縮尺により表記するものとする。

**【0255】**

図 18 (A) では、支持基板 1601 上に、プロッキング膜 1602、絶縁層 1603、保護層 1604、絶縁層 1605、半導体層 1606、配線層 1607、保護層 1608、平坦化層 1609、絶縁層 1610、配線層 1611、選択用トランジスタ 1501、消去用トランジスタ 1701、配線層 1611、平坦化層 1612、平坦化層 1613、隔壁 1508、画素電極 1614、有機薄膜 1615、有機導電体膜 1616、及び対向基板 1617 が設けられた断面図について示している。なお、絶縁層 1605 は、駆動用トランジスタ 1502 のゲート絶縁膜として機能するものである。また、半導体層 1606 は駆動用トランジスタ 1502 の半導体層として機能するものである。また、配線層 1607 は駆動用トランジスタ 1502 のゲート電極として機能するものである。また配線層 1601 は、電源線 1507 より延びて設けられ、電源線の電位と等電位の配線として機能するものである。また配線層 1611 は、選択用トランジスタ 1501 のゲートに接続される走査線 1505 としての機能を有するものである。また画素電極 1614、有機薄膜 1615、及び有機導電体膜 1616 は積層して設けることにより、発光素子 1504 としての機能を有するものである。

20

**【0256】**

また図 18 (B) では、支持基板上にプロッキング膜、絶縁層、及び保護層を介して配線層 1624 に接続された駆動用トランジスタ 1502 が設けられ、駆動用トランジスタ 1502 上に平坦化層、絶縁層を介して半導体層 1618、絶縁層 1619、保護層 1620 が設けられ、更に平坦化層上に、配線層 1621、配線層 1622、配線層 1623 が設けられた断面図を示している。なお配線層 1624 は駆動用トランジスタ 1502 のソースまたはドレインの一方に接続されており、電源線 1507 として機能するものである。また半導体層 1618 は選択用トランジスタ 1501 の半導体層におけるソースまたはドレインの一方として機能するものである。また、絶縁層 1619 は選択用トランジスタ 1501 におけるゲート絶縁膜として機能するものである。また、配線層 1621 は信号線 1506 として機能するものである。また、配線層 1622 は支持基板の垂直方向に対し、平坦化層及び絶縁層を貫通するように形成された開口により、選択用トランジスタ 1501 のソースまたはドレインの一方と駆動用トランジスタのゲートとを接続する機能を有する。また、配線層 1623 は、平坦化層、保護層 1620、及び絶縁層 1619 を貫通するように形成された開口により、駆動用トランジスタのソースまたはドレインの他方と画素電極とを接続する機能を有する。

30

40

**【0257】**

本実施の形態で示す画素で構成される発光素子を具備する表示装置は、上記実施の形態

50

で示した半導体基板を用いて作製することができる。従って、ガラス基板等の透光性基板である支持基板 1601 上に 3 次元的に設けられた選択用トランジスタ 1501、駆動用トランジスタ 1502 のチャネル領域を単結晶シリコンで作製することができる。そして特に図 17 及び図 18 で説明した画素の構造を具備する表示装置は、n チャネル型電界効果トランジスタ及び p チャネル型電界効果トランジスタ毎に作製する層を分けて発光素子を具備する表示装置を作製することができる。そして同じ導電型の電界効果トランジスタ毎に 3 次元的に半導体層を積層し高集積化した構造の電界効果トランジスタで構成された画素を有するため、半導体層は同一絶縁層に接して隣接して配置される他、上下方向に平坦化層を介して異なる絶縁層に接して積層することができる。従って、画素内の電界効果トランジスタの配置の自由度が広く、より高集積化、高性能化を達成することができる。

そして特に図 21 及び図 22 で説明した下面射出構造の発光素子を具備する表示装置においては、画素の開口率の向上及び画素に占める電界効果トランジスタの面積の削減を図ることができ、好適である。

#### 【 0258 】

上述の表示装置を構成する画素は、ガラス基板上に接合されたそれぞれ結晶面方位が一定の半導体層によって各画素の電界効果トランジスタが形成されているので、表示速度の高速化のみならず低消費電力化を図ることができる。

#### 【 0259 】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

#### ( 実施の形態 8 )

#### 【 0260 】

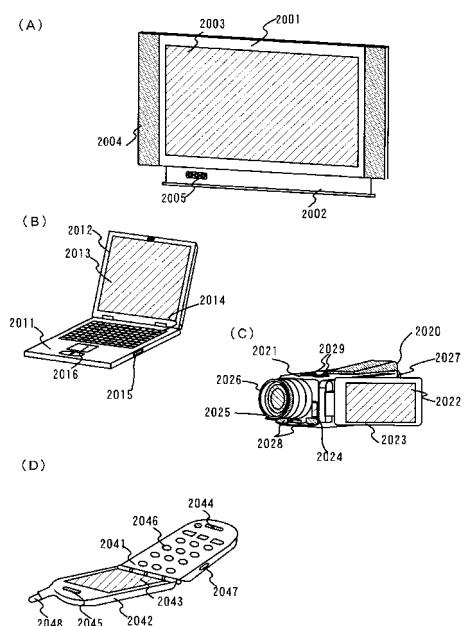

本実施の形態では、本発明を適用して作製された表示装置を用いて完成させた様々な電子機器について、図 20 を用いて説明する。

#### 【 0261 】

本発明を適用して作製された表示装置を有する電子機器として、テレビジョン、ビデオカメラ、デジタルカメラ等のカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーオーディオ、オーディオコンポ等）、ノート型パーソナルコンピュータ、ゲーム機器、携帯情報端末（モバイルコンピュータ、携帯電話、携帯型ゲーム機又は電子書籍等）、記録媒体を備えた画像再生装置（具体的にはデジタルビデオディスク（DVD）等の記録媒体を再生し、その画像を表示しうる表示装置を備えた装置）、照明器具等が挙げられる。これらの電子機器の具体例を図 20 に示す。

#### 【 0262 】

図 20 ( A ) は画像表示機であり、筐体 2001、支持台 2002、表示部 2003、スピーカー部 2004、ビデオ入力端子 2005 等を含む。本発明を用いて形成される表示装置を表示部 2003 等に用いることにより作製される。なお、画像表示機は、パーソナルコンピュータ用、TV 放送受信用、広告表示用等の全ての情報表示用装置が含まれる。上記実施の形態で示した支持基板に形成される電界効果トランジスタを用いて表示部 2003 の画素を作製することにより、表示部 2003 の画素を構成する電界効果トランジスタの高性能化を実現し、且つ電界効果トランジスタの微細加工技術に依拠することなく、画素内の電界効果トランジスタ数を増やしても電界効果トランジスタ数の増加に伴い低下した画素の開口率を向上及び画素に占める電界効果トランジスタの面積の削減を図ることのできる表示部 2003 を有する画像表示機を提供することができる。

#### 【 0263 】

図 20 ( B ) はノート型パーソナルコンピュータであり、本体 2011、筐体 2012、表示部 2013、キーボード 2014、外部接続ポート 2015、ポインティングマウス 2016 等を含む。本発明を用いて形成される表示装置をその表示部 2013 に用いることにより作製される。上記実施の形態で示した支持基板に形成される電界効果トランジスタを用いて表示部 2003 の画素を作製することにより、表示部 2013 の画素を構成する電界効果トランジスタの高性能化を実現し、且つ電界効果トランジスタの微細加工技

10

20

30

40

50

術に依拠することなく、画素内の電界効果トランジスタ数を増やしても電界効果トランジスタ数の増加に伴い低下した画素の開口率を向上及び画素に占める電界効果トランジスタの面積の削減を図ることのできる表示部 2013 を有するノート型パーソナルコンピュータを提供することができる。

#### 【0264】

図 20 (C) はビデオカメラであり、本体 2021、表示部 2022、筐体 2023、外部接続ポート 2024、リモコン受信部 2025、受像部 2026、バッテリー 2027、音声入力部 2028、操作キー 2029、接眼部 2020 等を含む。上記実施の形態で示した支持基板に形成される電界効果トランジスタを用いて表示部 2022 の画素を作製することにより、表示部 2022 の画素を構成する電界効果トランジスタの高性能化を実現し、且つ電界効果トランジスタの微細加工技術に依拠することなく、画素内の電界効果トランジスタ数を増やしても電界効果トランジスタ数の増加に伴い低下した画素の開口率を向上及び画素に占める電界効果トランジスタの面積の削減を図ることのできる表示部 2022 を有するビデオカメラを提供することができる。10

#### 【0265】

図 20 (D) は携帯電話であり、本体 2041、筐体 2042、表示部 2043、音声入力部 2044、音声出力部 2045、操作キー 2046、外部接続ポート 2047、アンテナ 2048 等を含む。本発明を用いて形成される表示装置をその表示部 2043 に用いることにより作製される。上記実施の形態で示した支持基板に形成される電界効果トランジスタを用いて表示部 2043 の画素を作製することにより、表示部 2043 の画素を構成する電界効果トランジスタの高性能化を実現し、且つ電界効果トランジスタの微細加工技術に依拠することなく、画素内の電界効果トランジスタ数を増やしても電界効果トランジスタ数の増加に伴い低下した画素の開口率を向上及び画素に占める電界効果トランジスタの面積の削減を図ることのできる表示部 2043 を有する携帯電話を提供することができる。20

#### 【0266】

以上のようにして、本発明を用いて形成された表示装置を用いた電子機器を得ることができる。本発明を用いて形成された表示装置の適用範囲は極めて広く、この表示装置をここに示した以外のあらゆる分野の電子機器に適用することが可能である。

#### 【0267】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

#### 【図面の簡単な説明】

#### 【0268】

【図 1】本発明の表示装置を構成する画素が有する電界効果トランジスタを説明する図。

【図 2】本発明の表示装置を構成する画素が有する電界効果トランジスタを説明する図。

【図 3】本発明の表示装置における電界効果トランジスタの作製方法を説明する図。

【図 4】本発明の表示装置における電界効果トランジスタの作製方法を説明する図。

【図 5】本発明の表示装置における電界効果トランジスタの作製方法を説明する図。

【図 6】本発明の表示装置における電界効果トランジスタの作製方法を説明する図。

【図 7】本発明の表示装置における電界効果トランジスタの作製方法を説明する図。

【図 8】本発明の表示装置における電界効果トランジスタの作製方法を説明する図。

【図 9】本発明の表示装置における電界効果トランジスタの作製方法を説明する図。

【図 10】本発明の表示装置における電界効果トランジスタの作製方法を説明する図。

【図 11】本発明の表示装置における電界効果トランジスタの作製方法を説明する図。

【図 12】本発明の表示装置における電界効果トランジスタの作製方法を説明する図。

【図 13】本発明の表示装置における電界効果トランジスタの作製方法を説明する図。

【図 14】本発明の表示装置における電界効果トランジスタの作製方法を説明する図。

【図 15】本発明の表示装置を構成する画素を説明する図。

【図 16】本発明の表示装置を構成する画素を説明する図。

【図 17】本発明の表示装置を構成する画素を説明する図。

30

40

50

- 【図18】本発明の表示装置を構成する画素を説明する図。

【図19】本発明の表示装置を構成する画素を説明する図。

【図20】本発明の表示装置を具備する電子機器を説明する図。

【図21】本発明の表示装置を構成する画素を説明する図。

【図22】本発明の表示装置を構成する画素を説明する図。

## 【符号の説明】

## 【0269】

|       |          |    |

|-------|----------|----|

| 1 0 1 | 支持基板     |    |

| 1 0 2 | 半導体層     |    |

| 1 0 4 | 絶縁層      | 10 |

| 1 0 7 | マスク      |    |

| 1 0 8 | 半導体基板    |    |

| 1 0 9 | ブロッキング層  |    |

| 1 1 0 | 脆化層      |    |

| 1 1 7 | マスク      |    |

| 1 1 9 | 半導体層     |    |

| 1 2 1 | 保護層      |    |

| 1 5 0 | 脆化層      |    |

| 1 5 1 | 支持基板     |    |

| 1 5 2 | 窒化シリコン膜  | 20 |

| 1 5 3 | マスク      |    |

| 1 5 4 | 保護層      |    |

| 1 5 7 | 絶縁層      |    |

| 1 5 8 | 半導体基板    |    |

| 1 5 9 | ブロッキング層  |    |

| 1 6 2 | 保護層      |    |

| 1 6 3 | 窒化シリコン層  |    |

| 1 6 4 | 半導体層     |    |

| 1 6 5 | 脆化層      |    |

| 1 6 6 | 半導体層     | 30 |

| 1 6 7 | マスク      |    |

| 1 6 8 | 保護層      |    |

| 1 6 9 | 半導体層     |    |

| 2 0 0 | 支持基板     |    |

| 2 0 1 | ブロッキング層  |    |

| 2 0 2 | 絶縁層      |    |

| 2 0 3 | 保護層      |    |

| 2 0 4 | 半導体層     |    |

| 2 0 5 | ゲート絶縁層   |    |

| 2 0 6 | ゲート電極層   | 40 |

| 2 0 7 | 不純物元素    |    |

| 2 0 9 | チャネル形成領域 |    |

| 2 1 0 | 絶縁層      |    |

| 2 1 1 | 平坦化層     |    |

| 2 1 2 | 絶縁層      |    |

| 2 1 3 | 半導体基板    |    |

| 2 1 4 | 脆化層      |    |

| 2 1 5 | 半導体層     |    |

| 2 1 6 | 半導体層     |    |

| 2 1 7 | ゲート絶縁層   | 50 |

|         |            |    |

|---------|------------|----|

| 2 1 8   | ゲート電極層     |    |

| 2 1 9   | 不純物元素      |    |

| 2 2 1   | チャネル形成領域   |    |

| 2 2 2   | 絶縁層        |    |

| 2 2 3   | 平坦化層       |    |

| 2 2 4   | 配線層        |    |

| 2 2 5   | 配線層        |    |

| 2 2 6   | 配線層        |    |

| 2 3 0   | 電界効果トランジスタ | 10 |

| 2 3 1   | 電界効果トランジスタ |    |

| 2 3 3   | 配線層        |    |

| 2 3 4   | 配線層        |    |

| 2 3 5   | 配線層        |    |

| 2 3 6   | 配線層        |    |

| 2 3 7   | 配線層        |    |

| 3 0 1   | 半導体基板      |    |

| 3 0 2   | 脆化層        |    |

| 3 0 3   | 半導体層       |    |

| 3 0 4   | 絶縁膜        |    |

| 3 0 5   | コレット       | 20 |

| 3 0 8   | 半導体層       |    |

| 3 1 0   | 支持基板       |    |

| 3 1 1   | 絶縁膜        |    |

| 3 1 4   | 絶縁膜        |    |

| 3 2 0   | 絶縁膜        |    |

| 3 2 1   | 半導体基板      |    |

| 3 2 2   | 脆化層        |    |

| 3 2 3   | 半導体層       |    |

| 3 2 4   | 絶縁膜        |    |

| 3 2 5   | 保持手段       | 30 |

| 3 2 7   | コレット       |    |

| 3 2 8   | 半導体層       |    |

| 3 3 0   | 支持基板       |    |

| 3 3 1   | 絶縁膜        |    |

| 9 0 1   | 半導体基板      |    |

| 9 0 2   | ステージ       |    |

| 9 0 3   | 支持基板       |    |

| 9 0 4   | ステージ       |    |

| 9 0 5   | コレット       |    |

| 9 0 6   | コレット駆動部    | 40 |

| 9 0 7   | ステージ駆動部    |    |

| 9 0 8   | C P U      |    |

| 9 0 9   | 反転装置       |    |

| 9 1 0   | 反転用コレット    |    |

| 1 5 0 0 | 画素         |    |

| 1 5 0 1 | 選択用トランジスタ  |    |

| 1 5 0 2 | 駆動用トランジスタ  |    |

| 1 5 0 3 | 容量素子       |    |

| 1 5 0 4 | 発光素子       |    |

| 1 5 0 5 | 走査線        | 50 |

|         |            |    |

|---------|------------|----|

| 1 5 0 6 | 信号線        |    |

| 1 5 0 7 | 電源線        |    |

| 1 5 0 8 | 隔壁         |    |

| 1 6 0 1 | 支持基板       |    |

| 1 6 0 2 | プロッキング膜    |    |

| 1 6 0 3 | 絶縁層        |    |

| 1 6 0 4 | 保護層        |    |

| 1 6 0 5 | 絶縁層        |    |

| 1 6 0 6 | 半導体層       |    |

| 1 6 0 7 | 配線層        | 10 |

| 1 6 0 8 | 保護層        |    |

| 1 6 0 9 | 平坦化層       |    |

| 1 6 1 0 | 絶縁層        |    |

| 1 6 1 1 | 配線層        |    |

| 1 6 1 2 | 平坦化層       |    |

| 1 6 1 3 | 平坦化層       |    |

| 1 6 1 4 | 画素電極       |    |

| 1 6 1 5 | 有機導電体膜     |    |

| 1 6 1 6 | 有機導電体膜     |    |

| 1 6 1 7 | 対向基板       | 20 |

| 1 6 1 8 | 半導体層       |    |

| 1 6 1 9 | 絶縁層        |    |

| 1 6 2 0 | 保護層        |    |

| 1 6 2 1 | 配線層        |    |

| 1 6 2 2 | 配線層        |    |

| 1 6 2 3 | 配線層        |    |

| 1 6 2 4 | 配線層        |    |

| 1 7 0 1 | 消去用トランジスタ  |    |

| 1 7 0 2 | 走査線        |    |

| 1 8 0 1 | 配線層        | 30 |

| 2 0 0 1 | 筐体         |    |

| 2 0 0 2 | 支持台        |    |

| 2 0 0 3 | 表示部        |    |

| 2 0 0 4 | スピーカー部     |    |

| 2 0 0 5 | ビデオ入力端子    |    |

| 2 0 1 1 | 本体         |    |

| 2 0 1 2 | 筐体         |    |

| 2 0 1 3 | 表示部        |    |

| 2 0 1 4 | キーボード      |    |

| 2 0 1 5 | 外部接続ポート    | 40 |

| 2 0 1 6 | ポインティングマウス |    |

| 2 0 2 0 | 接眼部        |    |

| 2 0 2 1 | 本体         |    |

| 2 0 2 2 | 表示部        |    |

| 2 0 2 3 | 筐体         |    |

| 2 0 2 4 | 外部接続ポート    |    |

| 2 0 2 5 | リモコン受信部    |    |

| 2 0 2 6 | 受像部        |    |

| 2 0 2 7 | バッテリー      |    |

| 2 0 2 8 | 音声入力部      | 50 |

|         |                    |    |

|---------|--------------------|----|

| 2 0 2 9 | 操作キー               |    |

| 2 0 4 1 | 本体                 |    |

| 2 0 4 2 | 筐体                 |    |

| 2 0 4 3 | 表示部                |    |

| 2 0 4 4 | 音声入力部              |    |

| 2 0 4 5 | 音声出力部              |    |

| 2 0 4 6 | 操作キー               |    |

| 2 0 4 7 | 外部接続ポート            |    |

| 2 0 4 8 | アンテナ               |    |

| 2 0 8 a | 不純物領域              | 10 |

| 2 0 8 b | 不純物領域              |    |

| 2 2 0 a | 不純物領域              |    |

| 2 2 0 b | 不純物領域              |    |

| 4 5 0 1 | 基板                 |    |

| 4 5 0 2 | 陽極                 |    |

| 4 5 0 3 | 正孔注入層              |    |

| 4 5 0 4 | 正孔輸送層              |    |

| 4 5 0 5 | 発光層                |    |

| 4 5 0 6 | 電子輸送層              |    |

| 4 5 0 7 | 電子注入層              | 20 |

| 4 5 0 8 | 陰極                 |    |

| 9 0 1 a | 半導体基板              |    |

| 9 0 1 b | 半導体基板              |    |

| 9 0 1 c | 半導体基板              |    |

| 9 0 2 a | ステージ               |    |

| 9 0 2 b | ステージ               |    |

| 9 0 2 c | ステージ               |    |

| 9 0 7 a | ステージ駆動部            |    |

| 9 0 7 b | ステージ駆動部            |    |

| 2 2 0 1 | 発光素子が発光する領域        | 30 |

| 2 2 0 2 | 矢印                 |    |

| 2 2 0 3 | 電界効果トランジスタが設けられる領域 |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

---

フロントページの続き

|                          |                      |

|--------------------------|----------------------|

| (51)Int.Cl.              | F I                  |

| H 01 L 21/8234 (2006.01) | H 01 L 29/78 6 1 3 A |

| H 01 L 27/06 (2006.01)   | H 01 L 29/78 6 1 9 A |

| H 01 L 27/088 (2006.01)  | H 01 L 27/12 B       |

| H 01 L 21/8238 (2006.01) | H 01 L 27/06 1 0 2 A |

| H 01 L 27/092 (2006.01)  | H 01 L 27/08 1 0 2 A |

| G 02 F 1/1368 (2006.01)  | H 01 L 27/08 1 0 2 B |

| G 09 F 9/30 (2006.01)    | H 01 L 27/08 3 2 1 A |

| H 01 L 27/08 (2006.01)   | H 01 L 27/08 3 2 1 C |

|                          | G 02 F 1/1368        |

|                          | G 09 F 9/30 3 3 8    |

|                          | H 01 L 27/08 3 3 1 E |

(56)参考文献 特表平07-504782(JP,A)

特開2005-328026(JP,A)

特開平07-014982(JP,A)

特開昭63-054763(JP,A)

特開昭60-154549(JP,A)

特開2004-214645(JP,A)

特開2005-109498(JP,A)

特開2003-152185(JP,A)

## (58)調査した分野(Int.Cl., DB名)

|        |               |

|--------|---------------|

| H 01 L | 2 7 / 0 0     |

| G 02 F | 1 / 1 3 6 8   |

| G 09 F | 9 / 3 0       |

| H 01 L | 2 1 / 0 2     |

| H 01 L | 2 1 / 3 3 6   |

| H 01 L | 2 1 / 8 2 3 4 |

| H 01 L | 2 1 / 8 2 3 8 |

| H 01 L | 2 7 / 0 6     |

| H 01 L | 2 7 / 0 8     |

| H 01 L | 2 7 / 0 8 8   |

| H 01 L | 2 7 / 0 9 2   |

| H 01 L | 2 7 / 1 2     |

| H 01 L | 2 9 / 7 8 6   |