(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4509972号

(P4509972)

(45) 発行日 平成22年7月21日(2010.7.21)

(24) 登録日 平成22年5月14日(2010.5.14)

(51) Int.Cl.

H01L 23/12 (2006.01)

F 1

H01L 23/12

B

請求項の数 31 (全 26 頁)

(21) 出願番号 特願2006-161700 (P2006-161700)

(22) 出願日 平成18年6月9日 (2006.6.9)

(65) 公開番号 特開2007-96262 (P2007-96262A)

(43) 公開日 平成19年4月12日 (2007.4.12)

審査請求日 平成21年3月19日 (2009.3.19)

(31) 優先権主張番号 特願2005-254031 (P2005-254031)

(32) 優先日 平成17年9月1日 (2005.9.1)

(33) 優先権主張国 日本国 (JP)

早期審査対象出願

(73) 特許権者 000004547

日本特殊陶業株式会社

愛知県名古屋市瑞穂区高辻町14番18号

(74) 代理人 100114605

弁理士 渥美 久彦

(72) 発明者 山本 洋

名古屋市瑞穂区高辻町14番18号 日本

特殊陶業株式会社 内

(72) 発明者 関 寿毅

名古屋市瑞穂区高辻町14番18号 日本

特殊陶業株式会社 内

(72) 発明者 由利 伸治

名古屋市瑞穂区高辻町14番18号 日本

特殊陶業株式会社 内

最終頁に続く

(54) 【発明の名称】配線基板、埋め込み用セラミックチップ

## (57) 【特許請求の範囲】

## 【請求項 1】

コア主面及びコア裏面を有し、少なくとも前記コア主面にて開口する収容穴部を有する基板コアと、

チップ第1主面及びチップ第2主面を有するセラミック焼結体、前記セラミック焼結体の内部に形成された内部導体、前記チップ第1主面上に突設され前記内部導体に導通するメタライズ層からなる複数の第1端子電極、前記チップ第2主面上に突設され前記内部導体に導通するメタライズ層からなる複数の第2端子電極を有し、前記コア主面と前記チップ第1主面とを同じ側に向けた状態で前記収容穴部内に収容された埋め込み用セラミックチップと、

前記収容穴部の内面と前記埋め込み用セラミックチップの側面との隙間を埋めて前記埋め込み用セラミックチップを固定する充填剤と、

層間絶縁層及び導体層を前記コア主面及び前記チップ第1主面の上にて交互に積層したビルドアップ層と

を備え、

前記複数の第2端子電極を包囲する第2主面側凸部を前記チップ第2主面上に突設し、

前記第2主面側凸部の外縁がチップ縁と重なるように配置され、

前記第2主面側凸部はニッケルを主材料として形成され、前記第2主面側凸部の表面は銅めっき層により全体的に被覆され、前記銅めっき層の表面は粗化されている

ことを特徴とする配線基板。

10

20

## 【請求項 2】

コア主面及びコア裏面を有し、前記コア主面及び前記コア裏面の両方に開口する収容穴部を有する基板コアと、

チップ第1主面及びチップ第2主面を有するセラミック焼結体、前記セラミック焼結体の内部に形成された内部導体、前記チップ第1主面上に突設され前記内部導体に導通する複数の第1端子電極、前記チップ第2主面上に突設され前記内部導体に導通する複数の第2端子電極を有し、前記コア主面と前記チップ第1主面とを同じ側に向けかつ前記コア裏面と前記チップ第2主面とを同じ側に向けた状態で前記収容穴部内に収容された埋め込み用セラミックチップと、

前記収容穴部の内面と前記埋め込み用セラミックチップの側面との隙間を埋めて前記埋め込み用セラミックチップを固定する充填剤と、 10

層間絶縁層及び導体層を前記コア主面及び前記チップ第1主面の上にて交互に積層した第1ビルドアップ層と、

層間絶縁層及び導体層を前記コア裏面及び前記チップ第2主面の上にて交互に積層した構造を有する第2ビルドアップ層と

を備え、

前記複数の第2端子電極を包囲する第2主面側凸部を前記チップ第2主面上に突設し、

前記第2主面側凸部の外縁がチップ縁と重なるように配置され、

前記第2主面側凸部はニッケルを主材料として形成され、前記第2主面側凸部の表面は銅めっき層により全体的に被覆され、前記銅めっき層の表面は粗化されている

ことを特徴とする配線基板。 20

## 【請求項 3】

前記複数の第1端子電極を包囲する第1主面側凸部を前記チップ第1主面上に突設したことの特徴とする請求項1または2に記載の配線基板。

## 【請求項 4】

前記第1主面側凸部は前記複数の第1端子電極と同じまたはそれ以上の高さを有し、前記第2主面側凸部は前記複数の第2端子電極と同じまたはそれ以上の高さを有することを特徴とする請求項1乃至3のいずれか1項に記載の配線基板。

## 【請求項 5】

前記第1主面側凸部は、ニッケルを主材料とする焼結金属層であることを特徴とする請求項1乃至4のいずれか1項に記載の配線基板。 30

## 【請求項 6】

前記埋め込み用セラミックチップは、セラミック誘電体層を介して第1内部電極層と第2内部電極層とが交互に積層配置された構造のセラミックキャパシタであることを特徴とする請求項1乃至5のいずれか1項に記載の配線基板。

## 【請求項 7】

前記チップ第1主面上及び前記チップ第2主面上には段差部が存在するとともに、前記段差部を含む領域に前記第1主面側凸部及び前記第2主面側凸部がそれぞれ配置されていることを特徴とする請求項2乃至6のいずれか1項に記載の配線基板。

## 【請求項 8】

前記第2主面側凸部の幅が、50μm以上であることを特徴とする請求項1乃至7のいずれか1項に記載の配線基板。 40

## 【請求項 9】

前記銅めっき層は、前記複数の第2端子電極及び前記第2主面側凸部の表面に形成されるとともに、表面粗さRaが0.2μm以上であることを特徴とする請求項1乃至8のいずれか1項に記載の配線基板。

## 【請求項 10】

前記銅めっき層は5μm以上に形成されることを特徴とする請求項1乃至9のいずれか1項に記載の配線基板。

## 【請求項 11】

10

20

30

40

50

前記チップ第2主面において前記複数の第2端子電極同士の間、及び、前記複数の第2端子電極と前記第2主面側凸部との間にできる凹部が、前記層間絶縁層で埋められていることを特徴とする請求項1乃至10のいずれか1項に記載の配線基板。

【請求項12】

高分子材料を主体として形成された基板コアの収容穴部内に収容され、前記収容穴部との隙間を充填剤で埋めた状態で使用されるセラミックチップであって、

チップ主面を有する板状のセラミック焼結体と、

前記セラミック焼結体の内部に形成された内部導体と、

前記チップ主面上に突設され前記内部導体に導通するメタライズ層からなる複数の端子電極と、

10

前記複数の端子電極を包囲するようにして前記チップ主面上に突設された凸部とを備え、

前記凸部の外縁がチップ縁と重なるように配置され、

前記凸部はニッケルを主材料として形成され、前記凸部の表面は銅めっき層により全体的に被覆され、前記銅めっき層の表面は粗化されている

ることを特徴とする埋め込み用セラミックチップ。

【請求項13】

前記凸部は前記複数の端子電極と同じまたはそれ以上の高さを有することを特徴とする請求項12に記載の埋め込み用セラミックチップ。

【請求項14】

前記凸部は、ニッケルを主材料とする焼結金属層であることを特徴とする請求項12または13に記載の埋め込み用セラミックチップ。

20

【請求項15】

セラミック誘電体層を介して第1内部電極層と第2内部電極層とが交互に積層配置された構造のセラミックキャパシタであることを特徴とする請求項12乃至14のいずれか1項に記載の埋め込み用セラミックチップ。

【請求項16】

前記チップ主面上には段差部が存在するとともに、前記段差部を含む領域に前記凸部が配置されていることを特徴とする請求項12乃至15のいずれか1項に記載の埋め込み用セラミックチップ。

30

【請求項17】

前記凸部の幅が、 $50 \mu m$ 以上であることを特徴とする請求項12乃至16のいずれか1項に記載の埋め込み用セラミックチップ。

【請求項18】

前記銅めっき層は、前記複数の第2端子電極及び前記第2主面側凸部の表面に形成されるとともに、表面粗さRaが $0.2 \mu m$ 以上であることを特徴とする請求項12乃至17のいずれか1項に記載の埋め込み用セラミックチップ。

【請求項19】

前記銅めっき層は $5 \mu m$ 以上に形成されることを特徴とする請求項12乃至18のいずれか1項に記載の埋め込み用セラミックチップ。

40

【請求項20】

コア主面及びコア裏面を有し、前記コア主面及び前記コア裏面の両方にて開口する収容穴部を有する基板コアと、

チップ第1主面及びチップ第2主面を有するセラミック焼結体、前記セラミック焼結体の内部に形成された内部導体、前記チップ第1主面上に突設され前記内部導体に導通するメタライズ層からなる複数の第1端子電極、前記チップ第2主面上に突設され前記内部導体に導通するメタライズ層からなる複数の第2端子電極を有し、前記コア主面と前記チップ第1主面とを同じ側に向けかつ前記コア裏面と前記チップ第2主面とを同じ側に向けた状態で前記収容穴部内に収容された埋め込み用セラミックチップと、

前記収容穴部の内面と前記埋め込み用チップの側面との隙間を埋めて前記埋め込み用セ

50

ラミックチップを固定する充填剤と、

層間絶縁層及び導体層を前記コア主面及び前記チップ第1主面の上にて交互に積層した構造を有した第1ビルドアップ層と、

層間絶縁層及び導体層を前記コア裏面及び前記チップ第2主面の上にて交互に積層した構造を有する第2ビルドアップ層と

を備え、前記チップ第2主面上の外周縁部に、チップ外周側からの前記充填剤の侵入を防止するダムとして機能する第2主面側ダムメタライズ層が配置され、

前記第2主面側ダムメタライズ層の外縁がチップ縁と重なるように配置され、

前記第2主面側ダムメタライズ層はニッケルを主材料として形成され、前記第2主面側ダムメタライズ層の表面は銅めっき層により全体的に被覆され、前記銅めっき層の表面は粗化されている

ことを特徴とする配線基板。

**【請求項21】**

前記複数の第2端子電極は、グランド第2端子電極と電源第2端子電極とからなり、

前記グランド第2端子電極が前記第2主面側ダムメタライズ層と繋がっておりかつ複数の前記電源第2端子電極を包囲する第2プレーングランド電極とされているか、或いは、前記電源第2端子電極が前記第2主面側ダムメタライズ層と繋がっておりかつ複数の前記グランド第2端子電極を包囲する第2プレーン電源電極とされている

ことを特徴とする請求項20に記載の配線基板。

**【請求項22】**

前記チップ第1主面上の外周縁部に、チップ外周側からの前記充填剤の侵入を防止するダムとして機能する第1主面側ダムメタライズ層が配置されており、

前記複数の第1端子電極は、グランド第1端子電極と電源第1端子電極とからなり、

前記グランド第1端子電極が前記第1主面側ダムメタライズ層と繋がっておりかつ複数の前記電源第1端子電極を包囲する第1プレーングランド電極とされているか、或いは、前記電源第1端子電極が前記第1主面側ダムメタライズ層と繋がっておりかつ複数の前記グランド第1端子電極を包囲する第1プレーン電源電極とされている

ことを特徴とする請求項21に記載の配線基板。

**【請求項23】**

前記銅めっき層は5μm以上に形成されることを特徴とする請求項20乃至22のいずれか1項に記載の配線基板。

**【請求項24】**

前記チップ第1主面上或いは前記チップ第2主面上に切欠部が存在するとともに、前記ダムメタライズ層は少なくとも前記切欠部まで形成されていることを特徴とする請求項20乃至22のいずれか1項に記載の配線基板。

**【請求項25】**

前記ダムメタライズ層は前記切欠部を含む領域に配置されていることを特徴とする請求項24に記載の配線基板。

**【請求項26】**

前記ダムメタライズ層は、外縁がR面とされていることを特徴とする請求項20乃至22のいずれか1項に記載の配線基板。

**【請求項27】**

高分子材料を主体として形成された基板コアの収容穴部内に収容され、前記収容穴部との隙間を充填剤で埋めた状態で使用されるセラミックチップであって、

チップ主面を有する板状のセラミック焼結体と、

前記セラミック焼結体の内部に形成された内部導体と、

前記チップ主面上に突設され前記内部導体に導通するメタライズ層からなる複数の端子電極と

を有し、

前記チップ主面上の外周縁部に、チップ外周側からの前記充填剤の侵入を防止するダム

10

20

30

40

50

として機能するダムメタライズ層が配置されており、

前記複数の端子電極は、グランド端子電極と電源端子電極とからなり、

前記グランド端子電極が前記ダムメタライズ層と繋がっておりかつ複数の前記電源端子電極を包囲するプレーングランド電極とされているか、或いは、前記電源端子電極が前記ダムメタライズ層と繋がっておりかつ複数の前記グランド端子電極を包囲するプレーン電源電極とされ、

前記ダムメタライズ層の外縁がチップ縁と重なるように配置され、

前記ダムメタライズ層はニッケルを主材料として形成され、前記ダムメタライズ層の表面は銅めっき層により全体的に被覆され、前記銅めっき層の表面は粗化されていることを特徴とする埋め込み用セラミックチップ。

10

【請求項 28】

前記銅めっき層は 5  $\mu$ m 以上に形成されることを特徴とする請求項 27 に記載の埋め込み用セラミックチップ。

【請求項 29】

前記チップ主面上に切欠部が存在するとともに、前記ダムメタライズ層は少なくとも前記切欠部まで形成されていることを特徴とする請求項 27 に記載の埋め込み用セラミックチップ。

【請求項 30】

前記ダムメタライズ層は前記切欠部を含む領域に配置されていることを特徴とする請求項 29 に記載の埋め込み用セラミックチップ。

20

【請求項 31】

前記ダムメタライズ層は、外縁が R 面とされていることを特徴とする請求項 27 に記載の埋め込み用セラミックチップ。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、基板コアの収容穴部内に埋め込み用セラミックチップを埋め込み、さらにその表面にビルドアップ層を積層形成した構造の配線基板、埋め込み用セラミックチップに関するものである。

【背景技術】

30

【0002】

コンピュータの C P U などに使用される半導体集積回路素子 ( I C チップ ) は、近年ますます高速化、高機能化しており、これに付随して端子数が増え、端子間ピッチも狭くなる傾向にある。一般的に I C チップの底面には多数の端子が密集してアレイ状に配置されており、このような端子群はマザーボード側の端子群に対してフリップチップの形態で接続される。ただし、 I C チップ側の端子群とマザーボード側の端子群とでは端子間ピッチに大きな差があることから、 I C チップをマザーボード上に直接的に接続することは困難である。そのため、通常は I C チップを I C チップ搭載用配線基板上に搭載し、その I C チップ搭載用配線基板をマザーボード上に搭載するという手法が採用される。この種の I C チップ搭載用配線基板としては、例えば、高分子材料製のコア基板内にセラミックチップを埋め込んでコア部を構成し、そのコア部の表面及び裏面にビルドアップ層を形成したもののが従来提案されている ( 例えば、特許文献 1, 2 参照 ) 。

40

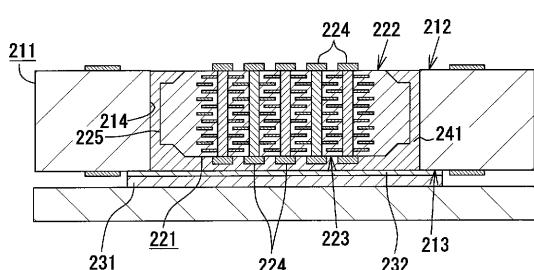

【0003】

上記従来の I C チップ搭載用配線基板の製造方法を、図 18, 図 19 を参照して以下に説明する。まず、コア表面 212 及びコア裏面 213 の両方にて開口する収容穴部 214 を有する高分子材料製の基板コア 211 を準備する。併せて、チップ表面 222 及びチップ裏面 223 にそれぞれ複数の端子電極 224 を突設した埋め込み用セラミックチップ 221 を準備する。次に、コア裏面 213 側に粘着テープ 231 を貼り付けるテーピング工程を行い、収容穴部 214 のコア裏面 213 側の開口をあらかじめシールする。そして、収容穴部 214 内に埋め込み用セラミックチップ 221 を収容する収容工程を行い、チッ

50

チップ裏面 223 を粘着テープ 231 の粘着面 232 に貼り付けて仮固定する。次に、収容穴部 214 の内面と埋め込み用セラミックチップ 221 の側面 225 との隙間を充填剤 241 で埋めた後にそれを硬化させる固定工程を行い、基板コア 211 内にて埋め込み用セラミックチップ 221 を固定する。この後、基板コア 211 及び埋め込み用セラミックチップ 221 からなるコア部の表面及び裏面に対して、高分子材料を主体とする層間絶縁層の形成及び導体層の形成を交互に行うこと、ビルドアップ層を形成する。その結果、所望の IC チップ搭載用配線基板が得られる。

【特許文献 1】特開 2005-39217 号公報

【特許文献 2】特開 2005-39243 号公報

【発明の開示】

10

【発明が解決しようとする課題】

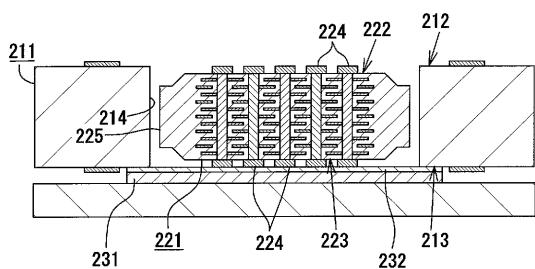

【0004】

ところが、上記の隙間に充填剤 241 を充填すると、埋め込み用セラミックチップ 221 が粘着テープ 231 の粘着面 232 から端子電極 224 の高さ分だけ浮いてしまい、充填剤 241 が埋め込み用セラミックチップ 221 のチップ裏面 223 上に流れ込んでしまう可能性があった（図 19 参照）。特に、端子電極 224 が埋め込み用セラミックチップ 221 の外周部に位置していない場合、外周部の厚みが端子電極 224 がある部分よりも薄くなるため、充填剤 241 の流れ込みが顕著になってしまう。その結果、チップ裏面 223 上の端子電極 224 が充填剤 241 に覆われてしまうため、上記コア部の裏面側のビルドアップ層との導通を図ることが困難となる場合がある。また、導通を図ることができたとしても、高い信頼性を付与できない場合がある。

20

【0005】

本発明は上記の課題に鑑みてなされたものであり、その目的は、ビルドアップ層と埋め込み用セラミックチップとの確実な導通を図ることが可能な配線基板を提供することにある。また、本発明の別の目的は、配線基板に使用するのに好適な埋め込み用セラミックチップを提供することにある。

【課題を解決するための手段】

【0006】

そして上記課題を解決するための手段（手段 1）としては、コア正面及びコア裏面を有し、少なくとも前記コア正面にて開口する収容穴部を有する基板コアと、チップ第 1 主面及びチップ第 2 主面を有するセラミック焼結体、前記セラミック焼結体の内部に形成された内部導体、前記チップ第 1 主面上に突設され前記内部導体に導通するメタライズ層からなる複数の第 1 端子電極、前記チップ第 2 主面上に突設され前記内部導体に導通するメタライズ層からなる複数の第 2 端子電極を有し、前記コア正面と前記チップ第 1 主面とを同じ側に向けた状態で前記収容穴部内に収容された埋め込み用セラミックチップと、前記収容穴部の内面と前記埋め込み用セラミックチップの側面との隙間を埋めて前記埋め込み用セラミックチップを固定する充填剤と、層間絶縁層及び導体層を前記コア正面及び前記チップ第 1 主面の上にて交互に積層したビルドアップ層とを備え、前記複数の第 2 端子電極を包囲する第 2 主面側凸部を前記チップ第 2 主面上に突設し、前記第 2 主面側凸部の外縁がチップ縁と重なるように配置され、前記第 2 主面側凸部はニッケルを主材料として形成され、前記第 2 主面側凸部の表面は銅めっき層により全体的に被覆され、前記銅めっき層の表面は粗化されていることを特徴とする配線基板がある。

30

【0007】

従って、手段 1 の配線基板によると、複数の第 2 端子電極を包囲する第 2 主面側凸部をチップ第 2 主面上に設けた結果、収容穴部の内面と埋め込み用セラミックチップの側面との隙間を充填剤で埋める際に、チップ第 2 主面への充填剤の侵入が第 2 主面側凸部によつて防止される。よって、第 2 端子電極が充填剤に覆われることを防止できるため、埋め込み用セラミックチップとビルドアップ層などとの確実な導通を図ることができる。

40

【0008】

本発明の課題を解決するための別の手段（手段 2）としては、コア正面及びコア裏面を

50

有し、前記コア正面及び前記コア裏面の両方に開口する収容穴部を有する基板コアと、チップ第1正面及びチップ第2正面を有するセラミック焼結体、前記セラミック焼結体の内部に形成された内部導体、前記チップ第1正面に突設され前記内部導体に導通する複数の第1端子電極、前記チップ第2正面に突設され前記内部導体に導通する複数の第2端子電極を有し、前記コア正面と前記チップ第1正面と同じ側に向けかつ前記コア裏面と前記チップ第2正面と同じ側に向けた状態で前記収容穴部内に収容された埋め込み用セラミックチップと、前記収容穴部の内面と前記埋め込み用セラミックチップの側面との隙間を埋めて前記埋め込み用セラミックチップを固定する充填剤と、層間絶縁層及び導体層を前記コア正面及び前記チップ第1正面の上にて交互に積層した第1ビルドアップ層と、層間絶縁層及び導体層を前記コア裏面及び前記チップ第2正面の上にて交互に積層した構造を有する第2ビルドアップ層とを備え、前記複数の第2端子電極を包囲する第2正面側凸部を前記チップ第2正面に突設し、前記第2正面側凸部の外縁がチップ縁と重なるように配置され、前記第2正面側凸部はニッケルを主材料として形成され、前記第2正面側凸部の表面は銅めっき層により全体的に被覆され、前記銅めっき層の表面は粗化されていることを特徴とする配線基板がある。

#### 【0009】

従って、手段2の配線基板によると、複数の第2端子電極を包囲する第2正面側凸部をチップ第2正面に設けた結果、収容穴部の内面と埋め込み用セラミックチップの側面との隙間を充填剤で埋める際に、チップ第2正面への充填剤の侵入が第2正面側凸部によって防止される。よって、第2端子電極が充填剤に覆われることを防止できるため、埋め込み用セラミックチップと第2ビルドアップ層との確実な導通を図ることができる。なお、複数の第1端子電極及び複数の第2端子電極は、例えばメタライズ層からなるものとしてもよい。

#### 【0010】

上記配線基板を構成する基板コアは、配線基板におけるコア部の一部分をなすものであって、コア正面及びその反対側に位置するコア裏面を有する板状に形成される。かかる基板コアは、埋め込み用セラミックチップを収容するための収容穴部を1つまたは2つ以上有している。この収容穴部は、コア正面のみにて開口する非貫通穴であってもよく、あるいはコア正面及びコア裏面の両方に開口する貫通穴であってもよい。なお、埋め込み用セラミックチップは収容穴部内に完全に埋没するようにして収容されていてもよいが、その一部を突出させた状態で収容されていてもよい。

#### 【0011】

基板コアを形成する材料は特に限定されないが、好ましい基板コアは高分子材料を主体として形成される。基板コアを形成するための高分子材料の具体例としては、例えば、E P樹脂（エポキシ樹脂）、P I樹脂（ポリイミド樹脂）、B T樹脂（ビスマレイミド・トリアジン樹脂）、P P E樹脂（ポリフェニレンエーテル樹脂）などがある。そのほか、これらの樹脂とガラス繊維（ガラス繊布やガラス不織布）やポリアミド繊維等の有機繊維との複合材料を使用してもよい。

#### 【0012】

上記配線基板を構成する埋め込み用セラミックチップは、チップ第1正面及びその反対側面に位置するチップ第2正面を有する板状のセラミック焼結体である。埋め込み用セラミックチップは、コア正面とチップ第1正面と同じ側に向けた状態で収容穴部内に収容されている。また、このような収容状態で、埋め込み用セラミックチップは例えば高分子材料製の充填剤により固定される。前記セラミック焼結体としては、アルミナ、窒化アルミニウム、窒化ほう素、炭化珪素、窒化珪素などといった高温焼成セラミックの焼結体が好適に使用されるほか、ホウケイ酸系ガラスやホウケイ酸鉛系ガラスにアルミナ等の無機セラミックフィラーを添加したガラスセラミックのような低温焼成セラミックの焼結体が好適に使用される。この場合、用途に応じて、チタン酸バリウム、チタン酸鉛、チタン酸ストロンチウムなどの誘電体セラミックの焼結体を使用することも好ましい。誘電体セラミックの焼結体を使用した場合、静電容量の大きなセラミックキャパシタを実現しやすく

10

20

30

40

50

なる。

【0013】

セラミック焼結体の内部には内部導体が形成されている。このような内部導体を形成する材料としては特に限定されないが、セラミックと同時に焼結しうる金属、例えば、ニッケル、モリブデン、タンゲステン、チタン等の使用が好適である。なお、低温焼成セラミックの焼結体を選択した場合、内部導体を形成する材料として、さらに銅や銀などの使用が可能となる。内部導体は、セラミック焼結体の厚さ方向に延びるビア導体であってもよく、セラミック焼結体の面方向に延びる内層導体層であってもよい。

【0014】

セラミック焼結体のチップ第1主面上には、内部導体に導通する複数の第1端子電極が突設されている。同様に、セラミック焼結体のチップ第2主面上には、内部導体に導通する複数の第2端子電極が突設されている。複数の第1端子電極及び複数の第2端子電極は例えばメタライズ層からなるものとしてもよい。これら第1端子電極及び第2端子電極は、セラミックと同時に焼結しうるためメタライズに適した金属材料、例えば、ニッケル、モリブデン、タンゲステン、チタン等を用いて形成されている。なお、前記メタライズ層は電源層及び/またはグランド層に導通していてもよい。

10

【0015】

ここで埋め込み用セラミックチップは、セラミック誘電体層を介して第1内部電極層と第2内部電極層とが交互に積層配置された構造のセラミックキャパシタであってもよい。このようにキャパシタとしての機能を付与した埋め込み用セラミックチップを用いた場合、例えば半導体集積回路素子の近傍に配置されることで浮遊インダクタンスを確実に低下させることができるために、半導体集積回路素子を安定的に動作させることが可能となる。ここでいうセラミックキャパシタには、基板（セラミックに限らない基板）上にセラミック材料により薄膜を形成したキャパシタも含まれる。

20

【0016】

上記配線基板を構成するビルトアップ層は、高分子材料を主体とする層間絶縁層及び導体層を交互に接続した構造を有している。ビルトアップ層はコア部の片面にのみ（即ちコア正面及び前記チップ第1正面の上にのみ）形成されていてもよく、コア部の両面に（即ちコア正面及び前記チップ第1正面の上、コア裏面及び前記チップ第2正面の上）形成されていてもよい。なお、コア正面及び前記チップ第1正面の上に形成されたビルトアップ層については、その表面においてセラミックチップに対応した領域に半導体素子搭載部が設定される。このような半導体素子搭載部に半導体素子が搭載可能であるため、基板コアに半導体素子搭載部を設けた場合に比べて半導体素子との熱膨張係数差を小さくすることができる。従って、半導体素子に作用する熱応力の影響を軽減しやすい構造となっている。

30

【0017】

上記配線基板を構成する第2正面側凸部は、チップ第2主面上において複数の第2端子電極を包囲するように突設されている。なお、同様の凸部（第1正面側凸部）は、チップ第1主面上において複数の第1端子電極を包囲するように突設されていてもよい。このように構成すれば、収容穴部の内面と埋め込み用セラミックチップの側面との隙間を充填剤で埋める際に、チップ第1正面への充填剤の侵入が第1正面側凸部によって防止される。よって、第1端子電極が充填剤に覆われることを防止できる。

40

【0018】

第1正面側凸部及び第2正面側凸部を構成する材料としては、高分子材料、金属材料、セラミック材料などが挙げられる。第1正面側凸部及び第2正面側凸部を構成する金属としては、例えば、ニッケル、モリブデン、タンゲステン、チタン、銅、銀などを使用することが可能であり、特にはメタライズ層からなる第1端子電極及び第2端子電極と同種の金属材料を使用することが好適である。即ち、前記第1正面側凸部及び前記第2正面側凸部は、前記チップ第1正面及び前記チップ第2正面の外縁部にそれぞれ配置されたメタライズ層であることが好ましい。このような構成であると、第1端子電極、第2端子電極、

50

第1主面側凸部及び第2主面側凸部を同じ工程で同時に形成する事が可能となるため、工数が減り、低コスト化を達成しやすくなる。なお、前記セラミック焼結体との密着性を考慮した場合には、第1主面側凸部及び第2主面側凸部を構成する材料として、セラミック焼結体と同組成のセラミック材料を用いることが好ましい。

【0019】

第1端子電極及び第2端子電極の厚さは特に限定されないが、例えば10μm以上100μm程度に設定されることがよい。即ち、この厚さが10μm未満であると、層間絶縁層と埋め込み用セラミックチップとの密着強度を向上させることができない可能性がある。また、この厚さが100μmを超えるような場合には、ビルドアップ層表面の平坦性が低くなる可能性がある。

10

【0020】

なお、前記第1主面側凸部は前記複数の第1端子電極と同じまたはそれ以上の高さを有し、前記第2主面側凸部は前記複数の第2端子電極と同じまたはそれ以上の高さを有することが好ましい。このように構成すれば、チップ第1主面やチップ第2主面への充填剤の侵入をより確実に防止できる。なお、第1主面側凸部及び第2主面側凸部が第1端子電極及び第2端子電極と同種の金属材料からなる場合、第1端子電極と第1主面側凸部、及び、第2端子電極と第2主面側凸部は、互いに繋がっていてもよい。

【0021】

また、前記チップ第1主面上及び前記チップ第2主面上に段差部が存在するような場合、前記段差部を含む領域に前記第1主面側凸部及び前記第2主面側凸部がそれぞれ配置されていることが好ましい。チップ第1主面上及びチップ第2主面上に段差部が存在していると、本発明の解決すべき課題の1つである「チップ第1主面やチップ第2主面への充填剤の侵入」といった問題が生じやすいからである。

20

【0022】

複数の第2端子電極及び第2主面側凸部の表面は、セラミック焼結体のチップ第2主面よりも粗くなっていることがよい。また、複数の第1端子電極及び第1主面側凸部の表面は、セラミック焼結体のチップ第1主面よりも粗くなっていてもよい。即ち、本発明の構成を採用した場合、層間絶縁層との接合界面においてセラミックチップ側が有する粗面の割合が大きくなることで、層間絶縁層との密着強度を従来に比べて向上できるからである。

30

【0023】

具体的には下記の構成にすることが好適である。即ち、前記複数の第2端子電極及び前記第2主面側凸部の表面に、前記複数の第2端子電極を構成する金属よりも柔らかい金属からなる金属層を形成する。その理由は次のとおりである。即ち、メタライズ層からなる複数の第2端子電極は、焼結金属層であって比較的硬質であることから、エッチャント等を使用してその表面を直接粗化することが極めて困難である。従って、柔らかい金属からなる層を形成しその層を表面粗化するようにすれば、所望の粗面を比較的簡単にかつ確実に得ることができるからである。ここで金属層の表面粗さRaは0.2μm以上であることがよく、特には0.2μm以上1.0μm以下であることがよい。金属層の表面粗さRaがこの程度以上でないと、その表面がセラミック焼結体のチップ主面の粗さとあまり変わらなくなり、複数の第2端子電極の占有面積をチップ主面の面積の半分以上に設定したとしても、密着強度を十分に向上できないおそれがあるからである。

40

【0024】

この場合、金属層は複数の第2端子電極の種類に応じて適宜選択されるが、例えば、複数の第2端子電極がニッケルからなる場合には、金属層として銅層（特には銅めっき層）を選択することが好適である。このような組み合わせにすると、ニッケルを直接表面粗化するよりも簡単にかつ確実に粗面を形成できるからである。この場合の銅めっき層は、粗化処理による除去分を考慮して安全のために厚さ5μm以上に形成されることが好ましい。なお、軟質の金属層を形成する手法としては、上記のようなめっき法が、簡単かつ低コストという理由で好適である。しかし、めっき法以外にも、例えば、スパッタリング、C

50

VD、真空蒸着などといった手法を採用することも可能である。

【0025】

そして同様の理由により、前記複数の第1端子電極及び前記第1主面側凸部の表面に、前記複数の第1端子電極を構成する金属よりも柔らかい金属からなる金属層を形成し、その金属層の表面粗さRaを0.2μm以上とすることが好適である。

【0026】

前記第1主面側凸部の幅及び前記第2主面側凸部の幅は特に限定されないが、それぞれ50μm以上であることが好ましい。凸部の幅が50μm未満になると、充填剤の侵入を確実に防止するダムとしての機能を十分に果たさなくなる可能性があるからである。

【0027】

前記埋め込み用セラミックチップのチップ縁から前記第2主面側凸部までの距離は特に限定されないが、200μm以下であることが好ましい。この距離が200μmを超えるような第2主面側凸部を形成しようとすると、その第2主面側凸部の幅を狭くする必要性が生じ、結果として第2主面側凸部の表面積が減少し、接合界面における粗面の割合が小さくなってしまう。これに対し前記距離が200μm以下であれば、第2主面側凸部の幅をある程度広く確保でき、接合界面における粗面の割合が大きくなる。よって、セラミックチップと層間絶縁層との密着強度の向上に寄与できる。なお、前記埋め込み用セラミックチップのチップ縁から前記第1主面側凸部までの距離についても、同様の理由から200μm以下であることが好ましい。前記距離は小さければ小さいほどよいため、第2主面側凸部あるいは第1主面側凸部はチップ縁に重なるようにして形成されていてもよい。

10

【0028】

前記チップ第2主面において前記複数の第2端子電極同士の間、及び、前記複数の第2端子電極と前記第2主面側凸部との間にできる凹部が、前記層間絶縁層で埋められていることが好ましい。この構成によると、セラミックチップと層間絶縁層との接触面積が増えるため、セラミックチップと層間絶縁層との密着強度が向上しうるからである。なお、前記チップ第1主面において前記複数の第1端子電極同士の間、及び、前記複数の第1端子電極と前記第1主面側凸部との間にできる凹部についても、同様の理由により、前記層間絶縁層で埋められていることが好ましい。

20

【0029】

また、本発明の課題を解決するための別の手段（手段3）としては、高分子材料を主体として形成された基板コアの収容穴部内に収容され、前記収容穴部との隙間を充填剤で埋めた状態で使用されるセラミックチップであって、チップ主面を有する板状のセラミック焼結体と、前記セラミック焼結体の内部に形成された内部導体と、前記チップ主面上に突設され前記内部導体に導通するメタライズ層からなる複数の端子電極と、前記複数の端子電極を包囲するようにして前記チップ主面上に突設された凸部とを備え、前記凸部の外縁がチップ縁と重なるように配置され、前記凸部はニッケルを主材料として形成され、前記凸部の表面は銅めっき層により全体的に被覆され、前記銅めっき層の表面は粗化されていることを特徴とする埋め込み用セラミックチップがある。

30

【0030】

従って、手段3の埋め込み用セラミックチップによると、複数の端子電極を包囲する凸部をチップ主面上に設けた結果、収容穴部との隙間を充填剤で埋める際に、チップ主面への充填剤の侵入が凸部によって防止される。よって、端子電極が充填剤に覆われることを防止できるため、埋め込み用セラミックチップと他層との確実な導通を図ることができる。チップ主面が、チップ第1主面及びチップ第2主面の反対側に位置するチップ第2主面の2つである場合、前記凸部をチップ第1主面及びチップ第2主面の両方に設けてよい。

40

【0031】

上記手段3のセラミックチップにおいては、前記複数の端子電極を包囲する凸部を前記チップ主面上に突設してもよい。また、前記凸部は前記複数の端子電極と同じまたはそれ以上の高さを有していてもよい。前記凸部は前記チップ主面の外縁部に配置されたメタラ

50

イズ層であってもよい。特に複数の端子電極がメタライズ層からなる場合、凸部もメタライズ層からなるものとすれば、これらを1つの工程で形成でき、工数増を回避することができる。また、このような工程で両者を形成することにより、容易に凸部と複数の端子電極とを同じ高さにすることができる。上記手段3のセラミックチップは、セラミック誘電体層を介して第1内部電極層と第2内部電極層とが交互に積層配置された構造のセラミックキャパシタであってもよい。また、前記チップ主面上に段差部が存在するような場合、前記段差部を含む領域に前記凸部が配置されていてもよい。前記凸部の幅が50μm以上であってもよく、チップ縁から前記凸部までの距離が200μm以下であってもよい。前記複数の第2端子電極及び前記第2主面側凸部の表面には、前記複数の端子電極を構成する金属よりも柔らかい金属からなる金属層が形成されるとともに、その金属層の表面粗さRaが0.2μm以上であってもよい。

10

【発明を実施するための最良の形態】

【0032】

【第1実施形態】

【0033】

以下、本発明の配線基板を具体化した第1実施形態を図面に基づき詳細に説明する。

【0034】

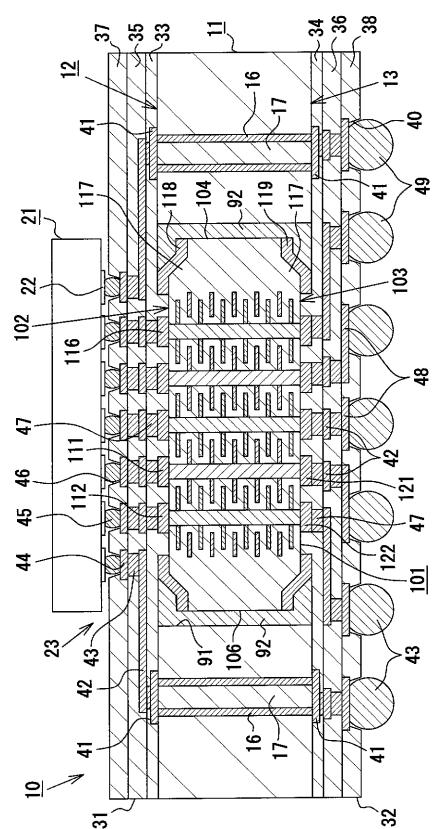

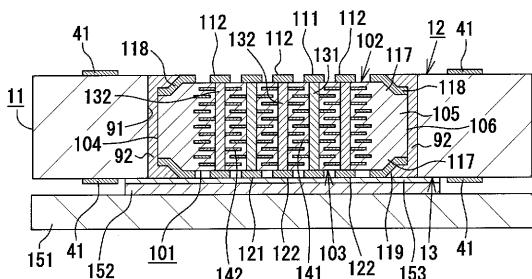

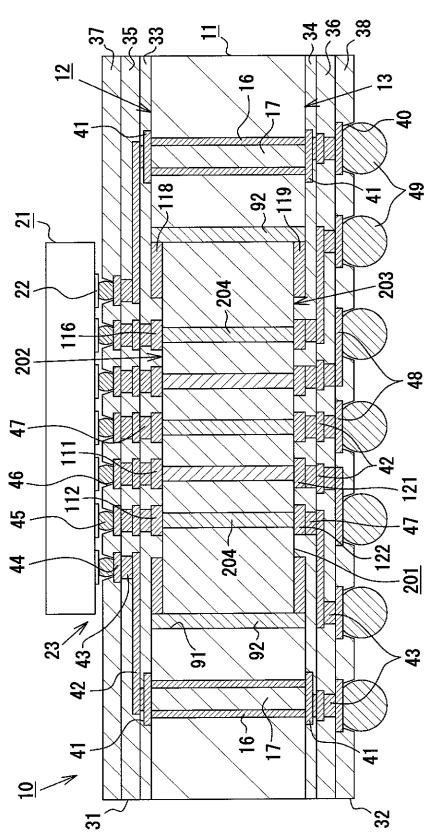

図1に示されるように、本実施形態の配線基板10は、ICチップ搭載用の配線基板であって、ガラスエポキシからなる略矩形板状の基板コア11と、基板コア11の上面12(コア正面)上に形成される第1ビルドアップ層31(ビルドアップ層)と、基板コア11の下面13(コア裏面)上に形成される第2ビルドアップ層32とからなる。基板コア11における複数箇所にはスルーホール導体16が形成されている。かかるスルーホール導体16は、基板コア11の上面12側と下面13側とを接続導通している。なお、スルーホール導体16の内部は、例えばエポキシ樹脂などの閉塞体17で埋められている。また、基板コア11の上面12及び下面13には、銅からなる導体層41がパターン形成されており、各導体層41は、スルーホール導体16に電気的に接続されている。

20

【0035】

基板コア11の上面12上に形成された第1ビルドアップ層31は、エポキシ樹脂からなる2層の樹脂絶縁層33,35(いわゆる層間絶縁層)と、銅からなる導体層42とを交互に積層した構造を有している。第2層の樹脂絶縁層35の表面上における複数箇所には、端子パッド44がアレイ状に形成されている。また、樹脂絶縁層35の表面は、ソルダーレジスト37によってほぼ全体的に覆われている。ソルダーレジスト37の所定箇所には、端子パッド44を露出させる開口部46が形成されている。端子パッド44の表面上には、複数のはんだバンプ45が配設されている。各はんだバンプ45は、ICチップ21(半導体集積回路素子)の面接続端子22に電気的に接続されている。なお、各端子パッド44及び各はんだバンプ45は、第1ビルドアップ層31においてセラミックキャパシタ101の真上の領域内に位置しており、この領域が半導体素子搭載部23となる。また、樹脂絶縁層33,35内には、それぞれビア導体43,47が設けられている。これらのビア導体43,47のほとんどは同軸上に配置されるとともに、それらを介して導体層41,42及び端子パッド44が相互に電気的に接続されている。

30

【0036】

図1に示されるように、基板コア11の下面13上に形成された第2ビルドアップ層32は、上述した第1ビルドアップ層31とほぼ同じ構造を有している。即ち、第2ビルドアップ層32は、エポキシ樹脂からなる2層の樹脂絶縁層34,36(いわゆる層間絶縁層)と、導体層42とを交互に積層した構造を有している。第2層の樹脂絶縁層36の下面における複数箇所には、ビア導体43を介して導体層42に電気的に接続されるBGA用パッド48が格子状に形成されている。また、樹脂絶縁層36の下面は、ソルダーレジスト38によってほぼ全体的に覆われている。ソルダーレジスト38の所定箇所には、BGA用パッド48を露出させる開口部40が形成されている。BGA用パッド48の表面上には、図示しないマザーボードとの電気的な接続を図るための複数のはんだバンプ

40

50

4 9 が配設されている。そして、各はんだバンプ 4 9 により、図 1 に示される配線基板 1 0 は図示しないマザーボード上に実装される。

【 0 0 3 7 】

前記基板コア 1 1 は、上面 1 2 の中央部及び下面 1 3 の中央部にて開口する平面視で矩形形状の収容穴部 9 1 を有している。即ち、収容穴部 9 1 は貫通穴部である。収容穴部 9 1 内には、図 2 , 図 3 等に示すセラミックキャパシタ 1 0 1 (埋め込み用セラミックチップ) が、埋め込んだ状態で収容されている。なお、セラミックキャパシタ 1 0 1 は、上面 1 0 2 (チップ第 1 主面) を基板コア 1 1 の上面 1 2 と同じ側に向けた状態で収容されている。本実施形態のセラミックキャパシタ 1 0 1 は、縦 1 2 . 0 mm × 横 1 2 . 0 mm × 厚さ 0 . 8 mm の矩形平板状である。なお、セラミックキャパシタ 1 0 1 の厚さは、0 . 2 mm 以上 1 . 0 mm 以下であることが好ましい。仮に、0 . 2 mm 未満であると、半導体素子搭載部 2 3 上の I C チップ 2 1 をセラミックキャパシタ 1 0 1 によって確実に支持できなくなる。一方、1 . 0 mm よりも大きいと、配線基板 1 0 が肉厚になってしまふ。また、収容穴部 9 1 の内面とセラミックキャパシタ 1 0 1 の側面 1 0 6 との隙間は、高分子材料 (本実施形態では熱硬化性樹脂) からなる充填剤 9 2 によって埋められている。この充填剤 9 2 は、セラミックキャパシタ 1 0 1 を基板コア 1 1 に固定するとともに、セラミックキャパシタ 1 0 1 及び基板コア 1 1 の面方向や厚さ方向への変形を自身の弾性変形により吸収する機能を有している。なお、セラミックキャパシタ 1 0 1 は、平面視略正方形状をなしており、四隅に C 0 . 6 0 以上のテーパ (または、半径 0 . 6 0 mm 以上のアーチル) を有している。これにより、温度変化に伴う充填剤 9 2 の変形時において、セラミックキャパシタ 1 0 1 の角部への応力集中を緩和できるため、充填剤 9 2 のクラックの発生を防止できる。

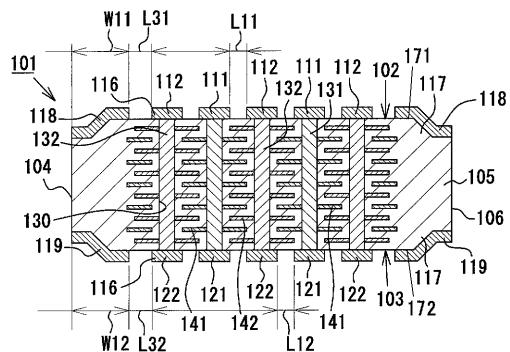

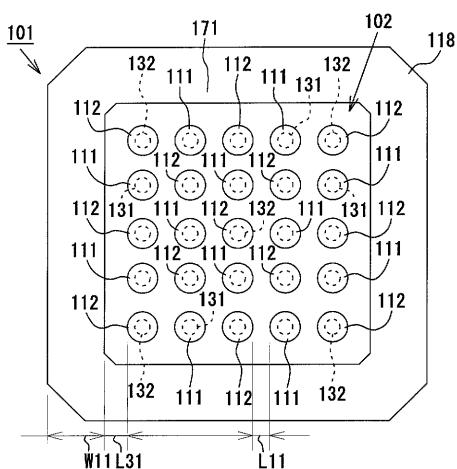

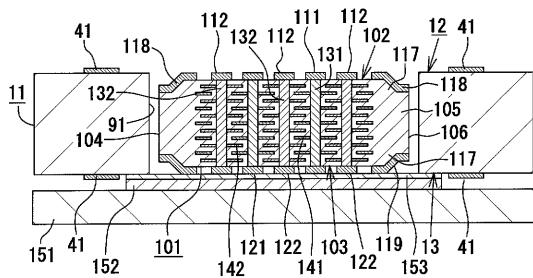

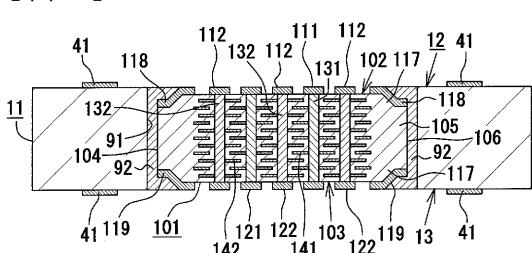

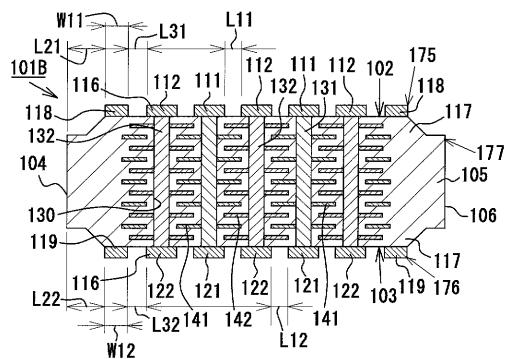

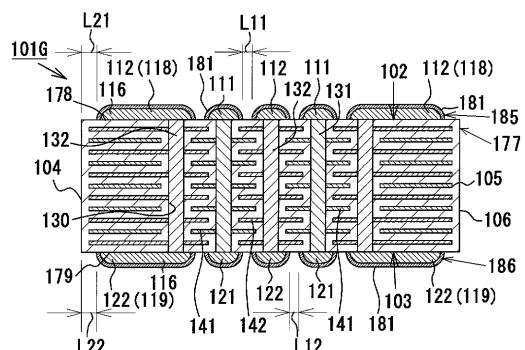

【 0 0 3 8 】

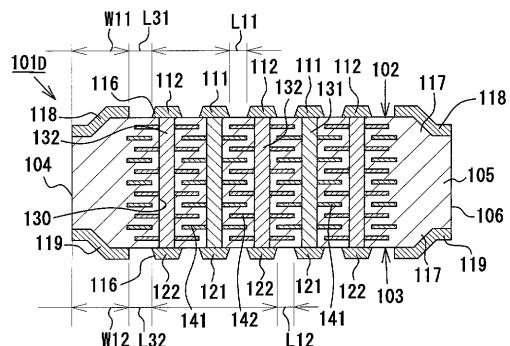

図 1 ~ 図 3 に示されるように、本実施形態のセラミックキャパシタ 1 0 1 は、いわゆるビアアレイタイプのセラミックキャパシタである。セラミックキャパシタ 1 0 1 を構成するセラミック焼結体 1 0 4 は、上面 1 0 2 及び下面 1 0 3 (チップ第 2 主面) を有する板状物である。なお、セラミック焼結体 1 0 4 の上面 1 0 2 上には、前記第 1 ビルドアップ層 3 1 を構成する前記樹脂絶縁層 3 3 が形成され、セラミック焼結体 1 0 4 の下面 1 0 3 には、前記第 2 ビルドアップ層 3 2 を構成する前記樹脂絶縁層 3 4 が形成されている。セラミック焼結体 1 0 4 は、セラミック誘電体層 1 0 5 を介して第 1 内部電極層 1 4 1 (内部導体) と第 2 内部電極層 1 4 2 (内部導体) とを交互に積層配置した構造を有している。セラミック誘電体層 1 0 5 は、高誘電率セラミックの一種であるチタン酸バリウムの焼結体からなり、第 1 内部電極層 1 4 1 及び第 2 内部電極層 1 4 2 間の誘電体 (絶縁体) として機能する。第 1 内部電極層 1 4 1 及び第 2 内部電極層 1 4 2 は、いずれもニッケルを主成分として形成された層であって、セラミック焼結体 1 0 4 の内部において一層おきに配置されている。

【 0 0 3 9 】

図 2 , 図 3 に示されるように、セラミック焼結体 1 0 4 には多数のビアホール 1 3 0 が形成されている。これらのビアホール 1 3 0 は、セラミック焼結体 1 0 4 をその厚さ方向に貫通するとともに、全面にわたって格子状 (アレイ状) に配置されている。各ビアホール 1 3 0 内には、セラミック焼結体 1 0 4 の上面 1 0 2 及び下面 1 0 3 間を貫通する複数のビア導体 1 3 1 , 1 3 2 (内部導体) が、ニッケルを主材料として形成されている。各第 1 ビア導体 1 3 1 は、各第 1 内部電極層 1 4 1 を貫通しており、それら同士を互いに電気的に接続している。各第 2 ビア導体 1 3 2 は、各第 2 内部電極層 1 4 2 を貫通しており、それら同士を互いに電気的に接続している。

【 0 0 4 0 】

そして図 2 , 図 3 に示されるように、セラミック焼結体 1 0 4 の上面 1 0 2 上には、複数の第 1 外部端子電極 1 1 1 , 1 1 2 (第 1 端子電極) が突設されている。これら第 1 外部端子電極 1 1 1 , 1 1 2 は、上面 1 0 2 全体にわたって格子状 (アレイ状) に配置されている。一方、セラミック焼結体 1 0 4 の下面 1 0 3 上には、複数の第 2 外部端子電極 1

21, 122 (第2端子電極)が突設されている。これら第2外部端子電極121, 122は、下面103全体にわたって格子状(アレイ状)に配置されている。上面102側にある第1外部端子電極111, 112は、前記ビア導体47に対して電気的に接続される。一方、下面103側にある第2外部端子電極121, 122は、図示しないマザーボードが有する電極(接触子)に対して、ビア導体47、導体層42、ビア導体43、BGA用パッド48及びはんだバンプ49を介して電気的に接続される。また、第1外部端子電極111, 112の底面略中央部は、ビア導体131, 132の上面102側の端面に対して直接接続されており、第2外部端子電極121, 122の底面略中央部は、ビア導体131, 132の下面103側の端面に対して直接接続されている。よって、外部端子電極111, 121はビア導体131及び第1内部電極層141に導通しており、外部端子電極112, 122はビア導体132及び第2内部電極層142に導通している。10

#### 【0041】

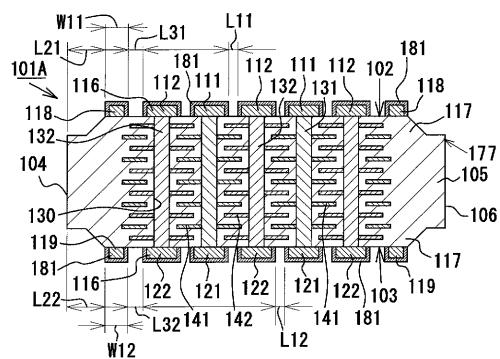

図2に示されるように、本実施形態の第1外部端子電極111, 112は、ニッケルを主材料として形成されたメタライズ層116からなっている。同様に、第2外部端子電極121, 122も、メタライズ層116からなっている。特に図8に示す変形例のセラミックキャパシタ101Aのように、第1外部端子電極111, 112及び第2外部端子電極121, 122におけるメタライズ層116の表面が、銅めっき層181によって全体的に被覆されていてもよい。即ち、銅めっき層181は、メタライズ層116を構成する金属よりも軟かい金属からなっている。なお、図8のものにおいては、銅めっき層181の表面は粗化されているため、第1外部端子電極111, 112の表面は、セラミック焼結体104の上面102よりも粗くなっている。同様に、第2外部端子電極121, 122の表面も、セラミック焼結体104の下面103よりも粗くなっている。なお、本実施形態の変形例における銅めっき層181の表面粗さRaは、約0.5μmに設定されている。また、外部端子電極111, 112, 121, 122のメタライズ層116の厚さは、約20μmに設定されている。図3に示されるように、上面102に垂直な方向(部品厚さ方向)から見たときの外部端子電極111, 112, 121, 122は略円形状をなしている。なお本実施形態では、外部端子電極111, 112, 121, 122の直径が約500μmに設定され、ピッチの最小長さが約580μmに設定されている。20

#### 【0042】

また、図2に示されるように、セラミック焼結体104の上面102上には、ダムメタライズ層118(第1正面側凸部)が突設されている。ダムメタライズ層118は、上面102の外周縁部171において複数の第1外部端子電極111, 112を包囲するように配置されている。また、ダムメタライズ層118は、上面102上の外周部分に存在する段差部(切欠部)117を含む領域に配置されている。同様に、セラミック焼結体104の下面103上には、ダムメタライズ層119(第2正面側凸部)が突設されている。ダムメタライズ層119は、下面103の外周縁部172において複数の第2外部端子電極121, 122を包囲するように配置されている。また、ダムメタライズ層119は、下面103上の外周部分に存在する段差部117を含む領域に配置されている。ダムメタライズ層118, 119は、ニッケルを主材料として形成される。図8に示す変形例のように、ダムメタライズ層118, 119の表面が銅めっき層181によって全体的に被覆されていてもよい。即ち、ダムメタライズ層118, 119及び銅めっき層181は、外部端子電極111, 112, 121, 122とほぼ同じ層構造を有している。また、銅めっき層181は、ダムメタライズ層118, 119を構成する金属よりも軟かい金属からなっている。なお、ダムメタライズ層118, 119は、他の導体部分には何ら導通していない。さらに、銅めっき層181の表面は粗化されているため、ダムメタライズ層118, 119の表面は、セラミック焼結体104の上面102及び下面103よりも粗くなっている。また、ダムメタライズ層118, 119は、外部端子電極111, 112, 121, 122のメタライズ層116と同じ厚さ(高さ)を有しており、約20μmに設定されている。図3に示されるように、上面102に垂直な方向(部品厚さ方向)から見たときのダムメタライズ層118, 119(銅めっき層181)の外形形状は略矩形状である。304050

り、略矩形状の開口部を有した形状をなしている。

【0043】

また、図2、図3に示す本実施形態のセラミックキャパシタ101において、ダムメタライズ層118、119の幅W11、W12は、それぞれ50μm以上（具体的には500μm～1000μm程度）に設定されている。セラミックキャパシタ101のチップ縁からダムメタライズ層118、119までの距離はそれぞれ0μmに設定されている。つまり、ダムメタライズ層118、119の外縁はチップ縁と重なっており、それゆえダムメタライズ層118、119が幅広になっている。また、複数の第1端子電極111、112同士の間の距離L11、複数の第2端子電極121、122同士の間の距離L12は、それぞれ200μm以下（具体的には150μm～200μm程度）に設定されている。複数の第1端子電極111、112とダムメタライズ層118との間の距離L31、複数の第2端子電極121、122とダムメタライズ層119との間の距離L32は、それぞれ200μm以下（具体的には150μm～200μm程度）に設定されている。

10

【0044】

マザーボード側から第2外部端子電極121、122を介して通電を行い、第1内部電極層141-第2内部電極層142間に電圧を加えると、第1内部電極層141に例えばプラスの電荷が蓄積し、第2内部電極層142に例えばマイナスの電荷が蓄積する。その結果、セラミックキャパシタ101がキャパシタとして機能する。また、このセラミックキャパシタ101では、第1ビア導体131及び第2ビア導体132がそれぞれ交互に隣接して配置され、かつ、第1ビア導体131及び第2ビア導体132を流れる電流の方向が互いに逆向きになるように設定されている。これにより、インダクタンス成分の低減化が図られている。

20

【0045】

次に、本実施形態の配線基板10の製造方法について述べる。

【0046】

準備工程では、基板コア11とセラミックキャパシタ101とを、それぞれ従来周知の手法により作製し、あらかじめ準備しておく。

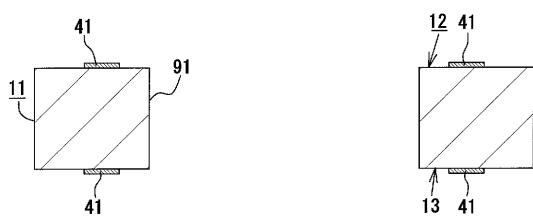

【0047】

基板コア11は以下のように作製される。まず、縦400mm×横400mm×厚み0.8mmの基材の両面に銅箔が貼付された銅張積層板を準備する。なお、基材の厚みは、0.2mm以上1.0mm以下であることが好ましい。次に、銅張積層板に対してドリル機を用いて孔あけ加工を行い、スルーホール導体16を形成するための貫通孔（図示略）を所定位置にあらかじめ形成しておく。また、銅張積層板に対してルータを用いて孔あけ加工を行い、収容穴部91となる貫通孔を所定位置にあらかじめ形成しておく（図4参照）。なお、収容穴部91となる貫通孔は、一边が14.0mmで、四隅に半径0.1～2mmのアールを有する断面略正方形形状の孔である。そして、従来公知の手法に従って無電解銅めっき及び電解銅めっきを行うことでスルーホール導体16を形成する。さらに、銅張積層板の両面の銅箔のエッティングを行って導体層41を例えばサブトラクティブ法によってパターニングする。具体的には、無電解銅めっきの後、この無電解銅めっき層を共通電極として電解銅めっきを施す。さらにドライフィルムをラミネートし、同ドライフィルムに対して露光及び現像を行うことにより、ドライフィルムを所定パターンに形成する。この状態で、不要な電解銅めっき層、無電解銅めっき層及び銅箔をエッティングで除去する。その後、ドライフィルムを剥離することにより基板コア11を得る。

30

40

【0048】

また、図2に示すセラミックキャパシタ101は以下のように作製される。即ち、セラミックのグリーンシートを形成し、このグリーンシートに内部電極層用ニッケルペーストをスクリーン印刷して乾燥させる。これにより、後に第1内部電極層141となる第1内部電極部と、第2内部電極層142となる第2内部電極部とが形成される。次に、第1内部電極部が形成されたグリーンシートと第2内部電極部が形成されたグリーンシートとを交互に積層し、シート積層方向に押圧力を付与することにより、各グリーンシートを一体

50

化してグリーンシート積層体を形成する。

【0049】

さらに、レーザー加工機を用いてグリーンシート積層体にビアホール130を多数個貫通形成し、図示しないペースト圧入充填装置を用いて、ビア導体用ニッケルペーストを各ビアホール130内に充填する。次に、グリーンシート積層体の上面にペーストを印刷し、グリーンシート積層体の上面側にて各導体部の上端面を覆うように第1外部端子電極111, 112のメタライズ層116を形成し、上面の他の領域にダムメタライズ層118を形成する(メタライズ工程)。また、グリーンシート積層体の下面にペーストを印刷し、グリーンシート積層体の下面側にて各導体部の下端面を覆うように第2外部端子電極121, 122のメタライズ層116を形成し、下面の他の領域にダムメタライズ層119を形成する(メタライズ工程)。10

【0050】

この後、グリーンシート積層体の乾燥を行い、表面端子部をある程度固化させる。次に、グリーンシート積層体を脱脂し、さらに所定温度で所定時間焼成を行う。その結果、チタン酸バリウム及びペースト中のニッケルが同時焼結し、セラミック焼結体104となる結果、図2, 図3に示したセラミックキャパシタ101が得られる。

【0051】

図8に示す変形例のセラミックキャパシタ101Aを得たい場合には、さらに下記の工程を実施する。即ち、得られたセラミック焼結体104が有する各外部端子電極111, 112, 121, 122及び各ダムメタライズ層118, 119に対して無電解銅めっき(厚さ10μm程度)を行う。その結果、各外部端子電極111, 112, 121, 122及び各ダムメタライズ層118, 119の上に銅めっき層181が形成され、図8のようなセラミックキャパシタ101Aが完成する。なお、無電解銅めっきはやや厚めの10μm程度であるため、後の粗化工程を経た後でも銅の厚みを確保できる。なお、無電解銅めっきに代えて電解銅めっきを行ってもよい。20

【0052】

続くテーピング工程では、収容穴部91の下面13側開口を、剥離可能な粘着テープ152でシールする。この粘着テープ152は、支持台151によって支持されている。かかる粘着テープ152の粘着面153には、セラミックキャパシタ101が貼り付けられて仮固定されている。さらに収容工程では、マウント装置(ヤマハ発動機株式会社製)を用いて、収容穴部91内にセラミックキャパシタ101を収容する(図5参照)。このとき、粘着テープ152の粘着面153に第2外部端子電極121, 122及びダムメタライズ層119が貼り付けられる。30

【0053】

そして、固定工程を実施し、収容穴部91の内面とセラミックキャパシタ101の側面106との隙間に、ディスペンサ装置(Asymtek社製)を用いて、熱硬化性樹脂製の充填剤92(株式会社ナミックス製 アンダフィル材)を充填する(図6参照)。その後、加熱処理を行うと、充填剤92が硬化して、セラミックキャパシタ101が収容穴部91内に固定される。そして、この時点で、粘着テープ152を剥離する(図7参照)。40

【0054】

ここで図8に示す変形例のセラミックキャパシタ101Aにおいては、粗化工程を実施する。粗化工程では、外部端子電極111, 112, 121, 122及びダムメタライズ層118, 119の上にある銅めっき層181の表面の粗化(CZ処理)を行う。このように、メタライズ層116, 118, 119よりも軟かい銅めっき層181を表面粗化すれば、所望の粗面を比較的簡単にかつ確実に得ることができる。同時に、基板コア11の上面12及び下面13に形成された導体層41の表面の粗化も行う。そして、粗化工程が終了したら、洗浄工程を実施する。また、必要に応じて、シランカップリング剤(信越化学工業株式会社製)を用いて、基板コア11の上面12及び下面13に対してカップリング処理を行ってもよい。

【0055】

10

20

30

40

50

洗浄工程の終了後、ビルドアップ層形成工程を実施する。ビルドアップ層形成工程では、従来周知の手法に基づいて上面 102 及び上面 102 の上に第 1 ビルドアップ層 31 を形成するとともに、下面 103 及び下面 103 の上に第 2 ビルドアップ層 32 を形成する。その結果、基板コア 11 及びビルドアップ層 31, 32 からなる配線基板 10 が完成する。

#### 【0056】

従って、本実施形態によれば以下の効果を得ることができる。

#### 【0057】

(1) 本実施形態の配線基板 10 によれば、ダムメタライズ層 118 を上面 102 上に設けたことにより、収容穴部 91 の内面とセラミックキャパシタ 101 の側面 106 との隙間を充填剤 92 で埋める際に、上面 102 への充填剤 92 の侵入がダムメタライズ層 118 によって防止される。同様に、ダムメタライズ層 119 を下面 103 上に設けたことにより、上記の隙間を充填剤 92 で埋める際に、下面 103 への充填剤 92 の侵入がダムメタライズ層 119 によって防止される。即ち、ダムメタライズ層 118, 119 は、充填剤 92 を堰き止めるためのいわゆる「ダム」となる。従って、外部端子電極 111, 112, 121, 122 が充填剤 92 に覆われることを防止できるため、第 1 ビルドアップ層 31 - セラミックキャパシタ 101 - 第 2 ビルドアップ層 32 間での確実な導通を図ることができる。

#### 【0058】

(2) 図 8 に示した本実施形態の変形例のセラミックキャパシタ 101A では、上面 102 上に第 1 外部端子電極 111, 112 に加えてダムメタライズ層 118 が設けられ、下面 103 上に第 2 外部端子電極 121, 122 に加えてダムメタライズ層 119 が設けられている。しかも、これらの表面には粗化された銅めっき層 181 が形成されている。このため、第 1 ビルドアップ層 31 を構成する樹脂絶縁層 33 との接合界面における粗化金属部分の割合が大きくなり、樹脂絶縁層 33 との密着強度が向上する。また、第 2 ビルドアップ層 32 を構成する樹脂絶縁層 34 との接合界面における粗化金属部分の割合が大きくなり、樹脂絶縁層 34 との密着強度が向上する。また、上面 102 における凹凸もある程度解消されるため、ビルドアップ層 31, 32 表面の平坦性がよくなり、IC チップ 21 を搭載しやすくなる。以上のことから、熱膨張などに起因したビルドアップ層 31, 32 の浮きやデラミネーションの発生を防止できるため、高い信頼性を付与することができる。

#### 【0059】

(3) 本実施形態では、第 1 ビルドアップ層 31 の半導体素子搭載部 23 がセラミックキャパシタ 101 の真上の領域内に位置しているため、半導体素子搭載部 23 は高剛性で熱膨張率が小さいセラミックキャパシタ 101 によって支持される。よって、上記半導体素子搭載部 23 においては、第 1 ビルドアップ層 31 が変形しにくくなるため、半導体素子搭載部 23 に搭載される IC チップ 21 をより安定的に支持できる。ゆえに、IC チップ 21 として、発熱量が大きいために熱応力の影響が大きい 10mm 角以上の大型の IC チップや、Low-k (低誘電率) の IC チップを用いることができる。

#### 【0060】

さらに、本実施形態の配線基板 10 はセラミックキャパシタ 101 を有するため、セラミックキャパシタ 101 にてノイズを除去することで IC チップ 21 へ良好な電源供給を行なうことができる。しかも、IC チップ 21 が半導体素子搭載部 23 に搭載されるため、IC チップ 21 はセラミックキャパシタ 101 の真上に配置される。これにより、IC チップ 21 とセラミックキャパシタ 101 とをつなぐ配線 (コンデンサ接続配線) が短縮される。ゆえに、IC チップ 21 とセラミックキャパシタ 101 との間で侵入するノイズを極めて小さく抑えることができ、誤動作等の不具合を生じることもなく高い信頼性を得ることができる。

#### 【0061】

(4) 以下、本実施形態の変形例について説明する。図 8 に示した上記の変形例では、セラミックキャパシタ 101A のチップ縁からダムメタライズ層 118, 119 までの距

10

20

30

40

50

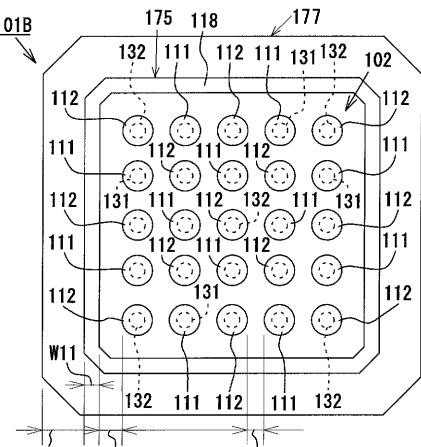

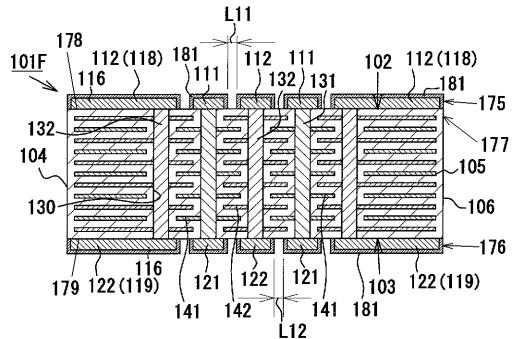

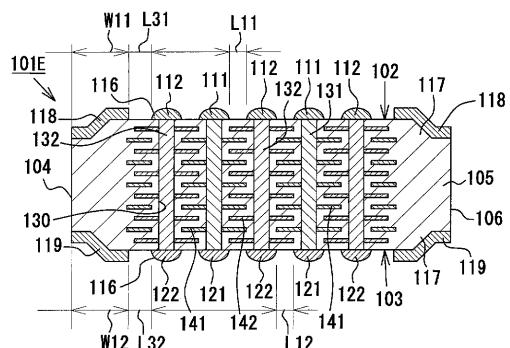

離 L 21, L 22 が、それぞれ 200 μm 以下（具体的には 150 μm ~ 200 μm 程度）に設定されている。また、図 9, 図 10 に示す別の変形例においても、セラミックキャパシタ 101B のチップ縁 177 から第 1 主面側ダムメタライズ層 118、第 2 主面側ダムメタライズ層 119 までの距離 L 21, L 22 が、それぞれ 200 μm 以下（具体的には 150 μm ~ 200 μm 程度）に設定されている。つまり、ダムメタライズ層 118, 119 の外縁 175, 176 はチップ縁 177 と重なっておらず、それゆえダムメタライズ層 118, 119 も図 2, 図 3 にて示したもの比べて若干幅狭になっている。また、ダムメタライズ層 118, 119 は、上面 102 上の外周部分に存在する切欠部（段差部）117 まで形成されている。切欠部 117 は C 面取り部、R 面取り部であっても構わない。そして、図 2, 図 3 にて示したものに代えて、このような構成のセラミックキャパシタ 101A, 101B を基板コア 11 に内蔵させてもよい。 10

### [第 2 実施形態]

#### 【0062】

以下、本発明の配線基板を具体化した第 2 実施形態を図面に基づき詳細に説明する。

#### 【0063】

図 11 に示されるように、本実施形態の配線基板 10B には、前記第 1 実施形態に示すセラミックキャパシタ 101 の代わりに、キャパシタの機能を有しないセラミックチップ 201 が設けられている。セラミックチップ 201 には、上面 202（チップ第 1 主面）及び下面 203（チップ第 2 主面）を貫通する複数のビア導体 204（内部導体）がアレイ状に形成されている。上面 202 には、第 1 外部端子電極 111, 112 のメタライズ層 116 が設けられ、下面 203 には、第 2 外部端子電極 121, 122 のメタライズ層 116 が設けられている。また、上面 202 及び下面 203 には、ダムメタライズ層 118, 119 が設けられている。なお、本実施形態のメタライズ層 116, 118, 119 は、モリブデンを主体として形成されている。また、メタライズ層 116, 118, 119 の表面には、図示しないニッケルめっき層及び図示しない銅めっき層が順番に積層されているてもよい。従って、本実施形態においては、ビルドアップ層 31, 32 を構成する層間絶縁層 33, 34 とセラミックチップ 201 との密着強度に優れた配線基板 10B を提供することができる。 20

### [第 3 実施形態]

#### 【0064】

以下、本発明の配線基板を具体化した第 3 実施形態を図面に基づき詳細に説明する。 30

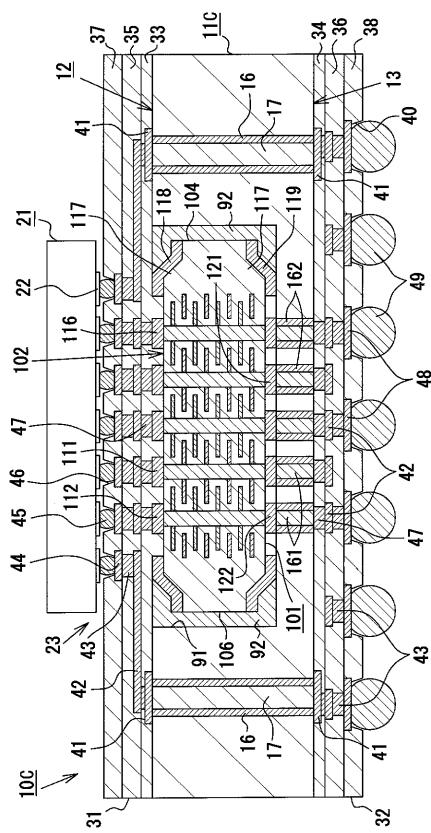

#### 【0065】

図 12 に示されるように、本実施形態の配線基板 10C では、基板コア 11C の収容穴部 91 が、基板コア 11C の上面 12 のみにて開口する有底の凹部（非貫通穴部）となっている。よって、第 2 ビルドアップ層 32 の樹脂絶縁層 34 は、全体が基板コア 11C の下面 13 に当接している。また、収容穴部 91 内には、前記第 1 実施形態と同様の構成を有するセラミックキャパシタ 101 が設けられている。なお、樹脂絶縁層 34 及びセラミックキャパシタ 101 は、収容穴部 91 の底面と基板コア 11C の下面 13 とを貫通する複数のビア導体 162 を介して互いに電気的に接続されている。これらビア導体 162 の内部は、導体ペースト 161 で埋められている。 40

#### 【0066】

なお、本発明の各実施の形態は以下のように変更してもよい。

#### 【0067】

・上記各実施形態では、粗化工程において、各銅めっき層 181 の表面の粗化と同時に、各導体層 41 の表面の粗化を行っていた。しかし、各導体層 41 の粗化を、各銅めっき層 181 の粗化とは別々に行ってもよい。

#### 【0068】

・上記各実施形態では、上面 102 に垂直な方向から見たときのダムメタライズ層 118, 119（銅めっき層 181）の外形形状は略矩形状であり、略矩形状の開口部を有した形状をなしていた。しかし、ダムメタライズ層 118, 119（銅めっき層 181）の 50

形状は他の形状であってもよい。

【0069】

・上記第1, 第3実施形態では、ダムメタライズ層118, 119及び銅めっき層18 1からなる表面導体が、外部端子電極111, 112, 121, 122とほぼ同じ層構造を有していたが、異なる層構造を有していてもよい。また、ダムメタライズ層118, 119の厚さは、メタライズ層116と同じ厚さであってもよいし、メタライズ層116よりも厚くてもよい。

【0070】

・上記各実施形態の充填剤92の代わりに、樹脂絶縁層33の一部を充填剤としてもよい。これは、第1ビルトアップ層31を構成する樹脂絶縁層33を形成する際に、流動性を有する樹脂フィルムを用いて加圧ラミネートすることにより可能となる。このようにすれば、収容穴部91の内面とセラミックキャパシタ101の側面106との隙間を充填剤92であらかじめ埋めなくても、樹脂フィルムの一部が隙間に入るため、樹脂フィルムの一部を充填剤として機能させることができる。また、上記実施形態では、隙間に對しディスペンサ装置を用いて充填剤92を充填したが、これに限定されるものではなく、例えば印刷装置を用いて充填剤92を印刷充填してもよい。

10

【0071】

・上記各実施形態における外部端子電極111, 112, 121, 122は、図2等に示すように上辺及び下辺の長さが等しい矩形状の断面を有していたが、これとは異なるものであってもよい。例えば、図13に示す別の実施形態のセラミックキャパシタ101Dにおいて、外部端子電極111, 112, 121, 122は、下辺よりも上辺のほうが短い先細り形状の断面を有している。また、図14に示す別の実施形態のセラミックキャパシタ101Eにおいて、外部端子電極111, 112, 121, 122は、表面が球面となつた形状を有している。図13, 図14のような電極形状であると、樹脂絶縁層33, 34の樹脂が凹部に流れ込みやすくなり、密着性向上を達成しやすくなる。ただし、この構成を採用する場合においても、ダムメタライズ層118, 119はその表面に平坦部を有していることが好ましい。その理由は、表面が球面である場合に比べて表面が平坦部であるほうが、ダムとしての機能を果たしやすいからである。

20

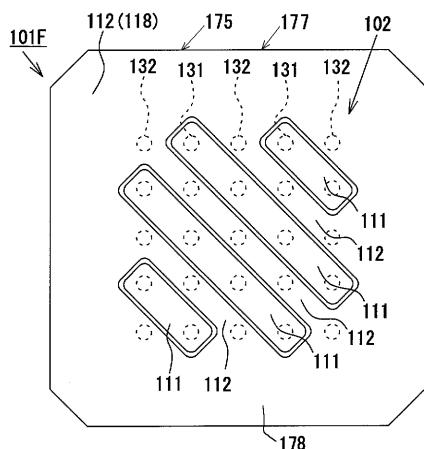

【0072】

・図15, 図16に示す別の実施形態のセラミックキャパシタ101Fは段差部を有するものではないが、電源第1外部端子電極111、グランド第1外部端子電極112、電源第2外部端子電極121、グランド第2外部端子電極122を備えている。この実施形態の外部端子電極111, 121は、複数のビア導体131同士を互いに接続するように配置された直線状の電極である。一方、外部端子電極112, 122は、複数のビア導体132同士を互いに接続するように配置されたプレーン状の電極である。なお、グランド第1外部端子電極112、グランド第2外部端子電極122はそれぞれ連結しており、その外縁175, 176はチップ縁177にまで及んでいる。つまり、第1主面側ダムメタライズ層118と繋がっているグランド第1外部端子電極112は、上面102の外周縁部178において複数の電源第1外部端子電極111を包囲するように配置されている。それゆえ、グランド第1外部端子電極112は、第1ダムメタライズ層118としての機能も備えている第1プレーングランド電極と把握できる。また、第2主面側ダムメタライズ層119と繋がっているグランド第2外部端子電極122は、下面103の外周縁部179において複数の電源第2外部端子電極121を包囲するように配置されている。それゆえ、グランド第2外部端子電極122は、第2ダムメタライズ層119としての機能も備えている第2プレーングランド電極と把握できる。また、外縁175, 176を含む側面106が、面一とされているため、キャパシタ上面102への充填剤92の進入を防ぐことができる。そしてこの構成の利点は、充填剤92の充填硬化時においてチップ縁177付近の充填剤92にクラックが発生しにくくなることである。よって、信頼性を向上させることができる。

30

【0073】

40

50

・図17に示す別の実施形態のセラミックキャパシタ101Gも、図16のものと類似の構成を有している。ただし、ダムメタライズ層118, 119を兼ねる外部端子電極112, 122がチップ縁まで及んでいない点が相違している。また、外部端子電極111, 112, 121, 122の表面が球面となった電極形状を呈している。この構成においては、グランド第1外部端子電極112、グランド第2外部端子電極122はそれぞれ連結しており、その外縁185, 186はR面とされている。従って、この構成であっても、充填剤92の充填硬化時においてチップ縁177付近の充填剤92にクラックが発生しにくくなり、信頼性を向上させることができる。その理由は不明であるが、チップの上面102（または下面103）と電極側面とがなす角が90°より広くなり、クラック発生の起点となり得なくなるからである、と推測される。

10

#### 【0074】

・上記セラミックキャパシタ101F, 101Gにおいて、第2プレーングランド電極の代わりに、第2プレーン電源電極を形成してもよい。つまり、上面102側では、グランド第1外部端子電極112が、第1主面側ダムメタライズ層118と繋がっており、上面102の外周縁部178において複数の電源第1外部端子電極111を包囲するように配置されている一方、下面103側では、電源第2外部端子電極が、第2主面側ダムメタライズ層119と繋がっており、下面103の外周縁部179において、複数のグランド第2外部端子電極を包囲するように配置されている第2プレーン電源電極である形態としてもよい。上面102、下面103の端子電極を異種のプレーン電極とすることにより、電解めっきを効率よく行うことが可能である。

20

#### 【0075】

・上記各実施形態では基板コア11の収容穴部91内にセラミックチップを収容したものを例示したが、セラミックを主成分とするチップ以外の被収容物、例えば複数の端子電極を有するチップ部品を収容した構成としてもよい。

#### 【0076】

次に、前述した実施形態によって把握される技術的思想を以下に列挙する。

#### 【0077】

(1) 高分子材料を主体として板状に形成され、コア主面及びコア裏面を有し、少なくとも前記コア主面にて開口する収容穴部を有する基板コアと、チップ第1主面及びチップ第2主面を有する板状のセラミック焼結体、前記セラミック焼結体の内部に形成された内部導体、前記チップ第1主面上に突設され前記内部導体に導通するメタライズ層からなる複数の第1端子電極、前記チップ第2主面上に突設され前記内部導体に導通するメタライズ層からなる複数の第2端子電極を有し、前記コア主面と前記チップ第1主面とを同じ側に向けた状態で前記収容穴部内に収容された埋め込み用セラミックチップと、前記収容穴部の内面と前記埋め込み用セラミックチップの側面との隙間を埋めて前記埋め込み用セラミックチップを固定する充填剤と、高分子材料を主体とする層間絶縁層及び導体層を前記コア主面及び前記チップ第1主面の上にて交互に積層した構造を有し、その表面に半導体素子搭載部が設定されたビルドアップ層とを備え、前記複数の第2端子電極を包囲する第2主面側凸部を前記チップ第2主面上に突設したことを特徴とする配線基板。

30

#### 【0078】

(2) 高分子材料を主体として板状に形成され、コア主面及びコア裏面を有し、前記コア主面及び前記コア裏面の両方にて開口する収容穴部を有する基板コアと、チップ第1主面及びチップ第2主面を有する板状のセラミック焼結体、前記セラミック焼結体の内部に形成された内部導体、前記チップ第1主面上に突設され前記内部導体に導通するメタライズ層からなる複数の第1端子電極、前記チップ第2主面上に突設され前記内部導体に導通するメタライズ層からなる複数の第2端子電極を有し、前記コア主面と前記チップ第1主面とを同じ側に向けかつ前記コア裏面と前記チップ第2主面とを同じ側に向けた状態で前記収容穴部内に収容された埋め込み用セラミックチップと、前記収容穴部の内面と前記埋め込み用セラミックチップの側面との隙間を埋めて前記埋め込み用セラミックチップを固定する充填剤と、高分子材料を主体とする層間絶縁層及び導体層を前記コア主面及び前記

40

50

チップ第1主面の上にて交互に積層した構造を有し、その表面に半導体素子搭載部が設定された第1ビルドアップ層と、高分子材料を主体とする層間絶縁層及び導体層を前記コア裏面及び前記チップ第2主面の上にて交互に積層した構造を有する第2ビルドアップ層とを備え、前記複数の第2端子電極を包囲する第2主面側凸部を前記チップ第2主面上に突設したことを特徴とする配線基板。

【0079】

(3) コア主面及びコア裏面の両方に開口する収容穴部を有する基板コアと、複数の第1端子電極、複数の第2端子電極、第1主面側凸部及び第2主面側凸部を形成した埋め込み用セラミックチップとを準備する準備工程と、前記収容穴部のコア裏面側開口を剥離可能な粘着テープでシールするテープリング工程と、前記収容穴部内に前記埋め込み用セラミックチップを収容するとともに、前記粘着テープの粘着面に前記第2主面側凸部を貼り付ける収容工程と、前記収容工程後、前記収容穴部の内面と前記埋め込み用セラミックチップの側面との隙間を充填剤で埋めて、前記埋め込み用セラミックチップを固定する固定工程とを含むことを特徴とする配線基板の製造方法。

10

【0080】

(4) 上記(3)において、前記第1主面側凸部及び前記第2主面側凸部は、前記複数の第1端子電極及び前記複数の第2端子電極を形成するメタライズ工程の際に併せて形成されるメタライズ層であることを特徴とする配線基板の製造方法。

【0081】

(5) 高分子材料を主体として形成された基板コアの収容穴部内に収容され、前記収容穴部との隙間を充填剤で埋めた状態で使用されるチップ部品であって、チップ主面を有する部品本体と、前記部品本体の内部に形成された内部導体と、前記チップ主面上に設けられ前記内部導体に導通する複数の端子電極と、前記複数の端子電極を包囲するようにして前記チップ主面上に突設された凸部とを備えることを特徴とする埋め込み用チップ部品。

20

【0082】

(6) コア主面及びコア裏面を有し、前記コア主面及び前記コア裏面の両方に開口する収容穴部を有する基板コアと、チップ第1主面及びチップ第2主面を有するセラミック焼結体、前記セラミック焼結体の内部に形成された内部導体、前記チップ第1主面上に突設され前記内部導体に導通するメタライズ層からなる複数の第1端子電極、前記チップ第2主面上に突設され前記内部導体に導通するメタライズ層からなる複数の第2端子電極を有し、前記コア主面と前記チップ第1主面と同じ側に向けかつ前記コア裏面と前記チップ第2主面と同じ側に向けた状態で前記収容穴部内に収容された埋め込み用チップと、前記収容穴部の内面と前記埋め込み用チップの側面との隙間を埋めて前記埋め込み用セラミックチップを固定する充填剤と、層間絶縁層及び導体層を前記コア主面及び前記チップ第1主面の上にて交互に積層した構造を有した第1ビルドアップ層と、層間絶縁層及び導体層を前記コア裏面及び前記チップ第2主面の上にて交互に積層した構造を有する第2ビルドアップ層とを備え、前記チップ第2主面上の外周縁部に、第2主面側ダムメタライズ層が配置されていることを特徴とする配線基板。

30

【0083】

(7) 上記(6)において、前記複数の第2端子電極は、グランド第2端子電極と、電源第2端子電極とからなり、前記グランド第2端子電極は、前記第2主面側ダムメタライズ層と繋がっており、かつ、複数の前記電源第2端子電極を包囲する第2プレーングランド電極とされている、或いは、前記電源第2端子電極は、前記第2主面側ダムメタライズ層と繋がっており、かつ、複数の前記グランド第2端子電極を包囲する第2プレーン電源電極とされていることを特徴とする配線基板。

40

【0084】

(8) 上記(7)において、前記チップ第1主面上の外周縁部に、第1主面側ダムメタライズ層が配置されており、前記複数の第1端子電極は、グランド第1端子電極と、電源第1端子電極とからなり、前記グランド第1端子電極は、前記第1主面側ダムメタライズ層と繋がっており、かつ、複数の前記電源第1端子電極を包囲する第1プレーングランド

50

電極とされている、或いは、前記電源第1端子電極は、前記第1主面側ダムメタライズ層と繋がっており、かつ、複数の前記グランド第1端子電極を包囲する第1プレーン電源電極とされていることを特徴とする配線基板。

【0085】

(9) 上記(6)乃至(8)のいずれか1項において、ダムメタライズ層は、チップ縁まで形成されていることを特徴とする配線基板。

【0086】

(10) 上記(6)乃至(8)のいずれか1項において、前記チップ第1主面上或いは前記チップ第2主面上に切欠部が存在するとともに、ダムメタライズ層は少なくとも切欠部まで形成されていることを特徴とする配線基板。 10

【0087】

(11) 上記(10)において、ダムメタライズ層は切欠部を含む領域に配置されていることを特徴とする配線基板。

【0088】

(12) 上記(6)乃至(8)のいずれか1項において、ダムメタライズ層は、外縁がR面とされていることを特徴とする配線基板。

【0089】

(13) 高分子材料を主体として形成された基板コアの収容穴部内に収容され、前記収容穴部との隙間を充填剤で埋めた状態で使用されるセラミックチップであって、チップ主面を有する板状のセラミック焼結体と、前記セラミック焼結体の内部に形成された内部導体と、前記チップ主面上に突設され前記内部導体に導通するメタライズ層からなる複数の端子電極とを有し、前記チップ主面上の外周縁部に、ダムメタライズ層が配置されており、前記複数の端子電極は、グランド端子電極と、電源端子電極とからなり、前記グランド端子電極は、ダムメタライズ層と繋がっており、かつ、複数の前記電源端子電極を包囲するプレーングランド電極とされている、或いは、前記電源端子電極は、前記ダムメタライズ層と繋がっており、かつ、複数の前記グランド端子電極を包囲するプレーン電源電極とされていることを特徴とする埋め込み用セラミックチップ。 20

【0090】

(14) 上記(13)において、ダムメタライズ層は、チップ縁まで形成されていることを特徴とする埋め込み用セラミックチップ。 30

【0091】

(15) 上記(13)において、前記主面上に切欠部が存在するとともに、ダムメタライズ層は少なくとも切欠部まで形成されていることを特徴とする埋め込み用セラミックチップ。

【0092】

(16) 上記(15)において、ダムメタライズ層は切欠部を含む領域に配置されていることを特徴とする埋め込み用セラミックチップ。

【0093】

(17) 上記(13)において、ダムメタライズ層は、外縁がR面とされていることを特徴とする埋め込み用セラミックチップ。 40

【図面の簡単な説明】

【0094】

【図1】本発明を具体化した第1実施形態の配線基板を示す概略断面図。

【図2】同じく、セラミックキャパシタを示す概略断面図。

【図3】同じく、セラミックキャパシタを示す概略上面図。

【図4】同じく、配線基板の製造方法の説明図。

【図5】同じく、配線基板の製造方法の説明図。

【図6】同じく、配線基板の製造方法の説明図。

【図7】同じく、配線基板の製造方法の説明図。

【図8】第1実施形態の変形例であるセラミックキャパシタを示す概略断面図。 50

【図9】第1実施形態の変形例であるセラミックキャパシタを示す概略断面図。

【図10】第1実施形態の変形例であるセラミックキャパシタを示す概略上面図。

【図11】第2実施形態の配線基板を示す概略断面図。

【図12】第3実施形態の配線基板を示す概略断面図。

【図13】別の実施形態のセラミックキャパシタを示す概略断面図。

【図14】別の実施形態のセラミックキャパシタを示す概略断面図。

【図15】別の実施形態のセラミックキャパシタを示す概略断面図。

【図16】別の実施形態のセラミックキャパシタを示す概略上面図。

【図17】別の実施形態のセラミックキャパシタを示す概略断面図。

【図18】従来技術の配線基板の製造方法を示す説明図。

10

【図19】従来技術の問題点を示す説明図。

【符号の説明】

【0095】

10, 10B, 10C...配線基板

11, 11C...基板コア

12...コア正面としての上面

13...コア裏面としての下面

31...ビルドアップ層としての第1ビルドアップ層

32...第2ビルドアップ層

33, 34, 35, 36...層間絶縁層としての樹脂絶縁層

20

42...導体層

91...収容穴部

92...充填剤

101, 101A, 101D, 101E, 101F, 101G...埋め込み用セラミックチップとしてのセラミックキャパシタ

102, 202...チップ第1正面としての上面

103, 203...チップ第2正面及びチップ正面としての下面

104...セラミック焼結体

105...セラミック誘電体層

106...埋め込み用セラミックチップの側面

30

111, 112...第1端子電極としての第1外部端子電極

116...メタライズ層

117...段差部

118...第1正面側凸部としてのダムメタライズ層

119...第2正面側凸部及び凸部としてのダムメタライズ層

121, 122...第2端子電極及び端子電極としての第2外部端子電極

131, 132, 204...内部導体としてのピア導体

141...内部導体としての第1内部電極層

142...内部導体としての第2内部電極層

181...金属層

40

201...埋め込み用セラミックチップとしてのセラミックチップ

W12...第2正面側凸部の幅

L22...第2正面側凸部までの距離

【 四 1 】

【図2】

【図3】

【 四 4 】

【図6】

【 5 】

【圖 7】

【 図 8 】

【図9】

【 図 1 0 】

### 【图 1 1】

【図12】

【図13】

【図15】

【図14】

【図16】

【図17】

【図19】

【図18】

---

フロントページの続き

(72)発明者 村松 正樹

名古屋市瑞穂区高辻町14番18号 日本特殊陶業株式会社 内

(72)発明者 佐藤 元彦

名古屋市瑞穂区高辻町14番18号 日本特殊陶業株式会社 内

(72)発明者 土佐 晃文

名古屋市瑞穂区高辻町14番18号 日本特殊陶業株式会社 内

審査官 坂本 薫昭

(56)参考文献 特開2005-039243 (JP, A)

特開2004-172412 (JP, A)

特開2001-118746 (JP, A)

特開2000-261124 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 23 / 12

H 05 K 1 / 18