(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2018년06월20일

(11) 등록번호 10-1857022

(24) 등록일자 2018년05월04일

(51) 국제특허분류(Int. Cl.)

H01L 29/872 (2006.01) H01L 29/40 (2006.01)

H01L 29/47 (2006.01) H01L 29/788 (2006.01)

(21) 출원번호 10-2013-7023370

(22) 출원일자(국제) 2012년02월03일

심사청구일자 2016년01월29일

(85) 번역문제출일자 2013년09월03일

(65) 공개번호 10-2014-0057475

(43) 공개일자 2014년05월13일

(86) 국제출원번호 PCT/US2012/023724

(87) 국제공개번호 WO 2012/106572

국제공개일자 2012년08월09일

(30) 우선권주장

13/021,078 2011년02월04일 미국(US)

(56) 선행기술조사문현

US20040183115 A1\*

\*는 심사관에 의하여 인용된 문현

(73) 특허권자

비사이 제너럴 세미컨덕터 엘엘씨

미국 뉴욕 11788, 하우퍼우즈, 150 모터 파크웨이

(72) 발명자

카오 렁 청

타이페이 시티 완산 디스트릭트 무신 로드 232항

3단 앤리6 4층 18호

(74) 대리인

특허법인대한

전체 청구항 수 : 총 5 항

심사관 : 안경민

(54) 발명의 명칭 다중 부유게이트를 갖는 트렌치 MOS 장벽 쇼트키(TMBS)

**(57) 요 약**

제1 도전형의 반도체 기판을 포함하는 반도체 정류기가 제공된다. 기판 상에는 에피택시층이 형성된다. 에피택시층은 기판보다 낮은 농도로 도핑된 제1 도전형으로 이루어진다. 에피택시층 내에는 다수의 부유게이트가 형성되고, 에피택시층 위에는 이 에피택시층과 쇼트키 접촉을 이루는 금속층이 배치된다. 금속층 위에 제1 전극이 형성되고, 기판의 뒷면에는 제2 전극이 형성된다.

**대 표 도** - 도2

## 명세서

### 청구범위

청구항 1

삭제

청구항 2

삭제

청구항 3

삭제

청구항 4

삭제

청구항 5

삭제

청구항 6

삭제

청구항 7

삭제

청구항 8

제1 도전형으로 된 반도체 기판과, 상기 기판 상에 형성되며 상기 기판보다 낮은 높도로 도핑된 제1 도전형의 에피택시층을 포함하는 반도체 기판을 준비하는 단계;

상기 반도체 기판의 표면에, 측벽과 바닥을 갖는 다수의 트렌치를 에칭하되, 인접한 트렌치와 트렌치 사이에 메사부가 형성되도록 에칭하는 단계;

각 트렌치 내에 다수의 부유게이트를 형성하는 단계; 및

상기 메사부의 표면에는 쇼트키 접촉이 이루어지도록 하기 위해 금속층을 형성하는 단계;를 포함하며

상기 각 트렌치 내에 형성된 다수의 부유게이트에는 유전층과 도전층이 교대로 층이 이루어지도록 형성되고,

상기 유전층과 도전층이 교대로 층을 형성하는 단계는

상기 메사부의 표면과 상기 다수 트렌치의 측벽과 바닥에 고온 산화 공정 또는 화학기상증착을 통해 게이트 산화층을 형성하는 제1단계; 와,

상기 게이트 산화층 위에 화학기상증착(CVD)를 이용하여 제1 도전층을 형성하기 위해 임의의 금속 또는 도핑 폴리실리콘 또는 도핑된 비정질 실리콘을 상기 다수의 트렌치를 채우는 제2단계; 와,

이방성 에칭을 이용하여 상기 제2단계에서 채워진 제1 도전층의 잉여부분을 제거하고, 또한 게이트 산화층의 상부면이 상기 잉여부분을 제거한 제1 도전층의 상면과 동일 평면이 되도록 에칭하는 제3단계;

상기 게이트 산화층의 에칭 공정 후에 트렌치 내에서 제1유전층을 상기 제1도전층의 위에 형성하는 제4단계;

상기 제1유전층을 이방성 에칭하여 그 두께를 0,2 내지 2 미크론으로 줄이는 제5단계;를 통해 제1도전층과 제1유전층을 형성시킨 다음

상기 제2단계 내지 제5단계를 반복 실시하여 상기 유전층과 도전층이 교대로 층을 형성하도록 하고, 그 다음으로

스퍼터링을 통해 메사부상에 쇼트키 접촉 영역을 형성하기 위해 상기 금속층을 증착하는 단계;와

상기 금속층의 상면에 양전극을 형성하는 단계;와;

상기 반도체 기판의 뒷면에 음전극을 형성하는 단계;를 포함하는 반도체 정류기 제조방법.

### 청구항 9

삭제

### 청구항 10

삭제

### 청구항 11

제8항에 있어서, 상기 금속층은 니켈이고, 상기 에피택시층은 실리콘을 포함하여 니켈과 에피택시층 사이의 계면에 실리사이드 층이 형성되도록 하는 반도체 정류기 제조방법

### 청구항 12

제8항에 있어서, 상기 도전층은 알루미늄인 반도체 정류기 제조방법.

### 청구항 13

제8항에 있어서, 상기 도전층은 도핑 폴리실리콘인 반도체 정류기 제조방법.

### 청구항 14

제8항 또는 제11항 내지 제13항 중 어느 한 항의 반도체 정류기 제조방법을 통해 제조된 반도체 정류기

## 발명의 설명

### 기술 분야

[0001] 본 발명은 반도체 소자에 관한 것으로서, 보다 구체적으로는, 트렌치 MOS 소자의 게이트 구조에 관한 것이다.

### 배경 기술

[0002] 종래, 쇼트키 다이오드는, 일반적으로 단결정 실리콘으로 제작되는 고농도 도핑된 반도체 기판을 포함한다. 제2의 층이 기판을 덮고 있는데, 이 제2층(드리프트 영역(drift region)이라고 부름)은 기판과 동일한 도전형의 캐리어(carrier)를 갖는 재료로 제작되며 기판보다 낮은 농도로 도핑된다. 금속층 또는 또는 메탈 실리사이드(metal silicide) 층이, 저농도 도핑된 드리프트 영역과 쇼트키 접촉(Schottky contact)을 형성하며 다이오드 양전극(애노드)을 구성한다.

[0003] 쇼트키 다이오드와 같은 단극형(유니폴라) 소자를 제작할 때에는 두 가지 상반되는 제약조건이 있게 된다. 구체적으로, 이 소자는 높은 항복전압(breakdown voltage)을 가지면서도 가장 낮은 도통상태 저항(Ron: on-state resistance)을 띠어야 한다. 도통상태 저항을 최소화하려면 보다 낮은 농도로 도핑된 층의 두께를 최소화해야 하고 이 층의 도핑량을 최대로 해야 한다. 반대로, 높은 역항복전압(reverse breakdown voltage)을 얻기 위해서는, 등전위면이 강하게 휘어지는 영역의 발생을 막으면서, 보다 낮은 농도로 도핑된 층의 도핑량을 최소화해야 하고 그 두께를 최대로 해야 한다.

[0004] 이러한 상반된 제약조건을 조정하기 위해 다양한 해결책이 제시되어 왔고, 이에 의해 트렌치 MOS 정전용량 쇼트키 다이오드 구조의 개발이 이루어졌는데, 이 다이오드는 트렌치 MOS 장벽 쇼트키(TMBS: trench MOS barrier schottky) 다이오드라고 부른다. 이 다이오드의 구조의 예를 들면, 하부의 기판보다 적게 N 형 도핑된 두꺼운 드리프트 영역의 상부에 도전 영역(예를 들어, 고농도 도핑된 N 형 폴리실리콘 영역)이 형성된다. 절연층은 상기 두꺼운 층과 상기 도전 영역을 격리한다. 양전극 층이 전체 구조를 덮되, 절연된 도전 영역의 상부 표면에

접촉하여 저농도 도핑된 드리프트 영역과 쇼트키 접촉을 형성한다.

[0005] 역방향 바이어스를 인가하면, 절연된 도전 영역은 드리프트 영역 내로의 측면 공핍(lateral depletion)을 일으켜서, 이 층에서의 등전위면의 분포를 변화시킨다. 이에, 드리프트 영역의 도핑량이 증가되고, 따라서, 역항복 전압에 역효과를 주지 않으면서 도통상태 저항이 감소될 수 있다.

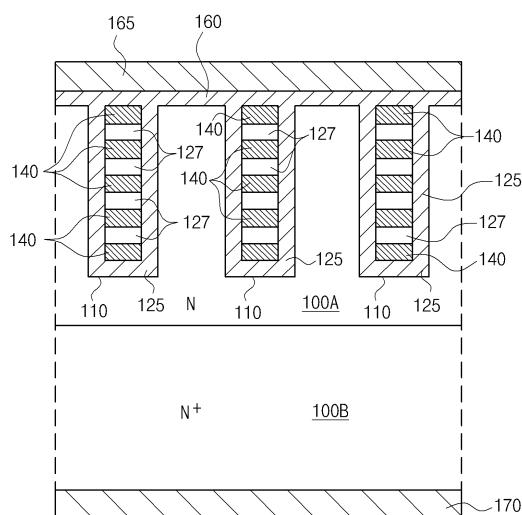

[0006] 도 1은 기존의 TMBS 쇼트키 다이오드, 즉, 정류기의 개략적 부분도이다. 이 다이오드는 고농도 도핑된 N형 실리콘 웨이퍼(1)와 그 위에 형성된 저농도 도핑된 N형 에피택시층(epitaxial layer)(2)으로 구성된다. 이 에피택시층에는 개방부가 형성되어 있는데, 이들 개방부는, 예를 들어, 구덩이(트렌치, trench) 형태로 형성할 수 있다. 도전 영역(3)이 개방부 내에 형성되는데, 이들 도전 영역은 예를 들어 도핑 폴리실리콘(doped polysilicon) 재료로 제작된다. 절연층(4)이 각 도전 영역(3)과 해당 개방부(예를 들어, 트렌치) 벽 사이에 개재되어 있다. 절연층(4)은 예를 들어 열 산화에 의해 형성할 수 있고, 개방부에는 등각 증착법(conformal deposition)에 의해서 폴리실리콘을 채울 수 있다. 그 후에 평탄화 단계를 진행한다. 이 후, 단결정 실리콘 영역상의 실리사이드(5)를 그리고 폴리실리콘의 충전된 영역상의 실리사이드(6)를 형성할 수 있는 금속(예를 들어 니켈)을 증착한다. 실리사이드가 형성되면, 실리콘과 반응하지 않은 금속을 선택적 에칭으로 제거한다. 그 후, 양전극 금속층(7)을 상면에 형성하고, 음전극 금속층(8)을 하면에 형성한다.

[0007] 평면 구조 대신에 트렌치 구조를 사용하면, 약 20V의 추가적인 차단 성능이 얻어진다(약 2 미크론() 폭의 트렌치의 경우에). 이러한 성능 향상의 원인은 전계 피크가 에피택시층 표면으로부터 트렌치 바닥으로 이동(relocation)하는 것 그리고 실리콘에서의 전계의 재분포(redistribution)에 따른 것이다. 이 추가적 차단 성능은 높은 차단 전압(blocking voltage)에 대해서는 그 중요성이 감소된다. 예를 들어, 20V의 추가적 차단 성능이 80V 소자의 차단 전압에 대해서는 25%가 증가되는 것이지만, 180V 소자에 대해서는 11%가 증가될 뿐이다.

## 발명의 내용

### 해결하려는 과제

[0008] 본 발명의 목적은 종래의 트렌치 MOS 장벽 쇼트키(TMBS) 다이오드의 게이트 구조를 변경함으로써(구체적으로 다중 부유게이트 구조) 보다 높은 차단 전압 성능을 얻기 위한, 다중 부유게이트 트렌치 MOS 장벽 쇼트키 다이오드(MFGTMBS)를 제공하는 것이다.

### 과제의 해결 수단

[0009] 본 발명의 일측면에 따르면, 제1 도전형의 반도체 기판을 포함하는 반도체 정류기가 제공된다. 기판 상에는 에피택시층(epitaxial layer)이 형성된다. 이 에피택시층은 기판보다 낮은 농도로 도핑된 제1 도전형으로 이루어진다. 에피택시층 내에는 다수의 부유게이트(floating gate)가 형성되고, 에피택시층 위에는 이 에피택시층과 쇼트키 접촉(Schottky contact)을 형성하는 금속층이 배치된다. 금속층 위에는 제1 전극이 형성되고, 기판의 뒷면에는 제2 전극이 형성된다.

[0010] 본 발명의 다른 측면에 따르면, 반도체 정류기를 제조하는 방법이 제공된다. 이 방법은 제1 도전형의 반도체 재료를 준비하고, 반도체 재료의 표면에 다수의 트렌치(trench)를 에칭하되 인접한 트렌치와 트렌치 사이에 메사부(mesa)가 형성되도록 에칭하는 것이 포함된다. 각 트렌치에는 측벽과 바닥이 포함되어 있다. 각 트렌치 내에 다수의 부유게이트를 형성한다. 메사부의 표면에는 금속층을 형성하여 쇼트키 접촉이 이루어지도록 한다.

## 발명의 효과

[0011] 본 발명에 따르면, 트렌치 MOS 장벽 쇼트키(TMBS) 다이오드의 게이트를 다수 형성함으로써, 소자의 에피택시층의 전계 피크의 위치를 이동시켜서 차단 전압의 추가적 증가를 꾀할 수 있다. 각 부유게이트의 모서리에서의 전하 결합 및 전계 밀집을 통해서, 다수의 전계가 소자의 에피택시층에 발생하도록 하여 초접합형 전계가 형성되도록 함으로써 보다 더 고농도로 도핑된 에피택시층을 사용할 수 있게 되어 보다 높은 차단 전압 성능을 얻게 된다.

## 도면의 간단한 설명

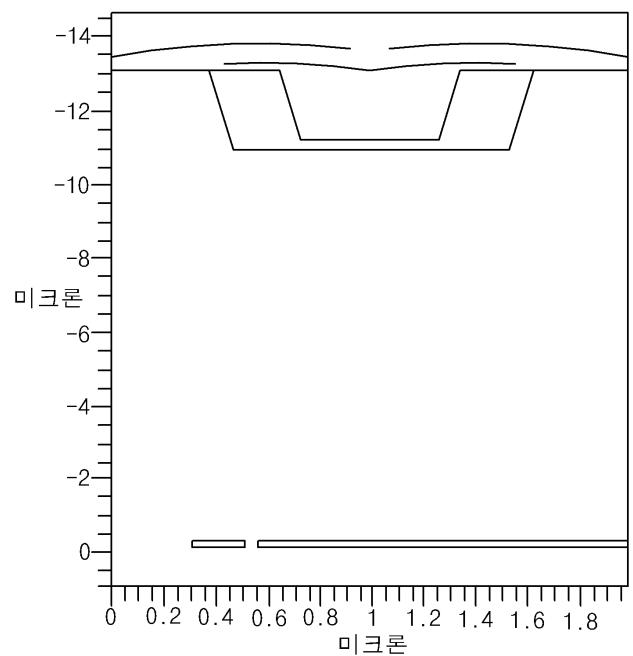

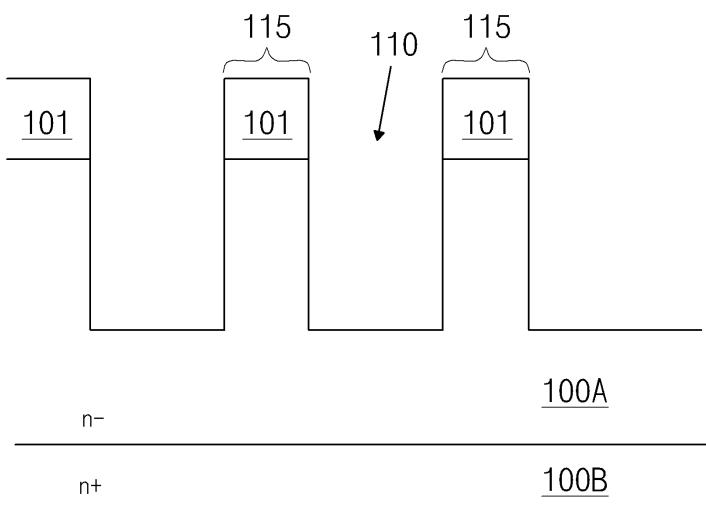

[0012] 도 1은 기존의 TMBS 쇼트키 다이오드, 즉, 정류기의 개략적 부분도이다.

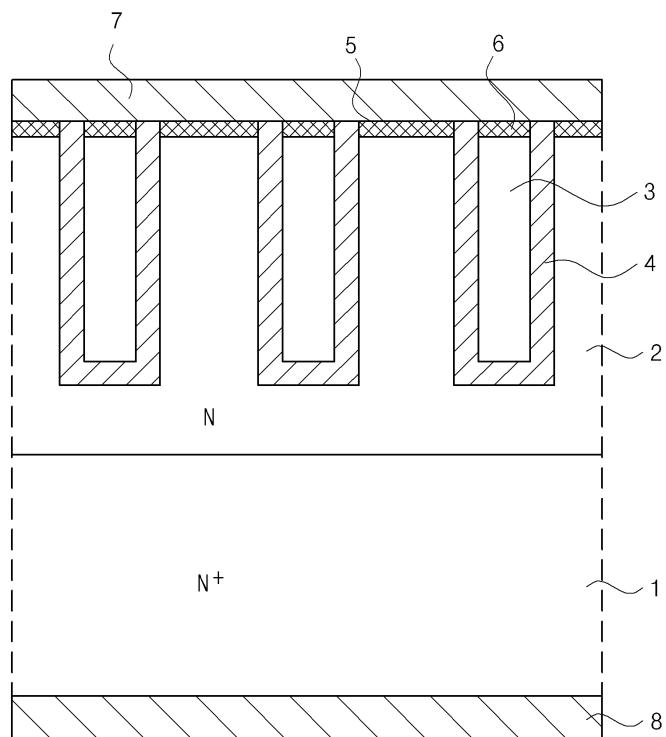

도 2는 MFGTMBS 다이오드의 활성 영역의 단면도를 나타낸다.

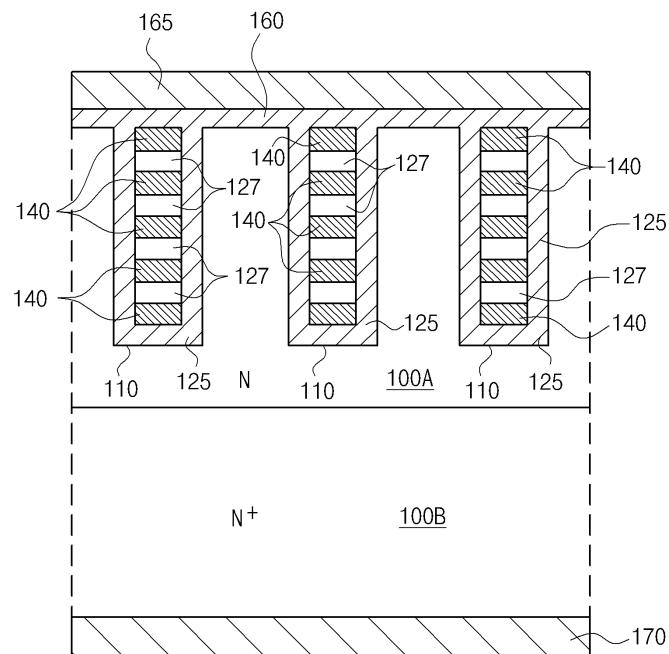

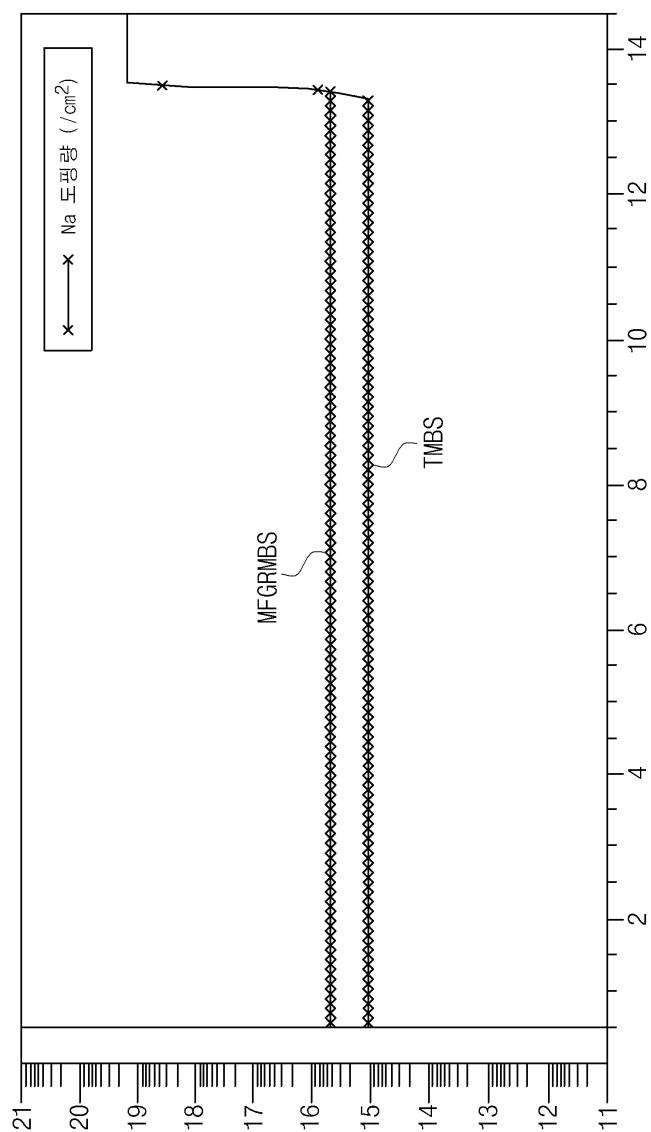

도 3a 및 3b는 각각, 다섯 개의 부유게이트를 갖는 TMBS 다이오드 및 단일 게이트를 갖는 TMBS 다이오드의 단면도이다. 도 3c는 도 3a 및 3b에 나타낸 다이오드 모두에 대한 확산저항분포(SPR: spreading resistance profile)를 나타낸다.

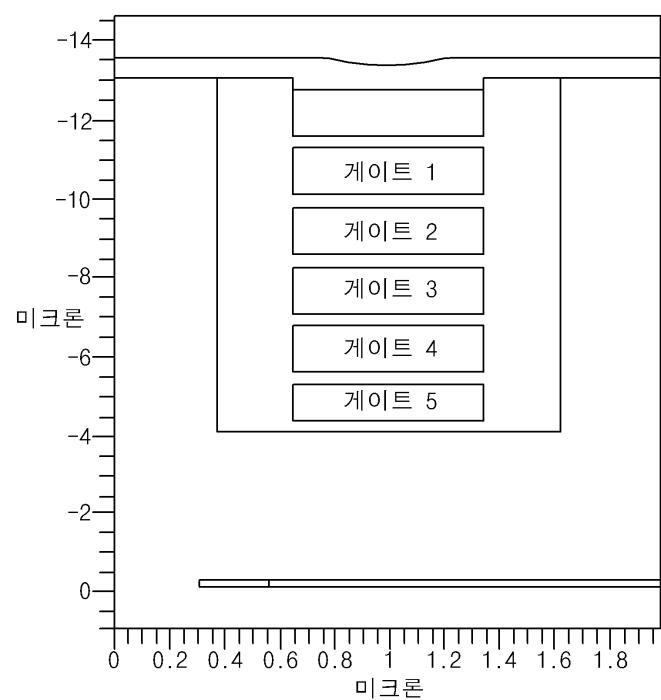

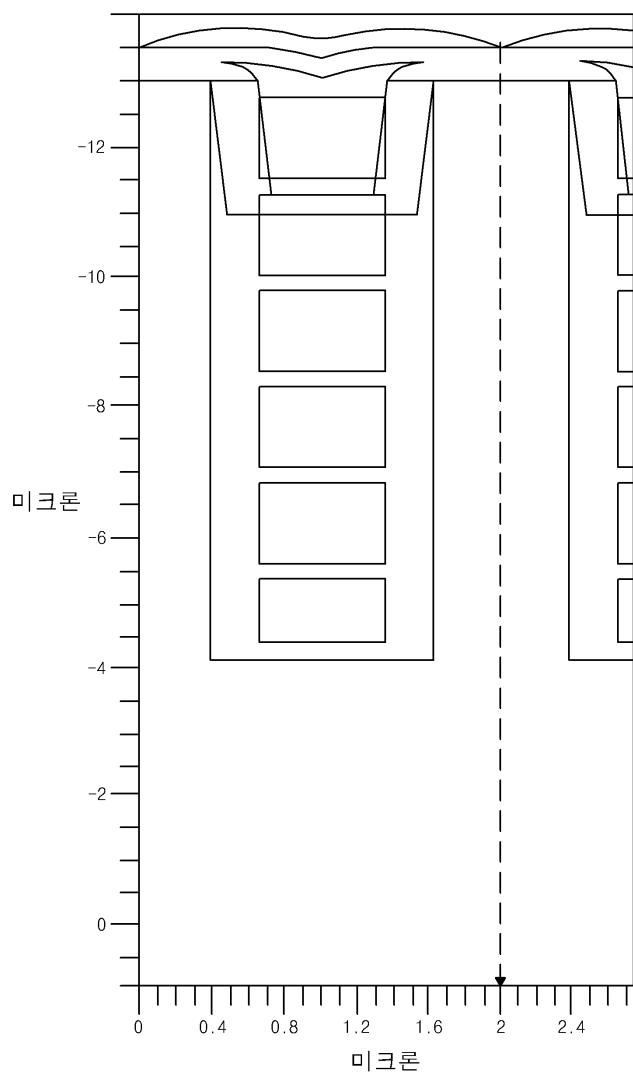

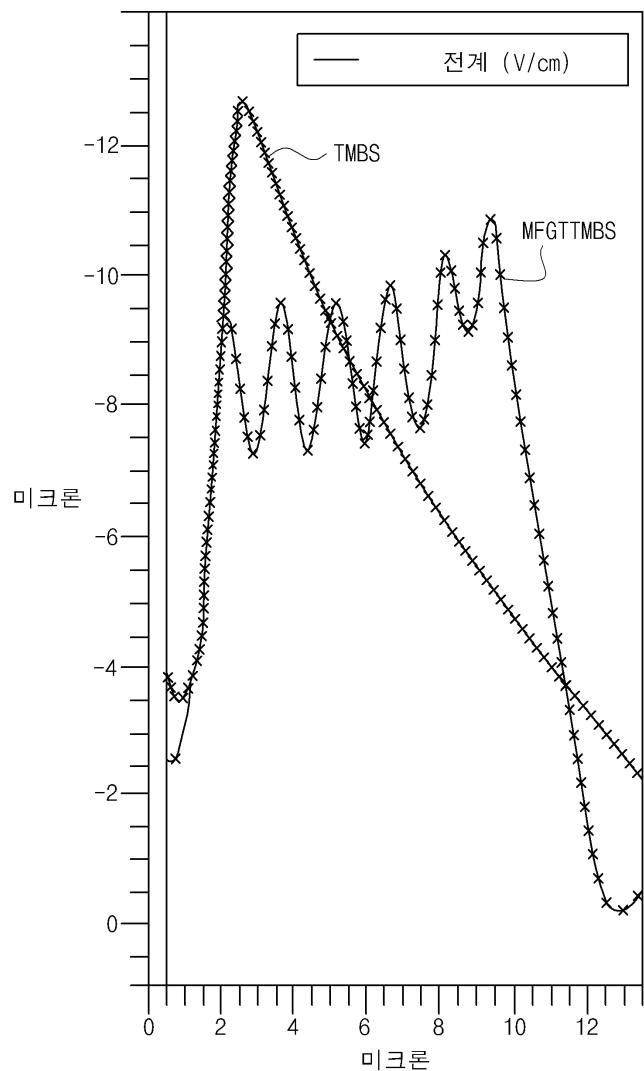

도 4a는 다섯 개의 부유게이트를 갖는 MFGTMBS 다이오드의 단면과 단일 게이트를 갖는 TMBS 다이오드의 단면을 중첩한 것을 나타낸다. 도 4b는 도 4a에 나타낸 두 다이오드를 200V로 역바이어스시킬 때의 전계 분포를 나타낸다.

도 5~15는 도 2의 소자를 제작하기 위한 공정 순서의 일례를 나타낸다.

### 발명을 실시하기 위한 구체적인 내용

[0013]

아래에 설명하는 것과 같이, 트렌치 MOS 장벽 쇼트키(TMBS) 다이오드의 게이트 구조를 변경하여, 소자의 에피택시층의 전계 피크의 위치를 더 이동시킨다. 이러한 방법에 의해서, 트렌치 설계법을 활용하여 차단 전압의 추가적 증가를 꾀할 수 있다. 구체적으로, 단일 게이트(single gate) 설계를 활용하는 대신에, 다중 부유게이트(multiple floating gate)를 갖는 TMBS 다이오드를 제공한다. 본 명세서에서는 이 소자를 다중 부유게이트 TMBS(MFGTMBS: multiple floating gate TMBS)라 부르기로 한다. 각 부유게이트의 모서리(corner)에서의 전하 결합(charge coupling) 및 전계 밀집(filed crowding)을 통해서, 소자의 에피택시층에 다중 전계가 발생한다. 이에 의해, 초접합형 전계(super junction-like electric field)가 형성되어, 보다 더 고농도로 도핑된 에피택시층을 사용할 수 있음에 의해서 더 높은 차단 전압 성능을 얻게 된다.

[0014]

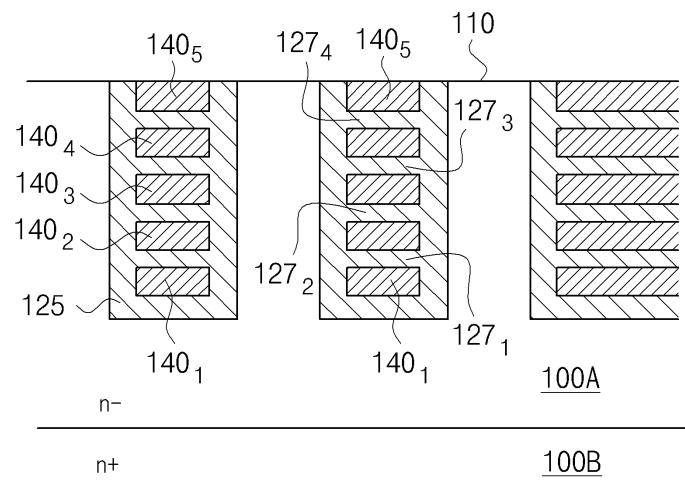

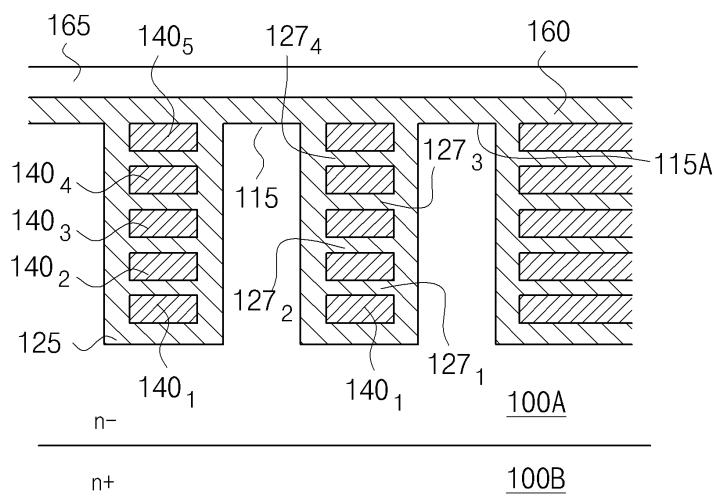

도 2는 MFGTMBS 다이오드의 활성 영역의 단면도를 나타낸다. 활성 영역에는 제1 도전형의 불순물(도편트)로 고농도 도핑된(예를 들어, n+ 형) 반도체 기판(100B)이 포함되어 있다. 제1 에피택시층(100A)이 기판(100B) 위에 형성되는데, 이는 제1 도전형의 도편트로 보다 저농도로 도핑(예를 들어, n- 형)되어 있다. 한 개 이상의 트렌치(110)가 제1 에피택시층(100A)에 형성된다. 트렌치(110) 내면에는 절연층(125)이 마감 형성되어 있다. 트렌치(110)에는 도전 물질과 절연 물질이 각각 도전층(140)과 절연층(127)의 교대층으로서 채워진다. 도전층(140)은 부유게이트(140)로서의 역할을 하며, 예컨대 금속(예를 들면, 알루미늄) 또는 도핑 폴리실리콘과 같은 도전형 물질로 형성될 수 있다. 절연층(127)은 예컨대 SiO<sub>2</sub>와 같은 적절한 절연 물질로 형성될 수 있다. 절연층 125와 절연층 127은 동일한 절연 물질로 형성할 수도 있고 다른 물질로 형성할 수도 있다. 도 2에 표시된 예에서는 다섯 개의 부유게이트(140)가 도시되어 있지만, 더 일반화하면, 부유게이트의 수는 어떠한 개수라도 가능하다.

[0015]

금속층(160)이 도전 물질(140)과 제1 에피택시층(100A)의 노출된 표면에 형성된다. 금속층(160)과 제1 에피택시층(100A) 사이의 계면에는 쇼트키 접촉이 형성된다. 양전극 금속(165)이 금속층(160) 위에 형성되고, 음전극 전극(170)이 반도체 기판(100B)의 뒷면에 형성된다.

[0016]

다중 부유게이트 TMBS의 성능 특성을 설명하기 위해 시뮬레이션을 수행하였다. 예를 들어, 도 3a는 다섯 개의 부유게이트를 갖는 TMBS 다이오드(도 2 참조)를, 도 3b는 단일 게이트를 갖는 TMBS 다이오드의 단면을 나타낸다. 도 3c는 도 3a 및 3b에 나타낸 두 다이오드에 대한 확산저항분포(SPR)를 나타낸다.

[0017]

도 4a는 다섯 개의 부유게이트를 갖는 MFGTMBS 다이오드와 단일 게이트를 갖는 TMBS 다이오드의 단면을 중첩한 것이다. 도 4b는 200V로 역바이어스된 도 4a의 두 다이오드에서의 전계 분포를 나타낸다. 도시한 것과 같이 단일 게이트 TMBS 다이오드에는 한 곳에 전계 피크가 나타난다. 그러나 MFGTMBS 다이오드는 각 부유게이트의 모서리에서의 전하 결합 및 전계 밀집에 의해서 전계가 재분포되어 다수의 전계 피크가 생성될 수 있다. 앞에서 언급한 바와 같이, 이 방식에 의해서, 초접합형 전계가 생성되어 보다 고농도 도핑된 에피택시층을 사용할 수 있기 때문에 보다 더 큰 차단 전압 성능을 갖는 소자가 만들어진다. 예를 들어, 단일 게이트 TMBS 다이오드는 약 1 10<sup>15</sup>/cm<sup>3</sup>의 에피택시층 도핑 농도를 가질 수 있는 반면에, 다섯 개의 부유게이트를 갖는 동일한 전압 정격의 MFGTMBS 다이오드의 일부 실시예에서는 약 5 10<sup>15</sup>/cm<sup>3</sup>의 에피택시층 도핑 농도를 가질 수 있다.

[0018]

또한 전계를 이동시킴으로써, 보다 고농도로 도핑된 에피택시층에 의해 소자의 순방향 전압이 개선되는 결과를 낳을 것이다. 동일한 역 차단전압을 TMBS 및 MFGTMBS 소자 모두에서 얻을 수 있지만, MFGTMBS 다이오드의 경우에는 70% 이상 칩크기가 감소된 소자가 만들어질 수 있다.

[0019]

또한 시뮬레이션 결과, 메사부(messa) 폭이 대략 1.5 미크론보다 큰 경우에는 MFGTMBS 다이오드에서의 누설전류 밀도가 단일 게이트 TMBS 다이오드에서보다 큰 것으로 나타났다. 그러나 대략 2 미크론 미만의 메사부 폭을 갖

는 MFGTMBS 다이오드의 실제 총 누설전류는 단일 게이트 TMBS 다이오드의 실제 총 누설전류보다 크지 않다. 예를 들어, 1.5 미크론의 메사부 폭을 갖는 MFGTMBS 다이오드의 JR은  $2.2 \cdot 10^{-11} \text{ A/m}^2$ 로서 200V의 단일 게이트 TMBS 다이오드의 JR값  $1.5 \cdot 10^{-11} \text{ A/m}^2$ 보다 크지만, 실리콘의 사용량은 단일 게이트 TMBS 다이오드에 비해 단지 40%에 불과하다. 예를 들어, 0.6V의 목표 순방향 전압에 대해서, MFGTMBS 다이오드의 총 누설전류는  $(2.2 \cdot 10^{-11})(0.4) = 8.8 \cdot 10^{-12} \text{ A/m}^2$ 가 될 것이며, 이는 200V의 단일 게이트 TMBS 다이오드에 대한 값  $(1.5 \cdot 10^{-11})(1.0) \text{ A/m}^2$  보다 낮다.

[0020] 단일 게이트 TMBS 다이오드에서 누설전류는 게이트의 깊이를 조절하여 제어할 수 있다. 쇼트키 누설의 원인이 되는 주요 요인이 장벽 저하(barrier lowering)인 것으로 믿어지고 있기 때문에, MFGTMBS 다이오드의 누설전류는 첫 번째 부유게이트의 깊이를 증가시킴으로써 감소될 수 있고, 이는 표면 전계를 줄이는 데 일조할 것이다. 최종적으로, MFGTMBS 다이오드의 스위칭 성능은 200V 단일 게이트 TMBS보다 더 좋을 것으로 예상되는데, 그 이유는 순방향으로 동작시에 다수 캐리어의 농도가 더 높음으로 인해 소수 캐리어의 수는 더 적기 때문이다. 결과적으로, 스위칭 속도가 훨씬 빨라지게 된다. 사실, 200V의 MFGTMBS 다이오드의 스위칭 성능은 100V의 단일 게이트 TMBS의 스위칭 성능과 유사하다.

[0021] 추가 시뮬레이션 결과, MFGTMBS 다이오드의 메사부의 폭을 변화시켜서, 단일 게이트 TMBS에서의 절충 문제와 유사하게, 소자의 역방향 및 순방향 성능 간에 절충을 할 수 있음이 증명되었다.

[0022] 도 2의 MFGTMBS 다이오드를 제작하기 위해 사용할 수 있는 방법의 한 예에 대해서 도 5~15를 참조하여 설명한다.

[0023] 도 5는 제1 도전형으로 도핑된(예를 들어, n- 형) 제1층(100A)과 이보다 고농도로 제1 도전형의 도편트로 도핑된(예를 들어, n+ 형) 기재(100B)를 포함하는 반도체 기판(100)의 단면도이다. 산화층(101)을 화학기상증착(CVD)에 의해 제1층(100A) 위에 형성한다. 그 두께는 예를 들어, 2000~10000 옹스트롬이다. 다수의 트렌치(110) 영역을 형성하기 위해 산화층(101) 위에 포토레지스트(도시하지 않았음)를 코팅한다. 각 트렌치(110)는 메사부(115)에 의해서 서로 분리된다.

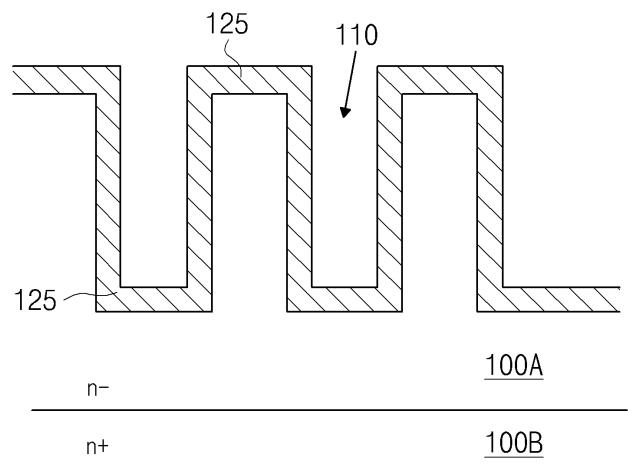

[0024] 도 6에서, 산화층(101)을 제거한 후에, 고온 산화 공정을 이용하여 게이트 산화층(125)을 형성한다. 게이트 산화층(125)(일부 예에서는 약 150 옹스트롬 내지 3000 옹스트롬의 두께를 가짐)을, 트렌치의 측벽(110A)과 바닥(110B)에, 그리고 메사부(115)의 표면에 형성한다(도 7 참조). 게이트 산화층(125)은, 산화 공정 대신에 CVD를 이용해서 형성할 수도 있다.

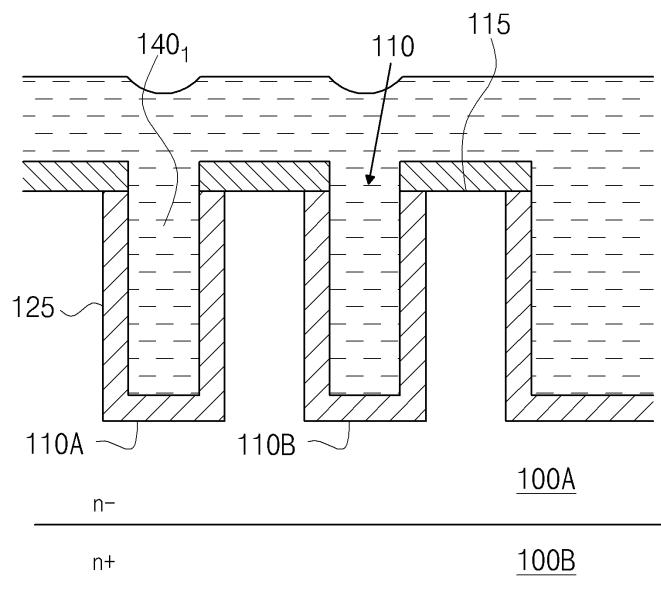

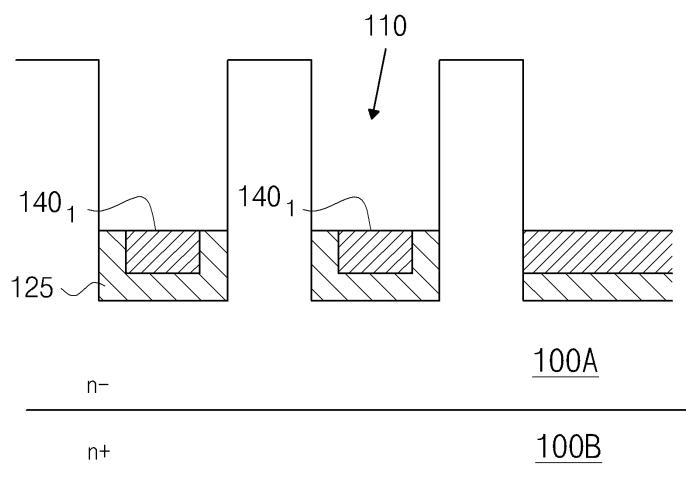

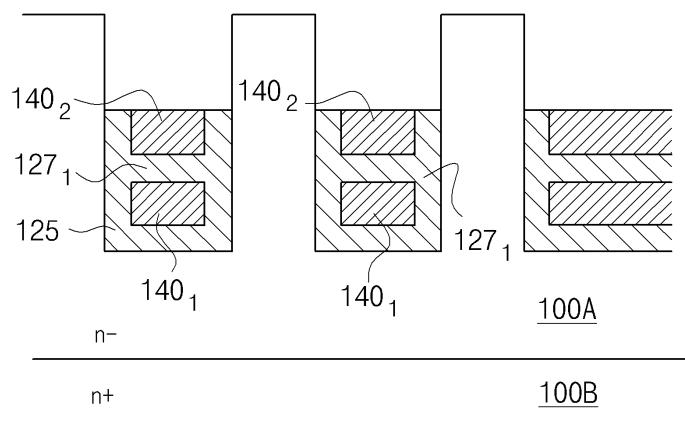

[0025] 다음으로, 도 7에 나타낸 것과 같이, 게이트 산화층(125) 위에 CVD를 이용하여 제1 도전층(140<sub>1</sub>)을 형성하여 트렌치(110)를 채운다. 제1 도전층(140<sub>1</sub>)은 임의의 금속, 도핑 폴리실리콘, 또는 도핑된 비정질 실리콘 등과 같은 재료로 형성할 수 있다. 하나의 특정 실시예에서 상기 제1 도전층(140<sub>1</sub>)은 알루미늄이다. 일부 실시예에서, 상기 제1 도전층(140<sub>1</sub>)은 약 0.1~5 미크론의 두께로 형성할 수 있다.

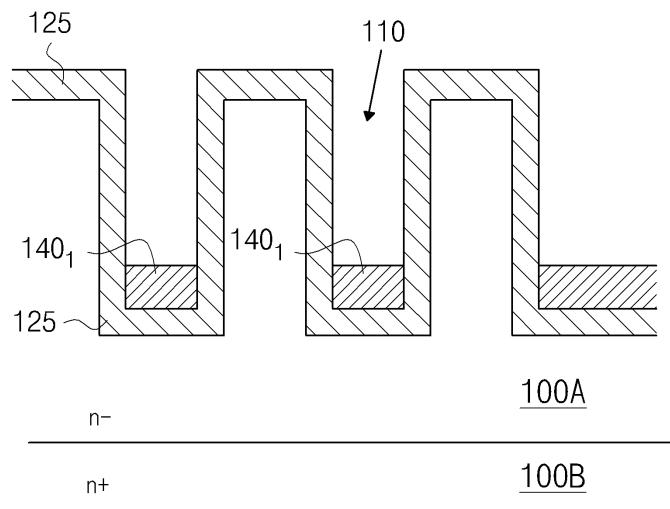

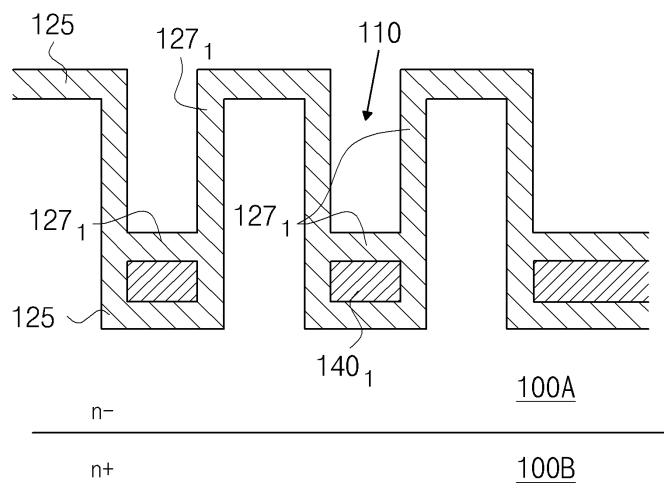

[0026] 이제 도 8을 참조하면, 이방성 에칭을 이용하여 트렌치(110) 내에서 제1 도전층(140<sub>1</sub>)의 잉여부분을 제거한다. 마찬가지로 도 9에서와 같이, 게이트 산화층(125)의 상부면이 대략적으로 제1 도전층(140<sub>1</sub>)의 상면과 동일 평면이 되도록 게이트 산화층(125)을 에칭한다. 이 에칭 공정 후, 도 10에서와 같이, 트렌치(110) 내에서 제1 유전층(127<sub>1</sub>)을 제1 도전층(140<sub>1</sub>) 위에 형성한다. 유전층(127)은 예를 들면 SiO<sub>2</sub>와 같은 임의의 적절한 재료로 형성할 수 있다. 그 다음에 제1 유전층(127<sub>1</sub>)을 이방성 에칭하여 제1 도전층(140<sub>1</sub>) 위에서 그 두께를 줄인다. 일부 실시예에서, 제1 유전층(127)은 0.2 내지 2 미크론의 두께까지 줄일 수 있다.

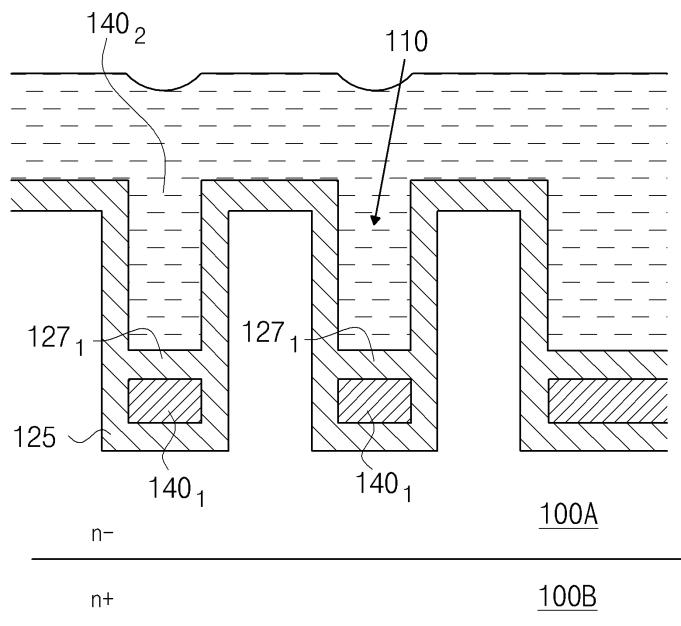

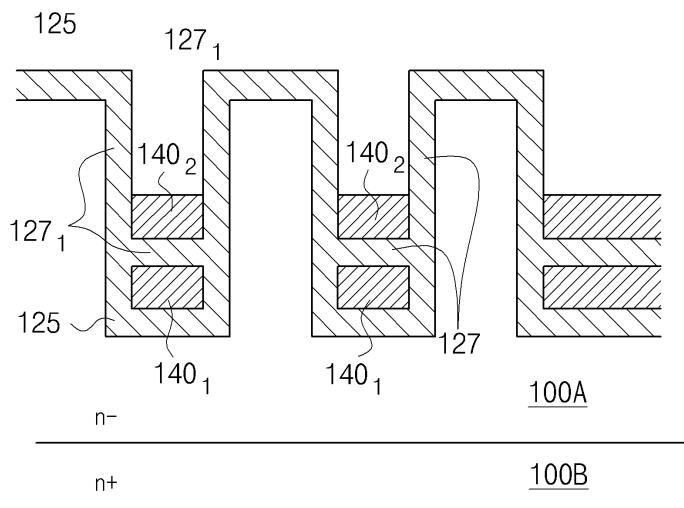

[0027] 제1 도전층(140<sub>1</sub>)은 도 2에 나타낸 제1 부유게이트의 역할을 한다. 도 7~9에 도시한 과정을, 형성하고자 할 각 부유게이트에 대해서 반복한다. 예를 들어, 도 11에서와 같이 제2 도전층(140<sub>2</sub>)을 제 유전층(127<sub>1</sub>) 위에 형성하고, 도 12에서와 같이 에칭한다. 그 다음 도 13과 같이(도 9와 마찬가지로), 제1 유전층(127<sub>1</sub>)의 상부면이 제2 도전층(140<sub>2</sub>)의 상부면과 대략 동일 평면이 되도록 에칭한다. 도 14는 다섯 개의 도전층(140<sub>1</sub>~140<sub>5</sub>)을 형성한 후의 결과물을 나타낸다.

[0028] 다음에, 도 15를 참조하면, 부유게이트를 형성한 후에, 스퍼터링 또는 다른 적절한 프로세스를 써서 메사부

(115) 상에 쇼트키 접촉 영역(115A)을 형성하기 위해 도전층(160)을 증착한다. 도전층(160)은 그 아래의 제1층(100A)과 쇼트키 다이오드를 형성할 수 있는 임의의 재료로 형성하면 된다. 예를 들어, 도전층(160)은 메탈 실리사이드 층일 수 있다.

[0029] 계속해서 도체를 증착 및 에칭하여 다이오드 양전극(165)을 형성하는데, 이때 양전극(165)은 도전층(160)과 같은 면적으로 연장 형성할 수 있다. 마찬가지로, 음전극(170)을 기재(100B)의 뒷면에 형성한다.

[0030] 이상의 예와 개시사항은 예시의 목적일 뿐 한정의 목적은 아니다. 이들 예와 설명으로부터 기술분야에서 통상의 지식을 가진 자(당업자)는 많은 변형물과 대체물을 얻을 수 있을 것이다. 이러한 모든 대체물과 변형물은 첨부된 청구범위 내에 포함되는 것이다. 당업자는 여기서 설명한 특정 실시예에 대한 다른 등가물이며, 또한 이러한 등가물은 첨부한 청구범위 내에 포함되는 것으로 의도된 것임을 알 것이다.

### 부호의 설명

[0031] 1: 실리콘 웨이퍼 2: 에피택시층 3: 도전 영역 4: 절연층 5: 실리사이드 6: 실리사이드 7: 양전극 금속층

8: 음전극 금속층 100: 반도체 기판 100A: 제1층(제1 에피택시층) 100B: 기판(반도체 기판, 기재) 101: 산화층 110: 트렌치 110A: 트렌치의 측벽 110B: 트렌치의 바닥 115: 메사부 115A: 쇼트키 접촉 영역 125: 게이트 산화층(절연층) 127: 절연층 127<sub>1</sub>: 제1 유전층 127<sub>2</sub>: 제2 유전층 140: 도전층(부유게이트) 140<sub>1</sub>: 제1 도전층 140<sub>1~140<sub>5</sub></sub>: 도전층 140<sub>2</sub>: 제2 도전층 160: 금속층(도전층) 165: 양전극 금속(양전극) 170: 음전극 전극(음전극)

### 도면

#### 도면1

## 도면2

## 도면3a

도면3b

도면 3c

도면4a

도면4b

도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13

도면14

도면15

【심사관 직권보정사항】

【직권보정 1】

【보정항목】 요약서

【보정세부항목】 청구항14, 줄1

【변경전】

상기 제8항 또는 제11항 내지 제13항 중 한 항의

【변경후】

제8항 또는 제11항 내지 제13항 중 어느 한 항의

【직권보정 2】

【보정항목】 청구범위

【보정세부항목】 청구항 8, 줄28

【변경전】

상기 도전총의

【변경후】

상기 금속총의

【직권보정 3】

【보정항목】 청구범위

【보정세부항목】 청구항 8, 줄14

【변경전】

화학기상증측(CVD)

【변경후】

화학기상증착(CVD)

【직권보정 4】

【보정항목】 청구범위

【보정세부항목】 청구항 8, 줄26

【변경전】

도전총을

【변경후】

상기 금속총을