(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5283759号

(P5283759)

(45) 発行日 平成25年9月4日(2013.9.4)

(24) 登録日 平成25年6月7日(2013.6.7)

(51) Int.Cl.

F 1

|                   |                  |            |         |

|-------------------|------------------|------------|---------|

| <b>G06F 1/32</b>  | <b>(2006.01)</b> | G06F 1/00  | 3 3 2 A |

| <b>G06F 1/00</b>  | <b>(2006.01)</b> | G06F 1/00  | 3 4 O   |

| <b>G06F 15/78</b> | <b>(2006.01)</b> | G06F 15/78 | 5 1 O P |

| <b>G06F 9/50</b>  | <b>(2006.01)</b> | G06F 15/78 | 5 1 O G |

|                   |                  | G06F 9/46  | 4 6 5 D |

請求項の数 12 (全 18 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2011-540918 (P2011-540918)  |

| (86) (22) 出願日 | 平成21年12月11日 (2009.12.11)      |

| (65) 公表番号     | 特表2012-511788 (P2012-511788A) |

| (43) 公表日      | 平成24年5月24日 (2012.5.24)        |

| (86) 國際出願番号   | PCT/US2009/067654             |

| (87) 國際公開番号   | W02010/068855                 |

| (87) 國際公開日    | 平成22年6月17日 (2010.6.17)        |

| 審査請求日         | 平成23年6月10日 (2011.6.10)        |

| (31) 優先権主張番号  | 12/333,063                    |

| (32) 優先日      | 平成20年12月11日 (2008.12.11)      |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                        |

|-----------|----------------------------------------------------------------------------------------|

| (73) 特許権者 | 507364838<br>クアルコム、インコーポレイテッド<br>アメリカ合衆国 カリフォルニア 921<br>21 サン・ディエゴ モアハウス・ド<br>ライブ 5775 |

| (74) 代理人  | 100108453<br>弁理士 村山 靖彦                                                                 |

| (74) 代理人  | 100163522<br>弁理士 黒田 晋平                                                                 |

| (72) 発明者  | マイケル・ウィリアム・モロー<br>アメリカ合衆国・カリフォルニア・921<br>21・サン・ディエゴ・モアハウス・ド<br>ライブ・5775                |

最終頁に続く

(54) 【発明の名称】非対称マルチプロセッサに対する適応型スレッドスケジューリングのための装置および方法

## (57) 【特許請求の範囲】

## 【請求項1】

システムのエネルギーを低減するための、複数のコアに対する適応型スレッドスケジューリングの方法であつて、

スレッドスケジューラで前記複数のコアに関連した漏れ電流情報を受け取る段階と、

システムのエネルギー使用を低減するために、前記漏れ電流情報を用いて前記複数のコアのうちの1つに対してスレッドをスケジュール設定する段階と

を有し、

複数の温度センサを読み取って、対応するコアに関連した動作温度を求める段階と、

前記動作温度および前記コアに関連した所定のプロセス定数に基づいて、前記複数のコアに関連した前記漏れ電流情報を算出する段階と

をさらに有することを特徴とする方法。

## 【請求項2】

前記漏れ電流情報が、次式によって算定され、

## 【数1】

$$I_{off} = e^{\left\{ \frac{-V_t}{S/\ln 10} \right\}}$$

ここで、 $I_{off}$ は漏れ電流情報であり、 $V_t$ は閾値電圧であり、 $S$ は次式による閾値下の電圧振幅であり、

## 【数2】

10

$$S = \frac{kT}{q} \ln(10) \left\{ 1 + \frac{C_D}{C_{OX}} \right\}$$

ここで、 $k$ はボルツマン定数であり、 $T$ はケルビン単位の動作温度であり、 $q$ は電気素量であり、 $C_D$ は空乏層容量であり、 $C_{OX}$ はゲート酸化物の静電容量であって、

$V_t$ 、 $k$ 、 $q$ 、 $C_D$ 、および $C_{OX}$ が所定のプロセス定数であることを特徴とする請求項1に記載の方法。

20

## 【請求項3】

前記複数のコアのうちの1つに対してスレッドをスケジュール設定する段階が、

前記複数のコアに関連した少なくとも1つの交差周波数を求める段階と、

より低い割り当てられた周波数において、前記複数のコアのうち、他のコアより漏れ電力が小さく高効率を有する1つのコアに対してスレッドをスケジュール設定する段階とを含むことを特徴とする請求項1に記載の方法。

## 【請求項4】

前記複数のコアのうちの1つに対してスレッドをスケジュール設定する段階が、

割り当てられるべき前記スレッドに割り当てられた周波数および電圧で、前記複数のコアの動的電力を算出する段階と、

30

前記漏れ電流情報に基づいて前記複数のコアの漏れ電力を求める段階と、

最低のコア電力を有するコアにスレッドを割り当てる段階とを含むことを特徴とする請求項1に記載の方法。

## 【請求項5】

特定の環境温度におけるセンサ読み取り値と予期されたセンサ値との比較に基づいて、前記複数のコアに関連した漏れ電流情報を提供するために利用されるオンチップセンサを較正する段階をさらに有することを特徴とする請求項1に記載の方法。

## 【請求項6】

現行用途の予期されたセンサ値には適合しないが、別用途の予期されたセンサ値に適合するセンサ読み取り値を求める段階と、

40

当該部分を前記別用途で用いるように組み合わせる段階とをさらに有することを特徴とする請求項5に記載の方法。

## 【請求項7】

前記特定の環境温度が、指定温度範囲内の温度の定数を見いだすために、前記コアの動作周波数をゼロヘルツに設定して複数の温度センサを読み取ることにより求められることを特徴とする請求項5に記載の方法。

## 【請求項8】

システムのエネルギーを低減するための、複数のコアに対する適応型スレッドスケジューリング用の装置であって、

50

漏れ電流情報を提供するための、前記複数のコアに関連した複数のセンサと、

適応型スレッドスケジューラを実行する複数のコアと

を具備し、

各コアは、コアに割り当てるべきタスクに応じて割り当てる動作周波数および電源電圧レベルを有し、

前記適応型スレッドスケジューラは、システムのエネルギー使用を低減するために、前記漏れ電流情報を用いて、前記複数のコアのうちの1つに対してスレッドをスケジュール設定し、

前記複数のセンサは、対応するコアに関連した動作温度を求め、前記動作温度および前記コアに関連した所定のプロセス定数に基づいて、前記複数のコアに関連した前記漏れ電流情報を算出する少なくとも1つの温度センサを含むことを特徴とする装置。

10

#### 【請求項9】

システムのエネルギーを低減するために、そのコンテンツが、非対称マルチプロセッサに、複数のマルチプロセッサのコアに対する適応型スレッドスケジューリングの方法を実行させるコンピュータ読み取り可能な記録媒体であって、

スレッドスケジューラで前記複数のコアに関連した漏れ電流情報を受け取る手順と、

システムのエネルギー使用を低減するために、前記漏れ電流情報を用いて前記複数のコアのうちの1つに対してスレッドをスケジュール設定する手順と

を実行させるためのプログラムを記録し、

前記プログラムは、

複数の温度センサを読み取って、対応するコアに関連した動作温度を求める手順と、

20

前記動作温度および前記コアに関連した所定のプロセス定数に基づいて、前記複数のコアに関連した前記漏れ電流情報を算出する手順と

をさらに実行させることを特徴とするコンピュータ読み取り可能な記録媒体。

#### 【請求項10】

前記複数のコアのうちの1つに対してスレッドをスケジュール設定する手順が、

割り当てるべき前記スレッドに割り当たられた周波数および電圧で、前記複数のコアの動的電力を算出する手順と、

前記漏れ電流情報に基づいて前記複数のコアの漏れ電力を求める手順と、

最低のコア電力を有するコアに前記スレッドを割り当てる手順と

を含むことを特徴とする請求項9に記載のコンピュータ読み取り可能な記録媒体。

30

#### 【請求項11】

前記プログラムが、特定の環境温度におけるセンサ読取り値と予期されたセンサ値との比較に基づいて、前記複数のコアに関連した漏れ電流情報を提供するために利用されるオンチップセンサを較正する手順をさらに実行させることを特徴とする請求項9に記載のコンピュータ読み取り可能な記録媒体。

#### 【請求項12】

前記特定の環境温度が、指定温度範囲内の温度の定数を見いだすために、前記コアの動作周波数をゼロヘルツに設定して複数の温度センサを読み取ることにより求められることを特徴とする請求項11に記載のコンピュータ読み取り可能な記録媒体。

#### 【発明の詳細な説明】

40

#### 【技術分野】

#### 【0001】

本開示は、一般に、少ない電力消費で必要な性能を達成するための、漏れ電流および動的電力に基づく、非対称マルチプロセッサシステムにおけるスレッドスケジューリングの適合のための技術に関する。

#### 【背景技術】

#### 【0002】

携帯電話、ラップトップコンピュータ、携帯情報端末(PDA)など多くの携帯用製品は、通信およびマルチメディアプログラムなどのプログラムを実行する処理システムを利用する。このような製品向けの処理システムは、シングルチップ上に構成された、例えば、複

50

数のプロセッサ、命令およびデータを蓄積するためのメモリ、コントローラ、通信用インターフェイスなどの周辺機器、および固定機能のロジックブロックを含むことができる。同時に、携帯用製品は、処理システムから高機能動作への対応を頻繁に要求される、バッテリー形式の限定されたエネルギー源を有する。バッテリー寿命を向上するために、可能なときには低い電力レベルでこれらの動作を遂行することが望まれる。多くのパーソナルコンピュータは、全体的なエネルギー消費を低減するために、低消費電流で高機能動作に対応するようにも開発されている。

#### 【0003】

処理システムの内部では、複数のプロセッサが、それぞれ異なり、ビデオ、グラフィックス、または通信処理など特定のシステムの機能またはプロセスに対して最適化され得る複数のプロセッサ間の選択的負荷バランスを可能にする非対称多重処理機構など、複数の別々の機構に構成され得る。処理機能は、選択されたプロセッサ上での実行向けにスケジュール設定された複数のスレッドまたはタスクに分配され得る。スレッドは、別のスレッドと並行して動作することができる、個々にスケジュール設定可能な最小のプロセスまたは一連の命令と考えられる。本発明の文脈では、スレッドとタスクとは互換性があるよう用いることができる。タスクまたはスレッドは、例えばシステム機能に関連した要求性能を満たすために、オペレーティングシステム(OS)のスケジューラによってプロセッサに一般に割り当てられる副機能であり得る。タスクの実行に関連する電力は、周波数と、スイッチングキャパシタンスと、供給電圧の2乗との関数であるので、電力使用を低減するには、一般にこれらの変数の少なくとも1つを減少させる必要がある。電力使用をより十分に最適化するために、多くの処理システムが、電力を使用する1つまたは複数の回路領域における周波数および動作電圧を制御する。ビデオ、グラフィックス、および通信など、携帯機器で動作している様々な機能の必要とする性質により、複数のプロセッサが、製品の要件を満たすためにギガヘルツの周波数で動作する必要があり得る。処理システムに対する機能的要求が多種多様なので、動作周波数は、一般に既存の動作環境に適合される。同様に、電圧を低下させると、電力だけでなく影響を受けるロジックデバイスおよびメモリデバイスの動作周波数にも影響が及び、次いで周波数の制御状況が影響を受ける。

#### 【0004】

それぞれの新技術の開発に伴って回路密度が増加するので、アイドルまたはスタンバイ状態の期間中の電力損失も増加している。回路密度の増加に伴って回路の漏れ電流も増加する傾向があり、大幅な電力損失のなおいっそう大きな原因になっている。より高いクロック周波数を可能にする、密度増加とより短いデバイス遅延とを達成するために、一般に内部回路デバイスの閾値電圧が低下される。閾値電圧を低下させると、一般に漏れ電流が増加し、漏れ電流は、プロセスの変化および温度による影響も受ける。高密度チップのエネルギー消費のかなりの部分が漏れ電流に起因することがある。

#### 【0005】

オペレーティングシステムのスケジューラレベルでは、多重処理システムにおけるタスク割当ては、通常は公称PVT環境と称される、一貫したプロセス特性(P)で製造された、一定の公称動作電圧(V)および公称温度(T)の範囲内で動作するチップを有する公称の動作環境の範囲内でさえ、困難な問題である。携帯機器は、別々のプロセスで製造された複数のチップを使用することがあり、また、チップ内部およびチップ間でのプロセス特性の広範な変化、制御可能であり得る別々の動作電圧の使用、および周囲温度の幅広い変化を経験する可能性があるので、タスク割当て問題は、携帯機器の性質によってさらに困難になる。PVTの変化は、一般に、動的および静的な漏れ電力を含めてチップの電力利用に劇的な影響を及ぼす。

#### 【先行技術文献】

#### 【非特許文献】

#### 【0006】

【非特許文献1】D. H. Kim, K. Roy, S. Hsu, R. K. Krishnamurthy, and S. Borkar, "An On-Die CMOS Leakage Current Sensor for Measuring Process Variation in Sub-90nm

10

20

30

40

50

"m generations", IEEE 2004 Symposium on VLSI Circuits digest of technical papers, pages 250 and 251

【非特許文献 2】L. T. Clark, M. Morrow, and W. Brown, "Reverse-Body Bias and Supply Collapse for Low Effective Standby Power", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 12, No. 9, September 2004

#### 【発明の概要】

#### 【課題を解決するための手段】

#### 【0007】

本発明の一実施態様は、システムのエネルギーを低減するために、複数のコアに対する適応型スレッドスケジューリングの方法を提供する。スレッドスケジューラは、複数のコアに関連した漏れ電流情報を受け取る。漏れ電流情報は、システムのエネルギー使用を低減するために、複数のコアのうちの1つに対してスレッドをスケジュール設定するように用いられる。

#### 【0008】

本発明の別実施態様は、システムのエネルギーを低減するために、複数のコアに対する適応型スレッドスケジューリング用の装置を提供する。複数のコアに関連した複数のセンサが、漏れ電流情報を提供する。複数のコアが、適応型スレッドスケジューラを実行し、各コアが、コアに割り当てられるべきタスクに応じて割り当てられる動作周波数および電源電圧レベルを有する。適応型スレッドスケジューラは、システムのエネルギー使用を低減するために、漏れ電流情報を用いて、複数のコアのうちの1つに対してスレッドをスケジュール設定する。

#### 【0009】

本発明の別の実施態様は、システムのエネルギーを低減するために、そのコンテンツが、非対称マルチプロセッサに、複数のマルチプロセッサのコアに対する適応型スレッドスケジューリングの方法を実行させるコンピュータ読み取り可能な記録媒体を提供する。スレッドスケジューラは、複数のコアに関連した漏れ電流情報を受け取る。漏れ電流情報は、システムのエネルギー使用を低減するために、複数のコアのうちの1つに対してスレッドをスケジュール設定するために用いられる。

#### 【0010】

本発明の他の実施態様は、本発明の様々な実施形態が具体例として示されて説明される以下の詳細な説明から、当業者には容易に明らかになるであろう。本発明が、他の様々な実施形態で実施され得て、そのいくつかの詳細は、様々な他の点において、すべて本発明から逸脱することなく変更可能であることが理解されよう。したがって、図面および詳細な説明は、本来限定的ではなく例示的なものであると見なされるべきである。

#### 【図面の簡単な説明】

#### 【0011】

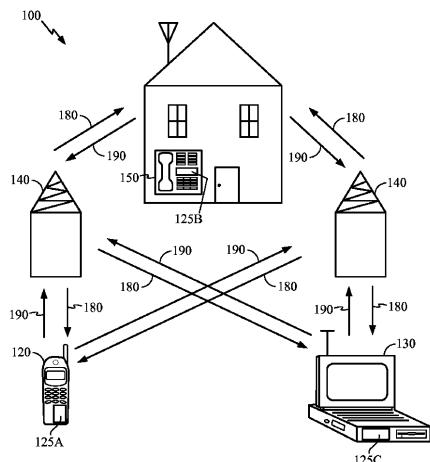

【図1】例示的な無線通信システムを示す図である。

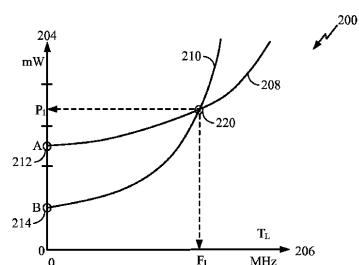

【図2A】例示的なデュアルコアプロセッサの、低温での、特定のプロセス(P)、電圧(V)、温度(T)のPVT環境の実例となる電力対動作周波数を示すグラフである。

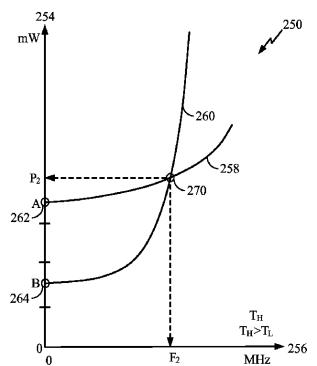

【図2B】図2Aのデュアルコアプロセッサの、高温でのPVT環境の実例となる電力対動作周波数を示すグラフである。

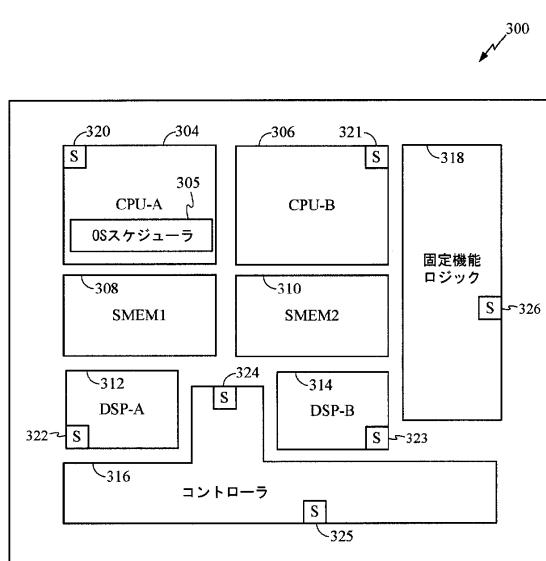

【図3】チップ上の例示的な非対称マルチプロセッサシステムを示すブロック図である。

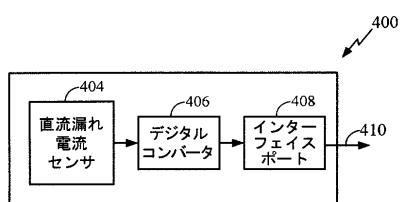

【図4A】例示的な第1センサ回路を示すブロック図である。

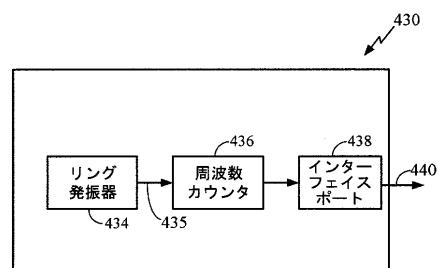

【図4B】例示的な第2センサ回路を示すブロック図である。

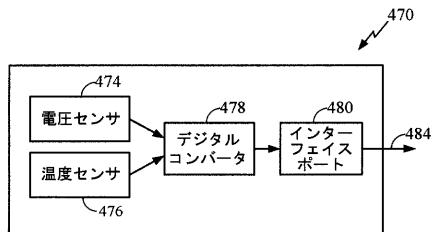

【図4C】例示的な第3センサ回路を示すブロック図である。

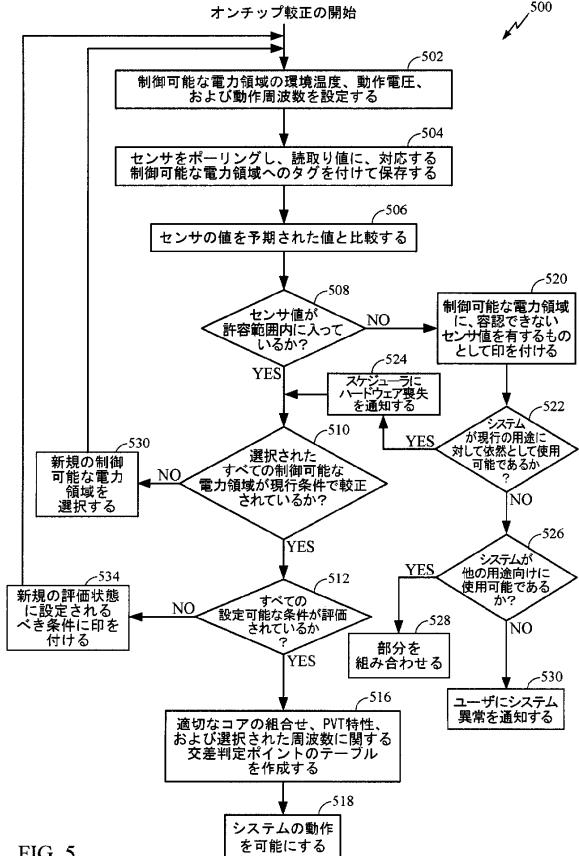

【図5】例示的なオンチップセンサの較正プロセスの流れ図である。

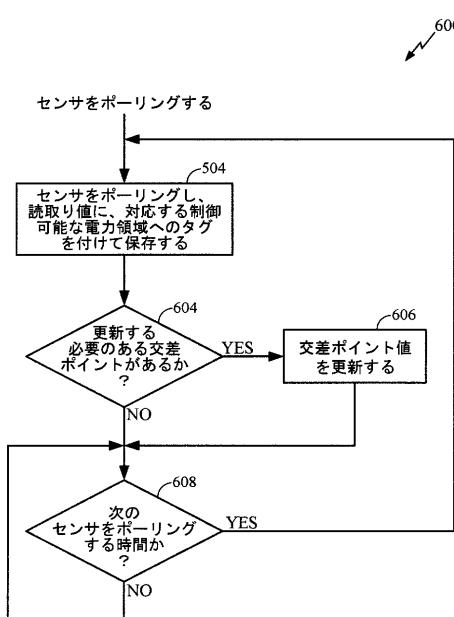

【図6A】例示的なセンサポーリングのバックグラウンド処理の流れ図である。

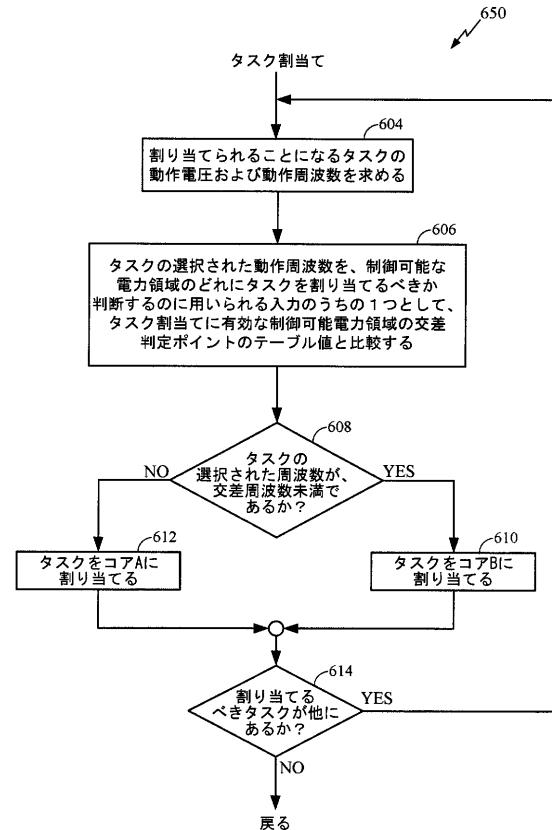

【図6B】漏れ電流情報に部分的に基づいた例示的な第1適応型スレッドスケジューリングプロセスの流れ図である。

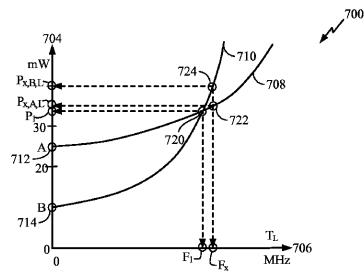

【図7A】例示的なデュアルコアプロセッサの、低温での、プロセス(P)、電圧(V)、温度

10

20

30

40

50

(T)のPVT環境の実例となる電力対動作周波数を示すグラフである。

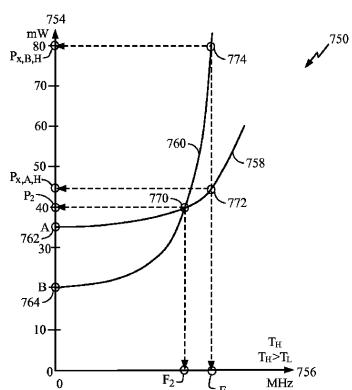

【図7B】図7Aの例示的なデュアルコアプロセッサの、高温でのPVT環境の実例となる電力対動作周波数を示すグラフである。

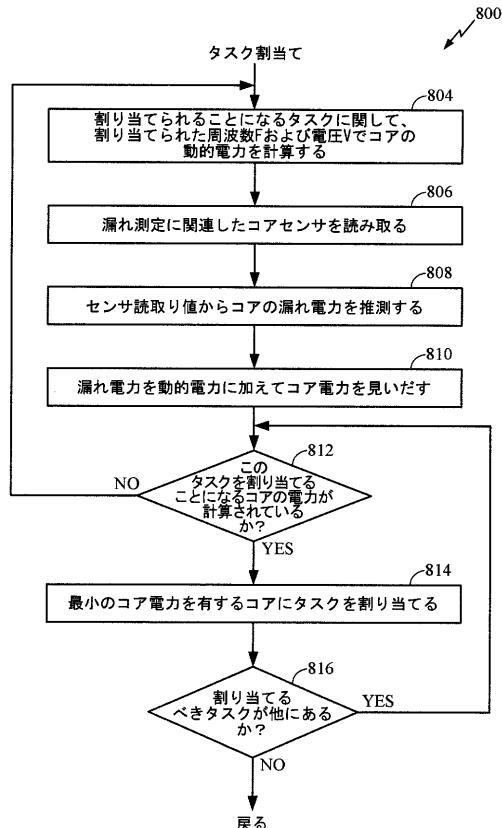

【図8】漏れ電流情報に部分的に基づいた例示的な第2適応型スレッドスケジューリングプロセスの流れ図である。

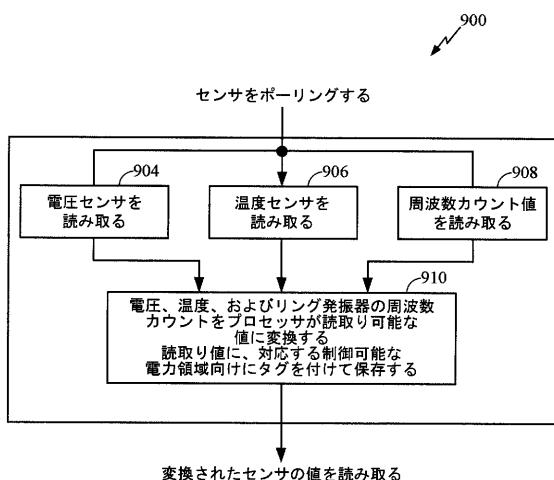

【図9】様々なセンサ出力から静的漏れ電流および動的電力を求めるための例示的なセンサポーリングプロセスの流れ図である。

**【発明を実施するための形態】**

**【0012】**

以下で添付の図面に関連して示される詳細な説明は、本発明の様々な例示的な実施形態の説明を意図したものであり、本発明が実施され得る唯一の実施形態を表すことを意図していない。詳細な説明は、本発明に対する十分な理解をもたらすために特定の詳細を含んでいる。しかしながら、本発明が、これらの特定の詳細なしで実施され得ることが当業者には明らかであろう。いくつかの例では、本発明の概念が不明瞭にならないようにするために、周知の構造体および構成要素がブロック図の形態で示されている。10

**【0013】**

本発明の教示による動作を実行するためのコンピュータプログラムコードすなわち「プログラムコード」は、C、C++、JAVA(登録商標)、Smalltalk、JavaScript(登録商標)、Visual Basic(登録商標)、TSQL、Perlなどの高級プログラミング言語、または様々な他のプログラミング言語で記述することができる。ターゲットプロセッサのアーキテクチャ向けのプログラムも、固有のアセンブリ言語で直接記述することができる。固有のアセンブリプログラムは、マシンレベルのバイナリ命令の命令ニーモニック表現を用いる。本明細書で用いられるプログラムコードすなわちコンピュータ読み取り可能な記録媒体に記録されたプログラムは、そのフォーマットがプロセッサによって理解され得るオブジェクトコードなどの機械語コードを指す。20

**【0014】**

図1は、本発明の一実施形態が有利に用いられ得る例示的な無線通信システム100を示す。説明のために、図1は、3つの遠隔装置120、130、150ならびに2つのベースステーション140を示す。図1は、ベースステーション140から遠隔装置120、130、150への順方向リンク信号180、ならびに遠隔装置120、130、150からベースステーション140への逆方向リンク信号190を示す。当然ながら、同様の無線通信システムは、さらに多くの遠隔装置およびベースステーションを有し得る。遠隔装置120、130、150は、構成要素125A、125B、125Cで表されるように、本発明を実施するように適合されたハードウェア構成要素、ソフトウェア構成要素、またはその両方を含む。例えば、構成要素125A、125B、125Cは、以下でさらに論じられるように、センサ、プロセッサ、および適応型スレッドスケジューリングソフトウェアを含むことができる。30

**【0015】**

図1で、遠隔装置120は移動電話として示され、遠隔装置130はポータブルコンピュータとして示され、遠隔装置150は無線ローカルループシステム中の固定ロケーション遠隔装置として示されている。一例として、遠隔装置は、あるいは携帯電話、ポケットベル、携帯用無線電話機、携帯用パーソナルコミュニケーションシステム(PCS)ユニット、携帯情報端末などの携帯用データユニット、またはメータ読み取り装置などの固定ロケーションデータユニットであってよい。図1は、本開示の教示による遠隔装置を示しているが、本開示は、示された例示的ユニットに限定されない。本発明の実施形態は、以下でさらに詳細に説明されるように、2つ以上のプロセッサならびに静的漏れ電流および動的電力を求めることができるセンサを有する任意のデバイスに適切に用いることができる。40

**【0016】**

図2Aは、例示的なデュアルコアプロセッサの、低温( $T_L$ )での、プロセス(P)、電圧(V)、温度(T)のPVT<sub>L</sub>環境の実例となる、ミリワット(mW)単位の電力204対メガヘルツ(MHz)単位の動作周波数206のグラフ200を示す。コアAの動的電力対周波数(PvF)曲線208およびコアB

10

20

30

40

50

のPvF曲線210は、それぞれ電力ポイント212および電力ポイント214で始まる。2つの電力ポイント212, 214は、PVT<sub>L</sub>環境における、それぞれコアAおよびコアBの静的漏れ電力である。具体的には、コアAは、電力ポイント212で示されるように、コアBより漏れ電力が大きいが、周波数F<sub>1</sub>を上回る高周波での動作あたりの動的電力の使用がコアBを下回る。コアBは、電力ポイント214で示されるように、コアAと比較して、F<sub>1</sub>より低い周波数で漏れ電力がより小さく、より効率的である。交差ポイント(P<sub>1</sub>, F<sub>1</sub>)220は、デュアルコアに対する動作周波数およびPVT環境に応じてコアAまたはコアBへタスクを割り当てることが考えられる交差判定ポイントを表す。

#### 【 0 0 1 7 】

図2Bは、図2Aのデュアルコアプロセッサの、高温(T<sub>H</sub>)でのPVT<sub>H</sub>環境の実例となる電力25 10 4対動作周波数256を示すグラフ250である。コアAの動的PvF曲線258およびコアBの動的PvF曲線260は、それぞれ電力ポイント262および電力ポイント264で始まる。2つの電力ポイント262, 264は、PVT<sub>H</sub>環境における、それぞれコアAおよびコアBの静的漏れ電力であり、T<sub>H</sub>>T<sub>L</sub>である。具体的には、コアAは、電力ポイント262で示されるように、コアBより漏れ電力が大きいが、周波数F<sub>2</sub>を上回る高周波での動作あたりの動的電力の使用がコアBを下回る。コアBは、電力ポイント264で示されるように、コアAと比較して、F<sub>2</sub>より低い周波数で漏れ電力がより小さく、より効率的である。交差ポイント(P<sub>2</sub>, F<sub>2</sub>)270は、デュアルコアに対する動作周波数およびPVT環境に応じてコアAまたはコアBへタスクを割り当てることが考えられる別の判定ポイントを表す。

#### 【 0 0 1 8 】

グラフ200とグラフ250との比較は、グラフ250に関連したより高い温度によって、交差ポイント(P<sub>2</sub>, F<sub>2</sub>)270は、交差ポイント(P<sub>1</sub>, F<sub>1</sub>)220より、電力レベルが高く(P<sub>2</sub>>P<sub>1</sub>)、周波数が低い(F<sub>2</sub><F<sub>1</sub>)ことを示す。2つのグラフ200, 250によって特徴付けられた例示的なデュアルコアプロセッサに関して、交差周波数F<sub>1</sub>または交差周波数F<sub>2</sub>より低い選択された動作周波数を有するタスクをコアBに割り当てる、選択されたタスクの動作周波数が交差ポイントの周波数を上回るタスクをコアAに割り当てるにより、一般に、より低い電力使用が達成されることになる。

#### 【 0 0 1 9 】

図2Aおよび図2Bで評価されるデュアルコアは、2つの別々の製造プロセス向けに設計することができる。例えば、コアAは、主として高機能を達成する低電圧閾値(Io-Vt)トランジスタプロセスを用いて、漏れ電流の増加という犠牲を払って製造されてよい。コアBは、主として漏れ電流が小さい優れた性能を達成するために、高電圧閾値(hi-Vt)トランジスタプロセスを用いて製造されてよい。また、2つのコアのどちらかは、例えばタイミングがクリティカルパスである回路にIo-Vtトランジスタを用いる、hi-VtトランジスタとIo-Vtトランジスタの組合せを用いて製造されてよい。本発明の技術は、本発明の方式が現在するかまたは将来的に適用可能な、上記で扱った製造設計ならびに他の製造設計のうち任意のものを含む1つまたは複数のプロセスを用いて製造されたコアに対して適用可能である。

#### 【 0 0 2 0 】

図3は、チップ(SoC)300上の例示的な非対称マルチプロセッサシステムを示す。図3に示された特定の構成は例示的なものであり、本発明の技術は、図3に示されたものよりある程度周波数制御および電圧制御が可能な電力領域を有する複数のチップから成る他のシステム構成に適用可能であることに留意されたい。例示的な非対称マルチプロセッサSoC 30 30 0は、中央処理装置A(CPU-A)304、CPU-B 306、共有メモリ1(SMEM-1)308、SMEM-2 310、デジタル信号プロセッサA(DSP-A)312、DSP-B 314、コントローラ316、固定機能ロジック318、および複数のセンサ320～326を含む。センサ320～326は、CPU-A 304、CPU-B 306、DSP-A 312、およびDSP-B 314などの様々なコアに対するタスク割当てに影響を及ぼし得る条件を監視し、例えば非対称マルチプロセッサSoC 300の交差ポイントの情報を応答してコントローラ316および固定機能ロジック318の動作に影響を及ぼすように配置される。オペレーティングシステム(OS)スケジューラ305などのOSスケジューラは、マルチプロセッサシ 40 50

システムのプロセッサの1つまたは複数に対して働くことができる。このスケジューラは、以下でより詳細に説明されるように、PVT動作空間にわたって、マルチプロセッサシステムの相対的電力および性能曲線に基づいて、プロセッサ上で実行するべきタスクをスケジュール設定することになる。

#### 【0021】

図4Aは、例示的な第1センサ回路400を示すブロック図である。第1センサ回路400は、直流漏れ電流センサ404、デジタルコンバータ406、および漏れ電流値を出力端410に出力するインターフェイスポート408を含む。様々なタイプの漏れ電流センサを、直流漏れ電流センサ404に用いることができる。そのような漏れ検出回路は、文献「An On-Die CMOS Leakage Current Sensor for Measuring Process Variation in Sub-90nm generations」(非特許文献1)に説明されており、これを参照によって本明細書に組み込む。使用される漏れ電流センサのタイプに基づいて、適切なデジタルコンバータがデジタルコンバータ406として選択される。以下でより詳細に説明されるように、出力端410の漏れ電流値も較正プロセスに利用される。漏れ電流値は、電圧制御および周波数制御が可能な特定の電力領域が、その制御可能な電力領域に関して周波数がゼロヘルツ(Hz)でアイドル状態または低電力状態であるときなどの、チップの動作中に監視され得る。

#### 【0022】

図4Bは、例示的な第2センサ回路430を示すブロック図である。第2センサ回路430は、リング発振器434、周波数カウンタ436、インターフェイスポート438、および出力端440を含む。リング発振器434は、関連する制御可能な電力領域の漏れ電流を求めるために、関連する制御可能な電力領域で使用されているトランジスタを使用して構成されてよい。例えば、リング発振器は、主にCPU-A 304で使用され得る高閾値電圧トランジスタで構成されてよく、CPU-A 304に関連した漏れ電流が求められ得る周波数で動作する。リング発振器の出力435は、漏れ電流を表す周波数カウントを求めるために一定の測定期間を通じて周波数カウンタ436でカウントされる振動波形から成る。周波数カウントは、インターフェイスポート438によって出力に選択される。

#### 【0023】

別の実施形態では、コアで使用されるトランジスタのタイプに基づいて複数のリング発振器が利用されてよい。例えば、低閾値電圧トランジスタおよび高閾値電圧トランジスタの組合せを用いて構成されたコアでは、2つのリング発振器が利用され得る。一方のリング発振器が低閾値電圧トランジスタで構成され、他方のリング発振器が高閾値電圧トランジスタで構成される。両方のリング発振器が、測定して読み取られることになり、関連するコアの漏れ電流情報をもたらす。別の実施形態では、第2センサ回路430の設計が全体的に複写され得るが、漏れ電流情報を求めるために利用されたものとは異なるトランジスタの組を用いて構成され、プロセス変化を測定するように使用されてよい。

#### 【0024】

図4Cは、例示的な第3センサ回路470を示すブロック図である。第3センサ回路470は、電圧センサ474、温度センサ476、デジタルコンバータ478、インターフェイスポート480、および出力端484を含む。電圧センサ474および温度センサ476は、それぞれが、例えばCPU-A 304などの制御可能な電力領域の電圧および温度にそれぞれ関連した電圧レベルを生成することができる。両センサの出力電圧レベルは、アナログデジタルコンバータを使用するものなどのデジタルコンバータ478でデジタル形式に変換され、測定したセンサおよびその位置のタイプに従ってタグを付けられてよい。次いで、変換された電圧値および温度値が、インターフェイスポート440によって出力に選択される。

#### 【0025】

図5は、オンチップセンサの較正プロセス500の流れ図である。プロセス500は、ソフトウェアプロシージャまたはマルチプロセッサOSのフレームワーク内で動作するプロシージャで実施されてよく、これらは、試験する構成における環境の温度を調整するように出力も制御することができる。プロセス500は、較正されているチップの外部の動作環境を設定するステップと、オンチップセンサの値を読み取るステップと、読み取られたセンサ値

10

20

30

40

50

を評価するステップと、交差判定ポイントを求めるステップと、チップまたはシステムが所期の用途に対して動作可能かどうか判断するステップとを含む。プロセス500は、環境温度が制御されない可能性がある製品システムのテスト中に実行されてもよい。この場合、較正プロセスは、試験時間に、コアの選択可能な動作周波数のすべてがゼロヘルツに設定された状態で、複数の温度センサから現在の温度をサンプリングし、許容範囲内にある読み取り値間の平均を見いだすために複数の温度センサ読み取り値を比較し、それに応じて較正プロセスを調整する。また、これらのセンサは、後のシステム使用で起こる製品の動作条件の期間中に得られた新規の読み取り値に基づいて、再度較正されてよい。

#### 【 0 0 2 6 】

ブロック502で、初期の環境温度、動作電圧および動作周波数が、図3のCPUA 304などの制御可能な電力領域向けに設定される。例えば、図2Aの電力ポイント212に関連づけられるものなど、漏れ電流の静的電力値を求めるために、低温、低い動作電圧およびゼロ周波数が設定されてよい。ブロック504で、1つまたは複数のセンサがポーリングされ、読み取り値は、測定されたセンサのタイプおよびテスト中の制御可能な電力領域に従ってタグを付けられ、以下でより詳細に説明されるように、後の評価のために保存される。例えば、図3のセンサ320が読み取られ、タグを付けられて、読み取り値が保存される。ブロック506で、センサ値は、期待値、例えば最小の期待値および最大の期待値と比較される。判定ブロック508で、センサ値が許容範囲内にあるかどうか判断される。センサ値が許容範囲内にある場合、プロセス500は判定ブロック510へ進む。判定ブロック510で、選択された制御可能な電力領域がすべて較正されたかどうか判断される。選択された制御可能な電力領域がすべて較正されている場合、プロセス500は判定ブロック512へ進む。判定ブロック512で、設定可能な条件がすべて評価されているかどうか判断される。設定可能な条件がすべて評価されている場合、センサ較正プロセスはブロック516へ進む。ブロック516で、交差判定ポイントの1つまたは複数のテーブルが、適切なコアの組合せ、PVT特性、および選択された周波数に関して作成される。ブロック518で、センサ較正プロセスが終了して、システムの動作が可能になり得る。動作可能になった後に、図3のOSスケジューラ305は、以下でより詳細に説明されるように、様々な較正されたセンサ読み取り値を用いて様々なコアに対してスレッドをスケジュール設定することができる。

#### 【 0 0 2 7 】

判定ブロック508に戻って、センサ値が許容範囲内にない場合、次いで、プロセス500は判定ブロック520へ進む。ブロック520で、この制御可能な電力領域は、1つまたは複数の容認できないセンサ値を有するものとして印を付けられる。判定ブロック522で、システムが現行の用途に対して依然として使用可能であるかどうか判断される。システムが現行の用途に対して依然として使用可能な場合、プロセス500はブロック524へ進む。ブロック524で、OSスケジューラ305は、ハードウェア喪失の通知を受ける。例えば、フォールトトレラントシステムでは、1つのCPUがオフラインであって電源が切られていることが、システム動作に関して許容され得る。システムが現行の用途に対して使用不可能な場合、プロセス500はブロック526へ進む。判定ブロック526で、システムが、例えばバッテリー動作を必要としないデスクトップ型など他の用途向けに使用可能であるかどうか判断される。システムが他の用途向けに使用可能な場合、プロセス500はブロック528へ進む。ブロック528で、その部分が、センサ値に従って組合せ(binning)向けに印を付けられる。例えば、諸部分は、センサによってもたらされた漏れ電流情報の範囲に従って組み合わされてよい。システムが他の用途向けに使用可能でない場合、プロセス500はブロック530へ進む。ブロック530で、ユーザは、システム異常の通知を受ける。

#### 【 0 0 2 8 】

判定ブロック510に戻って、すべての選択された制御可能な電力領域が較正済みになつてはいないと判断された場合、プロセス500は判定ブロック530へ進む。ブロック530で、CPU-B 306など新規の制御可能な電力領域が、図3のセンサ321のセンサ較正に選択される。プロセス500は、必要に応じて、新規の制御可能な電力領域向けの環境温度、動作電圧、および動作周波数を、初期の制御可能な電力領域向けのセンサの較正で利用されたのと同

10

20

30

40

50

等の設定に調整するために、ブロック502へ戻る。

**【0029】**

判定ブロック512に戻って、すべての設定可能な条件が評価済みになってはいないと判断された場合、プロセス500は判定ブロック534へ進む。ブロック534で、新規の評価状態に設定されるべき条件に印が付けられ、プロセス500は、新規の条件を設定するためにブロック502へ戻る。

**【0030】**

図6Aは、例示的なセンサーリングのバックグラウンド処理600の流れ図である。処理600は、マルチプロセッサOSのフレームワーク内で動作する1つまたは複数のソフトウェアプロシージャで実施され得る。システムの動作中、センサは、例えば特定の時間周期で、または様々な制御可能な電力領域へのタスクの割当てに先立って、ポーリングされる。ブロック504で、センサがポーリングされ、その読み取り値は、対応する制御可能な電力領域向けにタグを付けられ、後の評価のために保存される。判定ブロック604で、何らかの交差ポイントを更新する必要があるかどうか判断される。例えば、携帯機器の場合、環境温度が、図2Aのグラフ200および図2Bのグラフ250で示されたように急速に変化することがあって交差ポイントに影響を及ぼす。交差ポイントを更新する必要がある場合、バックグラウンド処理600はブロック606へ進む。ブロック606で、1つまたは複数の適切な交差ポイントが更新される。判定ブロック604に戻って、交差ポイントを更新する必要がない場合、次いで、バックグラウンド処理600は判定ブロック608へ進む。判定ブロック608で、次のセンサをポーリングする時間かどうか判断される。次のセンサをポーリングする時間である場合、バックグラウンド処理600はブロック504へ進む。次のセンサをポーリングする時間でない場合、バックグラウンド処理600はセンサのポーリング時間になるまで待つ。バックグラウンド処理600が動作中である一方で、他のシステム動作は製品の動作要件を満たし続ける。

**【0031】**

図6Bは、部分的に漏れ電流情報に基づいた例示的な第1適応型スレッドスケジューリングプロセス650の流れ図である。プロセス650は、図3のOSスケジューラ305などのマルチプロセッサOSのフレームワーク内で動作する1つまたは複数のソフトウェアプロシージャで実施され得る。プロセス650は、タスクが、図3のCPU-A 304およびCPU-B 306など2つのプロセッサコアのうちの1つに割り当てられるときの例示的場合に関して示されている。マルチプロセッサOSスケジューラまたは同様のものが、タスクを割り当てるべきであることを判断する。ブロック604で、タスクを実行するための適切な動作電圧および動作周波数を求めるために、割り当たるべきタスクが評価される。ブロック606で、タスクの選択された動作周波数が、制御可能な電力領域のいずれにタスクを割り当てるべきか判断するのに用いられる入力のうちの1つとして、タスク割当てに有効な制御可能電力領域の交差判定ポイントの値と比較される。ブロック608で、タスクの選択された周波数が、適切な交差周波数未満であるかどうか判断される。タスクの周波数が適切な交差周波数を下回る場合、プロセス650はブロック610へ進む。ブロック610で、タスクは、CPU-B 306など第1のコアの制御可能な電力領域に割り当たられる。タスクの周波数が、適切な交差周波数以上である場合、プロセス650はブロック612へ進む。ブロック612で、タスクは、CPU-A 304など第2のコアの制御可能な電力領域に割り当たられる。判定ブロック614で、割り当たるべき他のタスクがあるかどうか判断される。割り当たるべきタスクがさらにある場合、プロセス650はブロック604へ戻る。割り当たるべきタスクがない場合、プロセス650は、これを呼び出したルーチンへ戻る。この適応型スレッドスケジューリングプロセスは、2つを上回るコアへ拡張可能である。3つ以上の制御可能な電力領域の場合、タスクの割当を判断するのに複数の交差ポイントが評価されてよい。

**【0032】**

図7Aは、例示的なデュアルコアプロセッサの、低温( $T_L$ )での、プロセス(P)、電圧(V)、温度(T)のPVT<sub>L</sub>環境の実例となる、ミリワット(mW)単位の電力704対メガヘルツ(MHz)単位の動作周波数706のグラフ700を示す。コアAの動的電力対周波数(PvF)曲線708およびコアB

10

20

30

40

50

のPvF曲線710は、それぞれ電力ポイント712および電力ポイント714で始まる。2つの電力ポイント712, 714は、特定のPVT<sub>L</sub>条件における、それぞれコアAおよびコアBの静的漏れ電力である。具体的には、コアAは、電力ポイント712で示されるようにコアBより漏れ電力が大きく約25mWであるが、周波数F<sub>1</sub>を上回る高周波数における動作あたりの動的電力の使用がコアBを下回る。コアBは、コアAと比較して、F<sub>1</sub>より低い周波数で、電力ポイント714で示されるように約10mWと漏れ電力がより小さく、より効率的である。交差ポイント(P<sub>1</sub>, F<sub>1</sub>)720は、デュアルコアの動作周波数およびPVT環境に応じてコアAまたはコアBへタスクを割り当てることが考えられ得る交差ポイントを表す。

### 【0033】

図7Bは、図7Aの例示的なデュアルコアプロセッサの、高温(T<sub>H</sub>)でのPVT<sub>H</sub>環境の実例となる電力754対動作周波数756を示すグラフ750である。コアAの動的PvF曲線758およびコアBのPvF曲線760は、それぞれ電力ポイント762および電力ポイント764で始まる。2つの電力ポイント762, 764は、T<sub>H</sub>>T<sub>L</sub>であるPVT<sub>H</sub>条件における、それぞれコアAおよびコアBの静的漏れ電力である。具体的には、コアAは、電力ポイント762で示されるように、約35mWの漏れ電力はコアBのものより大きいが、周波数F<sub>2</sub>を上回る高周波数での動作あたりの動的電力の使用がコアBを下回る。コアBは、電力ポイント764で示されるように漏れ電力が約20mWで、コアAと比較して、F<sub>2</sub>より低い周波数でより小さく、より効率的である。交差ポイント(P<sub>2</sub>, F<sub>2</sub>)770は、デュアルコアに対する動作周波数およびPVT環境に応じて、コアAまたはコアBへタスクを割り当てることが考えられ得る別の判定ポイントを表す。

### 【0034】

一実施例として、図7Aに示されるような特性を有する2つのプロセッサコアのうちの1つに対して、特定のタスクが割り当てられることになる。特定のタスクは、要件を満たすためにどちらのコアに対しても周波数x(F<sub>X</sub>)を必要とする。周波数F<sub>X</sub>は、両方のコアに対して最小のコア電圧源を必要とする。図7Aに示されるように、動作温度T<sub>L</sub>および動作周波数F<sub>X</sub>で、コアAは、ポイント(P<sub>X, A, L</sub>, F<sub>X</sub>)722に関連した動的電力P<sub>X, A, L</sub>を示すことになり、コアBは、ポイント(P<sub>X, B, L</sub>, F<sub>X</sub>)724に関連した動的電力P<sub>X, B, L</sub>を示すことになる。この特定のタスクに関して、コアAの電力は、漏れ電力(P<sub>L, A, L</sub>)に動的電力(P<sub>D, A, L</sub>)を加えたものから成り、この実施例の場合、25mW+35mW=60mWと等しい。コアBの電力は、P<sub>L, B, L</sub>+P<sub>D, B, L</sub>=10mW+40mW=50mWと等しい。この解析に基づいて、この特定のタスクは、たとえそれが交差ポイント720より上にあり、コアAの動的電力(35mW)より高い動的電力成分(40mW)を有しても、コアBに割り当てられるべきである。ポイント712におけるコアAの漏れ電力が、この特定のタスクがどこに割り当てられるべきかという判断において、かなりの電力を寄与する。

### 【0035】

この分析は、図7Bに示されるように、高温T<sub>H</sub>(T<sub>H</sub>>T<sub>L</sub>)で再考される。動作温度T<sub>H</sub>および動作周波数F<sub>X</sub>で、コアAは、ポイント(P<sub>X, A, H</sub>, F<sub>X</sub>)772に関連した動的電力P<sub>X, A, H</sub>を示すことになり、コアBは、ポイント(P<sub>X, B, H</sub>, F<sub>X</sub>)774に関連した動的電力P<sub>X, B, H</sub>を示すことになる。この特定のタスクに関して、コアAの電力は、漏れ電力(P<sub>L, A, H</sub>)に動的電力(P<sub>D, A, H</sub>)を加えたものから成り、T<sub>H</sub>では、35mW+45mW=80mWと等しい。コアBの電力は、P<sub>L, B, H</sub>+P<sub>D, B, H</sub>=20mW+80mW=100mWと等しい。この分析に基づいて、この特定のタスクは、コアAに割り当てるべきである。より高温では、コアBの動的電力成分が、この特定のタスクがどこに割り当てるべきかという判断においてかなり寄与する。

### 【0036】

図7Aおよび図7Bに示された分析に基づいて、スケジューリングアルゴリズムは線形システム最適化に基づいて用いられてよい。例えば、温度「t」におけるコアiの電力はP<sub>i, t</sub>であり、これは漏れ電力(P<sub>L, i, t</sub>)に動的電力(P<sub>D, i, t</sub>)を加えたものと等しい。すべてのコアの電力は、P<sub>cores, t</sub>= P<sub>i, t</sub>である。

### 【0037】

動的電力は、コア供給電圧(V)、動作周波数(F)、および式(1)によって全般的に管理されるスイッチングキャパシタンス(C)に左右され、

10

20

30

40

50

$$PD=CV^2F \quad (1)$$

であり、ここで、Vは動作電圧であり、Fは動作周波数であり、Cは、評価されている制御可能な電力領域のスイッチングキャパシタンスを表す定数である。コアに割り当てられることになる各タスクは、要件を満たすために、そのコアに関してソフトウェアによって求められる最低周波数Fで動作することが要求される。指定の周波数Fでコアを動作させるのに十分な電力を供給する一方で電力を低減するために、供給電圧もソフトウェアによって求められる。スイッチングキャパシタンスは、製品リリースに先立って、設計および製造のプロセスによって決定される。したがって、動的電力は、センサを必要とせずに、オペレーティングシステムスケジューラによって近似される計算値であり得る。

## 【0038】

10

漏れ電力が温度およびプロセスに強く左右されるので、スケジューラに漏れ情報をもたらすようにセンサが使用される。センサ入力に基づいて漏れ電力を近似し、特定の周波数Fおよび電圧Vでタスクを割り当てられることになる各コアの動的電力を計算することにより、スケジューラは、最低の電力定格を有するコアを選択することができる。適応型スケジューリング手法を利用することにより、チップの老化につれて変化する漏れ電流の影響も考慮に入れることができる。また、フォールトトレラント機構として、適応型スケジューリング手法は、許容範囲を越える漏れ電流の増加を引き起こすいかなるオンチップ故障も考慮に入れることができる。

## 【0039】

20

図8は、漏れ電流情報に部分的に基づいた例示的な第2適応型スレッドスケジューリングプロセス800の流れ図である。プロセス800は、図3のOSスケジューラ305などのマルチプロセッサOSのフレームワーク内で動作する1つまたは複数のソフトウェアプロシージャで実施され得る。複数のコアのうち1つに割り当てられることになるタスクは、検討中のコア向けの動作周波数Fおよび電圧Vに関して評価されている。ブロック804で、動的電力が、割り当てられた周波数F、電圧V、および指定のスイッチング値Cで、コア向けに計算される。ブロック806で、漏れ測定に関連したコアセンサが読み取られる。ブロック808で、センサ読み取り値からコアの漏れ電力が推測される。ブロック810で、推測された漏れ電力が動的電力に加えられてコア電力が見いだされる。判定ブロック812で、このタスクを割り当てうことになるコアのコア電力が計算されているかどうか判断される。このタスクを割り当てることになるコアの電力が計算されていない場合、プロセス800はブロック804に戻って別のコアを評価する。プロセス800は、このタスク割当てに関して検討されるべきすべてのコアが評価されるまで継続する。一旦、このタスク割当てに関して検討されるべき諸コアの個々のコア電力が評価されると、プロセス800はブロック814へ進む。ブロック814で、このタスクは、最低のコア電力を有するコアに割り当てられる。判定ブロック816で、割り当てられるべきさらなるタスクがあるかどうか判断される。割り当てられるべきさらなるタスクがある場合、プロセス800は判定ブロック812へ戻る。割り当てられるべきタスクがそれ以上ない場合、プロセス800は、これを呼び出したルーチンへ戻る。

## 【0040】

30

図9は、様々なセンサ出力から静的漏れ電流および動的電力を求めるための例示的なセンサポーリングプロセス900の流れ図である。プロセス900は、マルチプロセッサOSのフレームワーク内で動作する1つまたは複数のソフトウェアプロシージャで実施され得る。システムプロセスにより、ブロック504はセンサをポーリングすることが可能になる。ブロック904で、図4Cの電圧センサ474などの電圧センサが読み取られる。ブロック906で、図4Cの温度センサ476などの温度センサが読み取られる。ブロック908で、周波数カウント値が、図4Bの周波数カウンタ436などの周波数カウンタから読み取られる。ブロック910で、読み取られたセンサ値が、検知された条件を表す、デジタル値などのプロセッサ読み取り可能な値に変換される。この読み取り値は、対応する制御可能な電力領域向けにタグを付けて保存される。ブロック910は、ハードウェア制御またはソフトウェア制御のいずれかの下で、読み取って変換してからタグを付けることになるセンサを個々に選択することができる。

40

50

## 【0041】

漏れ電流は、例えばドレインからソースへの漏れ電流およびゲート漏れ電流などの様々な要因から生じる可能性がある。漏れ電流の主要な形態は、一般に、使用されるプロセス技術によって変化する。従来のプロセスにおける漏れ電流の最大の原因の1つは、ドレインからソースへの漏れ電流であった。参照によって本明細書に組み込まれている文献「Reverse-Body Bias and Supply Collapse for Low Effective Standby Power」(非特許文献2)に説明されているように、ドレインからソースへの漏れ電流( $I_{off}$ )は、式2を利用して近似的に計算することができ、

## 【0042】

【数1】

10

$$I_{off} = e^{\frac{-V_t}{S/\ln 10}} \quad (2)$$

## 【0043】

上式で、 $V_t$ は閾値電圧であり、Sは式3から求められる閾値下の電圧振幅であり、

## 【0044】

【数2】

20

$$S = \frac{kT}{q} \ln(10) \left\{ 1 + \frac{C_D}{C_{OX}} \right\} \quad (3)$$

## 【0045】

ここで、kはボルツマン定数であり、Tはケルビン単位の動作温度であり、qは電気素量であり、 $C_D$ は空乏層容量であり、 $C_{OX}$ は漏れ電流 $I_{off}$ の温度依存性をもたらすゲート酸化物の静電容量であり、制御可能な電力領域を製造するのに用いられるプロセスは $C_{OX}$ によって評価される。図9のブロック906でもたらされるものなど、特定の温度センサの読み取り値に基づいて、式2および式3を利用して漏れ電流情報が推測されてよい。漏れ電流も、図5の較正プロセス500に関して説明されたように、以前の較正に基づくものでよく、図9のブロック908でもたらされる周波数カウント値は、漏れ電流測定のために較正され得る。また、図9のブロック904でもたらされる電圧読み取り値も、漏れ電流情報を求めたり、動的電力の利用率を求めるかまたは確認したりするのに用いられてよい。

30

## 【0046】

本明細書に開示された実施形態に関連して説明された様々な例示的論理ブロック、モジュール、回路、要素、および構成要素は、汎用プロセッサ、デジタル信号プロセッサ(DSP)、特定用途向け集積回路(ASIC)、フィールドプログラマブルゲートアレイ(FPGA)あるいは本明細書に説明された機能を遂行するように設計された他のプログラマブルロジック構成要素、個別のゲートまたはトランジスタロジック、個別のハードウェア構成要素、またはそれらの任意の組合せを用いて実施するかまたは遂行されてよい。汎用プロセッサはマイクロプロセッサでよいが、選択的に、プロセッサは、任意の従来型プロセッサ、コントローラ、マイクロコントローラまたはステートマシンでよい。プロセッサは、コンピューティング構成要素の組合せ、例えばDSPとマイクロプロセッサの組合せ、複数のマイクロプロセッサ、DSPコアと1つまたは複数のマイクロプロセッサの併用、または所望の用途に適切な他のこののような構成として実施され得る。

40

## 【0047】

本明細書に開示された実施形態に関連して説明された方法は、ハードウェアで直接的に、プロセッサによって実行されるソフトウェアモジュールで、あるいはこの両者の組合せで実施され得る。ソフトウェアモジュールは、RAMメモリ、フラッシュメモリ、ROMメモリ

50

、EPROMメモリ、EEPROMメモリ、レジスタ、ハードディスク、リムーバブルディスク、CD-ROM、または当技術分野で既知のコンピュータ読み取り可能な記録媒体の他の形態の中に存在してよい。コンピュータ読み取り可能な記録媒体は、これに対してプロセッサが情報を読み取り、かつ書き込むことができるようプロセッサに接続され得る。選択的に、コンピュータ読み取り可能な記録媒体はプロセッサに一体化されてよい。

## 【0048】

本発明は、複数のコアに対する適応型スレッドスケジューリングの例示的実施形態に連付けて開示されているが、多種多様な実装形態が、上記の議論および以下の特許請求の範囲と合致する当技術分野の業者によって利用され得ることが理解されよう。

## 【符号の説明】

10

## 【0049】

|                                         |             |    |

|-----------------------------------------|-------------|----|

| 100                                     | 無線通信システム    |    |

| 120                                     | 遠隔装置        |    |

| 125A , 125B , 125C                      | 構成要素        |    |

| 130                                     | 遠隔装置        |    |

| 140                                     | ベースステーション   |    |

| 150                                     | 遠隔装置        |    |

| 180                                     | 順方向リンク信号    |    |

| 190                                     | 逆方向リンク信号    |    |

| 300                                     | 非対称マルチプロセッサ | 20 |

| 304                                     | CPU-A       |    |

| 305                                     | OSスケジューラ    |    |

| 306                                     | CPU-B       |    |

| 308                                     | 共有メモリ1      |    |

| 310                                     | 共有メモリ2      |    |

| 312                                     | DSP-A       |    |

| 314                                     | DSP-B       |    |

| 316                                     | コントローラ      |    |

| 318                                     | 固定機能ロジック    |    |

| 320 , 321 , 322 , 323 , 324 , 325 , 326 | センサ         | 30 |

| 400                                     | 第1センサ回路     |    |

| 404                                     | 直流漏れ電流センサ   |    |

| 406                                     | デジタルコンバータ   |    |

| 408                                     | インターフェイスポート |    |

| 410                                     | 出力端         |    |

| 430                                     | 第2センサ回路     |    |

| 434                                     | リング発振器      |    |

| 436                                     | 周波数カウンタ     |    |

| 438                                     | インターフェイスポート |    |

| 440                                     | 出力端         | 40 |

| 470                                     | 第3センサ回路     |    |

| 474                                     | 電圧センサ       |    |

| 476                                     | 温度センサ       |    |

| 478                                     | デジタルコンバータ   |    |

| 480                                     | インターフェイスポート |    |

| 484                                     | 出力端         |    |

【図1】

FIG. 1

【図2B】

FIG. 2B

【図2A】

FIG. 2A

【 図 3 】

FIG. 3

【図4A】

FIG. 4A

【図4B】

FIG. 4B

【図4C】

FIG. 4C

【図5】

FIG. 5

【図6A】

FIG. 6A

【図6B】

FIG. 6B

【図 7 A】

【図 7 B】

【図 8】

FIG. 8

【図 9】

FIG. 9

---

フロントページの続き

(72)発明者 マニシュ・ガーグ

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

審査官 緑川 隆

(56)参考文献 国際公開第2007/038530(WO,A1)

特開2006-319153(JP,A)

特開2005-267635(JP,A)

特開2006-133995(JP,A)

特開2007-148952(JP,A)

特開2006-120175(JP,A)

米国特許第7886172(US,B2)

米国特許出願公開第2009/0328055(US,A1)

(58)調査した分野(Int.Cl., DB名)

G 06 F 1 / 32

G 06 F 1 / 00

G 06 F 9 / 50

G 06 F 15 / 78