(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5610897号

(P5610897)

(45) 発行日 平成26年10月22日(2014.10.22)

(24) 登録日 平成26年9月12日(2014.9.12)

|                        |                  |

|------------------------|------------------|

| (51) Int.Cl.           | F 1              |

| B 41 J 2/52 (2006.01)  | B 41 J 2/52      |

| G 06 T 1/60 (2006.01)  | G 06 T 1/60 450B |

| H 04 N 1/403 (2006.01) | H 04 N 1/40 103A |

| G 06 F 3/12 (2006.01)  | G 06 F 3/12 B    |

請求項の数 12 (全 15 頁)

(21) 出願番号 特願2010-168484 (P2010-168484)

(22) 出願日 平成22年7月27日 (2010.7.27)

(65) 公開番号 特開2012-25121 (P2012-25121A)

(43) 公開日 平成24年2月9日 (2012.2.9)

審査請求日 平成25年7月29日 (2013.7.29)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 110001243

特許業務法人 谷・阿部特許事務所

(74) 代理人 100077481

弁理士 谷 義一

(74) 代理人 100088915

弁理士 阿部 和夫

(72) 発明者 中村 宏典

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

審査官 下村 輝秋

最終頁に続く

(54) 【発明の名称】データ処理装置およびデータ処理方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1格納部から読み出した複数のインデックスが配列されるL(L-2)行のテーブルのうちM(1≤M≤L)行のインデックスを第2格納部に転送する転送手段と、

画像データの各画素に対し、前記第2格納部に格納されるM行の複数のインデックスをそれぞれ対応させることにより、前記画像データの変換処理をする変換手段と、

前記第2格納部に転送すべきM行のインデックスの前記テーブルの読み出しアドレスを指定するための指定手段と、

を備え、

前記指定手段は、前記テーブルに前記第2格納部に格納されるM行のインデックスに連続するM行のインデックスが存在する場合は、該連続するM行のインデックスの先頭のアドレスを前記読み出しアドレスとして指定し、前記テーブルに前記第2格納部に格納されるM行のインデックスに連続するM行のインデックスが存在しない場合は、前記テーブルの先頭のアドレスを前記読み出しアドレスとして指定することを特徴とするデータ処理装置。

## 【請求項 2】

前記転送手段は、前記指定手段により指定されたアドレスに基づいて、前記変換手段によりM行のインデックスに対応する変換処理が終了した後に、前記テーブルに前記第2格納部に格納されるM行のインデックスに連続するM行のインデックスが存在する場合は、該連続するM行のインデックスにより前記第2格納部の内容を更新し、前記テーブルに第

2格納部に格納されるM行のインデックスに連続するM行のインデックスが存在しない場合は、前記テーブルの先頭に戻って連続するM行のインデックスにより前記第2格納部の内容を更新することを特徴とする請求項1に記載のデータ処理装置。

**【請求項3】**

前記テーブルの読み出しラインを管理するテーブル用ラインカウンタをさらに備え、前記テーブル用ラインカウンタの値に基づいて、読み出しラインが前記テーブルのL行に対応すると判定された場合、前記指定手段は前記テーブルの先頭のアドレスを前記読み出しアドレスとして指定し、前記テーブル用ラインカウンタの値を初期値に戻すことを特徴とする請求項1又は2に記載のデータ処理装置。

**【請求項4】**

前記テーブル用ラインカウンタの値に基づいて、読み出しラインが前記テーブルのL行に対応しないと判定された場合、前記指定手段は前記読み出しアドレスを前記テーブルのライン間のアドレスオフセット分進め、前記テーブル用ラインカウンタの値をインクリメントすることを特徴とする請求項3に記載のデータ処理装置。

**【請求項5】**

前記画像データは、B行ずつ(B M)の複数のバンドから構成されるものであり、前記変換手段による変換処理は、前記バンド単位で実行し、

前記バンド内のラインを管理するバンド用ラインカウンタをさらに備え、前記バンド用ラインカウンタの値がBと判定された場合、前記バンド用ラインカウンタの値を初期値に戻すことを特徴とする請求項3又は4に記載のデータ処理装置。

**【請求項6】**

前記画像データは、多値データであり、前記インデックスは、多値データをドットパターンに変換するための変換パターンを特定する情報を特徴とする請求項1ないし5のいずれか1項に記載のデータ処理装置。

**【請求項7】**

前記テーブルは、前記多値データの各階調レベルに共通して使用されるものであることを特徴とする請求項6に記載のデータ処理装置。

**【請求項8】**

前記変換手段は、前記画像データの各画素の位置に応じて、前記第2格納部に格納されるM行の複数のインデックスを用いることにより、複数のパターンの中から1つのパターンを選択して、前記画像データの変換を行うことを特徴とする請求項1ないし7のいずれか1項に記載のデータ処理装置。

**【請求項9】**

前記第2格納部、前記転送手段及び前記変換手段は同一の処理部に備えられ、前記第1格納部は、前記処理部の外部メモリであることを特徴とする請求項1ないし8のいずれか1項に記載のデータ処理装置。

**【請求項10】**

前記画像データは、階調値と画素の位置を示すアドレス値を含むことを特徴とする請求項1ないし9のいずれか1項に記載のデータ処理装置。

**【請求項11】**

前記転送手段は、前記M行のインデックスを前記第2格納部にDMA転送することを特徴とする請求項1ないし10のいずれか1項に記載のデータ処理装置。

**【請求項12】**

第1格納部から読み出した複数のインデックスが配列されるL(L 2)行のテーブルのうちM(1 M < L)行のインデックスを第2格納部に転送する転送工程と、

画像データの各画素に対し、前記第2格納部に格納されるM行の複数のインデックスをそれぞれ対応させることにより、前記画像データの変換処理をする変換工程と、

前記第2格納部に転送すべきM行のインデックスの前記テーブルの読み出しアドレスを指定するための指定工程と、

10

20

30

40

50

を備え、

前記指定工程では、前記テーブルに前記第2格納部に格納されるM行のインデックスに連続するM行のインデックスが存在する場合は、該連続するM行のインデックスの先頭のアドレスを前記読み出しあドレスとして指定し、前記テーブルに前記第2格納部に格納されるM行のインデックスに連続するM行のインデックスが存在しない場合は、前記テーブルの先頭のアドレスを前記読み出しあドレスとして指定することを特徴とするデータ処理方法。

【発明の詳細な説明】

【技術分野】

【0001】

10

本発明は、2次元に配列されたパラメータ情報を、その配列規則を損なうことなく、画像データの個々の画素位置に対応させて処理を行うデータ処理に関する。特に、画像データ内の画像処理単位（バンド）に含まれるライン数と、上記2次元パラメータ情報のライン数とが調和しない場合であっても、2次元パラメータの配列規則を損なわずに、画像データ内の領域全ての画素に対して処理を行う方法に関する。

【背景技術】

【0002】

20

互いの位置関係が定められた複数のデータの夫々に対し、やはり互いの位置関係が定められたパラメータの夫々を対応させるような処理は、様々な場面で用いられる。例えば、記録装置で画像を記録するためのデータを生成する画像処理において、個々の画素が有する多値データのそれぞれに対し2値のドットパターンを対応させる処理がこれに相当する。また、このように生成した個々の画素のドットパターンに、ドット記録の許容あるいは非許容を予め定めたマスクパターンを対応させることによって、各走査で実際に記録を行うドットを決定するマルチパス記録のための処理もこれに該当する。

【0003】

このようなドットパターンやマスクパターンを、画像領域に対しなるべく非周期に定めようとする場合、画像領域のそれぞれの画素位置に対応する多数のパラメータを、互いの位置関係を固定した状態ですなわち2次元に格納するメモリが要される。但し、上記画像処理を行うCPUがこのような多数のパラメータが格納されたメモリに順次アクセスしながら処理を行うと、処理のための時間が多く要され、記録装置であれば記録速度を低下させてしまう。

30

【0004】

このような処理速度の低下を改善するため、処理を実行する回路の内部に高速メモリ（キャッシュメモリ）を設け、上記大容量のメモリ（低速メモリ）に記憶されているデータを高速メモリに記憶したのち、処理を実行する方法が知られている。このようにすれば、低速メモリに対するアクセス回数を抑えることが出来るので、画像処理に関わる時間を記録速度に影響を与えない程度まで短縮することが出来る。しかし、上記非周期のために用意する2次元テーブルが余り大きいと、回路内部に用意するキャッシュメモリすなわち回路規模も大きくなり、コストを増大させてしまう。

【0005】

40

このように、従来では非周期に配列するパラメータの夫々を、個々のデータに対応付けて処理する状況において、回路規模と高速処理とを両立させることは困難な状況であった。

【0006】

これに対し例えば特許文献1には、低速メモリに格納されたパラメータの一部を、キャッシュメモリに読み出し、格納されたパラメータに対応する領域を単位として、順番に処理を行っていく構成が開示されている。特許文献1の方法を採用すれば、キャッシュメモリ自体に一度に大容量の情報を記憶できなくても、例えば1ライン分のパラメータを格納できるだけの少ないメモリ容量があれば、従来よりも高速なアクセスおよび処理を行うことが出来る。但しこの場合、確かにキャッシュメモリの容量を抑えることは出来るが、処

50

理の単位ごとに C P U の設定が必要な回路では、1 ラインごとに C P U による設定や画像データへのアクセスが必要となり、このことがオーバーヘッドを招致する場合もある。このような状況の下、画像データを複数ラインごとに分割して複数のバンドを生成し、C P U によるメモリへのアクセスやパラメータの設定などを、バンドごとに実行すれば、上記問題を解決することが期待できる。

【先行技術文献】

【特許文献】

【0 0 0 7】

【特許文献 1】特開 2 0 0 2 - 2 6 9 5 7 7 号公報

【特許文献 2】特開 2 0 0 4 - 0 1 5 2 1 3 号公報

10

【発明の概要】

【発明が解決しようとする課題】

【0 0 0 8】

しかしながら、上記特許文献 1 のように、バンドごとに画像処理を行う構成の場合、予めメモリに格納されている 2 次元データの領域（数）が、必ずしもバンドの大きさに調和するとは限らない。

【0 0 0 9】

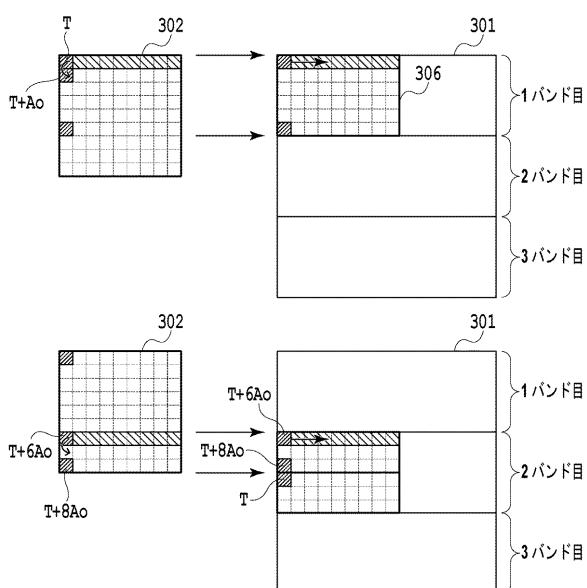

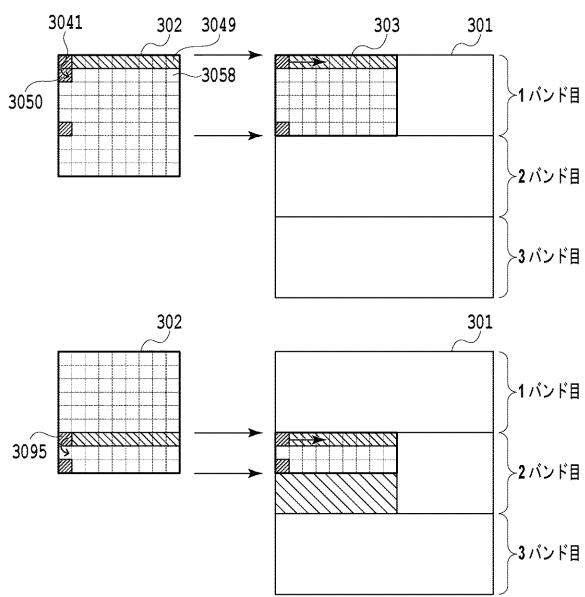

図 1 1 は、外部メモリに 2 次元に格納されているパラメータの配列状態と、これらパラメータを用いて処理されるべき画像データとの対応関係を説明するための模式図である。ここでは簡単のため、画像データ 3 0 1 は、y 方向に 18 画素（18 ライン）、x 方向には 10 画素以上の領域を有するものとする。そして、画像データ 3 0 1 は、6 ラインずつ 3 つのバンドに分割され、1 バンドずつ C P U から呼び出されて処理が施される構成とする。一方、外部メモリに格納された 2 次元パラメータ 3 0 2 は、x 方向に 9 画素分、y 方向に 9 画素（ライン）の 81 個のデータで構成されているものとする。

20

【0 0 1 0】

この場合、まず 1 バンド目の画像を処理するため、C P U は外部メモリにアクセスし、読み込み開始アドレスとして、2 次元パラメータ 3 0 2 のアドレス 3 0 4 1 を指定する。そして、この最上位ラインについては、先頭の 3 0 4 1 から x 方向に 9 つ進んだアドレス 3 0 4 9 までの領域に格納されている、グレーで示した領域 3 0 3 に含まれる 9 つのデータ群をキャッシュメモリに格納する。画像データ 3 0 1 の 1 バンド目 1 ライン目に配列する個々の画素データは、この 9 つのデータのそれぞれによって処理される。

30

【0 0 1 1】

1 バンド目の 2 ライン目については、読み込み開始アドレスを、アドレス 3 0 4 1 から y 方向に 1 ライン分シフトしたアドレス 3 0 5 0 に指定する。そして、先頭の 3 0 5 0 から x 方向に 9 つ進んだアドレス 3 0 5 8 までの領域に格納されている 9 つのデータ群を、キャッシュメモリに格納する。画像データ 3 0 1 の 1 バンド目 2 ライン目に配列する個々の画素データは、この 9 つのデータのそれぞれによって処理される。以上のような動作を繰り返し、1 バンド目に相当する 6 ライン目までのデータ読み込みおよび処理が完了する。このように、1 バンド目については、2 次元パラメータ 3 0 2 の配列関係を崩すことなく、画像データ 3 0 1 の個々の画素に対応させて処理を行うことが出来る。

40

【0 0 1 2】

2 バンド目の画像を処理する際、C P U は 2 次元パラメータ 3 0 2 の読み込み開始アドレスとして、既に読み込んだ 6 ライン目に続く 7 ライン目の先頭アドレス 3 0 9 5 を指定する。そして、1 バンド目と同様にして、順次ラインの読み取りおよび処理を進めていく。しかし、2 バンド目については、最初の 3 ライン目まで処理したところで 2 次元パラメータ 3 0 2 の全データの読み取りが終ってしまう。すなわち、同じバンド内において、単純に先頭アドレスの位置を y 方向に 1 つずつシフトさせていく構成では、4 ライン目のために先頭アドレスを指定することが出来なくなってしまう。

【0 0 1 3】

このような状況を回避するため、処理の単位となるバンドに含まれるライン数を、2 次

50

元パラメータのライン数に合わせて適宜設定する方法も考えられる。本例の場合は、2バンド目のライン数を3ラインにすれば、2バンド目の処理は順調に完結し、3バンド目の処理もスムーズに先頭から開始することが出来る。しかしながら、バンドごとにライン数を設定するという新たなジョブが追加されると、ライン数の管理も複雑になり、CPUに更なる負荷をかけ、オーバーヘッドを効果的に回避することが難しくなる。

#### 【0014】

本発明は、上記問題点を解決するためになされたものである。よって、その目的とするところは、複数データの夫々に対し、2次元パラメータの夫々を配列規則を損なうことなく対応させながら、大掛かりなキャッシュメモリを用いることなく、高速処理することが可能なデータ処理方法を提供することである。

10

#### 【課題を解決するための手段】

#### 【0015】

そのために本発明は、第1格納部から読み出した複数のインデックスが配列されるL(L-2)行のテーブルのうちM(1 M < L)行のインデックスを第2格納部に転送する転送手段と、画像データの各画素に対し、前記第2格納部に格納されるM行の複数のインデックスをそれぞれ対応させることにより、前記画像データの変換処理をする変換手段と、前記第2格納部に転送すべきM行のインデックスの前記テーブルの読み出しアドレスを指定するための指定手段と、を備え、前記指定手段は、前記テーブルに前記第2格納部に格納されるM行のインデックスに連続するM行のインデックスが存在する場合は、該連続するM行のインデックスの先頭のアドレスを前記読み出しアドレスとして指定し、前記テーブルに前記第2格納部に格納されるM行のインデックスに連続するM行のインデックスが存在しない場合は、前記テーブルの先頭のアドレスを前記読み出しアドレスとして指定することを特徴とする。

20

#### 【発明の効果】

#### 【0016】

本発明によれば、2次元に配列する複数データの夫々に対し、2次元パラメータの夫々を配列規則を損なうことなく対応させながら、大掛かりなキャッシュメモリを用いることなく、高速処理することが可能となる。

#### 【図面の簡単な説明】

#### 【0017】

30

【図1】本発明に使用可能なインクジェット記録装置の外観斜視図である。

【図2】記録装置の記録部の構成を説明するための斜視図である。

【図3】記録装置における制御の構成を説明するためのブロック図である。

【図4】画像処理の工程を説明するためのブロック図である。

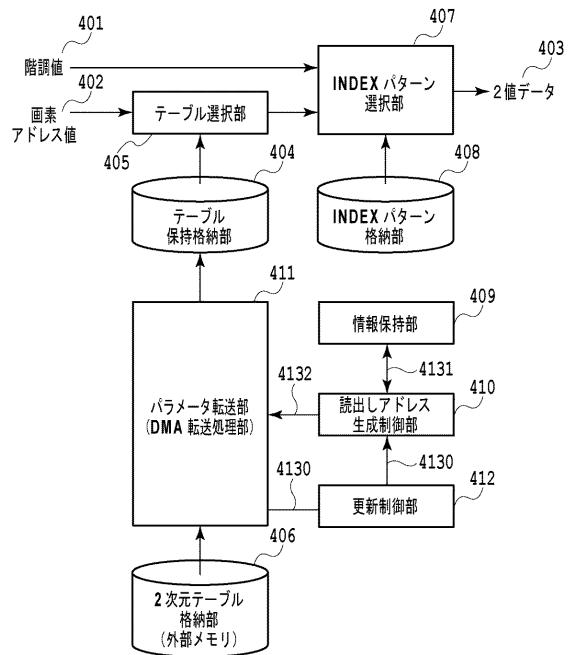

【図5】INDEX処理部における具体的な処理を実行する回路構成図である。

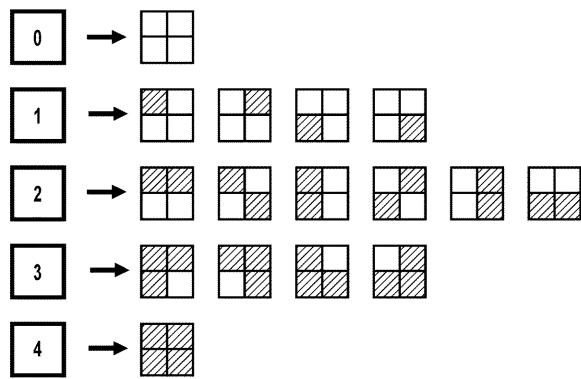

【図6】複数のドットパターンを、各レベルについて示した図である。

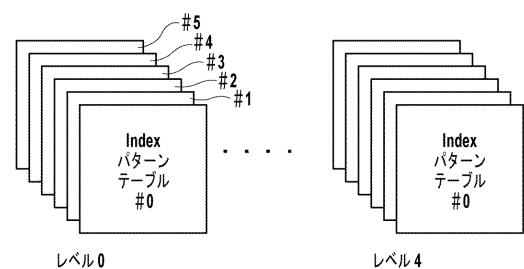

【図7】複数のドットパターンの格納状態を説明するための模式図である。

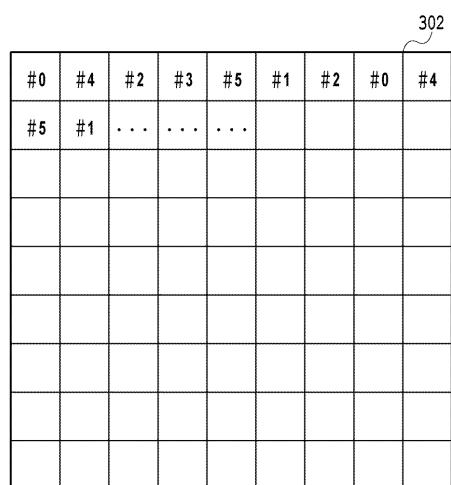

【図8】2次元テーブルの一例を示す図である。

【図9】2次元テーブルと画像データとの対応関係を説明するための模式図である。

【図10】INDEX処理の工程を説明するためのフローチャートである。

40

【図11】2次元パラメータと画像データとの対応関係を説明する図である。

#### 【発明を実施するための形態】

#### 【0018】

以下、図面を参照して本発明の実施例を詳細に説明する。以下に説明する実施例は、特許文献2に開示されている画像処理において、INDEX処理部が実行する処理を対象としたものである。但し、本発明は、このような画像処理に限定されるものではない。本発明は、互いの位置関係が定められた複数のデータの夫々に対し、外部メモリに格納された2次元テーブルの個々のパラメータ値を、その配列規則を損なうことなしに1対1で対応させながら処理を行う構成であれば、その効果を発揮することができる。

#### 【実施例1】

50

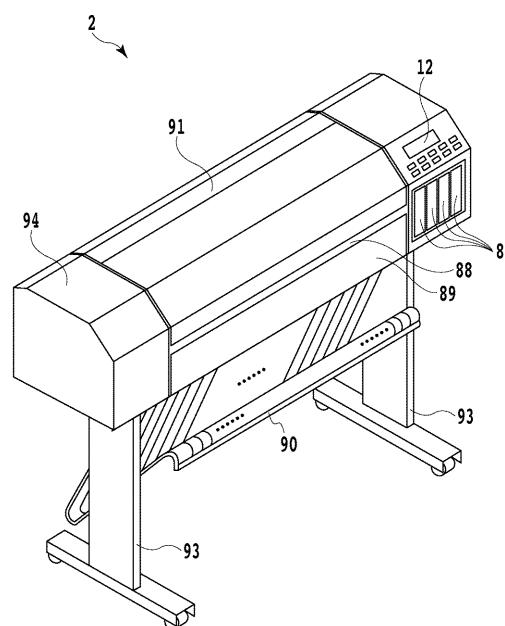

## 【0019】

図1は、本発明に適用可能なインクジェット記録装置（以下、記録装置）2の外観斜視図である。本実施例の記録装置2は、外部に接続されたホスト装置から受信した画像データを、A0サイズやB0サイズのような比較的大判の記録媒体に記録することが可能なインクジェット記録装置である。2個の脚部93に支持された装置本体94の前面には、手差し挿入口88およびロール紙カセット89が備えられている。記録時には、手差し挿入口88あるいはロール紙カセット89から供給された記録媒体に対し、本体内部に備えられた記録ヘッドが、画像データに従ってインクを吐出する。記録後の記録媒体はスタッカ90に排出される。

## 【0020】

10

記録ヘッドは、シアン、マゼンタ、イエローおよびブラックの4色のインクを用いて画像を記録し、これら4色のインクはインク供給ユニット8から供給される。アッパーカバー91は透明で開閉可能なカバーである。アッパーカバー91を閉じた状態では、記録動作中の記録ヘッドや記録媒体を観察することができる。一方、アッパーカバー91を開放した状態では、記録ヘッドの交換や記録装置2のメンテナンス等を行うことが出来る。操作パネル12は、記録方法や記録媒体などの設定を行うための入力キーや装置の情報を表示する画面が配備されている。

## 【0021】

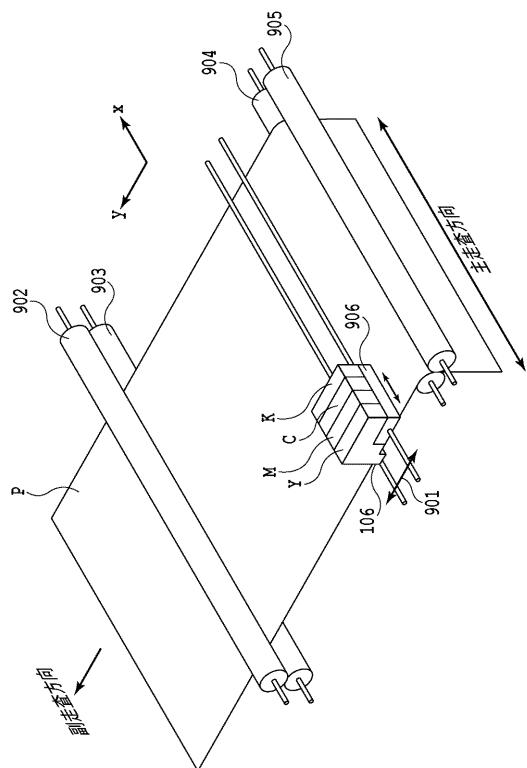

図2は、記録装置2の記録部の構成を説明するための斜視図である。記録ヘッド106は主走査方向（x方向）に一定の速度で移動するキャリッジ906に搭載され、上記一定の速度に対応した周波数でインクを滴として吐出する。このような1回の記録主走査が終了するごとに、記録媒体Pは、給紙ローラ904および補助ローラ905のローラ対、搬送ローラ902および補助ローラ903ローラ対に挟持されながら副走査方向（y方向）に所定の量だけ搬送される。上記記録主走査と搬送動作とを交互に繰り返すことにより、記録媒体Pに段階的に画像が記録される。

20

## 【0022】

30

記録ヘッド105は、ブラック（K）、シアン（C）、マゼンタ（M）およびイエロー（Y）の記録ヘッドが、図のようにx方向に並列配置されて構成されている。各色の記録ヘッドには、複数の記録素子がy方向に1200dpi（dot/inch）の密度で配備されており、インク供給ユニット8から供給されたインクを画像データに従って吐出する。なお、一般に、シリアル型のインクジェット記録装置の場合、1回の記録主走査で記録を行うことが出来る画像の単位を「バンド」と称することがあるが、本明細書における「バンド」はこのような定義ではない。本明細書においては、CPUが画像処理を一まとめに行うデータの単位を示す。本明細書におけるバンドの詳細は後述する。

## 【0023】

30

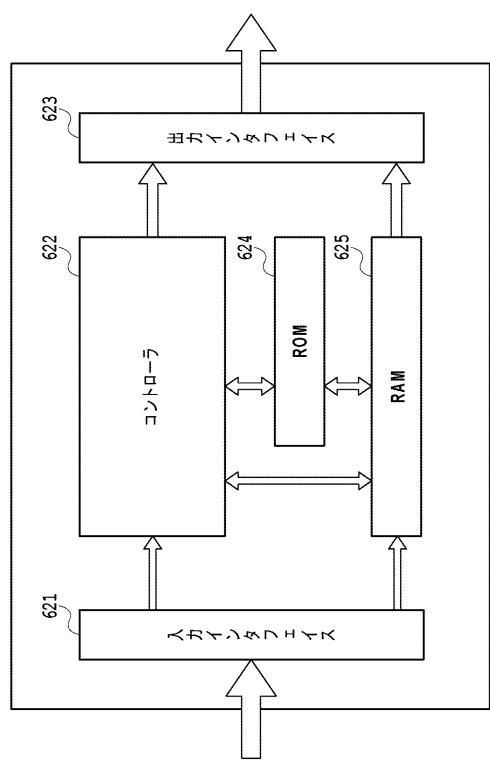

図3は、インクジェット記録装置2における制御の構成を説明するためのブロック図である。入力インタフェイス621は、記録装置の外部に接続されたホスト装置や、操作パネル12からの入力情報を受信する。コントローラ622は、CPUのほか、本発明の特徴的な回路などによって構成されており、ROM624に格納された各種プログラムに従って、記録装置全体の制御を行う。例えば、コントローラ622は、入力インタフェイス621を介してホスト装置から受信した画像データを、ROM624に記憶されているプログラムに従って、記録ヘッド106が記録可能な記録データを生成する。生成した記録データは出力インタフェイス623を介して記録ヘッド106に出力される。ROM624には、上記プログラムのほか、画像処理で使用する色分解テーブルや、本発明の特徴的な2次元テーブル等の各種パラメータも記憶されている。RAM620は、上述した画像処理のほかコントローラ622が各種処理を実行する際にワークエリアとして利用される。

40

## 【0024】

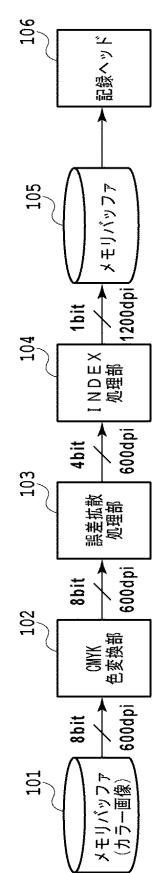

図4は、コントローラ622が実行する画像処理の工程を説明するためのブロック図である。外部に接続されたホスト装置などから記録すべき画像データが受信されると、当該

50

画像データは装置内のメモリバッファ 101 に格納される。このときの画像データは 600 dpi の解像度を有し、1 画素につき 8 bit 256 階調で表現される多値の画像データ (R, G, B) とする。メモリバッファ 101 に格納された多値の画像データは、その後 1 画素ずつ CMYK 色変換部 102 に転送され、記録装置が使用するインク色 CMYK に対応した多値の画像データ (600 dpi, 8 bit) に変換される。CMYK 色変換部 102 で変換された各色の画像データは、誤差拡散処理部 103 によってそれぞれ低階調化処理が施され、5 階調にまで量子化される。

#### 【0025】

誤差拡散処理部 103 で量子化された各色の 5 階調の階調データは、更に INDEX 处理部 104 で 2 値化される。そして、記録ヘッド 106 の記録解像度 1200 dpi に対応した個々の画素に対し、ドットを記録する (1) あるいは記録しない (0) を示す 2 値データに変換される。このような 2 値の記録データ (1200 dpi, 1 bit) は、インク色ごとにプリントバッファ 105 に格納される。プリントバッファ 105 に、1 回分の記録走査が行えるだけの 2 値データが蓄積されると、記録ヘッド 106 はプリントバッファ 105 に格納された 2 値データに従って、1 回分の記録走査を行う。

#### 【0026】

図 5 は、INDEX 处理部 104 における具体的な処理を実行する回路構成図である。この INDEX 处理部 104 は CPU により制御される。誤差拡散処理部 103 から出力されるデータは、5 階調のレベル値 (階調値) 401 と画素の位置を示すアドレス値 402 を有している。レベル値 401 は、600 dpi の各画素に対応する 5 階調の階調データであり、0 ~ 4 の値をとり得る。INDEX パターン選択部 407 では、このようなレベル値 401 と画素アドレス値 402 とから、1200 dpi の 2 画素 × 2 画素の各画素におけるドットの記録 (0) 或いは非記録 (1) を定めた 2 値データ 403 を出力する。

#### 【0027】

図 6 は、2 画素 × 2 画素のうち、どの画素を記録画素としどの画素を非記録画素とするかを定める複数のパターン (複数の 2 値データ) を、各レベルについて示した図である。図において、黒で示したエリアがドットを記録する記録画素 (1)、白で示したエリアが非記録画素 (0) である。一般に、入力データのレベルが 0 のとき、2 画素 × 2 画素の全ての画素が非記録画素 (0) となり、記録画素 (1) は存在しない。よって、レベル 0 では 2 画素 × 2 画素の全ての画素が非記録画素となる 1 つのパターンが用意されるのみである。入力データのレベルが 1 のとき、2 画素 × 2 画素のうち 3 つの画素が非記録画素 (0) となり、1 つの画素が記録画素 (1) となる。よって、レベル 1 では図に示すような 4 通りのパターンが用意される。入力データのレベルが 2 のとき、2 画素 × 2 画素のうち 2 つの画素が非記録画素 (0) となり、2 つの画素が記録画素 (1) となる。よって、レベル 2 では図のような 6 通りのパターンが用意される。また、入力データのレベルが 3 のとき、2 画素 × 2 画素のうち 1 つの画素が非記録画素 (0) となり、3 つの画素が記録画素 (1) となる。よって、レベル 3 では図のような 4 通りのパターンが用意される。更に、入力データのレベルが 4 のとき、2 画素 × 2 画素のうち全ての画素が記録画素 (1) となる。よって、レベル 4 では図のような 1 通りのパターンが用意される。

#### 【0028】

本実施形態では、このような個々のレベルに対応する複数のドットパターンが INDEX パターン格納部 408 に格納されており、INDEX パターン選択部 407 は、このような複数のパターンの中から、注目画素の位置に応じたパターンを 1 つ選択する。

#### 【0029】

図 7 は、INDEX パターン格納部 408 における、複数のドットパターン (2 値データ) の格納状態を説明するための模式図である。ここでは、レベル 1 ~ レベル 4 のそれについて、#0 ~ #5 の 6 通りずつのパターンが用意されている。個々のパターン 601 は、図 6 で示した 2 画素 × 2 画素に対応する 4 ビットデータに相当する。図 6 で示したように、レベル 2 以外のレベルでは、6 通りのパターンを有さないが、本実施例では、各レベルの #0 ~ #5 の全てに図 6 で示したパターンのいずれかが格納されている。例えば

10

20

30

40

50

、レベル4では、#0～#5の全てに、2画素×2画素の全ての画素が記録画素(1)となるパターンが記憶されており、レベル3では、#0～#5の全てに、図6で示した4通りのパターンのうちのいずれか一つが格納されている。レベル2については、図6で示した6通りのパターンの1つずつが、#0～#5のそれぞれに対応して格納されている。

#### 【0030】

INDEXパターン選択部407では、このような複数のパターンの中から、1つのパターンが注目画素の位置に応じて1つ選択される。このために本実施例では、テーブル選択部405が、画素アドレス値402に応じてINDEXパターン格納部に格納された#0～#5のいずれかのテーブルを指定する構成になっている。そして、画像中の画素の位置においてこれら複数のパターンが代わる代わる選択されることにより、入力データ(階調値)が同じ値を持つ場合であっても同じパターンが主走査方向や副走査方向に連続しないようにしている。本発明者らの検討によれば、このような複数のパターンは主走査方向および副走査方向に非周期且つ満遍なく使用されることが好ましい。そのため、本実施例では画素位置に対応するテーブルの番号(#0～#5)を予め定めた2次元テーブルを第1の格納部である外部メモリ406に格納している。なお、この2次元テーブルは、階調値に共通して使用される。

#### 【0031】

なお、以上では、600dpiの5値データを1200dpiの2値データに変換する構成を例としているため、INDEXパターンは2画素×2画素の4ビットとなり、レベル2に対応する6種類が最高のパターン数となった。しかし、無論本発明はこのような構成に限定されるものではない。2値化を行うためにN画素×M画素(N, M > 2)のINDEXパターンを利用する場合は、1つのレベルについて更に多くのパターン(例えばL種類のパターン)を用意することが出来る。この場合、図7に示したINDEXパターンを管理するためのテーブルも更に多くの種類(#0～#L-1)だけ用意すれば良い。また、INDEXパターンが1通りしか用意されないレベル0やレベル4については、特にテーブル番号からINDEXパターンを指定することなく、2値データ(0はあるいは1)をそのまま出力するようにしてもよい。

#### 【0032】

図8は、画素位置に応じてINDEXパターンを定めるための、2次元テーブルの一例を示す図である。x方向がキャリッジの進行方向すなわち主走査方向に対応し、y方向が記録媒体の搬送方向すなわち副走査方向に対応している。このようなテーブル番号の配置が画像データの個々の画素に対応するテーブル番号の配置となるように、個々のテーブル番号が非周期且つ満遍なく配置されている。

#### 【0033】

本実施例ではこのように9ライン分の2次元テーブルが用意され、これら9ラインのうちの1ラインがパラメータ転送部411によって呼び出され、第2の格納部である書き換え可能なテーブル保持格納部404に一時的に格納される。そして、テーブル選択部405は、画素アドレス値402に従って、テーブル保持格納部404に格納された1ライン分のテーブル番号から1つを選択し、このテーブル番号をINDEXパターン選択部407に指示する。INDEXパターン選択部407は、再度図7を参照するに、入力したレベル値401に対応する複数のパターン中から、指示されたテーブル番号に相当するINDEXパターンを選択し、2値データ403としてこれを出力する。なお、2次元テーブルは、1行あたり9画素分のテーブル番号しか備えていないため、画像データの1行あたりの画素数が10画素以上であれば、この1行分(9画素分)のテーブルを繰り返し使用する。

#### 【0034】

再度図5を参照する。更新制御部412は、1ライン分のINDEX処理が完了するたびにテーブル保持格納部404内のテーブル番号を更新するように、タイミング信号4130をパラメータ転送部411に発信する。また、読み出しあドレス生成制御部410は、情報保持部409に記憶されている様々な情報に基づいて、次の更新の際に2次元テー

10

20

30

40

50

ブルのどのアドレスから転送を開始するかを示す情報（読み出しアドレス信号 4132）を、パラメータ転送部に指示する。情報保持部 409 には、2 次元テーブルの 1 ライン目の先頭アドレス（T）や、2 次元テーブルのライン間のアドレスオフセット値（A0）などが保持されている。パラメータ転送部 411 は、これら更新制御部 412 から指示されるタイミング信号 4130 と、読み出しアドレス生成制御部 410 から指示される読み出しアドレス信号 4132 に従って、テーブル保持格納部 404 へのテーブル番号の更新を行う。

#### 【0035】

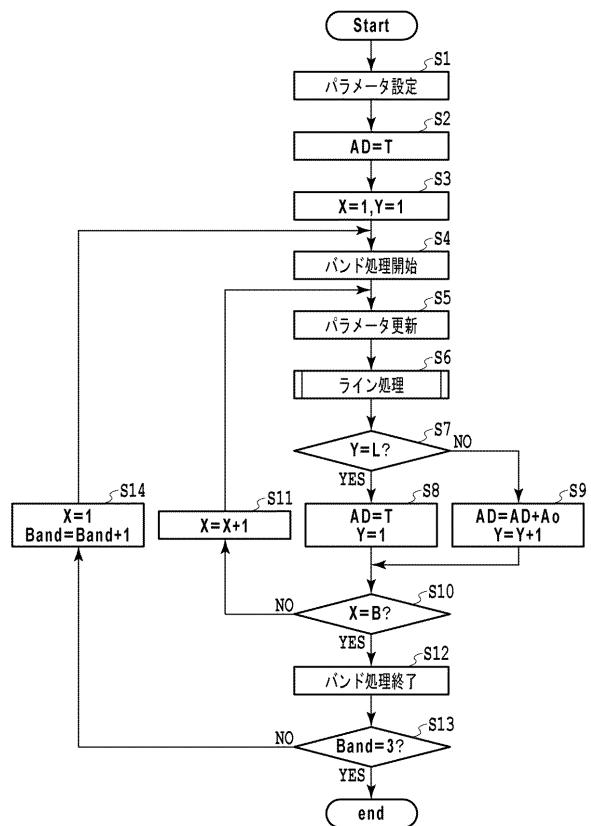

図 9 は、本実施例における 2 次元テーブルと、当該テーブルに記憶されている個々のテーブル番号に従って処理されるべき画像データとの対応関係を、図 11 と比較しながら説明するための模式図である。ここでは、2 次元テーブルは 9 ライン、画像データは 6 ラインずつの 3 つのバンドによって構成されている例を示している。また、図 10 は、このような画像データに対する INDEX 处理の工程を説明するためのフローチャートである。以下、図 9 を参照しながら図 10 のフローチャートの各工程を説明する。

10

#### 【0036】

本処理が開始されると、まずステップ S1 において、CPU が情報保持部 409 に対し、2 次元テーブルの先頭アドレス T、2 次元テーブルにおけるライン間のアドレスオフセット A0、1 つのバンドに含まれるライン数 B などを設定する。続くステップ S2 および S3 では、処理に使用する変数の初期設定を行う。具体的には、ステップ S2 において、読み出しアドレス AD を 2 次元テーブルの先頭アドレスに設定（AD = T）する。また、ステップ S3 では、バンド内のラインを 1 つずつ管理するためのカウンタ X（1 X 6）、2 次元テーブル 302 内の読み出しラインを 1 つずつ管理するためのカウンタ Y（1 Y 9）を、それぞれ 1 に設定する。また、画像内の 3 つのバンドを管理するためのカウンタ Band（1 Band 3）も 1 に設定する。

20

#### 【0037】

ステップ S4 において、CPU は、注目するバンドのバンド処理を開始するための各種設定を行う。バンド処理が開始されると、更新制御部 412 は、読み出しアドレス生成制御部 410 とパラメータ転送部 411 へ更新指示を通知する。これに伴いパラメータ転送部 411 は、アドレス生成制御部 410 から得た読み出しアドレス AD に従って、2 次元テーブル 406 から 1 ライン分の新たなパラメータ（テーブル番号）を読み出し、テーブル保持格納部 404 の内容を更新する（ステップ S5）。

30

#### 【0038】

その後、ステップ S6 にて、バンド内の注目する 1 ラインに含まれる画素のそれぞれに、テーブル保持格納部に格納された 1 ライン分のパラメータを対応させながら、画像処理を行う。具体的には、テーブル選択部 405 が、注目する画素の画素アドレス値 402 に基づいて、テーブル保持格納部 404 に配列するテーブル番号の 1 つを選択する。そして、INDEX パターン選択部 407 が選択されたテーブル番号に対応する INDEX パターンを INDEX パターン格納部 408 から読み出して、2 値データ 403 として出力する。このような変換処理を画像データの 1 ライン分について行う。

#### 【0039】

40

ステップ S7 では、2 次元テーブル用のラインカウンタ Y の値が、2 次元テーブルのライン数 L (= 9) と同値であるか否かを判断する。同値である（Y = L）と判断した場合は、ステップ S8 へ進み、読み出しアドレス AD を 2 次元テーブルの先頭アドレス T に戻し（AD = T）、ラインカウンタ Y を 1 に戻す。一方、ステップ S7 で、同値でない（Y < T）と判断した場合は、2 次元テーブルの中に前回読み出したデータに連続する読み出すべきデータがまだ存在することになる。よって、ステップ S9 へ進み、読み出しアドレス AD をアドレスオフセット A0 分だけ進める（AD = AD + A0）。また、ラインカウンタ Y を 1 ライン分インクリメントする。

#### 【0040】

ステップ S10 では、バンド用のラインカウンタ X の値が、バンドのライン数 B (= 6

50

) と同値であるか否かを判断する。同値ではない ( $X < B$ ) 場合、処理中のバンドにはまだ処理すべきラインが存在するので、ステップ S 1 1 でバンド用のラインカウンタ  $X$  をインクリメントした後、次のラインの処理を行うためにステップ S 5 に戻る。一方、ステップ S 1 0 でバンド用のラインカウンタ  $X$  がバンドのライン数  $B$  ( $= 6$ ) と同値である場合は、処理中の対象となっているバンドの全ラインに対する処理が終了したと判断し、ステップ S 1 2 に進む。ステップ S 1 2 では、CPU に対し、注目するバンドの処理が完了したことを通知する。

#### 【 0 0 4 1 】

ステップ S 1 3 では、バンド用のカウンタ  $Band$  が、画像内のバンド数 3 と同値であるか否かを判断する。  $Band < 3$  の場合、処理すべきバンドがまだ残っているので、ステップ S 1 4 でバンド用のカウンタ  $Band$  をインクリメントし、更にバンド内のラインカウンタ  $X$  を 1 に戻した後、次のバンドの処理を行うためにステップ S 4 に戻る。一方、ステップ S 1 3 で、  $Band = 3$  である場合、全バンドに対する処理が完了したと判断し、本処理を終了する。なお、上述のフローにおける判断は、CPU もしくは INDEX 处理部 104 に設けた判定部が行う。

10

#### 【 0 0 4 2 】

以上説明したフローチャートでは、バンド内のラインを管理するためのカウンタ  $X$  と、2 次元テーブル内のラインを管理するためのカウンタ  $Y$  とを、それぞれ独立に管理し初期化 ( $X = 1$  或いは  $Y = 1$ ) している。より詳しくは、バンド内のライン数 ( $B = 6$ ) と 2 次元テーブルのライン数 ( $L = 9$ ) の値およびカウンタ  $X$ 、  $Y$  を情報保持部 409 で管理し、各カウンタをこれら値と対比しながら適切なタイミングで初期値に戻している。そして、常に、次の読み出しアドレス  $AD$  が、カウンタ値  $Y$  に対応付けて把握されている。以上のような構成により、バンド内のラインと 2 次元テーブルのラインを、互いの配列を崩すことなく、1 ラインずつ順番に対応付けることが出来る。

20

#### 【 0 0 4 3 】

例えば図 9 の 2 バンド目を参照するに、2 バンド目の処理開始持、バンド用のカウンタ  $X = 1$  であるが、2 次元テーブル用のカウンタ  $Y$  はステップ S 609 によって  $Y = 7$  に設定されている。よって、2 バンド目の 1 ライン目の画像データには、2 次元テーブルの 7 ライン目 (読み出しアドレス  $AD = T + 6A0$ ) のパラメータ (テーブル番号) が対応付けられる。また、2 バンド目の 4 ライン目の処理のとき、バンド用のカウンタ  $X = 4$  であるが、2 次元テーブル用のカウンタ  $Y$  は、ステップ S 608 によって 1 に戻される。よって、2 バンド目の 4 ライン目の画像データには、2 次元テーブルの 1 ライン目 (読み出しアドレス  $AD = T$ ) のパラメータが対応付けられる。

30

#### 【 0 0 4 4 】

このように、本実施例によれば、CPU による再設定を行わなくても、テーブル保持格納部の内容を 2 次元テーブルの 1 ライン目に戻すことが可能となる。すなわち、バンドごとにライン数を設定しなくても、2 次元テーブルの配列規則を崩さずに画像データに対応させることが出来るので、オーバーヘッドの懸念も回避される。つまり、本実施例によれば、2 次元テーブルの配列規則を画像データの配列に対して崩すことなくタイル状に対応させながら、高速な画像処理を行うことが可能となる。

40

#### 【 0 0 4 5 】

なお、以上説明した実施例では、2 次元テーブルは 9 ライン、画像データは 6 ラインずつの 3 つのバンドによって構成されている例について説明したが、無論本発明はこのような構成に限定されるものではない。本発明は、B 行ずつのラインを有する複数のバンドで構成される画像データに対し、L 行 (ライン) の 2 次元テーブルを用いて処理する場合の全てに対応することが出来る。2 次元テーブルについては、ライン数 (行数) その領域が大きいほど画像データ内での周期性を少なくし、周期性に伴うモアレなどを回避することが出来る。2 次元テーブル内のライン数が大きくなつたとしても、回路内部のテーブル保持格納部 404 のメモリ容量を大きくする必要はないので、本発明をより効果的に利用することが出来る。また、画像データが大きいほどバンド内のライン数やバンド数は大きく

50

なる傾向があるが、処理する対象が大きいほど、わずかなメモリで高速処理を実現する本発明の効果も大きくなる。

【0046】

また、上記実施例では、テーブル保持格納部の容量を2次元テーブルの1ライン分として説明したが、本発明はこれに限定されるものではない。テーブル保持格納部には2次元テーブルの2ライン以上(M行)が格納される構成であっても良い。但し、少ないメモリで高速な処理を行うという本発明の効果を発揮するためには、Mは1  $M < L / 2$  (Lは2次元パラメータの行数)を満足する値であることが要される。何ライン分用意するにせよ、テーブル保持格納部が外部に設けられた2次元テーブルよりも少ない容量であれば、外部メモリのパラメータを部分的に読み出して高速に処理するという効果を発揮することはできる。但し、回路規模を抑えるという意味では、上記実施例のように、画像処理の1つの単位である1ライン分のメモリとするのが効果的である。あるいは、テーブル更新を画像処理中に並行して行える構成の場合は、画像処理の単位の2倍のメモリ(2ライン分のメモリ)を用意しておくのが、高速化の上では好ましい。

10

【0047】

上記実施例では、画像処理の単位を1ラインずつ行う構成で説明したが、本発明はこのような構成に限定されるものでもない。テーブル保持格納部のメモリ容量が画像処理の単位あるいはそれ以上用意されていれば、本発明の効果を発揮することは出来る。例えば、画像処理の単位が2ラインの場合、テーブル保持格納部は2次元テーブルの2ライン以上の容量を有していれば良く、アドレスオフセットA<sub>0</sub>は2ライン分のオフセット量とすればよい。また、画像処理の単位が複数ラインの場合、2次元テーブルのライン数によっては、2次元テーブルの最後の複数ライン分を読み取っている最中に、2次元テーブルの読み出しアドレスを1ライン目に戻す必要が生じる場合がある。このような場合には、読み出しアドレスA<sub>d</sub>を、最初のラインを読み取るためと、1ライン目に戻すためとの2回に分けて設定し、読み出しを行えばよい。また、上記実施例では、この2次元テーブルは、階調値に共通して使用する形態であるが、例えば、階調値の一部のために、同じサイズのテーブル406やテーブル保持格納部404等を別に備える形態にしても構わない。

20

【0048】

以上では、一例としてINDEX処理を説明したが、本発明は2次元に配列されたパラメータを、その配列規則を損なうことなく、画像データの個々の画素位置に1対1で対応させながら行なうデータ処理であれば、どのような目的の処理にも対応可能である。例えば、予め用意されたディザパターンを用いて、多値の画像データを2値化するディザ処理を行う際も、上記実施例の構成を応用することが出来る。また、ドット記録の許容あるいは非許容を予め定めたマスクパターンを2次元テーブルに格納し、各走査で実際に記録を行うドットを決定するマルチパス記録のための処理にも上記実施例の構成を応用することが出来る。

30

【符号の説明】

【0049】

|     |               |  |

|-----|---------------|--|

| 401 | レベル値          |  |

| 402 | 画素アドレス値       |  |

| 403 | 2値データ         |  |

| 404 | テーブル保持格納部     |  |

| 405 | テーブル選択部       |  |

| 406 | 2次元テーブル格納部    |  |

| 407 | INDEXパターン選択部  |  |

| 408 | INDEXパターン格納部  |  |

| 409 | 情報保持部         |  |

| 410 | 読み出しアドレス生成制御部 |  |

| 411 | パラメータ転送部      |  |

| 412 | 更新制御部         |  |

40

50

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

1バンド=6ライン

外部メモリの2次元テーブルのライン数=9ライン

【図10】

【図11】

---

フロントページの続き

(56)参考文献 特開2001-054956(JP,A)

特開2004-274131(JP,A)

特開2005-157530(JP,A)

特開2006-123197(JP,A)

特開2006-148643(JP,A)

特開2005-161630(JP,A)

(58)調査した分野(Int.Cl., DB名)

B41J2/52-2/525

B41J5/00-5/52

B41J21/00-21-18

G06T1/00

G06T1/60

H04N1/40