(12) 发明专利

(10) 授权公告号 CN 107526543 B

(45) 授权公告日 2022.02.01

(21) 申请号 201710455905.1

(51) Int.CI.

(22) 申请日 2017.06.16

G06F 3/06 (2006.01)

(65) 同一申请的已公布的文献号

申请公布号 CN 107526543 A

(43) 申请公布日 2017.12.29

(56) 对比文件

US 2005081080 A1, 2005.04.14

(30) 优先权数据

US 5490154 A, 1996.02.06

62/352,509 2016.06.20 US

US 2013246878 A1, 2013.09.19

15/242,433 2016.08.19 US

CN 103917964 A, 2014.07.09

(73) 专利权人 三星电子株式会社

US 2009319859 A1, 2009.12.24

地址 韩国京畿道

US 2015286528 A1, 2015.10.08

(72) 发明人 I.S.崔 奇亮奭

US 2014269048 A1, 2014.09.18

(74) 专利代理机构 北京市柳沈律师事务所

US 7903806 B1, 2011.03.08

11105

US 2008288814 A1, 2008.11.20

代理人 邵亚丽 刘虹

WO 2015155860 A1, 2015.10.15

CN 103329103 A, 2013.09.25

审查员 刘褚焱

权利要求书3页 说明书11页 附图13页

(54) 发明名称

形性存储设备

(57) 摘要

本发明提供一种固态驱动器，其根据使用固态驱动器中的存储的应用的要求来选择物理快闪存储器块以及擦除和编程方法。固态驱动器中的磨损跟踪器对编程和擦除周期进行计数，并且固态驱动器中的原始比特错误率跟踪器监视从固态驱动器读取的数据中的原始比特错误率。所述应用向固态驱动器提供关于可允许保留时间和关于平均响应时间的要求，所述可允许保留时间与所述应用存储的数据的预期存储时间相对应，并且所述平均响应时间与对于所述快闪存储器的编程次数和读取次数相对应。固态驱动器识别适于满足所述要求的物理快闪存储器块，并且从所识别的物理快闪存储器块当中向所述应用分配存储空间。

1. 一种用于分配连接到主机的固态驱动器中的快闪存储器的部分的方法, 该快闪存储器包括多个物理快闪存储器块, 所述方法包括:

对快闪存储器执行多个读取操作, 一个或多个读取操作包括纠错码解码操作, 所述纠错码解码操作产生比特错误计数;

从所述多个比特错误计数中, 针对所述多个物理快闪存储器块中的一个或多个, 计算原始比特错误率;

对针对所述多个物理快闪存储器块中的每一个执行的编程和擦除周期进行计数;

对于多个编程方法中的每一个, 针对一个或多个物理快闪存储器块, 从所述原始比特错误率和编程和擦除周期的数量中, 计算以下各项:

平均响应时间, 和

估计的可允许保留时间;

从运行在主机上的第一应用接收要求的第一集合;

对于一个或多个物理快闪存储器块确定是否适于满足要求的第一集合;

形成物理快闪存储器块的第一列表, 第一列表中的物理快闪存储器块适于满足要求的第一集合;

从第一应用接收对存储空间的分配的请求; 以及

向第一应用分配来自第一列表的第一物理快闪存储器块。

2. 如权利要求1所述的方法, 其中, 所述多个编程方法包括:

利用第一步长的递增步进脉冲编程方法; 和

利用第二步长的递增步进脉冲编程方法,

其中, 第一步长大于第二步长。

3. 如权利要求1所述的方法, 其中, 要求的第一集合包括所要求的可允许保留时间和所要求的平均响应时间。

4. 如权利要求3所述的方法, 其中, 对于一个或多个物理快闪存储器块, 确定是否适于满足要求的第一集合包括:

针对所述多个编程方法中的任何编程方法确定:

所计算的平均响应时间是否小于所要求的平均响应时间; 以及

所计算的估计的可允许保留时间是否大于所要求的可允许保留时间。

5. 如权利要求1所述的方法, 还包括擦除第一物理快闪存储器块。

6. 如权利要求5所述的方法, 其中, 所述第一物理快闪存储器块的擦除包括:

当浅擦除过程的预测效果是第一物理快闪存储器块仍然适于满足要求的第一集合时, 采用浅擦除过程; 以及

当浅擦除过程的预测效果是第一物理快闪存储器块不再适于满足要求的第一集合时, 采用正常擦除过程。

7. 如权利要求1所述的方法, 其中, 针对一个或多个物理快闪存储器块, 对所估计的可允许保留时间的计算包括:

对作为保留时间的函数的比特错误计数执行线性拟合; 以及

计算对于其线性拟合超过最大可接受的原始比特错误率的保留时间。

8. 如权利要求7所述的方法, 其中, 所述最大可接受的原始比特错误率是每一百万比特

一个比特错误。

9. 如权利要求1所述的方法,还包括:

从运行在主机上的第二应用接收与要求的第一集合不同的要求的第二集合;

对于一个或多个物理快闪存储器块确定是否适于满足要求的第二集合;

形成物理快闪存储器块的第二列表,所述第二列表中的物理快闪存储器块适于满足要求的第二集合;

从第二应用接收对存储空间的分配的请求;以及

向第二应用分配来自第二列表的第二物理快闪存储器块。

10. 如权利要求9所述的方法,还包括擦除第二物理快闪存储器块。

11. 如权利要求10所述的方法,其中,第二物理快闪存储器块的擦除包括:

当浅擦除过程的预测效果是第一物理快闪存储器块仍然适于满足要求的第一集合时,采用浅擦除过程;以及

当浅擦除过程的预测效果是第一物理快闪存储器块不再适于满足要求的第一集合时,采用正常擦除过程。

12. 一种固态驱动器,包括:

存储控制器,所述存储控制器包括硬件处理电路;和

快闪存储器,包括多个物理快闪存储器块,每个物理快闪存储器块包括多个物理页面,所述存储控制器包括:

形性引擎,包括:

NAND控制器;

保留预测器;

磨损跟踪器;和

原始比特错误率跟踪器;以及

存储虚拟器,包括:

虚拟存储表格;

地址转换块;和

聚类引擎;

所述NAND控制器被配置为对所述快闪存储器执行多个读取操作,一个或多个读取操作包括纠错码解码操作,所述纠错码解码操作产生比特错误计数;

所述原始比特错误率跟踪器被配置为从多个比特错误计数中针对所述多个物理快闪存储器块中的一个或多个计算原始比特错误率;

所述磨损跟踪器被配置为对针对所述多个物理快闪存储器块中的一个或多个执行的编程和擦除周期进行计数;

所述聚类引擎被配置为对于多个编程方法中的每一个,针对一个或多个物理快闪存储器块,从所述原始比特错误率和编程和擦除周期的数量中计算以下各项:

平均响应时间,和

估计的可允许保留时间;

所述虚拟存储表格被配置为从运行在主机上的第一应用中接收要求的第一集合;

所述聚类引擎被配置为从虚拟存储表格接收要求的第一集合,并且对于一个或多个物

理快闪存储器块确定是否适于满足要求的第一集合；

所述聚类引擎被配置为形成物理快闪存储器块的第一列表，所述第一列表中的物理快闪存储器块适于满足要求的第一集合；

所述聚类引擎被配置为从第一应用接收对存储空间的分配的请求；以及

所述聚类引擎被配置为向第一应用分配来自第一列表的第一物理快闪存储器块。

13. 如权利要求12所述的固态驱动器，其中，所述多个编程方法包括：

利用第一步长的递增步进脉冲编程方法；和

利用第二步长的递增步进脉冲编程方法，

其中，第一步长大于第二步长。

14. 如权利要求12所述的固态驱动器，其中，要求的第一集合包括所要求的可允许保留时间和所要求的平均响应时间。

15. 如权利要求12所述的固态驱动器，其中对于一个或多个物理快闪存储器块，确定是否适于满足要求的第一集合包括：

针对所述多个编程方法中的任何编程方法确定：

所计算的平均响应时间是否小于所要求的平均响应时间；以及

所计算的估计的可允许保留时间是否大于所要求的可允许保留时间。

16. 如权利要求12所述的固态驱动器，其中，所述NAND控制器还被配置为擦除第一物理快闪存储器块。

17. 如权利要求12所述的固态驱动器，其中第一物理快闪存储器块的擦除包括：

当浅擦除过程的预测效果是第一物理快闪存储器块仍然适于满足要求的第一集合时，采用浅擦除过程；以及

当浅擦除过程的预测效果是第一物理快闪存储器块不再适于满足要求的第一集合时，采用正常擦除过程。

18. 如权利要求12所述的固态驱动器，其中，针对一个或多个物理快闪存储器块，计算作为性能度量的函数的估计的可允许保留时间，包括：

对作为保留时间的函数的比特错误计数执行线性拟合；以及

计算对于其线性拟合超过最大可接受的原始比特错误率的保留时间。

19. 如权利要求18所述的固态驱动器，其中，所述最大可接受的原始比特错误率是每一百万比特一个比特错误。

20. 如权利要求12所述的固态驱动器，其中：

所述虚拟存储表格还被配置为从运行在所述主机上的第二应用接收与要求的第一集合不同的要求的第二集合；

所述聚类引擎还被配置为：

从虚拟存储表格接收要求的第二集合，并且对于

一个或多个物理快闪存储器块，确定是否适于满足要求的第二集合；

形成物理快闪存储器块的第二列表，所述第二列表中的物理快闪存储器块适于满足要求的第二集合；

从第二应用接收对存储空间的分配的请求；以及

向第二应用分配来自第二列表的第二物理快闪存储器块。

## 形性存储设备

### 技术领域

[0001] 根据本发明的实施例的一个或多个方面涉及快闪存储器，并且更具体地，涉及用于调整快闪存储器设备的操作以适应各种情形的系统和方法。

### 背景技术

[0002] 快闪存储器是其中数据的保留时间可以取决于各种因素的一种形式的持久性存储设备。例如，快闪存储器单元 (flash memory cell) 中的数据的保留时间可以取决于该单元已经经历的编程和擦除周期的数量、所使用的擦除方法、和所使用的编程方法。使用快闪存储器的各种应用可以具有不同的要求，例如，一些应用要求非常长的保留时间，而其它应用仅仅要求较短的保留时间。对于仅仅要求较短的保留时间的应用，以提供较长的保留时间的方式来操作快闪存储器可能不是有利的，这会导致例如降低的性能。

[0003] 因此，存在对于用于调整快闪存储器设备的操作以适应各种情形的系统和方法的需求。

### 发明内容

[0004] 本公开的实施例的各方面专注于一种固态驱动器，其根据使用所述固态驱动器中的存储的应用的要求来选择物理快闪存储器块以及擦除和编程方法。固态驱动器中的磨损跟踪器可以对编程和擦除周期进行计数，并且固态驱动器中原始比特错误率跟踪器可以监视从固态驱动器读取的数据中的原始比特错误。所述应用可以向固态驱动器提供关于可允许保留时间和关于平均响应时间的要求，所述可允许保留时间与由所述应用存储的数据的预期存储时间相对应，并且所述平均响应时间与对于所述快闪存储器的编程次数和读取次数相对应。固态驱动器可以识别适于满足所述要求的物理快闪存储器块，并且可以从所识别的物理快闪存储器块当中向所述应用分配存储空间。

[0005] 根据本发明的实施例，提供了一种用于分配连接到主机的固态驱动器中的快闪存储器的部分的方法，该快闪存储器包括多个物理快闪存储器块，所述方法包括：对快闪存储器执行多个读取操作，一个或多个读取操作包括纠错码解码操作，所述纠错码解码操作产生比特错误计数；从多个比特错误计数计算针对所述多个物理快闪存储器块中的一个或多个的原始比特错误率；对针对所述多个物理快闪存储器块中的每一个执行的编程和擦除周期进行计数；对于多个编程方法中的每一个，针对一个或多个物理快闪存储器块，从所述原始比特错误率以及编程和擦除周期的数量，来计算以下各项：平均响应时间，和估计的可允许保留时间；从运行在主机上的第一应用接收要求的第一集合；针对一个或多个物理快闪存储器块，确定其是否适于满足要求的第一集合；形成物理快闪存储器块的第一列表，所述第一列表中的物理快闪存储器块适于满足要求的第一集合；从第一应用接收对存储空间的分配的请求；以及向所述应用分配来自第一列表的第一物理快闪存储器块。

[0006] 在一个实施例中，所述多个编程方法包括：利用第一步长的递增步进脉冲编程方法；和利用第二步长的递增步进脉冲编程方法，第一步长大于第二步长。

[0007] 在一个实施例中,要求的第一集合包括所要求的可允许保留时间和所要求的平均响应时间。

[0008] 在一个实施例中,所述针对一个或多个物理快闪存储器块确定其是否适于满足要求的第一集合的步骤包括:针对所述多个编程方法中的任何编程方法确定:所计算的平均响应时间是否小于所要求的平均响应时间;以及所计算的估计的可允许保留时间是否大于所要求的可允许保留时间。

[0009] 在一个实施例中,所述方法包括擦除第一物理快闪存储器块。

[0010] 在一个实施例中,所述第一物理快闪存储器块的擦除包括:当浅擦除过程的预测效果是第一物理快闪存储器块仍然适于满足要求的第一集合时,采用浅擦除过程;以及当浅擦除过程的预测效果是第一物理快闪存储器块不再适于满足要求的第一集合时,采用正常擦除过程。

[0011] 在一个实施例中,针对一个或多个物理快闪存储器块的、对所估计的可允许保留时间的计算包括:对作为保留时间的函数的比特错误计数执行线性拟合;以及如果线性拟合超过最大可接受的原始比特错误率,则计算与该线性拟合关联的保留时间。

[0012] 在一个实施例中,所述最大可接受的原始比特错误率是每一百比特一个比特错误。

[0013] 在一个实施例中,所述方法包括:从运行在主机上的第二应用接收与要求的第一集合不同的要求的第二集合;针对一个或多个物理快闪存储器块,确定其是否适于满足要求的第二集合;形成物理快闪存储器块的第二列表,所述第二列表中的物理快闪存储器块适于满足要求的第二集合;从第二应用接收对存储空间的分配的请求;以及向所述应用分配来自第二列表的第二物理快闪存储器块。

[0014] 在一个实施例中,所述方法包括擦除第二物理快闪存储器块。

[0015] 在一个实施例中,第二物理快闪存储器块的擦除包括:当浅擦除过程的预测效果是第一物理快闪存储器块仍然适于满足要求的第一集合时,采用浅擦除过程;以及当浅擦除过程的预测效果是第一物理快闪存储器块不再适于满足要求的第一集合时,采用正常擦除过程。

[0016] 根据本发明的实施例,提供了一种固态驱动器,包括:存储控制器,所述存储控制器包括处理单元;和快闪存储器,包括多个物理快闪存储器块,每个物理快闪存储器块包括多个物理页面,所述存储控制器包括:形性引擎,包括:NAND控制器;保持预测器;磨损跟踪器;和原始比特错误率跟踪器;以及存储虚拟器,其包括:虚拟存储表格;地址转换块;和聚类引擎;所述NAND控制器被配置为对所述快闪存储器执行多个读取操作,一个或多个读取操作包括纠错码解码操作,所述纠错码解码操作产生比特错误计数;所述原始比特错误率跟踪器被配置为针对所述多个物理快闪存储器块中的一个或多个、从多个比特错误计数计算原始比特错误率;所述磨损跟踪器被配置为对针对所述多个物理快闪存储器块中的一个或多个执行的编程和擦除周期进行计数;所述聚类引擎被配置为对于多个编程方法中的每一个,针对一个或多个物理快闪存储器块,从所述原始比特错误率以及编程和擦除周期的数量来计算以下各项:平均响应时间,和估计的可允许保留时间;所述虚拟存储表格被配置为从运行在主机上的第一应用接收要求的第一集合;所述聚类引擎被配置为从虚拟存储表格接收要求的第一集合,以及针对一个或多个物理快闪存储器块确定其是否适于满足要求

的第一集合；所述聚类引擎被配置为形成物理快闪存储器块的第一列表，所述第一列表中的物理快闪存储器块适于满足要求的第一集合；所述聚类引擎被配置为从第一应用接收对存储空间的分配的请求；以及所述聚类引擎被配置为向所述应用分配来自第一列表的第一物理快闪存储器块。

[0017] 在一个实施例中，所述多个编程方法包括：利用第一步长的递增步进脉冲编程方法；和利用第二步长的递增步进脉冲编程方法，第一步长大于第二步长。

[0018] 在一个实施例中，要求的第一集合包括所要求的可允许保留时间和所要求的平均响应时间。

[0019] 在一个实施例中，所述针对一个或多个物理快闪存储器块确定其是否适于满足要求的第一集合包括：针对所述多个编程方法中的任何编程方法确定：所计算的平均响应时间是否小于所要求的平均响应时间；以及所计算的估计的可允许保留时间是否大于所要求的可允许保留时间。

[0020] 在一个实施例中，所述NAND控制器还被配置为擦除第一物理快闪存储器块。

[0021] 在一个实施例中，第一物理快闪存储器块的擦除包括：当浅擦除的预测结果是第一物理快闪存储器块仍然适于满足要求的第一集合时，采用浅擦除过程；以及当浅擦除的预测结果是第一物理快闪存储器块不再适于满足要求的第一集合时，采用正常擦除过程。

[0022] 在一个实施例中，所述针对所述多个物理快闪存储器块中的一个或多个的对作为性能度量的函数的估计的可允许保留时间的计算包括：对作为保留时间的函数的比特错误计数执行线性拟合；以及如果线性拟合超过最大可接受的原始比特错误率，则计算与该线性拟合关联的保留时间。

[0023] 在一个实施例中，所述最大可接受的原始比特错误率是每一百比特一个比特错误。

[0024] 在一个实施例中，所述虚拟存储表格还被配置为从运行在所述主机上的第二应用接收与要求的第一集合不同的要求的第二集合；所述聚类引擎还被配置为：从虚拟存储表格接收要求的第二集合，并且针对一个或多个物理快闪存储器块确定其是否适于满足要求的第二集合；形成物理快闪存储器块的第二列表，所述第二列表中的物理快闪存储器块适于满足要求的第二集合；从第二应用接收对存储空间的分配的请求；以及向所述应用分配来自第二列表的第二物理快闪存储器块。

[0025] 本发明的示例实施例可以针对各种情形来适当地调整快闪存储器设备的操作。因此，示例实施例可以在设备的性能和寿命方面带来好处。

## 附图说明

- [0026] 图1A是作为保留时间的函数的原始比特错误率的图形；

- [0027] 图1B是作为编程和擦除周期的数量的函数的原始比特错误率的图形；

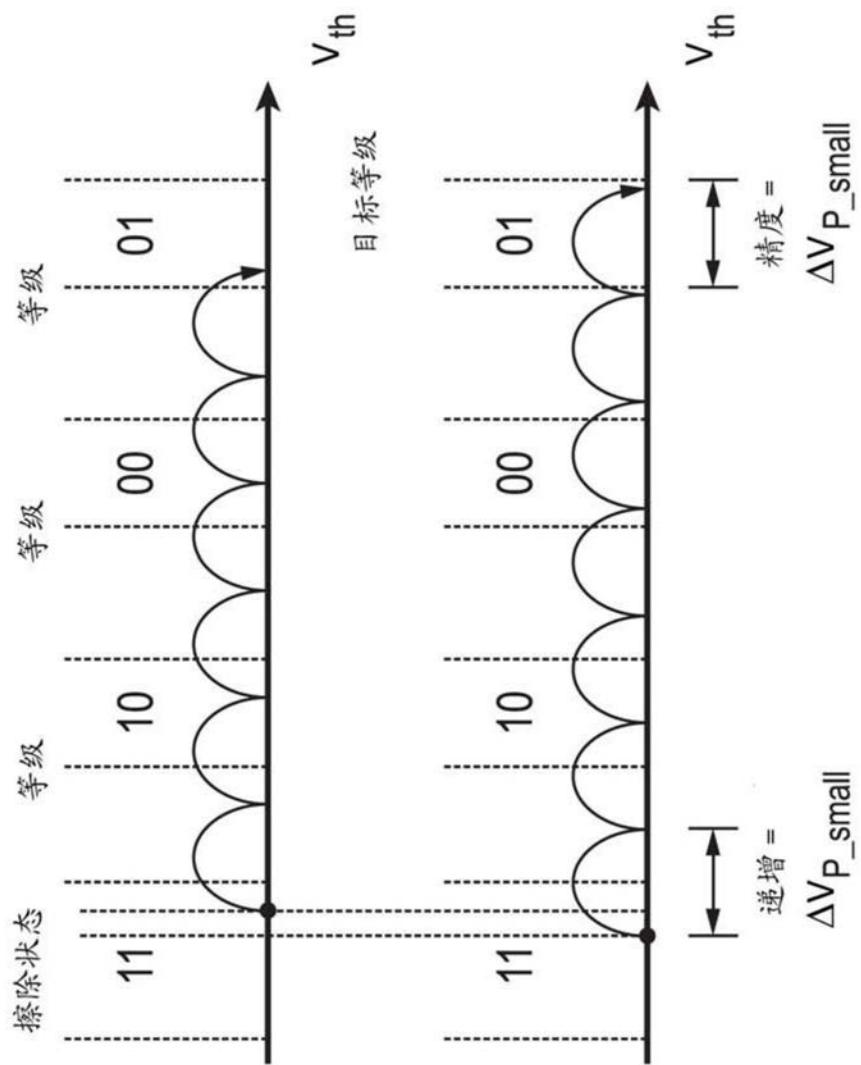

- [0028] 图2A是根据本发明的实施例的电压步进序列(voltage step sequence)的示图；

- [0029] 图2B是根据本发明的实施例的电压步进序列的示图；

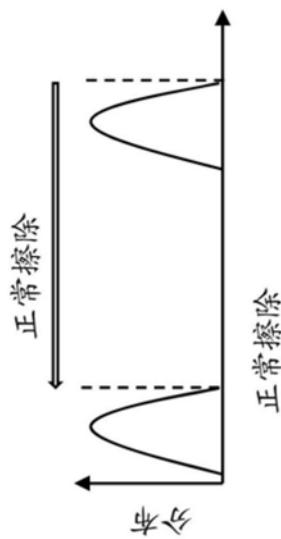

- [0030] 图3A是根据本发明的实施例的用于已编程状态和已擦除状态的电压分布的图形；

- [0031] 图3B是根据本发明的实施例的用于已编程状态和已擦除状态的电压分布的图形；

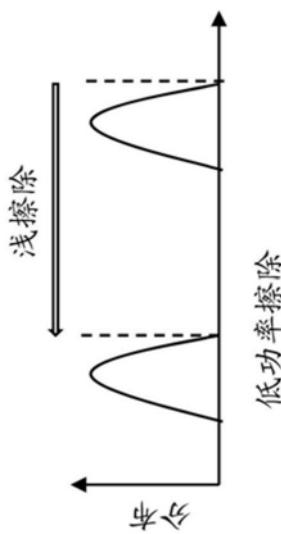

- [0032] 图4是根据本发明的实施例的作为保留时间的函数的原始比特错误率的图形；

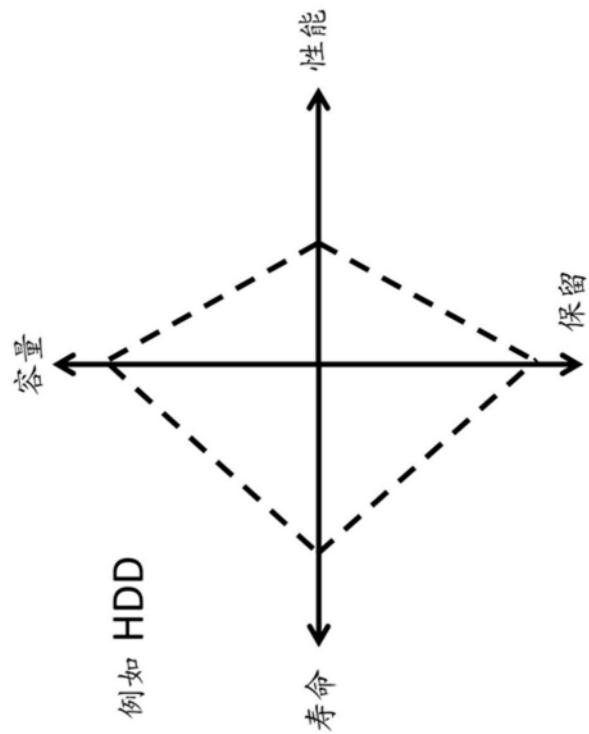

- [0033] 图5A是硬盘驱动器的四轴特性的示图；

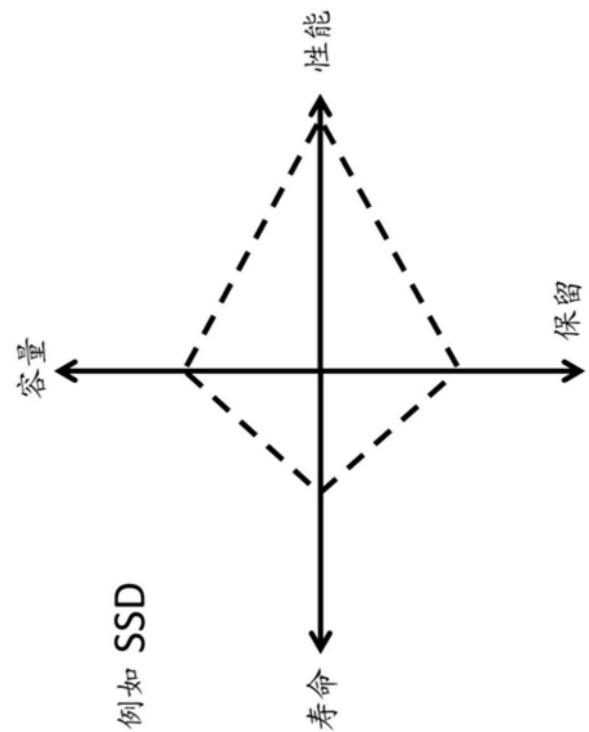

- [0034] 图5B是根据本发明的实施例的固态驱动器的四轴特性的示图；

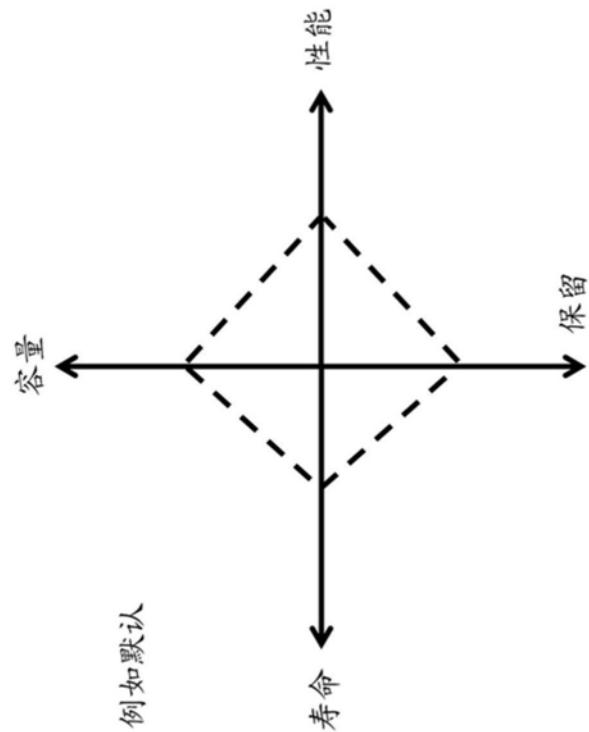

- [0035] 图5C是根据本发明的实施例的固态驱动器的四轴特性的示图；

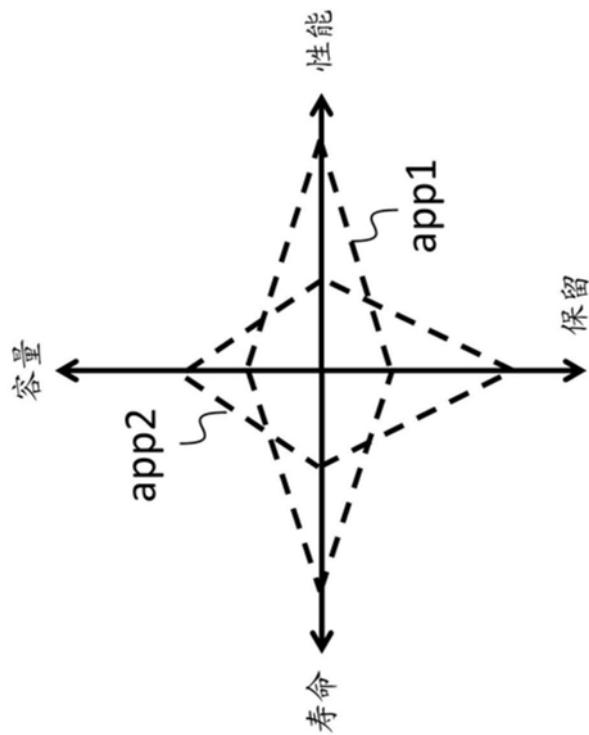

- [0036] 图5D是根据本发明的实施例的固态驱动器的四轴特性的示图；

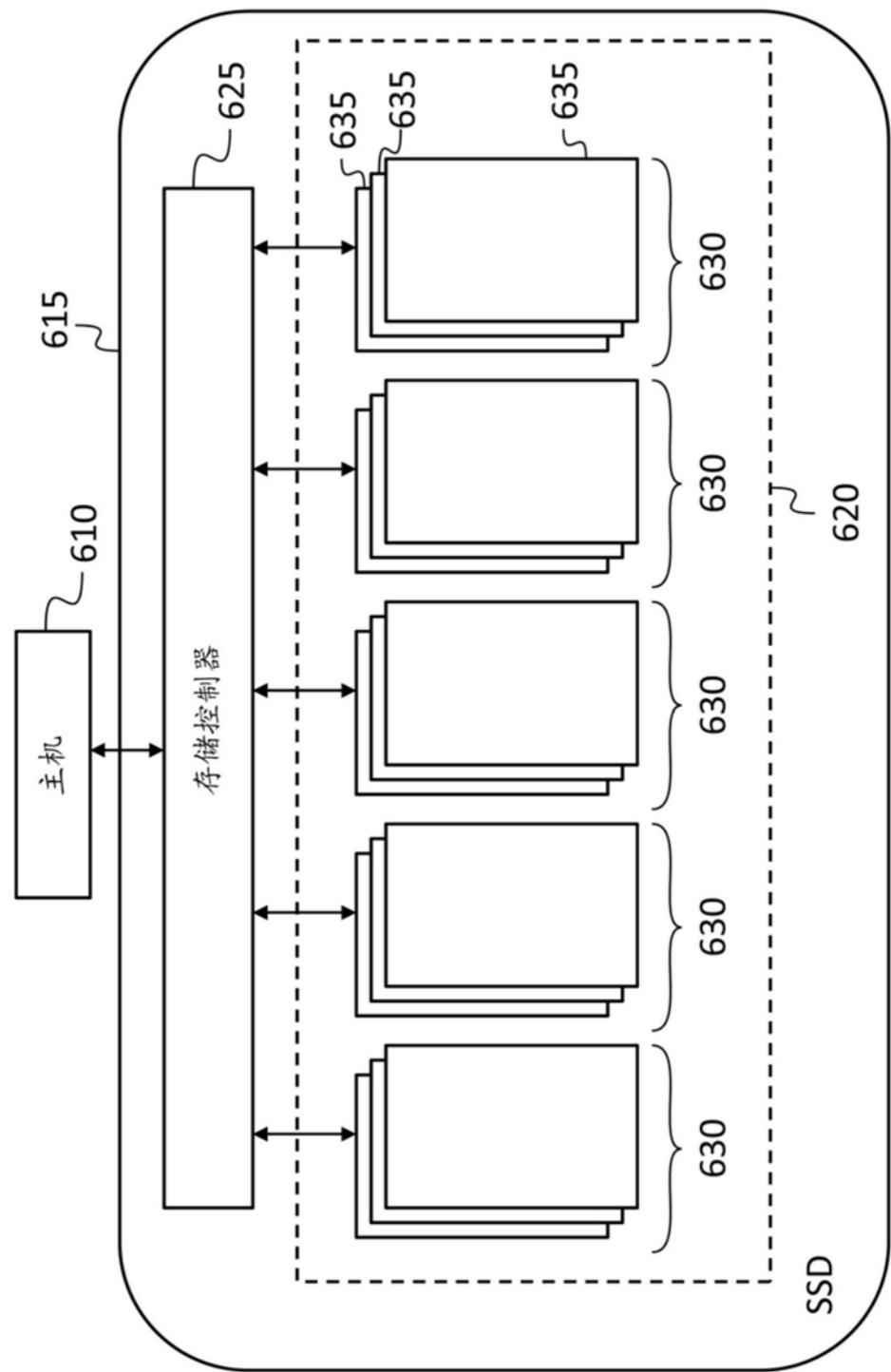

- [0037] 图6是根据本发明的实施例的主机和固态驱动器的框图；

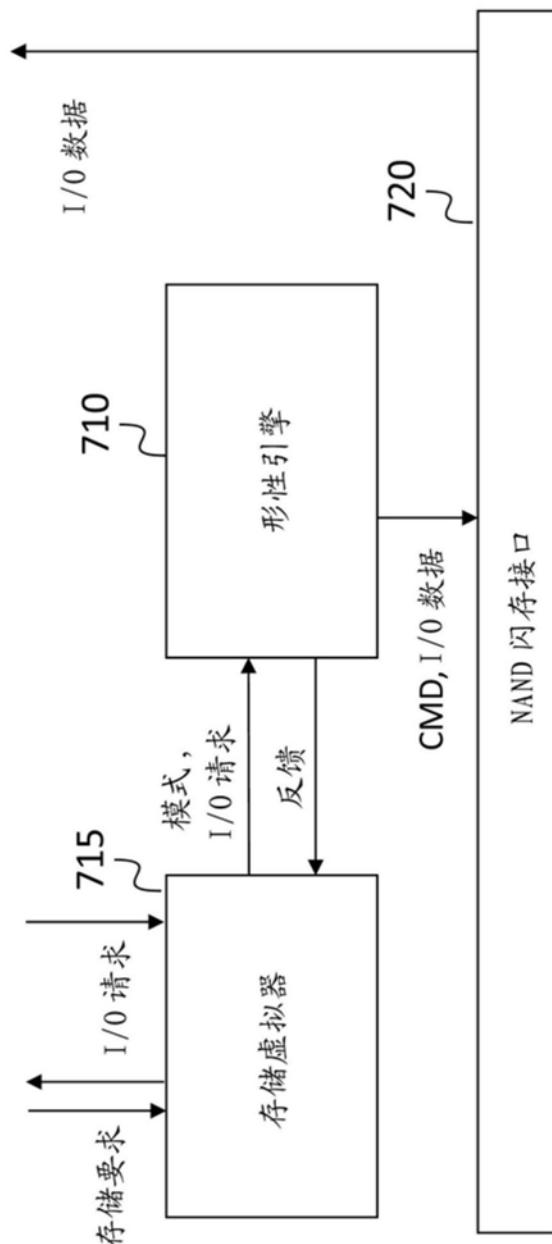

- [0038] 图7是根据本发明的实施例的形性系统的框图；

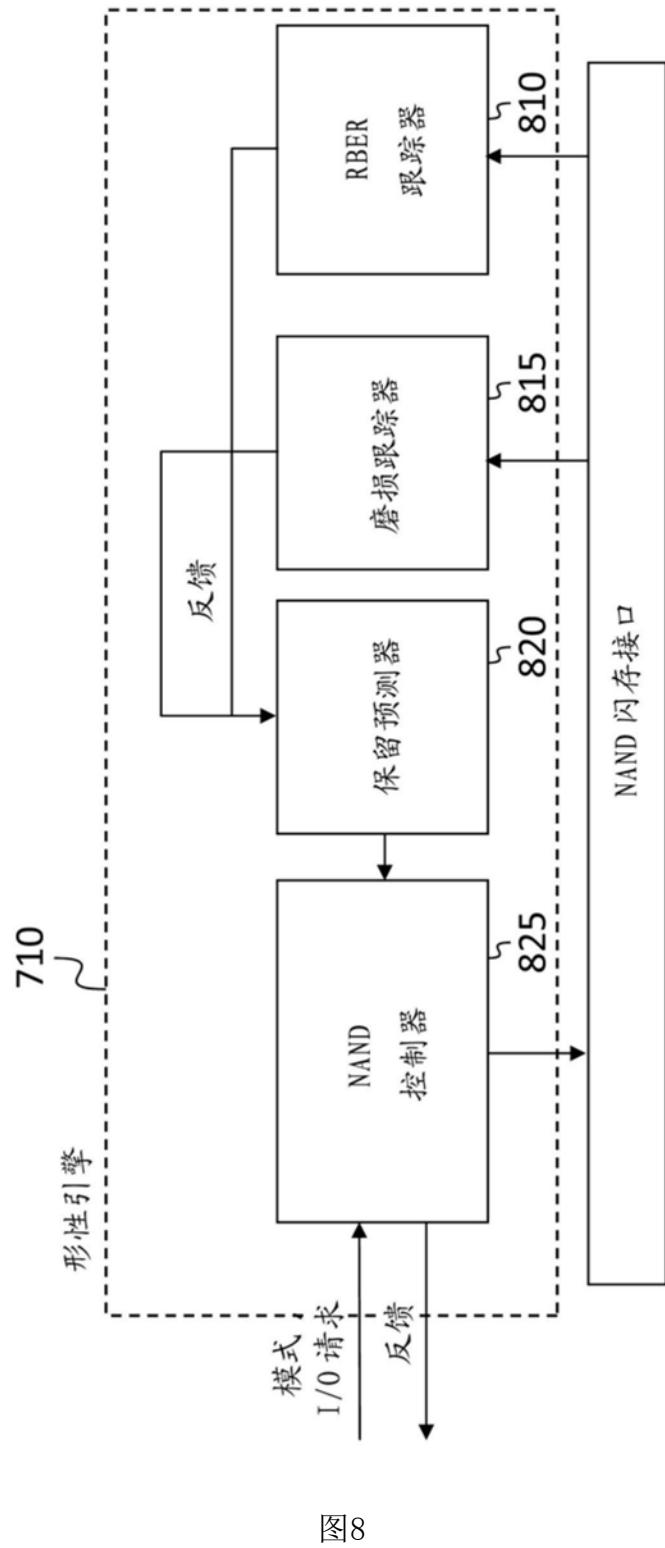

- [0039] 图8是根据本发明的实施例的形性引擎的框图；

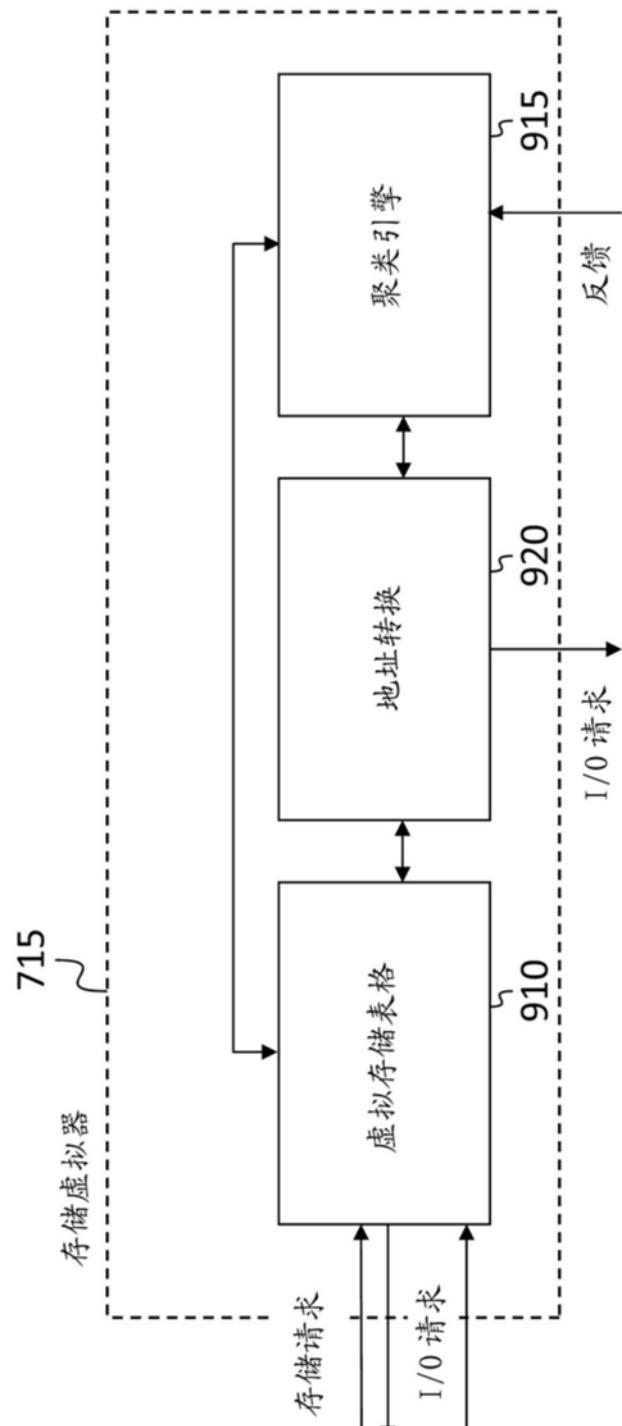

- [0040] 图9是根据本发明的实施例的存储虚拟器的框图；

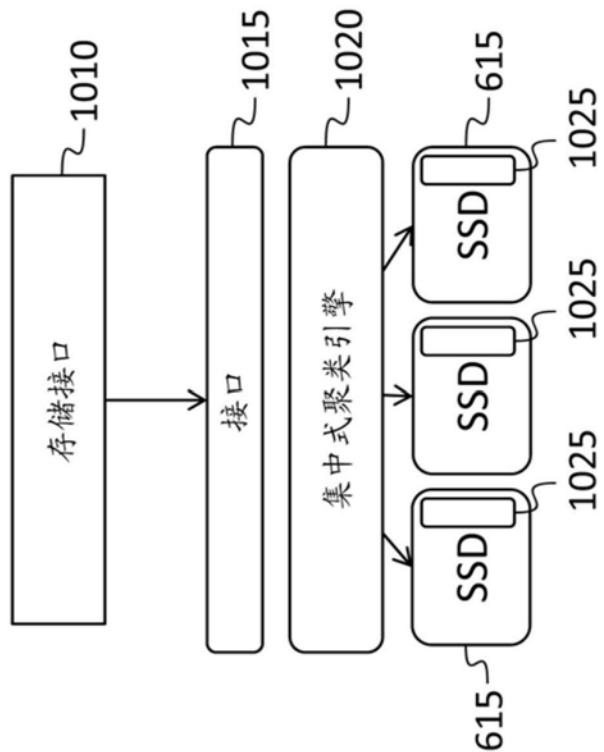

- [0041] 图10A是根据本发明的实施例的具有多个薄聚类引擎的系统的框图；和

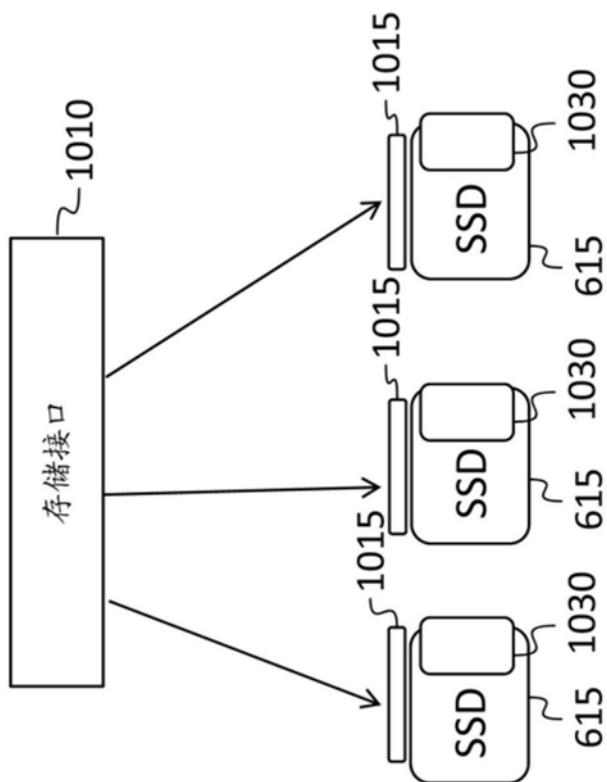

- [0042] 图10B是根据本发明的实施例的具有多个厚聚类引擎的系统的框图。

## 具体实施方式

[0043] 下面结合附图阐述的详细描述被意图作为对于根据本发明提供的形性 (morphic) 存储设备的示例实施例的描述，并且不被意图代表其中可以构建或者利用本发明的仅有形式。该描述结合所说明的实施例来阐述本发明的特征。然而，将理解，可以通过意图被包含在本发明的精神和范围内的其它实施例来实现相同或者等同的功能和结构。如在本文中的别处所表示的，相似的元素标号意图指示相似的元素或特征。

[0044] 诸如固态驱动器的快闪存储器设备是具有在一些方面与诸如硬盘驱动器的其它持久性存储器设备不同的特性的持久性存储器设备。在快闪存储器中，浮置栅极上的电荷可以用来存储信息，并且所述电荷可以随着时间而从浮置栅极泄露，导致所存储的信息的丢失或部分丢失。而且，数据随着时间而丢失的程度取决于若干因素。

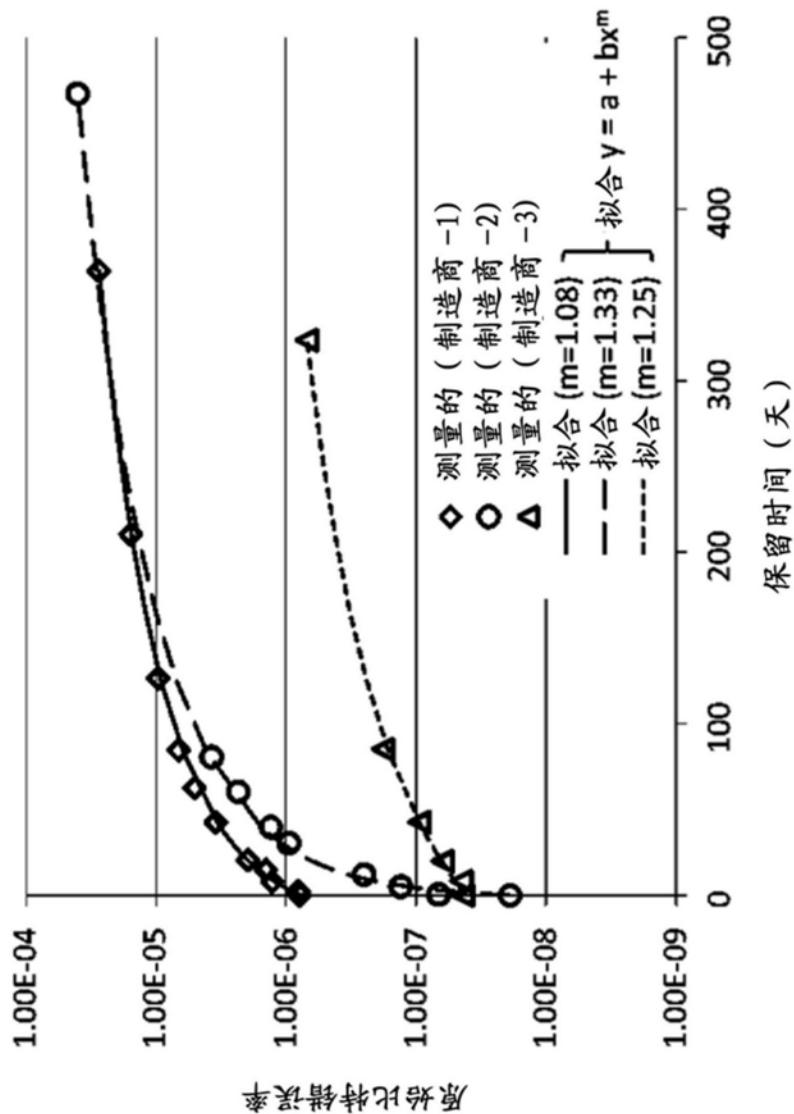

[0045] 参考图1A，从快闪存储器读取的数据的原始比特错误率可以，如图所示，取决于保留时间，即，数据被写入时和数据被读取时之间的时间。所述比特错误率还可以取决于设备的性质，由不同的制造商制造的设备表现出不同的比特错误率，该比特错误率是保留时间的函数。

[0046] 参考1B，原始比特错误率可以不仅仅取决于保留时间，还取决于快闪存储器已经经受的 (subjected to) 编程和擦除周期的数量，随着编程和擦除周期的数量增加，快闪存储器在更长的时间段里存储数据的能力下降。在图1B中，曲线105示出3年保留比特错误率，曲线110示出1年保留比特错误率，曲线115示出3月保留比特错误率，曲线120示出3星期保留比特错误率，曲线125示出3天保留比特错误率，曲线130示出编程干扰比特错误率，曲线135示出1天保留比特错误率，曲线140示出读取比特错误率，并且曲线145示出擦除比特错误率。

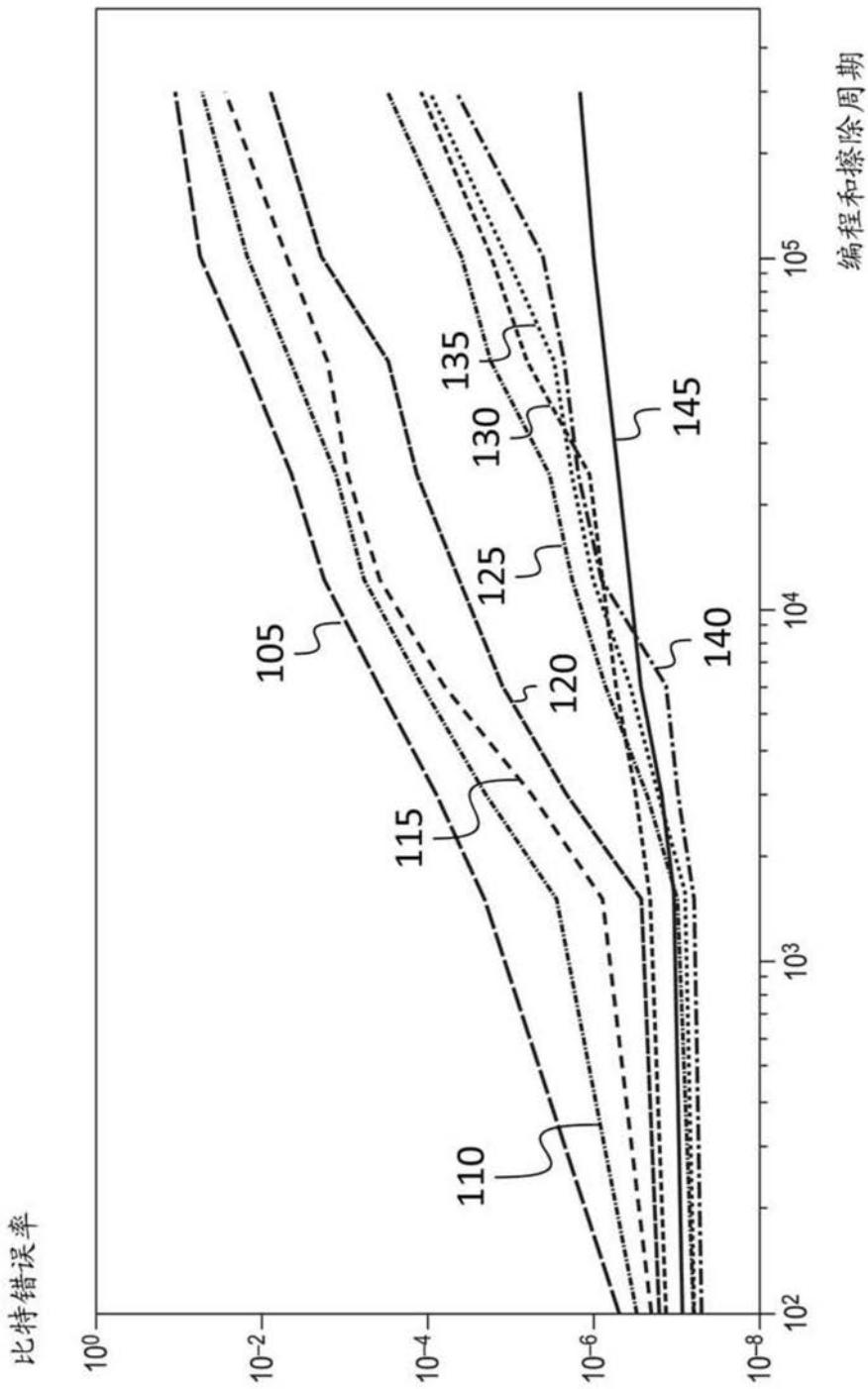

[0047] 参考图2A和图2B，当递增步进脉冲编程 (ISPP) 被使用时，用于编程操作的步长 (step size) 可以影响能够被放置在浮置栅极上的电荷的精度。因此，在所有其它因素都相等的情况下，使用的步长越小，原始比特错误率越低。然而，更小的步长的使用可以导致编程操作花费更长时间来完成。

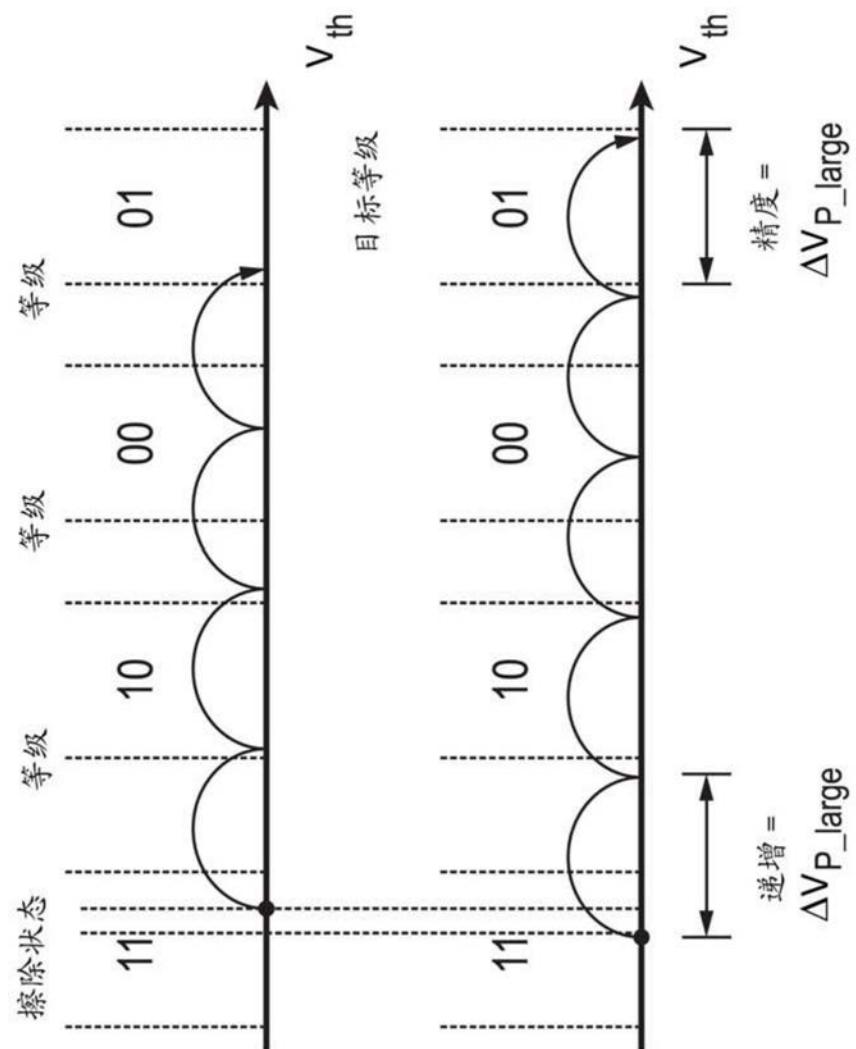

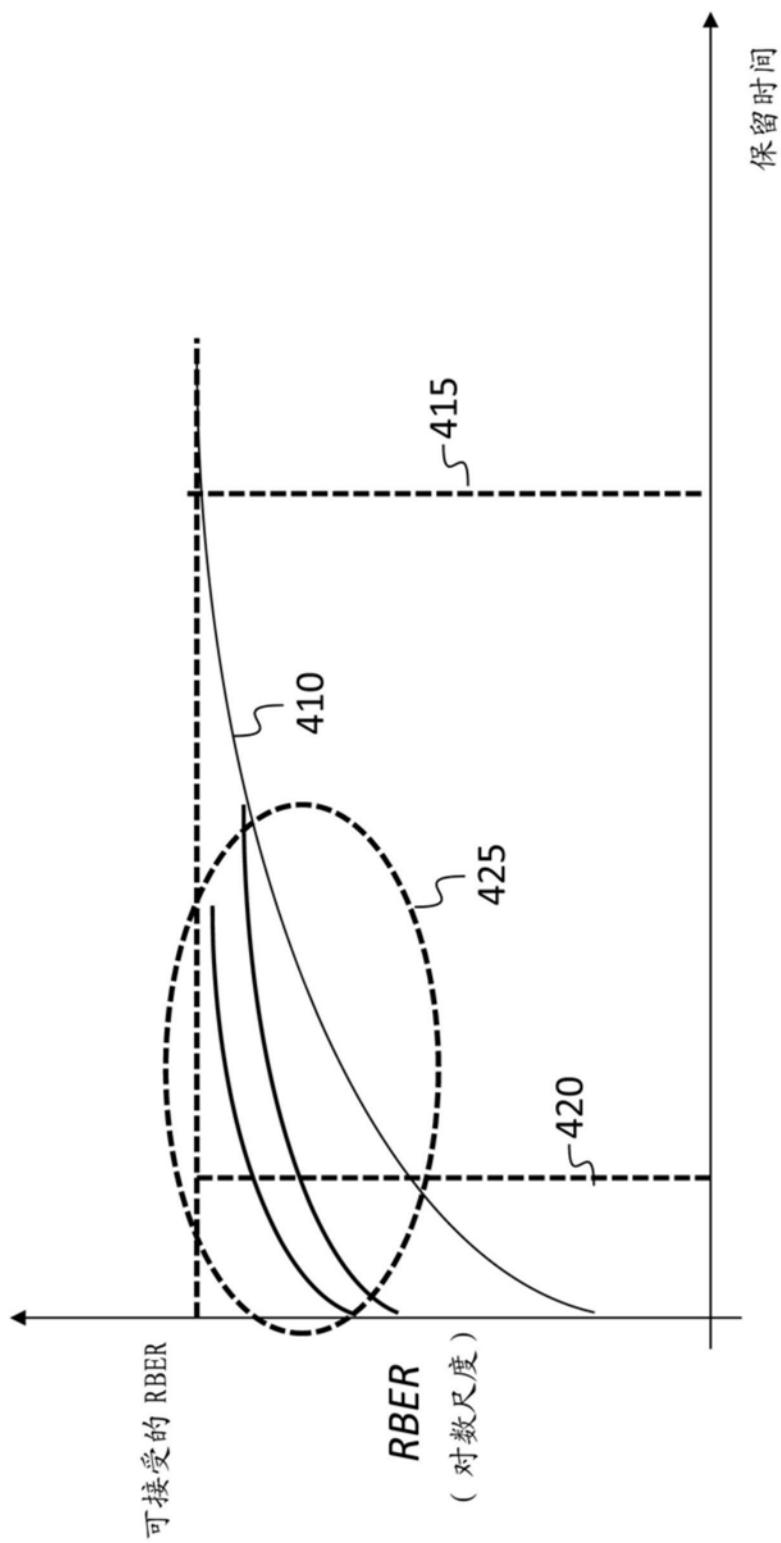

[0048] 参考图3A和图3B，使用浅擦除过程来擦除存储器 (图3B) 与正常擦除过程 (图3A) 相比可以导致延长的寿命 (也就是说，在大量的编程和擦除周期之后，较长的可允许保留时间)，所述浅擦除过程倾向于使存储器的劣化小于正常擦除过程。如这里所使用的，所述“可

允许保留时间”是在维持可接受的原始比特错误率的同时、数据可以被留下存储在快闪存储器中的时间。

[0049] 可允许保留时间可以取决于可接受的原始比特错误率；在一些实施例中，可接受的原始比特错误率是 $10^{-6}$ ，也就是说，每一百万个比特有一个错误。然而，对于具有相同历史的设备而言，与使用正常擦除过程相比，使用浅擦除过程可以在任何给定的编程和擦除周期期间导致更高的比特错误率，因为浅擦除过程可以缩小能够被存储在浮置栅极上的电荷值的范围。

[0050] 因而，可以考虑到所应用的保留时间要求来选择编程和擦除过程。例如，一些应用（诸如网络高速缓存）可能要求仅仅几天的保留时间，而其它应用可能要求一年或更长的保留时间。例如，对于要求仅仅几天的保留时间的应用，使用已经经受大量的编程和擦除周期的快闪存储器的物理块或许是可接受的，或者使用具有大步长的ISPP或许是可能的。

[0051] 参考图4，例如，快闪存储器的物理块和提供较长可允许保留时间415的擦除和编程过程（由原始比特错误率曲线410表示的）可以用于预计将被留下来长时间存储的数据。可以使用提供较短的可允许保留时间的过程425（例如，浅擦除过程或者具有大步长的ISPP）来处理对其而言较短的可允许保留时间420就足够的数据。

[0052] 参考图5A-图5D，诸如硬盘驱动器或者固态驱动器的持久性存储设备可以具有若干相关特性。例如，在吞吐量或者延迟方面，或者在执行读取操作、擦除操作、或者写入（或者编程）操作所需要的时间方面，这样的设备可以提供给定水平的性能（“Perf.”）。

[0053] 对于固态驱动器，完成擦除操作或者编程操作所需要的时间可以显著不同于（例如，长于）完成读取操作所需要的时间，并且平均响应时间可以用来表示设备的性能的特征。可以从读取时间、擦除时间和编程时间来计算这个平均响应时间，并且可以考虑到对于被写入的每条数据的读取的数量的典型比率、和用于降低较长的擦除时间和编程时间的影响的缓解措施（诸如，缓冲）的使用，来计算所述平均响应时间。

[0054] 在一些实施例中，平均响应时间可以如下定义：

$$T_{avg} = (\sum_{1=t}^{N_{read}} T_{read,t} + \sum_{1=t}^{N_{write}} T_{write,t}) / (N_{read} + N_{write})$$

[0055] 其中 $N_{read}$ 和 $N_{write}$ 分别是在指定时间段（例如，10秒）上由基准测试（benchmarking test）执行的读取和写入的数量，并且其中 $T_{read,i}$ 和 $T_{write,i}$ 分别是在所述测试期间的第*i*读取时间和第*i*写入时间。

[0056] 设备可以具有一定的寿命，对于硬盘驱动器而言，可以通过移动部件所经历的磨损速率来确定所述寿命，并且对于固态驱动器而言，可以通过由编程和擦除周期导致的劣化来确定所述寿命。设备可以具有容量（“Cap.”）和可允许保留时间（“Ret.”），所述容量（“Cap.”）也就是设备能够存储的数据的最大量。

[0057] 从图5A和图5B可以看出，例如，与固态驱动器相比，硬盘驱动器可以具有更大的容量和更长的保留时间，但是更短的寿命和更慢的响应时间（也就是说，更差的性能）。类似地，从图5C和图5D可以看出，与固态驱动器的默认特性（图5C）相比，第一应用（“app1”，图5D）可以具有高性能要求和短保留时间要求，并且第二应用（“app2”，图5D）可以具有低性能要求和长保留时间要求。

[0058] 参考图6，在一个实施例中，主机610可以连接到固态驱动器615，并且可以将固态驱动器615用于持久性存储。固态驱动器615可以是被配置为提供持久性存储的封装

(enclosure) 中的独立 (self-contained) 单元。

[0060] 固态驱动器615可以通过存储接口 (例如, 通过通常被主机610用于存储操作的连接器和协议) 连接到主机610。所述连接器和协议可以遵照, 例如, 串行高级技术附件 (Serial Advanced Technology Attachment, SATA), 光纤通道, 串行连接SCSI (Serial Attached SCSI, SAS), 非易失性存储器快速 (Non Volatile Memory Express, NVMe) 等等, 或者遵照更通用的接口, 诸如以太网或通用串行总线 (Universal Serial Bus, USB)。

[0061] 固态驱动器615中的快闪存储器620可以被组织成物理快闪存储器块630 (或者“闪存块”或者“快闪存储器块”) 和物理页面635。物理快闪存储器块630可以是在一个操作中可擦除的存储器的最小单元, 并且物理页面635可以是在一个操作中能够被写入的存储器的最小单元。每个物理快闪存储器块630可以包括多个物理页面635。

[0062] 主机610可以与海量存储设备交互, 所述海量存储设备具有针对逻辑页码的存储访问请求, 例如请求将数据存储在任何逻辑页码处的页面中, 请求读取存储在任何逻辑页码处的页面中的数据, 或者请求擦除存储在任何逻辑页码处的页面中的数据。对于固态驱动器615, 静态逻辑到物理 (L-P) 映射可以不被使用, 因为读取/写入尺寸和擦除尺寸之间的差异决定了将数据从一个物理位置不断地移动到另一物理位置的垃圾控制机制, 因此, 存在对于动态L-P映射的需求。

[0063] 闪存转换层 (flash translation layer) 可以将逻辑页码动态地转换或者映射到物理页码。当在任何逻辑页码处的页面中的数据上覆盖新数据时, 接下来闪存转换层可以将当前与该逻辑页码相对应的物理页面635标记为无效 (而不是擦除包含这个物理页面635的物理快闪存储器块630), 更新从逻辑页码到物理页面635的映射以便将所述逻辑页码映射到新的物理页面635, 并且将所述新数据写入所述新的物理页面635。闪存转换层可以实施在运行在固态驱动器615中的存储控制器625 (例如, 微控制器) 上的软件中。

[0064] 可以利用纠错码来对从主机610接收的用于编程到快闪存储器620中的数据进行编码, 并且当从快闪存储器620读取数据时, 可以利用纠错码解码操作来处理读取的原始 (raw) 数据, 该纠错码解码操作可以产生错误被纠正的解码数据和比特错误计数 (即, 通过纠错码解码操作已纠正的比特错误的数量的计数)。

[0065] 偶尔闪存转换层可以执行被称为“垃圾收集”的操作。在这个操作中, 在物理快闪存储器块630中剩余的有效物理页面635已经被移动到一个或多个其它物理快闪存储器块630中的物理页面635以后, 包含已经被标记为无效的物理页面635的大比例 (例如, 超过设置的阈值的比例) 的任何物理快闪存储器块630可以被擦除, 以使得最新擦除的物理快闪存储器块630可用于新数据的写入。

[0066] 多个应用可以在主机610中运行 (例如, 执行), 并且可以生成可以被发送到固态驱动器615的输入/输出 (I/O) 请求 (例如, 擦除请求、编程 (写入) 请求、和读取请求)。每个这样的应用可以具有对持久性存储的特性的要求, 例如, 规定最大可接受的平均响应时间和最小可允许保留时间的要求。

[0067] 在一些实施例中, 这些要求可以被固态驱动器615用来确定哪些快闪存储器块630可以被用于存储用于应用的数据, 并且可以被固态驱动器615用来选择, 例如, 将在写入用于所述应用的数据时使用的步长。

[0068] 当每个应用开始运行时, 其可以向固态驱动器615注册, 从而向固态驱动器615标

识它自身并且将它的存储要求发送到固态驱动器615。以这种方式,固态驱动器615可以保证由任何应用生成的输入/输出请求都以满足该应用的要求的方式来处理。固态驱动器615的、根据可应用的要求对输入/输出请求自适应地做出响应的品质,将在本文中被称为“形性(morphic)”。

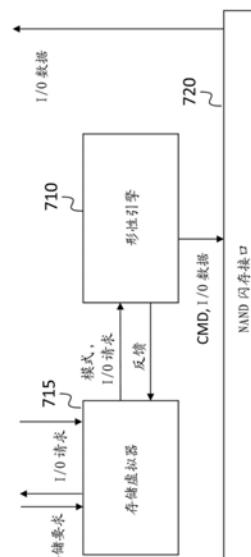

[0069] 参考图7,在一些实施例中,根据来自应用的请求,形性引擎710和存储虚拟器715可以在存储控制器625中被采用,以向所述应用分配快闪存储器。形性引擎710可以连接到NAND闪存接口720以处理由应用经由存储虚拟器715发送的输入/输出(I/O)请求。

[0070] 参考图8,在一些实施例中,形性引擎710可包括原始比特错误率(RBER)跟踪器810、磨损跟踪器815、保留预测器820和NAND控制器825。

[0071] 原始比特错误率跟踪器810可以监视每个物理快闪存储器块630的原始比特错误率。原始比特错误率跟踪器810可以通过在每次响应于主机请求而从快闪存储器读取数据时跟踪比特错误计数来实现这个监视。在一些实施例中,比特错误计数可以作为额外的条目被记录在闪存转换层中。

[0072] 当例如在某些时候在物理快闪存储器块630中尚未执行主机请求的读取操作时,原始比特错误率跟踪器810还可以执行“采样”读取操作(也就是说,并非源于主机请求的读取操作)以获得物理快闪存储器块630中的原始比特错误率的更新的测量。以这种方式,原始比特错误率跟踪器810可以随着时间而创建列出针对每个物理快闪存储器块630的所观察到的比特错误率的表格。

[0073] 在一些实施例中,所述表格可以具有用于每个物理快闪存储器块630的多个条目,例如,用于利用使用大步长的ISPP编程的存储器单元的第一观察到的原始比特错误率、和用于利用使用小步长的ISPP编程的存储器单元的第二观察到的原始比特错误率。所述表格可以被存储在非易失性存储器中(例如,存储在快闪存储器620中),从而在对于固态驱动器615的电力供应被暂时中断时该表格被保存(preserve)。

[0074] 磨损跟踪器815可以监视在快闪存储器上执行的编程操作和擦除操作,并且对针对每个物理快闪存储器块630执行的编程和擦除周期的数量进行计数。在一些实施例中,还出于磨损均衡(wear-leveling)的目的,在闪存转换层中,所执行的编程和擦除周期的数量可以被跟踪。以这种方式,磨损跟踪器815可以随着时间而创建列出(针对每个物理快闪存储器块630)已经在物理快闪存储器块630上执行的编程和擦除周期的数量的表格。

[0075] 在一些实施例中,所述表格可以具有用于每个物理快闪存储器块630的多个条目,例如,使用浅擦除过程执行的编程和擦除周期的第一计数、和使用正常擦除过程执行的编程和擦除周期的单独的第二计数。所述表格可以被存储在非易失性存储器中(例如,存储在快闪存储器620中),从而在对于固态驱动器615的电力供应被暂时中断时该表格被保存。

[0076] 保留预测器820可以用来针对各种擦除和编程方法中的每一个来估计每个物理快闪存储器块630的可允许保留时间。在一个实施例中,保留预测器820可以对比特错误率执行线性拟合(或者指数拟合),所述比特错误率是(如从原始比特错误率跟踪器810报告的)保留时间的函数,并且保留预测器820可以计算可允许保留时间,所述可允许保留时间是在这个拟合的原始比特错误率等于阈值(也就是说,最大可接受的原始比特错误率(例如,每一百万比特一个比特错误)时的保留时间的值。在一些实施例中,保留预测器820可以参考由磨损跟踪器815生成的所述表格来计算可允许保留时间。在一些实施例中,所述阈值可以

是可编程变量。

[0077] NAND控制器825可以是可以与快闪存储器620直接交互的驱动器例程,其发布(issue)块级(block level)和页面级(page level)的读取、写入、和擦除命令。NAND控制器825可以处理在从快闪存储器620读取的原始数据中检测和纠正比特错误的纠错码解码算法。NAND控制器825还可以将信息从保留预测器820转发到存储虚拟器715。NAND控制器825还可以提供对擦除过程(例如,使用了浅擦除还是正常擦除)和编程过程(例如,将在采用ISPP的编程操作中采用的步长)的控制。

[0078] 参考图9,在存储虚拟器715中,虚拟存储表格910可以针对在固态驱动器615处注册的每个应用来存储要求的集合,其指示例如最大可接受的平均响应时间和最小可允许保留时间。所述要求还可以包括容量要求,其指示多少个块将潜在地被所述应用使用。

[0079] 聚类引擎(clustering engine)915可以从虚拟存储表格910接收信息并且可以生成用于在固态驱动器615处注册的每个应用的聚类列表(cluster list),所述聚类是根据保留预测器820的计算而适于满足各个应用的要求的物理快闪存储器块630的集合,并且所述聚类列表是所述聚类中的物理快闪存储器块630的列表。

[0080] 地址转换块920(其可以是闪存转换层的一部分)可以维护将逻辑页面地址映射到快闪存储器620中的物理页面地址的交叉参考表格。

[0081] 每次作为一个或多个聚类中的成员的物理快闪存储器块630被擦除时,聚类引擎915都可以重新评估所述物理快闪存储器块630是否保持具有成为所述聚类中的成员的资格(该资格潜在地已经被另外的编程和擦除周期影响),并且可以相应地更新所述聚类和聚类列表。

[0082] 当物理快闪存储器块630适于满足与聚类相对应的应用的要求时,也就是说,当对于一些编程方法而言(例如,对于将在ISPP中使用的一些步长而言),应用的平均响应时间要求和可允许保留时间要求两者都被并行或者同时满足时,物理快闪存储器块630可以被认为具有成为所述聚类中的成员的资格。

[0083] 如果应用具有对于可用的物理快闪存储器块630中的任何一个而言都太过严格(stringent)的要求,则最接近满足所述要求的一个或多个物理快闪存储器块630可以被认为具有成为用于所述应用的聚类中的成员的资格。在这种情形中,所述应用可以被警告不满足它的要求的物理快闪存储器块630正被分配给它。这个确定可以考虑到物理快闪存储器块630已经经历的编程和擦除周期的历史来做出,该历史包括,如果物理快闪存储器块630是被新擦除的,那么最近的擦除是使用浅擦除过程还是正常擦除过程来执行的。

[0084] 在一些实施例中,在垃圾收集期间,正通过垃圾收集回收的块的擦除可以被推迟,直到该块被分配给特定的应用。在这个实施例中,当如果块是使用正常擦除来擦除的,则该块将适于满足与聚类相对应的应用的要求时,聚类引擎915可以将该块包括在该聚类中。在块被分配给应用之后,如果浅擦除足以允许该块满足所述应用的要求,则可以使用浅擦除来擦除该块;否则,使用正常擦除来擦除该块。

[0085] 在任何操作中,当应用做出对持久性存储的分配的请求时,所述请求可以被虚拟存储表格910接收,所述虚拟存储表格910可以向聚类引擎915做出对于一个或多个有资格的物理快闪存储器块630(也就是说,满足所述应用的要求的物理快闪存储器块630)的列表的请求。然后地址转换块920可以在有资格的物理快闪存储器块630中的一个或多个内分配

由所述应用请求的(多个)存储区域,并且可以更新从逻辑页码到物理页码的映射。

[0086] 当所述应用随后将数据写入固态驱动器615时,可以使用与应用的要求一致的编程参数来执行编程操作(例如,具有满足平均响应时间要求足够大并且满足可允许保留时间要求足够小的步长的ISPP)。

[0087] 参考图10A和图10B,在一些实施例中,多个固态驱动器615可以连接在一起,以形成向主机610提供存储的逻辑存储层。在这样的实施例中,共享聚类信息以使得可以根据所述聚类信息来做出存储分配决定,可能是有帮助的。

[0088] 例如,在图10A中,如果应用(通过存储接口1010和第二接口1015)做出对于大量存储的分配请求,则维护由固态驱动器615的各个薄聚类引擎1025生成的聚类列表的副本的集中式聚类引擎1020,可以从固态驱动器615中的一个或多个中的一个或多个有资格的物理快闪存储器块630分配空间。

[0089] 在图10B的实施例中,每个固态驱动器615可以包括厚聚类引擎1030,其可以维护除了它自己的聚类列表之外的、其它厚聚类引擎1030中的每一个的聚类列表的副本。在这个实施例中,当固态驱动器615(通过存储接口1010和第二接口1015)接收到对于超出了固态驱动器615的有资格的物理快闪存储器块630内的可用量的存储量的分配请求时,所述固态驱动器615可以将该未满足分配要求的请求传播到另一固态驱动器615(如果该另一固态驱动器615不能够接纳该未满足分配要求的请求,则其进而可以将该请求传播到又一固态驱动器615)。

[0090] 考虑到前述内容,固态驱动器615可以通过调整擦除参数和编程参数、以及选择适应应用的要求的物理快闪存储器块630,来高效满足各种应用的存储要求。以这种方式,例如,长保留时间可以被提供给要求长保留时间的应用,并且更短的保留时间可以与例如相应的性能的提高一起被提供给仅仅要求更短的保留时间的应用。

[0091] 根据这里描述的本发明的实施例的固态驱动器615和/或任何其它相关设备或者组件可以利用任何合适的硬件、固件(例如专用集成电路)、软件、或者它们的合适的组合来实施。例如,固态驱动器615的各种组件可以被形成在一个集成电路(IC)芯片上或者形成在分开的IC芯片上。另外,固态驱动器615的各种组件可以被实施在柔性印刷电路薄膜、带载封装(TCP)、或者印刷电路板(PCB)上,或者与固态驱动器615形成在相同的基底上。

[0092] 另外,固态驱动器615的各种组件可以是在一个或多个计算设备中的一个或多个处理器上运行的、执行计算机程序指令并且与其它系统组件交互以执行这里描述的各种功能的进程或者线程。计算机程序指令可以被存储在存储器中,所述存储器可以被实施在使用诸如例如随机访问存储器(RAM)的标准存储器设备的计算设备中。所述计算机程序指令还可以被存储在其它非瞬时性计算机可读介质(诸如,例如,CD-ROM、闪存驱动器等等)中。

[0093] 并且,本发明所属领域普通技术人员应该认识到,各种计算设备的功能可以组合或者集成到单一计算设备中,或者特定计算设备的功能可以分布在一个或多个其它计算设备之间,而不脱离本发明的示范性实施例的范围。

[0094] 存储控制器625可以是处理电路自身,或者可以包括处理电路。术语“处理电路”在本文中被期望包括被用来处理数据或数字信号的硬件、固件、和软件的任何组合。处理电路硬件可以包括,例如,专用集成电路(application specific integrated circuit,ASIC)、通用或者专用中央处理单元(central processing unit,CPU)、数字信号处理器(digital

signal processors, DSP)、图形处理单元 (graphics processing unit, GPU) 和诸如现场可编程门阵列 (field programmable gate array, FPGA) 的可编程逻辑器件。

[0095] 在如这里所使用的处理电路中, 每个功能可以要么由被配置 (也就是说, 硬连线) 为执行该功能的硬件执行, 要么由被配置为执行存储在非瞬时性存储介质中的指令的更通用的硬件 (诸如CPU) 执行。处理电路可以被制造在单一印刷布线板 (printed wiring board, PWB) 上, 或者分布在若干个互连的PWB上。处理电路可以包含其它处理电路; 例如, 处理电路可以包括在PWB上互连的两个处理电路, FPGA和CPU。

[0096] 将理解, 虽然术语“第一”、“第二”、“第三”等等可以在这里用来描述各种元素、组件、区、层和/或分区, 但是这些元素、组件、区、层、和/或分区不应该被这些术语限制。这些术语仅仅被用来区分一个元素、组件、区、层或者分区与另一个元素、组件、区、层或者分区。因此, 以上讨论的第一元素、组件、区、层或分区可以被命名为第二元素、组件、区、层或分区, 而不脱离本发明构思的精神和范围。

[0097] 空间相对术语, 诸如“在...之下”、“在...下”、“低于”、“下面”、“在...上”、“更上的”等等, 可以在这里被使用以方便用来描述如附图中所示的一个元素或特征与另一(多个)元素或者(多个)特征的关系的描述。将理解, 这样的空间相对术语意图包含除了附图中描绘的朝向之外的、正被使用或操作的设备的其它朝向。例如, 如果附图中的设备被翻转, 则被描述为在其它元素或特征“下”、“之下”或“下面”的元素将被朝向所述其它元素或特征“上”。因此, 示例术语“在...下”和“下面”能够包含“在...上”的朝向和“在...下”的朝向两者。所述设备可以另外朝向(例如, 旋转90度或者朝向其它朝向), 并且这里所使用的空间相对描述符应该被相应地解释。此外, 还将理解, 当层被称为“在”两个层“之间”时, 所述层可以是所述两个层之间的仅有的层, 或者也可以存在一个或多个插入其间的层。

[0098] 这里所使用的术语仅仅用于描述特殊实施例的目的, 并且不意图对本发明构思进行限制。如这里所使用的, 术语“基本上”、“关于”、和另外相似的术语被用作接近度的术语, 而不用作程度的术语, 并且意图说明将被本发明所属领域的普通技术人员所识别的测量的或者计算的值中的固有偏差。如这里所使用的, 术语“主要组件”意味着构成在重量上构成合成物的至少一半的组件, 并且当术语“主要部分”被应用到多个项目时, 意味着所述项目的至少一半。

[0099] 如这里所使用的, 单数形式“一”也意图包括复数形式, 除非上下文清楚地另外指示。还将理解, 当术语“包括”和/或“包含”在本说明书中使用时, 指定所陈述的特征、整体、步骤、操作、元素、和/或组件的存在, 但是不排除一个或多个其它特征、整体、步骤、操作、元素、组件和/或它们的组的存在或者添加。如这里所使用的, 术语“和/或”包括相关联的列出的项目中的一个或多个的任何组合和所有组合。当诸如“...中的至少一个”的表达在一列元素之后时, 其修改整个列表的元素, 并且不是修改所述列表的单个元素。另外, 当描述本发明构思的实施例时, “可以”的使用是指“本发明的一个或多个实施例”。并且, 术语“示范性”意图指代示例或者例示。如这里所使用的, 术语“使用”、“使用了”、和“被使用”可以分别与术语“利用”、“利用了”和“被利用”同义地考虑。

[0100] 将理解, 当元素或者层被称为“在”另一元素或者层“上”, “连接到”、“耦合到”另一元素或者层, 或者与另一元素或层“相邻”时, 所述元素或者层可以直接在另一元素或者层上, 直接连接到、直接耦合到另一元素或者层, 或者与另一元素或层紧邻, 或者可以存在一

个或多个插入其间的元素或者层。相反,当元素或者层被称为“直接在”另一元素或者层“上”,“直接连接到”、“直接耦合到”另一元素或者层,或者“紧邻”另一元素或者层时,不存在插入其间的元素或者层。

[0101] 这里叙述的任何数值范围意图包括归入所叙述的范围内的具有相同数值精度的全部子范围。例如,范围“1.0到10.0”意图包括所叙述的最小值1.0和所叙述的最大值10.0之间的(并且包括这两者)全部子范围,也就是说,具有等于或者大于1.0的最小值和等于或小于10.0的最大值,诸如,例如,2.4到7.6。这里叙述的任何最大数值限制都意图包括归入其中的所有更低的数值限制,并且在本说明书中叙述的任何最小的数值限制意图归入其中的所有更高的数值限制。

[0102] 虽然已经在本文中具体地描述和示出了形性存储设备的示例实施例,但是许多修改和变化对本领域技术人员将是清楚的。因此,将理解,根据本发明的远离构建的形性存储设备可以与这里所具体描述的那样不同地具体实现。本发明还被定义在所附权利要求书及其等同物中。

图1A

图1B

图2A

图2B

图3A

图3B

图4

图 5A

图 5B

图5C

图5D

图6

图7

图9

图10A

图10B