(19)

OFICINA ESPAÑOLA DE

PATENTES Y MARCAS

ESPAÑA

(11) Número de publicación: **2 880 927**

(51) Int. Cl.:

**H04L 25/02** (2006.01)

**H04L 25/14** (2006.01)

**H04L 25/49** (2006.01)

**H04L 25/493** (2006.01)

**H04L 5/14** (2006.01)

**H04L 5/16** (2006.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

T3

- (86) Fecha de presentación y número de la solicitud internacional: **28.06.2013 PCT/US2013/048758**

(87) Fecha y número de publicación internacional: **03.01.2014 WO14005117**

(96) Fecha de presentación y número de la solicitud europea: **28.06.2013 E 13741905 (7)**

(97) Fecha y número de publicación de la concesión europea: **19.05.2021 EP 2868046**

---

(54) Título: **Multiplexor de tipo clavija con salida de polaridad y N fases**

(30) Prioridad:

**29.06.2012 US 201261666197 P

16.05.2013 US 201313895651**

(45) Fecha de publicación y mención en BOPI de la traducción de la patente:

**26.11.2021**

(73) Titular/es:

**QUALCOMM INCORPORATED (100.0%)

5775 Morehouse Drive

San Diego, CA 92121, US**

(72) Inventor/es:

**WILEY, GEORGE ALAN;

RASKIN, GLENN D. y

LEE, CHULKYU**

(74) Agente/Representante:

**FORTEA LAGUNA, Juan José**

**ES 2 880 927 T3**

---

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín Europeo de Patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre Concesión de Patentes Europeas).

## DESCRIPCIÓN

Multiplexor de tipo clavija con salida de polaridad y N fases

5    **Referencia cruzada a solicitud relacionada**

[0001] La presente solicitud de patente reivindica la prioridad de la solicitud provisional n.º 61/666.197 titulada "N-Phase Polarity Output Pin Mode Multiplexer [Multiplexor de tipo clavija con salida de polaridad y N fases]" presentada el 29 de junio de 2012.

10    **Antecedentes**

**Campo**

15    [0002] La presente divulgación se refiere en general a interfaces de comunicaciones de datos de alta velocidad y, más en particular, a la multiplexación de clavijas de entrada y salida de un procesador de aplicaciones integrado en el teléfono celular.

20    **Antecedentes**

[0003] Los fabricantes de dispositivos móviles, tales como teléfonos celulares, pueden obtener componentes de los dispositivos móviles desde diversas fuentes, incluyendo diferentes fabricantes. Por ejemplo, un procesador de aplicaciones y un teléfono celular se pueden obtener de un primer fabricante, mientras que la pantalla para el teléfono celular se puede obtener de un segundo fabricante. Además, se definen múltiples normas para interconectar determinados componentes de los dispositivos móviles. Por ejemplo, hay múltiples tipos de interfaz definidos para las comunicaciones entre un procesador de aplicaciones y una pantalla dentro de un dispositivo móvil. Algunas pantallas proporcionan una interfaz de conformidad con la interfaz de sistema de pantalla (DSI) especificada por la Alianza de Interfaz de Procesador de la Industria Móvil (MIPI). Otras pantallas pueden utilizar otros tipos de interfaces físicas, que pueden ser más eficaces que la DSI convencional. Sería económico configurar el mismo procesador de aplicaciones para su uso con más de una interfaz de pantalla. El documento US2008212709 A1 está dirigido a la provisión de una interfaz serie de alta velocidad usa modulación de tres fases para codificar conjuntamente datos e información de reloj. El documento US2003/016758 A1 divulga una interfaz universal para comunicar información a una interfaz física patentada.

35    **Breve explicación**

[0004] La invención está definida únicamente por las reivindicaciones adjuntas. En lo sucesivo, las referencias a modos de realización que no se encuentran dentro del alcance de las reivindicaciones se deben entender como ejemplos útiles para comprender la invención.

40    [0005] Los modos de realización divulgados en el presente documento proporcionan sistemas, procedimientos y aparatos que permiten que un procesador de aplicaciones se comunique con una pantalla usando cualquiera de una pluralidad de normas de interfaz. De acuerdo con determinados aspectos descritos en el presente documento, dos o más dispositivos de circuito integrado (CI) pueden estar colocalizados en un aparato electrónico y comunicativamente acoplados a través de uno o más enlaces de datos que se pueden configurar como se deseé para la compatibilidad con una de una pluralidad de normas de interfaz.

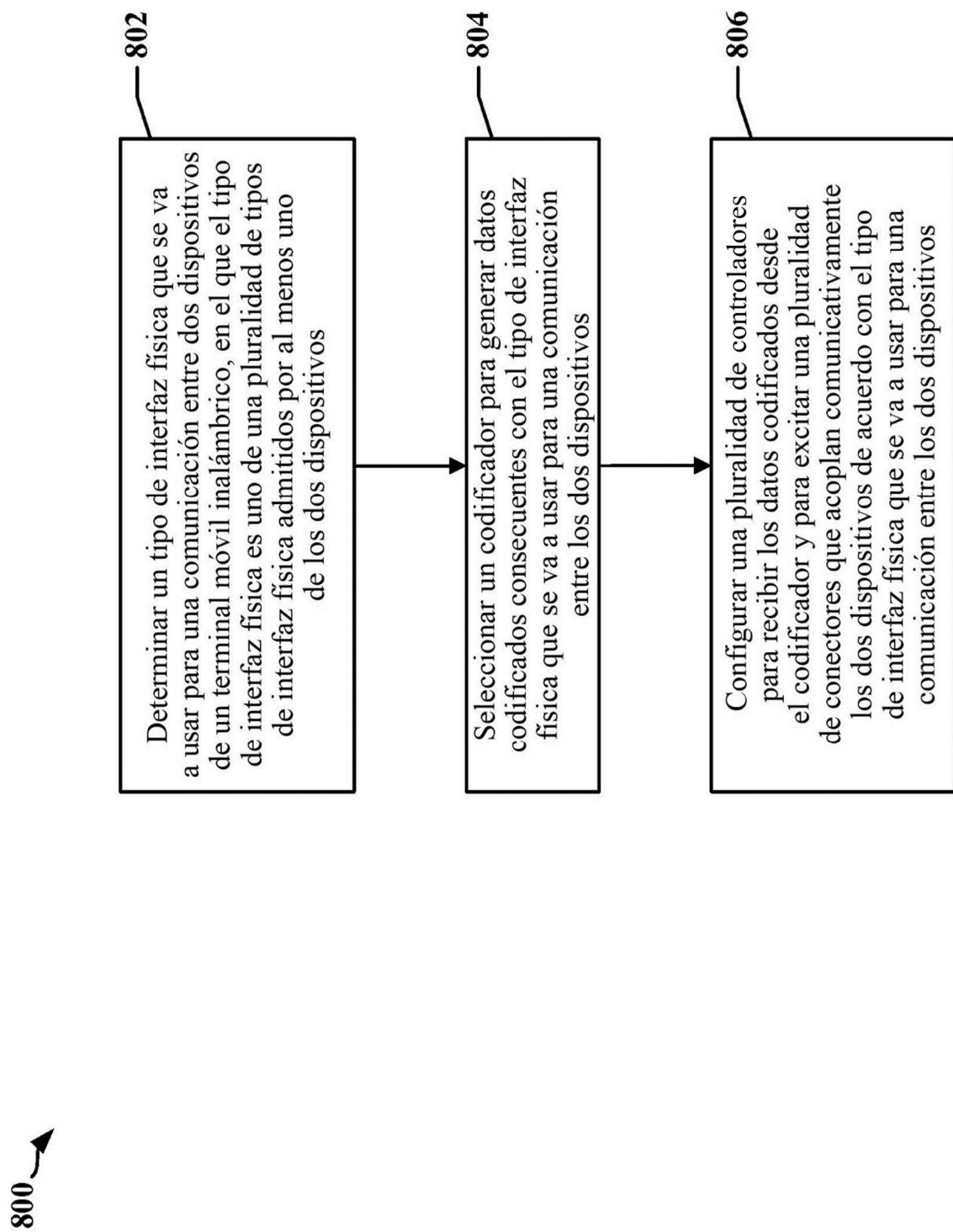

50    [0006] En un aspecto de la divulgación, un procedimiento de transferencia de datos comprende determinar un tipo de interfaz física que se va a usar para una comunicación entre dos dispositivos de un terminal móvil inalámbrico, seleccionar un codificador para generar datos codificados consecuentes con el tipo de interfaz física que se va a usar para una comunicación entre los dos dispositivos, y configurar una pluralidad de controladores para recibir los datos codificados desde el codificador y para excitar una pluralidad de conectores que acoplan comunicativamente los dos dispositivos de acuerdo con el tipo de interfaz física que se va a usar para la comunicación entre los dos dispositivos. El tipo de interfaz física puede ser uno de una pluralidad de tipos de interfaz física admitidos por al menos uno de los dos dispositivos.

55    [0007] En un aspecto de la divulgación, el procedimiento de transferencia de datos comprende controlar una pluralidad de conmutadores para acoplar salidas del codificador seleccionado a la pluralidad de controladores.

60    [0008] En un aspecto de la divulgación, la pluralidad de conectores comprende al menos algunos conectores bidireccionales. El codificador puede proporcionar los datos codificados en señales codificadas diferencialmente.

65    [0009] En un aspecto de la divulgación, configurar la pluralidad de controladores para recibir los datos codificados incluye hacer que una o más salidas de otro y/o diferente codificador pasen a un modo de alta impedancia. El otro y/o diferente codificador puede comprender un codificador de N fases.

**[0010]** En un aspecto de la divulgación, el codificador proporciona los datos codificados en una secuencia de símbolos codificados usando una combinación de un estado de fase de un primer par de los conectores, una polaridad de un segundo par de conectores y una selección de al menos un conector no excitado. El primer par de los conectores puede comprender los mismos cables que el segundo par de conectores. Se puede hacer que una o más salidas de un codificador diferencial pasen a un modo de alta impedancia. Los datos codificados se pueden referir a una cámara o una pantalla controlada por uno de los dos dispositivos.

**[0011]** En un aspecto de la divulgación, un aparato comprende una pluralidad de conectores que acoplan comunicativamente un primer dispositivo de CI con un segundo dispositivo de CI, medios para generar datos codificados consecuentes con el tipo de interfaz física que se va a usar para una comunicación entre los dos dispositivos, y medios para configurar una pluralidad de controladores para recibir los datos codificados de uno de los al menos dos codificadores y para excitar una pluralidad de conectores que acoplan comunicativamente los dos dispositivos de acuerdo con el tipo de interfaz física que se va a usar para una comunicación entre los dos dispositivos. Los medios para generar datos codificados pueden incluir al menos dos codificadores que están configurados para codificar datos de diferentes maneras. La pluralidad de conectores puede comprender cables, trazados u otros conectores conductores de electricidad.

**[0012]** En un aspecto de la divulgación, un aparato comprende una pluralidad de conectores que acoplan comunicativamente un primer dispositivo con un segundo dispositivo en un terminal móvil inalámbrico, y un sistema de procesamiento configurado para determinar un modo de funcionamiento para comunicarse entre el primer dispositivo y el segundo dispositivo, seleccionar un codificador para excitar la pluralidad de conectores, y configurar una pluralidad de controladores para recibir datos codificados desde el codificador. La pluralidad de controladores puede excitar la pluralidad de conectores.

**[0013]** En un aspecto de la divulgación, un medio de almacenamiento legible por procesador tiene una o más instrucciones que, cuando son ejecutadas por al menos un circuito de procesamiento, hacen que el al menos un circuito de procesamiento determine un tipo de interfaz física que se va a usar para una comunicación entre dos dispositivos de un terminal móvil inalámbrico, seleccionar un codificador para generar datos codificados consecuentes con el tipo de interfaz física que se va a usar para una comunicación entre los dos dispositivos, y configurar una pluralidad de controladores para recibir los datos codificados desde el codificador y para excitar una pluralidad de conectores que acoplan comunicativamente los dos dispositivos de acuerdo con el tipo de interfaz física que se va a usar para una comunicación entre los dos dispositivos. El tipo de interfaz física puede ser uno de una pluralidad de tipos de interfaz física admitidos por al menos uno de los dos dispositivos.

### 35 **Breve descripción de los dibujos**

#### **[0014]**

La FIG. 1 representa un aparato que emplea un enlace de datos entre dispositivos de CI que funciona de forma selectiva de acuerdo con una de una pluralidad de normas disponibles.

La FIG. 2 ilustra una arquitectura de sistema para un aparato que emplea un enlace de datos entre dispositivos de CI que funciona de forma selectiva de acuerdo con una de una pluralidad de normas disponibles.

La FIG. 3 ilustra un ejemplo de enlace de datos que usa señalización diferencial.

La FIG. 4 ilustra un ejemplo de codificador de datos en polaridad y  $N$  fases.

La FIG. 5 ilustra la señalización en una interfaz codificada en polaridad y  $N$  fases.

La FIG. 6 ilustra un descodificador de datos en polaridad y  $N$  fases.

La FIG. 7 ilustra una arquitectura de sistema para un aparato que puede usar selectivamente codificación de polaridad y  $N$  fases o señalización diferencial.

La FIG. 8 es un diagrama de flujo de un procedimiento para codificación de polaridad y  $N$  fases selectiva.

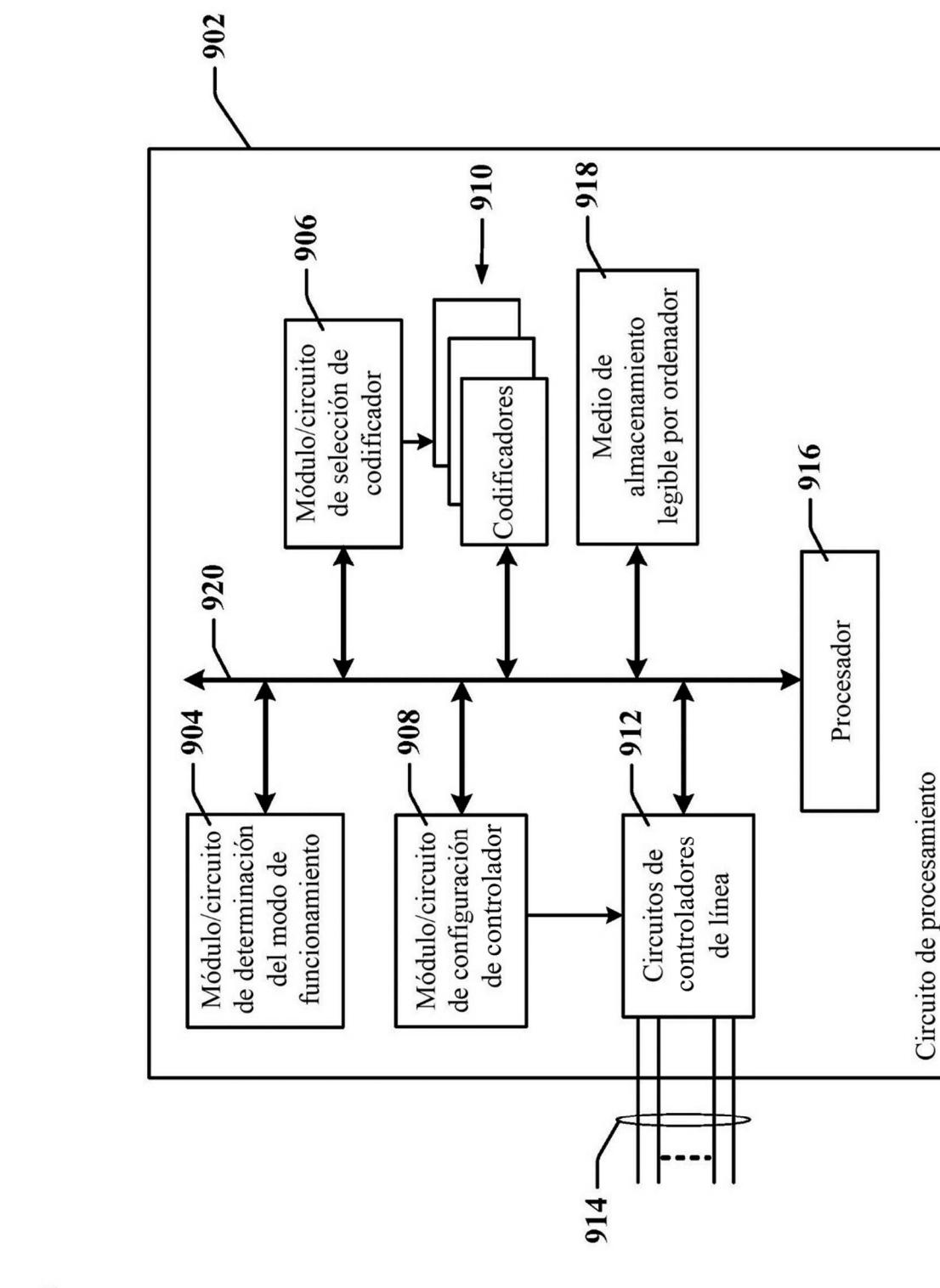

La FIG. 9 es un diagrama que ilustra un ejemplo de implementación en hardware para un aparato que emplea codificación de datos en polaridad y  $N$  fases.

### 60 **Descripción detallada**

**[0015]** Se describen ahora diversos aspectos con referencia a los dibujos. En la siguiente descripción se exponen, con propósitos explicativos, numerosos detalles específicos para permitir una plena comprensión de uno o más aspectos. Sin embargo, puede resultar evidente que dicho(s) aspecto(s) se puede(n) llevar a la práctica sin estos detalles específicos.

[0016] Como se usan en la presente solicitud, los términos "componente", "módulo", "sistema" y similares pretenden incluir una entidad relacionada con la informática, tal como, pero sin limitarse a, hardware, firmware, una combinación de hardware y software, software o software en ejecución. Por ejemplo, un componente puede ser, pero no se limita a ser, un proceso que se ejecuta en un procesador, un procesador, un objeto, un ejecutable, un línea de ejecución, un programa y/o un ordenador. A modo de ilustración, tanto una aplicación que se ejecuta en un dispositivo informático como el dispositivo informático pueden ser un componente. Uno o más componentes pueden residir dentro de un proceso y/o línea de ejecución, y un componente puede estar localizado en un ordenador y/o estar distribuido entre dos o más ordenadores. Además, estos componentes se pueden ejecutar desde diversos medios legibles por ordenador que tienen diversas estructuras de datos almacenadas en los mismos. Los componentes se pueden comunicar por medio de procesos locales y/o remotos, por ejemplo, de acuerdo con una señal que tiene uno o más paquetes de datos, tales como datos de un componente que interactúa con otro componente en un sistema local, un sistema distribuido y/o a través de una red, tal como Internet, con otros sistemas por medio de la señal.

[0017] Por otro lado, el término "o" pretende significar una "o" inclusiva en lugar de una "o" exclusiva. Es decir, a menos que se especifique de otro modo, o que resulte claro a partir del contexto, la frase "X emplea A o B" pretende significar cualquiera de las permutaciones inclusivas naturales. Es decir, la frase "X emplea A o B" se satisface en cualquiera de los siguientes casos: X emplea A; X emplea B; o X emplea tanto A como B. Además, los artículos "un" y "uno(a)", como se usan en la presente solicitud y en las reivindicaciones adjuntas, se deberían interpretar, en general, con el significado de "uno(a) o más", a no ser que se especifique de otro modo o que resulte claro a partir del contexto que se refieren a una forma en singular.

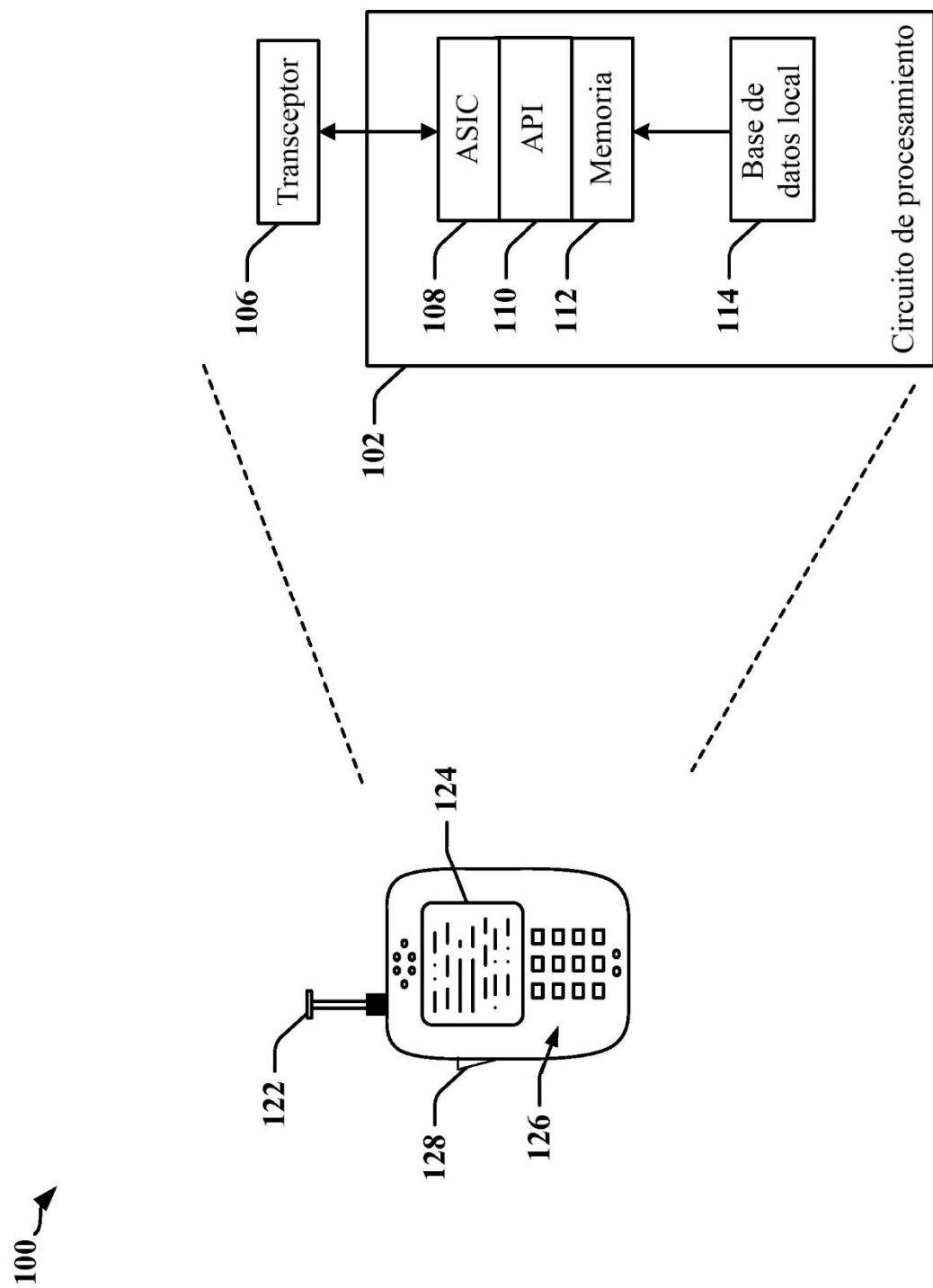

[0018] Determinados modos de realización de la invención pueden ser aplicables a enlaces de comunicaciones implementados entre componentes electrónicos que pueden incluir subcomponentes de un dispositivo, tales como un teléfono, un dispositivo informático móvil, un aparato eléctrico, unos sistemas electrónicos de automóvil, unos sistemas de aviónica, etc. La FIG. 1 representa un aparato que emplea un enlace de datos entre dispositivos de CI que funciona de forma selectiva de acuerdo con una de una pluralidad de normas disponibles. En un ejemplo, el aparato 100 puede comprender un dispositivo de comunicación inalámbrica que se comunica a través de un transceptor de RF con una red de acceso por radio (RAN), una red de acceso central, Internet y/u otra red. El aparato 100 puede incluir un transceptor de comunicaciones 106 acoplado funcionalmente al circuito de procesamiento 102. El circuito de procesamiento 102 puede incluir uno o más dispositivos de CI, tales como un CI específico de la aplicación (ASIC) 108. El ASIC 108 puede incluir uno o más dispositivos de procesamiento, circuitos lógicos, etc. El circuito de procesamiento 102 puede incluir y/o estar acoplado a un almacenamiento legible por procesador 112 que puede mantener instrucciones y datos que el circuito de procesamiento 102 puede ejecutar. El circuito de procesamiento 102 puede ser controlado por una o más de una capa de sistema operativo y de interfaz de programación de aplicaciones (API) 110 que admite y permite la ejecución de módulos de software que residen en medios de almacenamiento, tales como el dispositivo de memoria 112 del dispositivo inalámbrico. El dispositivo de memoria 112 puede comprender memoria de solo lectura o de acceso aleatorio (ROM y RAM), EEPROM, tarjetas de memoria *flash* o cualquier dispositivo de memoria que se pueda usar en sistemas de procesamiento y plataformas informáticas. El circuito de procesamiento 102 puede incluir o acceder a una base de datos local 114 que puede mantener parámetros operativos y otra información usada para configurar y hacer funcionar el aparato 100. La base de datos local 114 se puede implementar usando uno o más de un módulo de base de datos, memoria *flash*, medios magnéticos, EEPROM, medios ópticos, cinta, disco flexible o duro o similares. El circuito de procesamiento también puede estar acoplado funcionalmente a dispositivos externos tales como una antena 122, una pantalla 124, unos controles de operador, tales como un botón 128 y un teclado 126, entre otros componentes.

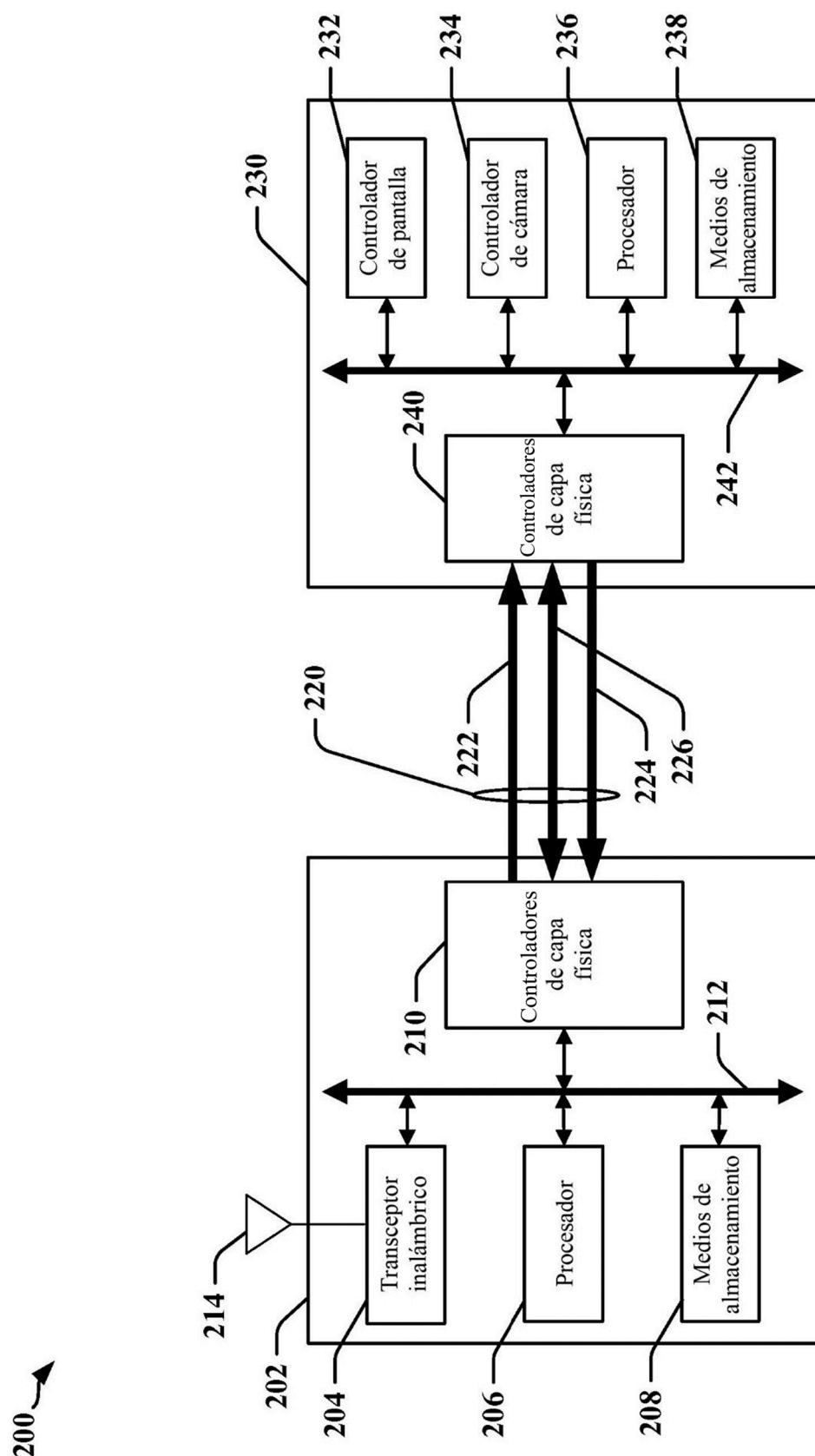

[0019] La FIG. 2 es un esquema de bloques 200 que ilustra determinados aspectos de un aparato tal como un dispositivo móvil inalámbrico, un teléfono móvil, un sistema informático móvil, un teléfono inalámbrico, un ordenador portátil, un dispositivo informático de tableta, un reproductor de medios, un dispositivo de juegos o similares. El aparato 200 puede comprender una pluralidad de dispositivos de CI 202 y 230 que intercambian datos e información de control a través de un enlace de comunicación 220. El enlace de comunicación 220 se puede usar para conectar dispositivos de CI 202 y 222 que están localizados muy cerca uno del otro, o que están localizados físicamente en diferentes partes del aparato 200. En un ejemplo, el enlace de comunicaciones 220 se puede proporcionar en un soporte de chip, sustrato o placa de circuito que lleva los dispositivos de CI 202 y 230. En otro ejemplo, un primer dispositivo de CI 202 puede estar localizado en una sección de teclado de un teléfono plegable, mientras que un segundo dispositivo de CI 230 puede estar localizado en una sección de pantalla del teléfono plegable. En otro ejemplo, una parte del enlace de comunicaciones 220 puede comprender una conexión por cable u óptica.

[0020] El enlace de comunicaciones 220 puede comprender múltiples canales 222, 224 y 226. Uno o más canales 226 pueden ser bidireccionales y pueden funcionar en modos semidúplex y/o dúplex completo. Uno o más canales 222 y 224 pueden ser unidireccionales. El enlace de comunicación 220 puede ser asimétrico, con lo que se proporciona un mayor ancho de banda en una dirección. En un ejemplo descrito en el presente documento, un primer canal de comunicaciones 222 se puede denominar enlace directo 222, mientras que un segundo canal de

comunicaciones 224 se puede denominar enlace inverso 224. El primer dispositivo de CI 202 se puede designar sistema principal o transmisor, mientras que el segundo dispositivo de CI 230 se puede designar sistema cliente o receptor, aun cuando ambos dispositivos de CI 202 y 230 estén configurados para transmitir y recibir en el enlace de comunicaciones 222. En un ejemplo, el enlace directo 222 puede funcionar a una velocidad de transferencia de datos más alta cuando se comunican datos desde un primer dispositivo de CI 202 a un segundo dispositivo de CI 230, mientras que el enlace inverso 224 puede funcionar a una velocidad de transferencia de datos más baja cuando se comunican datos desde el segundo dispositivo de CI 230 al primer dispositivo de CI 202.

**[0021]** Los dispositivos de CI 202 y 230 pueden incluir cada uno un procesador u otro circuito o dispositivo de procesamiento y/o informático 206, 236. En un ejemplo, el primer dispositivo de CI 202 puede realizar funciones centrales del aparato 200, incluyendo el mantenimiento de comunicaciones inalámbricas a través de un transceptor inalámbrico 204 y una antena 214, mientras que el segundo dispositivo de CI 230 puede admitir una interfaz de usuario que gestiona o hace funcionar un controlador de pantalla 232, y puede controlar las operaciones de una cámara o dispositivo de entrada de vídeo usando un controlador de cámara 234. Otras características admitidas por uno o más de los dispositivos de CI 202 y 230 pueden incluir un teclado, un componente de reconocimiento de voz y otros dispositivos de entrada o salida. El controlador de pantalla 232 puede comprender circuitos y controladores de software que admiten pantallas tales como un panel de pantalla de cristal líquido (LCD), una pantalla táctil, indicadores, etc. Los medios de almacenamiento 208 y 238 pueden comprender dispositivos de almacenamiento transitorio y/o no transitorio adaptados para mantener instrucciones y datos usados por los respectivos procesadores 206 y 236, y/u otros componentes de los dispositivos de CI 202 y 230. La comunicación entre cada procesador 206, 236 y sus correspondientes medios de almacenamiento 208 y 238 y otros módulos y circuitos puede ser facilitada por uno o más buses 212 y 242, respectivamente.

**[0022]** El enlace inverso 224 se puede hacer funcionar de la misma manera que el enlace directo 222, y el enlace directo 222 y el enlace inverso 224 tal vez puedan transmitir a velocidades comparables o a velocidades diferentes, donde la velocidad se puede expresar como una velocidad de transferencia de datos y/o una velocidad de reloj. Las velocidades de transferencia de datos directa e inversa pueden ser sustancialmente iguales o diferir en órdenes de magnitud, dependiendo de la aplicación. En algunas aplicaciones, un solo enlace bidireccional 226 puede admitir comunicaciones entre el primer dispositivo de CI 202 y el segundo dispositivo de CI 230. El enlace directo 222 y/o el enlace inverso 224 pueden ser configurables para funcionar en un modo bidireccional cuando, por ejemplo, los enlaces directo e inverso 222 y 224 comparten las mismas conexiones físicas y funcionan en semidúplex. En un ejemplo, el enlace de comunicaciones 220 se pueden hacer funcionar para comunicar control, mandatos y otra información entre el primer dispositivo de CI 202 y el segundo dispositivo de CI 230, de acuerdo con una norma industrial o de otro tipo.

**[0023]** Las normas industriales pueden ser específicas de la aplicación. En un ejemplo, la norma MIPI define interfaces de capa física que incluyen una especificación de interfaz síncrona (D-PHY) entre un dispositivo de CI de procesador de aplicaciones 202 y un dispositivo de CI 230 que admite la cámara o pantalla en un dispositivo móvil. La especificación D-PHY rige las características de funcionamiento de productos de conformidad con las especificaciones MIPI para dispositivos móviles. Una interfaz D-PHY puede admitir transferencias de datos usando una interfaz serie flexible, de bajo coste y de alta velocidad que se interconecta entre los componentes 202 y 230 dentro de un dispositivo móvil. Estas interfaces pueden comprender buses paralelos de semiconductor complementario de óxido metálico (CMOS) que proporcionan velocidades de bits relativamente bajas con bordes lentos para evitar problemas de interferencia electromagnética (EMI).

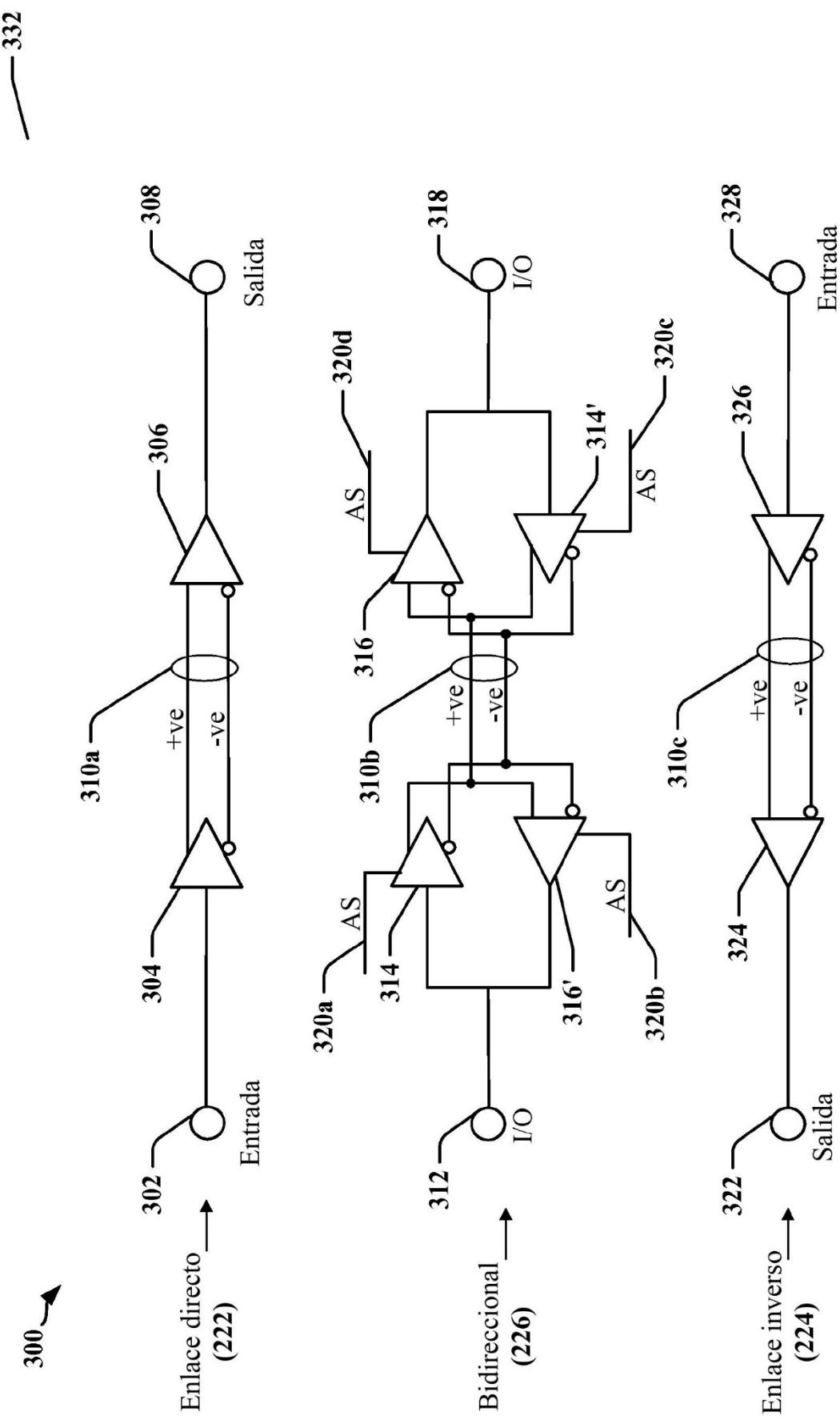

**[0024]** La FIG. 3 es un diagrama esquemático que ilustra una implementación de determinados aspectos del enlace de comunicación 220 representado en la FIG. 2 usando señalización diferencial. La señalización diferencial implica transmitir eléctricamente información con dos señales complementarias enviadas en un par de hilos 310a, 310b o 310c, que se puede denominar par diferencial. El uso de pares diferenciales puede reducir significativamente la EMI anulando el efecto de la interferencia de modo común que afecta a ambos cables de un par diferencial. En el enlace directo 222, un amplificador diferencial principal 304 puede excitar un par de cables 310a. El amplificador diferencial 304 recibe un flujo de datos de entrada 302 y genera versiones positivas y negativas de la entrada 302, que a continuación se proporcionan al par de cables 310a. El receptor diferencial 306 en el lado del cliente genera un flujo de datos de salida 308 realizando una comparación de las señales transmitidas en el par de cables 310a.

**[0025]** En el enlace inverso 224, un amplificador diferencial de lado de cliente 326 puede activar uno o más pares de cables 310c. El amplificador diferencial 326 recibe un flujo de datos de entrada 328 y genera versiones positivas y negativas de la entrada 328, que se proporcionan al par de cables 310c. El receptor diferencial 324 en el ordenador principal genera un flujo de datos de salida 322 realizando una comparación de las señales transmitidas en el par de cables 310c.

**[0026]** En un enlace bidireccional 226, el ordenador principal y el cliente pueden transmitir y recibir datos usando el mismo par de cables 310b configurado en modo semidúplex. Un bus bidireccional se puede hacer funcionar de forma alternativa o adicional en modo dúplex completo usando combinaciones de controladores de enlace directo e inverso 304, 326 para excitar múltiples pares de cables 310a, 310c. En la implementación bidireccional

5 semidúplex representada, se puede evitar que los transmisores 314 y 314' exciten el par de cables 310b simultáneamente, y se puede usar un control de activación de salida (AS) 320a, 320c (respectivamente) para forzar a los transmisores 314 y 314' a pasar a un estado de alta impedancia. Se puede impedir que el receptor diferencial 316' excite la entrada/salida 312 mientras el transmisor diferencial 314 está activo, usando típicamente un control de AS 320b para forzar al receptor diferencial 316' a pasar a un estado de alta impedancia. Se puede impedir que el receptor diferencial 316 excite la entrada/salida 318 mientras el transmisor diferencial 314' está activo, usando típicamente un control de AS 320d para forzar al receptor diferencial 316 a pasar a un estado de alta impedancia. En algunos casos, las salidas de los transmisores diferenciales 314 y 314' y los receptores diferenciales 316 y 316' pueden estar en un estado de alta impedancia cuando la interfaz no está activa. En consecuencia, la AS controla 10 320a, 320c, 320b y 320d de los transmisores diferenciales 314, 314', y los receptores diferenciales 316 y 316' pueden funcionar independientemente uno de otro.

15 [0027] Cada amplificador diferencial 304, 314, 314' y 326 puede comprender un par de amplificadores, uno de los cuales recibe en una entrada la inversa de la entrada del otro amplificador. Los amplificadores diferenciales 304, 314, 314' y 326 pueden recibir una sola entrada y comprender un inversor interno que genera una entrada inversa para su uso con un par de amplificadores. Los amplificadores diferenciales 304, 314, 314' y 326 también se pueden construir usando dos amplificadores controlados por separado, de modo que sus respectivas salidas se pueden situar en un modo de alta impedancia independientemente unas de otras.

20 [0028] De acuerdo con determinados aspectos divulgados en el presente documento, los sistemas y aparatos pueden emplear procedimientos de interfaz de codificación y descodificación de datos de múltiples fases para una comunicación entre los dispositivos de CI 202 y 230. Un codificador de múltiples fases puede excitar una pluralidad de conductores (es decir,  $M$  conductores). Los  $M$  conductores comprenden típicamente tres o más conductores, y cada conductor se puede denominar hilo, aunque los  $M$  conductores pueden comprender trazados conductores en 25 una placa de circuito o dentro de una capa conductora de un dispositivo de CI semiconductor. Los  $M$  conductores se pueden dividir en una pluralidad de grupos de transmisión, codificando cada grupo una parte de un bloque de datos que se va a transmitir. Se define un sistema de codificación de  $N$  fases en el que los bits de datos se codifican en las transiciones de fase y los cambios de polaridad en los  $M$  conductores. En un ejemplo, un sistema de codificación de  $N$  fases para un sistema de 3 cables puede comprender tres estados de fase y dos polaridades, 30 proporcionando 6 estados y 5 posibles transiciones de cada estado. Se pueden detectar y descodificar cambios de tensión y/o corriente determinísticos para extraer datos de los  $M$  conductores. La descodificación no depende de conductores independientes o pares de conductores y la información de temporización se puede obtener directamente de las transiciones de fase y/o polaridad en los  $M$  conductores. La transferencia de datos de polaridad y  $N$  fases se puede aplicar a cualquier interfaz de señalización, tal como una interfaz eléctrica, óptica y de 35 radiofrecuencia (RF), por ejemplo.

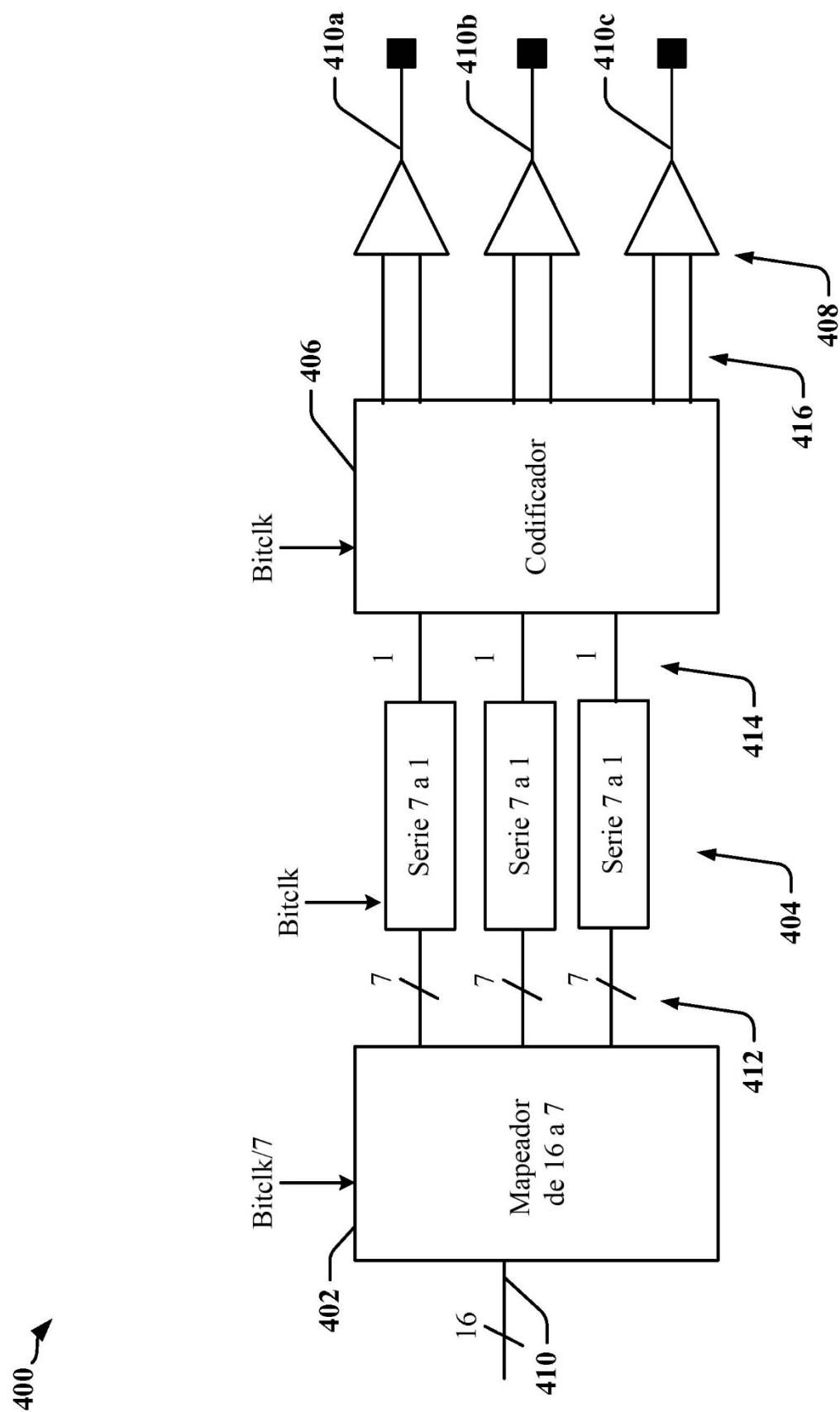

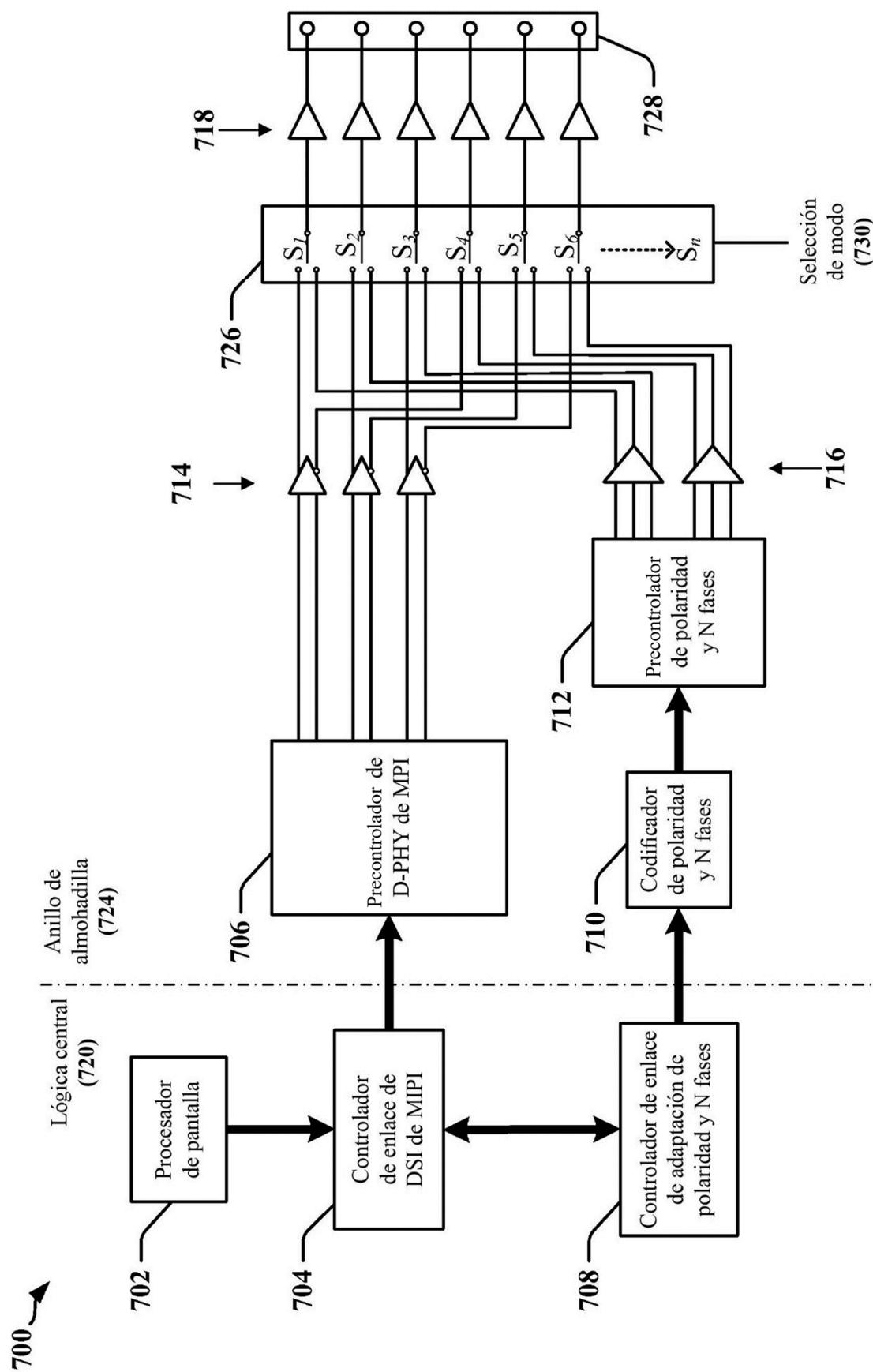

40 [0029] La FIG. 4 es un diagrama esquemático que ilustra el uso de codificación de polaridad y  $N$  fases para implementar determinados aspectos del enlace de comunicación 220 representado en la FIG. 2. El enlace de comunicación 220 puede comprender un bus alámbrico que tiene una pluralidad de cables de señal, que pueden estar configurados para transmitir datos codificados en  $N$  fases en una interfaz digital de alta velocidad, tal como una interfaz digital de pantalla móvil (MDDI). Uno o más de los canales 222, 224 y 226 pueden usar codificación de polaridad y  $N$  fases. Los controladores de capa física 210 y 240 pueden estar adaptados para codificar y descodificar datos codificados en polaridad y  $N$  fases transmitidos en el enlace 220. El uso de la codificación de polaridad y  $N$  fases proporciona una transferencia de datos de alta velocidad y puede consumir la mitad o menos 45 de la alimentación de otras interfaces, ya que hay menos controladores activos en los enlaces de datos codificados en polaridad y  $N$  fases 220. Los dispositivos de codificación de polaridad y  $N$  fases 210 y/o 240 pueden codificar múltiples bits por transición en el enlace de comunicaciones 220. En un ejemplo, se puede usar una combinación de codificación de 3 fases y polaridad para admitir un CI de controlador de LCD de 80 tramas por segundo de matriz de gráficos de vídeo amplia (WVGA) sin un búfer de trama, suministrando datos de píxeles a 810 Mb/s para 50 actualizar la pantalla.

55 [0030] En el ejemplo representado en 400, un transmisor de codificación de polaridad y  $N$  fases y  $M$  cables está configurado para  $M=3$  y  $N=3$ . El ejemplo de codificación de 3 fases y 3 cables se selecciona únicamente con el propósito de simplificar las descripciones de determinados aspectos de la presente invención. Los principios y las técnicas divulgados para codificadores de 3 fases y 3 cables se pueden aplicar en otras configuraciones de codificadores de polaridad de  $N$  fases y  $M$  cables.

60 [0031] Cuando se usa la codificación de polaridad y  $N$  fases, los conectores tales como los cables de señal 410a, 410b y 410c de un bus de  $N$  líneas pueden estar no excitados, excitados a positivo o excitados a negativo. Un cable de señal no excitado 410a, 410b o 410c puede estar en un estado de alta impedancia. Un cable de señal no excitado 410a, 410b o 410c se puede excitar o llevar al menos parcialmente a un nivel de tensión que se encuentra sustancialmente a medio camino entre los niveles de tensión positiva y negativa proporcionados en los cables de señal excitados. Un cable de señal no excitado 410a, 410b o 410c puede no tener corriente fluyendo a su través. En el ejemplo 400, cada cable de señal 410a, 410b y 410c puede estar en uno de tres estados (denotados por +1, -1 o 0) usando controladores 408. En un ejemplo, los controladores 408 pueden comprender controladores de modo corriente de nivel de unidad. En otro ejemplo, los controladores 408 pueden excitar tensiones de polaridad 65

opuesta en dos señales 410a y 410b, mientras que la tercera señal 410c está a alta impedancia y/o está puesta a tierra. Para cada intervalo de símbolo transmitido, al menos una señal está en el estado no excitado (0), mientras que el número de señales excitadas a positivo (estado +1) es igual al número de señales excitadas a negativo (estado -1), de modo que la suma de la corriente que fluye hasta el receptor siempre es cero. Para cada símbolo, el estado de al menos un cable de señal 410a, 410b o 410c se cambia a partir del símbolo transmitido en el intervalo de transmisión precedente.

**[0032]** Un mapeador 402 puede recibir datos de 16 bits 410, y el mapeador 402 puede mapear los datos de entrada 410 a 7 símbolos 412 para transmitir secuencialmente a través de los cables de señal 410a, 410b y 410c. Un codificador de  $N$  fases y  $M$  cables 406 recibe los 7 símbolos 412 generados por el mapeador de símbolo en símbolo 414 y calcula el estado de cada cable de señal 410a, 410b y 410c para cada intervalo de símbolo. Los 7 símbolos 412 se pueden poner en serie usando convertidores paralelo-serie 404, por ejemplo. El codificador 406 selecciona los estados de los cables de señal 410a, 410b y 410c en base al símbolo de entrada 414 y los estados previos de los cables de señal 410a, 410b y 410c.

**[0033]** El uso de codificación de  $N$  fases y  $M$  cables permite codificar un número de bits en una pluralidad de símbolos, donde los bits por símbolo no son un número entero. En el ejemplo simple de sistema de 4 cables, hay 4 combinaciones disponibles de 2 cables, que se pueden excitar simultáneamente, y 2 posibles combinaciones de polaridad en el par de cables que se excita, generando 6 posibles estados. Puesto que cada transición se produce desde un estado actual, 5 de los 6 estados están disponibles en cada transición. Se requiere que cambie el estado de al menos un cable en cada transición. Con 5 estados, se pueden codificar  $\log_2(5) \cong 2,32$  bits por símbolo. En consecuencia, un mapeador puede aceptar una palabra de 16 bits y convertirla en 7 símbolos, ya que 7 símbolos que transmiten 2,32 bits por símbolo pueden codificar 16,24 bits. En otras palabras, una combinación de siete símbolos que codifica cinco estados tiene  $5^7$  (78.125) permutaciones. En consecuencia, los 7 símbolos se pueden usar para codificar las  $2^{16}$  (65.536) permutaciones de 16 bits.

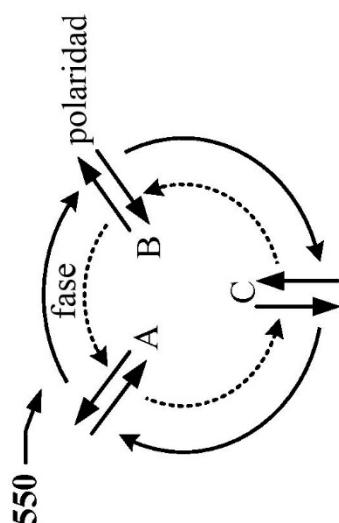

**[0034]** La FIG. 5 ilustra un ejemplo de señalización 500 que emplea un sistema de codificación de datos por modulación de tres fases basado en el diagrama de estados circular 550. De acuerdo con el sistema de codificación de datos, una señal de 3 fases puede girar en dos direcciones y se puede transmitir en tres conductores 410a, 410b y 410c. Las tres señales transmitidas por los conductores 410a, 410b, 410c comprenden la señal de 3 fases y se excitan independientemente, estando cada señal desfasada 120 grados con respecto a las otras dos señales. En cualquier momento, cada uno de los 3 cables está en un estado diferente (representado por V+, V- y abierto) de los otros 2 cables. El sistema de codificación también codifica información en la polaridad de los dos de los conductores 410a, 410b y/o 410c que se excitan de forma activa a un nivel positivo y negativo. En 508 se indica la polaridad para la secuencia de estados representados.

**[0035]** En cualquier momento en una implementación de 3 cables, exactamente dos de los conductores 410a, 410b, 410c transmiten una señal, y los estados de codificación de datos se pueden definir en términos de diferencia de tensión o flujo de corriente entre conductores. Como se muestra en el diagrama de estados 550, se definen tres estados de fase (correspondientes respectivamente a los estados A, B y C) con un flujo de señal del estado A al B, del B al C y del C al A en una dirección, por ejemplo. Las transiciones entre los tres estados se definen a continuación de acuerdo con el diagrama de estados 550 para asegurar transiciones de estado circulares. En un modo de realización, la rotación en sentido horario (A a B) a (B a C), (B a C) a (C a A) y (C a A) a (A a B) en las transiciones de estado se pueden usar para transmitir un 1 lógico, mientras que las transiciones en sentido antihorario (B a C) a (A a B), (A a B) a (C a A) y (C a A) a (B a C) en las transiciones de estado se pueden usar para transmitir un 0 lógico. También se observa que sólo uno de los estados (A a B), (B a C) y (C a A) puede ser cierto en cualquier momento. En consecuencia, se puede codificar un bit en cada transición controlando si la señal está "girando" en sentido horario o antihorario. En un ejemplo, la dirección de rotación se puede determinar en base a cuál de los 3 cables no está excitado después de la transición.

**[0036]** También se puede codificar información en la polaridad de los cables de señal excitados 410a, 410b, 410c o en la dirección del flujo de corriente entre dos cables de señal 410a, 410b, 410c. Las señales 502, 504 y 506 ilustran los niveles de tensión aplicados a los conductores 410a, 410b, 410c, respectivamente en cada estado de fase. En cualquier momento, un primer conductor está acoplado a una tensión positiva (+V, por ejemplo), un segundo conductor está acoplado a una tensión negativa (-V, por ejemplo), mientras que el tercer conductor restante está en circuito abierto. Así pues, un estado de codificación de polaridad se puede determinar mediante el flujo de corriente entre el primer y el segundo conductores o las polaridades de tensión del primer y el segundo conductores. En algunos modos de realización, se pueden codificar dos bits de datos en cada transición de fase. Un descodificador puede determinar una rotación para obtener el primer bit, y el segundo bit se puede determinar en base a la polaridad. El descodificador que tiene una dirección de rotación determinada puede determinar el estado de fase actual y la polaridad de la tensión aplicada entre los dos conectores activos 502, 504 y/o 506, o la dirección del flujo de corriente a través de los dos conductores activos 502, 504 y/o 506.

**[0037]** Como se divulga en el presente documento, un bit de datos se puede codificar en la rotación, o cambio de fase, en un sistema de codificación de 3 fases y 3 cables, y un bit adicional se puede codificar en la polaridad de los dos cables excitados. Determinados modos de realización codifican más de dos bits en cada transición de

un sistema de codificación de 3 fases y 3 cables permitiendo la transición a cualquiera de los estados posibles desde un estado actual. Dadas 3 fases de rotación y dos polaridades para cada fase, se definen 6 estados, de modo que hay 5 estados disponibles desde cualquier estado actual. En consecuencia, puede haber  $\log_2(5) \approx 2,32$  bits por símbolo (transición) y el mapeador puede aceptar una palabra de 16 bits y convertirla en 7 símbolos.

- 5 [0038] La transferencia de datos en  $N$  fases puede usar más de tres cables proporcionados en un medio de comunicación, tal como un bus. El uso de cables de señal adicionales que se pueden excitar simultáneamente proporciona más combinaciones de estados y polaridades y permite codificar más bits de datos en cada transición entre estados. Esto puede mejorar significativamente el rendimiento del sistema y reducir el consumo de alimentación en relación con los enfoques que usan múltiples pares diferenciales para transmitir bits de datos, mientras se proporciona un ancho de banda incrementado.

- 10 [0039] En un ejemplo, un codificador puede transmitir símbolos usando 6 cables con 2 pares de cables excitados para cada estado. Los 6 cables pueden estar indicados con las referencias A a F, de modo que, en un estado, los cables A y F se excitan a positivo, los cables B y E a negativo y los cables C y D no se excitan (o no transmiten corriente). Para seis cables, puede haber:

$$C(6,4) = \frac{6!}{(6-4)! \cdot 4!} = 15$$

- 20 20 posibles combinaciones de cables excitados de forma activa, con:

$$C(4,2) = \frac{4!}{(4-2)! \cdot 2!} = 6$$

combinaciones diferentes de polaridad para cada estado de fase.

- 25 [0040] Las 15 combinaciones diferentes de cables excitados de forma activa pueden incluir:

|         |         |         |         |         |

|---------|---------|---------|---------|---------|

| A B C D | A B C E | A B C F | A B D E | A B D F |

| A B E F | A C D E | A C D F | A C E F | A D E F |

| B C D E | B C D F | B C E F | B D E F | C D E F |

- 30 [0041] De los 4 cables excitados, las posibles combinaciones de dos cables excitados a positivo (y los otros dos deben estar en negativo). Las combinaciones de polaridad pueden comprender:

$$+--- \quad +--+ \quad +-+- \quad -+-+ \quad -++- \quad ---+$$

- 35 [0042] En consecuencia, el número total de estados diferentes se puede calcular como  $15 \times 6 = 90$ . Para garantizar una transición entre símbolos, hay 89 estados disponibles desde cualquier estado actual, y el número de bits que se pueden codificar en cada símbolo se puede calcular como:  $\log_2(89) \approx 6,47$  bits por símbolo. En este ejemplo, el mapeador puede codificar una palabra de 32 bits en 5 símbolos, dado que  $5 \times 6,47 = 32,35$  bits.

- 40 [0043] La ecuación general para el número de combinaciones de cables que se pueden excitar para un bus de cualquier tamaño, en función del número de cables del bus y el número de cables excitados simultáneamente es:

$$C(N_{hilos}, N_{excitados}) = \frac{N_{hilos}!}{(N_{hilos} - N_{excitados})! \cdot N_{excitados}!}$$

- [0044] La ecuación para el número de combinaciones de polaridad para los cables que se excitan es:

$$C\left(N_{excitados}, \frac{N_{excitados}}{2}\right) = \frac{N_{excitados}!}{\left(\frac{N_{excitados}}{2}\right)!}$$

45

- [0045] El número de bits por símbolo es:

$$\log_2 \left( C(N_{hilos}, N_{excitados}) \cdot C \left( N_{excitados}, \frac{N_{excitados}}{2} \right) - 1 \right)$$

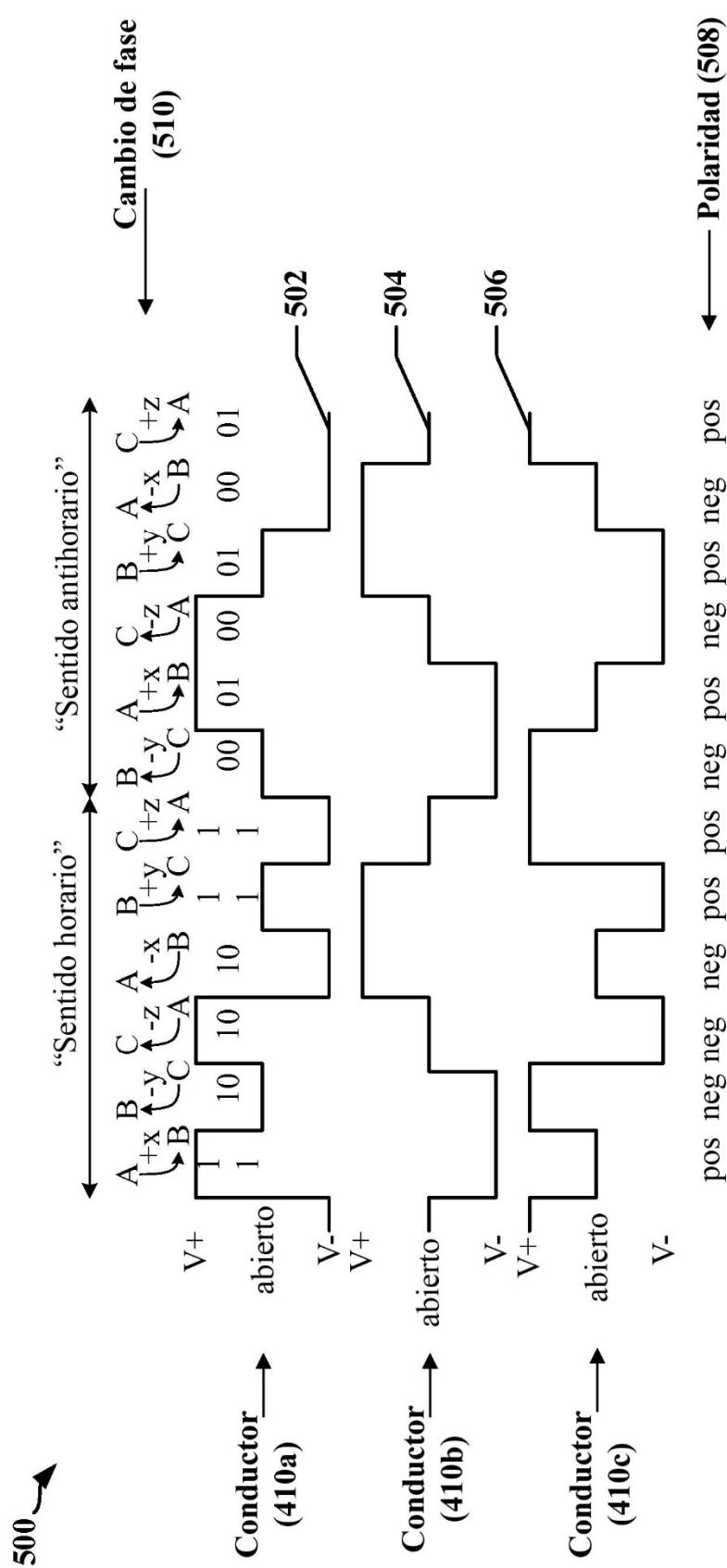

**[0046]** La FIG. 6 ilustra un ejemplo 600 de receptor en una PHY de 3 fases. Los comparadores 602 y el descodificador 604 están configurados para proporcionar una representación digital del estado de cada una de las tres líneas de transmisión 612a, 612b y 612c, así como el cambio en el estado de las tres líneas de transmisión en comparación con el estado transmitido en el período de símbolo previo. Unos convertidores serie-paralelo 606 ensamblan siete estados consecutivos para generar un conjunto de 7 símbolos que el desmapeador 608 va a procesar para obtener 16 bits de datos que se pueden almacenar en un búfer de FIFO 610.

**[0047]** De acuerdo con determinados aspectos divulgados en el presente documento, se puede controlar una pluralidad de amplificadores de tres estados para generar un conjunto de estados de salida definidos por un codificador diferencial, un codificador de polaridad y  $N$  fases u otro codificador que codifica información en cables o conectores que pueden adoptar uno de los tres estados descritos.

**[0048]** Con referencia de nuevo a la FIG. 4, el enlace de comunicación 220 puede comprender una interfaz digital de alta velocidad que puede estar configurada para admitir tanto un sistema de codificación diferencial como la codificación de polaridad y  $N$  fases. Los controladores de capa física 210 y 240 pueden comprender codificadores y descodificadores de polaridad y  $N$  fases, que pueden codificar múltiples bits por transición en la interfaz, y controladores de línea para excitar los conectores 410a, 410b y 410c. Los controladores de línea se pueden construir con amplificadores que generan una salida activa que puede tener una tensión positiva o negativa, o una salida de alta impedancia con lo que un conector 410a, 410b o 410c está en un estado indefinido o en un estado que es definido por los componentes eléctricos externos. En consecuencia, los controladores de salida 408 pueden recibir mediante un par de señales 416 que incluye control de datos y de salida (control de modo de alta impedancia). A este respecto, los amplificadores de tres estados usados para la codificación de polaridad y  $N$  fases y la codificación diferencial pueden generar tres estados de salida iguales o similares. Cuando se usan para codificación diferencial, los pares de los amplificadores de tres estados en un controlador de línea diferencial 306, 316, 316' o 324 pueden recibir la misma señal de entrada y la misma señal de control de salida, mientras que los controladores de línea de codificación de polaridad y  $N$  fases 408 reciben diferentes señales de control de entrada y salida. En consecuencia, los controladores de línea de codificación de polaridad y  $N$  fases 408 se pueden controlar a través de lógica y/o commutadores para funcionar como controladores de línea diferenciales 306, 316, 316' y 324.

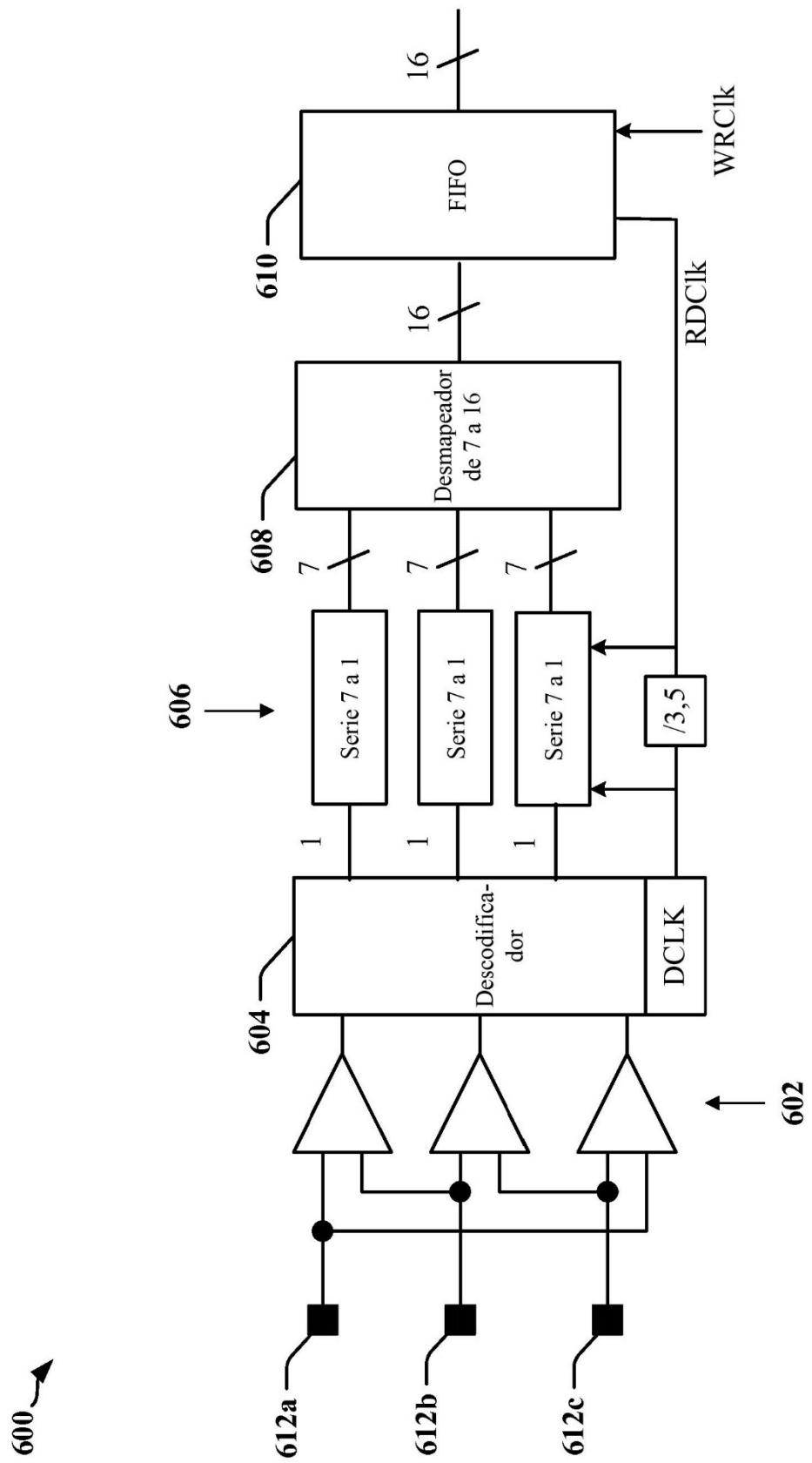

**[0049]** Determinados modos de realización proporcionan una interfaz configurable que puede activar selectivamente un número deseado de cables para comunicar datos, y/o reconfigurar una interfaz codificada en polaridad y  $N$  fases de  $M$  cables, para que sirva de interfaz diferencial. La FIG. 7 ilustra un ejemplo en el que una plataforma móvil 700 emplea multiplexación de clavijas para reconfigurar la interfaz. En el ejemplo, un procesador de pantalla 702 genera datos de pantalla para un dispositivo de pantalla 124 (véase la FIG. 1). El procesador de pantalla 702 puede estar integrado con un circuito de procesamiento 206, por ejemplo. Se pueden transmitir datos a un dispositivo 230 que incluye un controlador de pantalla 232 a través de un enlace de comunicaciones 220, usando una DSI de norma MIPI o una interfaz MDDI de polaridad y  $N$  fases descrita en el presente documento. La FIG. 7 muestra una configuración de ejemplo en la que un elemento de conmutación 726 selecciona entre las salidas de 3 controladores diferenciales 714 y las salidas de dos codificadores de 3 fases y 3 cables para excitar 6 clavijas de salida 728. Se pueden definir otras combinaciones y configuraciones de los elementos. Además, el elemento de conmutación 724 puede comprender una matriz de conmutación que permite que las clavijas de salida 728 se mapeen a cualquier salida de cualquier controlador diferencial 714 o cualquier salida de cualquier codificador de  $N$  fases y  $M$  cables.

**[0050]** Cuando se configura una interfaz DSI de MIPI, los datos de píxeles de pantalla que se originan en el procesador de pantalla 702 se proporcionan al controlador de enlace de DSI de MIPI 704, que formatea los datos de píxeles de pantalla en paquetes para enviarlos a través de una interfaz serie de alta velocidad 728 a la pantalla, típicamente a través del dispositivo 230 y/o el controlador de pantalla 232. Tanto los datos de píxeles como la información de control se pueden transmitir a través de este enlace 728. Se puede proporcionar un enlace inverso para leer el estado de la pantalla 124 o para recibir otra información.

**[0051]** Los paquetes de datos generados por el controlador de enlace de DSI de MIPI 704 en los circuitos lógicos digitales centrales 720 se pueden proporcionar a un precontrolador de DPHY de MIPI 706, que se puede realizar en una sección de entrada/salida (anillo de almohadilla) 724. Los paquetes de datos se pueden proporcionar a un conjunto de controladores de salida 718 a través de controladores diferenciales 714 y/o un multiplexor de conmutadores electrónico 726. Los controladores diferenciales 714 pueden estar habilitados mientras que los controladores de  $N$  fases 716 están inhabilitados. En un ejemplo, los controladores de  $N$  fases 716 pueden estar inhabilitados cuando los controladores de  $N$  fases 714 se fuerzan o se ponen de otro modo en el modo de salida de alta impedancia. En otro ejemplo, el multiplexor de conmutadores 726 puede seleccionar entre controladores diferenciales 714 y controladores de  $N$  fases 716 para proporcionar entradas a los controladores de línea 718.

- [0052] Cuando se requiere codificación de polaridad y  $N$  fases, los conmutadores 726 del multiplexor de conmutadores 726 se pueden hacer funcionar para seleccionar las salidas de los controladores de  $N$  fases 716 como entradas para los controladores de salida 718. De forma adicional o alternativa, los controladores de  $N$  fases 716 pueden estar habilitados mientras que los controladores diferenciales 714 están inhabilitados. En esta configuración, los paquetes de datos generados por el controlador de enlace de DSI de MIPI 704 se pueden codificar usando un codificador de polaridad y  $N$  fases 710 y proporcionar al precontrolador de polaridad y  $N$  fases 712.

- [0053] El codificador usado para formatear datos puede tomar la determinación de si uno o más de los controladores de línea 718 está en modo de alta impedancia. En un ejemplo, el precontrolador de DPHY de MIPI 706 puede controlar el control de salida (control de alta impedancia) de los controladores de línea 718, cuando la interfaz se excita en un modo de codificación diferencial. En otro ejemplo, el precontrolador de polaridad y  $N$  fases 712 puede controlar el control de salida de los controladores de línea 718, cuando la interfaz se excita en un modo de codificación de polaridad y  $N$  fases.

- [0054] De acuerdo con determinados aspectos descritos en el presente documento, los paquetes de datos similares a los paquetes de DSI de MIPI se envían a través de un enlace de polaridad y  $N$  fases. Tal vez sea necesario reformatear algunos paquetes para hacer un uso adecuado de los grupos de símbolos en el enlace de polaridad y  $N$  fases. Por ejemplo, la DSI de MIPI puede estar orientada a bytes, pero el enlace de polaridad y  $N$  fases puede transferir una palabra de 16 bits cada vez, y se puede añadir un byte a los paquetes de longitud impar. La sincronización de enlace para polaridad y  $N$  fases también puede ser ligeramente diferente.

- [0055] Un controlador de enlace de  $N$  fases y M cables 708 puede proporcionar palabras de datos de entrada como entrada a un mapeador 402 (*cf.* FIG. 4), que mapea la palabra de entrada a una serie de símbolos que se van a enviar a través del bus. El mapeador 402 se puede incorporar en un elemento de codificación 710. Un propósito del mapeador 402 es calcular los valores de un grupo de símbolos en base a una palabra de datos de entrada. Esto puede resultar útil en particular si el número de bits por símbolo no es un número entero. En el ejemplo simple descrito en relación con la FIG. 4, se emplea un sistema de 3 cables en el que hay 3 combinaciones posibles de 2 cables que se van a excitar simultáneamente, dado que hay un cable que no se excita. También hay 2 posibles combinaciones de polaridad para cada par de cables que se pueden excitar, proporcionando 6 estados posibles. 5 de los 6 estados son usables porque se requiere una transición entre dos símbolos cualesquiera. Con 5 estados puede haber  $\log_2(5) \approx 2,32$  bits por símbolo. El mapeador puede aceptar una palabra de 16 bits y convertirla en 7 símbolos.

- [0056] Los paquetes de datos generados por el controlador de enlace de adaptación de polaridad y  $N$  fases 708 se pueden proporcionar al codificador de polaridad y  $N$  fases 710 para codificar grupos de datos de enlace (por ejemplo, palabras de 16 bits o de 32 bits) en grupos de símbolos y facilitar un símbolo cada vez al precontrolador de polaridad y  $N$  fases 712. En un ejemplo, el controlador de enlace de adaptación de polaridad y  $N$  fases 708 se puede realizar en la lógica digital central 720, y el codificador de polaridad y  $N$  fases 710 se puede realizar en el anillo de almohadilla 724. El precontrolador 712 puede amplificar las señales de entrada recibidas hasta un nivel suficiente para excitar los búferes 716 y/o el controlador de salida 718.

- [0057] El multiplexor de conmutadores 726 puede seleccionar la salida del precontrolador de DPHY de MIPI 706 o la salida del precontrolador de polaridad y  $N$  fases 712 que se va a proporcionar a los controladores de salida 718. El multiplexor de conmutadores 726 puede transmitir señales que tienen un nivel de tensión o corriente mucho menor que la salida de los controladores de salida 718. En consecuencia, las señales de salida del precontrolador de DPHY de MIPI 706 y/o el precontrolador de polaridad y  $N$  fases 712 se pueden commutar fácilmente en un dispositivo de CI tal como el dispositivo 302. En algunos casos, las señales de control que determinan si uno o más controladores de salida que deberían estar en un estado de alta impedancia se pueden commutar usando el multiplexor de conmutadores 726 o un dispositivo de commutación relacionado.

- [0058] El estado de selección de modo 730 del multiplexor de conmutadores 726 se puede establecer en una selección predeterminada o preconfigurada cuando se enciende el sistema. Típicamente, solo se necesita configurar este estado una vez, porque la pantalla 124 puede estar unida de forma permanente o semipermanente al circuito de procesamiento 102 (*véase* la FIG. 1). En consecuencia, el multiplexor de conmutadores se puede configurar durante la fabricación y no es necesario cambiar el ajuste durante el funcionamiento normal del sistema. El multiplexor de conmutadores 726 puede ser direccionado por un procesador 206 o 236 a través de uno o más registros de configuración, que pueden ser no volátiles. El código para programar el multiplexor de conmutadores se puede almacenar en el almacenamiento 112. El uso del multiplexor de conmutadores 726 para commutar señales de bajo nivel permite usar el mismo procesador de aplicaciones para más de una interfaz, sin necesidad de duplicar almohadillas o clavijas de E/S. Por lo tanto, se pueden usar las mismas almohadillas o clavijas de E/S 728 para más de una interfaz, donde la programación del multiplexor de conmutadores solo se necesita realizar una vez por sistema.

- [0059] La FIG. 8 es un diagrama de flujo que ilustra un sistema de codificación de acuerdo con determinados aspectos de la invención. Uno o más dispositivos de CI 202 y 230 pueden implementar el procedimiento. En la

- etapa 802, el uno o más dispositivos de CI 202 pueden determinar un tipo de interfaz física que se va a usar para una comunicación entre dos dispositivos en un terminal móvil inalámbrico. El tipo de interfaz física puede ser uno de una pluralidad de tipos de interfaz física admitidos por al menos uno de los dos dispositivos. Uno o más de los dispositivos pueden incluir un codificador de  $N$  fases y un codificador diferencial, por ejemplo.

- [0060] En la etapa 804, el uno o más dispositivos de CI 202 pueden seleccionar un codificador para generar datos codificados consecuentes con el tipo de interfaz física que se va a usar para una comunicación entre los dos dispositivos. Los datos se pueden comunicar a través de un bus que tiene una pluralidad de conectores que acoplan comunicativamente los dos dispositivos. La pluralidad de conectores puede incluir al menos algunos conectores bidireccionales. Los conectores pueden incluir conectores eléctricos u ópticos.

- [0061] De acuerdo con determinados aspectos divulgados en el presente documento, el codificador puede proporcionar los datos codificados en señales codificadas diferencialmente. Configurar la pluralidad de controladores para recibir los datos codificados puede incluir hacer que una o más salidas de otro codificador pasen a un modo de alta impedancia. El otro codificador puede incluir un codificador de  $N$  fases.

- [0062] De acuerdo con determinados aspectos divulgados en el presente documento, el codificador seleccionado puede proporcionar los datos codificados en una secuencia de símbolos codificados usando una combinación de un estado de fase de un primer par de los conectores, una polaridad de un segundo par de conectores y una selección de al menos un conector no excitado. El primer par de los conectores puede comprender los mismos cables que el segundo par de conectores o al menos un cable diferente. Configurar la pluralidad de controladores para recibir los datos codificados puede incluir hacer que una o más salidas de un codificador diferencial pasen a un modo de alta impedancia.

- [0063] En la etapa 806, el uno o más dispositivos de CI 202 pueden configurar una pluralidad de controladores para recibir los datos codificados desde el codificador y para excitar una pluralidad de conectores que acoplan comunicativamente los dos dispositivos de acuerdo con el tipo de interfaz física que se va a usar para una comunicación entre los dos dispositivos. La pluralidad de controladores se puede configurar controlando una pluralidad de interruptores para acoplar las salidas del codificador a la pluralidad de controladores.

- [0064] En un aspecto de la divulgación, los datos codificados se pueden referir a una cámara o una pantalla controlada por uno de los dos dispositivos de CI.

- [0065] La FIG. 9 es un diagrama 900 que ilustra un ejemplo simplificado de una implementación de hardware para un aparato que emplea un circuito de procesamiento 902. El circuito de procesamiento 902 puede estar implementado con una arquitectura de bus, representada, en general, mediante el bus 920. El bus 920 puede incluir cualquier número de buses y puentes de interconexión, dependiendo de la aplicación específica del circuito de procesamiento 902 y de las restricciones de diseño globales. El bus 920 enlaza entre sí diversos circuitos, incluyendo uno o más procesadores y/o módulos de hardware, representados mediante el procesador 916, los módulos o circuitos 904, 906 y 908, una pluralidad de codificadores diferentes 910, controladores de línea configurables para excitar conectores o cables 914 y el medio de almacenamiento legible por ordenador 918. El bus 920 también puede enlazar otros circuitos diversos, tales como fuentes de temporización, dispositivos periféricos, reguladores de tensión y circuitos de gestión de alimentación, que son bien conocidos en la técnica y que, por lo tanto, no se describirán en mayor detalle.

- [0066] El procesador 916 es responsable del procesamiento general, que incluye la ejecución de software almacenado en el medio de almacenamiento legible por ordenador 918. El software, cuando es ejecutado por el procesador 916, hace que el circuito de procesamiento 902 realice las diversas funciones descritas *supra* para cualquier aparato particular. El medio de almacenamiento legible por ordenador 918 también se puede usar para almacenar datos que el procesador 916 manipula cuando ejecuta el software. El circuito de procesamiento 902 incluye además al menos uno de los módulos 904, 906 y 908. Los módulos pueden ser módulos de software que se ejecutan en el procesador 916, residentes/almacenados en el medio de almacenamiento legible por ordenador 918, uno o más módulos de hardware acoplados al procesador 916, o alguna combinación de los mismos.

- [0067] En una configuración, el aparato 900 para comunicación inalámbrica incluye medios 904 para determinar un modo de funcionamiento para una comunicación entre los dos dispositivos de CI, medios 906 para seleccionar uno de los codificadores 910 para proporcionar datos codificados para transmisión en la pluralidad de conectores 914, y medios 908 para configurar una pluralidad de controladores 912 para recibir datos codificados desde el codificador 910 y para excitar los conectores y/o cables 914. Los medios mencionados anteriormente pueden ser uno o más de los módulos mencionados anteriormente del aparato 900 y/o el circuito de procesamiento 902 del aparato 902 configurado para realizar las funciones indicadas mediante los medios mencionados anteriormente. Los medios mencionados anteriormente se pueden implementar, por ejemplo, usando alguna combinación de un procesador 206 o 236, unos controladores de capa física 210 o 240 y unos medios de almacenamiento 208 y 238.

- [0068] Se entiende que el orden o la jerarquía específicos de las etapas de los procesos divulgados son ilustrativos de enfoques ejemplares. En base a las preferencias de diseño, se entiende que el orden o la jerarquía

específicos de las etapas de los procesos se pueden reorganizar. Las reivindicaciones de procedimiento adjuntas presentan elementos de las diversas etapas en un orden de muestra y no se pretende limitarlas al orden o la jerarquía específicos presentados.

- 5 [0069] La invención está definida únicamente por las reivindicaciones adjuntas.

## **REIVINDICACIONES**

1. Un procedimiento de transferencia de datos operativo en al menos uno de dos dispositivos (202, 230) de un terminal, estando los dos dispositivos acoplados comunicativamente a través de un enlace de comunicación (220), siendo configurable dicho enlace de comunicación para compatibilidad con una pluralidad de normas de interfaz física, comprendiendo el procedimiento:

5 determinar (802) una norma de interfaz física que se va a usar para una comunicación entre los dos dispositivos (202, 230), en el que la norma de interfaz física es una de unas normas de interfaz física admitidas por al menos uno de los dos dispositivos (202, 230);

10 seleccionar (804) un codificador (210, 240) de una pluralidad de codificadores disponibles para al menos uno de los dos dispositivos para generar datos codificados consecuentes con la norma de interfaz física que se va a usar para una comunicación entre los dos dispositivos (232, 230); y

15 configurar (806) una pluralidad de controladores (210, 240) para recibir los datos codificados desde el codificador y para excitar una pluralidad de conectores que acoplan comunicativamente los dos dispositivos de acuerdo con la norma de interfaz física que se va a usar para una comunicación entre los dos dispositivos,

20 en el que el codificador (210, 240) se selecciona de la pluralidad de codificadores que incluye un primer codificador configurado para proporcionar los datos codificados en señales codificadas diferencialmente y un segundo codificador que es un codificador de N fases configurado para codificar datos en una secuencia de símbolos usando una combinación de un estado de fase de un primer par de la pluralidad de conectores, una polaridad de un segundo par de la pluralidad de conectores, y una selección de al menos un conector no excitado.

25

30 2. El procedimiento de la reivindicación 1, que comprende además controlar una pluralidad de conmutadores (726) para acoplar salidas del codificador a la pluralidad de controladores.

35 3. El procedimiento de la reivindicación 1 o la reivindicación 2, en el que configurar la pluralidad de controladores (210, 240, 706, 710, 712) para recibir los datos codificados incluye hacer que una o más salidas de un codificador diferente, diferente al codificador seleccionado, pasen a un modo de alta impedancia.

40 4. Un programa informático que comprende instrucciones que, cuando son ejecutadas por un circuito de procesamiento, hacen que el circuito de procesamiento realice el procedimiento de cualquiera de las reivindicaciones 1 a 3.

45 5. Un aparato que comprende:

50 una pluralidad de conectores que acoplan comunicativamente un primer dispositivo de circuito integrado, CI, con un segundo dispositivo de CI de un terminal; teniendo los dos dispositivos de CI un enlace de comunicación (220) entre los mismos, comprendiendo dicho enlace de comunicación una pluralidad de tipos de interfaz física, estando configurada al menos una interfaz física para admitir al menos dos sistemas de codificación;

55 medios para determinar (904) un tipo de interfaz física que se va a usar para una comunicación entre los dos dispositivos de CI del terminal, en el que el tipo de interfaz física es uno de una pluralidad de tipos de interfaz física admitidos por al menos uno de los dos dispositivos de CI;

60 medios para generar datos codificados (906) consecuentes con el tipo de interfaz física que se va a usar para una comunicación entre los dos dispositivos de CI, en el que los medios para generar datos codificados incluyen al menos dos codificadores (210, 240, 910) que están configurados para codificar datos de diferentes maneras; y

65 medios para configurar una pluralidad de controladores (210, 240, 908, 912) para recibir los datos codificados desde uno de los al menos dos codificadores (210, 240, 910) y para excitar la pluralidad de conectores que acoplan comunicativamente los dos dispositivos de CI de acuerdo con el tipo de interfaz física que se va a usar para una comunicación entre los dos dispositivos de CI,

70 en el que los al menos dos codificadores (210, 240, 910) incluyen un primer codificador configurado para proporcionar los datos codificados en señales codificadas diferencialmente y un segundo codificador que es un codificador de N fases configurado para codificar datos en una secuencia de símbolos usando una combinación de un estado de fase de un primer par de la pluralidad de conectores,

una polaridad de un segundo par de la pluralidad de conectores, y una selección de al menos un conector no excitado.

- 5      6. El aparato de la reivindicación 5, en el que los medios para configurar la pluralidad de controladores comprenden una pluralidad de conmutadores (726) que conecta selectivamente salidas del uno de los al menos dos codificadores (210, 240, 910) a la pluralidad de controladores (210, 240, 908, 912).

- 10     7. El aparato de la reivindicación 5 o 6, en el que los medios para configurar la pluralidad de controladores (210, 240, 908, 912) están configurados para hacer que una o más salidas de uno diferente de los al menos dos codificadores pasen a un modo de alta impedancia.

- 15     8. El aparato de cualquiera de las reivindicaciones 5 a 7, en el que los medios para configurar la pluralidad de controladores (210, 240, 908, 912) están configurados para hacer que una o más salidas de un codificador diferencial pasen a un modo de alta impedancia.

9. El aparato de la reivindicación 5, en el que los medios para determinar, los medios para generar, y los medios para configurar comprenden un circuito de procesamiento.

FIG. 1

FIG. 2

**FIG. 3**

FIG. 4

FIG. 5

FIG. 6

FIG. 7

**FIG. 8**

**FIG. 9**