(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6076616号

(P6076616)

(45) 発行日 平成29年2月8日(2017.2.8)

(24) 登録日 平成29年1月20日(2017.1.20)

|                        |             |         |  |

|------------------------|-------------|---------|--|

| (51) Int.Cl.           | F 1         |         |  |

| HO3K 19/0944 (2006.01) | HO3K 19/094 | Z NMA   |  |

| HO1L 29/786 (2006.01)  | HO1L 29/78  | 6 1 8 B |  |

| HO1L 21/8238 (2006.01) | HO1L 29/78  | 6 1 3 A |  |

| HO1L 27/092 (2006.01)  | HO1L 27/08  | 3 2 1 L |  |

| HO3K 17/687 (2006.01)  | HO1L 27/08  | 3 2 1 G |  |

請求項の数 1 (全 73 頁) 最終頁に続く

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2012-104413 (P2012-104413)  |

| (22) 出願日     | 平成24年5月1日(2012.5.1)           |

| (65) 公開番号    | 特開2012-253751 (P2012-253751A) |

| (43) 公開日     | 平成24年12月20日(2012.12.20)       |

| 審査請求日        | 平成27年4月27日(2015.4.27)         |

| (31) 優先権主張番号 | 特願2011-103821 (P2011-103821)  |

| (32) 優先日     | 平成23年5月6日(2011.5.6)           |

| (33) 優先権主張国  | 日本国(JP)                       |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 閑根 英輔<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| 審査官       | 白井 亮                                           |

前置審査

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1及び第2の入力端子と、出力端子と、第1乃至第6のトランジスタと、を有し、前記第1の入力端子は、前記第1のトランジスタを介して、前記第3のトランジスタのゲート及び前記第5のトランジスタのゲートと電気的に接続され、前記第2の入力端子は、前記第2のトランジスタを介して、前記第4のトランジスタのゲート及び前記第6のトランジスタのゲートと電気的に接続され、前記出力端子は、前記第3のトランジスタ又は前記第4のトランジスタを介して第1の配線と電気的に接続され、前記出力端子は、前記第5のトランジスタ及び前記第6のトランジスタを介して第2の配線と電気的に接続され、

前記第1及び第2のトランジスタは、酸化物半導体を有することを特徴とする半導体装置。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

トランジスタなどの半導体素子を含む論理回路に関する。また、該論理回路を有する半導体装置に関する。

## 【0002】

なお、本明細書において半導体装置とは、半導体特性を利用して機能しうる装

10

20

置全般をいい、該論理回路を含む半導体回路や、該半導体回路を含む電気光学装置および発光表示装置などの電子機器も全て半導体装置である。

【背景技術】

【0003】

一般的に、Si-waferやSOI(Silicon On Insulator)基板を用いて作製されたトランジスタを有する回路は、微細に形成されることで動作電圧が小さくなり、結果として、該回路(さらには該回路を有する半導体装置)における消費電力は小さくなる。

【0004】

また、演算処理を行う各種論理回路は、電源を投入(オン)した状態で動作し、電源を切断(オフ)した状態で停止する。また、該各種論理回路において、電源をオフすると、オフする直前に行われていた処理内容が消去される。

【0005】

例えば、レジスタ回路、ラッチ回路およびフリップフロップ回路などの論理状態を記憶しておくべき順序回路を含む論理回路として、仮想電源線および仮想接地線が真の電源線および真の接地線の間に設けられ、該真の電源線および該仮想電源線の間にpチャネル型トランジスタが設けられ、該真の接地線および該仮想接地線の間にnチャネル型トランジスタが設けられ、該仮想電源線および該仮想接地線の間に該順序回路が設けられた論理回路がある(特許文献1参照)。該論理回路は、該pチャネル型トランジスタおよび該nチャネル型トランジスタにおいて導通状態と非導通状態を周期的に繰り返すことで該論理回路が保持する情報を欠落させないように動作させることができる。

【0006】

さらに、上記論理回路をnチャネル型トランジスタおよびpチャネル型トランジスタを含むCMOS回路で構成することができるが、MOSトランジスタの微細化に伴ってオフ電流が増大するため、非動作時の消費電力(待機時の消費電力、以下、待機電力とも呼ぶ。)の増大が問題となっている。例えば、チャネル長が0.1μm以下程度に微細化されたシリコンMOSトランジスタでは、ソースを基準としてゲートに印加される電圧(Vgs)ともいう。)をしきい値電圧より低くしても、ソースおよびドレイン間の電流をゼロすることはできない。なお、本明細書においては、このようにトランジスタのVgsが該トランジスタのしきい値電圧より低い場合に流れるソースおよびドレイン間の電流をオフ電流とする。

【0007】

上述したオフ電流に起因する待機電力の増大を抑制するために、スイッチングトランジスタを用いる技術が提案されている(特許文献2参照)。特許文献2に開示の技術は、電源とCMOS回路との間に、該CMOS回路と比較してオフ電流が小さいスイッチングトランジスタを設け、該CMOS回路が動作していないとき(非動作時)には該スイッチングトランジスタをオフすることで待機電力を低減しようとするものである。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開平9-64715号公報

【特許文献2】特開2008-219882号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかし、特許文献1で開示される技術のように、真の電源線および真の接地線の他に仮想電源線および仮想接地線を設けることや、極性の異なるトランジスタを形成することは、論理回路の作製工程数を増加させ、該論理回路における該トランジスタの占有面積を拡大することになり、論理回路の微細化に適していない。

【0010】

10

20

30

40

50

また、特許文献 2 で開示される技術のように、スイッチングトランジスタを設ける場合、CMOS 回路に十分な電流を供給し、該 CMOS 回路の動作を確保するために、スイッチングトランジスタのチャネル幅を、該 CMOS 回路を構成するトランジスタのチャネル幅と同等、またはそれ以上とする必要が生じる。したがって、スイッチングトランジスタのチャネル幅を、集積回路を構成するトランジスタのチャネル幅より小さくして、スイッチングトランジスタ自体のオフ電流を抑制するという方法は、作製工程の観点から困難であるといえる。

#### 【0011】

そこで、本発明の一態様は、微細化に適し、且つ演算処理を実行中に電源をオフする場合でも、電源をオフする直前に入力された電位を保持できる論理回路を提供することを課題の一とする。また、該論理回路を有する半導体装置を提供することを課題とする。

10

#### 【課題を解決するための手段】

#### 【0012】

本発明の一態様は、高電位側電源電位線および低電位側電源電位線の間に設けられた 1 以上の入力端子および 1 以上の出力端子を有する論理回路において、該論理回路に入力された電位、または演算処理後の電位を低下させる電流経路（リーコンプルメント経路ともいう）に、極めてオフ電流の低いスイッチング素子（例えばトランジスタなど）を設けることで、論理回路の電源をオフした後も入力された電位、または演算処理後の電位が保持されることである。

#### 【0013】

20

本発明の一態様は、入力端子および出力端子と、入力端子および出力端子に電気的に接続された主要論理回路部と、入力端子および主要論理回路部に電気的に接続されたスイッチング素子とを有し、スイッチング素子の第 1 端子は入力端子と電気的に接続されており、スイッチング素子の第 2 端子は主要論理回路部を構成する 1 以上のトランジスタのゲートと電気的に接続されており、スイッチング素子は、オフ状態におけるリーコンプルメント電流がチャネル幅  $1 \mu m$  あたり  $1 \times 10^{-17} A$  以下のトランジスタとする論理回路である。

#### 【0014】

また、本発明の別の態様は、上記論理回路において、入力端子は複数設けられていてもよく、その場合は、スイッチング素子も同数設け、各スイッチング素子の第 1 端子は、各入力端子と電気的に接続され、各スイッチング素子の第 2 端子は主要論理回路を構成する 1 以上のトランジスタのゲートと電気的に接続された論理回路である。

30

#### 【0015】

また、本発明の別の態様は、入力端子および出力端子と、入力端子および出力端子、ならびに高電位側電源電位線および低電位側電源電位線に電気的に接続された主要論理回路部と、高電位側電源電位線および低電位側電源電位線、ならびに出力端子との間で構成される電流経路とにおいて、主要論理回路部内に第 1 のスイッチング素子および第 2 のスイッチング素子を有し、第 1 のスイッチング素子の第 1 端子は高電位側電源電位線と、第 1 のスイッチング素子の第 2 端子は出力端子と電気的に接続されており、第 2 のスイッチング素子の第 1 端子は低電位側電源電位線と、第 2 のスイッチング素子の第 2 端子は出力端子と電気的に接続されており、第 1 のスイッチング素子および第 2 のスイッチング素子は、オフ状態におけるリーコンプルメント電流がチャネル幅  $1 \mu m$  あたり  $1 \times 10^{-17} A$  以下のトランジスタとする論理回路である。つまり、第 1 のスイッチング素子および第 2 のスイッチング素子のそれぞれは、該電流経路において、該出力端子と電気的に接続されている。

40

#### 【0016】

また、本発明の別の態様は、上記論理回路において、上記電流経路において、3 以上のスイッチング素子を有し、3 以上のスイッチング素子のうち、少なくとも 1 のスイッチング素子の第 1 端子は高電位側電源電位線と、少なくとも 1 のスイッチング素子の第 2 端子は出力端子と電気的に接続されており、3 以上のスイッチング素子のうち、残りのスイッチング素子の第 1 端子は低電位側電源電位線と、残りのスイッチング素子の第 2 端子は出力端子と電気的に接続されている論理回路である。つまり、上記電流経路において、3

50

以上のスイッチング素子を設けても、出力端子と電気的に接続されている。

【0017】

上記した本発明の一態様の主要論理回路部としては、NOT回路、NAND回路、NOR回路、AND回路、OR回路、XOR回路、XNOR回路が挙げられる。

【0018】

上記した本発明の一態様の論理回路において、オフ状態におけるリーク電流がチャネル幅  $1 \mu m$  あたり  $1 \times 10^{-17} A$  以下のトランジスタは、酸化物半導体などのワイドギャップ半導体をチャネル形成領域に用いることができる。特に、水素濃度が  $5 \times 10^{19} / cm^3$  以下であり、且つ化学量論的組成比に対して酸素が過剰に含まれている酸化物半導体をチャネル形成領域に用いることが好ましい。また、本明細書における酸化物半導体とは、半導体特性を示す金属酸化物である。そして、該酸化物半導体は、インジウム、ガリウム、スズおよび亜鉛から選ばれた一種以上の元素を含む金属酸化物である。

10

【0019】

また、本発明の別の一態様としては、上記本発明の一態様である論理回路を有する半導体装置である。

【発明の効果】

【0020】

電源をオフにした場合でも、電源をオフする直前に入力された電位を保持することができ、再度電源をオンした後、電源をオフする直前の状態から演算処理を素早く再開できる論理回路を提供できる。

20

【0021】

論理回路を構成するnチャネル型トランジスタに酸化物半導体を用いることで、該論理回路におけるCMOS回路を、重畠したpチャネル型トランジスタおよびnチャネル型トランジスタによって形成でき、該論理回路の微細化が可能となる。さらに、酸化物半導体を用いたトランジスタはオフ電流が極めて小さいため、微細化が可能であり、且つ消費電力が低減された該論理回路および該論理回路を有する半導体装置を提供できる。なお、本明細書において、消費電力とは、待機時の消費電力（待機電力）を含むものとする。

【図面の簡単な説明】

【0022】

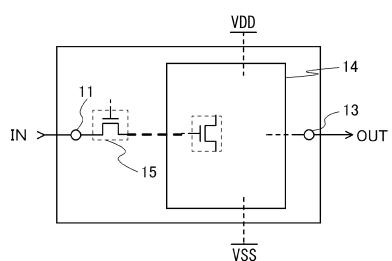

【図1】本発明の一態様である論理回路を説明するブロック図。

30

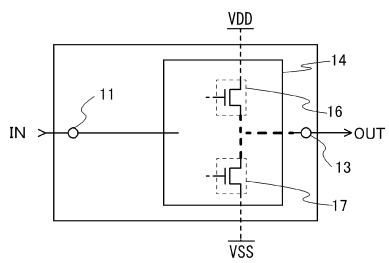

【図2】本発明の一態様である論理回路を説明するブロック図。

【図3】本発明の一態様に係る論理回路を説明する回路図。

【図4】本発明の一態様に係る論理回路を説明する回路図。

【図5】本発明の一態様に係る論理回路を説明する回路図。

【図6】本発明の一態様に係る論理回路を説明する回路図。

【図7】本発明の一態様に係る論理回路を説明する回路図。

【図8】本発明の一態様に係る論理回路を説明する回路図。

【図9】本発明の一態様に係る論理回路を説明する回路図。

【図10】本発明の一態様に係る論理回路を説明する回路図。

【図11】本発明の一態様に係る論理回路を説明する回路図。

40

【図12】本発明の一態様に係る論理回路を説明する回路図。

【図13】本発明の一態様に係る論理回路を説明する回路図。

【図14】本発明の一態様に係る論理回路を説明する回路図。

【図15】本発明の一態様に係る論理回路を説明する回路図。

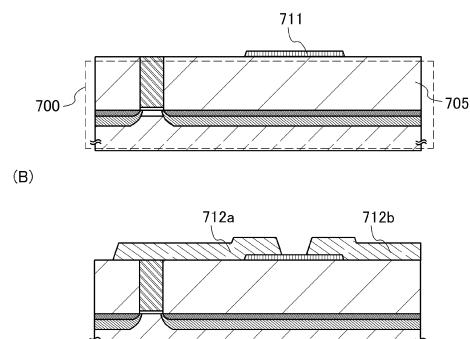

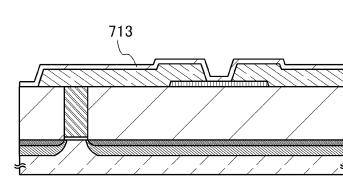

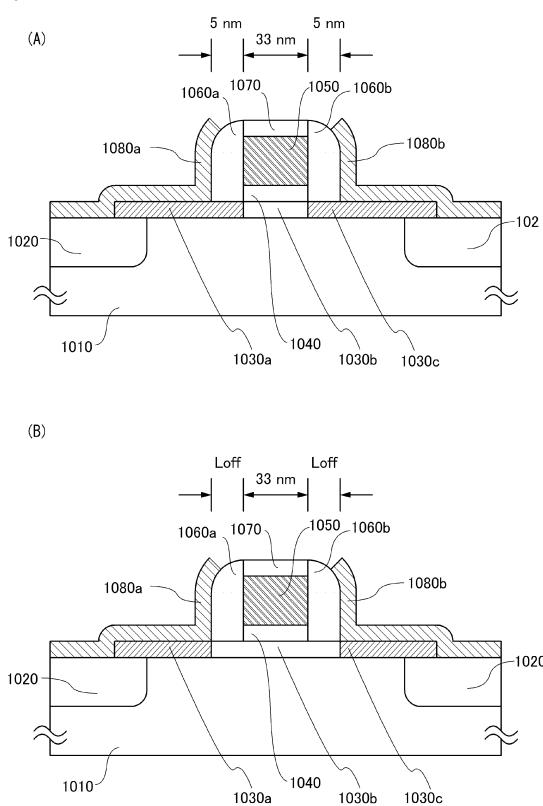

【図16】本発明の一態様に係るトランジスタを説明する断面図。

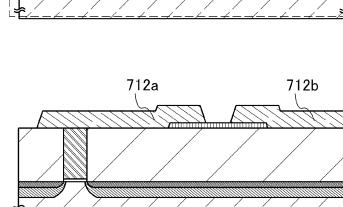

【図17】本発明の一態様に係るトランジスタの作製方法を説明する断面図。

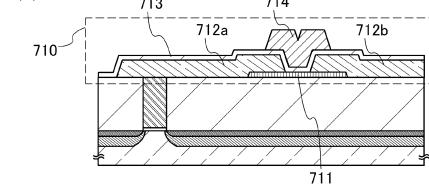

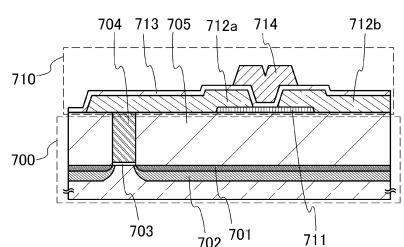

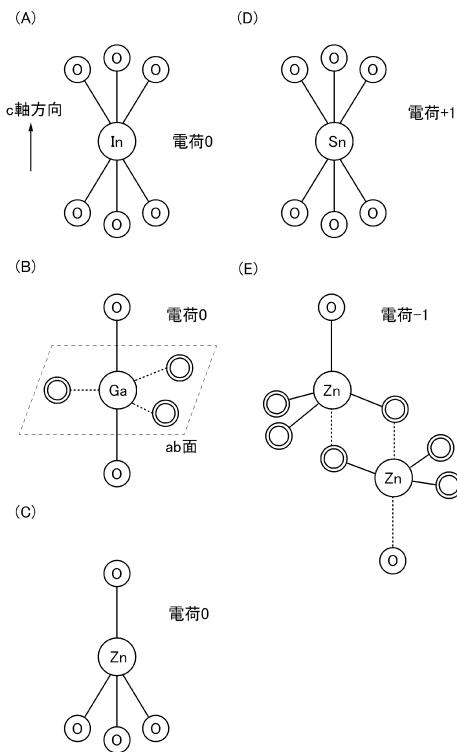

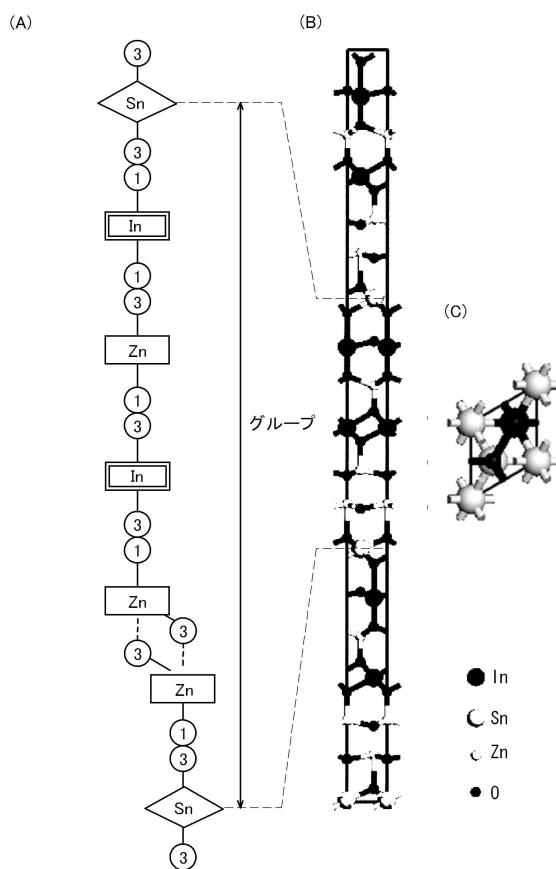

【図18】本発明の一態様に係る酸化物材料の構造を説明する図。

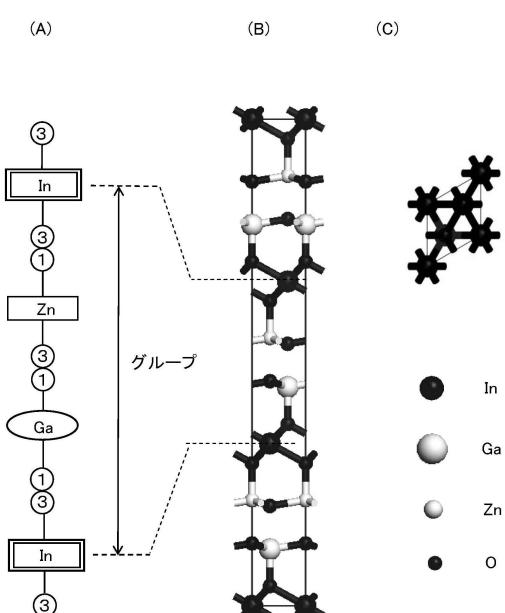

【図19】本発明の一態様に係る酸化物材料の構造を説明する図。

【図20】本発明の一態様に係る酸化物材料の構造を説明する図。

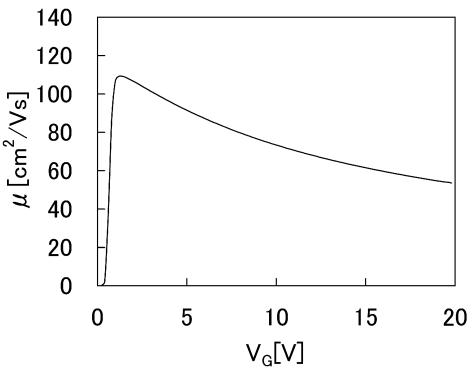

【図21】酸化物半導体を用いたトランジスタにおける電界効果移動度のゲート電圧依存

50

性の計算結果を説明する図。

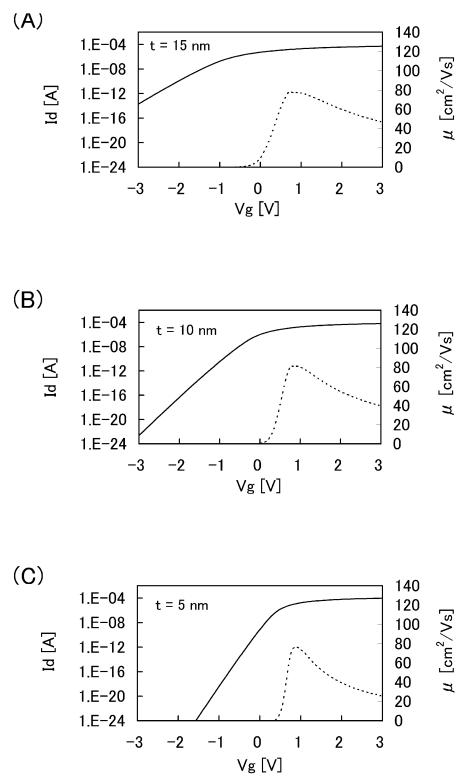

【図22】酸化物半導体を用いたトランジスタにおけるドレイン電流と移動度のゲート電圧依存性の計算結果を説明する図。

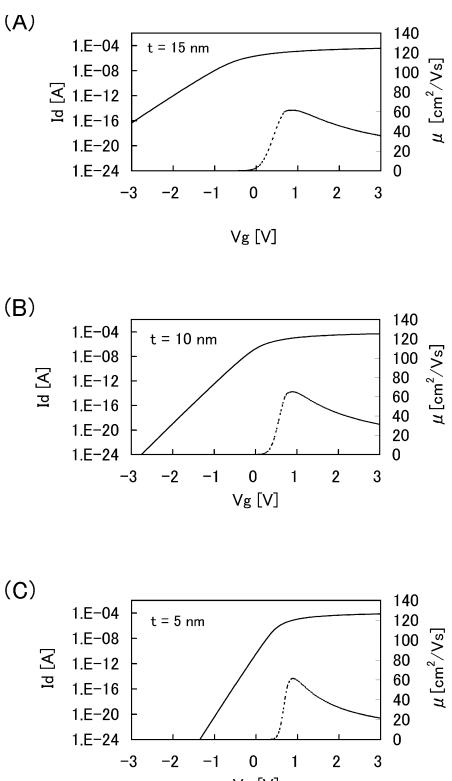

【図23】酸化物半導体を用いたトランジスタにおけるドレイン電流と移動度のゲート電圧依存性の計算結果を説明する図。

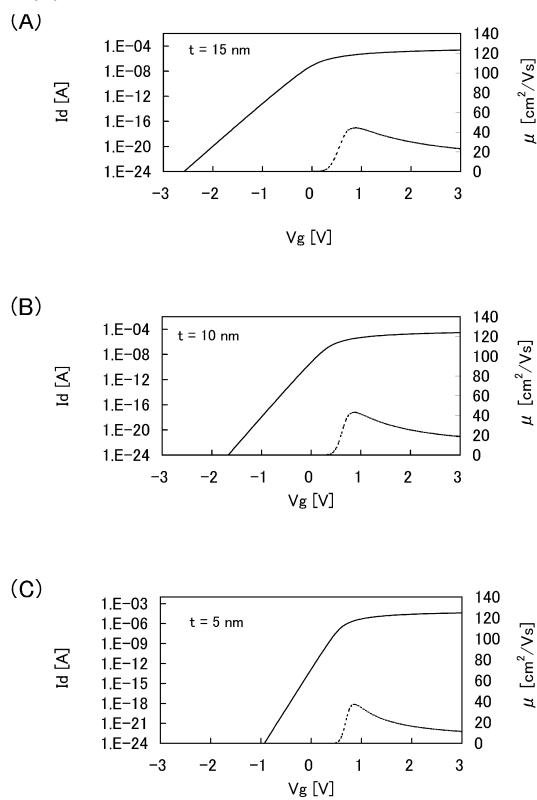

【図24】酸化物半導体を用いたトランジスタにおけるドレイン電流と移動度のゲート電圧依存性の計算結果を説明する図。

【図25】計算に用いたトランジスタの断面構造を説明する図。

【発明を実施するための形態】

【0023】

10

本発明の実施の形態について、図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同一部分または同様な機能を有する部分には、同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

【0024】

なお、本明細書で説明する各図において、各構成の大きさ、膜の厚さ、または領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。

20

【0025】

また、本明細書にて用いる第1、第2、第3などの用語は、構成要素の混同を避けるために付したものであり、数的に限定するものではない。そのため、例えば、「第1の」を「第2の」または「第3の」などと適宜置き換えて説明することができる。

【0026】

本明細書において、「AはBと電気的に接続される」または「AはBに電気的に接続される」と記載する場合、A、Bが直接接続されている場合と、AとBとの間に対象物を介して接続されている場合を含む。なお、A、Bおよび該対象物は、例えば、トランジスタなどのスイッチング素子、容量素子、抵抗素子、インダクタ、端子、回路、配線、電極、導電膜、などAとBとの間で電気信号の授受を可能とするものである。

30

【0027】

本明細書において、「ソース」とは、ソース電極、およびソース電極と電気的に接続されている領域又は対象物（例えば、ソース領域またはソース端子）などを含むものとする。「ドレイン」とは、ドレイン電極、およびドレイン電極と電気的に接続されている領域または対象物（例えば、ドレイン領域またはドレイン端子）などを含むものとする。また、トランジスタのソースおよびドレインは、トランジスタの極性や動作条件等によって替わるため、いざれがソースまたはドレインであるかを特定することが困難である。そこで、ソース端子およびドレイン端子の一方を第1端子、ソース端子およびドレイン端子の他方を第2端子と表記し、区別することとする。なお、「ゲート」と記載する場合は、ゲート電極、およびゲート電極と電気的に接続されている領域または対象物（例えば、ゲート端子）などを含むものとする。

40

【0028】

(実施の形態1)

本実施の形態では、本発明の一態様である論理回路の一例について説明する。はじめに、1以上の入力端子および1以上の出力端子を有する論理回路について説明する。なお、本明細書中において、論理回路に高電位側電源電位線および低電位側電源電位線は含まれないものとし、出力端子は定電位および接地電位などと、電気的に接続されておらずリードがないものとする。

【0029】

図1(A)に示す論理回路10は、主要論理回路部14と、入力電位信号(IN)が入

50

力される入力端子 11 と電気的に接続されたトランジスタ 15 と、演算処理後の出力電位信号 (OUT) が出力される出力端子 13 と、を有する。主要論理回路部 14 は、高電位側電源電位線および低電位側電源電位線と電気的に接続されており、入力端子 11 は、トランジスタ 15 の第 1 端子と電気的に接続されており、トランジスタ 15 の第 2 端子は、主要論理回路部 14 を構成するトランジスタのゲートと電気的に接続されている。また、主要論理回路部 14 は、他のトランジスタ、容量素子および抵抗素子などによって構成されていてもよい。

#### 【0030】

トランジスタ 15 が導通状態のとき (トランジスタ 15 の  $V_{GS}$  がしきい値電圧より高いとき)、主要論理回路部 14 は入力電位信号に基づいて演算処理を行う。つまり、トランジスタ 15 のゲートに高電位が入力されているとき、論理回路 10 は、入力電位信号によって、高電位側電源電位線 (図示せず) に対応して高電位側電源電位 ( $V_{DD}$  ともいう) である高電位、または低電位側電源電位線 (図示せず) に対応して低電位側電源電位 ( $V_{SS}$  ともいう) である低電位を出力する。なお、本明細書において高電位側電源電位 ( $V_{DD}$ ) は任意の正電位とすることができます。また、低電位側電源電位 ( $V_{SS}$ ) は、高電位側電源電位よりも低い電位であり、例えば、接地電位または  $0V$  とすることができます。

#### 【0031】

また、論理回路 10 において、トランジスタ 15 は極めてオフ電流が低いトランジスタで構成されている。例えば、極めてオフ電流が低いトランジスタの一例としては、室温 (25) における単位チャネル幅 ( $1\ \mu m$ )あたりの値が、 $10\ aA/\ \mu m$  ( $1 \times 10^{-17}\ A/\ \mu m$ ) 以下、さらには、 $1\ aA/\ \mu m$  ( $1 \times 10^{-18}\ A/\ \mu m$ ) 以下、さらには  $1\ zA/\ \mu m$  ( $1 \times 10^{-21}\ A/\ \mu m$ ) 以下、さらには  $1\ yA/\ \mu m$  ( $1 \times 10^{-24}\ A/\ \mu m$ ) 以下となるトランジスタである。

#### 【0032】

このように、論理回路 10 のトランジスタ 15 は極めてオフ電流の低いトランジスタであるため、演算処理中に、トランジスタ 15 を非導通状態 (トランジスタ 15 の  $V_{GS}$  がしきい値電圧より低い状態) にした後であれば、電源をオフにしても、論理回路 10 は、トランジスタ 15 の第 2 端子に電気的に接続された主要論理回路部 14 を構成するトランジスタのゲートの間で構成されるノードの電位を保持することができる。そして、再度電源をオンした後、トランジスタ 15 を導通状態にすることで、該ノードに保持された電位をもとに演算処理を再開できる。つまり、電源をオフする直前の状態から演算処理を再開できる。したがって、再度電源をオンした際に入力電位信号を供給する必要が無く、素早く演算処理を再開することができる。また、論理回路 10 の消費電力を低減することができる。

#### 【0033】

なお、本明細書において、電源をオフするとは、高電位側電源電位線と低電位側電源電位線との間に電位差を生じていない状態にすることを意味する。また、電源をオンするとは、高電位側電源電位線と低電位側電源電位線との間に電位差が生じる状態にすることを意味する。

#### 【0034】

本発明の一態様である論理回路は、1 の入力端子および1 の出力端子を有する論理回路に限らず、複数の入力端子および複数の出力端子を有する論理回路であってもよい。例えば、該論理回路は、2 の入力端子および1 の出力端子を有する論理回路や、2 の入力端子および2 の出力端子を有する論理回路、複数の入力端子および1 の出力端子を有する論理回路など、様々な回路構成とすることができます。その際、複数の入力端子の各入力端子と主要論理回路部を構成する1 以上のトランジスタのゲートとの間に極めてオフ電流の低いトランジスタを電気的に接続すればよい。

#### 【0035】

次に論理回路 10 の変形例について説明する。図 1 (B) に示した該変形例である論理

10

20

30

40

50

回路 20 は、2 以上の極めてオフ電流の低いトランジスタを含む主要論理回路部 14 と、入力端子 11 と、出力端子 13 とを有する。

【0036】

主要論理回路部 14 において、高電位側電源電位線および低電位側電源電位線ならびに出力端子 13 間に構成される電流経路において、第 1 のトランジスタ 16 および第 2 のトランジスタ 17 が該出力端子と電気的に接続されている。

【0037】

高電位側電源電位線と第 1 のトランジスタ 16 の第 1 端子は電気的に接続されており、出力端子 13 と第 1 のトランジスタ 16 の第 2 端子は電気的に接続されている。低電位側電源電位線と第 2 のトランジスタ 17 の第 1 端子は電気的に接続されており、出力端子 13 と第 2 のトランジスタ 17 の第 2 端子は電気的に接続されている。10

【0038】

なお、第 1 のトランジスタ 16 の第 1 端子と高電位側電源電位線との間、第 1 のトランジスタ 16 の第 2 端子と第 2 のトランジスタ 17 の第 2 端子との間、および第 2 のトランジスタ 17 の第 1 端子と低電位側電源電位線との間には、主要論理回路部 14 は、他のトランジスタ、容量素子および抵抗素子などが電気的に接続されていてもよい。

【0039】

論理回路 20 は、第 1 のトランジスタ 16 および第 2 のトランジスタ 17 が導通状態であるとき演算処理を行う。

【0040】

論理回路 20 において、第 1 のトランジスタ 16 および第 2 のトランジスタ 17 は、トランジスタ 15 と同様に極めてオフ電流が低いトランジスタである。なお、第 1 のトランジスタ 16 および第 2 のトランジスタ 17 の一例は、トランジスタ 15 の一例と同じである。20

【0041】

このように、論理回路 20 の第 1 のトランジスタ 16 および第 2 のトランジスタ 17 は極めてオフ電流の低いトランジスタであるため、演算処理中に、第 1 のトランジスタ 16 および第 2 のトランジスタ 17 を非導通状態（第 1 のトランジスタ 16 および第 2 のトランジスタ 17 の  $V_{gs}$  がしきい値電圧より低い状態）にした後であれば、電源をオフにしても、論理回路 20 は、出力端子 13 および第 1 のトランジスタ 16 の第 2 端子ならびに第 2 のトランジスタ 17 の第 2 端子の間で構成されるノードの電位を保持することができる。そして、再度電源をオンした後、第 1 のトランジスタ 16 および第 2 のトランジスタ 17 を導通状態（第 1 のトランジスタ 16 および第 2 のトランジスタ 17 の  $V_{gs}$  がしきい値電圧より高い状態）にすることで、電源をオフする直前の状態から演算処理を再開できる。したがって、再度電源をオンした際に入力電位信号を供給する必要が無く、素早く演算処理を再開することができる。また、論理回路 20 の消費電力を低減することができる。30

【0042】

また、本発明の一態様である論理回路において、主要論理回路部の構成よっては、複数の入力端子および 1 の出力端子を有する論理回路に、極めてオフ電流の低いトランジスタを 2 以上設ける必要がある。40

【0043】

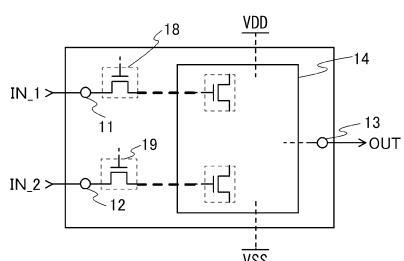

そこで、図 2 (A) および図 2 (B) に、2 の入力端子および 1 の出力端子を有する論理回路 30 および論理回路 40 について説明する。論理回路 30 は、2 の入力端子および 1 の出力端子を有する論理回路であって、2 の入力端子と主要論理回路部 14 の間に極めてオフ電流の低いトランジスタを設けた構成の論理回路である。

【0044】

論理回路 30 は、主要論理回路部 14 と、入力電位信号 (IN\_1) を供給する第 1 の入力端子 11 と電気的に接続された第 1 のトランジスタ 18 と、入力電位信号 (IN\_2) を供給する第 2 の入力端子 12 と電気的に接続された第 2 のトランジスタ 19 と、演算

10

20

30

40

50

処理後の出力電位信号(OUT)が出力される出力端子13とを有する。主要論理回路部14は、高電位側電源電位線および低電位側電源電位線と電気的に接続されており、第1の入力端子11は、第1のトランジスタ18の第1端子と電気的に接続されており、第2の入力端子12は、第2のトランジスタ19の第1端子と電気的に接続されている。第1のトランジスタ18の第2端子および第2のトランジスタ19の第2端子は、主要論理回路部14を構成するトランジスタのゲートと電気的に接続されている。また、主要論理回路部14は、他のトランジスタ、容量素子および抵抗素子などによって構成されていてもよい。

#### 【0045】

論理回路30は、第1のトランジスタ18および第2のトランジスタ19が導通状態であるとき演算処理を行う。 10

#### 【0046】

論理回路30において、第1のトランジスタ18および第2のトランジスタ19は、論理回路10におけるトランジスタ15と同様に極めてオフ電流が低いトランジスタである。なお、第1のトランジスタ18および第2のトランジスタ19の一例は、トランジスタ15の一例と同じである。

#### 【0047】

このように、論理回路30の第1のトランジスタ18および第2のトランジスタ19を極めてオフ電流の低いトランジスタであるため、演算処理中に、第1のトランジスタ18および第2のトランジスタ19を非導通状態(第1のトランジスタ18および第2のトランジスタ19のV<sub>gs</sub>がしきい値電圧より低い状態)にした後であれば、電源をオフにしても、論理回路30は、第1のトランジスタ18の第2端子に電気的に接続された主要論理回路部14を構成するトランジスタのゲートの間で構成されるノードの電位、および第2のトランジスタ19の第2端子に電気的に接続された主要論理回路部14を構成するトランジスタのゲートの間で構成されるノードの電位を保持することができる。そして、再度電源をオンした後、第1のトランジスタ18および第2のトランジスタ19を導通状態(第1のトランジスタ18および第2のトランジスタ19のV<sub>gs</sub>がしきい値電圧より高い状態)にすることで、該ノードに保持された電位をもとに演算処理を再開できる。つまり、電源をオフする直前の状態から演算処理を再開できる。したがって、再度電源をオンした際に入力電位信号を供給する必要が無く、素早く演算処理を再開することができる。 30

また、論理回路30の消費電力を低減することができる。

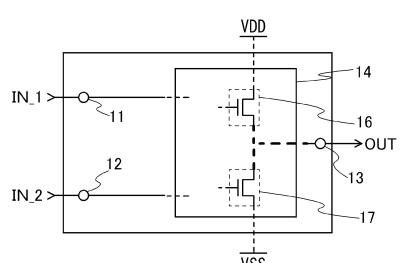

#### 【0048】

次に、図2(B)に示した論理回路30の変形例である論理回路40について説明する。論理回路40は、2の入力端子および1の出力端子を有する論理回路であって、図1(B)に示した論理回路20と同様に主要論理回路部に極めてオフ電流の低いトランジスタを含む構成の論理回路である。

#### 【0049】

図2(B)に示した論理回路40は、2以上のトランジスタを含む主要論理回路部14と、第1の入力端子11と、第2の入力端子12と、演算処理後の出力電位信号(OUT)が出力される出力端子13とを有する。 40

#### 【0050】

主要論理回路部14において、高電位側電源電位線および低電位側電源電位線ならびに出力端子13間に構成される電流経路において、第1のトランジスタ16および第2のトランジスタ17が該出力端子と電気的に接続されている。

#### 【0051】

高電位側電源線と第1のトランジスタ16の第1端子は電気的に接続されており、出力端子13と第1のトランジスタ16の第2端子は電気的に接続されている。低電位側電源線と第2のトランジスタ17の第1端子は電気的に接続されており、出力端子13と第2のトランジスタ17の第2端子は電気的に接続されている。

#### 【0052】

10

20

30

40

50

なお、第1のトランジスタ16の第1端子と高電位側電源電位線との間、第1のトランジスタ16の第2端子と第2のトランジスタ17の第2端子との間、および第2のトランジスタ17の第1端子と低電位側電源電位線との間には、主要論理回路部14は、他のトランジスタ、容量素子および抵抗素子などが電気的に接続されていてもよい。

【0053】

論理回路40は、第1のトランジスタ16および第2のトランジスタ17が導通状態であるとき演算処理を行う。

【0054】

論理回路40において、第1のトランジスタ16および第2のトランジスタ17は、論理回路10におけるトランジスタ15と同様に極めてオフ電流が低いトランジスタである。なお、第1のトランジスタ16および第2のトランジスタ17の一例は、トランジスタ15の一例と同じである。

10

【0055】

論理回路40の動作原理は、論理回路20と同様である。つまり、保持されるノードの電位は、出力端子13および第1のトランジスタ16の第2端子ならびに第2のトランジスタ17の第2端子の間で構成されるノードの電位である。したがって、再度電源をオンした際に入力電位信号を供給する必要が無く、素早く演算処理を再開することができる。また、論理回路40の消費電力を低減することができる。

【0056】

そして、論理回路10乃至論理回路40において、主要論理回路部14を構成するトランジスタについても、論理回路10のトランジスタ15に適用できる極めてオフ電流の低いトランジスタとすることできる。これにより、保持されているノードの電位が、主要論理回路部14を構成するトランジスタを介して低下することを抑制でき、さらに消費電力を低減することができる。

20

【0057】

以上より、論理回路10乃至論理回路40の消費電力が低減されることで、論理回路10乃至論理回路40のうちいずれか1以上を有する半導体装置も消費電力を低減することができる。さらに、論理回路10乃至論理回路40の消費電力を低減することで、論理回路10乃至論理回路40を動作させる外部回路の負荷が低減できる。これにより、論理回路10乃至論理回路40のうちいずれか1以上および該外部回路を有する半導体装置の機能拡張が可能となる。

30

【0058】

なお、本実施の形態の内容または該内容の一部は、他の実施の形態の内容若しくは該内容の一部と自由に組み合わせることが可能である。

【0059】

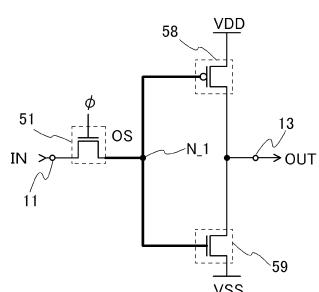

(実施の形態2)

本実施の形態では、実施の形態1に示した論理回路の一例について説明する。具体的には、NOT回路(インバータ回路)について図3を用いて説明する。なお、回路図においては、酸化物半導体(Oxide Semiconductor)を用いたトランジスタであることを示すために、点線を用いた回路記号およびOSの符号を併せて付す場合がある。そして、本実施の形態で説明する論理回路は、実施の形態1で説明した論理回路の一例であるため、実施の形態1での説明に用いた符号を適宜使用する。

40

【0060】

論理回路の構成例および動作例

図3(A)に示す論理回路50はNOT回路に新たにnチャネル型トランジスタを電気的に接続した論理回路である。本実施の形態では、該NOT回路を微細化に好適なCMOS回路による回路構成とするが、該NOT回路を他の抵抗素子やダイオードなどを用いる回路構成としてもよい。

【0061】

論理回路50は、nチャネル型トランジスタ51と、pチャネル型トランジスタ58お

50

およびnチャネル型トランジスタ59と、を有する。特に、nチャネル型トランジスタ51は極めてオフ電流の低いトランジスタである。

【0062】

論理回路50は、nチャネル型トランジスタ51の第1端子と入力電位信号(IN)を供給する入力端子11とが電気的に接続されており、nチャネル型トランジスタ51の第2端子とpチャネル型トランジスタ58のゲートおよびnチャネル型トランジスタ59のゲートとが電気的に接続されており、高電位側電源電位(VDD)を供給する高電位側電源電位線とpチャネル型トランジスタ58の第1端子とが電気的に接続されており、低電位側電源電位(VSS)を供給する低電位側電源電位線とnチャネル型トランジスタ59の第1端子とが電気的に接続されており、pチャネル型トランジスタ58の第2端子およびnチャネル型トランジスタ59の第2端子と出力電位信号(OUT)が出力される出力端子13とが電気的に接続されている。

【0063】

また、本発明の一態様である論理回路において、低電位側電源電位(VSS)は高電位側電源電位(VDD)より低ければどのような電位であってもよい。つまり、高電位側電源電位線と電気的に接続されるトランジスタの第1端子および低電位側電源電位線と電気的に接続されるトランジスタの第1端子の間に電位差を有すれば、低電位側電源電位はどのような電位であってもよい。例えば、該低電位側電源電位としては、接地電位または0Vとすることができる。なお、このことは、後述する本発明の一態様である他の論理回路においても適用される。

【0064】

論理回路50は、nチャネル型トランジスタ51のゲートの電位が高電位の場合(nチャネル型トランジスタ51のVgsがnチャネル型トランジスタ51のしきい値電圧より高い場合)において、従来のNOT回路と同様の演算処理を行う。例えば、高電位の入力電位信号が入力端子11に入力されると、出力端子13からは低電位側電源電位(VSS)である低電位が出力される。また、低電位の入力電位信号が入力端子11に入力されると、出力端子13からは高電位側電源電位(VDD)である高電位が出力される。

【0065】

次に、論理回路50の動作中に電源をオフした場合の回路動作について説明する。従来のNOT回路では、回路動作中に電源をオフした場合、高電位側電源電位(VDD)と低電位側電源電位(VSS)に電位差が無くなるため、演算処理中のデータは揮発する。

【0066】

一方、論理回路50では、nチャネル型トランジスタ51が極めてオフ電流の低いトランジスタであることから、nチャネル型トランジスタ51のゲートの電位を低電位(nチャネル型トランジスタ51のVgsをnチャネル型トランジスタ51のしきい値電圧より低い状態)とした後であれば、電源をオフしてもノードN\_1をフロー・ティングとすることができるため、該ノードN\_1の電位を保持することができる。なお、ノードN\_1とは、図3(A)において、「N\_1」で指示する部分を含む太線部である。また、保持ノード(ノードN\_1)に容量素子を設げずとも十分な期間、電位を保持できるが、さらなる保持期間を望む場合は、該保持ノードに一方の電極が電気的に接続され、且つ他方の電極が低電位側電源電位線に電気的に接続された容量素子を設けてよい。

【0067】

そして、再度電源をオンした後、nチャネル型トランジスタ51のゲートの電位を高電位(nチャネル型トランジスタ51のVgsをnチャネル型トランジスタ51のしきい値電圧より高い状態)にすることで、ノードN\_1に保持された電位をもとに演算処理を再開することができる。したがって、再度電源をオンした際に入力電位信号を供給する必要が無く、素早く演算処理を再開することができる。また、論理回路50の消費電力を低減することができる。

【0068】

論理回路50は、nチャネル型トランジスタ51の第2端子と電気的に接続されたノード

10

20

30

40

50

ドの電位が保持される形態であるが、論理回路 50 の変形例として、出力端子 13 と電気的に接続されたノードの電位が保持される形態としてもよい。そこで、図 3 (B) に論理回路 55 を示す。なお、論理回路 55 は、図 3 (A) の論理回路 50 に付した符号を適宜用いて説明する。

【0069】

論理回路 55 は、n チャネル型トランジスタ 51 と、n チャネル型トランジスタ 54 と、p チャネル型トランジスタ 58 および n チャネル型トランジスタ 59 と、を有する。特に、n チャネル型トランジスタ 51 および n チャネル型トランジスタ 54 は極めてオフ電流の低いトランジスタである。

【0070】

論理回路 55 は、入力電位信号 (IN) を供給する入力端子 11 と p チャネル型トランジスタ 58 のゲートおよび n チャネル型トランジスタ 59 のゲートとが電気的に接続されており、高電位側電源電位 (VDD) を供給する高電位側電源電位線と p チャネル型トランジスタ 58 の第 1 端子とが電気的に接続されており、p チャネル型トランジスタ 58 の第 2 端子と n チャネル型トランジスタ 51 の第 1 端子と電気的に接続されており、低電位側電源電位 (VSS) を供給する低電位側電源電位線と n チャネル型トランジスタ 59 の第 1 端子とが電気的に接続されており、n チャネル型トランジスタ 59 の第 2 端子と n チャネル型トランジスタ 54 の第 1 端子とが電気的に接続されており、n チャネル型トランジスタ 51 および n チャネル型トランジスタ 54 の第 2 端子と出力電位信号 (OUT) が 20 出力される出力端子 13 とが電気的に接続されている。なお、n チャネル型トランジスタ 51 のゲートおよび n チャネル型トランジスタ 54 のゲートは同電位である。

【0071】

論理回路 55 は、論理回路 50 と同様に n チャネル型トランジスタ 51 および n チャネル型トランジスタ 54 のゲートの電位 が高電位の場合において、従来の NOT 回路と同様の演算処理を行う。

【0072】

次に、論理回路 55 の動作中に電源をオフした場合の回路動作について説明する。従来の NOT 回路では、回路動作中に電源をオフした場合、演算処理中のデータは揮発する。

【0073】

一方、論理回路 55 では、n チャネル型トランジスタ 51 および n チャネル型トランジスタ 54 は極めてオフ電流の低いトランジスタであることから、n チャネル型トランジスタ 51 および n チャネル型トランジスタ 54 のゲートの電位 を低電位 (n チャネル型トランジスタ 51 および n チャネル型トランジスタ 54 の Vgs を n チャネル型トランジスタ 51 および n チャネル型トランジスタ 54 のしきい値電圧より低い状態) とした後であれば、電源をオフしても、ノード N\_2 をフローティングとすることができますため、該ノード N\_2 の電位を保持することができる。なお、ノード N\_2 とは、図 3 (B) において、「N\_2」で指示する部分を含む太線部である。また、保持ノード (ノード N\_2) に容量素子を設けずとも十分な期間、電位を保持できるが、さらなる保持期間を望む場合は、該保持ノードに一方の電極が電気的に接続され、且つ他方の電極が低電位側電源電位線に電気的に接続された容量素子を設けてもよい。

【0074】

そして、再度電源をオンした後、n チャネル型トランジスタ 51 および n チャネル型トランジスタ 54 のゲートの電位 を高電位 (n チャネル型トランジスタ 51 および n チャネル型トランジスタ 54 の Vgs を n チャネル型トランジスタ 51 および n チャネル型トランジスタ 54 のしきい値電圧より高い状態) にすることで、再度電源をオンした際に入力電位信号を供給する必要が無く、素早く演算処理を再開することができる。また、論理回路 55 の消費電力を低減することができる。

【0075】

論理回路 50 および論理回路 55 において、n チャネル型トランジスタ 51 および n チャネル型トランジスタ 54 は、上記した極めてオフ電流の低いトランジスタが適用できる

10

20

30

40

50

。例えば、実施の形態1で説明したトランジスタ15のように、室温(25℃)における単位チャネル幅(1μm)あたりの値が10aA/μm( $1 \times 10^{-17}$ A/μm)以下、さらには、1aA/μm( $1 \times 10^{-18}$ A/μm)以下、さらには1zA/μm( $1 \times 10^{-21}$ A/μm)以下、さらには1yA/μm( $1 \times 10^{-24}$ A/μm)以下となるトランジスタである。

#### 【0076】

極めてオフ電流の低いトランジスタは、酸化物半導体などのワイドギャップ半導体をチャネル形成領域に適用することで実現できる。さらに、キャリアの供与体となる水素を極めて低濃度に低下させた酸化物半導体をチャネル形成領域に適用することが好ましい。したがって、チャネル形成領域における酸化物半導体の水素濃度が $5 \times 10^{-9}$ /cm<sup>3</sup>以下、さらに $5 \times 10^{-8}$ /cm<sup>3</sup>以下であり、且つ化学量論的組成比に対して酸素が過剰に含まれていることが好ましい。なお、チャネル形成領域を構成する酸化物半導体中の水素濃度測定は、二次イオン質量分析法(SIMS: Secondary Ion Mass Spectrometry)で行ったものである。

10

#### 【0077】

また、酸化物半導体としては、少なくともインジウム(In)あるいは亜鉛(Zn)とを含む金属酸化物で形成されていることが好ましい。特にInとZnを含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム(Ga)を有することが好ましい。また、スタビライザーとしてスズ(Sn)を有することが好ましい。また、スタビライザーとしてハフニウム(Hf)を有することが好ましい。また、スタビライザーとしてアルミニウム(Al)を有することが好ましい。

20

#### 【0078】

また、他のスタビライザーとして、ランタノイドである、ランタン(La)、セリウム(Ce)、プラセオジム(Pr)、ネオジム(Nd)、サマリウム(Sm)、ユウロピウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、ジスプロシウム(Dy)、ホルミウム(Ho)、エルビウム(Er)、ツリウム(Tm)、イッテルビウム(Yb)、ルテチウム(Lu)のいずれか一種あるいは複数種を有してもよい。

#### 【0079】

なお、酸化物半導体のキャリア濃度は $1.0 \times 10^{14}$ /cm<sup>3</sup>未満まで小さくすることが好ましい。キャリア濃度を小さくすることで、トランジスタのオフ電流を低くすることができる。

30

#### 【0080】

論理回路50および論理回路55において、pチャネル型トランジスタ58およびnチャネル型トランジスタ59には、特に制限はなく、半導体材料を含む基板を用いて形成されるトランジスタであればよい。

#### 【0081】

なお、nチャネル型トランジスタ59についても、nチャネル型トランジスタ51およびnチャネル型トランジスタ54のように、上記水素濃度を有し、キャリアの供与体となる水素を極めて低濃度に低下させた酸化物半導体をチャネル形成領域に適用したトランジスタとすることで、論理回路50および論理回路55の消費電力をさらに低減させることができる。

40

#### 【0082】

本発明の一態様であるNOT回路において、論理回路50のように、素子数をできる限り少なくなるように極めてオフ電流が低いトランジスタを配置する回路構成は、論理回路55の回路構成より、素子数が少ないためにトランジスタの占有面積が小さく、微細化の観点から好ましい。また、本発明の一態様であるNOT回路において、論理回路55のように出力端子と電気的に接続されたノードの電位が保持される回路構成、別言すると演算処理後の電位が保持される回路構成は、論理回路50より、さらに高速に演算処理を再開させることができ、回路動作の高速化の観点から好ましい。

50

## 【0083】

さらに、本発明の一態様であるN O T回路（論理回路50および論理回路55）において、極めてオフ電流の低いトランジスタ以外の構成（従来のN O T回路に相当する構成）は、C M O S回路に限定されない。例えば、該構成の一部であるpチャネル型トランジスタをn型且つエンハンスマント型トランジスタとしてもよい。該n型且つエンハンスマント型トランジスタは、トランジスタの第1端子とゲートとが接続されたnチャネル型トランジスタであり、期間によらず導通状態（オン状態）を維持する。別言すれば、該n型且つエンハンスマント型トランジスタは抵抗素子として機能する。したがって、該構成の一部であるpチャネル型トランジスタに、n型且つエンハンスマント型トランジスタを適用することで、論理回路50および論理回路55を構成するトランジスタの極性を同じにすることができる。これにより、作製プロセスを低減することができ、論理回路50および論理回路55の歩留まりを向上させ、製造コストを低減させることができる。なお、該n型且つエンハンスマント型トランジスタにおいても、上記水素濃度を有する酸化物半導体でチャネル形成領域を構成するトランジスタとしてもよい。このように、nチャネル型トランジスタのみで構成される論理回路であっても、論理回路50および論理回路55を低消費電力化することができる。10

## 【0084】

以上より、論理回路50および論理回路55において、消費電力を低減することで、論理回路50および論理回路55の一方または双方を有する半導体装置の消費電力を低減することができる。さらに、論理回路50および論理回路55の消費電力を低減することで、論理回路50および論理回路55を動作させる外部回路の負荷が低減できる。これにより、論理回路50および論理回路55の一方または双方と、該外部回路とを有する半導体装置の機能拡張が可能となる。20

## 【0085】

なお、本実施の形態の内容または該内容の一部は、他の実施の形態の内容若しくは該内容の一部と自由に組み合わせることが可能である。

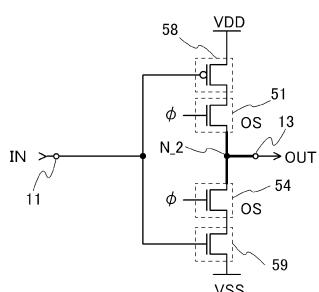

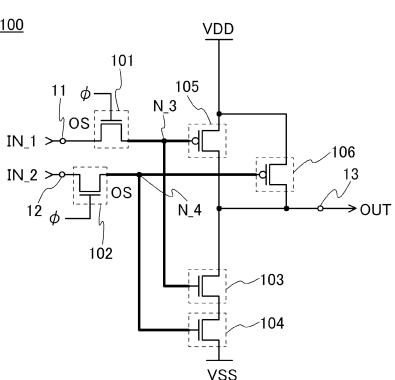

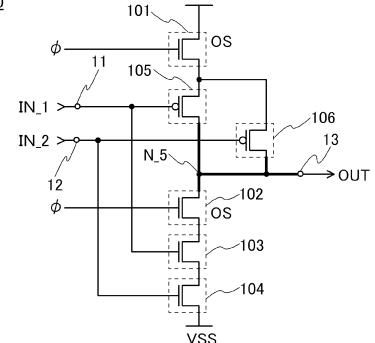

## 【0086】

## (実施の形態3)

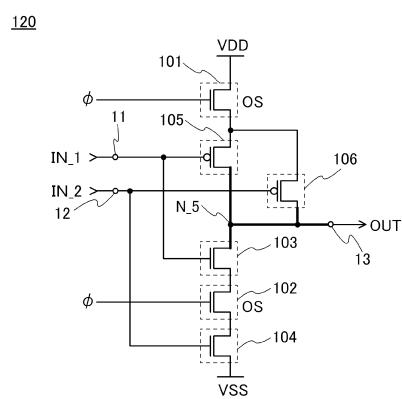

本実施の形態では、実施の形態1に示した論理回路の一例について説明する。具体的には、N A N D回路について図4を用いて説明する。なお、回路図においては、酸化物半導体を用いたトランジスタであることを示すために、点線を用いた回路記号およびO Sの符号を併せて付す場合がある。そして、本実施の形態で説明する論理回路は、実施の形態1での説明に用いた符号を適宜使用する。30

## 【0087】

## 論理回路の構成例および動作例

図4(A)に示す論理回路100はN A N D回路に新たにnチャネル型トランジスタを電気的に接続した論理回路である。本実施の形態では、該N A N D回路を微細化に好適なC M O S回路による回路構成とするが、該N A N D回路を他の抵抗素子やダイオードなどを用いる回路構成としてもよい。なお、図4において、N A N D回路には入力端子が2つあるため、一方を第1の入力端子11、もう一方を第2の入力端子12と符号を付する。40

## 【0088】

論理回路100は、nチャネル型トランジスタ101、nチャネル型トランジスタ102、nチャネル型トランジスタ103、およびnチャネル型トランジスタ104、ならびにpチャネル型トランジスタ105およびpチャネル型トランジスタ106と、を有する。特に、nチャネル型トランジスタ101およびnチャネル型トランジスタ102は極めてオフ電流の低いトランジスタである。

## 【0089】

論理回路100は、nチャネル型トランジスタ101の第1端子と入力電位信号(I N \_1)を供給する第1の入力端子11とが電気的に接続されており、nチャネル型トランジスタ101の第2端子とpチャネル型トランジスタ105のゲートおよびnチャネル型

トランジスタ 103 のゲートとが電気的に接続されており、n チャネル型トランジスタ 102 の第 1 端子と入力電位信号 (IN\_2) を供給する第 2 の入力端子 12 とが電気的に接続されており、n チャネル型トランジスタ 102 の第 2 端子と p チャネル型トランジスタ 106 のゲートおよび n チャネル型トランジスタ 104 のゲートとが電気的に接続されており、高電位側電源電位 (VDD) を供給する高電位側電源電位線と p チャネル型トランジスタ 105 の第 1 端子および p チャネル型トランジスタ 106 の第 1 端子とが電気的に接続されており、低電位側電源電位 (VSS) を供給する低電位側電源電位線と n チャネル型トランジスタ 104 の第 1 端子とが電気的に接続されており、n チャネル型トランジスタ 104 の第 2 端子と n チャネル型トランジスタ 103 の第 1 端子とが電気的に接続されており、p チャネル型トランジスタ 105 の第 2 端子および p チャネル型トランジスタ 106 の第 2 端子ならびに n チャネル型トランジスタ 103 の第 2 端子と出力電位信号 (OUT) が出力される出力端子 13 とが電気的に接続されている。なお、n チャネル型トランジスタ 101 のゲートおよび n チャネル型トランジスタ 102 のゲートは同電位である。

#### 【0090】

論理回路 100 は、n チャネル型トランジスタ 101 および n チャネル型トランジスタ 102 のゲートの電位  $V_{GS}$  が高電位の場合 (n チャネル型トランジスタ 101 および n チャネル型トランジスタ 102 の  $V_{GS}$  が n チャネル型トランジスタ 101 および n チャネル型トランジスタ 102 のしきい値電圧より高い場合) において、従来の NAND 回路と同様の演算処理を行う。例えば、高電位の入力電位信号が第 1 の入力端子 11 および第 2 の入力端子 12 に入力されると、出力端子 13 からは低電位側電源電位 (VSS) である低電位が出力される。また、低電位の入力電位信号が第 1 の入力端子 11 および第 2 の入力端子 12 のいずれか一方に入力されると、出力端子 13 からは高電位側電源電位 (VDD) である高電位が出力される。

#### 【0091】

次に、論理回路 100 の動作中に電源をオフした場合の回路動作について説明する。従来の NAND 回路では、回路動作中に電源をオフした場合、高電位側電源電位 (VDD) と低電位側電源電位 (VSS) に電位差が無くなるため、演算処理中のデータは揮発する。

#### 【0092】

一方、論理回路 100 では、n チャネル型トランジスタ 101 および n チャネル型トランジスタ 102 は極めてオフ電流の低いトランジスタであることから、n チャネル型トランジスタ 101 および n チャネル型トランジスタ 102 のゲートの電位  $V_{GS}$  を低電位 (n チャネル型トランジスタ 101 および n チャネル型トランジスタ 102 の  $V_{GS}$  を n チャネル型トランジスタ 101 および n チャネル型トランジスタ 102 のしきい値電圧より低い状態) とした後、電源をオフした場合、n チャネル型トランジスタ 101 および n チャネル型トランジスタ 102 のゲートの電位  $V_{GS}$  を低電位としている (n チャネル型トランジスタ 101 および n チャネル型トランジスタ 102 の  $V_{GS}$  を n チャネル型トランジスタ 101 および n チャネル型トランジスタ 102 のしきい値電圧より低くする) ことで、ノード N\_3 およびノード N\_4 をフローティングとすることができますため、該ノード N\_3 および該ノード N\_4 の電位を保持することができます。なお、ノード N\_3 とは、図 4 (A) において、「N\_3」で指し示す部分を含む太線部であり、ノード N\_4 とは、図 4 (A) において、「N\_4」で指し示す部分を含む太線部である。また、保持ノード (ノード N\_3 およびノード N\_4) に容量素子を設けずとも十分な期間、電位を保持できるが、さらなる保持期間を望む場合は、該保持ノードに一方の電極が電気的に接続され、且つ他方の電極が低電位側電源電位線に電気的に接続された容量素子を設けてもよい。

#### 【0093】

そして、再度電源をオンした後、n チャネル型トランジスタ 101 および n チャネル型トランジスタ 102 のゲートの電位  $V_{GS}$  を高電位にすることで、ノード N\_3 およびノード N\_4 に保持された電位をもとに演算処理を再開することができます。したがって、再度電

10

20

30

40

50

源をオンした際に入力電位信号を供給する必要が無く、素早く演算処理を再開することができる。また、論理回路 100 の消費電力を低減することができる。

【0094】

論理回路 100 は、n チャネル型トランジスタ 101 および n チャネル型トランジスタ 102 の第 2 端子と電気的に接続されたノードの電位が保持される形態であるが、論理回路 100 の変形例として、出力端子 13 と電気的に接続されたノードの電位が保持される形態としてもよい。そこで、図 4 (B) に該形態に対応する論理回路 110 を示す。なお、論理回路 110 は、図 4 (A) の論理回路 100 に付した符号を適宜用いて説明する。

【0095】

論理回路 110 は、n チャネル型トランジスタ 101、n チャネル型トランジスタ 102、n チャネル型トランジスタ 103、および n チャネル型トランジスタ 104、ならびに p チャネル型トランジスタ 105 および p チャネル型トランジスタ 106 と、を有する。論理回路 110 は論理回路 100 と比較して回路を構成するトランジスタの接続関係が異なる。なお、n チャネル型トランジスタ 101 および n チャネル型トランジスタ 102 は極めてオフ電流の低いトランジスタである。

【0096】

論理回路 110 は、第 1 の入力端子 11 と n チャネル型トランジスタ 103 のゲートおよび p チャネル型トランジスタ 105 のゲートとが電気的に接続されており、第 2 の入力端子 12 と n チャネル型トランジスタ 104 のゲートおよび p チャネル型トランジスタ 106 のゲートとが電気的に接続されており、高電位側電源電位 (VDD) を供給する高電位側電源電位線と n チャネル型トランジスタ 101 の第 1 端子とが電気的に接続されており、n チャネル型トランジスタ 101 の第 2 端子と p チャネル型トランジスタ 105 の第 1 端子および p チャネル型トランジスタ 106 の第 1 端子とが電気的に接続されており、低電位側電源電位 (VSS) を供給する低電位側電源電位線と n チャネル型トランジスタ 104 の第 1 端子とが電気的に接続されており、n チャネル型トランジスタ 104 の第 2 端子と n チャネル型トランジスタ 103 の第 1 端子とが電気的に接続されており、n チャネル型トランジスタ 103 の第 2 端子と n チャネル型トランジスタ 102 の第 1 端子とが電気的に接続されており、p チャネル型トランジスタ 105 の第 2 端子および p チャネル型トランジスタ 106 の第 2 端子ならびに n チャネル型トランジスタ 102 の第 2 端子と出力端子 13 とが電気的に接続されている。なお、n チャネル型トランジスタ 101 のゲートおよび n チャネル型トランジスタ 102 のゲートは同電位である。

【0097】

論理回路 110 は、論理回路 100 と同様に n チャネル型トランジスタ 101 および n チャネル型トランジスタ 102 のゲートの電位 が高電位の場合において、従来の NAND 回路と同様の演算処理を行う。

【0098】

次に、論理回路 110 の動作中に電源をオフした場合の回路動作について説明する。従来の NAND 回路では、回路動作中に電源をオフした場合、演算処理中のデータは揮発する。

【0099】

一方、論理回路 110 では、n チャネル型トランジスタ 101 および n チャネル型トランジスタ 102 は極めてオフ電流の低いトランジスタであることから、n チャネル型トランジスタ 101 および n チャネル型トランジスタ 102 のゲートの電位 を低電位とした後、電源をオフした場合、n チャネル型トランジスタ 101 および n チャネル型トランジスタ 102 のゲートの電位 を低電位としていることで、少なくともノード N\_5 をフローティングとすることができますため、該ノード N\_5 の電位を保持することができる。なお、ノード N\_5 とは、図 4 (B) において、「N\_5」で指示する部分を含む太線部である。なお、保持ノード (ノード N\_5) に容量素子を設けずとも十分な期間、電位を保持できるが、さらなる保持期間を望む場合は、該保持ノードに一方の電極が電気的に接続され、且つ他方の電極が低電位側電源電位線に電気的に接続された容量素子を設けてもよ

10

20

30

40

50

い。

【0100】

そして、再度電源をオンした後、nチャネル型トランジスタ101およびnチャネル型トランジスタ102のゲートの電位を高電位にすることで、再度電源をオンした際に入力電位信号を供給する必要が無く、素早く演算処理を再開することができる。また、論理回路110の消費電力を低減することができる。

【0101】

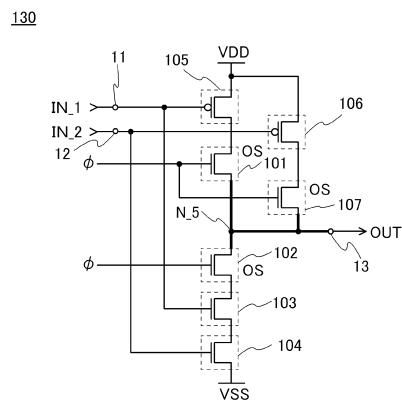

また、本実施の形態において、nチャネル型トランジスタ101およびnチャネル型トランジスタ102のように極めてオフ電流の低いトランジスタを配置する箇所は、電源をオフした際に、入力された保持すべき電位を低下させる電流経路（リーク経路）に配置すれば、論理回路100および論理回路110に限定されない。そこで、図5に、論理回路100および論理回路110とは、極めてオフ電流の低いトランジスタを配置する箇所が異なる論理回路の一例を示す。図5（A）は、該一例である論理回路120を示す回路図であり、図5（B）は、該一例である論理回路130を示す回路図である。なお、論理回路120および論理回路130は、図4（A）の論理回路100に付した符号を適宜用いて説明する。

【0102】

論理回路120は、nチャネル型トランジスタ101、nチャネル型トランジスタ102、nチャネル型トランジスタ103、およびnチャネル型トランジスタ104、ならびにpチャネル型トランジスタ105およびpチャネル型トランジスタ106と、を有する。なお、nチャネル型トランジスタ101およびnチャネル型トランジスタ102は極めてオフ電流の低いトランジスタである。

【0103】

論理回路120は、第1の入力端子11とnチャネル型トランジスタ103のゲートおよびpチャネル型トランジスタ105のゲートとが電気的に接続されており、第2の入力端子12とnチャネル型トランジスタ104のゲートおよびpチャネル型トランジスタ106のゲートとが電気的に接続されており、高電位側電源電位（VDD）を供給する高電位側電源電位線とnチャネル型トランジスタ101の第1端子と電気的に接続されており、nチャネル型トランジスタ101の第2端子とpチャネル型トランジスタ105の第1端子およびpチャネル型トランジスタ106の第1端子とが電気的に接続されており、低電位側電源電位（VSS）を供給する低電位側電源電位線とnチャネル型トランジスタ104の第1端子とが電気的に接続されており、nチャネル型トランジスタ104の第2端子とnチャネル型トランジスタ102の第1端子とが電気的に接続されており、nチャネル型トランジスタ102の第2端子とnチャネル型トランジスタ103の第1端子とが電気的に接続されており、pチャネル型トランジスタ105の第2端子およびpチャネル型トランジスタ106の第2端子ならびにnチャネル型トランジスタ103の第2端子と出力端子13とが電気的に接続されている。なお、nチャネル型トランジスタ101のゲートおよびnチャネル型トランジスタ102のゲートは同電位である。

【0104】

論理回路120は、論理回路100と同様にnチャネル型トランジスタ101およびnチャネル型トランジスタ102のゲートの電位が高電位の場合において、従来のNAND回路と同様の演算処理を行う。

【0105】

次に、論理回路120の動作中に電源をオフした場合の回路動作について説明する。従来のNAND回路では、回路動作中に電源をオフした場合、演算処理中のデータは揮発する。

【0106】

一方、論理回路120では、nチャネル型トランジスタ101およびnチャネル型トランジスタ102は極めてオフ電流の低いトランジスタであることから、nチャネル型トランジスタ101およびnチャネル型トランジスタ102のゲートの電位を低電位とした

10

20

30

40

50

後、電源をオフした場合、nチャネル型トランジスタ101およびnチャネル型トランジスタ102のゲートの電位を低電位としていることで、少なくともノードN\_5をフローティングとすることができるため、該ノードN\_5の電位を保持することができる。なお、保持ノード(ノードN\_5)に容量素子を設けずとも十分な期間、電位を保持できるが、さらなる保持期間を望む場合は、該保持ノードに一方の電極が電気的に接続され、且つ他方の電極が低電位側電源電位線に電気的に接続された容量素子を設けてもよい。

#### 【0107】

そして、再度電源をオンした後、nチャネル型トランジスタ101およびnチャネル型トランジスタ102のゲートの電位を高電位にすることで、再度電源をオンした際に入力電位信号を供給する必要が無く、素早く演算処理を再開することができる。また、論理回路120の消費電力を低減することができる。

10

#### 【0108】

論理回路130は、nチャネル型トランジスタ101、nチャネル型トランジスタ102、nチャネル型トランジスタ103、nチャネル型トランジスタ104、およびnチャネル型トランジスタ107、ならびにpチャネル型トランジスタ105およびpチャネル型トランジスタ106を有する。特に、nチャネル型トランジスタ101、nチャネル型トランジスタ102およびnチャネル型トランジスタ107は極めてオフ電流の低いトランジスタである。

#### 【0109】

論理回路130は、第1の入力端子11とnチャネル型トランジスタ103のゲートおよびpチャネル型トランジスタ105のゲートとが電気的に接続されており、第2の入力端子12とnチャネル型トランジスタ104のゲートおよびpチャネル型トランジスタ106のゲートとが電気的に接続されており、高電位側電源電位(VDD)を供給する高電位側電源電位線とpチャネル型トランジスタ105の第1端子およびpチャネル型トランジスタ106の第1端子とが電気的に接続されており、pチャネル型トランジスタ105の第2端子とnチャネル型トランジスタ101の第1端子とが電気的に接続されており、pチャネル型トランジスタ106の第2端子とnチャネル型トランジスタ107の第1端子とが電気的に接続されており、低電位側電源電位(VSS)を供給する低電位側電源電位線とnチャネル型トランジスタ104の第1端子とが電気的に接続されており、nチャネル型トランジスタ104の第2端子とnチャネル型トランジスタ103の第1端子とが電気的に接続されており、nチャネル型トランジスタ102の第1端子とが電気的に接続されており、nチャネル型トランジスタ101の第2端子およびnチャネル型トランジスタ102の第2端子ならびにnチャネル型トランジスタ107の第2端子と出力端子13とが電気的に接続されている。なお、nチャネル型トランジスタ101のゲート、nチャネル型トランジスタ102のゲートおよびnチャネル型トランジスタ107のゲートは同電位である。

20

#### 【0110】

論理回路130は、nチャネル型トランジスタ101、nチャネル型トランジスタ102およびnチャネル型トランジスタ107のゲートの電位が高電位の場合において、従来のNAND回路と同様の演算処理を行う。

30

#### 【0111】

次に、論理回路130の動作中に電源をオフした場合の回路動作について説明する。従来のNAND回路では、回路動作中に電源をオフした場合、演算処理中のデータは揮発する。

40

#### 【0112】

一方、論理回路130では、nチャネル型トランジスタ101、nチャネル型トランジスタ102およびnチャネル型トランジスタ107は極めてオフ電流の低いトランジスタであることから、nチャネル型トランジスタ101、nチャネル型トランジスタ102およびnチャネル型トランジスタ107のゲートの電位を低電位とした後、電源をオフした場合、ノードN\_5をフローティングとすることができるため、該ノードN\_5の電位

50

を保持することができる。なお、保持ノード（ノードN\_5）に容量素子を設けずとも十分な期間、電位を保持できるが、さらなる保持期間を望む場合は、該保持ノードに一方の電極が電気的に接続され、且つ他方の電極が低電位側電源電位線に電気的に接続された容量素子を設けてもよい。

【0113】

そして、再度電源をオンした後、nチャネル型トランジスタ101、nチャネル型トランジスタ102およびnチャネル型トランジスタ107のゲートの電位<sub>g</sub>を高電位にすることで、再度電源をオンした際に入力電位信号を供給する必要が無く、素早く演算処理を再開することができる。また、論理回路130の消費電力を低減することができる。

【0114】

論理回路100乃至論理回路130において、nチャネル型トランジスタ101、nチャネル型トランジスタ102およびnチャネル型トランジスタ107は、上記したように極めてオフ電流の低いトランジスタが適用される。該トランジスタは、例えば、実施の形態1で説明したトランジスタ15乃至トランジスタ19、実施の形態2で説明したnチャネル型トランジスタ51およびnチャネル型トランジスタ54におけるオフ電流特性を有する。そして、nチャネル型トランジスタ101、nチャネル型トランジスタ102およびnチャネル型トランジスタ107は、nチャネル型トランジスタ51およびnチャネル型トランジスタ54と同様に、酸化物半導体、特に上記水素濃度を有し、キャリアの供与体となる水素を極めて低濃度に低下させた酸化物半導体をチャネル形成領域に適用したトランジスタとすることができます。なお、酸化物半導体中のキャリア濃度についてもnチャネル型トランジスタ51およびnチャネル型トランジスタ54と同様であることが好ましい。

【0115】

論理回路100乃至論理回路130において、nチャネル型トランジスタ103およびnチャネル型トランジスタ104ならびにpチャネル型トランジスタ105およびpチャネル型トランジスタ106には、特に制限はなく、半導体材料を含む基板を用いて形成されるトランジスタであればよい。

【0116】

なお、nチャネル型トランジスタ103およびnチャネル型トランジスタ104についても、nチャネル型トランジスタ101、nチャネル型トランジスタ102およびnチャネル型トランジスタ107のように、上記水素濃度を有し、キャリアの供与体となる水素を極めて低濃度に低下させた酸化物半導体をチャネル形成領域に適用したトランジスタとすることで、論理回路100乃至論理回路130の消費電力をさらに低減させることができる。

【0117】

また、本発明の一態様であるNAND回路において、論理回路100乃至論理回路120のようにトランジスタの素子数をできる限り少なくなるように極めてオフ電流が低いトランジスタを配置する回路構成は、論理回路130の回路構成より、トランジスタの素子数が少ないためにトランジスタの占有面積が小さく、微細化の観点から好ましい。また、本発明の一態様であるNAND回路において、論理回路110乃至論理回路130のように出力端子と電気的に接続されたノードの電位が保持される回路構成、別言すると演算処理後の電位が保持される回路構成は、論理回路100よりさらに高速に演算処理を再開させることができ、回路動作の高速化の観点から好ましい。

【0118】

さらに、本発明の一態様であるNAND回路（論理回路100乃至論理回路130）において、極めてオフ電流の低いトランジスタ以外の構成（従来のNAND回路に相当する構成）は、CMOS回路に限定されない。例えば、論理回路50および論理回路55のように、該構成の一部であるpチャネル型トランジスタをn型且つエンハンスマント型トランジスタとしてもよい。該構成の一部であるpチャネル型トランジスタに、n型且つエンハンスマント型トランジスタを適用することで、論理回路100乃至論理回路130を構

10

20

30

40

50

成するトランジスタの極性を同じにすることができる。これにより、作製プロセスを低減することができ、論理回路 100 乃至論理回路 130 の歩留まりを向上させ、製造コストを低減させることができる。なお、該 n 型且つエンハンスメント型トランジスタにおいても、上記水素濃度を有する酸化物半導体でチャネル形成領域を構成するトランジスタとしてもよい。このように、n チャネル型トランジスタのみで構成される論理回路であっても、論理回路 100 乃至論理回路 130 を低消費電力化することができる。

#### 【0119】

以上より、論理回路 100 乃至論理回路 130 において、消費電力を低減することで、論理回路 100 乃至論理回路 130 のうち 1 以上の論理回路を有する半導体装置の消費電力を低減することができる。さらに、論理回路 100 乃至論理回路 130 の消費電力を低減することで、論理回路 100 乃至論理回路 130 を動作させる外部回路の負荷が低減できる。これにより、論理回路 100 乃至論理回路 130 のうち 1 以上の論理回路および該外部回路を有する半導体装置の機能拡張が可能となる。

10

#### 【0120】

なお、本実施の形態の内容または該内容の一部は、他の実施の形態の内容若しくは該内容の一部と自由に組み合わせることが可能である。

#### 【0121】

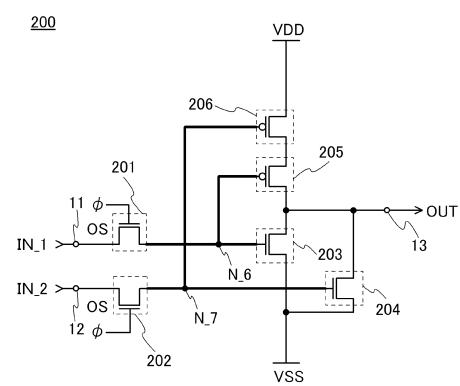

##### (実施の形態 4)

本実施の形態では、実施の形態 1 に示した論理回路の一例について説明する。具体的には、NOR 回路について図 6 を用いて説明する。なお、回路図においては、酸化物半導体を用いたトランジスタであることを示すために、点線を用いた回路記号および OS の符号を併せて付す場合がある。そして、本実施の形態で説明する論理回路は、実施の形態 1 での説明に用いた符号を適宜使用する。

20

#### 【0122】

##### 論理回路の構成例および動作例

図 6 (A) に示す論理回路 200 は NOR 回路に新たに n チャネル型トランジスタを電気的に接続した論理回路である。本実施の形態では、該 NOR 回路を微細化に好適な CMOS 回路による回路構成とするが、該 NOR 回路を他の抵抗素子やダイオードなどを用いる回路構成としてもよい。なお、図 6 において、NOR 回路には入力端子が 2 つあるため、一方を第 1 の入力端子 11、もう一方を第 2 の入力端子 12 と符号を付する。

30

#### 【0123】

論理回路 200 は、n チャネル型トランジスタ 201、n チャネル型トランジスタ 202、n チャネル型トランジスタ 203、および n チャネル型トランジスタ 204、ならびに p チャネル型トランジスタ 205 および p チャネル型トランジスタ 206 を有する。特に、n チャネル型トランジスタ 201 および n チャネル型トランジスタ 202 は極めてオフ電流の低いトランジスタである。

#### 【0124】

論理回路 200 は、n チャネル型トランジスタ 201 の第 1 端子と第 1 の入力端子 11 とが電気的に接続されており、n チャネル型トランジスタ 201 の第 2 端子と n チャネル型トランジスタ 203 のゲートおよび p チャネル型トランジスタ 205 のゲートとが電気的に接続されており、n チャネル型トランジスタ 202 の第 1 端子と第 2 の入力端子 12 とが電気的に接続されており、n チャネル型トランジスタ 202 の第 2 端子と n チャネル型トランジスタ 204 のゲートおよび p チャネル型トランジスタ 206 のゲートとが電気的に接続されており、高電位側電源電位 (VDD) を供給する高電位側電源電位線と p チャネル型トランジスタ 206 の第 1 端子とが電気的に接続されており、p チャネル型トランジスタ 206 の第 2 端子と p チャネル型トランジスタ 205 の第 1 端子とが電気的に接続されており、低電位側電源電位 (VSS) を供給する低電位側電源電位線と n チャネル型トランジスタ 203 の第 1 端子および n チャネル型トランジスタ 204 の第 1 端子とが電気的に接続されており、n チャネル型トランジスタ 203 の第 2 端子および n チャネル型トランジスタ 204 の第 2 端子ならびに p チャネル型トランジスタ 205 の第 2 端子と

40

50

出力端子 13 とが電気的に接続されている。

【0125】

論理回路 200 は、n チャネル型トランジスタ 201 および n チャネル型トランジスタ 202 のゲートの電位 を高電位の場合 (n チャネル型トランジスタ 201 および n チャネル型トランジスタ 202 の  $V_{gs}$  が n チャネル型トランジスタ 201 および n チャネル型トランジスタ 202 のしきい値電圧より高い場合) において、従来の NOR 回路と同様の演算処理を行う。例えば、高電位の入力電位信号が第 1 の入力端子 11 および第 2 の入力端子 12 のいずれか一方に入力されると、出力端子 13 からは低電位側電源電位 (VSS) である低電位が出力される。また、第 1 の入力端子 11 および第 2 の入力端子 12 に低電位の入力電位信号が入力されると、出力端子 13 からは高電位側電源電位 (VDD) である高電位が出力される。 10

【0126】

次に、論理回路 200 の動作中に電源をオフした場合の回路動作について説明する。従来の NOR 回路では、回路動作中に電源をオフした場合、高電位側電源電位 (VDD) と低電位側電源電位 (VSS) に電位差が無くなるため、演算処理中のデータは揮発する。

【0127】

一方、論理回路 200 では、n チャネル型トランジスタ 201 および n チャネル型トランジスタ 202 は極めてオフ電流の低いトランジスタであることから、n チャネル型トランジスタ 201 および n チャネル型トランジスタ 202 のゲートの電位 を低電位 (n チャネル型トランジスタ 201 および n チャネル型トランジスタ 202 の  $V_{gs}$  を n チャネル型トランジスタ 201 および n チャネル型トランジスタ 202 のしきい値電圧より低い状態) とした後、電源をオフした場合、n チャネル型トランジスタ 201 および n チャネル型トランジスタ 202 のゲートの電位 を低電位としている (n チャネル型トランジスタ 201 および n チャネル型トランジスタ 202 の  $V_{gs}$  を n チャネル型トランジスタ 201 および n チャネル型トランジスタ 202 のしきい値電圧より低くする) ことで、ノード N\_6 およびノード N\_7 をフローティングとすることができます。該ノード N\_6 および該ノード N\_7 の電位を保持することができる。なお、ノード N\_6 とは、図 6 (A) において、「N\_6」で指示する部分を含む太線部であり、また、ノード N\_7 とは、図 6 (A) において、「N\_7」で指示する部分を含む太線部である。なお、保持ノード (ノード N\_6 およびノード N\_7) に容量素子を設けずとも十分な期間、電位を保持できるが、さらなる保持期間を望む場合は、該保持ノードに一方の電極が電気的に接続され、且つ他方の電極が低電位側電源電位線に電気的に接続された容量素子を設けてよい。 20

【0128】

そして、再度電源をオンした後、n チャネル型トランジスタ 201 および n チャネル型トランジスタ 202 のゲートの電位 を高電位 (n チャネル型トランジスタ 201 および n チャネル型トランジスタ 202 の  $V_{gs}$  を n チャネル型トランジスタ 201 および n チャネル型トランジスタ 202 のしきい値電圧より高い状態) にすることで、ノード N\_6 およびノード N\_7 に保持された電位をもとに演算処理を再開することができる。したがって、再度電源をオンした際に入力電位信号を供給する必要が無く、素早く演算処理を再開することができる。また、論理回路 200 の消費電力を低減することができる。 30 40

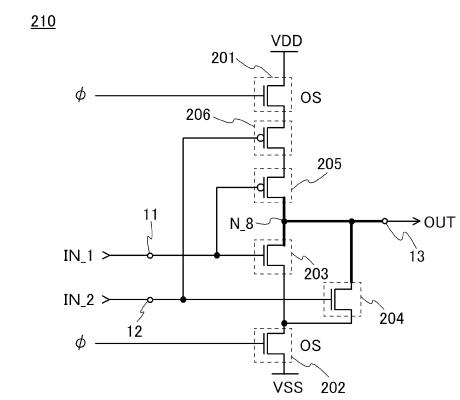

【0129】

論理回路 200 は、n チャネル型トランジスタ 201 の第 2 端子および n チャネル型トランジスタ 202 の第 2 端子と電気的に接続されたノードの電位が保持される形態であるが、論理回路 200 の変形例として、出力端子 13 と電気的に接続されたノードの電位が保持される形態としてもよい。そこで、図 6 (B) に該形態に対応する論理回路 210 を示す。なお、論理回路 210 は、図 6 (A) の論理回路 200 に付した符号を適宜用いて説明する。

【0130】

論理回路 210 は、n チャネル型トランジスタ 201、n チャネル型トランジスタ 20

2、nチャネル型トランジスタ203、およびnチャネル型トランジスタ204、ならびにpチャネル型トランジスタ205およびpチャネル型トランジスタ206を有する。論理回路210は論理回路200と比較して回路を構成するトランジスタの接続関係が異なる。なお、nチャネル型トランジスタ201およびnチャネル型トランジスタ202は極めてオフ電流の低いトランジスタである。

#### 【0131】

論理回路210は、第1の入力端子11とnチャネル型トランジスタ203のゲートおよびpチャネル型トランジスタ205のゲートとが電気的に接続されており、第2の入力端子12とnチャネル型トランジスタ204のゲートおよびpチャネル型トランジスタ206のゲートとが電気的に接続されており、高電位側電源電位(VDD)を供給する高電位側電源電位線とnチャネル型トランジスタ201の第1端子と電気的に接続されており、nチャネル型トランジスタ201の第2端子とpチャネル型トランジスタ206の第1端子とが電気的に接続されており、pチャネル型トランジスタ206の第2端子とpチャネル型トランジスタ205の第1端子とが電気的に接続されており、低電位側電源電位(VSS)を供給する低電位側電源電位線とnチャネル型トランジスタ202の第1端子とが電気的に接続されており、nチャネル型トランジスタ202の第2端子とnチャネル型トランジスタ203の第1端子およびnチャネル型トランジスタ204の第1端子とが電気的に接続されており、nチャネル型トランジスタ203の第2端子およびnチャネル型トランジスタ204の第2端子ならびにpチャネル型トランジスタ205の第2端子と出力端子13とが電気的に接続されている。なお、nチャネル型トランジスタ201のゲートおよびnチャネル型トランジスタ202のゲートは同電位である。

#### 【0132】

論理回路210は、論理回路200と同様にnチャネル型トランジスタ201およびnチャネル型トランジスタ202のゲートの電位が高電位の場合において、従来のNOR回路と同様の演算処理を行う。

#### 【0133】

次に、論理回路210の動作中に電源をオフした場合の回路動作について説明する。従来のNOR回路では、回路動作中に電源をオフした場合、演算処理中のデータは揮発する。

#### 【0134】

一方、論理回路210では、nチャネル型トランジスタ201およびnチャネル型トランジスタ202は極めてオフ電流の低いトランジスタであることから、nチャネル型トランジスタ201およびnチャネル型トランジスタ202のゲートの電位を低電位とした後、電源をオフした場合、nチャネル型トランジスタ201およびnチャネル型トランジスタ202のゲートの電位を低電位としていることで、出力端子13と電気的に接続された少なくともノードN\_8をフローティングとすることができますため、該ノードN\_8の電位を保持することができる。なお、ノードN\_8とは、図6(B)において、「N\_8」で指示する部分を含む太線部である。なお、保持ノード(ノードN\_8)に容量素子を設けずとも十分な期間、電位を保持できるが、さらなる保持期間を望む場合は、該保持ノードに一方の電極が電気的に接続され、且つ他方の電極が低電位側電源電位線に電気的に接続された容量素子を設けてもよい。

#### 【0135】

そして、再度電源をオンした後、nチャネル型トランジスタ201およびnチャネル型トランジスタ202のゲートの電位を高電位にすることで、再度電源をオンした際に入力電位信号を供給する必要が無く、素早く演算処理を再開することができる。また、論理回路210の消費電力を低減することができる。

#### 【0136】

また、本実施の形態において、nチャネル型トランジスタ201およびnチャネル型トランジスタ202のように極めてオフ電流の低いトランジスタを配置する箇所は、電源をオフした際に、入力された保持すべき電位を低下させる電流経路(リーク経路)に配置す

10

20

30

40

50

れば、論理回路 200 および論理回路 210 に限定されない。そこで、図 7 に、論理回路 200 および論理回路 210 とは、極めてオフ電流の低いトランジスタを配置する箇所が異なる論理回路の一例を示す。図 7 (A) は、該一例である論理回路 220 を示す回路図であり、図 7 (B) は、該一例である論理回路 230 を示す回路図である。なお、論理回路 220 および論理回路 230 は、図 6 (A) の論理回路 200 に付した符号を適宜用いて説明する。

#### 【0137】

論理回路 220 は、n チャネル型トランジスタ 201、n チャネル型トランジスタ 202、n チャネル型トランジスタ 203、および n チャネル型トランジスタ 204、ならびに p チャネル型トランジスタ 205 および p チャネル型トランジスタ 206 を有する。特に、n チャネル型トランジスタ 201 および n チャネル型トランジスタ 202 は極めてオフ電流の低いトランジスタである。

#### 【0138】

論理回路 220 は、第 1 の入力端子 11 と n チャネル型トランジスタ 203 のゲートおよび p チャネル型トランジスタ 205 のゲートとが電気的に接続されており、第 2 の入力端子 12 と n チャネル型トランジスタ 204 のゲートおよび p チャネル型トランジスタ 206 のゲートとが電気的に接続されており、高電位側電源電位 (VDD) を供給する高電位側電源電位線と p チャネル型トランジスタ 206 の第 1 端子とが電気的に接続されており、p チャネル型トランジスタ 206 の第 2 端子と n チャネル型トランジスタ 201 の第 1 端子とが電気的に接続されており、n チャネル型トランジスタ 201 の第 2 端子と p チャネル型トランジスタ 205 の第 1 端子とが電気的に接続されており、低電位側電源電位 (VSS) を供給する低電位側電源電位線と n チャネル型トランジスタ 202 の第 1 端子とが電気的に接続されており、n チャネル型トランジスタ 202 の第 2 端子と n チャネル型トランジスタ 203 の第 1 端子および n チャネル型トランジスタ 204 の第 1 端子とが電気的に接続されており、n チャネル型トランジスタ 203 の第 2 端子および n チャネル型トランジスタ 204 の第 2 端子ならびに p チャネル型トランジスタ 205 の第 2 端子と出力端子 13 とが電気的に接続されている。なお、n チャネル型トランジスタ 201 のゲートおよび n チャネル型トランジスタ 202 のゲートは同電位である。

#### 【0139】

論理回路 220 は、n チャネル型トランジスタ 201 および n チャネル型トランジスタ 202 のゲートの電位  $V_{G1}$  が高電位の場合において、従来の NOR 回路と同様の演算処理を行う。

#### 【0140】

次に、論理回路 220 の動作中に電源をオフした場合の回路動作について説明する。従来の NOR 回路では、回路動作中に電源をオフした場合、演算処理中のデータは揮発する。

#### 【0141】

一方、論理回路 220 では、n チャネル型トランジスタ 201 および n チャネル型トランジスタ 202 は極めてオフ電流の低いトランジスタであることから、n チャネル型トランジスタ 201 および n チャネル型トランジスタ 202 のゲートの電位  $V_{G1}$  を低電位とした後、電源をオフした場合、n チャネル型トランジスタ 201 および n チャネル型トランジスタ 202 のゲートの電位  $V_{G1}$  を低電位としていることで、少なくともノード N\_8 をフローティングとすることができるため、該ノード N\_8 の電位を保持することができる。なお、保持ノード (ノード N\_8) に容量素子を設けずとも十分な期間、電位を保持できるが、さらなる保持期間を望む場合は、該保持ノードに一方の電極が電気的に接続され、且つ他方の電極が低電位側電源電位線に電気的に接続された容量素子を設けてもよい。

#### 【0142】

そして、再度電源をオンした後、n チャネル型トランジスタ 201 および n チャネル型トランジスタ 202 のゲートの電位  $V_{G1}$  を高電位にすることで、再度電源をオンした際に入力電位信号を供給する必要が無く、素早く演算処理を再開することができる。また、論理

10

20

30

40

50

回路 220 の消費電力を低減することができる。

【0143】

論理回路 230 は、n チャネル型トランジスタ 201、n チャネル型トランジスタ 202、n チャネル型トランジスタ 203、n チャネル型トランジスタ 204、および n チャネル型トランジスタ 207、ならびに p チャネル型トランジスタ 205 および p チャネル型トランジスタ 206 を有する。なお、n チャネル型トランジスタ 201、n チャネル型トランジスタ 202 および n チャネル型トランジスタ 207 は極めてオフ電流の低いトランジスタである。

【0144】

論理回路 230 は、第 1 の入力端子 11 と n チャネル型トランジスタ 203 のゲート 10 および p チャネル型トランジスタ 205 のゲート とが電気的に接続されており、第 2 の入力端子 12 と n チャネル型トランジスタ 204 のゲート および p チャネル型トランジスタ 206 のゲート とが電気的に接続されており、高電位側電源電位 (VDD) を供給する高電位側電源電位線と n チャネル型トランジスタ 201 の第 1 端子 と電気的に接続されており、n チャネル型トランジスタ 201 の第 2 端子 と p チャネル型トランジスタ 206 の第 1 端子 とが電気的に接続されており、p チャネル型トランジスタ 206 の第 2 端子 と p チャネル型トランジスタ 205 の第 1 端子 とが電気的に接続されており、低電位側電源電位 (VSS) を供給する低電位側電源電位線と n チャネル型トランジスタ 204 の第 1 端子 とが電気的に接続されており、n チャネル型トランジスタ 204 の第 2 端子 と n チャネル型トランジスタ 202 の第 1 端子 および n チャネル型トランジスタ 203 の第 1 端子 とが電気的に接続されており、n チャネル型トランジスタ 203 の第 2 端子 と n チャネル型トランジスタ 207 の第 1 端子 とが電気的に接続されており、n チャネル型トランジスタ 202 の第 2 端子 および n チャネル型トランジスタ 207 の第 2 端子 ならびに p チャネル型トランジスタ 205 の第 2 端子 と出力端子 13 とが電気的に接続されている。なお、n チャネル型トランジスタ 201 のゲート、n チャネル型トランジスタ 202 および n チャネル型トランジスタ 207 のゲートは同電位である。

【0145】

論理回路 230 は、n チャネル型トランジスタ 201 のゲート、n チャネル型トランジスタ 202 および n チャネル型トランジスタ 207 のゲートの電位 が高電位の場合において、従来の NOR 回路と同様の演算処理を行う。

【0146】

次に、論理回路 230 の動作中に電源をオフした場合の回路動作について説明する。従来の NOR 回路では、回路動作中に電源をオフした場合、演算処理中のデータは揮発する。

【0147】

一方、論理回路 230 では、n チャネル型トランジスタ 201 のゲート、n チャネル型トランジスタ 202 および n チャネル型トランジスタ 207 は極めてオフ電流の低いトランジスタであることから、n チャネル型トランジスタ 201、n チャネル型トランジスタ 202 および n チャネル型トランジスタ 207 のゲートの電位 を低電位とした後、電源をオフした場合、n チャネル型トランジスタ 201 のゲート、n チャネル型トランジスタ 202 および n チャネル型トランジスタ 207 のゲートの電位 を低電位としていることで、少なくともノード N\_8 をフローティングとすることができますため、該ノード N\_8 の電位を保持することができる。なお、保持ノード (ノード N\_8) に容量素子を設けずとも十分な期間、電位を保持できるが、さらなる保持期間を望む場合は、該保持ノードに一方の電極が電気的に接続され、且つ他方の電極が低電位側電源電位線に電気的に接続された容量素子を設けてもよい。

【0148】

そして、再度電源をオンした後、n チャネル型トランジスタ 201、n チャネル型トランジスタ 202 および n チャネル型トランジスタ 207 のゲートの電位 を高電位にすることで、再度電源をオンした際に入力電位信号を供給する必要が無く、素早く演算処理を

10

20

30

40

50

再開することができる。また、論理回路 230 の消費電力を低減することができる。

【0149】

論理回路 200 乃至論理回路 230 において、n チャネル型トランジスタ 201、n チャネル型トランジスタ 202 および n チャネル型トランジスタ 207 は、上記したように極めてオフ電流の低いトランジスタが適用される。該トランジスタは、例えば、実施の形態 1 で説明したトランジスタ 15 乃至 19、実施の形態 2 で説明した n チャネル型トランジスタ 51 および n チャネル型トランジスタ 54 におけるオフ電流特性を有する。そして、n チャネル型トランジスタ 201、n チャネル型トランジスタ 202 および n チャネル型トランジスタ 207 は、n チャネル型トランジスタ 51 および n チャネル型トランジスタ 54 と同様に、酸化物半導体、特に上記水素濃度を有し、キャリアの供与体となる水素を極めて低濃度に低下させた酸化物半導体をチャネル形成領域に適用したトランジスタと 10 することができる。なお、酸化物半導体中のキャリア濃度についても n チャネル型トランジスタ 51 および n チャネル型トランジスタ 54 と同様であることが好ましい。

【0150】

論理回路 200 乃至論理回路 230 において、n チャネル型トランジスタ 203 および n チャネル型トランジスタ 204 ならびに p チャネル型トランジスタ 205 および p チャネル型トランジスタ 206 には、特に制限はなく、半導体材料を含む基板を用いて形成されるトランジスタであればよい。

【0151】

なお、n チャネル型トランジスタ 203 および n チャネル型トランジスタ 204 についても、n チャネル型トランジスタ 201、n チャネル型トランジスタ 202 および n チャネル型トランジスタ 207 のように、上記水素濃度を有し、キャリアの供与体となる水素を極めて低濃度に低下させた酸化物半導体をチャネル形成領域に適用したトランジスタと 20 することで、論理回路 200 乃至論理回路 230 の消費電力をさらに低減させることができる。

【0152】

本発明の一態様である NOR 回路において、論理回路 200 乃至論理回路 220 のように、トランジスタの素子数をできる限り少なくなるように極めてオフ電流が低いトランジスタを配置する回路構成は、論理回路 230 の回路構成より、トランジスタの素子数が少ないためにトランジスタの占有面積が小さく、微細化の観点から好ましい。また、本発明の一態様である NOR 回路において、論理回路 210 乃至論理回路 230 のように、出力端子と電気的に接続されたノードの電位が保持される回路構成、別言すると演算処理後の電位が保持される回路構成は、論理回路 200 よりさらに高速に演算処理を再開させることができ、回路動作の高速化の観点から好ましい。 30

【0153】

さらに、本発明の一態様である NOR 回路（論理回路 200 乃至論理回路 230 ）において、極めてオフ電流の低いトランジスタ以外の構成（従来の NOR 回路に相当する構成）は、CMOS 回路に限定されない。例えば、論理回路 50 および論理回路 55 のように、該構成の一部である p チャネル型トランジスタを n 型且つエンハンスマント型トランジスタとしてもよい。該構成の一部である p チャネル型トランジスタに、n 型且つエンハンスマント型トランジスタを適用することで、論理回路 200 乃至論理回路 230 を構成するトランジスタの極性を同じにすることができる。これにより、作製プロセスを低減することができ、論理回路 200 乃至論理回路 230 の歩留まりを向上させ、製造コストを低減させることができる。なお、該 n 型且つエンハンスマント型トランジスタにおいても、上記水素濃度を有する酸化物半導体でチャネル形成領域を構成するトランジスタとしてもよい。このように、n チャネル型トランジスタのみで構成される論理回路であっても、論理回路 200 乃至論理回路 230 を低消費電力化することができる。 40

【0154】

以上より、論理回路 200 乃至論理回路 230 において、消費電力を低減することで、論理回路 200 乃至論理回路 230 のうち 1 以上の論理回路を有する半導体装置の消費電 50

力を低減することができる。さらに、論理回路 200 乃至論理回路 230 の消費電力を低減することで、論理回路 200 乃至論理回路 230 を動作させる外部回路の負荷が低減できる。これにより、論理回路 200 乃至論理回路 230 のうち 1 以上の論理回路および該外部回路を有する半導体装置の機能拡張が可能となる。

【0155】

なお、本実施の形態の内容または該内容の一部は、他の実施の形態の内容若しくは該内容の一部と自由に組み合わせることが可能である。

【0156】

(実施の形態 5)

本実施の形態では、実施の形態 1 に示した論理回路の一例について説明する。具体的には、AND 回路について図 8 を用いて説明する。なお、回路図においては、酸化物半導体を用いたトランジスタであることを示すために、点線を用いた回路記号および OS の符号を併せて付す場合がある。そして、本実施の形態で説明する論理回路は、実施の形態 1 での説明に用いた符号を適宜使用する。

10

【0157】

論理回路の構成例および動作例

図 8 に示す論理回路 300 は AND 回路に新たに n チャネル型トランジスタを電気的に接続した論理回路である。本実施の形態では、該 AND 回路を微細化に好適な CMOS 回路による回路構成とするが、該 AND 回路を他の抵抗素子やダイオードなどを用いる回路構成としてもよい。なお、図 8 において、AND 回路には入力端子が 2 つあるため、一方を第 1 の入力端子 11、もう一方を第 2 の入力端子 12 と符号を付する。

20

【0158】

論理回路 300 は、n チャネル型トランジスタ 301、n チャネル型トランジスタ 302、n チャネル型トランジスタ 303、n チャネル型トランジスタ 304、および n チャネル型トランジスタ 308、ならびに p チャネル型トランジスタ 305、p チャネル型トランジスタ 306、および p チャネル型トランジスタ 309 を有する。特に、n チャネル型トランジスタ 301 および n チャネル型トランジスタ 302 は極めてオフ電流の低いトランジスタである。

【0159】

AND 回路は、実施の形態 3 で説明した NAND 回路と実施の形態 2 で説明した NOT 回路を電気的に接続した論理回路である。つまり、AND 回路は、NAND 回路の出力端子を、NOT 回路の入力端子と見なすことができる。該 AND 回路は、n チャネル型トランジスタ 303 と、n チャネル型トランジスタ 304 と、p チャネル型トランジスタ 305 と、および p チャネル型トランジスタ 306 とで NAND 回路を構成し、n チャネル型トランジスタ 308 と、および p チャネル型トランジスタ 309 とで NOT 回路を構成する。さらに、極めてオフ電流の低いトランジスタである n チャネル型トランジスタ 301 および n チャネル型トランジスタ 302 は、該 NAND 回路内に配置することもできるし、該 NOT 回路内に配置することもできる。なお、論理回路 300 は、n チャネル型トランジスタ 301 および n チャネル型トランジスタ 302 を該 NAND 回路内に配置する回路構成である。

30

【0160】

論理回路 300 を構成するトランジスタは、以下の接続関係を有する。はじめに NAND 回路の接続関係を記載する。

【0161】

第 1 の入力端子 11 と n チャネル型トランジスタ 303 のゲートおよび p チャネル型トランジスタ 305 のゲートとが電気的に接続されており、第 2 の入力端子 12 と n チャネル型トランジスタ 304 のゲートおよび p チャネル型トランジスタ 306 のゲートとが電気的に接続されており、高電位側電源電位 (VDD) を供給する高電位側電源電位線と n チャネル型トランジスタ 301 の第 1 端子とが電気的に接続されており、n チャネル型トランジスタ 301 の第 2 端子と p チャネル型トランジスタ 305 の第 1 端子および p チャ

40

50

ネル型トランジスタ306の第1端子とが電気的に接続されており、低電位側電源電位( VSS )を供給する低電位側電源電位線とnチャネル型トランジスタ304の第1端子とが電気的に接続されており、nチャネル型トランジスタ304の第2端子とnチャネル型トランジスタ303の第1端子とが電気的に接続されており、nチャネル型トランジスタ303の第2端子とnチャネル型トランジスタ302の第1端子とが電気的に接続されており、pチャネル型トランジスタ305の第2端子とpチャネル型トランジスタ306の第2端子とnチャネル型トランジスタ302の第2端子とが電気的に接続されている。なお、nチャネル型トランジスタ301のゲートおよびnチャネル型トランジスタ302のゲートは同電位である。

【0162】

10

次いで、論理回路300のNOT回路の接続関係を記載する。

【0163】

nチャネル型トランジスタ308のゲートおよびpチャネル型トランジスタ309のゲートと、pチャネル型トランジスタ305の第2端子およびpチャネル型トランジスタ306の第2端子ならびにnチャネル型トランジスタ302の第2端子とが電気的に接続されており、高電位側電源電位( VDD )を供給する高電位側電源電位線とpチャネル型トランジスタ309の第1端子とが電気的に接続されており、低電位側電源電位( VSS )を供給する低電位側電源電位線とnチャネル型トランジスタ308の第1端子とが電気的に接続されており、pチャネル型トランジスタ309の第2端子およびnチャネル型トランジスタ308の第2端子と出力端子13とが電気的に接続されている。

20

【0164】

論理回路300は、nチャネル型トランジスタ301およびnチャネル型トランジスタ302のゲート電位が高電位の場合( nチャネル型トランジスタ301およびnチャネル型トランジスタ302のVgsがnチャネル型トランジスタ301およびnチャネル型トランジスタ302のしきい値電圧より高い場合 )において、従来のAND回路と同様の演算処理を行う。例えば、高電位の入力電位信号が第1の入力端子11および第2の入力端子12に入力されると、出力端子13からは高電位側電源電位( VDD )である高電位が出力される。また、低電位の入力電位信号が第1の入力端子11および第2の入力端子12のいずれか一方に入力されると、出力端子13からは低電位側電源電位( VSS )である低電位が出力される。

30

【0165】

次に、論理回路300の動作中に電源をオフした場合の回路動作について説明する。従来のAND回路では、回路動作中に電源をオフした場合、高電位側電源電位( VDD )と低電位側電源電位( VSS )に電位差が無くなるため、演算処理中のデータは揮発する。

【0166】

一方、論理回路300では、nチャネル型トランジスタ301およびnチャネル型トランジスタ302は極めてオフ電流の低いトランジスタであることから、nチャネル型トランジスタ301およびnチャネル型トランジスタ302のゲートの電位を低電位( nチャネル型トランジスタ301およびnチャネル型トランジスタ302のVgsをnチャネル型トランジスタ301およびnチャネル型トランジスタ302のしきい値電圧より低い状態 )とした後、回路動作中に電源をオフした場合、nチャネル型トランジスタ301およびnチャネル型トランジスタ302のゲートの電位を低電位としている( nチャネル型トランジスタ301およびnチャネル型トランジスタ302のVgsをnチャネル型トランジスタ301およびnチャネル型トランジスタ302のしきい値電圧より低くする )ことで、少なくともノードN\_9をフローティングとすることができますため、該ノードN\_9の電位を保持することができる。なお、ノードN\_9とは、図8において、「N\_9」で指示する部分を含む太線部である。なお、保持ノード( ノードN\_9 )に容量素子を設けずとも十分な期間、電位を保持できるが、さらなる保持期間を望む場合は、該保持ノードに一方の電極が電気的に接続され、且つ他方の電極が低電位側電源電位線に電気的に接続された容量素子を設けてもよい。

40

50

## 【0167】

そして、再度電源をオンした後、nチャネル型トランジスタ301およびnチャネル型トランジスタ302のゲートの電位を高電位にすることで、ノードN\_9に保持された電位をもとに演算処理を再開することができる。したがって、再度電源をオンした際に入力電位信号を供給する必要が無く、素早く演算処理を再開することができる。また、論理回路300の消費電力を低減することができる。

## 【0168】

論理回路300は、NAND回路にnチャネル型トランジスタ301およびnチャネル型トランジスタ302を該NAND回路内に配置する回路構成であるが、論理回路300の変形例として、nチャネル型トランジスタ301およびnチャネル型トランジスタ302をNOT回路内に配置し、出力端子13と電気的に接続されたノードの電位が保持される形態としてもよい。そこで、図9に該形態に対応する論理回路310を示す。なお、論理回路310は、図8の論理回路300に付した符号を適宜用いて説明する。

10

## 【0169】

論理回路310は、論理回路300と同様にnチャネル型トランジスタ301、nチャネル型トランジスタ302、nチャネル型トランジスタ303、nチャネル型トランジスタ304、およびnチャネル型トランジスタ308、ならびにpチャネル型トランジスタ305、pチャネル型トランジスタ306、およびpチャネル型トランジスタ309を有する。特に、nチャネル型トランジスタ301およびnチャネル型トランジスタ302は極めてオフ電流の低いトランジスタである。

20

## 【0170】

nチャネル型トランジスタ303と、nチャネル型トランジスタ304と、pチャネル型トランジスタ305と、およびpチャネル型トランジスタ306とでNAND回路を構成し、nチャネル型トランジスタ308と、およびpチャネル型トランジスタ309とでNOT回路を構成する。さらに、論理回路310は、nチャネル型トランジスタ301およびnチャネル型トランジスタ302を該NOT回路内に配置する回路構成である。

## 【0171】

論理回路310を構成するトランジスタは、以下の接続関係を有する。はじめにNAND回路の接続関係を記載する。

## 【0172】

30

第1の入力端子11とnチャネル型トランジスタ303のゲートおよびpチャネル型トランジスタ305のゲートとが電気的に接続されており、第2の入力端子12とnチャネル型トランジスタ304のゲートおよびpチャネル型トランジスタ306のゲートとが電気的に接続されており、高電位側電源電位(VDD)を供給する高電位側電源電位線とpチャネル型トランジスタ305の第1端子およびpチャネル型トランジスタ306の第1端子とが電気的に接続されており、低電位側電源電位(VSS)を供給する低電位側電源電位線とnチャネル型トランジスタ304の第1端子とが電気的に接続されており、nチャネル型トランジスタ304の第2端子とnチャネル型トランジスタ303の第1端子とが電気的に接続されており、pチャネル型トランジスタ305の第2端子とpチャネル型トランジスタ306の第2端子とnチャネル型トランジスタ303の第2端子とが電気的に接続されている。

40

## 【0173】

次いで、論理回路310のNOT回路の接続関係を記載する。

## 【0174】

nチャネル型トランジスタ308のゲートおよびpチャネル型トランジスタ309のゲートと、pチャネル型トランジスタ305の第2端子およびpチャネル型トランジスタ306の第2端子ならびにnチャネル型トランジスタ303の第2端子とが電気的に接続されており、高電位側電源電位(VDD)を供給する高電位側電源電位線とpチャネル型トランジスタ309の第1端子とが電気的に接続されており、pチャネル型トランジスタ309の第2端子とnチャネル型トランジスタ301の第1端子とが電気的に接続されてお

50

り、低電位側電源電位 (VSS) を供給する低電位側電源電位線とnチャネル型トランジスタ308の第1端子とが電気的に接続されており、nチャネル型トランジスタ308の第2端子とnチャネル型トランジスタ302の第1端子とが電気的に接続されており、nチャネル型トランジスタ301の第2端子およびnチャネル型トランジスタ302の第2端子と出力端子13とが電気的に接続されている。なお、nチャネル型トランジスタ301のゲートおよびnチャネル型トランジスタ302のゲートは同電位である。

#### 【0175】

論理回路310は、論理回路300と同様にnチャネル型トランジスタ301およびnチャネル型トランジスタ302のゲート電位が高電位の場合において、従来のAND回路と同様の演算処理を行う。

10

#### 【0176】

次に、論理回路310の動作中に電源をオフした場合の回路動作について説明する。従来のAND回路では、回路動作中に電源をオフした場合、演算処理中のデータは揮発する。

#### 【0177】

一方、論理回路310では、nチャネル型トランジスタ301およびnチャネル型トランジスタ302は極めてオフ電流の低いトランジスタであることから、nチャネル型トランジスタ301およびnチャネル型トランジスタ302のゲートの電位を低電位とした後、電源をオフした場合、nチャネル型トランジスタ301およびnチャネル型トランジスタ302のゲートの電位を低電位としていることで、ノードN\_10をフローティングとすることができます。該ノードN\_10の電位を保持することができる。なお、ノードN\_10とは、図9において、「N\_10」で指示する部分を含む太線部である。また、保持ノード(ノードN\_10)に容量素子を設けずとも十分な期間、電位を保持できるが、さらなる保持期間を望む場合は、該保持ノードに一方の電極が電気的に接続され、且つ他方の電極が低電位側電源電位線に電気的に接続された容量素子を設けてもよい。

20

#### 【0178】

そして、再度電源をオンした後、nチャネル型トランジスタ301およびnチャネル型トランジスタ302のゲートの電位を高電位にすることで、再度電源をオンした際に入力電位信号を供給する必要が無く、論理回路310の演算処理を行うための消費電力を低減することができる。

30

#### 【0179】

また、上記したようにAND回路は、実施の形態3で説明したNAND回路に実施の形態2で説明したNOT回路を電気的に接続した論理回路であることから、実施の形態3で説明したNAND回路および実施の形態2で説明したNOT回路の様々な形態を適宜組み合わせて、AND回路を構成することができる。例えば、本発明の一態様のAND回路は、実施の形態3で説明した論理回路100乃至論理回路130のいずれか一と従来のNOT回路を電気的に接続したAND回路、または従来のNAND回路と実施の形態2で説明した論理回路50または論理回路55の一方を電気的に接続したAND回路とすることができます。

#### 【0180】

40

論理回路300および論理回路310において、nチャネル型トランジスタ301、nチャネル型トランジスタ302は、上記したように極めてオフ電流の低いトランジスタが適用される。該トランジスタは、例えば、実施の形態1で説明したトランジスタ15乃至19、実施の形態2で説明したnチャネル型トランジスタ51およびnチャネル型トランジスタ54におけるオフ電流特性を有する。そして、nチャネル型トランジスタ301、nチャネル型トランジスタ302は、nチャネル型トランジスタ51およびnチャネル型トランジスタ54と同様に、酸化物半導体、特に上記水素濃度を有し、キャリアの供与体となる水素を極めて低濃度に低下させた酸化物半導体をチャネル形成領域に適用したトランジスタとすることができます。なお、酸化物半導体中のキャリア濃度についても実施の形態2で説明したnチャネル型トランジスタ51およびnチャネル型トランジスタ54と同

50

様であることが好ましい。

【0181】

論理回路300および論理回路310において、nチャネル型トランジスタ303、nチャネル型トランジスタ304およびnチャネル型トランジスタ308、ならびにpチャネル型トランジスタ305、pチャネル型トランジスタ306およびpチャネル型トランジスタ309には、特に制限はなく、半導体材料を含む基板を用いて形成されるトランジスタであればよい。

【0182】

なお、nチャネル型トランジスタ303、nチャネル型トランジスタ304およびnチャネル型トランジスタ308についても、nチャネル型トランジスタ301、nチャネル型トランジスタ302のように、上記水素濃度を有し、キャリアの供与体となる水素を極めて低濃度に低下させた酸化物半導体をチャネル形成領域に適用したトランジスタとすることで、論理回路300および論理回路310の消費電力をさらに低減させる効果が大きくなる。

【0183】

本発明の一態様であるAND回路において、論理回路300および論理回路310のように、トランジスタの素子数をできる限り少なくなるように極めてオフ電流が低いトランジスタを配置する回路構成は、トランジスタの占有面積の拡大を最小限にすることができる、微細化の観点から好ましい。また、本発明の一態様であるAND回路において、論理回路310のように、出力端子13と電気的に接続されたノードの電位が保持される回路構成、別言すると演算処理後の電位が保持される回路構成は、論理回路300よりさらに高速に演算処理を再開させることができ、回路動作の高速化の観点から好ましい。

【0184】

さらに、本発明の一態様であるAND回路（論理回路300および論理回路310）において、極めてオフ電流の低いトランジスタ以外の構成（従来のAND回路に相当する構成）は、CMOS回路に限定されない。例えば、論理回路50および論理回路55のように、該構成の一部であるpチャネル型トランジスタをn型且つエンハンスマント型トランジスタとしてもよい。該構成の一部であるpチャネル型トランジスタに、n型且つエンハンスマント型トランジスタを適用することで、論理回路300および論理回路310を構成するトランジスタの極性を同じにすることができる。これにより、作製プロセスを低減することができ、論理回路300および論理回路310の歩留まりを向上させ、製造コストを低減させることができる。なお、該n型且つエンハンスマント型トランジスタにおいても、上記水素濃度を有する酸化物半導体でチャネル形成領域を構成するトランジスタとしてもよい。このように、nチャネル型トランジスタのみで構成される論理回路であっても、論理回路300乃至論理回路310を低消費電力化することができる。

【0185】

以上より、論理回路300および論理回路310において、消費電力を低減することで、論理回路300および論理回路310のすくなくとも一方の論理回路を有する半導体装置の消費電力を低減することができる。さらに、論理回路300および論理回路310の消費電力を低減することで、論理回路300および論理回路310を動作させる外部回路の負荷が低減できる。これにより、論理回路300および論理回路310のすくなくとも一方の論理回路および該外部回路を有する半導体装置の機能拡張が可能となる。

【0186】

なお、本実施の形態の内容または該内容の一部は、他の実施の形態の内容若しくは該内容の一部と自由に組み合わせることが可能である。

【0187】

（実施の形態6）

本実施の形態では、実施の形態1に示した論理回路の一例について説明する。具体的には、OR回路について図10を用いて説明する。なお、回路図においては、酸化物半導体を用いたトランジスタであることを示すために、点線を用いた回路記号およびOSの符号

10

20

30

40

50

を併せて付す場合がある。そして、本実施の形態で説明する論理回路は、実施の形態1での説明に用いた符号を適宜使用する。

【0188】

論理回路の構成例および動作例

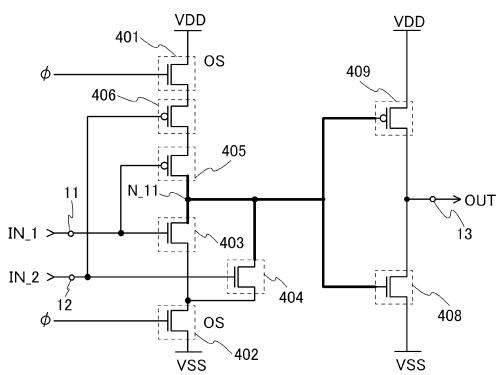

図10に示す論理回路400はOR回路に新たにnチャネル型トランジスタを電気的に接続した論理回路である。本実施の形態では、該OR回路を微細化に好適なCMOS回路による構成するが、該OR回路を他の抵抗素子やダイオードなどを用いる回路構成としてもよい。なお、図10において、OR回路には入力端子が2つあるため、一方を第1の入力端子11、もう一方を第2の入力端子12と符号を付する。

【0189】

論理回路400は、nチャネル型トランジスタ401、nチャネル型トランジスタ402、nチャネル型トランジスタ403、nチャネル型トランジスタ404、およびnチャネル型トランジスタ408、ならびにpチャネル型トランジスタ405と、pチャネル型トランジスタ406と、およびpチャネル型トランジスタ409を有する。特に、nチャネル型トランジスタ401およびnチャネル型トランジスタ402は極めてオフ電流の低いトランジスタである。

【0190】

本実施の形態で説明するOR回路は、実施の形態4で説明したNOR回路と実施の形態2で説明したNOT回路を電気的に接続した論理回路である。つまり、NOR回路の出力端子を、NOT回路の入力端子と見なすことができる。該OR回路は、nチャネル型トランジスタ403と、nチャネル型トランジスタ404と、pチャネル型トランジスタ405と、およびpチャネル型トランジスタ406とでNOR回路を構成し、nチャネル型トランジスタ408と、およびpチャネル型トランジスタ409とでNOT回路を構成する。さらに、極めてオフ電流の低いトランジスタであるnチャネル型トランジスタ401およびnチャネル型トランジスタ402は、該NOR回路内に配置することもできるし、該NOT回路内に配置することもできる。論理回路400は、nチャネル型トランジスタ401およびnチャネル型トランジスタ402を該NOR回路内に配置する回路構成である。

【0191】

論理回路400を構成するトランジスタは、以下の接続関係を有する。はじめにNOR回路の接続関係を記載する。

【0192】

第1の入力端子11とnチャネル型トランジスタ403のゲートおよびpチャネル型トランジスタ405のゲートとが電気的に接続されており、第2の入力端子12とnチャネル型トランジスタ404のゲートおよびpチャネル型トランジスタ406のゲートとが電気的に接続されており、高電位側電源電位(VDD)を供給する高電位側電源電位線とnチャネル型トランジスタ401の第1端子とが電気的に接続されており、nチャネル型トランジスタ401の第2端子とpチャネル型トランジスタ406の第1端子とが電気的に接続されており、pチャネル型トランジスタ406の第2端子とpチャネル型トランジスタ405の第1端子が電気的に接続されており、低電位側電源電位(VSS)を供給する低電位側電源電位線とnチャネル型トランジスタ402の第1端子とが電気的に接続されており、nチャネル型トランジスタ402の第2端子とnチャネル型トランジスタ403の第1端子およびnチャネル型トランジスタ404の第1端子とが電気的に接続されており、nチャネル型トランジスタ403の第2端子とnチャネル型トランジスタ404の第2端子とpチャネル型トランジスタ405の第2端子とが電気的に接続されている。なお、nチャネル型トランジスタ401のゲートおよびnチャネル型トランジスタ402のゲートは同電位である。

【0193】

次いで、論理回路400のNOT回路の接続関係を記載する。

【0194】

10

20

30

40

50

nチャネル型トランジスタ408のゲートおよびpチャネル型トランジスタ409のゲートと、nチャネル型トランジスタ403の第2端子およびnチャネル型トランジスタ404の第2端子ならびにpチャネル型トランジスタ405の第2端子とが電気的に接続されており、高電位側電源電位(VDD)を供給する高電位側電源電位線とpチャネル型トランジスタ409の第1端子とが電気的に接続されており、低電位側電源電位(VSS)を供給する低電位側電源電位線とnチャネル型トランジスタ408の第1端子とが電気的に接続されており、nチャネル型トランジスタ408の第2端子およびpチャネル型トランジスタ409の第2端子と出力端子13とが電気的に接続されている。

【0195】

論理回路400は、nチャネル型トランジスタ401およびnチャネル型トランジスタ402のゲートの電位が高電位の場合(nチャネル型トランジスタ401およびnチャネル型トランジスタ402のVgsがnチャネル型トランジスタ401およびnチャネル型トランジスタ402のしきい値電圧より高い場合)において、従来のOR回路と同様の演算処理を行う。例えば、高電位の入力電位信号が第1の入力端子11および第2の入力端子12のいずれか一方に入力されると、出力端子13からは高電位側電源電位(VDD)である高電位が出力される。また、低電位の入力電位信号が第1の入力端子11および第2の入力端子12に入力されると、出力端子13からは低電位側電源電位(VSS)である低電位が出力される。

【0196】

次に、論理回路400の動作中に電源をオフした場合の回路動作について説明する。従来のOR回路では、回路動作中に電源をオフした場合、高電位側電源電位(VDD)と低電位側電源電位(VSS)に電位差が無くなるため、演算処理中のデータは揮発する。

【0197】

一方、論理回路400では、nチャネル型トランジスタ401およびnチャネル型トランジスタ402は極めてオフ電流の低いトランジスタであることから、nチャネル型トランジスタ401およびnチャネル型トランジスタ402のゲートの電位を低電位(nチャネル型トランジスタ401およびnチャネル型トランジスタ402のVgsをnチャネル型トランジスタ401およびnチャネル型トランジスタ402のしきい値電圧より低い状態)とした後、電源をオフした場合、nチャネル型トランジスタ401およびnチャネル型トランジスタ402のゲートの電位を低電位としていることで、少なくともノードN\_11をフローティングとすることができます。該ノードN\_11の電位を保持することができる。なお、ノードN\_11とは、図10において、「N\_11」で指示する部分を含む太線部である。なお、保持ノード(ノードN\_11)に容量素子を設けずとも十分な期間、電位を保持できるが、さらなる保持期間を望む場合は、該保持ノードに一方の電極が電気的に接続され、且つ他方の電極が低電位側電源電位線に電気的に接続された容量素子を設けてもよい。

【0198】

そして、再度電源をオンした後、nチャネル型トランジスタ401およびnチャネル型トランジスタ402のゲートの電位を高電位にすることで、ノードN\_11に保持された電位をもとに演算処理を再開することができる。したがって、再度電源をオンした際に入力電位信号を供給する必要が無く、素早く演算処理を再開することができる。また、論理回路400の消費電力を低減することができる。

【0199】

論理回路400は、NOR回路にnチャネル型トランジスタ401およびnチャネル型トランジスタ402を該NOR回路内に配置する回路構成であるが、論理回路400の変形例として、nチャネル型トランジスタ401およびnチャネル型トランジスタ402をNOT回路内に配置し、出力端子13と電気的に接続されたノードの電位が保持される形態としてもよい。そこで、図11に該形態に対応する論理回路410を示す。なお、論理回路410は、図10の論理回路400に付した符号を適宜用いて説明する。

【0200】

10

20

30

40

50

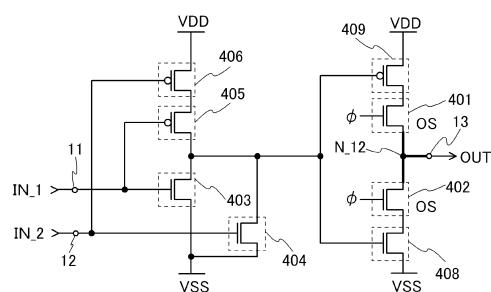

論理回路 410 は、論理回路 400 と同様に n チャネル型トランジスタ 401、n チャネル型トランジスタ 402、n チャネル型トランジスタ 403、n チャネル型トランジスタ 404、および n チャネル型トランジスタ 408、ならびに p チャネル型トランジスタ 405、p チャネル型トランジスタ 406、および p チャネル型トランジスタ 409 を有する。特に、n チャネル型トランジスタ 401 および n チャネル型トランジスタ 402 は極めてオフ電流の低いトランジスタである。

【0201】

n チャネル型トランジスタ 403 と、n チャネル型トランジスタ 404 と、p チャネル型トランジスタ 405 と、および p チャネル型トランジスタ 406 とで NOR 回路を構成し、n チャネル型トランジスタ 408 と、および p チャネル型トランジスタ 409 とで NOT 回路を構成する。さらに、論理回路 410 は、極めてオフ電流の低いトランジスタである n チャネル型トランジスタ 401 および n チャネル型トランジスタ 402 を該 NOT 回路内に配置する回路構成である。

【0202】

論理回路 410 を構成するトランジスタは、以下の接続関係を有する。はじめに NOR 回路の接続関係を記載する。

【0203】

第 1 の入力端子 11 と n チャネル型トランジスタ 403 のゲートおよび p チャネル型トランジスタ 405 のゲートとが電気的に接続されており、第 2 の入力端子 12 と n チャネル型トランジスタ 404 のゲートおよび p チャネル型トランジスタ 406 のゲートとが電気的に接続されており、高電位側電源電位 (VDD) を供給する高電位側電源電位線と p チャネル型トランジスタ 406 の第 1 端子と電気的に接続されており、p チャネル型トランジスタ 406 の第 2 端子と p チャネル型トランジスタ 405 の第 1 端子とが電気的に接続されており、低電位側電源電位 (VSS) を供給する低電位側電源電位線と n チャネル型トランジスタ 403 の第 1 端子および n チャネル型トランジスタ 404 の第 1 の端子とが電気的に接続されており、n チャネル型トランジスタ 403 の第 2 端子と n チャネル型トランジスタ 404 の第 2 端子と p チャネル型トランジスタ 405 の第 2 端子とが電気的に接続されている。

【0204】

次いで、論理回路 410 の NOT 回路の接続関係を記載する。

【0205】

n チャネル型トランジスタ 408 のゲートおよび p チャネル型トランジスタ 409 のゲートと、n チャネル型トランジスタ 403 の第 2 端子および n チャネル型トランジスタ 404 の第 2 端子ならびに p チャネル型トランジスタ 405 の第 2 端子とが電気的に接続されており、高電位側電源電位 (VDD) を供給する高電位側電源電位線と p チャネル型トランジスタ 409 の第 1 端子とが電気的に接続されており、p チャネル型トランジスタ 409 の第 2 端子と n チャネル型トランジスタ 401 の第 1 端子とが電気的に接続されており、低電位側電源電位 (VSS) を供給する低電位側電源電位線と n チャネル型トランジスタ 408 の第 1 端子とが電気的に接続されており、n チャネル型トランジスタ 408 の第 2 端子と n チャネル型トランジスタ 402 の第 1 端子とが電気的に接続されており、n チャネル型トランジスタ 401 の第 2 端子および n チャネル型トランジスタ 402 の第 2 端子と出力電位信号 (OUT) が出力される出力端子 13 とが電気的に接続されている。なお、n チャネル型トランジスタ 401 のゲートおよび n チャネル型トランジスタ 402 のゲートは同電位である。

【0206】

論理回路 410 は、論理回路 400 と同様に n チャネル型トランジスタ 401 および n チャネル型トランジスタ 402 のゲートの電位 が高電位の場合において、従来の OR 回路と同様の演算処理を行う。

【0207】

次に、論理回路 410 の動作中に電源をオフした場合の回路動作について説明する。従

10

20

30

40

50

来のOR回路では、回路動作中に電源をオフした場合、演算処理中のデータは揮発する。

【0208】

一方、論理回路410では、nチャネル型トランジスタ401およびnチャネル型トランジスタ402は極めてオフ電流の低いトランジスタであることから、nチャネル型トランジスタ401およびnチャネル型トランジスタ402のゲートの電位<sub>1</sub>を低電位とした後、電源をオフした場合、nチャネル型トランジスタ401およびnチャネル型トランジスタ402のゲートの電位<sub>1</sub>を低電位としていることで、ノードN\_12をフローティングとすることができるため、該ノードN\_12の電位を保持することができる。なお、ノードN\_12とは、図11において、「N\_12」で指し示す部分を含む太線部である。また、保持ノード（ノードN\_12）に容量素子を設けずとも十分な期間、電位を保持できるが、さらなる保持期間を望む場合は、該保持ノードに一方の電極が電気的に接続され、且つ他方の電極が低電位側電源電位線に電気的に接続された容量素子を設けてもよい。10

【0209】

そして、再度電源をオンした後、nチャネル型トランジスタ401およびnチャネル型トランジスタ402のゲートの電位<sub>1</sub>を高電位にすることで、再度電源をオンした際に入力電位信号を供給する必要が無く、素早く演算処理を再開することができる。また、論理回路410の消費電力を低減することができる。

【0210】

また、上記したようにOR回路は、実施の形態4で説明したNOR回路に実施の形態2で説明したNOT回路を電気的に接続した論理回路であることから、実施の形態4で説明したNOR回路および実施の形態2で説明したNOT回路の様々な形態を適宜組み合わせて、OR回路を構成することができる。例えば、本発明の一態様のOR回路は、実施の形態4で説明した論理回路200乃至論理回路230のいずれか一と從来のNOT回路を電気的に接続したOR回路、または從来のNOR回路と実施の形態2で説明した論理回路50または論理回路55の一方を電気的に接続したOR回路とすることができます。20

【0211】

論理回路400および論理回路410において、nチャネル型トランジスタ401、nチャネル型トランジスタ402は、上記したように極めてオフ電流の低いトランジスタが適用される。該トランジスタは、例えば、実施の形態1で説明したトランジスタ15、実施の形態2で説明したnチャネル型トランジスタ51およびnチャネル型トランジスタ54におけるオフ電流特性を有する。そして、nチャネル型トランジスタ401、nチャネル型トランジスタ402は、nチャネル型トランジスタ51およびnチャネル型トランジスタ54と同様に、酸化物半導体、特に上記水素濃度を有し、キャリアの供与体となる水素を極めて低濃度に低下させた酸化物半導体をチャネル形成領域に適用したトランジスタとすることができます。なお、酸化物半導体中のキャリア濃度についても実施の形態2で説明したnチャネル型トランジスタ51およびnチャネル型トランジスタ54と同様であることが好ましい。30

【0212】

論理回路400および論理回路410において、nチャネル型トランジスタ403、nチャネル型トランジスタ404およびnチャネル型トランジスタ408、ならびにpチャネル型トランジスタ405、pチャネル型トランジスタ406およびpチャネル型トランジスタ409には、特に制限はなく、半導体材料を含む基板を用いて形成されるトランジスタであればよい。40

【0213】

なお、nチャネル型トランジスタ403、nチャネル型トランジスタ404およびnチャネル型トランジスタ408についても、nチャネル型トランジスタ401、nチャネル型トランジスタ402のように、上記水素濃度を有し、キャリアの供与体となる水素を極めて低濃度に低下させた酸化物半導体をチャネル形成領域に適用したトランジスタとすることで、論理回路400および論理回路410の演算処理を行うための消費電力を低減させる効果が大きくなる。50

## 【0214】

本発明の一態様であるO R回路において、論理回路400および論理回路410のように、トランジスタの素子数をできる限り少なくなるように極めてオフ電流が低いトランジスタを配置する回路構成は、トランジスタの占有面積の拡大を最小限にすることができる、微細化の観点から好ましい。また、本発明の一態様であるO R回路において、論理回路410のように、出力端子13と電気的に接続されたノードの電位が保持される回路構成、別言すると演算処理後の電位が保持される回路構成は、論理回路400よりさらに高速に演算処理を再開させることができ、回路動作の高速化の観点から好ましい。

## 【0215】

さらに、本発明の一態様であるO R回路（論理回路400および論理回路410）において、極めてオフ電流の低いトランジスタ以外の構成（従来のO R回路に相当する構成）は、CMOS回路に限定されない。例えば、論理回路50および論理回路55のように、該構成の一部であるpチャネル型トランジスタをn型且つエンハンスマント型トランジスタとしてもよい。該構成の一部であるpチャネル型トランジスタに、n型且つエンハンスマント型トランジスタを適用することで、論理回路400および論理回路410を構成するトランジスタの極性を同じにすることができる。これにより、作製プロセスを低減することができ、論理回路400および論理回路410の歩留まりを向上させ、製造コストを低減させることができる。なお、該n型且つエンハンスマント型トランジスタにおいても、上記水素濃度を有する酸化物半導体でチャネル形成領域を構成するトランジスタとしてもよい。このように、nチャネル型トランジスタのみで構成される論理回路であっても、論理回路400および論理回路410を低消費電力化することができる。

10

## 【0216】

以上より、論理回路400および論理回路410において、消費電力を低減することで、論理回路400および論理回路410の少なくとも一方の論理回路を有する半導体装置の消費電力を低減することができる。さらに、論理回路400および論理回路410の消費電力を低減することで、論理回路400および論理回路410を動作させる外部回路の負荷が低減できる。これにより、論理回路400および論理回路410の少なくとも一方の論理回路および該外部回路を有する半導体装置の機能拡張が可能となる。

20

## 【0217】

なお、本実施の形態の内容または該内容の一部は、他の実施の形態の内容若しくは該内容の一部と自由に組み合わせることが可能である。

30

## 【0218】

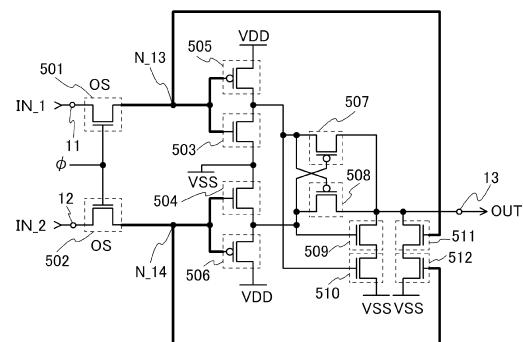

## (実施の形態7)

本実施の形態では、実施の形態1に示した論理回路の一例について説明する。具体的には、XOR回路について図12を用いて説明する。なお、回路図においては、酸化物半導体を用いたトランジスタであることを示すために、点線を用いた回路記号およびOSの符号を併せて付す場合がある。そして、本実施の形態で説明する論理回路は、実施の形態1での説明に用いた符号を適宜使用する。

## 【0219】

## 論理回路の構成例および動作例

40

図12に示す論理回路500はXOR回路に新たにnチャネル型トランジスタを電気的に接続した論理回路である。本実施の形態では、該XOR回路を微細化に好適なCMOS回路による回路構成とするが、該XOR回路を他の抵抗素子やダイオードなどを用いた回路構成としてもよい。なお、図12において、XOR回路には入力端子が2つあるため、一方を第1の入力端子11、もう一方を第2の入力端子12と符号を付する。

## 【0220】

論理回路500は、nチャネル型トランジスタ501、nチャネル型トランジスタ502、nチャネル型トランジスタ503、nチャネル型トランジスタ504、nチャネル型トランジスタ509、nチャネル型トランジスタ510、nチャネル型トランジスタ511、およびnチャネル型トランジスタ512、ならびにpチャネル型トランジスタ505

50

、pチャネル型トランジスタ506、pチャネル型トランジスタ507、およびpチャネル型トランジスタ508を有する。特に、nチャネル型トランジスタ501およびnチャネル型トランジスタ502は極めてオフ電流の低いトランジスタである。

【0221】

論理回路500を構成するトランジスタは、以下の接続関係を有する。

【0222】

第1の入力端子11はnチャネル型トランジスタ501の第1端子と電気的に接続されている。第2の入力端子12はnチャネル型トランジスタ502の第1端子と電気的に接続されている。

【0223】

nチャネル型トランジスタ501の第2端子は、nチャネル型トランジスタ503のゲート、およびnチャネル型トランジスタ511のゲート、ならびにpチャネル型トランジスタ505のゲートと電気的に接続されており、nチャネル型トランジスタ502の第2端子は、nチャネル型トランジスタ504のゲート、およびnチャネル型トランジスタ512のゲート、ならびにpチャネル型トランジスタ506のゲートと電気的に接続されている。

10

【0224】

pチャネル型トランジスタ505の第1端子およびpチャネル型トランジスタ506の第1端子は、高電位側電源電位(VDD)を供給する高電位側電源電位線と電気的に接続されている。pチャネル型トランジスタ505の第2端子は、nチャネル型トランジスタ503の第1端子と電気的に接続されている。pチャネル型トランジスタ506の第2端子はnチャネル型トランジスタ504の第1端子と電気的に接続されている。nチャネル型トランジスタ503の第2端子およびnチャネル型トランジスタ504の第2端子は、低電位側電源電位(VSS)を供給する低電位側電源電位線と電気的に接続されている。

20

【0225】

nチャネル型トランジスタ503の第1端子およびpチャネル型トランジスタ505の第2端子は、pチャネル型トランジスタ508のゲート、およびnチャネル型トランジスタ510のゲート、ならびにpチャネル型トランジスタ507の第1端子と電気的に接続されている。

【0226】

30

nチャネル型トランジスタ504の第1端子およびpチャネル型トランジスタ506の第2端子は、pチャネル型トランジスタ507のゲート、およびnチャネル型トランジスタ509のゲート、ならびにpチャネル型トランジスタ508の第1端子と電気的に接続されている。

【0227】

nチャネル型トランジスタ510の第1端子は、低電位側電源電位(VSS)を供給する低電位側電源電位線と電気的に接続されており、nチャネル型トランジスタ510の第2端子は、nチャネル型トランジスタ509の第1端子と電気的に接続されている。

【0228】

nチャネル型トランジスタ512の第1端子は、低電位側電源電位(VSS)を供給する低電位側電源電位線と電気的に接続されており、nチャネル型トランジスタ512の第2端子は、nチャネル型トランジスタ511の第1端子と電気的に接続されている。

40

【0229】

出力端子13は、pチャネル型トランジスタ507の第2端子、およびpチャネル型トランジスタ508の第2端子、ならびにnチャネル型トランジスタ509の第2端子、およびnチャネル型トランジスタ511の第2端子と電気的に接続されている。

【0230】

なお、nチャネル型トランジスタ501のゲートおよびnチャネル型トランジスタ502のゲートは同電位である。

【0231】

50

論理回路 500 は、n チャネル型トランジスタ 501 および n チャネル型トランジスタ 502 のゲートの電位  $V_{GS}$  が高電位の場合 (n チャネル型トランジスタ 501 および n チャネル型トランジスタ 502 の  $V_{GS}$  が n チャネル型トランジスタ 501 および n チャネル型トランジスタ 502 のしきい値電圧より高い場合) において、従来の XOR 回路と同様の演算処理を行う。例えば、高電位の入力電位信号が第 1 の入力端子 11 および第 2 の入力端子 12 に入力されると、出力端子 13 からは低電位側電源電位 (VSS) である低電位が出力される。また、第 1 の入力端子 11 および第 2 の入力端子 12 のいずれか一方から高電位の入力電位信号が、他方から低電位の入力電位信号が入力されると、出力端子 13 からは高電位側電源電位 (VDD) である高電位が出力される。また、低電位の入力電位信号が第 1 の入力端子 11 および第 2 の入力端子 12 に入力されると、出力端子 13 からは低電位側電源電位 (VSS) である低電位が出力される。

10

#### 【0232】

次に、論理回路 500 の動作中に電源をオフした場合の回路動作について説明する。従来の XOR 回路では、回路動作中に電源をオフした場合、高電位側電源電位 (VDD) と低電位側電源電位 (VSS) に電位差が無くなるため、演算処理中のデータは揮発する。

#### 【0233】

一方、論理回路 500 では、n チャネル型トランジスタ 501 および n チャネル型トランジスタ 502 は極めてオフ電流の低いトランジスタであることから、n チャネル型トランジスタ 501 および n チャネル型トランジスタ 502 のゲートの電位  $V_{GS}$  を低電位 (n チャネル型トランジスタ 501 および n チャネル型トランジスタ 502 のしきい値電圧より低い状態) とした後、電源をオフした場合、n チャネル型トランジスタ 501 および n チャネル型トランジスタ 502 のゲートの電位  $V_{GS}$  を低電位としていることで、ノード N\_13 およびノード N\_14 をフローティングとすることができます。該ノード N\_13 および該ノード N\_14 の電位を保持することができる。なお、ノード N\_13 とは、図 12において、「N\_13」で示される部分を含む太線部であり、ノード N\_14 とは、図 12において、「N\_14」で示される部分を含む太線部である。また、保持ノード (ノード N\_13 およびノード N\_14) に容量素子を設けずとも十分な期間、電位を保持できるが、さらなる保持期間を望む場合は、該保持ノードに一方の電極が電気的に接続され、且つ他方の電極が低電位側電源電位線に電気的に接続された容量素子を設けてもよい。

20

30

#### 【0234】

そして、再度電源をオンした後、n チャネル型トランジスタ 501 および n チャネル型トランジスタ 502 のゲートの電位  $V_{GS}$  を高電位にすることで、ノード N\_13 およびノード N\_14 に保持された電位をもとに演算処理を再開することができる。したがって、再度電源をオンした際に入力電位信号を供給する必要が無く、素早く演算処理を再開することができる。また、論理回路 500 の消費電力を低減することができる。

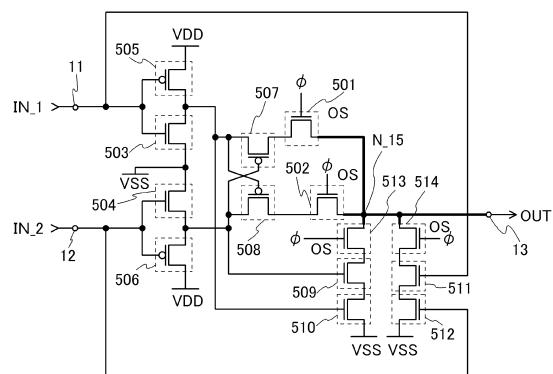

#### 【0235】

また、本実施の形態において、n チャネル型トランジスタ 501 および n チャネル型トランジスタ 502 のように極めてオフ電流の低いトランジスタを配置する箇所は、電源をオフした際に、入力された保持すべき電位を低下させる電流経路 (リーク経路) に配置すれば、論理回路 500 に限定されない。そこで、図 13 に、論理回路 500 とは、極めてオフ電流の低いトランジスタを配置する箇所が異なる論理回路の一例を示す。図 13 は、該一例である論理回路 520 を示す回路図である。なお、論理回路 520 は、図 12 の論理回路 500 に付した符号を適宜用いて説明する。

40

#### 【0236】

論理回路 520 は、n チャネル型トランジスタ 501、n チャネル型トランジスタ 502、n チャネル型トランジスタ 503、n チャネル型トランジスタ 504、n チャネル型トランジスタ 509、n チャネル型トランジスタ 510、n チャネル型トランジスタ 511、n チャネル型トランジスタ 512、n チャネル型トランジスタ 513、および n チャネル型トランジスタ 514、ならびに p チャネル型トランジスタ 505、p チャネル型ト

50

ランジスタ506、pチャネル型トランジスタ507、およびpチャネル型トランジスタ508、を有する。特に、nチャネル型トランジスタ501、nチャネル型トランジスタ502、nチャネル型トランジスタ513およびnチャネル型トランジスタ514は極めてオフ電流の低いトランジスタである。

## 【0237】

論理回路520を構成するトランジスタは、以下の接続関係を有する。

## 【0238】

第1の入力端子11は、nチャネル型トランジスタ503のゲート、およびnチャネル型トランジスタ511のゲート、ならびにpチャネル型トランジスタ505のゲートと電気的に接続されている。第2の入力端子12は、nチャネル型トランジスタ504ゲート、およびnチャネル型トランジスタ512のゲート、ならびにpチャネル型トランジスタ506のゲートと電気的に接続されている。

10

## 【0239】

pチャネル型トランジスタ505の第1端子およびpチャネル型トランジスタ506の第1端子は、高電位側電源電位(VDD)を供給する高電位側電源電位線と電気的に接続されている。pチャネル型トランジスタ505の第2端子は、nチャネル型トランジスタ503の第1端子と電気的に接続されている。pチャネル型トランジスタ506の第2端子はnチャネル型トランジスタ504の第1端子と電気的に接続されている。nチャネル型トランジスタ503の第2端子およびnチャネル型トランジスタ504の第2端子は、低電位側電源電位(VSS)を供給する低電位側電源電位線と電気的に接続されている。

20

## 【0240】

nチャネル型トランジスタ503の第1端子およびpチャネル型トランジスタ505の第2端子は、pチャネル型トランジスタ508のゲート、およびnチャネル型トランジスタ510のゲート、ならびにpチャネル型トランジスタ507の第1端子と電気的に接続されている。

## 【0241】

nチャネル型トランジスタ504の第1端子およびpチャネル型トランジスタ506の第2端子は、pチャネル型トランジスタ507のゲート、およびnチャネル型トランジスタ509のゲート、ならびにpチャネル型トランジスタ508の第1端子と電気的に接続されている。

30

## 【0242】

pチャネル型トランジスタ507の第2端子は、nチャネル型トランジスタ501の第1端子と電気的に接続されている。pチャネル型トランジスタ508の第2端子は、nチャネル型トランジスタ502の第1端子と電気的に接続されている。

## 【0243】

nチャネル型トランジスタ510の第1端子は、低電位側電源電位(VSS)を供給する低電位側電源電位線と電気的に接続されており、nチャネル型トランジスタ510の第2端子は、nチャネル型トランジスタ509の第1端子と電気的に接続されている。nチャネル型トランジスタ509の第2端子は、nチャネル型トランジスタ513の第1端子と電気的に接続されている。

40

## 【0244】

nチャネル型トランジスタ512の第1端子は、低電位側電源電位(VSS)を供給する低電位側電源電位線と電気的に接続されており、nチャネル型トランジスタ512の第2端子は、nチャネル型トランジスタ511の第1端子と電気的に接続されている。nチャネル型トランジスタ511の第2端子は、nチャネル型トランジスタ514の第1端子と電気的に接続されている。

## 【0245】

出力端子13は、nチャネル型トランジスタ501の第2端子、nチャネル型トランジスタ502の第2端子、nチャネル型トランジスタ513の第2端子、およびnチャネル型トランジスタ514の第2端子と電気的に接続されている。

50

## 【0246】

なお、nチャネル型トランジスタ501のゲート、nチャネル型トランジスタ502、nチャネル型トランジスタ513、およびnチャネル型トランジスタ514のゲートは同電位である。

## 【0247】

論理回路520は、論理回路500と同様にnチャネル型トランジスタ501のゲート、nチャネル型トランジスタ502、nチャネル型トランジスタ513、およびnチャネル型トランジスタ514のゲートの電位が高電位の場合において、従来のXOR回路と同様の演算処理を行う。

## 【0248】

次に、論理回路520の動作中に電源をオフした場合の回路動作について説明する。従来のXOR回路では、回路動作中に電源をオフした場合、演算処理中のデータは揮発する。

## 【0249】

一方、論理回路520では、nチャネル型トランジスタ501、nチャネル型トランジスタ502、nチャネル型トランジスタ513、およびnチャネル型トランジスタ514は極めてオフ電流の低いトランジスタであることから、nチャネル型トランジスタ501、nチャネル型トランジスタ502、nチャネル型トランジスタ513およびnチャネル型トランジスタ514のゲートの電位を低電位とした後、電源をオフした場合、nチャネル型トランジスタ501のゲート、nチャネル型トランジスタ502、nチャネル型トランジスタ513、およびnチャネル型トランジスタ514のゲートの電位を低電位としていることで、ノードN\_15をフローティングとすることができるため、該ノードN\_15の電位を保持することができる。なお、ノードN\_15とは、図13において、「N\_15」で指示する部分を含む太線部である。また、保持ノード（ノードN\_15）に容量素子を設けずとも十分な期間、電位を保持できるが、さらなる保持期間を望む場合は、該保持ノードに一方の電極が電気的に接続され、且つ他方の電極が低電位側電源電位線に電気的に接続された容量素子を設けてもよい。

## 【0250】

そして、再度電源をオンした後、nチャネル型トランジスタ501、nチャネル型トランジスタ502、nチャネル型トランジスタ513およびnチャネル型トランジスタ514のゲートの電位を高電位にすることで、再度電源をオンした際に入力電位信号を供給する必要が無く、素早く演算処理を再開することができる。また、論理回路520の消費電力を低減することができる。

## 【0251】

また、本発明の一態様であるXOR回路は、本発明の一態様である論理回路を適宜組み合わせた回路構成にすることができるから、本発明の一態様であるXOR回路は、論理回路500および論理回路520に限定されない。

## 【0252】

論理回路500および論理回路520において、nチャネル型トランジスタ501のゲート、nチャネル型トランジスタ502、nチャネル型トランジスタ513、およびnチャネル型トランジスタ514は、上記したように極めてオフ電流の低いトランジスタが適用される。該トランジスタは、例えば、実施の形態1で説明したトランジスタ15乃至19、実施の形態2で説明したnチャネル型トランジスタ51およびnチャネル型トランジスタ54におけるオフ電流特性を有する。そして、nチャネル型トランジスタ501のゲート、nチャネル型トランジスタ502、nチャネル型トランジスタ513、およびnチャネル型トランジスタ514は、nチャネル型トランジスタ51およびnチャネル型トランジスタ54と同様に、酸化物半導体、特に上記水素濃度を有し、キャリアの供与体となる水素を極めて低濃度に低下させた酸化物半導体をチャネル形成領域に適用したトランジスタとすることができる。なお、酸化物半導体中のキャリア濃度についても実施の形態2で説明したnチャネル型トランジスタ51およびnチャネル型トランジスタ54と同様で

10

20

30

40

50

あることが好ましい。

【0253】

論理回路500および論理回路520において、nチャネル型トランジスタ503、nチャネル型トランジスタ504、nチャネル型トランジスタ509、nチャネル型トランジスタ510、nチャネル型トランジスタ511およびnチャネル型トランジスタ512、ならびにpチャネル型トランジスタ505、pチャネル型トランジスタ506、pチャネル型トランジスタ507およびpチャネル型トランジスタ508には、特に制限はなく、半導体材料を含む基板を用いて形成されるトランジスタであればよい。

【0254】

なお、nチャネル型トランジスタ503、nチャネル型トランジスタ504、nチャネル型トランジスタ509、nチャネル型トランジスタ510、nチャネル型トランジスタ511およびnチャネル型トランジスタ512についても、nチャネル型トランジスタ501、nチャネル型トランジスタ502、nチャネル型トランジスタ513およびnチャネル型トランジスタ514のように、上記水素濃度を有し、キャリアの供与体となる水素を極めて低濃度に低下させた酸化物半導体をチャネル形成領域に適用したトランジスタとすることで、論理回路500および論理回路520の演算処理を行うための消費電力を低減させる効果が大きくなる。

【0255】

本発明の一態様であるXOR回路において、論理回路500のように、トランジスタの素子数をできる限り少なくなるように極めてオフ電流が低いトランジスタを配置する回路構成は、トランジスタの占有面積の拡大を最小限にすることができる、微細化の観点から好ましい。また、本発明の一態様であるXOR回路において、論理回路520のように、出力端子13と電気的に接続されたノードの電位が保持される回路構成、別言すると演算処理後の電位が保持される回路構成は、論理回路500よりもさらに高速に演算処理を再開させることができ、回路動作の高速化の観点から好ましい。

【0256】

さらに、本発明の一態様であるXOR回路（論理回路500および論理回路520）において、極めてオフ電流の低いトランジスタ以外の構成（従来のXOR回路に相当する構成）は、CMOS回路に限定されない。例えば、論理回路50および論理回路55のように、該構成の一部であるpチャネル型トランジスタをn型且つエンハンスマント型トランジスタとしてもよい。該構成の一部であるpチャネル型トランジスタに、n型且つエンハンスマント型トランジスタを適用することで、論理回路500および論理回路520を構成するトランジスタの極性を同じにすることができる。これにより、作製プロセスを低減することができ、論理回路500および論理回路520の歩留まりを向上させ、製造コストを低減させることができる。なお、該n型且つエンハンスマント型トランジスタにおいても、上記水素濃度を有する酸化物半導体でチャネル形成領域を構成するトランジスタとしてもよい。したがって、nチャネル型トランジスタのみで構成される論理回路でありながら、論理回路500および論理回路520を低消費電力化することができる。

【0257】

このように、論理回路500および論理回路520において、消費電力を低減することで、論理回路500および論理回路520の少なくとも一方の論理回路を有する半導体装置の消費電力を低減することができる。さらに、論理回路500および論理回路520の消費電力を低減することで、論理回路500および論理回路520を動作させる外部回路の負荷が低減できる。これにより、論理回路500および論理回路520の少なくとも一方の論理回路および該外部回路を有する半導体装置の機能拡張が可能となる。

【0258】

なお、本実施の形態の内容または該内容の一部は、他の実施の形態の内容若しくは該内容の一部と自由に組み合わせることが可能である。

【0259】

（実施の形態8）

10

20

30

40

50

本実施の形態では、実施の形態1に示した論理回路の一例について説明する。具体的には、X N O R回路について図14を用いて説明する。なお、回路図においては、酸化物半導体を用いたトランジスタであることを示すために、点線を用いた回路記号およびOSの符号を併せて付す場合がある。そして、本実施の形態で説明する論理回路は、実施の形態1での説明に用いた符号を適宜使用する。

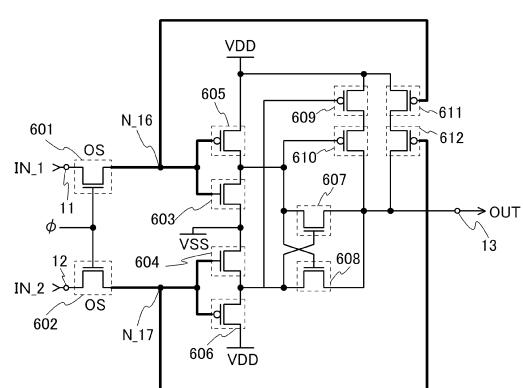

#### 【0260】

##### 論理回路の構成例のおよび動作例

図14に示す論理回路600はX N O R回路に新たにnチャネル型トランジスタを電気的に接続した論理回路である。本実施の形態では、該X N O R回路を微細化に好適なC M OS回路による回路構成とするが、該X N O R回路を他の抵抗素子やダイオードなど用いた回路構成としてもよい。なお、図14において、X N O R回路には入力端子が2つあるため、一方を第1の入力端子11、もう一方を第2の入力端子12と符号を付する。

10

#### 【0261】

論理回路600は、nチャネル型トランジスタ601、nチャネル型トランジスタ602、nチャネル型トランジスタ603、nチャネル型トランジスタ604、nチャネル型トランジスタ607、およびnチャネル型トランジスタ608、ならびにpチャネル型トランジスタ605、pチャネル型トランジスタ606、pチャネル型トランジスタ609、pチャネル型トランジスタ610、pチャネル型トランジスタ611およびpチャネル型トランジスタ612を有する。特に、nチャネル型トランジスタ601およびnチャネル型トランジスタ602は極めてオフ電流の低いトランジスタである。

20

#### 【0262】

論理回路600を構成するトランジスタは、以下の接続関係を有する。

#### 【0263】

第1の入力端子11はnチャネル型トランジスタ601の第1端子と電気的に接続されている。第2の入力端子12はnチャネル型トランジスタ602の第1端子と電気的に接続されている。

#### 【0264】

nチャネル型トランジスタ601の第2端子は、pチャネル型トランジスタ605のゲート、およびpチャネル型トランジスタ611のゲート、ならびにnチャネル型トランジスタ603のゲートと電気的に接続されており、nチャネル型トランジスタ602の第2端子は、pチャネル型トランジスタ606のゲート、およびpチャネル型トランジスタ612のゲート、ならびにnチャネル型トランジスタ604のゲートと電気的に接続されている。

30

#### 【0265】

pチャネル型トランジスタ605の第1端子、およびpチャネル型トランジスタ606の第1端子は、高電位側電源電位(V D D)を供給する高電位側電源電位線と電気的に接続されている。

#### 【0266】

pチャネル型トランジスタ605の第2端子は、nチャネル型トランジスタ603の第1端子と電気的に接続されている。pチャネル型トランジスタ606の第2端子はnチャネル型トランジスタ604の第1端子と電気的に接続されている。nチャネル型トランジスタ603の第2端子およびnチャネル型トランジスタ604の第2端子は、低電位側電源電位(V S S)を供給する低電位側電源電位線と電気的に接続されている。

40

#### 【0267】

nチャネル型トランジスタ603の第1端子およびpチャネル型トランジスタ605の第2端子は、nチャネル型トランジスタ608のゲート、およびnチャネル型トランジスタ607の第1端子、ならびにpチャネル型トランジスタ610のゲートと電気的に接続されている。

#### 【0268】

nチャネル型トランジスタ604の第1端子およびpチャネル型トランジスタ606の

50

第2端子は、nチャネル型トランジスタ607のゲート、およびnチャネル型トランジスタ608の第1端子、ならびにpチャネル型トランジスタ609のゲートと電気的に接続されている。

【0269】

また、pチャネル型トランジスタ609の第1端子およびpチャネル型トランジスタ611の第1端子は、高電位側電源電位(VDD)を供給する高電位側電源電位線と電気的に接続されている。pチャネル型トランジスタ609の第2端子はpチャネル型トランジスタ610の第1端子と電気的に接続されており、pチャネル型トランジスタ611の第2端子はpチャネル型トランジスタ612の第1端子と電気的に接続されている。

【0270】

出力端子13は、nチャネル型トランジスタ607の第2端子、およびnチャネル型トランジスタ608の第2端子、ならびにpチャネル型トランジスタ610の第2端子、およびpチャネル型トランジスタ612の第2端子と電気的に接続されている。

【0271】

なお、nチャネル型トランジスタ601のゲートおよびnチャネル型トランジスタ602のゲートは同電位である。

【0272】

論理回路600は、nチャネル型トランジスタ601およびnチャネル型トランジスタ602のゲートの電位が高電位の場合(nチャネル型トランジスタ601およびnチャネル型トランジスタ602のVgsがnチャネル型トランジスタ601およびnチャネル型トランジスタ602のしきい値電圧より高い場合)において、従来のXNOR回路と同様の演算処理を行う。例えば、高電位の入力電位信号が第1の入力端子11および第2の入力端子12に入力されると、出力端子13からは高電位側電源電位(VDD)である高電位が出力される。また、第1の入力端子11および第2の入力端子12のいずれか一方から高電位の入力電位信号が、他方から低電位の入力電位信号が入力されると、出力端子13からは低電位側電源電位(VSS)である低電位が出力される。また、低電位の入力電位信号が第1の入力端子11および第2の入力端子12に入力されると、出力端子13からは高電位側電源電位(VDD)である高電位が出力される。

【0273】

次に、論理回路600の動作中に電源をオフした場合の回路動作について説明する。従来のXNOR回路では、回路動作中に電源をオフした場合、高電位側電源電位(VDD)と低電位側電源電位(VSS)に電位差が無くなるため、演算処理中のデータは揮発する。

【0274】

一方、論理回路600では、nチャネル型トランジスタ601およびnチャネル型トランジスタ602は極めてオフ電流の低いトランジスタであることから、nチャネル型トランジスタ601およびnチャネル型トランジスタ602のゲートの電位を低電位(nチャネル型トランジスタ601およびnチャネル型トランジスタ602のVgsをnチャネル型トランジスタ601およびnチャネル型トランジスタ602のしきい値電圧より低い状態)とした後、電源をオフした場合、nチャネル型トランジスタ601およびnチャネル型トランジスタ602のゲートの電位を低電位とすることで、ノードN\_16およびノードN\_17をフローティングとすることができます。該ノードN\_16および該ノードN\_17の電位を保持することができる。なお、ノードN\_16とは、図14において、「N\_16」で指し示す部分を含む太線部であり、ノードN\_17とは、図14において、「N\_17」で指し示す部分を含む太線部である。また、保持ノード(ノードN\_16およびノードN\_17)に容量素子を設けずとも十分な期間、電位を保持できるが、さらなる保持期間を望む場合は、該保持ノードに一方の電極が電気的に接続され、且つ他方の電極が低電位側電源電位線に電気的に接続された容量素子を設けてもよい。

【0275】

そして、再度電源をオンした後、nチャネル型トランジスタ601およびnチャネル型

10

20

30

40

50

トランジスタ 602 のゲートの電位 を高電位にすることで、ノード N\_16 およびノード N\_17 に保持された電位をもとに演算処理を再開することができる。したがって、再度電源をオンした際に入力電位信号を供給する必要が無く、素早く演算処理を再開することができる。また、論理回路 600 の消費電力を低減することができる。

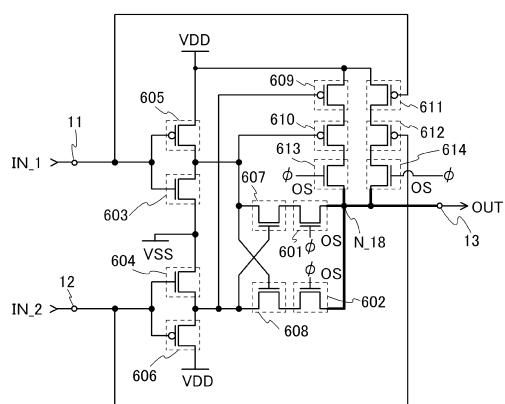

【0276】

また、本実施の形態において、n チャネル型トランジスタ 601 および p チャネル型トランジスタ 602 のように極めてオフ電流の低いトランジスタを配置する箇所は、電源をオフした際に、入力された保持すべき電位を低下させる電流経路（リーコンプル経路）に配置すれば、論理回路 600 に限定されない。そこで、図 15 に、論理回路 600 とは、極めてオフ電流の低いトランジスタを配置する箇所が異なる論理回路の一例を示す。図 15 は、該一例である論理回路 620 を示す回路図である。なお、論理回路 620 は、図 14 の論理回路 600 に付した符号を適宜用いて説明する。

10

【0277】

論理回路 620 は、n チャネル型トランジスタ 601、n チャネル型トランジスタ 602、n チャネル型トランジスタ 603、n チャネル型トランジスタ 604、n チャネル型トランジスタ 607、n チャネル型トランジスタ 608、n チャネル型トランジスタ 613、および n チャネル型トランジスタ 614、ならびに p チャネル型トランジスタ 605、p チャネル型トランジスタ 606、p チャネル型トランジスタ 609、p チャネル型トランジスタ 610、p チャネル型トランジスタ 611、および p チャネル型トランジスタ 612 を有する。特に、n チャネル型トランジスタ 601、n チャネル型トランジスタ 602、n チャネル型トランジスタ 613 および n チャネル型トランジスタ 614 は極めてオフ電流の低いトランジスタである。

20

【0278】

論理回路 620 を構成するトランジスタは、以下の接続関係を有する。

【0279】

第 1 の入力端子 11 は、p チャネル型トランジスタ 605 ゲート、および p チャネル型トランジスタ 611 のゲート、ならびに n チャネル型トランジスタ 603 のゲートと電気的に接続されている。第 2 の入力端子 12 は、p チャネル型トランジスタ 606 ゲート、および p チャネル型トランジスタ 612 のゲート、ならびに n チャネル型トランジスタ 604 のゲートと電気的に接続されている。

30

【0280】

p チャネル型トランジスタ 605 の第 1 端子および p チャネル型トランジスタ 606 の第 1 端子は、高電位側電源電位 (VDD) を供給する高電位側電源電位線と電気的に接続されている。p チャネル型トランジスタ 605 の第 2 端子は、n チャネル型トランジスタ 603 の第 1 端子と電気的に接続されている。p チャネル型トランジスタ 606 の第 2 端子は n チャネル型トランジスタ 604 の第 1 端子と電気的に接続されている。n チャネル型トランジスタ 603 の第 2 端子および n チャネル型トランジスタ 604 の第 2 端子は、低電位側電源電位 (VSS) を供給する低電位側電源電位線と電気的に接続されている。

【0281】

n チャネル型トランジスタ 603 の第 1 端子および p チャネル型トランジスタ 605 の第 2 端子は、n チャネル型トランジスタ 608 のゲート、および n チャネル型トランジスタ 607 の第 1 端子、ならびに p チャネル型トランジスタ 610 のゲートと電気的に接続されている。

40

【0282】

n チャネル型トランジスタ 604 の第 1 端子および p チャネル型トランジスタ 606 の第 2 端子は、n チャネル型トランジスタ 607 のゲート、p チャネル型トランジスタ 609 のゲート、n チャネル型トランジスタ 608 の第 1 端子と電気的に接続されている。

【0283】

n チャネル型トランジスタ 607 の第 2 端子は、n チャネル型トランジスタ 601 の第 1 端子と電気的に接続されている。n チャネル型トランジスタ 608 の第 2 端子は、n チ

50

ヤネル型トランジスタ 602 の第 1 端子と電気的に接続されている。

【0284】

p チャネル型トランジスタ 609 の第 1 端子は、高電位側電源電位 (VDD) を供給する高電位側電源電位線と電気的に接続されており、p チャネル型トランジスタ 609 の第 2 端子は、p チャネル型トランジスタ 610 の第 1 端子と電気的に接続されている。p チャネル型トランジスタ 610 の第 2 端子は、n チャネル型トランジスタ 613 の第 1 端子と電気的に接続されている。

【0285】

p チャネル型トランジスタ 611 の第 1 端子は、高電位側電源電位 (VDD) を供給する高電位側電源電位線と電気的に接続されており、p チャネル型トランジスタ 611 の第 2 端子は、p チャネル型トランジスタ 612 の第 1 端子と電気的に接続されている。p チャネル型トランジスタ 612 の第 2 端子は、n チャネル型トランジスタ 614 の第 1 端子と電気的に接続されている。

10

【0286】

出力端子 13 は、n チャネル型トランジスタ 601 の第 2 端子、n チャネル型トランジスタ 602 の第 2 端子、n チャネル型トランジスタ 613 の第 2 端子、および n チャネル型トランジスタ 614 の第 2 端子と電気的に接続されている。

【0287】

なお、n チャネル型トランジスタ 601 のゲート、n チャネル型トランジスタ 602、n チャネル型トランジスタ 613、および n チャネル型トランジスタ 614 のゲートは同電位である。

20

【0288】

論理回路 620 は、論理回路 600 と同様に n チャネル型トランジスタ 601 のゲート、n チャネル型トランジスタ 602、n チャネル型トランジスタ 613、および n チャネル型トランジスタ 614 のゲートの電位 が高電位の場合において、従来の XNOR 回路と同様の演算処理を行う。

【0289】

次に、論理回路 620 の動作中に電源をオフした場合の回路動作について説明する。従来の XNOR 回路では、回路動作中に電源をオフした場合、演算処理中のデータは揮発する。

30

【0290】

一方、論理回路 620 では、n チャネル型トランジスタ 601 のゲート、n チャネル型トランジスタ 602、n チャネル型トランジスタ 613、および n チャネル型トランジスタ 614 は極めてオフ電流の低いトランジスタであることから、n チャネル型トランジスタ 601、n チャネル型トランジスタ 602、n チャネル型トランジスタ 613 および n チャネル型トランジスタ 614 のゲートの電位 を低電位とした後、電源をオフした場合、n チャネル型トランジスタ 601 のゲート、n チャネル型トランジスタ 602、n チャネル型トランジスタ 613、および n チャネル型トランジスタ 614 のゲートの電位 を低電位とすることで、ノード N\_18 をフローティングとすることができるため、該ノード N\_18 の電位を保持することができる。なお、ノード N\_18 とは、図 15 において、「N\_18」で指し示す部分を含む太線部である。なお、保持ノード (ノード N\_18) に容量素子を設けずとも十分な期間、電位を保持できるが、さらなる保持期間を望む場合は、該保持ノードに一方の電極が電気的に接続され、且つ他方の電極が低電位側電源電位線に電気的に接続された容量素子を設けてよい。

40

【0291】