19 RÉPUBLIQUE FRANÇAISE

**INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE**

PARIS

11 N° de publication :

(à n'utiliser que pour les commandes de reproduction)

**2 533 095**

82 15297

21 N° d'enregistrement national :

51 Int Cl<sup>3</sup> : H 04 L 27/22.

12

## DEMANDE DE BREVET D'INVENTION

A1

22 Date de dépôt : 9 septembre 1982.

30 Priorité

71 Demandeur(s) : AGENCE SPATIALE EUROPEENNE, organisation intergouvernementale. — FR.

④ Date de la mise à disposition du public de la demande : BOPI « Brevets » n° 11 du 16 mars 1984.

60 Références à d'autres documents nationaux appartenants :

72 Inventeur(s) : Gerardus Drewes et Enno Ebels Lijphart.

54 Procédé et dispositif de démodulation d'une onde porteuse modulée en phase par une onde sous-porteuse qui est modulée en déplacement de phase par des signaux en bande de base.

57 L'invention concerne un procédé de démodulation d'une onde porteuse modulée en phase par une onde sous-porteuse qui est modulée en déplacement de phase par des signaux en bande de base.

Le problème technique posé est de réduire la dégradation du signal, et, par suite, la puissance d'émission ou les dimensions de l'antenne de réception.

Selon l'invention, on effectue d'abord un changement de fréquence à une fréquence intermédiaire  $f_c$  inférieure à celle de l'onde porteuse, on effectue une démodulation en phase en vue d'extraire l'onde sous-porteuse en utilisant une boucle de Costas, on effectue un échantillonnage numérique du signal démodulé dans une boucle de Costas à une fréquence double de la fréquence intermédiaire  $f_c$  et on régénère la fréquence d'horloge des éléments binaires  $f_b$  dans une boucle d'asservissement de phase du premier ordre en utilisant la fréquence de l'onde sous-porteuse comme fréquence de référence.

L'invention s'applique en particulier aux transmissions de données entre un engin spatial et une station terrestre.

EB 2 533 095 - A1

"Procédé et dispositif de démodulation d'une onde porteuse modulée en phase par une onde sous-porteuse qui est modulée en déplacement de phase par des signaux en bande de base".

La présente invention concerne les transmissions

5 de signaux numériques par ondes porteuses ; ces transmissions

s'effectuent par exemple entre un engin spatial et une station

terrestre.

Dans le cas d'une transmission de données d'un

10 engin spatial vers une station terrestre, l'information à trans-

mettre est constituée par des données binaires qui ont été pro-

duites par échantillonnage à bord de l'engin spatial et coda-

ge binaire. Le code obtenu qui est désigné sous le terme impropre

15 de modulations par impulsions codées (MIC), peut subir un codage

supplémentaire en vue de la détection et de la correction d'er-

reurs, tel qu'un code récurrent ou un code de Reed-Solomon. Les

codes obtenus sont mis sous forme de code binaire ou "non retour

20 à zéro" (NRZ), ou encore sous forme de code à niveaux de phase

écartés (SP-L) qui a l'avantage d'être un code à auto-synchroni-

sation. On obtient alors des signaux en bande de base qui servent

25 à moduler en phase une onde porteuse (MDP = modulation en déplace-

ment de phase) ; selon cette modulation, une transition du code se

traduit par une inversion de phase de l'onde porteuse ou de la

sous-porteuse. Dans le cas d'une modulation de la sous-porteuse,

la fréquence de cette dernière est cohérente avec le débit numé-

rique. Dans le cas où la sous-porteuse présente un passage à

30 zéro par valeurs croissantes au début de chaque élément binaire,

comme cela est prescrit dans certaines normes de modulation, cette

caractéristique peut être utilisée pour résoudre le problème de

l'ambiguité de la phase de l'onde MDP.

35 L'onde MDP est ensuite soumise à une deuxième

modulation qui, selon la pratique usuelle est une modulation en

phase conventionnelle. Dans le cas où la première modulation en

phase par les signaux en bande de base a été effectuée sur la

porteuse, cette deuxième modulation n'a pas lieu et on a alors af-

faire à une modulation connue sous le nom d'une modulation en

déplacement de phase binaire (MDPB). Enfin, l'onde porteuse à

fréquence radio ainsi modulée peut subir un changement de fréquence à une fréquence supérieure et elle est finalement transmise vers la terre.

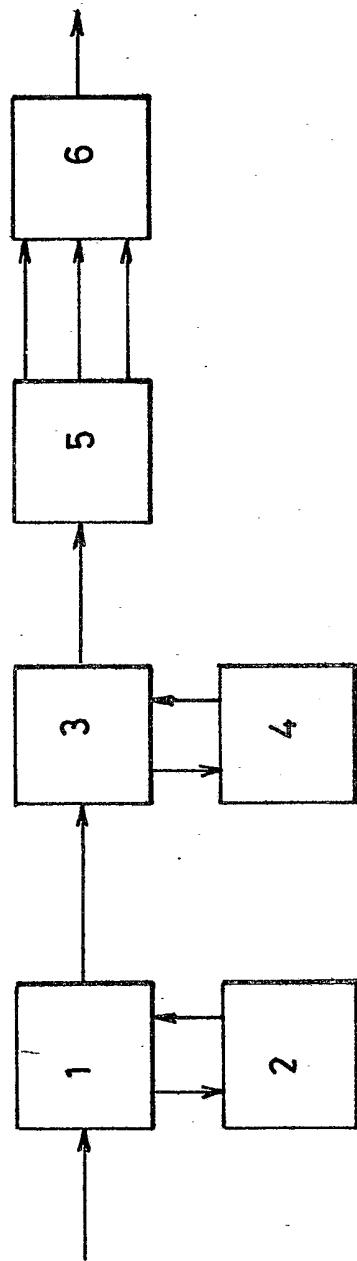

La fig.1 représente un schéma en bloc fonctionnel d'un récepteur classique d'ondes modulées en phase et comportant une sous-porteuse. On effectue essentiellement les opérations inverses de celles de la modulation. Un démodulateur 1 effectue la démodulation en phase des signaux reçus, de manière à fournir la sous-porteuse modulée par la bande de base. Pour assurer une réception en phase de la porteuse, le démodulateur 1 doit pouvoir déterminer ou estimer la phase et la fréquence du signal reçu avec l'erreur la plus faible possible. Ceci peut être réalisé en utilisant un signal de référence qui est dérivé de la composante remanente à la fréquence de la porteuse de l'onde reçue ; cette composante peut être poursuivie en utilisant une boucle d'asservissement de porteuse 2. La sous-porteuse modulée par la bande de base est envoyée sur un deuxième démodulateur 3 qui effectue une démodulation en phase de manière à obtenir les signaux en bande de base ; de manière analogue au premier démodulateur, ce démodulateur 3 comporte des moyens d'asservissement de la sous-porteuse. Du fait qu'une modulation MDP ne laisse pas subsister de composante utilisable de la sous-porteuse, la boucle d'asservissement 4 de la sous-porteuse doit nécessairement être une boucle dans laquelle on effectue une élévation au carré des signaux ou une boucle de Costas.

Dans le cas d'une modulation MDPB, la boucle d'asservissement de la porteuse 2 doit être basée sur le même principe de la boucle à élévation au carré ou la boucle de Costas où l'on peut utiliser une réception du type cohérent. Dans ce cas il n'y a pas de démodulation de la sous-porteuse.

Les signaux en bande de base sont envoyés ensuite dans un synchroniseur primaire 5 qui régénère le signal d'horloge des éléments binaires et produit ainsi les flux d'éléments binaires et une information sur le degré de confiance si l'on a utilisé à l'émission un codage de détection et de correc-

tion d'erreurs: dans le cas où il y a ensuite un décodeur récurrent, ceci est dénommé "décision souple" et est codé sous forme de deux éléments binaires. Enfin, un décodeur 6 reconstitue les données binaires initiales en effectuant un décodage approprié 5 tel qu'un décodage récurrent suivi d'un décodage de Reed-Solomon.

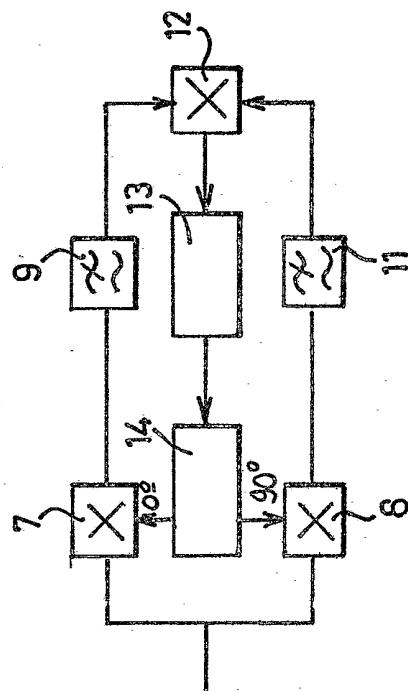

La fig.2 représente le schéma d'un démodulateur en phase, utilisant une boucle de Costas. L'onde à démoduler est envoyée sur deux branches : une branche "données" et une branche "erreurs" comportant chacune un mélangeur ou multiplicateur 7 10 respectivement 8 et un filtre adapté 9 respectivement 11. Les signaux fournis par ces deux branches sont multipliés dans un multiplicateur 12 dont le signal de sortie est filtré dans un filtre de boucle de deuxième ordre 13, le signal filtré constituant le signal de commande de la fréquence d'un oscillateur 15 variable 14 qui fournit une fréquence de référence aux deux multiplicateurs 7 et 8, la fréquence de référence fournie au multiplicateur 8 de la branche "erreurs" étant déphasée de 90°. Dans le cas de la boucle d'asservissement de la sous-porteuse 4 de la fig.1 par exemple, les deux branches "données" et "erreurs" four- 20 nissent des signaux à la fréquence de la bande de base et la branche centrale constituée par les éléments 13 et 14 restitue des signaux à la fréquence de l'onde sous-porteuse.

Un dispositif de démodulation tel que celui schématisé par la fig.1 présente une dégradation de l'information par rapport à ses caractéristiques théoriques : c'est-à-dire que pour une probabilité d'erreurs données, il nécessite un rapport puissance sur bruit plus élevée, la puissance étant la puissance du signal reçu et le bruit étant la densité spectrale du bruit, qu'il soit un bruit blanc ou un bruit de Gauss. De plus ce dispositif 25 présente des effets de seuil dans les boucles d'asservissement de phase, ce qui augmente la dégradation près du seuil.

La nécessité de réduire la dégradation et de diminuer les seuils est accrue lorsque l'on utilise un codage de détection et de correction d'erreurs, du fait que le but réel de 30 ce codage est de réduire l'énergie nécessaire à la réception par 35

élément binaire, c'est-à-dire de réduire la puissance transmise ou les dimensions de l'antenne. Par ailleurs, l'utilisation de ces codes entraîne une augmentation de la largeur du canal, c'est-à-dire une augmentation du débit d'éléments binaires. De ce fait, 5 l'énergie par élément binaire qui doit être démodulée est réduite. Enfin, certains décodeurs de codage de détection et de correction d'erreurs, en particulier les décodeurs récurrents, sont conçus en se basant sur l'hypothèse que les erreurs du code démodulé sont aléatoires, c'est-à-dire qu'elles se conforment à 10 la distribution de Poisson. Cependant, la possibilité accrue d'erreurs résultant de la dégradation n'est généralement pas indépendante du temps mais présente des rafales d'erreurs. Cet effet réduit notablement l'avantage que l'on peut espérer d'un codage de détection et de correction d'erreurs.

15 Les raisons de la dégradation sont liées à la réalisation technologique des récepteurs. C'est ainsi que, par exemple, l'utilisation de filtres à l'entrée des démodulateurs en vue d'améliorer la réponse dynamique du système peut compromettre les caractéristiques voulues des filtres adaptés et créer 20 des variations du temps de propagation de groupe sur tout le spectre, ce qui augmente la dégradation et élève les seuils. Des sautillements des oscillateurs locaux peuvent nécessiter l'utilisation de boucles d'asservissement de phase dont la bande passante est si grande que des données sont poursuivies ; par contre, 25 le sautillage du signal de référence entraîne une dégradation des données. Lorsque l'on utilise une boucle de Costas, généralement les filtres de données des deux branches ne sont pas accordés mais font seulement des approximations du spectre des données. Ceci augmente le sautillage de la sous-porteuse et é- 30 lève le seuil d'acquisition.

35 Un autre inconvénient résulte du fait que les méthodes de poursuite de la sous-porteuse à partir d'un signal modulé biphasé présentent une ambiguïté de phase de  $180^\circ$  qui entraîne une ambiguïté de signe du signal en bande de base. Si l'on se base sur la définition que la sous-porteuse présente un

passage par zéro par valeurs croissantes au début de chaque élément binaire, on peut résoudre cette ambiguïté. Mais ceci n'est pas réalisé avec des démodulateurs de sous-porteuse et des synchroniseurs primaires.

5 Enfin, les dispositifs de démodulation actuels comportent de nombreux composants de technologie analogique tels que les amplificateurs opérationnels. De tels composants analogiques nécessitent un accord fin régulier du fait de la dérive. Cet accord fin ne peut être réalisé que par des utilisateurs

10 très spécialisés et avec des équipements spécialisés et dans la pratique il en résulte une dégradation plus grande et des seuils plus mauvais.

La présente invention a pour objet un procédé de démodulation d'une onde porteuse modulée en phase par une onde sous-porteuse qui est modulée en déplacement de phase par des signaux en bande de base, selon lequel on effectue au moins une démodulation en phase en utilisant une boucle d'asservissement de Costas pour régénérer l'onde de modulation, les signaux en bande de base obtenus étant soumis à un processus d'échantillonnage et de filtrage suivis d'un décodage, procédé qui ne présente pas les inconvénients précités.

Conformément au procédé selon la présente invention, on effectue d'abord un changement de fréquence à une fréquence intermédiaire inférieure à celle de l'onde porteuse, on effectue une démodulation en phase en vue d'extraire l'onde sous-porteuse en utilisant une boucle de Costas dont une partie est réalisée en circuit numérique, dans laquelle la sous-porteuse est régénérée par un synthétiseur de forme d'onde et qui comporte des filtres numériques adaptés, on effectue un échantillonnage numérique du signal démodulé dans la boucle de Costas à une fréquence double de la fréquence intermédiaire et on régénère la fréquence d'horloge des éléments binaires dans une boucle d'asservissement de phase du premier ordre en utilisant la fréquence de l'onde sous-porteuse comme fréquence de référence.

35 L'invention consiste en fait à utiliser une fré-

quence intermédiaire , à inverser la séquence des démodulations des ondes porteuse et sous-porteuse dans la boucle de Costas et à remplacer la démodulation de la porteuse par un échantillonnage numérique du signal démodulé dans la boucle de Costas.

5 Le changement de fréquence à une fréquence intermédiaire permet d'améliorer les performances du démodulateur du fait que le rapport signal-bruit est meilleur à la fréquence intermédiaire, ce qui permet de fournir une composante plus élevée pour la démodulation de la porteuse.L'utilisation de filtres 10 numériques adaptés dans les deux branches de la boucle de Costas améliore le seuil d'acquisition de la sous-porteuse, parce que cela permet d'affranchir les filtres de la dérive et que l'on peut utiliser des filtres à boucle d'asservissement de phase à bande passante très étroite. L'interface entre les signaux analogiques et les signaux numériques est facilement réalisable en 15 utilisant par exemple, des circuits intégrés du type VLSI à très large degré d'intégration.

20 L'utilisation d'une boucle d'asservissement de phase du premier ordre commandée par l'onde sous-porteuse est basée sur le fait que la fréquence de la sous-porteuse et la fréquence d'horloge des éléments binaires sont cohérentes.. On peut, de ce fait, réduire indéfiniment la bande passante de la boucle, ce qui améliore les périodes de saisie de la fréquence 25 d'horloge des éléments binaires.

25 Selon une autre caractéristique de l'invention, la fréquence d'horloge des éléments binaires est obtenue par détermination de sa phase dans une boucle d'asservissement de phase du premier ordre effectuant le produit d'un signal numérique correspondant au début de chaque élément binaire par un signal correspondant au milieu de chaque élément binaire, la fréquence de la sous-porteuse étant divisée par le signal obtenu 30 pour obtenir la fréquence d'horloge des éléments binaires.

35 La détermination de la phase de la fréquence de l'horloge des éléments binaires permet de fournir une information sur l'apparition d'un glissement de la fréquence d'horloge

ce qui évite de recourir au processus de recherche connu sous le nom de "commutation nodale" (node-switching).

5 Selon encore une autre caractéristique de l'invention, le niveau du signal d'entrée de la boucle de Costas est régulé en fonction du niveau du signal numérique de sortie.

Grâce à cette régulation, on peut ajuster le niveau d'entrée de la boucle de Costas de manière à compenser le facteur de modulation.

10 Selon encore une autre caractéristique de l'invention, la forme des ondes de référence fournies par le synthétiseur de forme d'onde est adapté à la forme d'onde du signal d'entrée après sa modification par les caractéristiques du circuit effectuant la démodulation. De cette manière, on adapte au maximum les deux formes d'onde traitées par les circuits démodulateurs, ce qui permet encore d'améliorer le rapport signal sur bruit des données.

20 L'invention a également pour objet un dispositif pour la mise en oeuvre du procédé précité. Dans ce dispositif, chaque branche extérieure, "données" et "erreurs", de la boucle de Costas, comporte, en série à partir de l'entrée du signal modulé, un circuit mélangeur équilibré de démodulation recevant une forme d'onde à la fréquence de l'onde sous-porteuse, un filtre passe-bande, un multiplicateur d'échantillonnage recevant un signal de fréquence double de celle de la fréquence intermédiaire, un convertisseur analogique-numérique et un filtre numérique adapté commandé par la fréquence d'horloge des éléments binaires et dont la sortie est envoyée sur un multiplicateur des signaux "données" et "erreurs".

25 Selon une autre caractéristique du dispositif selon l'invention, la branche centrale de la boucle de Costas comporte, en série à partir du multiplicateur destiné aux "données" et "erreurs" un filtre de boucle du second ordre, un oscillateur à fréquence variable et un synthétiseur de formes d'onde piloté par la fréquence d'horloge des éléments binaires et relié aux deux circuits mélangeurs de démodulation par un convertisseur numérique-analogique. En particulier l'utilisation d'un synthé-

tiseur numérique de formes d'ondes permet d'obtenir toutes les formes d'ondes désirées.

Le dispositif selon l'invention peut également être utilisé pour la démodulation de signaux modulés par déplacement de phase binaire (MDPB). Pour réaliser cette démodulation on supprime la démodulation de la sous-porteuse et on effectue un échantillonnage numérique du signal à une fréquence quadruple de la fréquence intermédiaire.

D'autres caractéristiques et avantages de l'invention ressortiront de la description qui suit, faite à titre illustratif en se référant aux dessins sur lesquels :

- la fig.3 est un schéma-bloc illustrant le principe de l'invention, et

- la fig.4 représente un mode de réalisation de l'invention.

Le signal reçu du véhicule spatial est tout d'abord soumis à un changement de fréquence pour l'amener à une fréquence intermédiaire inférieure à la fréquence de la porteuse initiale. Le signal reçu en 15 (fig.3) est envoyé sur un dispositif de changement de fréquence de type connu 16 qui effectue un changement de fréquence à la fréquence intermédiaire  $f_c$  ; ce dispositif de conversion de fréquence comporte une commande automatique de gain de manière à obtenir un signal calibré en fréquence et en niveau.

Conformément à l'invention, le signal à la fréquence intermédiaire ainsi obtenu est démodulé en phase dans un dispositif de démodulation comportant une boucle de Costas inversée, c'est-à-dire que la séquence de la démodulation des ondes porteuse et sous-porteuse est inversée. La démodulation de la sous-porteuse s'effectue d'abord en utilisant le signal produit par un synthétiseur de formes d'ondes de la sous-porteuse.

Les signaux obtenus après cette démodulation sont filtrés puis échantillonnés à une fréquence double de la fréquence intermédiaire  $f_c$ , ce qui réalise une démodulation de la porteuse. Dans chaque branche extérieure "données" et "erreurs" de la boucle de Costas, les signaux en bande de base ainsi obtenus sont mis sous forme numérique puis filtrés dans un filtre

adapté commandé par la fréquence d'horloge des éléments binaires  $f_B$  ; la multiplication des signaux "données" et des signaux "erreurs" se fait au niveau des signaux binaires en bande de base et sous forme numérique.

5 Le signal correspondant au produit des signaux "données" et "erreurs" commande, après filtrage, le synthétiseur de formes d'onde fournissant les signaux de référence à fréquence de la sous-porteuse pour les éléments effectuant la démodulation de cette dernière.

10 Ce procédé est illustré sur la fig.3 où l'on voit que le signal à fréquence intermédiaire fourni par le circuit 16 est envoyé par l'intermédiaire d'un atténuateur 17 à un ensemble de démodulation 18 qui est, en quelque sorte, une boucle de Costas comportant des éléments supplémentaires. La branche extérieure de 15 "données" comprend un mélangeur 19 recevant une forme d'onde à la fréquence de la sous-porteuse et effectuant la démodulation de cette dernière, un filtre passe-bande 21 passant la composante de la fréquence  $f_c$ , un circuit 22 dans lequel on effectue un échantillonnage avec un signal de référence de fréquence double de la 20 fréquence intermédiaire  $f_c$ , on numérise les signaux obtenus et on additionne et on soustrait les échantillons dans un registre d'intégration et un filtre numérique adapté 23 recevant un signal de référence à la fréquence d'horloge  $f_B$  des éléments binaires. De manière analogue, la branche "erreurs" de la boucle de Costas 25 comprend un mélangeur 24 recevant un signal déphasé de  $90^\circ$  par rapport à celui reçu par le mélangeur 19, un filtre passe-bande 25, un élément de démodulation et de numérisation 26 et un filtre numérique adapté 27 recevant également un signal de référence à la 30 fréquence de l'horloge des éléments binaires. Les deux signaux numériques en base de bande fournis par les deux branches de la boucle de Costas sont multipliés dans le multiplicateur 28 dont le signal de sortie est filtré par un filtre de boucle de second ordre 29 dont la sortie commande un oscillateur à fréquence variable 31 dont la fréquence de sortie  $f_M$  correspond à la fréquence 35 de la sous-porteuse. Le signal de sortie de l'oscillateur variable

31 est envoyé sur un synthétiseur de formes d'ondes 32 qui est piloté par la fréquence d'horloge des éléments binaires  $f_B$ . Une boucle d'asservissement de phase du second ordre 33 reçoit le signal à fréquence intermédiaire et fournit les signaux d'échantillonnage aux circuits de démodulation et de numérisation 22 et 26.

Le synthétiseur de formes d'onde comporte deux mémoires numériques dans lesquelles sont mémorisés des échantillons d'une période de la forme d'onde désirée ; à chaque impulsion d'horloge des éléments binaires, les valeurs suivantes de la forme d'onde sont produites par des convertisseurs numériques-analogiques 34 et 35. Conformément à l'invention, la forme d'onde fournie par le synthétiseur est telle qu'elle s'adapte à la forme d'onde de la sous-porteuse du signal d'entrée lorsqu'elle a été déformée par les caractéristiques de charge du circuit mélangeur de démodulation 19, respectivement 24. Dans le circuit synthétiseur de forme d'onde 32, un passage à zéro par valeurs croissantes correspond à une certaine adresse en mémoire ; on peut noter la valeur de l'adresse présente au début de l'horloge d'éléments binaires et en déterminer la valeur moyenne, afin de résoudre le problème de l'ambiguité de phase pour les modulations de phase simples (MDPB). Les signaux numériques en bande de base "données" obtenus à la sortie du filtre numérique adapté 23 sont traités de la manière suivante. Ils sont échantillonnés à la fin de chaque élément binaire et envoyés dans un circuit 36 de recodage de "décision souple" qui fournit le flux de données binaires. Par ailleurs, on peut calculer la valeur moyenne de la valeur absolue du signal sortant du filtre 23, cette moyenne s'effectuant sur plusieurs éléments binaires. Cette valeur moyenne est proportionnelle au niveau du signal de sortie de l'atténuateur 17, on peut le filtrer par un circuit numérique constituant une réplique d'un filtre RC. Le signal ainsi produit par un circuit 37 sert à commander l'atténuateur variable 17 de manière à stabiliser le niveau du signal d'entrée de la boucle de Costas.

Dans un troisième circuit 38, on élève le signal

de sortie du filtre 23 au carré et on l'additionne à une somme de carrés. A des intervalles réguliers, ce circuit 38 calcule la valeur

$$M_2 = \langle B^2 \rangle - \langle |B| \rangle^2$$

5 de laquelle découle la probabilité d'erreurs sur les éléments binaires si l'on suppose que l'on a affaire à un bruit distribué selon la loi de Gauss. On obtient alors à la sortie du circuit 38 une information représentative de la marge de liaison.

10 Selon l'invention, on régénère la fréquence d'horloge des éléments binaires qui est nécessaire pour lever l'ambiguité de phase dans les systèmes de modulation de phase simple (MDPB), et pour piloter les filtres numériques adaptés 23 et 27. Cette régénération de la fréquence d'horloge se fait en utilisant la fréquence  $f_M$  fournie par l'oscillateur 31 comme fréquence de référence, la fréquence d'horloge des éléments binaires  $f_B$  étant obtenue par division de la fréquence de cet oscillateur 31 par un nombre entier connu. La fréquence d'horloge qui est obtenue sert à piloter le synthétiseur d'ondes 32 et les filtres adaptés 23 et 27.

20 Du fait de la cohérence de la fréquence de la sous-porteuse  $f_C$  et de la fréquence d'horloge  $f_B$ , le circuit de régénération de la fréquence d'horloge ne doit simplement qu'ajuster la phase de cette fréquence d'horloge. Cette détermination de la phase de la fréquence d'horloge est réalisée dans une boucle d'asservissement de phase du premier ordre dans laquelle on effectue le produit d'un signal numérique correspondant à la fin de chaque élément binaire par un signal numérique correspondant au milieu de chaque élément binaire. A cet effet, ladite boucle comporte deux filtres adaptés recevant deux ondes déphasées de 180°.

25 Avantageusement, selon l'invention, ladite boucle de régénération de la phase de la fréquence d'horloge utilise un des éléments de la boucle de Costas qui vient d'être décrite, à savoir le filtre adapté 23 de la branche extérieure de "données" 35 de la boucle de Costas ; cette boucle de régénération de la phase du circuit d'horloge comporte un autre filtre semblable 39 qui reçoit une onde à la fréquence des éléments d'horloge qui est déphasée de 180° par rapport à celle envoyée sur le filtre 23.

Le détecteur de phase de la fréquence d'horloge 41 reçoit donc deux signaux filtrés dont l'un est échantillonné à la fin de chaque élément binaire et l'autre au milieu de chaque élément binaire. Ces deux signaux sont multipliés pour chaque 5 nouvel échantillon, c'est-à-dire deux fois par période d'horloge. Le produit effectué à la fin de chaque élément binaire est additionné à une somme courante et le produit effectué au milieu de chaque élément binaire est soustrait de cette somme courante.

10 Lorsque les instants d'échantillonnage sont avancés ou retardés par rapport aux transitions d'éléments binaires, cette somme augmente ou diminue. Lorsque l'on atteint un seuil élevé ou bas, la fréquence d'horloge est décalée d'un incrément, par exemple une période de la fréquence du signal créé par l'oscillateur 31 et le registre de sommation est remis à zéro.

15 La boucle d'asservissement de phase ainsi constituée est du premier ordre. Après acquisition, sa réponse peut être réduite indéfiniment en augmentant les seuils du fait que la fréquence d'horloge sera toujours poursuivie par la fréquence esclave de la sous-porteuse, la fréquence maître étant 20 celle délivrée par l'oscillateur 31. Il en résulte qu'une boucle d'asservissement de phase du premier ordre ne peut pas devenir instable en l'absence du signal.

La régénération de la fréquence d'horloge est réalisée dans un circuit 42 contenant le registre somme précité et 25 un circuit diviseur recevant la fréquence maître délivrée par l'oscillateur 31 et fournissant la fréquence d'horloge qui est envoyée d'une part au synthétiseur 32 et, d'autre part, aux trois filtres adaptés 23, 27 et 39.

30 Un signal de sortie du circuit de détection de phase de la fréquence d'horloge 41 est également utilisé pour fournir une information sur la stabilité de la fréquence d'horloge. A cet effet, un circuit 43 effectue l'intégration du signal de sortie du circuit 41 en vue de fournir éventuellement une information indiquant un glissement de la fréquence d'horloge.

35 On peut appliquer deux algorithmes aux filtres adapt

23, 27 et 39 selon l'application du démodulateur. Le premier algorithme simule une sortie continue en fournissant pour chaque échantillon  $i = S_i$  la valeur  $H_i = \sum_{j=i-N}^i S_j$

5 dans laquelle  $N$  est égal au nombre d'échantillons par élément binaire. Ce signal est obtenu avec une puissance de traitement réduite, en ajoutant l'échantillon  $i$  et en soustrayant l'échantillon  $i - N$  d'un résultat courant :

$$H_i = H_{i-1} + S_i - S_{i-N}$$

10 Le filtre est alors adapté à un format de modulation par impulsions codées (MIC) à onde carrée et il fournit la meilleure évaluation d'éléments binaires lorsqu'il est échantillonné à la fin d'une période d'élément binaire.

15 Le second algorithme simule le filtre d'intégration, échantillonnage et remise à zéro en produisant pour chaque élément binaire :

$$H = \sum_{j=1}^N S_j$$

20 Le premier algorithme rend la boucle de Costas indépendante de l'acquisition du signal d'horloge ; cependant, les paramètres de la boucle seront quelque peu dépendants de la densité de transition (la fréquence naturelle et le facteur d'amortissement sont multipliés par  $\sqrt{3}$  lorsque la densité de transition passe de zéro à 100%).

25 Le deuxième algorithme rend la boucle de Costas dépendante d'asservissement de la fréquence d'horloge, ce qui, dans certaines conditions, peut retarder l'acquisition. Mais, quand le verrouillage est obtenu, la boucle de Costas est indépendante de la densité de transition. Ainsi, une petite variation de cet algorithme permet de pondérer les différents échantillons.

$$H = \sum_{j=1}^N w_j S_j$$

30 afin d'adapter le filtre à un format de modulation par impulsions codées (MIC) à onde non carrée, c'est-à-dire lorsque l'on utilise les systèmes de modulation par déplacement minimal.

Une telle pondération est en principe également possible pour un filtre quasi continu mais ceci augmente notablement le traitement nécessaire.

Si les données MIC sont codées selon le code à 5 phases écartées, les filtres adaptés sont alors adaptés à une valeur seulement égale à la moitié de la période d'horloge. On obtient une adaptation au format à phases écartées en fixant un débit double dans les filtres adaptés et dans l'acquisition de la fréquence d'horloge. Les moitiés d'éléments binaires que l'on 10 obtient alors sont combinées par paires dans un décodeur à phases écartées 44 recevant les signaux fournis par la boucle de Costas et on obtient la sortie en non retour à zéro (NRZ-L) en utilisant l'algorithme approprié au code à phases écartées spécifique utilisé (L, M, ou 15 S) en résolvant alors l'ambiguité de phase à partir des statistiques des résultats.

Dans le cas spécifique du code à niveaux de phase écartés (SP-L) le traitement peut également être réalisé en multipliant le signal numérisé à la sortie des circuits 22 et 26 par le signal d'horloge en ondes carrées.

20 Dans les deux cas, le seuil d'acquisition de la boucle de Costas sera plus élevé de 3 dB que pour le code NRZ.

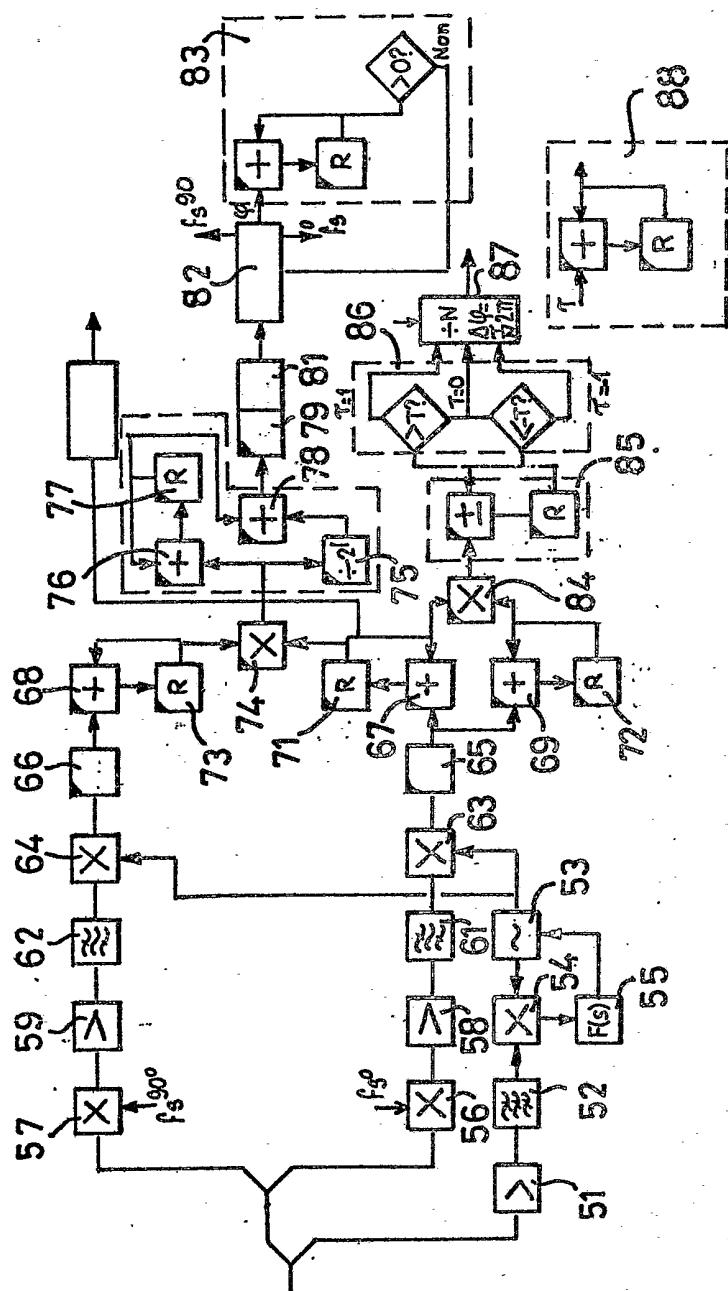

La fig.4 est un schéma bloc montrant un mode de réalisation de l'invention qui a été utilisé en tant que prototype et donne des détails sur une possibilité de réalisation pratique de l'invention sous forme modulaire, certains éléments du schéma de la fig.3 n'ayant pas été réalisés dans ce prototype.

La boucle d'asservissement de phase de poursuite de l'onde porteuse 33 du schéma de la fig.3, est constituée par 30 un amplificateur 51, un filtre à bande étroite 52 et une boucle d'asservissement de phase directe du second ordre constitué par un oscillateur commandé en tension à cristal 53, un multiplicateur 54 et un filtre de boucle 55.

Chaque branche extérieure de la boucle de Costas 35 comporte successivement un multiplicateur de la sous-porteuse 56, respectivement 57, constitué par un mélangeur équilibré, un am-

plificateur 58, respectivement 59, un filtre passe-bande 61, respectivement 62, un multiplicateur de la porteuse 63, respectivement 64 et un module de numérisation constitué par un convertisseur analogique-numérique 65, respectivement 66. Les filtres adaptés sont constitués chacun d'un additionneur 67, respectivement 68 et 69 associés à un registre 71, respectivement 72 et 73, de manière à constituer un module somme-dans-registre réalisant la fonction d'intégration, échantillonnage et remise à zéro. Les signaux fournis par les deux branches de la boucle de Costas sont envoyés sur un module multiplicateur constitué par un circuit intégré à très grand degré d'intégration (VLSI) 74.

Le signal fourni par ce multiplicateur 74 est envoyé sur un filtre de boucle du deuxième ordre comportant un intégrateur et un additionneur accéléré et constitué par diviseur par  $2^{1/2}$  d'une part, et un additionneur 76 associé à un registre 77 d'autre part, les signaux obtenus étant envoyés sur un additionneur 78. Le signal de sortie de cet additionneur est envoyé sur un convertisseur numérique-analogique 79, suivi d'un oscillateur commandé en tension à cristal 81 dont le signal de sortie est envoyé sur le synthétiseur de forme d'onde 82 qui comporte un dispositif de comparaison de la polarité de la phase numérique 83 qui renvoie une commande d'inversion de phase au synthétiseur 82 si le signal d'horloge des éléments binaires se trouve à un passage à zéro par valeurs décroissantes.

L'ensemble d'acquisition de l'horloge des éléments binaires comporte le filtre adapté constitué par les éléments 69 et 72, un multiplicateur 84, un ensemble comparateur de phases d'horloge et intégrateur 85, un ensemble de détection de seuils 86 et un diviseur 87 correspondant au diviseur 42 de la fig.3 et fournissant le signal d'horloge. Le circuit de détection de dérive du signal d'horloge 88 a été représenté séparément.

Le modulateur prototype représenté à la fig.4 a été essayé en même temps qu'un récepteur typique à asservissement de phase. Les résultats peuvent être résumés de la manière suivante.

La dégradation étant inférieure à 0,5 dB pour un rapport énergie par élément binaire sur bruit entre -2 dB et 10 dB

5 Le seuil d'acquisition est inférieur à 16 dB dans la boucle de Costas, ce qui correspond à un rapport énergie par élément binaire sur bruit inférieur à -4 dB.

La description ci-dessus n'est fournie qu'à titre d'exemple nullement limitatif et il est évident que l'on peut y apporter des modifications ou variantes sans sortir pour autant du cadre de la présente invention.

10 C'est ainsi que tous les traitements numériques peuvent être réalisés par un ou plusieurs processeurs en tranches en fonction de la vitesse de traitement désirée. Si on se réfère à la fig.3, certaines fonctions resteraient alors réalisées selon la technologie à fréquence intermédiaire ; il s'agit de la 15 boucle d'asservissement de phase 33, de l'atténuateur 16, des multiplicateurs 19 et 24, des filtres analogiques 21 et 25 et, éventuellement, de l'oscillateur à fréquence variable 31. Les échantillonneurs démodulateurs de la porteuse 22 et 26 peuvent alors constituer un sous ensemble spécial.

20 Toutes les autres fonctions numériques peuvent être réalisées dans une simple configuration de micro-ordinateur comportant des interfaces analogiques-numériques si le débit des "données" le permet.

25 Pour des débits de données très élevés, on peut enfin prévoir un processeur pour chaque fonction en prévoyant des modules de fonction selon la technique intégrée à grand degré d'intégration (VLSI) dans les endroits où le flot de "données" peut se heurter à un étranglement, par exemple dans les multiplicateurs.

REVENDICATIONS

1°) Procédé de démodulation d'une onde porteuse modulée en phase par une onde sous-porteuse qui est modulée en déplacement de phase par des signaux en bande de base, selon 5 lequel on effectue au moins une démodulation en phase en utilisant une boucle d'asservissement de Costas pour régénérer l'onde de modulation, les signaux en bande de base obtenus étant tous ensuite soumis à un processus d'échantillonage suivi d'un décodage, caractérisé en ce que l'on effectue d'abord un changement 10 de fréquence à une fréquence intermédiaire  $f_C$  inférieure à celle de l'onde porteuse, on effectue une démodulation en phase en vue d'extraire l'onde sous-porteuse en utilisant une boucle de Costas dont une partie est réalisée en circuit numérique, dans laquelle 15 la sous-porteuse est régénérée par un synthétiseur de forme d'cn- de et qui comporte des filtres numériques adaptés, on effectue un échantillonage numérique du signal démodulé dans la boucle de Costas à une fréquence double de la fréquence intermédiaire  $f_C$  et on régénère la fréquence d'horloge des éléments binaires  $f_B$  dans une boucle d'asservissement de phase du premier ordre en 20 utilisant la fréquence de l'onde sous-porteuse comme fréquence de référence.

2°) Procédé selon la revendication 1, caractérisé en ce que la fréquence d'horloge des éléments binaires  $f_B$  est obtenue par détermination de sa phase dans une boucle d'asservissement de phase du premier ordre effectuant le produit 25 d'un signal numérique correspondant à la fin de chaque élément binaire par un signal correspondant au milieu de chaque élément binaire, la fréquence de la sous-porteuse étant divisée par le signal obtenu pour obtenir la fréquence d'horloge des éléments binaires.

3°) Procédé selon l'une quelconque des revendications 1 et 2, caractérisé en ce que le niveau du signal d'entrée de la boucle de Costas est régulé en fonction du signal numérique de sortie.

4°) Procédé selon la revendication 2, caractérisé en ce que le signal correspondant à la phase de la fréquence d'horloge des signaux binaires est intégré de manière à obtenir un signal représentatif du glissement de la fréquence d'horloge des éléments binaires.

5 5°) Procédé selon l'une quelconque des revendications 1 à 4, caractérisé en ce que la forme de l'onde à la fréquence de l'onde sous-porteuse fournie par le synthétiseur de forme d'onde est adaptée à la forme d'onde du signal d'entrée à fréquence intermédiaire modifiée par les caractéristiques du circuit effectuant la démodulation.

10 6°) Procédé selon l'une quelconque des revendications 1 à 5, caractérisé en ce que le signal de sortie échantillonné à la fin de chaque élément binaire est élevé au carré et ajouté à une somme de carrés, de manière à calculer la probabilité 15 d'erreurs sur les éléments binaires.

20 7°) Procédé selon l'une quelconque des revendications 1 à 6, caractérisé en ce que la démodulation de la sous-porteuse est supprimée et en ce que la démodulation de la porteuse est effectuée par échantillonnage du signal à une fréquence égale à quatre fois la fréquence intermédiaire de manière à démoduler les signaux modulés par déplacement de phase binaire.

25 8°) Dispositif de démodulation pour la mise en oeuvre du procédé selon l'une des revendications 1 à 7, caractérisé en ce que chaque branche extérieure, "données" et "erreurs" de la boucle de Costas comporte en série, à partir du signal modulé, un circuit mélangeur de démodulation (19, 21, 56, 57) recevant une forme d'onde à la fréquence de l'onde sous-porteuse, un filtre passe-bande (21, 25, 61, 62), un multiplicateur d'échantillonnage (22, 30 26, 63, 64) recevant un signal de fréquence double de celle de la fréquence intermédiaire  $f_C$ , un convertisseur analogique-numérique (65, 66) et un filtre numérique adapté (23, 27, 67, 68, 71, 73) commandé par la fréquence d'horloge des éléments binaires et dont la sortie est envoyée sur un multiplicateur de signaux "données" et "erreurs"

- 9°) Dispositif selon la revendication 8, caractérisé en ce que la branche centrale de la boucle de Costas comporte, en série à partir du multiplicateur (28,74) des signaux "données" et "erreurs", un filtre de boucle du second ordre, (29, 5 75,76,77) un oscillateur à fréquence variable (31,81) et un synthétiseur de forme d'onde (32,82) piloté par la fréquence d'horloge des éléments binaires et relié aux deux circuits mélangeurs de démodulation (19,24,56,57) par un convertisseur numérique-analogique (34,55).

- 10 10°) Dispositif selon la revendication 9, caractérisé en ce que le synthétiseur de forme d'onde (31,81) comprend deux mémoires numériques dans chacune desquelles est enregistré un cycle de forme d'onde.

- 11°) Dispositif selon l'une des revendications 15 8 à 10, caractérisé en ce qu'il comporte une boucle de réaction à verrouillage de phase du second ordre (33,53,54,55) recevant le signal d'entrée à fréquence intermédiaire  $F_c$  et fournissant un signal à fréquence intermédiaire.

- 12°) Dispositif selon l'une des revendications 20 8 à 11, caractérisé en ce qu'il comporte un atténuateur variable (17) disposé à l'entrée de la boucle de Costas et commandé par un circuit numérique (37) qui est analogue à un filtre analogique en RC et qui fournit une valeur moyenne des signaux binaires de sortie.

- 13°) Dispositif selon l'une des revendications 25 8 à 12, caractérisé en ce que la boucle de réaction à verrouillage de phase du premier ordre servant à régénérer la fréquence de l'horloge des éléments binaires, comporte deux branches comportant chacune un filtre numérique adapté (23,36,67,71,69,72) 30 commandé par la fréquence d'horloge des éléments binaires, l'un desdits filtres étant le filtre (23,67,71) de la branche "données" de la boucle de Costas, et l'autre filtre (39,69,72) étant commandé par une onde en opposition de phase par rapport à celle commandant le filtre (23,67,71) de la boucle de Costas.

14°) Dispositif selon l'une des revendications 8 à 13, caractérisé en ce que les filtres numériques adaptés de la boucle de Costas et de la boucle de régénération de la fréquence d'horloge (23, 27, 39, 68, 73, 67, 71, 69, 72) sont constitués par 5 des modules somme-dans registre.

15°) Dispositif pour la mise en oeuvre du procédé selon l'une des revendications 1 à 7, caractérisé en ce qu'il comporte au moins un processeur du type à fonctionnement en tranches qui exécute au moins une partie des fonctions numériques du 10 procédé, les éléments fonctionnels analogiques étant réalisés selon la technologie dite à fonction intégrée.

16°) Dispositif selon la revendication 15, caractérisé par le fait que le processeur précité est constitué par un microprocesseur et en ce que les éléments fonctionnels numériques à fort débit d'éléments binaires sont réalisés séparément 15 selon la technique des circuits intégrés à très grand degré d'intégration (VLSI).

FIG.1FIG.2

FIG.3

3/3

FIG. 4