# (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.) *H01L 27/102* (2006.01)

(21) 출원번호 **10-2009-7019777**

(22) 출원일자(국제) **2008년03월26일** 심사청구일자 **2012년11월23일**

(85) 번역문제출일자 **2009년09월22일**

(65) 공개번호 10-2010-0014528

(43) 공개일자 **2010년02월10일**

(86) 국제출원번호 PCT/US2008/003975

(87) 국제공개번호 **WO 2009/008919** 국제공개일자 **2009년01월15일**

(30) 우선권주장

11/692,151 2007년03월27일 미국(US) 11/692,153 2007년03월27일 미국(US)

(56) 선행기술조사문헌

US20050052915 A1\*

US20050226067 A1\*

\*는 심사관에 의하여 인용된 문헌

(45) 공고일자 2015년05월07일

(11) 등록번호 10-1517913

(24) 등록일자 2015년04월29일

(73) 특허권자

#### 쌘디스크 3디 엘엘씨

미국, 캘리포니아 95035-7933, 밀피타스, 쌘디스 크 드라이브 951

(72) 발명자

### 허너, 에스., 브래드

미국, 캘리포니아 95125, 산 호세, 밀드레드 애비 뉴 1289

(74) 대리인 **박경재**

전체 청구항 수 : 총 40 항

심사관 : 임동재

(54) 발명의 명칭 크고 균일한 전류를 갖는 상향 지향 P-I-N 다이오드의 대형 어레이와 이를 포함하는 디바이스, 이를 형성하는 방법, 수직 배향 P-I-N 다이오드 및 단일체형 3차원 메모리 어레이의 형성 방법

# (57) 요 약

증착된 실리콘, 게르마늄 또는 실리콘-게르마늄으로 형성된 상향 지향 p-i-n 다이오드가 개시되어 있다. 다이오드는 저부 고 도핑 p-형 영역과, 중간 진성 또는 경 도핑 영역과, 상부 고 도핑 n-형 영역을 갖는다. 상부 고 도핑 p-형 영역은 비소로 도핑되고, 다이오드의 반도체 재료는 적절한 실리사이드, 게르마나이드 또는 실리사이드-게르마나이드와 접촉하여 결정화된다. 이런 상향 지향 다이오드의 대규모 어레이는 다이오드의 턴-온 전압보다 높은 전압이 인가될 때 어레이를 가로지른 전류의 양호한 균일성을 갖고 형성될 수 있다. 이 다이오드는 단일체형 3차원 메모리 어레이에 사용되는 것이 바람직하다. 상향 지향 p-i-n- 다이오드의 개체군을 형성하는 방법 및기타 실시예들도 설명되어 있다.

### 대 표 도 - 도5

### 명세서

### 청구범위

#### 청구항 1

기판 위에 형성된 복수의 수직 배향 p-i-n 다이오드들을 포함하며, 각 p-i-n 다이오드는 저부 고 도핑 p-형 영역(bottom heavily doped p-type region)과, 중간 진성 또는 경 도핑 영역(lightly doped region)과, 비소로 도핑된 상부 고 도핑 n-형 영역을 포함하는 제 1 디바이스 레벨(device level);

을 포함하고,

각 p-i-n 다이오드는 기둥(pillar) 형태를 가지며, 상기 p-i-n 다이오드들은 중착된 실리콘, 게르마늄 또는 실리콘-게르마늄을 포함하고, 상기 복수의 p-i-n 다이오드들은 상기 제 1 디바이스 레벨 내의 모든 p-i-n 다이오드를 포함하며,

각 다이오드의 상부 고 도핑 n-형 영역은 실리사이드(silicide), 게르마나이드 (germanide) 또는 실리사이드-게르마나이드(silicide-germanide) 층과 접촉하고,

상기 p-i-n 다이오드들의 99% 이상에 대하여, 저부 고 도핑 p-형 영역과 상부 고 도핑 n-형 영역 사이에 1.5V 내지 3.0V의 전압이 인가될 때, 상기 p-i-n 다이오드들을 통해 흐르는 전류는 1.5 마이크로 암페어(microamps) 이상 인, 디바이스.

#### 청구항 2

제 1항에 있어서, 상기 저부 고 도핑 p-형 영역과 상기 상부 고 도핑 n-형 영역 사이에 인가된 전압이 1.8V 내지 2.2V 일 때, 전류가 상기 p-i-n 다이오드들을 통해 흐르는, 디바이스.

#### 청구항 3

삭제

### 청구항 4

제 1항에 있어서, 상기 기판 위에 형성된 평행하고, 동일 평면인 레일형의 복수의 제 1 전도체들;

상기 제 1 전도체들 위에 형성된 평행하고, 동일 평면인 레일형의 복수의 제 2 전도체들을 더 포함하고,

각각의 p-i-n 다이오드는 상기 제 1 전도체들 중 하나와 상기 제 2 전도체들 중 하나 사이에 수직 방향으로 배치되는, 디바이스.

# 청구항 5

제 4항에 있어서, 상기 복수의 수직 배향 p-i-n 다이오드들은 10 0,000개 이상의 p-i-n 다이오드들을 포함하는, 디바이스.

# 청구항 6

제 1항에 있어서, 상기 제 1 디바이스 레벨 위에 단일체형으로 형성된 제 2 디바이스 레벨을 추가로 포함하는, 디바이스.

#### 청구항 7

제 1항에 있어서, 상기 기판은 단결정 실리콘을 포함하는, 디바이스.

### 청구항 8

복수의 메모리 셀들을 포함하는 제 1 메모리 레벨로서, 각각의 메모리 셀은 기둥 형태의 수직 배향 p-i-n 다이오드를 포함하고, 각각의 수직 배향 p-i-n 다이오드는 저부 고 도핑 p-형 영역과, 중간 진성 또는 경 도핑 영역과, 비소로 도핑된 상부 고 도핑 n-형 영역을 포함하며, 각각의 수직 배향 p-i-n 다이오드는 중착된 실리콘, 게르마늄 또는 실리콘-게르마늄을 포함하고, 각각의 수직 배향 p-i-n 다이오드의 상부 고 도핑 n-형 영역은 실리

사이드(silicide), 게르마나이드(germanide) 또는 실리사이드-게르마나이드(silicide-germanide) 층과 접촉하는 제 1 메모리 레벨;

을 포함하며,

상기 메모리 셀들은 프로그램 셀들 및 미프로그램 셀들을 포함하고,

상기 메모리 셀들의 절반 이상은 프로그램 셀들이며,

1.5V 내지 3.0V의 전압이 상기 저부 고 도핑 p-형 영역과 상기 상부 고 도핑 n-형 영역 사이에 인가될 때, 상기 프로그램 셀들의 99% 이상의 상기 p-i-n 다이오드들을 통해 흐르는 전류가 1.5 마이크로 암페어(microamps) 이 상이며,

상기 복수의 메모리 셀들은 상기 제 1 메모리 레벨에서의 모든 메모리 셀을 포함하는, 디바이스.

#### 청구항 9

제 8항에 있어서, 상기 저부 고 도핑 p-형 영역과 상기 상부 고 도핑 n-형 영역 사이에 인가된 전압이 1.8V 내지 2.2V 일 때, 전류가 상기 p-i-n 다이오드들을 통해 흐르는, 디바이스.

### 청구항 10

삭제

### 청구항 11

제 8항에 있어서, 기판 위에 형성된 평행하고, 동일 평면인 레일형의 복수의 제 1 전도체들과,

상기 제 1 전도체들 위에 형성된 평행하고, 동일 평면인 레일형의 복수의 제 2 전도체들을

더 포함하고,

각각의 수직 배향 p-i-n 다이오드는 상기 제 1 전도체들 중 하나와 상기 제 2 전도체들 중 하나 사이에 수직방 향으로 배치되는, 디바이스.

# 청구항 12

제 11항에 있어서, 각각의 메모리 셀은 상태-변화 요소를 더 포함하는, 디바이스.

# 청구항 13

제 12항에 있어서, 상기 상태-변화 요소는 안티퓨즈이고, 각각의 제 1 메모리 셀은 1회 프로그램 가능한 메모리셀인, 디바이스.

### 청구항 14

제 13항에 있어서, 상기 안티퓨즈는 유전체 층 또는 유전체 스택인, 디바이스.

#### 청구항 15

제 12항에 있어서, 상기 상태-변화 요소는 저항성-스위칭 소자이고, 각각의 메모리 셀은 재기록 가능한 메모리 셀인, 디바이스.

#### 청구항 16

제 15항에 있어서, 상기 저항성-스위칭 소자는 이원 금속 산화물 또는 탄소 나노튜브 직물을 포함하는, 디바이 스.

#### 청구항 17

제 8항에 있어서, 상기 복수의 메모리 셀들은 100,000개 이상의 메모리 셀들을 포함하는, 디바이스.

# 청구항 18

제 8항에 있어서, 상기 제 1 메모리 레벨은 기판 위에 형성되는, 디바이스.

#### 청구항 19

제 18항에 있어서, 기판은 단결정 실리콘을 포함하는, 디바이스.

#### 청구항 20

제 18항에 있어서, 제 2 메모리 레벨은 상기 제 1 메모리 레벨 위에 단일체형으로 형성되는, 디바이스.

#### 청구항 21

제 20항에 있어서, 상기 제 2 메모리 레벨은 복수의 제 2 p-i-n 다이오드들을 포함하고, 각각의 제 2 p-i-n 다이오드는 저부 고 도핑 n-형 영역과 상부 고 도핑 p-형 영역을 포함하는, 디바이스.

#### 청구항 22

수직 배향 p-i-n 다이오드를 형성하는 방법으로서,

기판 위에 레일형의 제 1 전도체를 형성하는 단계와;

- (a) 상기 레일형의 제 1 전도체 위에 증착된 반도체 재료의 저부 고 도핑 p-형 영역을 형성하는 단계와,

- (b) 반도체 재료의 저부 고 도핑 p-형 영역 위에 증착된 반도체 재료의 중간 진성 또는 경 도핑 영역을 형성하고, 상기 증착된 반도체 재료는 실리콘, 게르마늄 또는 실리콘-게르마늄 합금인, 증착된 반도체 재료의 중간 진성 또는 경 도핑 영역을 형성하는 단계와,

- (c) 기둥을 형성하도록 저부 고 도핑 p-형 영역과 중간 진성 또는 경 도핑 영역을 패턴화 및 에칭하는 단계, 및

- (d) 비소로 도핑된 상부 고 도핑 n-형 영역을 형성하는 단계,

를 수행함으로써, p-i-n 다이오드를 형성하는 단계와;

상기 p-i-n 다이오드의 상기 상부 고 도핑 n-형 영역과 접촉하도록 실리사이드-형성 금속영역을 형성하는 단계 와;

상기 실리사이드-형성 금속영역을 상기 p-i-n 다이오드의 상기 상부 고 도핑 n-형 영역과 반응시킴으로써 실리사이드, 게르마나이드 또는 실리사이드-게르마나이드를 형성하는 단계와;

상기 반도체 재료를 결정화하도록 어닐링하는 단계를 포함하고,

상기 반도체 재료의 일부는 중착시 비정질이고, 상기 어닐링 단계 이후 상기 실리사이드, 게르마나이드 또는 실리사이드-게르마나이드와 접촉하게 되는, 수직 배향 p-i-n 다이오드의 형성 방법.

# 청구항 23

제 22항에 있어서, 상기 실리사이드, 게르마나이드 또는 실리사이드-게르마나이드는, 티타늄 실리사이드, 티타늄 게르마나이드, 티타늄 실리사이드-게르마나이드, 코발트 실리사이드, 코발트 게르마나이드 또는 코발트 실리사이드-게르마나이드인, 수직 배향 p-i-n 다이오드의 형성 방법.

### 청구항 24

제 22항에 있어서, 상부 고 도핑 n-형 영역은 원 위치에 도핑되는, 수직 배향 p-i-n 다이오드의 형성 방법.

# 청구항 25

제 22항에 있어서, 상기 상부 고 도핑 n-형 영역은 이온 주입에 의해 중간 진성 또는 경 도핑 영역의 상부를 도 핑함으로써 도핑되는, 수직 배향 p-i-n 다이오드의 형성 방법.

### 청구항 26

제 25항에 있어서, 상기 상부 고 도핑 n-형 영역을 형성하기 위한 이온 주입은 상기 패턴화 및 에칭 단계 이전

에 발생하는, 수직 배향 p-i-n 다이오드의 형성 방법.

#### 청구항 27

제 25항에 있어서, 상기 상부 고 도핑 n-형 영역을 형성하기 위한 이온 주입은 상기 패턴화 및 에칭 단계 이후에 발생하는, 수직 배향 p-i-n 다이오드의 형성 방법.

#### 청구항 28

제 22항에 있어서, 상기 실리사이드-형성 금속영역은 티타늄, 코발트, 크롬, 탄탈륨, 백금, 니오븀 또는 팔라듐 층을 포함하는, 수직 배향 p-i-n 다이오드의 형성 방법.

#### 청구항 29

제 28항에 있어서, 상기 p-i-n 다이오드 상의 제2 레일형 전도체를 형성하는 단계를 더 포함하고, 상기 티타늄, 코발트, 크롬, 탄탈륨, 백금, 니오븀 또는 팔라듐 충은 제2 레일형 전도체의 일부인, 수직 배향 p-i-n 다이오드의 형성 방법.

#### 청구항 30

제 28항에 있어서, 상기 티타늄, 코발트, 크롬, 탄탈륨, 백금, 니오븀 또는 팔라듐 층은 상기 패턴화 및 에칭 단계 동안 상기 기둥을 에칭하기 위해 사용되는 경질 마스크의 일부인, 수직 배향 p-i-n 다이오드의 형성 방법.

#### 청구항 31

제 22항에 있어서, 상기 p-i-n 다이오드는 메모리 셀의 일부이고,

상기 메모리 셀은,

상기 레일형의 제 1 전도체의 일부와,

상기 레일형의 제 1 전도체와 레일형의 제 2 전도체 사이에 배치되어 있는 상기 p-i-n 다이오드 위의 레일형의 제 2 전도체의 일부를 포함하는, 수직 배향 p-i-n 다이오드의 형성 방법.

### 청구항 32

제 31항에 있어서, 상기 메모리 셀은 유전체 파열 안티퓨즈를 더 포함하고,

상기 유전체 파열 안티퓨즈 및 상기 p-i-n 다이오드는 상기 레일형의 제 1 전도체와 상기 레일형의 제 2 전도체사이에서 전기적으로 직렬로 배열되는, 수직 배향 p-i-n 다이오드의 형성 방법.

#### 청구항 33

제 32항에 있어서, 상기 유전체 파열 안티퓨즈는, HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, ZrO<sub>2</sub>, TiO<sub>2</sub>, La<sub>2</sub>O<sub>3</sub>, Ta<sub>2</sub>O<sub>5</sub>, RuO<sub>2</sub>, ZrSiO<sub>x</sub>, AlSiO<sub>x</sub>, HfSiO<sub>x</sub>, HfSiO<sub>x</sub>, HfSiO<sub>x</sub>, HfSiAlO<sub>x</sub>, HfSiA

### 청구항 34

제 32항에 있어서, 상기 유전체 파열 안티퓨즈는 실리콘 이산화물을 포함하는, 수직 배향 p-i-n 다이오드의 형성 방법.

# 청구항 35

제 31항에 있어서, 상기 메모리 셀은 저항성-스위칭 소자를 더 포함하고,

상기 저항성-스위칭 소자 및 상기 p-i-n 다이오드는 상기 레일형의 제 1 전도체와 상기 레일형의 제 2 전도체사이에서 전기적으로 직렬로 배열되는, 수직 배향 p-i-n 다이오드의 형성 방법.

### 청구항 36

제 35항에 있어서, 상기 저항성-스위칭 소자는 이원 금속 산화물을 포함하는, 수직 배향 p-i-n 다이오드의 형성

방법.

#### 청구항 37

제 36항에 있어서, 상기 이원 금속 산화물은, Ni<sub>x</sub>O<sub>y</sub>, Nb<sub>x</sub>O<sub>y</sub>, Ti<sub>x</sub>O<sub>y</sub>, Hf<sub>x</sub>O<sub>y</sub>, Al<sub>x</sub>O<sub>y</sub>, Mg<sub>x</sub>O<sub>y</sub>, CO<sub>x</sub>O<sub>y</sub>, Cr<sub>x</sub>O<sub>y</sub>, V<sub>x</sub>O<sub>y</sub>, Zn<sub>x</sub>O<sub>y</sub>, B<sub>x</sub>N<sub>y</sub> 및 Al<sub>x</sub>N<sub>y</sub> 중 하나 이상을 포함하는, 수직 배향 p-i-n 다이오드의 형성 방법.

### 청구항 38

제 35항에 있어서, 상기 저항성-스위칭 소자는 탄소 나노튜브 직물을 포함하는, 수직 배향 p-i-n 다이오드의 형성 방법.

### 청구항 39

제 22항에 있어서, 상기 기판은 단결정 실리콘 웨이퍼인, 수직 배향 p-i-n 다이오드의 형성 방법.

#### 청구항 40

단일체형 3차원 메모리 어레이를 형성하는 방법으로서, 상기 방법은 :

- a) 하기의 i) ~ vi) 단계들에 의해 기판 위에 제 1 메모리 레벨을 단일체형으로 형성하는 단계;

- i) 상기 기판 위에 레일형의 복수의 제 1 전도체들을 형성하는 단계,

- ii) 다음의 (a)~(d) 단계들에 의해 복수의 p-i-n 다이오드들을 형성하는 단계,

- (a) 상기 레일형의 제 1 전도체들 위에 증착된 반도체 재료의 저부 고 도핑 p-형 영역을 형성하는 단계,

- (b) 실리콘, 게르마늄 또는 실리콘-게르마늄 합금인 증착된 반도체 재료의 중간 진성 또는 경 도핑 영역을 증착된 반도체 재료의 상기 저부 고 도핑 p-형 영역 위에 형성하는 단계,

- (c) 복수의 제 1 기둥을 형성하도록 증착된 반도체 재료의 상기 저부 고 도핑 p-형 영역 및 증착된 반도체 재료의 중간 진성 또는 경 도핑 영역을 패턴화 및 에칭하는 단계,

- (d) 비소(arsenic)로 도핑된 상부 고 도핑 n-형 영역을 형성하는 단계,

- iii) 상기 p-i-n 다이오드들의 상기 상부 고 도핑 n-형 영역과 접촉하도록 실리사이드-형성 금속영역을 형성하는 단계와,

- iv) 상기 실리사이드-형성 금속영역을 상기 p-i-n 다이오드들의 상기 상부 고 도핑 n-형 영역과 반응시킴으로써 실리사이드, 게르마나이드 또는 실리사이드-게르마나이드를 형성하는 단계와,

- v) 상기 반도체 재료를 결정화하도록 어닐링하는 단계로서, 상기 반도체 재료의 일부는 증착시 비정질이고 상기 어닐링 단계 이후 상기 실리사이드, 게르마나이드 또는 실리사이드-게르마나이드와 접촉하게 되는 어닐링 단계,

- vi) 상기 중간 진성 또는 경 도핑 영역 위에 레일형의 복수의 제 2 전도체들을 형성하는 단계로서, 상기 제 1 메모리 레벨은 복수의 제 1 메모리 셀들을 포함하고, 각각의 제 1 메모리 셀은 레일형의 제 1 전도체들 중하나의 일부와, 복수의 제 1 기둥들 중 하나와, 제 2 전도체들 중 하나의 일부를 포함하는 형성 단계,

- b) 상기 제 1 메모리 레벨 위에 제 2 메모리 레벨을 단일체형으로 형성하는 단계;

- 를 포함하는, 단일체형 3차원 메모리 어레이의 형성 방법.

#### 청구항 41

제 40항에 있어서, 상기 제 2 메모리 레벨은 복수의 제 2 p-i-n 다이오드들을 포함하고, 각각의 제 2 p-i-n 다이오드는 저부 고 도핑 n-형 영역과, 중간 진성 또는 경 도핑 영역과, 상부 고 도핑 p-형 영역을 포함하는, 단일체형 3차원 메모리 어레이의 형성 방법.

#### 청구항 42

제 41항에 있어서, 상기 제 2 전도체들은 상기 제 1 메모리 레벨과 상기 제 2 메모리 레벨에 의해 공유되는. 단

일체형 3차원 메모리 어레이의 형성 방법.

# 발명의 설명

### 기술분야

본 출원은, 발명의 명칭이 "크고 균일한 전류를 갖는 상향 지향 P-I-N 다이오드를 형성하는 방법(Method to Form Upward-pointing P-I-N Diodes Having Large and Uniform Current)"인 2007년 3월 27일자로 출원된 헤르너(Herner)의 미국 특허 출원 제 11/692,151호(대리인 문서 번호 SAND-01179USO)와, 발명의 명칭이 "크고 균일한 전류를 갖는 상향 지향 P-I-N 다이오드의 대형 어레이(Large Array of Upward-Pointing P-I-N Diodes Having Large and Uniform Current)"인 2007년 3월 27일자로 출원된 헤르너의 미국 특허 출원 제 11/692,153호(대리인 문서 번호 SAND-01179US1)에 대한 우선권을 주장하며, 이들 양자 모두는 본 명세서에 그 전문이 참조로통합되어 있다.

#### [0002] 관련 출원

[0001]

[0003]

[0004]

[0005]

[0006]

[0007]

[0008]

[0009]

본 출원은 발명의 명칭이 "탄소 나노튜브 직물 요소 및 조종 요소를 포함하는 메모리 셀을 형성하는 방법 (Method to Form a Memory Cell Comprsing a Carbon Nanotube Fabric Element and a Steering Element)"인 2007년 3월 27일자로 출원된 헤르너(Herner) 등의 미국 특허 출원 제 11/692,144호(대리인 문서 번호 SAND-01193USO)와, 발명의 명칭이 "탄소 나노튜브 직물 요소 및 조종 요소를 포함하는 메모리 셀(Memory Cell Comprsing a Carbon Nanotube Fabric Element and a Steering Element)"인 2007년 3월 27일자로 출원된 헤르너 등의 미국 특허 출원 제 11/692,148호(대리인 문서 번호 SAND-01193US1)에 관련하며, 이들 양자 모두는 본 명세서에 그 전문이 참조로 통합되어 있다.

#### 배경기술

다이오드는 특정 턴-온(turn-on) 전압 아래에서 매우 작은 전류 흐름을 허용하고, 턴-온 전압 위에서 상당히 더 많은 전류를 허용하는 특성을 갖는다. 턴-온 전압을 초과하는 전압이 인가될 때 다이오드 사이의 전류의 균일성이 양호하면서 저부 고 도핑(heavily doped) p-형 영역과, 중간 진성 영역과, 상부 고 도핑 n-형영역을 갖는 수직 배향 p-i-n 다이오드의 대규모 개체군(large population)을 형성하는 것은 어렵다는 것이 판명되어 있다.

특히, 메모리 어레이에 사용하기 위해, 양호한 균일성을 갖는 이런 상향 지향 다이오드의 대규모 개체군을 형성하는 것이 바람직하다.

### 발명의 상세한 설명

본 발명의 하기의 청구범위에 정의되어 있으며, 본 장의 내용 중 어떠한 것도 이들 청구범위에 대한 제한으로서 인지되지 않아야 한다. 일반적으로, 본 발명은 상향 지향 p-i-n 다이오드의 개체군과 이를 형성하는 방법에 관 한 것이다.

본 발명의 제 1 실시예는 복수의 수직 배향 p-i-n 다이오드를 포함하는 기판 위에 형성된 제 1 디바이스 레벨을 제공하며, 여기서, 각 p-i-n 다이오드는 저부 고 도핑 p-형 영역과, 중간 진성 또는 경 도핑 영역과, 비소로 도핑된 상부 고 도핑 n-형 영역을 포함하고, 각 p-i-n 다이오드는 기둥 형태를 가지며, p-i-n 다이오드들의 99% 이상에 대하여, 저부 고 도핑 p-형 영역과 상부 고 도핑 n-형 영역 사이에 약 1.5V 내지 약 3.0V의 전압이 인가될 때, 상기 p-i-n 다이오드들을 통해 흐르는 전류는 1.5 마이크로 암페어(microamps) 이상이고, 상기 p-i-n 다이오드들은 중착된 실리콘, 게르마늄 또는 실리콘-게르마늄을 포함하고, 상기 복수의 p-i-n 다이오드들은 제 1 디바이스 레벨에서의 모든 p-i-n 다이오드를 포함한다.

본 발명의 제 2 실시예는 복수의 메모리 셀들을 포함하는 제 1 메모리 레벨을 제공하며, 여기서, 각각의 메모리 셀은 기둥 형태의 수직 배향 p-i-n 다이오드를 포함하고, 각각의 수직 배향 p-i-n 다이오드는 저부 고 도핑 p-형 영역과, 중간 진성 또는 경 도핑 영역과, 비소로 도핑된 상부 고 도핑 n-형 영역을 포함하고, 상기 메모리 셀들은 프로그램 셀들 및 미프로그램 셀들을 포함하고, 상기 메모리 셀들의 절반 이상은 프로그램 셀들이며, 약 1.5V 내지 약 3.0V의 전압이 저부 고 도핑 p-형 영역과 상부 고 도핑 n-형 영역 사이에 인가될 때, 상기 프로그램 셀들의 99% 이상의 상기 p-i-n 다이오드들을 통해 흐르는 전류는 1.5 마이크로 암페어(microamps) 이상이며, 복수의 메모리 셀들은 상기 제 1 메모리 레벨에서의 모든 메모리 셀을 포함한다.

본 발명의 제 3 실시예는 수직 배향 p-i-n 다이오드를 형성하는 방법을 제공하며, 이 방법은 기판 위에 레일형

### - 7 -

의 제 1 전도체를 형성하는 단계와; (a) 상기 레일형의 제 1 전도체 위에 증착된 반도체 재료의 저부 고 도핑 p-형 영역을 형성하는 단계와, (b) 반도체 재료의 저부 고 도핑 p-형 영역 위에 증착된 반도체 재료의 중간 진성 또는 경 도핑 영역을 형성하는 단계로서, 상기 증착된 반도체 재료는 실리콘, 게르마늄 또는 실리콘-게르마늄 합금인, 증착된 반도체 재료의 중간 진성 또는 경 도핑 영역을 형성하는 단계와, (c) 기둥을 형성하도록 저부 고 도핑 p-형 영역과 중간 진성 또는 경 도핑 영역을 패턴화 및 에칭하는 단계와, (d) 비소로 도핑된 상부고 도핑 n-형 영역을 형성하는 단계, 를 수행함으로써, p-i-n 다이오드를 형성하는 단계와; 상기 반도체 재료를 결정화하도록 어닐링하는 단계를 포함하고, 상기 반도체 재료의 일부는 증착시 비정질이고, 상기 어닐링 단계이후 상기 실리사이드, 게르마나이드 또는 실리사이드-게르마나이드와 접촉하게 되며, 상기 p-i-n 다이오드는 저부 고 도핑 p-형 영역과, 중간 진성 또는 경 도핑 영역과, 상부 고 도핑 n-형 영역을 포함한다.

[0010]

본 발명의 다른 실시예는 단일체형 3차원 메모리 어레이를 형성하는 방법을 제공하며, 이 방법은, a) 하기의 i) ~ vi) 단계들에 의해 기판 위에 제 1 메모리 레벨을 단일체형으로 형성하는 단계; i) 기판 위에 레일형의 복수 의 제 1 전도체들을 형성하는 단계, ii) 다음의 단계들에 의해 복수의 p-i-n 다이오드들을 형성하는 단계, (a) 레일형의 제 1 전도체들 위에 증착된 반도체 재료의 저부 고 도핑 p-형 영역을 형성하는 단계, (b) 실리콘, 게 르마늄 또는 실리콘-게르마늄 합금인 증착된 반도체 재료의 중간 진성 또는 경 도핑 영역을 증착된 반도체 재료 의 저부 고 도핑 p-형 반도체 위에 형성하는 단계, (c) 복수의 제 1 기둥을 형성하도록 증착된 반도체 재료의 상기 저부 고 도핑 p-형 영역 및 증착된 반도체 재료의 중간 진성 또는 경 도핑 영역을 패턴화 및 에칭하는 단 계, (d) 비소로 도핑된 상부 고 도핑 영역을 형성하는 단계, iii) 상기 p-i-n 다이오드들의 상기 상부 고 도핑 n-형 영역과 접촉하도록 실리사이드-형성 금속영역을 형성하는 단계와, iv) 상기 실리사이드-형성 금속영역을 상기 p-i-n 다이오드들의 상기 상부 고 도핑 n-형 영역과 반응시킴으로써 실리사이드, 게르마나이드 또는 실리 사이드-게르마나이드를 형성하는 단계와, v) 반도체 재료를 결정화하도록 어닐링하는 단계로서, 반도체 재료의 일부는 증착시 비정질이고 어닐링 단계 이후 실리사이드, 게르마나이드 또는 실리사이드-게르마나이드와 접촉하 게 되는 어닐링 단계, vi) 상기 중간 진성 또는 경 도핑 영역 위에 레일형의 복수의 제 2 전도체들을 형성하는 단계로서, 상기 제 1 메모리 레벨은 복수의 제 1 메모리 셀들을 포함하고, 각각의 제 1 메모리 셀은 레일형의 제 1 전도체들 중 하나의 일부와, 복수의 제 1 기둥들 중 하나와, 제 2 전도체들 중 하나의 일부를 포함하는 형 성단계, b) 상기 제 1 메모리 레벨 위에 제 2 메모리 레벨을 단일체형으로 형성하는 단계를 포함한다.

[0011]

본 명세서에 설명된 본 발명의 각 실시예 및 실시예는 단독으로 또는 서로 간에 조합하여 사용될 수 있다.

이제, 첨부 도면을 참조로 양호한 태양 및 실시예를 설명한다.

[0012]

# 실시예

[0020]

모두 본 발명의 양수인이 소유하고 있는 '470 출원, '030 특허 및 '549 출원에는 기둥 형태의 수직 배향된 p-i-n 다이오드를 각각 포함하는 메모리 셀이 설명되어 있다. 이런 다이오드는 실리콘, 게르마늄 또는 실리콘-게르마늄 합금 같은 반도체 재료로 형성되며, 제 1 반도체 형의 저부 고 도핑 영역과, 중간 진성 또는 경 도핑 영역과, 제 1 반도체 형과 반대인 제 2 반도체 형의 상부 고 도핑 영역을 포함한다. 저부 고 도핑 p-형 영역 및 상부 고 도핑 n-형 영역을 갖는 배향 또는 반대로, 저부 고 도핑 n-형 영역 및 상부 고 도핑 p-형 영역을 갖는 배향 양자 모두의 배향으로 이런 다이오드를 형성하는 것이 설명되어 있다.

[0021]

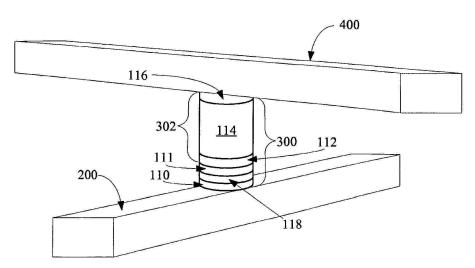

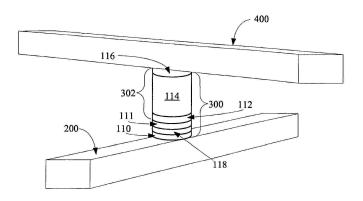

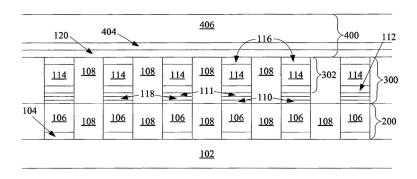

도 1은 '030 특허의 일 실시예에 따라 형성된 메모리 셀을 예시한다. 이런 메모리 셀은 저부 전도체(200)와 상부 전도체(400)를 포함하고, 이들 사이에 전기적으로 직렬로 수직 배향 p-i-n 다이오드(302)와 유전체 파열 안티퓨즈(118; antifuse)가 배열되어 있다. 그 초기, 미프로그램 상태에서, 저부 전도체(200)와 상부 전도체(400)사이에 예를 들어, 2V의 판독 전압(read voltage)이 인가될 때, 이들 사이에 매우 미소한 전류가 흐른다. 비교적 큰 프로그래밍 전압의 인가는 메모리 셀을 변화시키며, 프로그래밍 이후에는 동일 판독 전압에서 저부 전도체(200)와 상부 전도체(400)사이에 상당히 더 많은 전류가 흐른다. 미프로그램 상태와 프로그램 상태 사이의이러한 전류 편차는 측정가능하며, 각각이 별개의 데이터 상태에 대응할 수 있다. 예를 들어, 미프로그램 셀은데이터 "0"으로 간주되고, 프로그램 셀은데이터 "1"로 간주될 수 있다.

[0022]

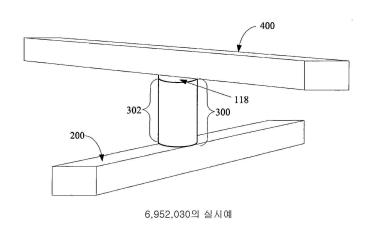

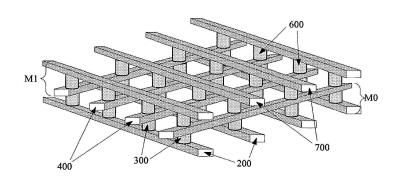

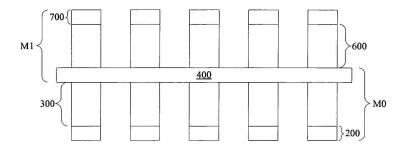

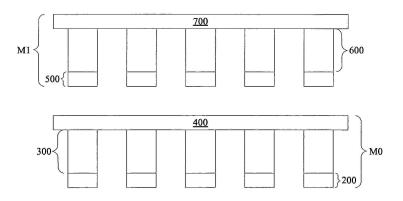

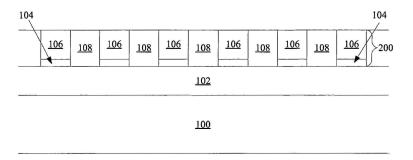

도 2는 복수의 저부 전도체(200)와, 각각 도 1에서와 같은 다이오드 및 유전체 파열 안티퓨즈를 포함하는 복수의 기둥(300)과, 복수의 상부 전도체(400)를 포함하는 제 1 메모리 레벨의 일부를 도시한다. 각 기둥(300)은 하나의 저부 전도체(200)와 하나의 상부 전도체(400) 사이에 배치된다. 이런 메모리 레벨은 종래의 단결정 실리콘웨이퍼 같은 기판 위에 형성될 수 있다. 제 1 메모리 레벨 위에 다수의 메모리 레벨이 적층 형성되어 고밀도 단일체형 3차원 메모리 어레이를 형성할 수 있다.

[0023]

다이오드는 정류 디바이스이며, 하나의 방향에서 다른 방향에서보다 더 쉽게 전류를 전도한다. 다이오드는 그양호한 전도 방향으로 지향(point)하는 것으로 지칭될 수 있다. 저부에 n-형 반도체 재료를 가지고 상부에 p-형반도체 재료를 가지는 수직 배향 다이오드는 하향 지향이라 지칭될 수 있으며, 저부에 p-형 반도체 재료를 가지 고 상부에 n-형 반도체 재료를 가지는 수직 배향 다이오드는 상향 지향이라 지칭될 수 있다. 본 출원에서, "상향", "하향", "위", "아래" 등 같은 공간적 관계를 나타내는 용어가 사용될 때, 이들 용어는 기준 프레임의 저부에 존재하는 것으로 가정되는 기판에 관련한 것이다. 예를 들어, 제 1 요소가 제 2 요소 위에 있는 것으로 설명되면, 제 1 요소는 제 2 요소보다 기판으로부터 더 멀리에 존재한다.

[0024]

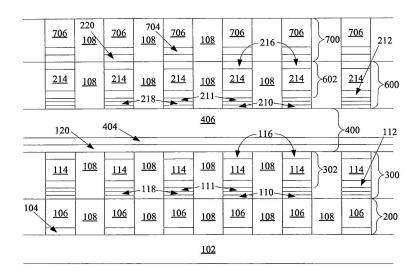

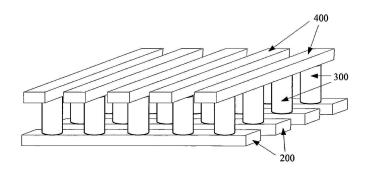

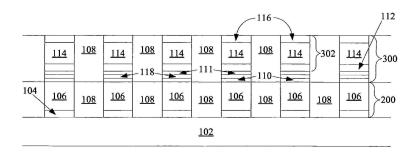

수직 방향으로 적충된 메모리 어레이에서, 전도체(400)가 제 1 메모리 레벨(M0)의 상부 전도체 및 제 2 메모리 레벨(M1)의 저부 전도체 양자 모두로서 기능하고 있는 도 3a의 사시도에 도시된 바와 같이, 수직 방향으로 인접한 메모리 레벨들은 전도체를 공유하는 것이 바람직하다. 동일 구조는 도 3b에 단면도로 도시되어 있다. 도 3c는 전도체가 공유되지 않는 어레이의 단면도를 도시한다. 도 3c에서, 각 메모리 레벨은 저부 전도체(200, 500)와, 기둥(300, 600)과 상부 전도체(400, 700)를 가지며, 메모리 레벨(M0, M1)을 분리하는 레벨간 유전체를 갖고, 어떠한 전도체도 공유하지 않는다. 도 3a 및 도 3b의 구조는 더 작은 수의 마스킹 단계를 필요로 하며,도 3c에 도시된 바와 동일한 밀도의 메모리 셀을 제조하기 위한 제조 비용을 감소시킨다. 인접한 레벨들 상의다이오드들이 반대 방향으로 지향하는 경우, 예를 들어, 제 1 메모리 레벨(M0) 다이오드가 상향 지향하고 제 2메모리 레벨(M1) 다이오드가 하향 지향하는 경우,도 3a 및 도 3b에서와 같이 전도체를 공유하는 것이 가장 쉽게 전기적으로 달성된다. 상향 지향 다이오드들만의 또는 하향 지향 다이오드들 만의 적충된 어레이는 도 3c에서와 같이 전도체가 공유되지 않는 상태로 형성되는 것이 일반적이다.

[0025]

대형 메모리 어레이는 통상적으로 각각이 감지될 수 있어야 하는 수백만의 메모리 셀들을 포함한다. 이런 대형어레이 내의 메모리 셀 사이의 특성들 중 일부가 불가피하게 변할 수 있다. 신뢰성을 향상시키기 위해, 메모리 셀들의 대형 어레이에 대해, 미프로그램 상태와 프로그램 상태 사이의 편차를 최대화하여 이들을 더 쉽게 구별할 수 있게 하는 것이 바람직하다. 또한, 셀들 간의 변화를 최소화하는 것이 바람직하며, 셀들이 가능한 균일하게 거동하게 하는 것이 바람직하다.

[0026]

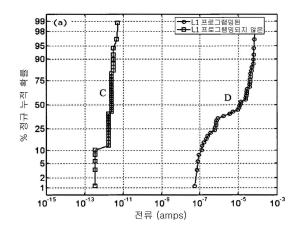

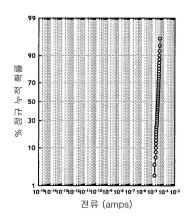

도 4a는 다이오드들이 모두 하향 지향하는, 즉, 다이오드들이 저부 고 도핑 n-형 영역과 중간 진성 영역과 상부 고 도핑 영역을 가지는, 전도체 사이에 직렬로 안티퓨즈와 다이오드를 포함하고 있는 '030 특허의 것들(도 1에 도시)과 같은 메모리 셀의 개체군을 위한 동일 인가 판독 전압하에서의 미프로그램 전류와 프로그램 전류를 나타내는 확율 플롯이다. 라인 A 상에 도시된 하향 지향 다이오드를 위한 미프로그램 전류는  $10^{-12}$ amps에 근접하게 긴밀하게 그룹을 형성한다. 유사하게, 라인 B 상에 도시된 프로그램 전류는 하나의 재외점(outlier)을 제외하면 약  $10^{-5}$ 과  $10^{-4}$  amps 사이에서 긴밀하게 그룹을 형성한다. 미프로그램 전류(라인 A) 및 프로그램 전류(라인 B)의 분포들은 서로 많이 이격되어 있으며, 양자 모두가 긴밀하게 그룹을 형성하고 있다.

[0027]

도 4b는 '030 특허에서와 같이 형성된 상향 지향 다이오드의 개체군을 위한 미프로그램 전류와 프로그램 전류를 도시하는 확율 플롯이다. 라인 C 상에 도시된 미프로그램 전류는 도 4a의 라인 A의 하향 지향 다이오드의 미프로그램 전류와 매우 유사하다. 그러나, 라인 D 상에 도시된 프로그램 전류는 도 4a의 라인 B 상의 프로그램 전류보다 매우 넓은 분포를 나타낸다. 이 상향 지향 다이오드를 위한 프로그램 전류는 약 8  $\times$  10 $^{-8}$  amps 내지 7  $\times$  10 $^{-5}$  amps의 범위이며, 편차는 크기의 3배에 근접한다. 많은 수의 이들 다이오드의 개체군은 1 microamp 미만의 프로그램 전류를 갖는다. 이러한 비균일성 및 낮은 프로그램 전류는 '030 특허의 상향 지향 다이오드가 하향 지향 다이오드보다 대형 어레이에 사용하기에 덜 바람직한 다이오드가 되게 한다.

[0028]

본 발명에서, 양호한 균일성 및 큰 프로그램 전류를 갖는 상향 지향 수직 배향 p-i-n 다이오드의 대규모 개체군을 산출하는 제조 기술이 발견되었다. 도 5는 본 발명의 일 실시예에 따라 형성된 상향 지향 다이오드를 포함하는 메모리 셀의 일 예를 도시한다. 이 메모리 셀에서, 다이오드는 유전체 파열 안티퓨즈와 쌍을 이루지만, 후술될 바와 같이, 도시된 메모리 셀은 이런 다이오드를 위한 다수의 가능한 용도 중 단 하나이며, 명료성을 위해 제공되어 있는 것이다.

[0029]

메모리 셀은 제 1 전도체(200)와 제 2 전도체(400)를 포함한다. 이들 사이에는 유전체 파열 안티퓨즈(118)[전도성 배리어 층(110, 111) 사이에 개재된 상태로 도시됨)와 다이오드(302)가 배치되어 있다. 다이오드(302)는 저부 고 도핑 p-형 영역(112)과, 중간 진성 영역(114)과, 상부 고 도핑 n-형 영역(116)을 포함한다. 다이오드(302)는 반도체 재료, 예를 들어, 실리콘, 게르마늄 또는 실리콘-게르마늄 합금으로 형성된다. 간결성을 위해,이 반도체 재료는 실리콘으로서 설명되어 있다. 실리콘은 증착시 주로 비정질인 것이 바람직하다 [원 위치(in-

situ) 도핑의 경우, p-형 영역(112) 전반에 걸쳐, 증착시 다결정 상태일 수 있음]. 상부 고 도핑 p-형 영역 (116)은 비소로 도핑된다. 양호한 실시예에서, 영역(116)은 중간 진성 영역(114)을 형성한 후 중간 진성 영역의 상부를 이온 주입에 의해 비소로 도핑함으로써 형성된다. 알 수 있는 바와 같이, 이온 주입 단계는 기둥을 형성하는 패터닝 및 에칭 단계 이전 또는 이후에 이루어질 수 있다. 대안적 실시예에서, 영역(116)은 적어도 5 ×  $10^{20}$  atoms/cm³의 비소 농도를 초래하기에 충분한 흐름으로 실리콘 증착 동안 AsH3 같은 적절한 소스 가스를 유동시킴으로써 원 위치에 도핑될 수 있다. 상부 전도체(400)의 저부 충은 티타늄, 코발트, 크롬, 탄탈륨, 백금, 니오븀 또는 팔라듐 같은 실리사이드-형성 금속이다. 티타늄 및 코발트가 바람직하며, 티타늄이 가장 바람직하다. 실리콘을 결정화하기 위해 수행되는 어닐링 동안, 실리사이드 형성 금속은 상부 고 도핑 n-형 영역(116)의 실리콘과 반응하여 실리사이드 층, 예를 들어, 티타늄 실리사이드를 형성한다. 도 6은 이런 상향 지향 다이오드의 개체군에 대해 약 2V의 판독 전압에서의 전류를 보여주는 확율 플롯이며, 관찰할 수 있는 바와 같이, 이 개체군은 양호한 균일성을 가지고, 다이오드들간의 매우 미소한 변동과 비교적 큰 순방향 전류를 갖고, 약 35.5 마이크로 암페어(microamps)의 중간 전류(median current)를 갖는다. 특히, 이 개체군 내의 모든 다이오드에 대한 2V에서의 프로그램 전류는 약 3 마이크로 암페어(microamps)를 초과한다.

[0030]

설명된 바와 같이, 설명된 어레이 내의 메모리 셀은 메모리 셀을 가로질러 판독 전압을 인가함으로써 감지된다. 이상적으로는, 판독 전압은 어레이 내의 모든 메모리 셀에 대해 동일하게 인가되지만, 실제로는 어레이 내의 각 각의 메모리 셀의 위치로 인해 약간의 변동이 있다. 예를 들어, 감지 회로로부터 더 멀리 위치된 셀은 감지 회 로에 인접하게 배치된 셀보다 더 긴 상호연결부를 가진다. 상호연결부의 길이 증가는 저항 증가를 초래하여 더 근접한 셀들에 비해 더 원거리의 셀들의 다이오드에 걸친 전압이 더 작아지게 한다. 그러나, 상호연결부 길이 및 저항의 변동으로 인한 다이오드의 판독 전류의 작은 변동은 본 발명의 다이오드의 고유한 특성이 아니다. 디 바이스 레벨이라는 용어는 일반적으로 동일 가공 단계에 의해 기판 위의 동일 레벨에 형성된 복수의 동일 평면 인 디바이스를 지칭하며, 디바이스 레벨의 예는 기판 위에 형성된 복수의 동일 평면인 메모리 셀을 포함하는 메 모리 레벨이다. 일 예에서, 본 발명에 따라 형성된 상향 지향 p-i-n 다이오드의 개체군을 포함하는 디바이스 레 벨에서, 다이오드를 가로질러, 즉, 다이오드의 저부 p-형 영역과 상부 n-형 영역 사이에 인가된 전압은 다이오 드의 위치에 무관하게, 디바이스 레벨 내의 임의의 다이오드에 대해 약 1.8V 내지 약 2.2V이며, 이 인가된 전압 하에서의 이 디바이스 레벨 내의 다이오드들의 99%를 통해 흐르는 전류는 1.5 마이크로 암페어(microamps) 이상 이다. 다른 예에서, 본 발명에서, 예를 들어, 반도체 재료가 Sio. &Geo. 2 같은 실리콘-게르마늄 합금이면, 다이오드 를 가로질러(다이오드의 저부 p-형 영역과 상부 n-형 영역 사이에) 인가된 전압이 약 1.1V 내지 약 3.0V, 바람 직하게는 약 1.5V 내지 약 3.0V, 가장 바람직하게는 약 1.8V 내지 약 2.2V일 때, 디바이스 레벨 내의 다이오드 들 중 99%에 대해 약 1.5 마이크로 암페어(microamps)의 전류를 달성할 수 있다. p-i-n 다이오드의 이 개체군은 100,000 p-i-n 다이오드들 이상, 예를 들어, 1,000,000 p-i-n 다이오드들 이상을 갖는 디바이스 레벨일 수 있다.

[0031]

양호한 실시예에서, 디바이스 레벨은 본 발명의 메모리 셀을 포함하는 메모리 레벨이고, 여기서, 제 1 메모리 셀은 프로그램 셀과 미프로그램 셀을 포함한다. 이런 메모리 어레이에서, 사용 동안, 일부 셀들은 프로그램되고 나머지는 프로그램되지 않는다. 양호한 실시예에서, 메모리 셀의 절반 이상이 프로그램 셀이면, 저부 고 도핑 p-형 영역과 상부 고 도핑 n-형 영역 사이에 약 1.5V 내지 약 3.0V의 전압이 인가될 때 프로그램 셀의 99%이상의 p-i-n 다이오드를 통해 흐르는 전류는 1.5 마이크로 암페어(microamps) 이상이며, 여기서, 복수의 메모리 셀들은 상기 제 1 메모리 레벨에서의 모든 메모리 셀을 포함한다. 더 양호한 실시예에서, 인가된 전압은 약 1.8V 내지 약 2.2V이다. 이 메모리 셀의 메모리 레벨은 100,000 셀 이상, 예를 들어, 1,000,000 셀 이상을 포함할 수 있으며, 각 셀은 본 발명에 따라 형성된 상향 지향 p-i-n 다이오드를 포함한다.

[0032]

본 발명의 상향 지향 다이오드는 가장 바람직하게는 각 메모리 레벨 상에 하향 지향 다이오드와 교번하는 상향 지향 다이오드를 갖는, 전도체를 공유하는 적충된 메모리 레벨의 어레이에 바람직하게 사용될 수 있다.

[0033]

본 명세서에 참조로 통합되어 있는, 발명의 명칭이 "다결정 반도체 재료 내에 증가하는 순서로 작동하는 불휘발성 메모리 셀(Nonvolatile Memory Cell Operating by Increasing Order in Polycrystalline Semiconductor Material)"인 2005년 6월 8일자로 출원된 헤르너 등의 미국 특허 출원 제 11/148,530호에 설명된 바와 같이, 증착된 비정질 실리콘이 실리콘 이산화물 및 티타늄 니트라이드 같은 높은 격자 불일치(high lattice mismatch)를 갖는 재료들과만 접촉하여 결정화될 때, 다결정 실리콘 또는 폴리실리콘은 높은 수의 결정 결함을 형성하여 높은 저항을 갖게 한다. 이 고-결함 폴리실리콘을 통한 프로그래밍 펄스는 명백히 폴리실리콘을 변화시키며, 더낮은 저항이 되게 한다.

[0034]

추가로, '549 출원, 발명의 명칭이 "실리사이드에 인접하게 결정화된 반도체 접합 다이오드를 포함하는 메모리셀(Memory Cell Comprising a Semiconductor Junction Diode Crystallized Adjacent to a Silicide)"인 헤르너의 미국 특허 제 7,176,064호 및 이하 '283 출원이라 지칭되는 발명의 명칭이 "유전체 안티퓨즈와 직렬로 실리사이드에 인접하게 결정화된 P-I-N 다이오드를 제조하는 방법(Method for Making a P-I-N Diode Crystallized Adjacent to a Silicide in Serise with A Dielectric Antifuse)"인 2006년 11월 15일자로 출원된 헤르너의 미국 특허 출원 제 11/560,283호에 설명된 바와 같이, 증착된 비정질 실리콘이 적절한 실리사이드, 예를 들어, 티타늄 실리사이드, 코발트 실리사이드 또는 다른 알려진 실리사이드-형성 금속 중 하나로 형성된실리사이드의 충과 접촉하여 결정화될 때,결과적인 결정화된 실리콘은 더 소수의 결함을 갖는 매우 더 높은 품질이며, 매우 더 낮은 저항을 갖는다. 티타늄 실리사이드 또는 코발트 실리사이드의 격자 간격은 실리콘의 격자간격과 매우 근사하며, 비정질 실리콘이 바람직한 배향으로 적절한 실리사이드의 충과 접촉하여 결정화된 때,실리사이드는 실리콘의 결정 형성을 위한 템플릿(template)을 제공하여 결함 형성을 최소화하는 것으로 믿어진다. 높은 격자 불일치를 갖는 재료에만 인접하게 결정화된 고-결함 실리콘과는 달리, 큰 전기적 필스의 인가는실리콘 층과 접촉하여 결정화된 이 저-결함, 저-저항 실리콘의 저항을 적절히 변화시키지 않는다.

[0035]

수직 배향 p-i-n 다이오드를 사용하는 일부 메모리 셀에서, 이때, '549 출원에서와 같이, 다이오드는 고-결함, 고-저항 폴리실리콘으로 형성되며, 메모리 셀은 폴리실리콘의 저항 상태를 변경함으로써 프로그램된다. 이들 고-결함-다이오드 셀에 대하여, 메모리 셀의 데이터 상태는 주로 다이오드의 폴리실리콘의 저항 상태로 저장된다. '283 출원에서와 같이, 다른 메모리 셀에서, 다이오드는 저-결함, 저-저항 실리콘으로 형성되며, 상대 상태-변화 요소(companion state-change element)(본 경우에는 유전체 파열 안티퓨즈)와 쌍을 이루고, 메모리 셀은 상태-변화 요소의 특성을 변경함으로써(예를 들어, 안티퓨즈를 파열시킴으로써) 프로그램된다. 용어 상태-변화 요소는 둘 이상의 안정한, 서로 구별할 수 있는 상태들, 일반적으로, 저항 상태들을 취할 수 있는 요소를 설명하기 위해 사용되며, 이들 사이에서 가역적으로 또는 비가역적으로 스위칭될 수 있다. 이들 저-결함-다이오드 셀에 대하여, 메모리 셀의 데이터 상태는 다이오드의 상태가 아니라, 주로 상태-변화 요소 내에 저장된다. (본 설명은 실리사이드에 인접하게 결정화된 실리콘의 사용을 설명한다는 것을 주의하여야 한다. 동일한 효과는 게르마나이드 또는 실리콘 게르마나이드에 인접하게 결정화된 게르마늄 및 실리콘 게르마늄에 대해서도 기대될 수 있다.)

[0036]

본 발명의 상향 지향 p-i-n 다이오드는 실리사이드와 접촉하여 결정화되며, 따라서, 저-결함, 저-저항 반도체 재료이다. 이때, 본 발명의 상향 지향 다이오드가 메모리 셀에 사용되면, 이들은 상태-변화 요소, 예를 들어, 안티퓨즈 또는 저항성-스위칭 소자와 쌍을 이룰때 바람직하게 사용된다. 이런 저항성-스위칭 소자의 일 예는 본 명세서에 참조로 통합되어 있는 발명의 명칭이 "다이오드 및 저항 스위칭 재료를 포함하는 불휘발성 메모리 셀 (Nonvolatile Memory Cell Comprising a Diode and a Resistance-Switching Material)"인 2006년 3월 31일자로 출원된 헤르너 등의 미국 특허 출원 제 11/395,995호에 설명된 바와 같이, Ni<sub>x</sub>O<sub>y</sub>, Nb<sub>x</sub>O<sub>y</sub>, Ti<sub>x</sub>O<sub>y</sub>, Hf<sub>x</sub>O<sub>y</sub>, Al<sub>x</sub>O<sub>y</sub>, Mg<sub>x</sub>O<sub>y</sub>, CO<sub>x</sub>O<sub>y</sub>, Cr<sub>x</sub>O<sub>y</sub>, V<sub>x</sub>O<sub>y</sub>, Zr<sub>x</sub>O<sub>y</sub>, B<sub>x</sub>N<sub>y</sub> 또는 Al<sub>x</sub>N<sub>y</sub> 같은 이원 금속 산화물이다. 저항 스위칭 요소의 다른 예는 본원과 동일자로 출원된 헤르너 등의 출원(대리인 문서번호 SAND-01193USO)에 설명된 바와 같이 탄소 나노 튜브 직물이다.

[0037]

본 발명의 상향 지향 다이오드는 다수의 디바이스에 유리하게 사용될 수 있으며, 메모리 셀에 사용하는 것에 한 정되지 않는다는 것에 주의하여야 하며, 메모리 셀에 사용되는 경우에도 본 명세서에 명시적으로 설명된 것들 같은 셀에 사용하는 것에 한정되지 않는다는 것을 주의하여야 한다.

[0038]

기판 위에 형성된, 저부 전도체와 상부 전도체 사이에 직렬로 배열된 고-K 유전체 안티퓨즈와 상향 지향 다이오드를 구비하는 제 1 메모리 레벨의 제조와, 하향 지향 다이오드를 포함하는 그 위의 제 2 메모리 레벨의 제조를 설명하는 상세한 실시예가 제공될 것이며, 여기서 두 메모리 레벨들은 전도체를 공유한다. '283 출원 및 본 명세서에 통합되어 있는 다른 출원들로부터의 세부 사항은 이 메모리 레벨의 제조에 유용할 수 있다. 본원 발명을 모호하게 만드는 것을 피하기 위해, 이들 또는 다른 통합되어 있는 문헌들로부터의 모든 세부사항이 포함되지는 않겠지만, 그 교지들 중 어떠한 것도 배제하고자 하는 것은 아니라는 것을 이해할 수 있을 것이다. 완전성을 위해, 재료, 단계 및 조건을 포함하는 다수의 세부하상이 설명될 것이지만, 본 기술 분야의 숙련자들은 결과물들이 본 발명의 범주 내에 포함되는 상태로 이들 세부사항들이 변경, 확장 또는 생략될 수 있다는 것을 알 수 있을 것이다.

[0039] <u>예</u>

[0046]

[0048]

- [0040] 도 7a로 전환하여, 메모리의 형성은 기판(100)에서 시작된다. 이 기판(100)은 단결정 실리콘, 실리콘-게르마늄 이나 실리콘-게르마늄-카본 같은 IV-IV 콤파운드, III-V 콤파운드, II-VII 콤파운드, 이런 기판 위의 에피텍셜 충 또는 임의의 다른 반도체 재료 같은 본 기술 분야에 공지된 임의의 반도체 기판일 수 있다. 기판은 내부에 제조된 집적 회로를 포함할 수 있다.

- [0041] 절연충(102)은 기판(100) 위에 형성된다. 절연충(102)은 실리콘 산화물, 실리콘 니트라이드, Si-C-O-H 필름 또는 기타 다른 적절한 절연 재료일 수 있다.

- [0042] 제 1 전도체(200)는 기판(100) 및 절연체(102) 위에 형성된다. 접착층(104)이 절연층(102)과 전도층(106) 사이에 포함되어 전도층(106)을 절연층(102)에 대해 접착하는 것을 돕는다. 위에 배설된 전도층(106)이 텅스텐이면, 접착층(104)으로서 티타늄 니트라이드가 적합하다. 전도층(106)은 텅스텐이나, 탄탈륨, 티타늄 또는 그 합금을 포함하는 다른 재료 같은 본 기술 분야에 공지된 임의의 전도성 재료를 포함할 수 있다.

- [0043] 전도체 레일을 형성하는 모든 층이 증착되고 나면, 층들은 단면이 도 7a에 도시되어 있는 평행하고, 동일 평면인 전도체(200)를 형성하기 위해 임의의 적절한 마스킹 및 에칭 프로세스를 사용하여 패턴화 및 에칭된다. 전도체(200)는 지면 외부로 연장한다. 일 실시예에서, 포토레지스트가 증착되고, 포토리소그래피에 의해패턴화되며, 충들이 에칭되고, 그후, 표준 처리 기술을 사용하여 포토레지스트가 제거된다.

- [0044] 다음에, 유전체 재료(108)가 전도체 레일(200)들의 사이 및 그 위에 증착된다. 유전체 재료(108)는 실리콘 산화물, 실리콘 니트라이드 또는 실리콘 옥시니트라이드 같은 임의의 알려진 전기 절연 재료일 수 있다. 양호한 실시예에서, 고밀도 플라즈마법에 의해 증착된 실리콘 이산화물이 유전체 재료(108)로서 사용된다.

- [0045] 마지막으로, 전도체 레일(200) 상부의 잉여 유전체 재료(108)가 제거되어 유전체 재료(108)에 의해 분리된 전도 체 레일(200)의 상부를 노출시키며, 실질적인 평면형 표면을 남기게 된다. 결과적인 구조는 도 7a에 도시되어 있다. 평면형 표면을 형성하기 위한 이 유전체 과충전물(overfill)의 제거는 화학 기계 평탄화(CMP) 또는 에치 백(etchback) 같은 본 기술 분야에 공지된 임의의 공정에 의해 수행될 수 있다.

- 도 7b로 전환하여, 다음에 선택적 전도층(110)이 증착된다. 층(110)은 전도성 재료, 예를 들어, 티타늄 니트라이드, 탄탈륨 니트라이드 또는 텅스텐이다. 이 층은 임의의 적절한 두께, 예를 들어, 약 50 내지 약 200 옹스트롬(angstroms), 바람직하게는 약 100 옹스트롬(angstroms)일 수 있다. 일부 실시예에서는 배리어층 (110)이 생략될 수 있다.

- [0047] 다음에, 본 실시예에서, 유전체 스택 또는 유전체 재료의 얇은 층(118)이 증착되어 유전체 파열 안티퓨즈를 형성한다. 일 실시예에서, HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, ZrO<sub>2</sub>, TiO<sub>2</sub>, La<sub>2</sub>O<sub>3</sub>, Ta<sub>2</sub>O<sub>5</sub>, RuO<sub>2</sub>, ZrSiO<sub>x</sub>, AlSiO<sub>x</sub>, HfSiO<sub>x</sub>, HfSiON, ZrSiAlO<sub>x</sub>, HfSiAlO<sub>x</sub> HfSiAlON 또는 ZrSiAlON 같은 고-K 유전체가, 예를 들어, 원자 층 증착(atomic layer deposition)에 의해 증착된다. HfO<sub>2</sub> 및 Al<sub>2</sub>O<sub>3</sub>이 바람직하다. HfO<sub>2</sub>가 사용되는 경우, 층(118)은 약 5 내지 약 100 옹스트롬(angstroms), 바람직하게는 약 40 옹스트롬(angstroms)의 두께를 갖는 것이 바람직하다. Al<sub>2</sub>O<sub>3</sub>이 사용되는 경우, 층(118)은 약 5 내지 약 80 옹스트롬(angstroms), 바람직하게는 약 30 옹스트롬(angstrom -s)의 두께를 갖는 것이 바람직하다. 대안적 실시예에서, 유전체 파열 안티퓨즈는 실리콘 이산화물을 포함할 수 있다.

- 전도층(111)은 층(118) 상에 증착된다. 이는 임의의 적절한 두께, 예를 들어, 약 50 내지 약 200 옹스트롬 (angstroms), 바람직하게는 약 100 옹스트롬(angst -roms)의 두께를 갖는 임의의 적절한 전도성 재료, 예를 들어, 티타늄 니트라이드일 수 있다. 일부 실시예에서, 전도층(111)은 생략될 수 있다.

- [0049] 다음에, 기둥으로 패턴화될 반도체 재료가 증착된다. 반도체 재료는 실리콘, 게르마늄, 실리콘-게르마늄 합금 또는 다른 적절한 반도체나 반도체 합금일 수 있다. 간결성을 위해, 본 설명은 반도체 재료를 실리콘으로 지칭 하지만, 숙련된 실시자는 이들 다른 적절한 재료 중 임의의 재료를 대신 선택할 수 있다는 것을 이해할 것이다.

- [0050] 저부 고 도핑 영역(112)은 본 기술 분야에 공지된 임의의 증착 및 도핑 방법에 의해 형성될 수 있다. 실리콘이 증착되고 그후 도핑될 수 있지만, 실리콘의 증착 동안 p-형 도펀트 원자, 예를 들어, 붕소를 제공하는 도너 가스를 유동시킴으로써 원 위치에 도핑되는 것이 바람직하다. 양호한 실시예에서, 도너 가스는 BCl<sub>3</sub>이고, p-형 영

- 역(112)은 약  $1 \times 10^{21}$  atoms/cm<sup>3</sup>의 농도로 도핑되는 것이 바람직하다. 고 도핑 영역(112)은 바람직하게는 약 100 내지 약 800 옹스트롬(angstroms)의 두께, 가장 바람직하게는 약 200 옹스트롬(angstroms)의 두께이다.

[0051]

다음에, 진성 또는 경 도핑 영역(114)이 본 기술 분야에 공지된 임의의 방법에 의해 형성될 수 있다. 영역(114)은 실리콘인 것이 바람직하며, 약 1200 내지 약 4000 옹스트롬(angstroms)의 두께, 바람직하게는 약 3000 옹스트롬(angstroms)의 두께를 갖는다. 붕소 같은 일반적 p-형 도펀트는 결정화를 촉진하는 경향이 있으며, 따라서, 고 도핑 영역(112)의 실리콘은 증착될 때 다결정이 되기 쉽다. 그러나, 진성 영역(114)은 증착될 때 비정질인 것이 바람직하다.

[0052]

아래에 배설된 전도층(111), 유전체 파열 안티퓨즈(118) 및 전도층(110)과 함께, 바로 증착된 반도체 영역(114, 112)은 기둥(300)을 형성하도록 패턴화 및 에칭된다. 기둥(300)은 아래의 전도체(200)와 대략 동일한 피치 및 대략 동일한 폭을 가져서 각 기둥(300)이 전도체(200)의 상부에 형성되어야 한다. 약간의 오정렬은 허용될 수있다.

[0053]

기둥(300)은 임의의 적절한 마스킹 및 에칭 프로세스를 사용하여 형성될 수 있다. 예를 들어, 포토레지스트는 증착되고, 표준 포토리소그래피 기술을 사용하여 패턴화되고, 에칭되고, 그후, 포토레지스트가 제거될 수 있다. 대안적으로, 예를 들어, 실리콘 이산화물 같은 일부 다른 재료의 경질 마스크가 저부 반반사 코팅(bottom antireflective coating; BARC)과 함께 반도체 층 스택의 상부에 형성되고, 그후 패턴화 및 에칭될 수 있다. 유사하게, 유전체 반반사 코팅(DARC)이 경질 마스크로서 사용될 수 있다.

[0054]

양자 모두가 본 발명의 양수인의 소유이며 본 명세서에 참조로 통합되어 있는 발명의 명칭이 "교번 위상 이동을 이용한 내부 비인쇄 윈도우를 갖는 포토마스크 피쳐스(Photomask Features sith Interior Nonprinting Window Using Alternating Phase Shifting)"인 2003년 12월 5일자로 출원된 첸(Chen)의 미국 출원 제 10/728,436호나, 발명의 명칭이 "무크롬 비인쇄 위상 이동 윈도우를 갖는 포토마스크 피쳐스(Photomask Features with Chromeless Nonprinting Phase Shifting Window)"인 2004년 4월 1일자로 출원된 첸의 미국 출원 제 10/815,312호에 설명된 포토리소그래피 기술이 본 발명에 따른 메모리 어레이의 형성에 사용되는 임의의 포토리소그래피 단계를 수행하기 위해 바람직하게 사용될 수 있다.

[0055]

기둥(300)의 직경은 필요에 따라, 예를 들어, 약 22 nm 내지 약 130 nm, 바람직하게는 약 32 nm 내지 약 80 nm, 예를 들어, 약 45 nm일 수 있다. 기둥(300) 사이의 간극은 기둥들의 직경과 대략 동일한 것이 바람직하다. 매우 작은 형상부가 기둥으로서 패턴화될 때, 포토리소그래피 공정은 코너를 둥글게하는 경향이 있으며, 그래서, 포토마스크 내의 대응 형상부의 실제 형상에 무관하게 기둥의 단면은 원형이되는 경향이 있다는 것을 주의하여야 한다.

[0056]

유전체 재료(108)는 반도체 기둥(300) 사이 및 위에 증착되어 기둥들 사이의 간극을 충전한다. 유전체 재료 (108)는 실리콘 산화물, 실리콘 니트라이드 또는 실리콘 옥시니트라이드 같은 임의의 알려진 전기 절연 재료일수 있다. 양호한 실시예에서, 실리콘 이산화물이 절연 재료로서 사용된다.

[0057]

다음에, 기둥(300)의 상부의 유전체 재료가 제거되어 유전체 재료(108)에 의해 분리된 기둥(300)의 상부를 노출시키고 실질적으로 평탄한 표면을 남긴다. 이 유전체 과충전물의 제거는 CMP 또는 에치백 같은 본 기술 분야에 공지된 임의의 공정에 의해 수행될 수 있다. CMP 또는 에치백 이후, 이온 주입이 수행되어 고 도핑 n-형 상부 영역(116)을 형성한다. n-형 도펀트는 예를 들어, 10 keV의 주입 에너지와 약  $3 \times 10^{15}/\mathrm{cm}^2$ 의 투여량을 갖는 비소의 얕은 주입(shallow implant)인 것이 바람직하다. 이 주입 단계는 다이오드(302)의 형성을 완성시킨다. 예를 들어, 약 300 내지 약 800 옹스트롬(angstroms)의 실리콘의 일부 두께가 CMP 동안 소실되며, 따라서, 다이오드(302)의 최종 높이는 약 800 내지 약 4000 옹스트롬(angstroms), 예를 들어, 약 45 nm의 형상부 크기를 갖는 다이오드에 대하여 약 2500 옹스트롬 (angstroms)일 수 있다.

[0058]

도 7c로 전환하여, 다음에, 예를 들어, 티타늄, 코발트, 크롬, 탄탈륨, 백금, 니오븀 또는 팔라듐 같은 실리사이드 형성 금속의 층(120)이 증착된다. 층(120)은 티타늄 또는 코발트인 것이 바람직하며, 층(120)이 티타늄인경우, 그 두께는 바람직하게는 약 10 내지 약 100 옹스트롬(angstroms), 가장 바람직하게는 약 20 옹스트롬(angstroms)이다. 층(120)에는 티타늄 니트라이드 층(404)이 이어진다. 층(404)은 바람직하게는 약 20 내지 약 100 옹스트롬(angstroms), 가장 바람직하게는 약 80 옹스트롬(angstroms)이다. 다음에, 예를 들어, 텅스텐 같은 전도성 재료의 층(406)이 증착된다. 예를 들어, 이 층은 CVD에 의해 형성된 약 1500 옹스트롬(angstroms)의 텅스텐일 수 있다. 층(406, 404, 120)은 레일형의 상부 전도체(400)로 패턴화 및 에칭되며, 이 레일형의 상부 전도체는 저부 전도체(200)에 수직인 방향으로 연장하는 것이 바람직하다. 상부 전도체(400)의 피치 및 배향은 각전도체(400)가 기둥(300)의 열의 상부에 형성되어 그와 접촉하도록 이루어지며, 전도체(400)는 기둥(300)과 대략 동일한 폭을 갖는 것이 바람직하다. 약간의 오정렬은 허용될 수 있다.

[0059]

다음에, 유전체 재료(미도시)가 전도체(400) 사이 및 그 위에 증착된다. 유전체 재료는 실리콘 산화물, 실리콘 니트라이드 또는 실리콘 옥시니트라이드 같은 임의의 알려진 전기 절연 재료일 수 있다. 양호한 실시예에서, 실리콘 산화물이 이 유전체 재료로서 사용된다.

[0060]

도 7c를 참조하면, 실리사이드 형성 금속의 층(120)은 상부 고 도핑 영역(116)의 실리콘과 접촉한다는 것을 주의하여야 한다. 후속 고온 단계 동안, 층(120)의 금속은 고 도핑 p-형 영역(116)의 실리콘 중 일부와 반응하여실리사이드 층(미도시)을 형성하며, 이 실리사이드 층은 다이오드와 상부 전도체(400) 사이에 있고, 대안적으로, 이 실리사이드 층은 상부 전도체(400)의 일부인 것으로 고려될 수 있다. 이 실리사이드 층은 실리콘을 결정화하기 위해 필요한 온도보다 낮은 온도에서 형성되며, 따라서, 진성 영역(114) 및 고 도핑 p-형 영역(116)이 여전히 대부분 비정질인 상태인 동안 형성된다. 실리콘-게르마늄 합금이 상부 고 도핑 영역(116)에 사용되는 경우, 실리사이드-게르마나이드 층은 예를 들어, 코발트 실리사이드-게르마나이드 또는 티타늄 실리사이드-게르마나이드로 형성될 수 있다. 유사하게, 게르마늄이 사용되면, 게르마나이드가 형성될 것이다.

[0061]

직전에 설명한 실시예에서, 도 7c의 다이오드(302)는 저부 고 도핑 p-형 영역과, 중간 진성 영역과, 상부 고 도핑 n-형 영역을 포함하는 상향 지향형이다. 양호한 실시예에서, 이것 위에 단일체형(monolithically)으로 형성될 다음 메모리 레벨은 직전에 형성된 제 1 메모리 레벨과 전도체(400)를 공유한다. 즉, 제 1 메모리 레벨의 상부 전도체(400)는 제 2 메모리 레벨의 하부 전도체로서 기능한다. 전도체가 이 방식으로 공유되면, 이때, 제 2 메모리 레벨 내의 다이오드는 저부 고 도핑 n-형 영역과, 중간 진성 영역과, 상부 고 도핑 p-형 영역을 포함하는 하향 지향형인 것이 바람직하다.

[0062]

도 7d로 전향하여, 다음에, 선택적 전도층(210), 고-K 유전체 안티퓨즈 증(218) 및 선택적 전도층(211)이 형성되며, 이는 제 1 메모리 레벨의 기둥(300)의 층들(110, 118, 111) 각각과 동일한 재료, 동일한 두께 및 동일한 방법을 사용하여 이루어지는 것이 바람직하다.

[0063]

다음에, 다이오드가 형성된다. 저부 고 도핑 영역(212)은 본 기술 분야에 공지된 임의의 증착 및 도핑 방법에 의해 형성된다. 실리콘이 증착되고, 그후 도핑되지만, 실리콘의 증착 동안, 예를 들어, 인 같은 n-형 도펀트 원자를 제공하는 도너 가스를 유동시킴으로써 원 위치에 도핑되는 것이 바람직하다. 고 도핑 영역(212)은 약 100 내지 약 800 옹스트롬(angstroms)인 것이 바람직하며, 가장 바람직하게는 약 100 내지 약 200 옹스트롬(angstroms)이다.

[0064]

다음에, 증착될 다음 반도체 영역은 도핑되지 않는 것이 바람직하다. 그렇지만, 증착된 실리콘에서, 인 같은 n-형 도펀트는 강한 계면 거동을 나타내어 실리콘이 증착될 때 표면을 향해 이주하는 경향이 있다. 실리콘의 증착은 어떠한 도펀트 가스도 제공되지 않는 상태로 지속되지만, 상향 이동하여 표면을 찾아가는 인 원자는 비의도적으로 이 영역을 도핑시킨다. 본 명세서에 참조로 통합되어 있는 발명의 명칭이 "N-형 도펀트 확산을 최소화하기 위한 증착된 반도체 구조 및 제조 방법(Deposited Semiconductor Structure to Minimise N-Type Dopant Diffusion and Method of Making)"인 2005년 12월 9일자로 출원된 헤르너의 미국 특허 출원 제 11/298,331호에 설명된 바와 같이, 증착된 실리콘 내의 인의 계면 거동은 게르마늄의 추가에 의해 억제된다. 적어도 10 at%의게르마늄을 포함하는 실리콘-게르마늄 합금의 충이 이 지점에 증착되는 것이 바람직하다. 예를 들어, 인을 제공하는 어떠한 도펀트 가스도 사용하지 않고, 도핑되지 않은 상태로 증착되는 약 200 옹스트롬(angstroms)의 Sio,8Geo,2가 증착되는 것이 바람직하다. 이 얇은 충은 도 7d에는 도시되어 있지 않다.

[0065]

이 얇은 실리콘-게르마늄 층의 사용은 형성되는 진성 영역내로의 n-형 도펀트의 비의도적 확산을 최소화하여 그 두께를 최대화한다. 진성 영역의 두께가 두꺼울수록 다이오드가 역방향 바이어스하에 있을 때 다이오드를 가로 지른 누설 전류가 최소화되어 전력 손실이 감소한다. 이 방법은 다이오드의 전체 높이를 증가시키지 않고 진성 영역의 두께가 증가될 수 있게 한다. 볼 수 있는 바와 같이, 다이오드는 기둥으로 패턴화되고, 다이오드의 높이 증가는 이들 기둥을 형성하는 에칭 단계 및 그들 사이의 간극을 충전하기 위한 단계의 형상비를 증가시킨다. 형상비가 증가하면, 에칭 및 충전 양자 모두가 더 곤란해진다.

[0066]

다음에, 진성 영역(214)이 본 기술 분야에 공지된 임의의 방법에 의해 형성될 수 있다. 영역(214)은 실리콘인 것이 바람직하며, 바람직하게는 약 1100 내지 약 3300 옹스트롬(angstroms), 바람직하게는 약 1700 옹스트롬(angstroms)의 두께를 갖는다. 고 도핑 영역(212) 및 진성 영역(214)의 실리콘은 증착시 비정질인 것이 바람직하다.

[0067]

아래에 배설된 전도층(211), 고-K 유전체 층(218) 및 전도층(210)과 함께 직전에 증착된 반도체 영역(214, 21 2)은 패턴화 및 에칭되어 기둥(600)을 형성한다. 기둥(600)은 각 기둥(600)이 전도체(400)의 상부에 형성되도록

아래의 전도체(400)와 대략 동일한 피치 및 대략 동일한 폭을 가져야 한다. 약간의 오정렬은 허용될 수 있다. 기둥(600)은 제 1 메모리 레벨의 기둥(300)을 형성하기 위해 사용된 것과 동일한 기술을 사용하여 패턴화 및 에 칭될 수 있다.

- [0068]

- 유전체 재료(108)가 반도체 기둥(600) 사이 및 위에 증착되어 그들 사이의 간극을 충전한다. 제 1 메모리 레벨에서와 같이, 기둥(600) 상부의 유전체 재료(108)가 제거되어 유전체 재료(108)에 의해 분리된 기둥(600)의 상부를 노출시키고, 실질적으로 평탄한 표면을 남기게 된다. 이 평탄화 단계 이후, 이온 주입이 수행되어 고 도평 p-형 상부 영역(116)을 형성한다. p-형 도펀트는, 예를 들어, 2 keV의 주입 에너지와 약 3 ×  $10^{15}/\mathrm{cm}^2$ 의 투여량을 갖는 붕소의 얕은 주입인 것이 바람직하다. 이 주입 단계는 다이오드(602)의 형성을 완료시킨다. CMP 단계동안 실리콘의 일부 두께가 소실되며 그래서, 완성된 다이오드(602)는 다이오드(302)와 비슷한 높이를 갖는다.

[0069]

상부 전도체(700)는 제 1 및 제 2 메모리 레벨들 사이에서 공유되는 전도체(400)와 동일한 방식 및 동일한 재료로 형성된다. 실리사이드-형성 금속의 충(220)이 증착되고, 이어서, 티타늄 니트라이드 충(704) 및 전도성 재료, 예를 들어, 텅스텐의 충(706)이 형성된다. 충들(706, 704, 220)은 전도체(400)에 실질적으로 수직이고 전도체(200)에 실질적으로 평행인 방향으로 연장하는 것이 바람직한 레일형의 상부 전도체(700)로 패턴화 및 에칭된다.

[0070]

형성시 각 메모리 레벨이 어닐링될 수 있지만, 바람직하게는 메모리 레벨 모두가 형성된 이후, 예를 들어, 약 750℃에서 약 60초 동안 단일 결정화 어닐링이 수행되어 다이오드(302, 602)의 반도체 재료를 결정화한다. 결과적인 다이오드는 일반적으로 다결정이다. 이들 다이오드의 반도체 재료가 양호한 격자 일치를 갖는 실리사이드 또는 실리사이드-게르마나이드 층과 접촉하여 결정화되기 때문에, 다이오드(302, 602 등)의 반도체 재료는 저결함 및 저-저항이다.

[0071]

직전에 설명된 실시예에서, 전도체는 메모리 레벨들 사이에 공유된다. 즉, 제 1 메모리 레벨의 상부 전도체 (400)는 제 2 메모리 레벨의 저부 전도체로서 기능한다. 다른 실시예에서, 레벨간 유전체는 도 7c의 제 1 메모리 레벨 위에 형성되고, 그 표면이 평탄화되고, 어떠한 공유된 전도체도 없이 이 평탄화된 레벨간 유전체 상에서 제 2 메모리 레벨의 구성이 시작된다. 주어진 실시예에서, 제 1 메모리 레벨의 다이오드는 저부 상에 p-형실리콘을 가지고, 상부 상에 n-형을 가지는 상향 지향식이고, 제 2 메모리 레벨의 다이오드는 저부 상에 n-형실리콘을 가지고 상부 상에 p-형을 가지는 하향 지향식이다. 전도체가 공유되는 실시예에서, 다이오드 유형들은 교번적으로 하나의 레벨 상에서 상향, 다음 레벨 상에서 하향인 것이 바람직하다. 전도체가 공유되지 않는 실시예에서, 다이오드는 모두 하향 또는 상향 지향식의 하나의 유형일 수 있다. 상향 또는 하향이라는 용어는 다이오드가 순방향 바이어스하에 있을 때 전류 흐름의 방향을 지칭한다.

[0072]

일부 실시예에서, 프로그래밍 펄스는 역방향 바이어스로 다이오드에 인가되는 것이 바람직할 수 있다. 이는 본 발명의 양수인의 소유이면서 본 명세서에 참조로 통합되어 있는, 발명의 명칭이 "조율가능한 저항을 갖는 스위칭가능한 반도체 메모리 요소를 포함하는 메모리 셀을 사용하는 방법(Method For Using A Memory Cell Comprising Switchable Semiconductor Memory Element With Trimmable Resistance)"인 2006년 7월 28일자로출원된 쿠마르(Kumar) 등의 미국 특허 출원 제 11/496,986호에 설명된 바와 같이, 어레이 내의 선택되지 않은 셀을 가로지른 누설을 감소 또는 제거하는 장점을 가질 수 있다.

[0073]

기판 위에 두 개의 메모리 레벨의 제조를 설명하였다. 추가적인 메모리 레벨이 동일 방식으로 형성되어 단일체형 3차원 메모리 어레이를 형성할 수 있다.

[0074]

단일체형 3차원 메모리 어레이는 어떠한 개입 기판도 갖지 않는 웨이퍼 같은 단일 기판 위에 다수의 메모리 레벨이 형성되어 있는 메모리 어레이이다. 하나의 메모리 레벨을 형성하는 충들은 기존 레벨 또는 레벨들의 충들위에 직접적으로 성장 또는 중착된다. 대조적으로, 적충형 메모리들은 발명의 명칭이 "3차원 구조 메모리(Three dimensional structure memory)"인 리디(Leedy)의 미국 특허 제 5,915,167호에서와 같이 별개의 기판 상에 메모리 레벨을 형성하고 서로의 위에 메모리 레벨들을 접착함으로써 구성되어 왔다. 기판은 접합 이전에 박화 또는 메모리 레벨들로부터 제거될 수 있지만, 메모리 레벨들은 최초에 별개의 기판 위에 형성되기 때문에, 이런메모리들은 진정한 단일체형 3차원 메모리 어레이가 아니다.

[0075]

기판 위에 형성된 단일체형 3차원 메모리 어레이는 적어도 기판 위의 제 1 높이에 형성된 제 1 메모리 레벨과, 제 1 높이와는 다른 제 2 높이에 형성된 제 2 메모리 레벨을 포함한다. 3개, 4개, 8개 또는 사실상 임의의 수의 메모리 레벨들이 이런 다중레벨 어레이에서 기판 위에 형성될 수 있다.

[0076]

제공된 실시예에서와 같은 차감형 기술(substractive technique)을 사용하는 대신 다마센(Damascene) 구조를 사

용하여 전도체가 형성되는 적층형 메모리 어레이를 형성하기 위한 대안적인 방법이 본 발명의 양수인에게 양도된, 본 명세서에 참조로 통합되어 있는 발명의 명칭이 "트렌치 에칭 동안 패턴화된 형상부를 보호하기 위한 전도성 경질 마스크(Conductive Hard Mask to Protect Patterned Features During Trench Etch)"인 2006년 5월 31일자로 출원된 라디간(Radigan) 등의 미국 특허 출원 제 11/444,936호에 설명되어 있다. 라디간 등의 방법은 본 발명에 따른 어레이를 형성하기 위해 대신 사용될 수 있다. 라디간 등의 방법에서, 전도성 경질 마스크는 그들 아래의 다이오드를 에칭하기 위해 사용된다. 이 경질 마스크를 본 발명에 적용시, 양호한 실시예에서, 다이오드의 실리콘과 접촉하는 경질 마스크의 저부 층은 티타늄, 코발트, 크롬, 탄탈륨, 백금, 니오븀 또는 팔라듐인 것이 바람직하다. 그후, 어닐링 동안, 실리사이드가 형성되어 실리사이드 결정화 템플릿을 제공한다. 본 실시예에서, 기둥을 형성하기 위한 패터닝 단계 이전에 상부 고 도핑 p-형 영역을 형성하기 위한 이온 주입 단계가 이루어진다.

- [0077]

- 현재까지 제공된 실시예에서, 실리사이드는 다이오드의 상부 접촉부에 형성된다. 대안 실시예에서, 이는 다른 장소에, 예를 들어, 저부 접촉부에 형성될 수 있다. 예를 들어, 다이오드의 실리콘은 다이오드의 상부에 형성된 안티퓨즈 또는 저항 스위칭 요소(예를 들어, 탄소 나노튜브 직물 또는 이원 금속 산화물) 같은 상태-변화 요소 및 실리사이드-형성 금속 상에 직접적으로 증착될 수 있다.

- [0078]

- 본 발명의 상향 지향 다이오드는 1회 프로그램가능 메모리 셀(안티퓨즈와 쌍을 이룰 때) 또는 재기록 가능한 메모리 셀(저항성-스위칭 소자와 쌍을 이룰 때)에 사용되는 것으로 설명하였다. 그러나, 본 발명의 다이오드의 모든 가능한 용례를 나열하는 것은 실용적이지 못하며, 이들 예들은 제한을 의미하지 않는다.

- [0079]

- 상세한 제조 방법을 본 명세서에 설명하였지만, 결과물이 본 발명의 범주 내에 든다면 동일한 구조를 형성하는 임의의 다른 방법이 사용될 수 있다.

- [0800]

- 상술한 상세한 설명은 본 발명이 취할 수 있는 다수의 형태 중 단지 소수를 설명하였다. 이 때문에, 본 상세한 설명은 제한이 아닌 예시이다. 본 발명의 범주를 규정하는 것은 모든 등가체를 포함하는 하기의 청구범위 뿐이 다.

#### 산업상 이용 가능성

[0081]

상술한 바와 같이, 본 발명은, 상향 지향 p-i-n 다이오드의 개체군과 이를 형성하는 방법을 제공하는데 사용된다.

# 도면의 간단한 설명

- [0013]

- 도 1은, '030 특허에 설명된 메모리의 일 실시예의 사시도.

- [0014] 도 2는, 도 1의 셀 같은 메모리 셀을 포함하는 제 1 메모리 레벨의 부분 사시도.

- [0015] 도 3a는, 전도체를 공유하는 두 개의 적충된 메모리 레벨들을 도시하는 사시도. 도 3b는 동일 구조의 단면도. 도 3c는 전도체를 공유하지 않는 두 개의 적충된 메모리 레벨들을 도시하는 단면도.

- [0016] 도 4a는, '030 특허의 일 실시예에 따라 형성된 상향 지향 다이오드들의 개체군에 대한 2V의 인가 전압에서의 전류의 확율 플롯(probability plot). 도 4b는 '030 특허의 일 실시예에 따라 형성된 상향 지향 다이오드의 개체군에 대한 2V의 인가 전압에서의 전류의 확율 플롯.

- [0017] 도 5는, 본 발명의 일 실시예의 사시도.

- [0018] 도 6은, 본 발명에 따라 형성된 상향 지향 다이오드의 개체군에 대한 2V의 인가 전압에서의 전류의 확율 플롯.

- [0019] 도 7a 내지 도 7d는, 제 1 메모리 레벨이 본 발명의 일 실시예에 따라 형성된 상향 지향 다이오드들을 포함하는, 두 개의 메모리 레벨의 형성 단계를 예시하는 단면도.

# 도면

# 도면1

# 도면2

# 도면3a

# 도면3b

# 도면3c

# 도면4a

# 도면4b

# 도면5

# 도면6

# 도면7a

# 도면7b

# 도면7c

# 도면7d