(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-7631

(P2004-7631A)

(43) 公開日 平成16年1月8日(2004.1.8)

(51) Int.C1.<sup>7</sup>

H03G 3/30

H03F 1/02

H03F 3/21

H04B 1/04

F 1

H03G 3/30

H03F 1/02

H03F 3/21

H04B 1/04

テーマコード(参考)

5J100

5J500

5K060

E

審査請求 未請求 請求項の数 43 O L (全 13 頁)

(21) 出願番号 特願2003-124921 (P2003-124921)

(22) 出願日 平成15年4月30日 (2003.4.30)

(31) 優先権主張番号 10/137833

(32) 優先日 平成14年5月1日 (2002.5.1)

(33) 優先権主張国 米国(US)

(71) 出願人 399117121

アジレント・テクノロジーズ・インク

A G I L E N T T E C H N O L O G I E

S, I N C.

アメリカ合衆国カリフォルニア州パロアル

ト ページ・ミル・ロード 395

395 Page Mill Road

Palo Alto, California

U. S. A.

(74) 代理人 10009623

弁理士 奥山 尚一

(74) 代理人 100096769

弁理士 有原 幸一

(74) 代理人 100107319

弁理士 松島 鉄男

最終頁に続く

(54) 【発明の名称】出力電力制御システム

## (57) 【要約】 (修正有)

【課題】 優れた比例追従正確度が得られ、かつ出力信号電力の立ち上がり時間の早い出力電力制御システムを提供する。

【解決手段】 出力電力制御システム40は、電力増幅器72と、電力増幅器72の一方の電力供給ライン78の電流を検出する抵抗84と、電流・電圧変換器86と、誤差増幅器90で負帰還をかけるフィードバックループ68から構成される。

【効果】 無線周波送信機に用いることにより、出力パワーレベルと、出力信号の立ち上がりを早くできる。

【選択図】 図3

**【特許請求の範囲】****【請求項 1】**

第1の電流を供給するように構成された増幅器と、

前記第1の電流に比例しかつ該電流よりも小さい第2の電流を供給するように構成された基準源と、

前記第2の電流に応答して、前記増幅器の利得を制御するフィードバック変換器と、

を含む出力電力制御システム。

**【請求項 2】**

前記フィードバック変換器は、前記第2の電流を電力制御電圧に変換するための電流・電圧変換器を備えることを特徴とする、請求項1に記載の出力電力制御システム。

10

**【請求項 3】**

前記電流・電圧変換器は、

供給電圧に結合されて、前記第2の電流を導通する抵抗器と、

前記供給電圧と前記抵抗器によって降下された電圧とを比較して、それらの差を出力電圧として出力するように構成された第1のコンパレータと、

前記出力電圧と基準電圧とを比較して、それらの差を前記電力制御電圧として出力するように構成された第2のコンパレータと、

を備えることを特徴とする、請求項2に記載の出力電力制御システム。

**【請求項 4】**

前記第2の電流が、前記第1の電流の $1 / ($ は1より大きい定数である $)$ 倍にほぼ等しいことを特徴とする、請求項1に記載の出力電力制御システム。

20

**【請求項 5】**

前記増幅器は、前記第1の電流を導通する幅Wの第1のトランジスタを含むことを特徴とする、請求項4に記載の出力電力制御システム。

**【請求項 6】**

前記基準源は、前記抵抗器に結合されて前記第2の電流を導通する幅Wの第2のトランジスタを含み、前記第2のトランジスタのゲートを前記第1のトランジスタのゲートに結合して、前記第2の電流が前記第1の電流の $1 /$ 倍にほぼ等しくなるようにしたことを特徴とする、請求項5に記載の出力電力制御システム。

**【請求項 7】**

が10以上であることを特徴とする、請求項6に記載の出力電力制御システム。

30

**【請求項 8】**

前記第1及び第2のトランジスタが、相補型金属酸化膜半導体トランジスタであることを特徴とする、請求項6に記載の出力電力制御システム。

**【請求項 9】**

前記第1及び第2のトランジスタが、エンハンスマント・モード・スードモルフィック高電子移動度トランジスタであることを特徴とする、請求項6に記載の出力電力制御システム。

**【請求項 10】**

前記増幅器は、前記電力制御電圧を印加して利得を制御するように構成された入力段をさらに含むことを特徴とする、請求項2に記載の出力電力制御システム。

40

**【請求項 11】**

前記増幅器が無線周波増幅器であることを特徴とする、請求項1に記載の出力電力制御システム。

**【請求項 12】**

電力制御電圧に対応する利得が得られるように入力信号を増幅して、出力信号を送り出すように構成された増幅器と、

第1の電流、及び、該第1の電流に比例しかつ該電流より小さい第2の電流を供給するように構成されたミラー基準電流源と、

前記第2の電流を前記電力制御電圧に変換して、前記利得を制御するように構成された負

50

のフィードバック変換器と、

を備える出力電力制御システム。

【請求項 1 3】

前記負のフィードバック変換器は、

供給電圧に結合されて第2の電流を導通する抵抗器と、

前記供給電圧と前記抵抗器によって降下された電圧とを比較して、それらの差を出力電圧として出力するように構成された第1のコンパレータと、

前記出力電圧と基準電圧とを比較して、それらの差を前記電力制御電圧として出力するように構成された第2のコンパレータと、

を備えることを特徴とする、請求項12に記載の出力電力制御システム。

10

【請求項 1 4】

前記ミラー基準電流源は、

前記第1の電流を導通する幅Wの第1のトランジスタと、

前記抵抗器に結合されて前記第2の電流を導通する幅Wの第2のトランジスタとを含み、

前記第1のトランジスタのゲートを前記第2のトランジスタのゲートに結合して、前記第2の電流が前記第1の電流の1/倍にほぼ等しくなるようにしたことを特徴とする、請求項13に記載の出力電力制御システム。

【請求項 1 5】

が10以上であることを特徴とする、請求項14に記載の出力電力制御システム。

20

【請求項 1 6】

前記第1及び第2のトランジスタが相補型金属酸化膜半導体トランジスタであることを特徴とする、請求項14に記載の出力電力制御システム。

【請求項 1 7】

前記第1及び第2のトランジスタが、エンハンスマント・モード・スードモルフィック高電子移動度トランジスタであることを特徴とする、請求項14に記載の出力電力制御システム。

【請求項 1 8】

前記第1及び第2のトランジスタが、シリコン・バイポーラ・トランジスタであることを特徴とする、請求項14に記載の出力電力制御システム。

30

【請求項 1 9】

前記第1及び第2のトランジスタが、ヘテロ接合バイポーラ・トランジスタであることを特徴とする、請求項14に記載の出力電力制御システム。

【請求項 2 0】

電力制御電圧入力を備え、前記電力制御電圧に対応する利得が得られるように無線周波入力信号を增幅する無線周波電力增幅器と、

基準電流を導通する幅Wの基準トランジスタと、

前記基準電流より大きい出力電流を導通して(ここで、前記基準電流は出力電流に比例する)、無線周波出力信号を生じるように構成された幅Wの出力トランジスタと、

前記基準電流を前記電力制御電圧に変換するように構成された負のフィードバック回路と、

を備える電流ミラー電力制御回路。

40

【請求項 2 1】

前記負のフィードバック変換器は、

供給電圧に結合されて前記基準電流を導通する抵抗器と、

前記供給電圧と前記抵抗器によって降下された電圧とを比較して、それらの差を出力電圧として出力するように構成された第1の比較回路と、

前記出力電圧と基準電圧とを比較して、それらの差を前記電力制御電圧として出力するように構成された第2の比較回路と、

を備えることを特徴とする、請求項20に記載の電流ミラー電力制御回路。

【請求項 2 2】

50

が 10 以上であることを特徴とする、請求項 20 に記載の電流ミラー電力制御回路。

【請求項 23】

前記基準及び出力トランジスタが相補型金属酸化膜半導体トランジスタであることを特徴とする、請求項 20 に記載の電流ミラー電力制御回路。

【請求項 24】

前記基準及び出力トランジスタが、エンハンスマント・モード・スードモルフィック高電子移動度トランジスタであることを特徴とする、請求項 20 に記載の電流ミラー電力制御回路。

【請求項 25】

電力制御電圧信号に対応する利得が得られるように、無線周波入力信号の送信を制御する 10 ように構成された入力段と、

出力電流及び無線周波出力信号を送り出すように構成された出力段と、

前記出力電流に比例しあつ該電流よりも小さい基準電流を送り出すように構成された基準段と、

前記基準電流を前記電力制御電圧信号に変換するように構成された電流・電圧フィードバック変換器と、

を備える無線周波電力増幅器。

【請求項 26】

前記電流・電圧フィードバック変換器は、

供給電圧に結合されて前記基準電流を導通する抵抗器と、

前記供給電圧と、前記抵抗器によって降下された電圧とを比較して、それらの差を出力電圧として出力するように構成された第 1 のコンパレータと、

前記出力電圧と基準電圧とを比較して、それらの差を前記電力制御電圧信号として出力するように構成された第 2 のコンパレータと、

を備えることを特徴とする、請求項 25 に記載の無線周波電力増幅器。

【請求項 27】

前記出力段は、出力電流を導通する幅 W の出力トランジスタを含むことを特徴とする、請求項 26 に記載の無線周波電力増幅器。

【請求項 28】

前記基準段は、前記抵抗器に結合されて前記基準電流を導通する幅 W の基準トランジスタを含み、前記基準トランジスタのゲートを前記出力トランジスタのゲートに結合して、前記基準電流が前記出力電流の 1 / 倍にほぼ等しくなるようにしたことを特徴とする、請求項 27 に記載の無線周波電力増幅器。

【請求項 29】

が 10 以上であることを特徴とする、請求項 28 に記載の無線周波電力増幅器。

【請求項 30】

前記基準及び出力トランジスタが、相補型金属酸化膜半導体トランジスタであることを特徴とする、請求項 28 に記載の無線周波電力増幅器。

【請求項 31】

前記基準及び出力トランジスタが、エンハンスマント・モード・スードモルフィック高電子移動度トランジスタであることを特徴とする、請求項 28 に記載の無線周波電力増幅器。

【請求項 32】

前記基準及び出力トランジスタが、シリコン・バイポーラ・トランジスタであることを特徴とする、請求項 28 に記載の無線周波電力増幅器。

【請求項 33】

前記基準及び出力トランジスタが、ヘテロ接合バイポーラ・トランジスタであることを特徴とする、請求項 28 に記載の無線周波電力増幅器。

【請求項 34】

第 1 の電流を制御するように構成された増幅器と、

10

20

30

40

50

前記第1の電流に比例しかつ該電流よりも小さい第2の電流を供給するように構成された基準手段と、

前記第2の電流に応答して、前記増幅器の利得を制御するフィードバック手段と、を備える出力電力制御システム。

【請求項35】

前記フィードバック手段は、前記第2の電流を電力制御電圧に変換するための電流・電圧変換器を含むことを特徴とする、請求項34に記載の出力電力制御システム。

【請求項36】

前記フィードバック手段は、さらに、

供給電圧に結合されて前記第2の電流を導通する抵抗器と、

前記供給電圧と、前記抵抗器によって降下された電圧とを比較して、それらの差を出力電圧として出力するように構成された第1のコンパレータと、

前記出力電圧と基準電圧とを比較して、それらの差を前記電力制御電圧として出力するように構成された第2のコンパレータと、

を備えることを特徴とする、請求項35に記載の出力電力制御システム。

【請求項37】

前記増幅器は、前記第1の電流を導通する幅Wの第1のトランジスタを含むことを特徴とする、請求項36に記載の出力電力制御システム。

【請求項38】

前記基準手段は、前記抵抗器に結合されて前記第2の電流を導通する幅Wの第2のトランジスタを含み、前記第2のトランジスタのゲートを前記第1のトランジスタのゲートに結合して、前記第2の電流が前記第1の電流の1/倍にほぼ等しくなるようにしたことを特徴とする、請求項33に記載の出力電力制御システム。

【請求項39】

が10以上であることを特徴とする、請求項38に記載の出力電力制御システム。

【請求項40】

増幅器の出力電力を制御する方法であって、

出力電流を供給するステップと、

前記出力電流に比例しかつ該電流よりも小さい基準電流を供給するステップと、

前記基準電流を電力制御電圧に変換して前記増幅器の利得を制御するステップと、

を含む方法。

【請求項41】

前記基準電流を前記電力制御電圧に変換するステップは、

供給電圧と抵抗器によって降下された電圧とを比較して、それらの差を出力電圧として送り出すステップと、

前記出力電圧と基準電圧とを比較して、それらの差を前記電力制御電圧として送り出すステップと、

を含むことを特徴とする、請求項40に記載の方法。

【請求項42】

前記出力電流を供給するステップは、

幅Wの出力トランジスタを設けるステップと、

前記出力トランジスタに前記出力電流を導通させるステップと、

を含むことを特徴とする、請求項41に記載の方法。

【請求項43】

前記基準電流を供給するステップは、

幅Wの基準トランジスタを設けるステップと、

前記基準トランジスタのゲートを前記出力トランジスタのゲートに結合するステップと、

前記基準トランジスタに前記基準電流を導通させるステップと、

を含み、

前記基準電流が、前記出力電流の1/倍にほぼ等しいことを特徴とする、請求項42に

10

20

30

40

50

記載の方法。

【発明の詳細な説明】

【0001】

【発明が属する技術分野】

本発明は、出力電力制御システムに関するものであり、とりわけ、無線周波送信機内の電力増幅器からの出力電力を制御するための出力電力制御システムに関するものである。

【0002】

【従来の技術】

無線周波送信機は、さまざまな用途において無線周波信号の送信に用いられている。一般に、送信機は、出力パワー・レベルと、出力信号の立ち上がり及び立下り時間を指定した規格に適合するように設計されている。多くの用途では、出力電力制御回路またはシステムによって、無線周波送信機に用いられている電力増幅器からの出力電力が制御される。あるタイプの出力電力制御回路には、出力信号の一部を電力増幅器の入力にフィードバックして、出力電力を制御するフィードバック・ループが含まれている。用いられる規格の1つに、EIA機構の800MHzセルラ加入者部門(cellular subscriber unit)のための1988年1月のEIA暫定規格IS-19B、3.1.3.3(米国)がある。例えば、この規格には、送信される出力電力信号の立ち上がり及び立下り時間が2ミリ秒未満と指定されている。

【0003】

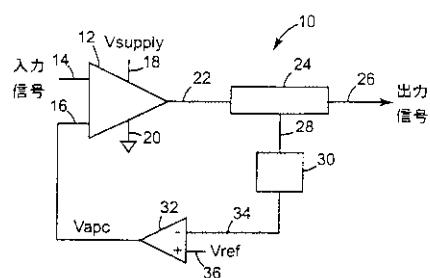

図1には、電力増幅器12の出力電力を制御するための従来の出力電力制御回路10が例示されている。出力電力制御回路10は、検出ダイオード回路(detector diode circuit)を介して送信される出力電力信号の一部を結合する、電圧制御式出力電力制御回路である。電力増幅器12は、電圧供給部18と、接地接続20を備えている。電力増幅器12は、入力14において受信した入力信号を伝送し、出力22に出力信号を送り出す。出力22の出力信号は、カプラ24によって、26に出力信号を送り出すように経路指定される。カプラ24を介して送られる出力電力の一部は、信号検出器30の入力28に経路指定される。信号検出器30は、26における出力信号のピーク・ペルに応答する。信号検出器30は、検出ダイオードを含み、34に検出信号を送り出す。コンパレータ32は、36の基準電圧と34の検出信号を比較する。コンパレータ32は、電力増幅器12の入力16に自動電力制御電圧(Vapc)を供給し、34の検出信号を36の基準電圧に一致させる。

【0004】

出力電力制御回路10によって用いられる従来の出力電力制御アプローチの欠点の1つは、利用可能な出力電力及びシステム効率を低減する損失である。一般に、無線周波増幅システムに利用可能なカプラは、大形で、高価であり、かつ指向特性が悪い。カプラの指向特性が悪いと、とりわけ、無線周波負荷インピーダンスが変動する場合に、出力電力の正確度が低くなる。このアプローチでは、電力増幅器のピーク電流負荷がモニタされないので、動作条件によっては、公称レベルをかなり上回る電流が供給され、その結果、システム効率がさらに低下することになる場合もある。例えば、携帯電話用といったバッテリ用途の場合、その結果は、通話可能時間の短縮ということである。

【0005】

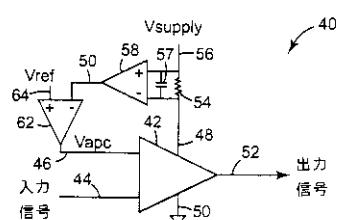

図2には、電力増幅器42の出力電力を制御するために用いられるもう1つの従来式アプローチが例示されている。図2には、56の電圧供給部と直列をなすセンス抵抗器54を利用して、電力増幅器42の電流に比例した電圧を生じさせる、従来の電流制御式出力電力制御回路40が例示されている。電力増幅器42は、44において入力信号を受け取り、52に出力信号を送り出す。電力増幅器42は、センス抵抗器54の一方の端部に結合された電圧供給接続部48と、接地接続部50を備えている。センス抵抗器54は、もう一方の端部が、電圧供給接続部56に結合されている。瞬間電流を分流して、センス抵抗器54を迂回させるべく、電圧供給接続部56と電力増幅器42の電圧供給接続部48との間ににおける、センス抵抗器54の両端間にコンデンサ57が結合されている。これによ

10

20

30

40

50

り、センス抵抗器 5 4 に平均電流が流れる。

【0006】

図2に例示のアプローチでは、フィードバック・ループを利用して、センス抵抗器 5 4 を通る電流を 4 6 の電力制御電圧に変換する。コンパレータ 5 8 は、センス抵抗器 5 4 を通る電流に対応する電圧を 5 0 に発生する。コンパレータ 6 2 は、5 0 の電圧と 6 4 の基準電圧とを比較して、4 6 に自動電力制御電圧 (Vapc) を生じさせ、電力増幅器 4 2 の利得を制御する。

【0007】

この第2のアプローチの欠点の1つは、利用可能な出力電力及びシステム効率を低下させる損失である。センス抵抗器は、コストが高くつき、物理的に大きくなる可能性がある。センス抵抗器によって、大幅な電圧降下が生じ、その結果、電力増幅器の出力電力利用可能度及び効率が低下する可能性もある。このアプローチには、制御ループ内において、全電力増幅器電流をフィードバックさせるという欠点もある。全電流が、必ずしも、出力電力に正比例して変動するとは限らない。この結果、電力制御の正確度が損なわれる可能性がある。

【0008】

【発明が解決しようとする課題】

以上に鑑みて、本発明の目的は、例えば、無線周波送信機の電力増幅器からの出力電力を制御するために用いられるような、改良された出力電力制御システムを提供することにある。

10

20

20

【0009】

【課題を解決するための手段】

本発明の態様の1つによれば、第1の電流を供給するように構成された増幅器と、第1の電流に比例しかつ該電流よりも小さい第2の電流を供給するように構成された基準源 (reference source) と、第2の電流に応答して、増幅器の利得を制御するフィードバック変換器とを含む、出力電力制御システムが得られる。

【0010】

【発明の実施の形態】

望ましい実施態様に関する以下の詳細な説明では、その一部をなし、本発明の実施可能な特定の実施態様を例証するために示された、添付の図面が参照される。もちろん、他の実施態様を利用することも可能であり、本発明の範囲を逸脱することなく、構造上または論理上の変更を加えることも可能である。従って、以下の詳細な説明は、制限を意味するものと解釈すべきではなく、本発明の範囲は、付属の請求項によって規定される。

30

【0011】

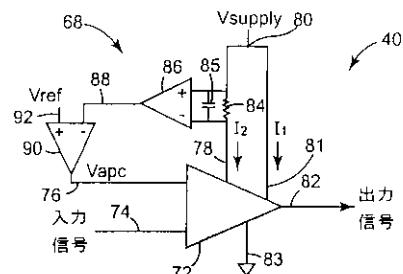

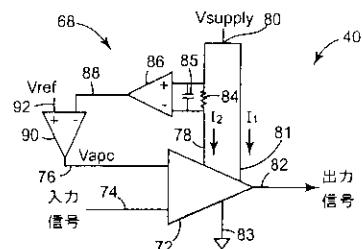

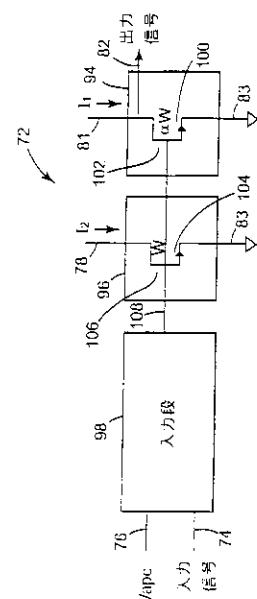

図3は、本発明による、電力増幅器 7 2 の出力電力を制御するための出力電力制御回路またはシステム 4 0 に関する典型的な実施態様の1つを例示したダイアグラムである。例示の実施態様の場合、電力増幅器 7 2 は、7 4 において送信入力信号を受け取り、8 2 に出力信号を送り出す。実施態様の1つでは、7 4 の送信入力信号及び 8 2 の出力信号は、無線周波信号であり、電力増幅器 7 2 は、無線周波増幅器である。典型的な実施態様では、電力増幅器 7 2 は、8 3 でアースに結合されている。

40

【0012】

電力増幅器 7 2 には、ノード 8 0 に施される電圧供給接続部 (Vsupply) に対する2つの接続が含まれている。ノード 8 0 における電圧供給接続部は、第1の電流すなわち出力電流 ( $I_1$ ) を電力増幅器 7 2 の出力段 9 4 (図4に示された) に伝導するライン 8 1 を介して、電力増幅器 7 2 に結合されている。フィードバック抵抗器 8 4 は、ノード 8 0 における電圧供給接続部とライン 7 8 の間に結合されており、ライン 7 8 は、電力増幅器 7 2 の第2の電圧供給接続部に結合されている。瞬間電流を分流して、フィードバック抵抗器 8 4 を迂回させるべく、ノード 8 0 の電圧供給接続とライン 7 8との間ににおける、フィードバック抵抗器 8 4 の両端間にコンデンサ 8 5 が結合されている。これにより、フィードバック抵抗器 8 4 に平均電流が流れる。フィードバック抵抗器 8 4 によって、第2

50

の電流すなわち基準電流 ( $I_2$ ) である前記平均電流が、電力増幅器 7 2 内の基準電流源 9 6 (図 4 に示された) に伝導される。典型的な実施態様の場合、基準電流  $I_2$  は、出力電流  $I_1$  に比例し、それよりも小さい。

#### 【0013】

典型的な実施態様の場合、全体が 6 8 で表示された電流・電圧変換フィードバック・ループによって、電力増幅器 7 2 の利得が制御される。典型的な実施態様の場合、電流・電圧変換フィードバック・ループ 6 8 は、基準電流  $I_2$  を電力制御電圧に変換して、電力増幅器 7 2 の利得を制御する。典型的な実施態様の場合、フィードバック抵抗器 8 4、第 1 のコンパレータ 8 6、及び、第 2 のコンパレータ 9 0 が、共同して、負のフィードバック・ループを構成する。フィードバック抵抗器 8 4 は、該抵抗器 8 4 の両端間に電圧降下を生じさせる基準電流  $I_2$  を導通させる。第 1 のコンパレータ 8 6 は、正の入力がノード 8 0 に結合され、負の入力がフィードバック抵抗器 8 4 の反対側において 7 8 に結合されている。第 1 のコンパレータ 8 6 は、ノード 8 0 の供給電圧と抵抗器 8 4 によって降下された電圧とを比較して、比較された電圧の差を電圧としてライン 8 8 に送り出す。第 2 のコンパレータ 9 0 は、負の入力がライン 8 8 の電圧に結合され、正の入力が 9 2 における基準電圧 ( $V_{ref}$ ) に結合されている。第 2 のコンパレータ 9 0 では、9 2 の基準電圧  $V_{ref}$  とライン 8 8 の電圧が比較され、比較された電圧の差が自動電力制御電圧 ( $V_{apc}$ ) として 7 6 に送り出される。自動電力制御電圧は、電力増幅器 7 2 の入力に加えられ、電力増幅器 7 2 の出力電力を制御することになる。

#### 【0014】

典型的な実施態様の場合、電流・電圧変換フィードバック・ループ 6 8 によって、8 2 の出力信号が 9 2 の基準電圧  $V_{ref}$  と一致するように、電力増幅器 7 2 の利得が制御される。基準電圧  $V_{ref}$  が増 / 減すると、出力電流  $I_1$  及び電力出力レベルに対応する基準電流  $I_2$  が、増 / 減した基準電圧  $V_{ref}$  に追従する。

#### 【0015】

典型的な実施態様の場合、基準電流  $I_2$  は、出力電流  $I_1$  に比例し、それよりも小さい。多くの実施態様において、基準電流  $I_2$  は、出力電流  $I_1$  より小さく、これにより、電流・電圧変換フィードバック・ループ 6 8 に小形で経済的なフィードバック抵抗器 8 4 を用いることが可能になる。結果として、いっそう多様な抵抗器のタイプを用いて、小形で経済的なフィードバック抵抗器 8 4 を実施することが可能になる。これによって、抵抗器の実施態様の選択、及び、ループ利得パラメータの最適化に関する柔軟性が増すことになる。多くの実施態様において、基準電流  $I_2$  が、8 2 における出力信号の出力電力の変動にしっかりと追従し、この結果、より優れた比例追従正確度が得られる。

#### 【0016】

図 4 は、電力増幅器 7 2 の典型的な実施態様の 1 つを例示したダイアグラムである。電力増幅器 7 2 には、増幅器または出力段 9 4、基準電流源 9 6、及び、入力段 9 8 が含まれている。典型的な実施態様の場合、入力段 9 8 は、第 1 の入力が 7 6 において電力制御電圧  $V_{apc}$  に結合され、第 2 の入力が 7 4 において送信入力信号に結合されている。実施態様の 1 つでは、7 6 の電力制御電圧  $V_{apc}$  は、入力段 9 8 内で用いられる電界効果トランジスタ (FET) の 1 つ以上のゲートを制御する。ゲート電圧を変化させて、増幅利得を変化させることによって、7 6 の電力制御電圧  $V_{apc}$  に対応する所定の出力信号が発生することになる。

#### 【0017】

典型的な実施態様の場合、入力段 9 8 は、出力 1 0 8 が基準電流源 9 6 における基準トランジスタ 1 0 4 のゲート 1 0 6 と、出力段 9 4 における出力トランジスタ 1 0 0 のゲート 1 0 2 に結合されている。基準電流源 9 6 は、ライン 7 8 を介して、基準電流  $I_2$  をアース 8 3 に伝導する。出力段 9 4 は、ライン 8 0 を介して、出力電流  $I_1$  をアース 8 3 に伝導する。出力トランジスタ 1 0 0 には、8 2 に出力信号を送り出すドレインが含まれている。実施態様の 1 つでは、基準トランジスタ 1 0 4 及び出力トランジスタ 1 0 0 は、相補型金属酸化膜半導体 (CMOS) トランジスタである。実施態様の 1 つでは、基準トラン

10

20

30

40

50

ジスタ104及び出力トランジスタ100は、エンハンスマント・モード・スードモルフィック高電子移動度(E-pHEMT)トランジスタである。実施態様の1つでは、基準トランジスタ104及び出力トランジスタ100は、シリコン・バイポーラ・トランジスタである。実施態様の1つでは、基準トランジスタ104及び出力トランジスタ100は、ヘテロ接合バイポーラ・トランジスタである。

#### 【0018】

典型的な実施態様の場合、基準トランジスタ104は、より小さい電流を導通するため、出力トランジスタ100より小さくなるように、比例したサイズが付与されている。CMOSトランジスタのような半導体素子のゲートの幅対長さ(今後は「W/L」と称する)の比によって、トランジスタ・サイズ、及び、トランジスタによって導通可能な最大電流が決まる。一般に、ゲートの長さLは、トランジスタの製作に用いられる半導体製作プロセスの最小特徴サイズに対応する固定値である。従って、トランジスタ・サイズは、一般に、トランジスタのゲート幅Wを変更することによって変更可能である。2つの異なるゲートW/L比を有し、ある特定のウェーハ上にごく近接して製作される2つの特定のトランジスタは、その相対電流比が、製作されるある特定ロットのウェーハ内におけるウェーハ毎の最小限の変動に一致する。実施態様の1つでは、基準トランジスタ104及び出力トランジスタ100は、シリコン・バイポーラ・トランジスタであり、トランジスタが導通する最大電流は、トランジスタのエミッタ幅を変更することによって制御される。実施態様の1つでは、基準トランジスタ104及び出力トランジスタ100は、ヘテロ接合バイポーラ・トランジスタであり、トランジスタが導通する最大電流は、トランジスタのエミッタ幅を変更することによって制御される。10 20

#### 【0019】

例示の実施態様では、出力トランジスタ100の幅はWであり、基準トランジスタ104の幅はWである。因数 $\alpha$ は、基準電流 $I_2$ 対出力電流 $I_1$ の電流比を指定するために用いられる定数である。多くの実施態様において、回路に対する損失を最小限に抑え、フィードバック抵抗器84によって生じる電力損失を低減するため、基準電流 $I_2$ は、出力電流 $I_1$ よりも小さい。基準トランジスタ104のゲート106は、出力トランジスタ100のゲート102に結合されているので、基準電流 $I_2$ の値は、出力電流 $I_1$ の1/10倍にほぼ等しい。典型的な実施態様の場合、ゲート長Lは、基準トランジスタ104及び出力トランジスタ100の両方ともほぼ同じである。他の実施態様には、基準トランジスタ104のゲート長Lが、出力トランジスタ100のゲート長Lと同じにはならないものもある。30

#### 【0020】

基準トランジスタ104と出力トランジスタ100のゲートW/L比は、任意の適合する値とすることが可能である。ある実施態様では、出力トランジスタ100が出力信号を82に送り出すので、出力トランジスタ100のW/L比は、5000を超える比較的大きい値になる。この実施態様の場合、基準トランジスタ104と出力トランジスタ100のW/L比は5000より小さい。ある実施態様では、 $\alpha$ の値は10であり、従って、基準トランジスタ104のW/L比が出力トランジスタ100のW/L比の1/10になって、基準電流 $I_2$ が出力電流 $I_1$ の1/10倍にほぼ等しくなる。ある実施態様では、 $\alpha$ の値が100である。従って、基準トランジスタ104のW/L比が出力トランジスタ100のW/L比の1/100になり、基準電流 $I_2$ が出力電流 $I_1$ の1/100倍にほぼ等しくなる。40

#### 【0021】

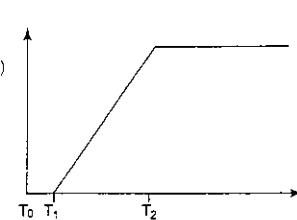

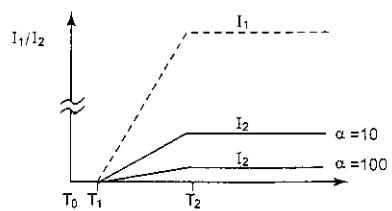

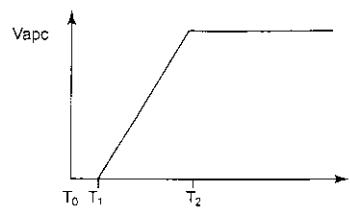

図5Aは、出力電力制御回路40の典型的な実施態様に関する出力信号電力対時間を例示したダイアグラムである。図5Bは、出力電力制御回路40の典型的な実施態様に関する出力電流 $I_1$ 及び基準電流 $I_2$ 対時間を例示したダイアグラムである。図5Cは、出力電力制御回路40の典型的な実施態様に関する自動電力制御電圧V<sub>apc</sub>対時間を例示したダイアグラムである。

#### 【0022】

10

20

30

40

50

典型的な実施態様の場合、時間  $T_0$  から時間  $T_1$  までは、電力増幅器 72 は起動せず、出力信号を 82 に送り出さない；基準トランジスタ 104 及び出力トランジスタ 100 は、オフになる；図 5B に例示の基準電流  $I_2$  及び出力電流  $I_1$  はゼロである；図 5A に例示の出力信号電力はゼロである；図 5C に例示の自動電力制御電圧  $V_{apc}$  はゼロである。

【0023】

典型的な実施態様の場合、時間  $T_1$  において、74 の送信入力信号が電力増幅器 72 によって受信される。74 の送信入力信号は、電力増幅器 72 によってある利得が得られるよう増幅され、出力信号 82 における送信電力が、時間  $T_1$  ~ 時間  $T_2$  間において増大し始める。典型的な実施態様の場合、 $T_1$  から  $T_2$  まで、出力トランジスタ 100 が、出力電流  $I_1$  を導通し始め、出力電流  $I_1$  の値が増大し始める。基準トランジスタ 104 のゲート 106 は、出力トランジスタ 100 のゲート 102 に結合されているので、基準電流  $I_2$  も同様に増大し始める。典型的な実施態様の場合、基準電流  $I_2$  の量は、出力電流  $I_1$  の量よりも少ない。図 5B には、出力電流  $I_1$  が点線で例示され、 $= 10$  及び  $= 100$  の場合の基準電流  $I_2$  の 2 つの値が実線で例示されている。典型的な実施態様の場合、基準電流  $I_2$  が出力電流  $I_1$  よりかなり小さいので、本発明の例証を単純化するため、電流軸は、中絶した軸として示されている。典型的な実施態様では、 $T_1$  から  $T_2$  まで、 $= 10$  及び  $= 100$  の場合の基準電流  $I_2$  の値は、それぞれ、出力電流  $I_1$  の  $1/10$  及び  $1/100$  の値にほぼ等しい。

【0024】

典型的な実施態様の場合、図 5C に例示の電力制御電圧  $V_{apc}$  は、フィードバック抵抗器 84、第 1 のコンパレータ 86、及び、第 2 のコンパレータ 90 を含む負のフィードバック・ループの出力である。典型的な実施態様の場合、負のフィードバック・ループの遅延は、ごくわずかであるため、電力制御電圧  $V_{apc}$  は、基準電流  $I_2$  にほぼ正比例して上昇し、従って、図 5A における出力信号電力の立ち上がり時間は最短に抑えられる。結果として、電力増幅器 72 の 82 における出力信号電力レベルは、82 における出力信号レベルが 76 における自動電力制御電圧  $V_{apc}$  に一致する時間  $T_2$  まで、自動電力制御電圧  $V_{apc}$  の変化に迅速に追従する。典型的な実施態様の場合、76 の自動電力制御電圧  $V_{apc}$  は、82 における出力信号電力レベルが、やはり、92 における基準電圧  $V_{ref}$  に一致するように、92 における基準電圧  $V_{ref}$  によって制御される。

【0025】

典型的な実施態様の場合、 $T_2$  において、82 における所望の出力信号電力レベルに達し、図 5C に例示の 76 における電力制御電圧  $V_{apc}$  は、定常状態に達する。図 5B に例示の出力電流  $I_1$  及び基準電流  $I_2$  も定常状態に達する。出力電流  $I_1$  が定常状態値のため、図 5A に例示の出力信号は定常状態値である。

【0026】

本明細書では、望ましい実施態様の解説を目的として、特定の実施態様について例証し、説明してきたが、通常の当業者には明らかのように、本発明の範囲を逸脱することなく、図示され、解説された特定の実施態様の代わりに、同じ目的の達成が見込まれる、多種多様な代替及び/または同等実施例を用いることが可能である。化学、機械、電気機械、電気、及び、コンピュータの技術者には容易に明らかになるように、本発明は多種多様な実施態様で実施することが可能である。本出願は、本明細書において論述した望ましい実施態様に対するいかなる改変または変更をも包含することを意図したものである。従って、本発明は、明らかに、請求項及びその同等物による制限だけしか受けないことを意図したものである。

【図面の簡単な説明】

【図 1】従来の電圧制御式出力電力制御回路を例示した図である。

【図 2】従来の電圧制御式出力電流制御回路を例示した図である。

【図 3】本発明による出力電力制御回路の典型的な実施態様の 1 つを例示したダイアグラムである。

【図 4】電力増幅器の典型的な実施態様の 1 つを例示したダイアグラムである。

10

20

30

40

50

【図5A】出力電力制御回路の典型的な実施態様に関する出力信号電力対時間を例示したダイアグラムである。

【図5B】出力電力制御回路の典型的な実施態様に関する出力電流  $I_1$  及び基準電流  $I_2$  対時間を例示したダイアグラムである。

【図5C】出力電力制御回路の典型的な実施態様に関する電力制御電圧対時間を例示したダイアグラムである。

【符号の説明】

6 8 電流・電圧変換フィードバック・ループ

7 2 電力増幅器

8 4 フィードバック抵抗器

8 6 , 9 0 コンパレータ

1 0 0 , 1 0 4 トランジスタ

10

【図1】

【図2】

【図3】

【図4】

【図5A】

【図 5 B】

【図 5 C】

---

フロントページの続き

(72)発明者 バルトロメウス・エイチ・ダブリュー・イー・ヤンセン

アメリカ合衆国カリフォルニア州 94044, パシフィカ, スタンリー・アヴェニュー 216

(72)発明者 レイ・マイロン・パークハースト, ジュニア

アメリカ合衆国カリフォルニア州 94538, フリーモント, アルゴノート・ウェイ 39120

, #273

F ターム(参考) 5J100 JA01 QA01 SA01

5J500 AA01 AA41 AC36 AF04 AF17 AH02 AH06 AH09 AH25 AH29

AK01 AK09 AM13 AS14 AT02 NM01 NN01 RG07 WU08

5K060 BB07 CC04 CC11 EE04 HH06 JJ02 JJ08 KK01 LL01 LL24