(19) **日本国特許庁(JP)**

# (12)特 許 公 報(B2)

(11)特許番号

特許第6151110号 (P6151110)

(45) 発行日 平成29年6月21日(2017.6.21)

(24) 登録日 平成29年6月2日(2017.6.2)

(51) Int.Cl. F 1

**HO2M 3/155 (2006.01)** HO2M 3/155 R HO2M 3/155 Y

請求項の数 11 (全 20 頁)

(21) 出願番号 特願2013-137780 (P2013-137780) (22) 出願日 平成25年7月1日 (2013.7.1)

(65) 公開番号 特開2015-12742 (P2015-12742A)

(43) 公開日 平成27年1月19日 (2015. 1. 19) 審査請求日 平成28年1月15日 (2016. 1. 15) ||(73)特許権者 000005108

株式会社日立製作所

東京都千代田区丸の内一丁目6番6号

||(74)代理人 110000350

ポレール特許業務法人

(72)発明者 増田 徹

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所 中央研究所内

(72) 発明者 畑中 歩

茨城県日立市大みか町七丁目1番1号 株

式会社日立製作所 日立研究所内

|(72)発明者 森 和久 |

茨城県日立市大みか町七丁目1番1号 株

式会社日立製作所 日立研究所内

最終頁に続く

(54) 【発明の名称】電力変換装置

## (57)【特許請求の範囲】

## 【請求項1】

直流電源と並列に、平滑コンデンサ回路と、スイッチング素子による第1の直列回路と、スナバ回路による第2の直列回路とを接続するとともに、前記第1の直列回路の前記スイッチング素子の接続点と前記第2の直列回路の前記スナバ回路の接続点との間を接続して構成された電力変換装置であって、

前記直流電源と並列に、第1のコンデンサとリアクタンスとの並列回路に第2のコンデンサを直列接続して構成された補償インピーダンス回路が接続されるとともに、

前記補償インピーダンス回路の入出力間のインピーダンスの周波数特性は、少なくとも 1 つ以上の極周波数と1 つ以上の零点周波数とを有しており、

前記補償インピーダンス回路の前記極周波数および前記零点周波数は、前記電力変換装置のスイッチングに伴って発生するサージ電圧振動に含まれる共振周波数に対して、前記零点周波数の1つが低周波側に配置され、前記極周波数の1つが高周波側に配置されることを特徴とする電力変換装置。

## 【請求項2】

請求項1に記載の電力変換装置において、

前記スイッチング素子による前記第1の直列回路はモジュールを構成し、前記モジュールの正電源端子と負電源端子との間に前記補償インピーダンス回路が接続されることを特徴とする電力変換装置。

#### 【請求項3】

請求項1または請求項2に記載の電力変換装置において、

前記スイッチング素子による前記第1の直列回路は正電源端子と負電源端子とを備えたモジュールを構成し、かつ上側アームを構成する前記スイッチング素子のドレイン近傍と、下側アームを構成する前記スイッチング素子のソース近傍との間に前記補償インピーダンス回路が接続される

ことを特徴とする電力変換装置。

#### 【請求項4】

直流電源と、

配線を介して前記直流電源に接続される平滑コンデンサと、

正電源配線および負電源配線を介して前記平滑コンデンサと接続されるパワー半導体モジュールと、

前記パワー半導体モジュールに接続されるゲート駆動制御回路と、

前記パワー半導体モジュールの中間出力端子に接続される誘導性負荷と、

前記パワー半導体モジュールの正電源端子と前記中間出力端子との間および負電源端子と前記中間出力端子との間に接続されるスナバ回路と、

前記パワー半導体モジュールの前記正電源端子と前記負電源端子とに接続される補償インピーダンス回路と

を備えた電力変換装置であって、

前記補償インピーダンス回路は、入出力の2端子を有し、入出力間のインピーダンスの周波数特性は、少なくとも1つ以上の極周波数と1つ以上の零点周波数とを有し、前記電力変換装置のスイッチングに伴って発生するサージ電圧振動に含まれる周波数成分のうち抑制しようとする周波数に対して、前記零点周波数の一つが低周波側に配置され、前記極周波数の1つが高周波側に配置され、前記電力変換装置のサージ電圧振動の振幅を抑制する

ことを特徴とする電力変換装置。

### 【請求項5】

請求項4に記載の電力変換装置において、

前記補償インピーダンス回路は、第1のコンデンサの一方の端子と第2のコンデンサの一方の端子とを直列接続し、前記第2のコンデンサの2つの端子間にインダクタンスを並列接続し、前記第1のコンデンサの他方の端子と前記第2のコンデンサの他方の端子との2端子を前記補償インピーダンス回路の入出力端子とすることにより構成され、

前記補償インピーダンス回路のインピーダンスの周波数依存性は、<u>前記零点周波数の1</u>つを低周波側に配置し、<u>前記極周波数の1つ</u>を高周波側に配置するよう、前記第1のコンデンサの容量、前記第2のコンデンサの容量、および前記インダクタンスの少なくともいずれか1つが調整されていることにより調整されている

ことを特徴とする電力変換装置。

#### 【請求項6】

請求項5に記載の電力変換装置において、

前記補償インピーダンス回路は、絶縁基板を挟む複数の導体で構成され、

前記複数の導体のうちの第1の導体と第2の導体との間に前記第1のコンデンサが構成され、前記複数の導体のうちの前記第1の導体と第3の導体との間に前記第2のコンデンサが構成され、前記第3の導体によって前記インダクタンスが構成され、

前記第2の導体および前記第3の導体にそれぞれ接続された2つの接続端子が、前記パワー半導体モジュールの前記正電源端子と前記負電源端子とに接続されることを特徴とする電力変換装置。

## 【請求項7】

請求項6に記載の電力変換装置において、

前記補償インピーダンス回路は、前記第2の導体および前記第3の導体の少なくともいずれか一方の導体パターンの一部の切り離しにより、前記第1のコンデンサの容量および前記第2のコンデンサの容量の少なくともいずれか一方を変更することが可能な構成であ

20

10

30

30

40

1)、

前記第1のコンデンサの容量および前記第2のコンデンサの容量の少なくともいずれか一方の変更は、前記電力変換装置のサージ電圧振動の振幅の抑制を最大にするように行われる

ことを特徴とする電力変換装置。

#### 【請求項8】

直流電源と、

配線を介して前記直流電源に接続される平滑コンデンサと、

正電源配線および負電源配線を介して前記平滑コンデンサと接続されるパワー半導体モジュールと、

該パワー半導体モジュールに接続されるゲート駆動制御回路と、

前記パワー半導体モジュールの中間出力端子に接続される誘導性負荷と、

前記パワー半導体モジュールの正電源端子と前記中間出力端子との間および負電源端子と前記中間出力端子との間に接続されるスナバ回路と、

前記パワー半導体モジュールに内包される補償インピーダンス回路と

を備えた電力変換装置であって、

前記補償インピーダンス回路は、入出力の2端子を有し、入出力間のインピーダンスの周波数特性は、少なくとも1つ以上の極周波数と1つ以上の零点周波数とを有し、前記電力変換装置のスイッチングに伴って発生するサージ電圧振動に含まれる周波数成分のうち抑制しようとする周波数に対して、前記零点周波数の一つが低周波側に配置され、前記極周波数の1つが高周波側に配置され、前記電力変換装置のサージ電圧振動の振幅を抑制する

ことを特徴とする電力変換装置。

#### 【請求項9】

請求項8に記載の電力変換装置において、

前記パワー半導体モジュールは、正電源側の主端子と、負電源側の主端子と、中間出力端子と、前記主端子の群が接続される第1の絶縁基板とを有し、

前記補償インピーダンス回路は、前記第1の絶縁基板に接続されることを特徴とする電力変換装置。

## 【請求項10】

請求項8または請求項9に記載の電力変換装置において、

前記パワー半導体モジュールは、絶縁基板を挟む複数の導体で構成され、

前記補償インピーダンス回路は、前記複数の導体のうちの第1の導体が前記複数の導体のうちの第2の導体との間に絶縁基板を誘電体として見込む第1の並行平板容量を構成し、前記複数の導体のうちの第3の導体が前記第2の導体との間に絶縁基板を誘電体として見込む第2の並行平板容量を構成し、前記第3の導体の一部にインダクタンスを発生するミアンダ状パターンが形成され、さらに前記ミアンダ状パターンの一端が第1のビアホール群によって前記第2の導体と接続され、前記第1の導体と前記第3の導体とをそれぞれ入力端子と出力端子とすることにより構成され、

前記第1の導体は前記複数の導体のうちの第4の導体と接続され、前記第3の導体は前記複数の導体のうちの第5の導体と接続され、前記第4の導体および前記第5の導体はそれぞれ正電源端子用主端子および負電源端子用主端子と接続されてそれぞれ前記パワー半導体モジュールの前記正電源端子および前記負電源端子に接続され、

前記第4の導体は第1のスイッチング素子チップのドレインおよび還流ダイオードチップのカソードと接続され、前記複数の導体のうちの第6の導体はボンディングワイヤを介して前記第1のスイッチング素子チップのゲート端子と接続され、

前記複数の導体のうちの第7の導体は、前記第1のスイッチング素子チップのソースおよび前記還流ダイオードチップのアノードとボンディングワイヤを介して接続され、かつ、第2のスイッチング素子チップのドレインおよび還流ダイオードチップのカソードと接続され、かつ、前記パワー半導体モジュールの中間端子の主端子と接続され、

10

20

30

40

前記複数の導体のうちの第8の導体は、ボンディングワイヤを介して前記第2のスイッチング素子チップのゲート端子と接続され、

前記複数の導体のうちの第9の導体は、前記第2のスイッチング素子チップのソースおよび前記還流ダイオードチップのアノードとボンディングワイヤを介して接続され、かつ、第2のビアホール群を介して前記複数の導体のうち裏面側導体である第10の導体と接続され、

前記第10の導体は、第3のビアホール群を介して前記第5の導体と接続され、

前記補償インピーダンス回路は、前記パワー半導体モジュールと共通の混載基板上に形成される

ことを特徴とする電力変換装置。

【請求項11】

請求項8乃至請求項10のいずれか1項に記載の電力変換装置において、

前記補償インピーダンス回路の入出力端子間の絶縁耐圧は、前記電力変換装置の前記直流電源の電圧の2倍以上の絶縁耐圧である

ことを特徴とする電力変換装置。

【発明の詳細な説明】

【技術分野】

[0001]

本発明は、電力変換装置に関し、特に半導体スイッチング素子を有する電力変換装置に関する。

20

10

【背景技術】

[0002]

スイッチングサージを抑えることができる従来の電力変換装置として、特許文献 1 に示すものが知られている。この電力変換装置は、直流電源ラインと、直流中間コンデンサと、インバータを備えている

このうち直流電源ラインは、直流電圧を出力するコンバータの出力端子に接続されている。直流中間コンデンサは、コンバータの出力する直流電圧を平滑化して安定化させる素子である。直流中間コンデンサは直流電源ラインに接続されている。インバータは直流中間コンデンサによって平滑化された直流電源電圧を3相交流電圧に変換する回路である。インバータは、直流電源ラインに接続されている。

30

[0003]

さらにこの電力変換装置は、直流電源ラインに並列接続されるコンデンサを備えている。このコンデンサと直流電源ラインのインダクタンスによってLC共振回路が構成される。このLC共振回路によって、インバータのスイッチングに伴って発生するスイッチングサージを抑えることができる。

【先行技術文献】

【特許文献】

[0004]

【特許文献1】特開2010-41790号公報

【発明の概要】

40

【発明が解決しようとする課題】

[0005]

特許文献1の電力変換装置では、スイッチングサージを抑えるために直流中間コンデンサ以外に、別途コンデンサを用意する必要がある。そのうえこのコンデンサは、サージ現象で発生する電荷を吸収するために、大きな容量のものである必要がある。

[0006]

また、特許文献 1 の図 8 には等価回路として配線インダクタンスLs 1 およびLs 2 が明示されているが、実際の電力変換回路の配線インダクタンスは分布的に発生するうえに近傍の別配線を流れる電流の影響をうけてその実効的なインダクタンスを把握することは困難である。従って、特許文献 1 に記載されているように、配線インダクタンスを明確に

把握して、別途調達するコンデンサを用いて、所望の並列共振回路を構成することは難しい。

#### [0007]

さらに、急峻なスイッチング(高いd V / d t および d i / d t でのスイッチング)を行う場合には、従来の低い d i / d t では無視してきた小さな寄生インダクタンスの影響が顕著となるため、大容量の体格の大きなコンデンサでは、そのリード配線や端子などに生じる寄生インダクタンスの影響が無視できなくなり、新たなサージ現象の原因となる悪循環となる。

## [0008]

従って、スイッチングサージを抑制するためには、特許文献1の図9に記載のように、スナバダイオードDsとスナバ抵抗Rsとで構成した並列回路にコンデンサCsを直列に接続してスナバ回路をスイッチング素子と並列に接続する対策方法が一般的である。

#### [0009]

しかしながら、前述のコンデンサ Csにおいてもその配線インダクタンスが発生し、スイッチング素子の端子間電圧(例えば、ドレイン・ソース間)においてサージ電圧とそれに連続する電圧共振振動が発生する。

#### [0010]

このような共振現象は、スイッチングサージ抑制のために追加したスナバ回路や、スイッチング素子を格納するパワーモジュールの寄生インダクタンス、スイッチング素子の寄生容量等が主要因である。この共振によって発生する放射ノイズや伝導ノイズの抑制には、別途対策が必要となる。

#### [0011]

電力変換器のスイッチング動作時のうち、特にターンオフ時にはサージピーク電圧が発生し、その後、電流変化のある経路の共振インピーダンスに起因するサージ電圧振動が継続する。従来はスナバ回路による抑制を行ったがスイッチングが急峻である場合、スナバ回路内の寄生 L やモジュールの寄生容量などにより、数十M H z 以上での高周波共振が発生してしまう。

#### [0012]

本発明は、上述した問題を解決するべきなされたものであって、その目的は、半導体スイッチング素子を有する電力変換装置において、共振振動の収束を速やかに実現し、その放射ノイズとなる高調波の電力レベルを低減することにある。

【課題を解決するための手段】

#### [0013]

そこで本発明の電力変換装置は、直流電源と並列に、平滑コンデンサ回路と、スイッチング素子による第1の直列回路と、スナバ回路による第2の直列回路とを接続するとともに、前記第1の直列回路の前記スイッチング素子の接続点と前記第2の直列回路の前記スナバ回路の接続点との間を接続して構成された電力変換装置であって、前記直流電源と並列に、第1のコンデンサとリアクタンスとの並列回路に第2のコンデンサを直列接続して構成された補償インピーダンス回路が接続されることを特徴とする。

## 【発明の効果】

## [0014]

本発明によれば、スイッチングに伴って発生するサージ電圧振動を抑制できる電力変換回路を提供することができる。

## 【図面の簡単な説明】

## [0015]

- 【図1】実施例1に係る電力変換装置の構成例を示す図。

- 【図2】実施例1に適用できる補償インピーダンス回路8の実装構成を示した図。

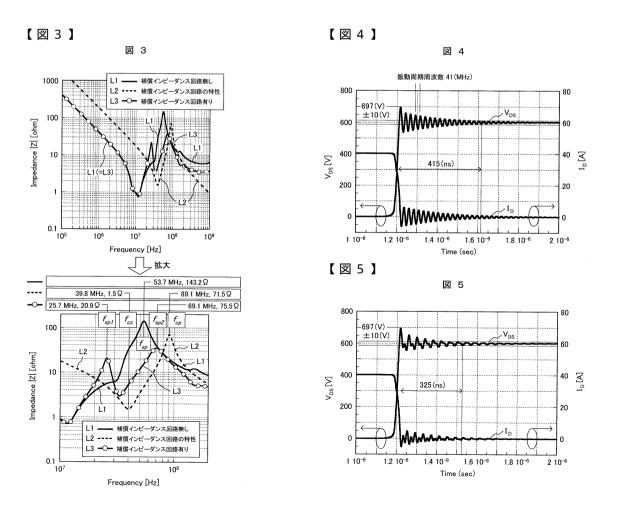

- 【図3】電力変換装置内のインピーダンスの周波数依存性を示した図。

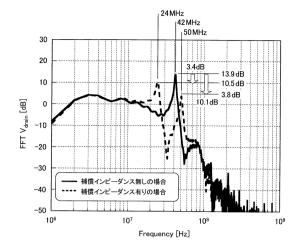

- 【図4】補償インピーダンスを用いない従来方式での過渡応答波形を示す図。

- 【図5】補償インピーダンスを用いた本発明方式での過渡応答波形を示す図。

20

10

30

40

【図6】図4、図5のドレイン・ソース間電圧VDSのFFT解析結果を示す図。

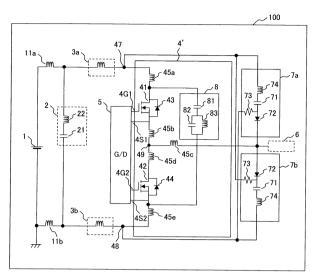

【図7】実施例2に係る電力変換装置の構成例を示す図。

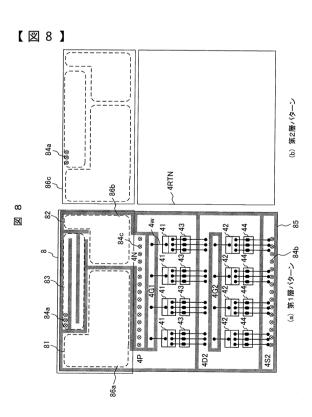

【図8】実施例3に係る電力変換装置の構成例を示す図。

【発明を実施するための形態】

### [0016]

本発明では、共振周波数にて増加するインピーダンスの周波数特性を考慮し、インピーダンスの値を低減させ、かつ複数周波数に分散させる手段、およびサージ電圧振動を抑制する手段を提供する。

## [0017]

上記課題を解決する複数の本発明のうちの一例を挙げるならば以下のようになる。すなわち、本発明の電力変換装置は、直流電源と並列に、平滑コンデンサ回路と、スイッチング素子による第1の直列回路と、スナバ回路による第2の直列回路とを接続するとともに、前記第1の直列回路の前記スイッチング素子の接続点と前記第2の直列回路の前記スナバ回路の接続点との間を接続して構成された電力変換装置であって、前記直流電源と並列に、第1のコンデンサとリアクタンスとの並列回路に第2のコンデンサを直列接続して構成された補償インピーダンス回路が接続されることを特徴とする。

### [0018]

ここで、例えば前記補償インピーダンス回路の入出力間のインピーダンスの周波数特性は、少なくとも1つ以上の極周波数と1つ以上の零点周波数とを有している構成としてもよい。

#### [0019]

さらには、例えば前記補償インピーダンス回路の前記極周波数および前記零点周波数は、前記電力変換装置のスイッチングに伴って発生するサージ電圧振動に含まれる共振周波数に対して、前記零点周波数の1つが低周波側に配置され、前記極周波数の1つが高周波側に配置される構成としてもよい。

### [0020]

これらの各構成においては、さらに、前記スイッチング素子による前記第1の直列回路 はモジュールを構成し、前記モジュールの正電源端子と負電源端子との間に前記補償イン ピーダンス回路が接続される構成としてもよい。

## [0021]

また、同じく上記の各構成においては、さらに、前記スイッチング素子による前記第1の直列回路は正電源端子と負電源端子とを備えたモジュールを構成し、かつ上側アームを構成する前記スイッチング素子のドレイン近傍と、下側アームを構成する前記スイッチング素子のソース近傍との間に前記補償インピーダンス回路が接続される構成としてもよい

#### [0022]

本発明の電力変換装置のより具体的な1つの構成は、例えば、直流電源と、配線を介して直流電源に接続される平滑コンデンサと、正電源配線および負電源配線を介して平滑コンデンサと接続されるパワー半導体モジュールと、パワー半導体モジュールに接続される誘導性負荷と、パワー半導体モジュールの中間出力端子に接続される誘導性中間出力端子との間に接続されるスナバ回路と、パワー半導体モジュールの正電源端子と中間出力端子との間および負電源端子と中間出力端子との間に接続されるスナバ回路と、パワー半導体モジュールの正電源端子と負電に接続される補償インピーダンス回路とを備えた電力変換装置であって、補償インピーダンス回路は、入出力間のインピーダンスの周波数特性は、少なくとも1つ以上の極周波数と1つ以上の零点周波数とを有し、電力変換装置のスチングに伴って発生するサージ電圧振動に含まれる周波数成分のうち抑制しようとする。配置され、電力変換装置のサージ電圧振動の振幅を抑制することを特徴とする。

## [0023]

ここで、前記補償インピーダンス回路は、第1のコンデンサの一方の端子と第2のコン

10

20

40

50

デンサの一方の端子とを直列接続し、前記第2のコンデンサの2つの端子間にインダクタンスを並列接続し、前記第1のコンデンサの他方の端子と前記第2のコンデンサの他方の端子との2端子を前記補償インピーダンス回路の入出力端子とすることにより構成され、前記補償インピーダンス回路のインピーダンスの周波数依存性は、前記第1の零点周波数の1つを低周波側に配置し、前記第1の極周波数の1つを高周波側に配置するよう、前記第1のコンデンサの容量、前記第2のコンデンサの容量、および前記インダクタンスの少なくともいずれか1つが調整されていることにより調整されている構成としてもよい。

### [0024]

さらには、前記補償インピーダンス回路は、絶縁基板を挟む複数の導体で構成され、前記複数の導体のうちの第1の導体と第2の導体との間に前記第1のコンデンサが構成され、前記複数の導体のうちの前記第1の導体と第3の導体との間に前記第2のコンデンサが構成され、前記第3の導体によって前記インダクタンスが構成され、前記第2の導体および前記第3の導体にそれぞれ接続された2つの接続端子が、前記パワー半導体モジュールの前記正電源端子と前記負電源端子とに接続される構成としてもよい。

#### [0025]

またさらには、前記補償インピーダンス回路は、前記第2の導体および前記第3の導体の少なくともいずれか一方の導体パターンの一部の切り離しにより、前記第1のコンデンサの容量および前記第2のコンデンサの容量の少なくともいずれか一方を変更することが可能な構成であり、前記第1のコンデンサの容量および前記第2のコンデンサの容量の少なくともいずれか一方の変更は、前記電力変換装置のサージ電圧振動の振幅の抑制を最大にするように行われる構成としてもよい。

#### [0026]

本発明の電力変換装置のより具体的な他の1つの構成は、例えば、直流電源と、配線を介して前記直流電源に接続される平滑コンデンサと、正電源配線および負電源配線を介して前記平滑コンデンサと接続されるパワー半導体モジュールと、該パワー半導体モジュールの中間出力端子に接続される誘導性負荷と、前記パワー半導体モジュールの中間出力端子との間および負電源端子と前記中間出力端子との間に接続されるスナバ回路と、前記パワー半導体モジュールの正電源端子と前記中間出力端子との間に接続されるスナバ回路と、前記パワー半導体モジュールの直路と、前記パワー半導体モジュールの内間と、前記パワー半導体モジュールに内包される補償インピーダンス回路とを備えた電力変換装置である、前記補償インピーダンス回路は、入出力の2端子を有し、入出力間のインピーダンスの周波数特性は、少なくとも1つ以上の極周波数と1つ以上の零点周波数とを有し、前記電力変換装置のスイッチングに伴って発生するサージ電圧振動に含まれる周波数成分のうち抑制しようとする周波数に対して、前記零点周波数の一つが低周波側に配置され、前記極周波数の1つが高周波側に配置され、前記電力変換装置のサージ電圧振動の振幅を抑制することを特徴とする。

## [0027]

ここで、前記パワー半導体モジュールは、正電源側の主端子と、負電源側の主端子と、中間出力端子と、前記主端子群が接続される第1の絶縁基板とを有し、前記補償インピーダンス回路は、前記第1の絶縁基板に接続される構成としてもよい。

#### [0028]

これらの各構成においては、さらに、前記パワー半導体モジュールは、絶縁基板を挟む複数の導体で構成され、前記補償インピーダンス回路は、前記複数の導体のうちの第1の導体が前記複数の導体のうちの第2の導体との間に絶縁基板を誘電体として見込む第1の並行平板容量を構成し、前記第2の導体との間に絶縁基板を誘電体として見込む第2の並行平板容量を構成し、前記第3の導体の一部にインダクタンスを発生するミアンダ状パターンが形成され、さらに前記ミアンダ上パターンの一端が第1のビアホール群によって前記第2の導体と接続され、前記第1の導体と前記第3の導体とをそれぞれ入力端子と出力端子とすることにより構成され、前記第1の導体は前記複数の導体のうちの第5の導体と接続され、前記第3の導体はそれぞれ正電源端子用

10

20

30

40

主端子および負電源端子用主端子と接続されてそれぞれ前記パワー半導体モジュールの前記正電源端子および前記負電源端子に接続され、前記第4の導体は第1のスイッチング素子チップのドレインおよび還流ダイオードチップのカソードと接続され、前記複数の導体のうちの第6の導体はボンディングワイヤを介して前記第1のスイッチング素子チップのゲート端子と接続され、前記複数の導体のうちの第7の導体は、前記第1のスイッチング素子チップのソースおよび前記還流ダイオードチップのアノードとボンディングワイヤを介して接続され、かつ、第2のスイッチング素子チップのドレインおよび還流ダイオードチップのカソードと接続され、かつ、前記パワー半導体モジュールの第9の第9のスイッチング素子チップのゲート端子と接続され、前記複数の導体のうちの第9のアカースおよび前記環流ダイオードチップのアイッチング素子チップのソースおよび前記還流ダイオードチップのアイッチング素子チップのソースおよび前記還流ダイオードチップのアカードとボンディングワイヤを介して接続され、かつ、第2のビアホール群を介して前記複数の導体のうち裏面側導体である第10の導体と接続され、前記補償インピーダンス回路は、前記パワー半導体モジュールと共通の混載基板上に形成される構成としてもよい。

[0029]

また、これらの各構成においては、さらに、前記補償インピーダンス回路の入出力端子間の絶縁耐圧は、前記電力変換装置の前記直流電源電圧の2倍以上の絶縁耐圧である構成としてもよい。

[0030]

以下、本発明の実施例について図面を用いて説明する。

【実施例1】

[0031]

実施例1では、サージ電圧の振動を抑制する電力変換装置100の例を説明する。

[0032]

図1に実施例1に係る電力変換装置100の構成図を示す。図1において、電力変換装置100は、直流電源1、平滑コンデンサ2、正電源配線3a、負電源配線3b、パワー半導体モジュール4、ゲート駆動制御回路5、誘導性負荷6、スナバ回路7、補償インピーダンス回路8で構成されている。

[0033]

このうち直流電源1は寄生抵抗と寄生インダクタンスを含む配線11aおよび11bを介して平滑コンデンサ2の両端に接続されている。尚、以降の説明では配線に伴う寄生抵抗については特に必要がない限り説明を割愛する。配線には寄生抵抗と寄生インダクタンスが生じるが、本発明に関しては寄生抵抗の値が主要ではないためである。

[0034]

平滑コンデンサ 2 は、主コンデンサ 2 1 と直列に生じる寄生インダクタンス 2 2 で構成される。

[0035]

正電源配線3aおよび負電源配線3bは、平滑コンデンサ2の両端をパワー半導体モジュール4の正電源端子47と負電源端子48に接続されるが、この部分の配線は主にインダクタンス(寄生インダクタンス)として機能する。

[0036]

パワー半導体モジュール4は、上アームではスイッチング素子41と還流ダイオード43を逆並列接続し、下アームではスイッチング素子42と還流ダイオード44を逆並列接続した構成をとる。上下アームの接続点が中間端子49である。スイッチング素子41のゲート駆動端子4G1とソース駆動端子4S1は、ゲート駆動回路5aに接続され、またスイッチング素子42のゲート駆動端子4G2とソース駆動端子4S2は、ゲート駆動回路5bに接続される。なお図1では、パワー半導体モジュール4を構成する主端子や絶縁基板に生じる寄生インダクタンス45a~45eを表記しているが、実回路上にインダクタンス素子が直接配線接続されたことを表したものでないことは言うまでもない。

10

20

30

50

20

30

40

50

#### [0037]

ゲート駆動制御回路 5 は、パワー半導体モジュール 4 のスイッチング素子 4 1 , 4 2 を駆動するために用いられ、そのゲート駆動信号はゲート駆動制御回路 5 の内部にて生成される。

## [0038]

誘導性負荷6は、パワー半導体モジュール4の出力負荷として接続され、例えばモータや電力系統網などに接続するためのフィルタリアクトルである。本実施例では発明の効果の説明に関わらないために、負荷の種別についての言及は割愛する。

## [0039]

スナバ回路7(7a,7b)は、例として放電阻止型RCDスナバ回路を用いて示している。スナバ回路7aはパワー半導体モジュール4の正電源端子47と中間端子49の間に接続され、スナバ回路7bはパワー半導体モジュール4の中間端子49と負電源端子48の間にそれぞれ接続されている。スナバ回路7(7a,7b)は、スナバコンデンサ71、ダイオード72、抵抗73によって構成されている。なお図示では、スナバ回路7(7a,7b)内の寄生インダクタンスを74として表記しているが、これも実回路上にインダクタンス素子が直接配線接続されたことを表したものでない。

#### [0040]

係る構成のスナバ回路7(7a,7b)では、スイッチング素子41,42がターンオフしたときのスイッチングサージ発生時に、寄生インダクタンス74に蓄積するエネルギーをコンデンサ71にて引き込むために比較的大きなコンデンサ71の容量が必要となる。特に急峻なスイッチングの場合には、その直列寄生インダクタンス74が影響してスナバ回路7の素子の寄生インダクタンス74によるスイッチングサージが発生する。

## [0041]

実施例1の電力変換装置100は、補償インピーダンス回路8に工夫を施したものである。この補償インピーダンス回路8は、パワー半導体モジュール4の正負の電源端子47,48間に接続され、直列接続された2つのコンデンサ81および82とコンデンサ82に並列接続されるインダクタ83から成る。なおインダクタ83は寄生インダクタンスではなく、実回路上にインダクタンス素子が直接配線接続されたものである。

## [0042]

この補償インピーダンス回路8を構成するコンデンサ81、82と、インダクタ83の各素子の容量は、スイッチングサージによるサージ電圧振動を抑制する観点から定められている。そのために、その合成インピーダンスの周波数依存性は、少なくとも1つ以上の零点周波数(fcz)と極周波数(fcp)を有し、サージ振動周波数を決めるインピーダンスのピーク周波数(fsp)に対して、零点周波数fcz<ピーク周波数fsp<極周波数fcpとなるように構成素子の値が決定されたものである。

## [0043]

次に、図1から図5を参照して、実施例1の電力変換装置の動作を説明する。まず図1のパワー半導体モジュール4において、スイッチング素子41及び42がスイッチングすると、それに伴ってサージ電圧が発生する。例えば、パワー半導体モジュール4のスイッチング素子42が導通から遮断へとターンオフする場合に、スイッチング素子42のドレイン・ソース間に、電源1が供給する直流電圧Eに加えサージピーク電圧 V(=L・di/dt)が発生する。ここでLは、スイッチング素子42のドレイン・ソースから電力変換器を見た場合のインダクタンスの総和値である。di/dtは、スイッチング素子42の導通から遮断への過渡電流の時間変化率である。

## [0044]

サージピークの発生後、スイッチング素子42のドレイン・ソース間にはサージ電圧振動が発生する。その振動周期は、電力変換装置100内の寄生インダクタンスLspと寄生コンデンサ容量Cspによって決定される。ここで、寄生インダクタンスLspと寄生コンデンサ容量Cspは、単一の寄生インダクタンス、単一の寄生コンデンサ容量ではない。

20

30

40

50

#### [0045]

例えば寄生インダクタンスLspについて示せば、スナバ回路7内の寄生インダクタンスやパワー半導体モジュール4内部の寄生インダクタンス等の総和である。寄生コンデンサ容量Cspについて示せば、パワー半導体モジュール4を構成するスイッチング素子41,42や還流ダイオード43,44の寄生容量の総和である。但し、寄生インダクタンスLspと寄生コンデンサ容量Cspを構成する寄生素子は、スイッチングの際に電流変動が生じる経路に在る寄生素子である。

### [0046]

例としてターンオフ時のスイッチング素子のドレイン・ソース間の電圧と電流の従来における過渡応答について図4に示している。図4は補償インピーダンス8を用いない従来方式の過渡応答波形である。この波形は、図1の電力変換装置100の回路例において、補償インピーダンス8を削除した場合の計算機解析によって算出されている。

#### [0047]

図 4 において、横軸はスイッチング素子のターンオフ前後の時間を示している。またこの図の縦軸には、スイッチング素子のドレイン・ソース間の電圧 V D S とドレイン電流 I Dを表示している。

### [0048]

図の上側の波形がドレイン・ソース間の電圧 V D S であり、ターンオフ前に 0 (V)であったものが、ターンオフにより急速に増加して最大 6 9 7 (V)に達し、その後減衰振動をしながら 6 0 0 (V)で安定する。但し、過渡的に振動周期周波数 4 1 (M H Z)で振動し、振動電圧が 6 0 0  $\pm$  1 0 (V)に至るまでに 4 1 5 (n s)を要した。このようにターンオフとともに、ドレイン・ソース間の電圧 V D S は、 6 0 0 (V)の直流電圧へと変化する過程で、約 1 0 0 (V)のサージピーク電圧 V が発生し、その後に周期約 4 1 (M H Z)の振動が生じている。

#### [0049]

スイッチング素子の電流波形も同様に振動が生じる。図の下側の波形がドレイン電流 I D であり、ターンオフ前に 4 0 ( A ) であったものが、ターンオフにより急速に減少し、その後減衰振動をしながら 0 ( A ) で安定する。但し、振動周期周波数 4 1 ( M H Z ) で振動が生じている。

## [0050]

図4の電圧振動の周期は、上述のように寄生インダクタンスLspと寄生コンデンサ容量Сspの共振周波数と等しい。図1において、補償インピーダンス回路8を用いない場合に、スイッチング素子42のドレイン・ソースから電力変換器を見た場合のインピーダンスの特性例を図3に示す。図3は、横軸に周波数、縦軸にインピーダンスを示したものであり、図3の上の特性は、周波数が10 $^5$ から10 $^9$ までの広範囲な、全体特性を示しており、図3の下の特性はその一部領域(10 $^7$ から10 $^8$ )を拡大して示している。この図では、実線で示す特性L1が、補償インピーダンスが無い場合のインピーダンスの周波数依存性である。

## [0051]

図3において L1は、周波数が10 $^7$ 以下の領域では周波数増加に伴いインピーダンスが減少し、10 $^8$ 近傍まで増加して100()程度に達し、その後10()程度に低下する特性である。このように補償インピーダンス回路8を用いない場合、スイッチング素子42のドレイン・ソースから電力変換器を見たときのインピーダンスの周波数依存特性は、インピーダンスが最大になる点と最小になる点を含んでいる。

#### [0052]

さらに拡大図で最大となる点(並列共振点)を検証すると、この図3の例では、並列共振が周波数 f s p = 5 3 . 7 (MHz)で発生し、そのピークインピーダンスの絶対値は143.2()である。このピークインピーダンスのため、スイッチングが発生した場合に、広帯域の過渡電流が発生し、そのうちインピーダンスの絶対値の大きな周波数、ここでは上記の並列共振周波数(5 3 . 7 (MHz))のインピーダンスが顕著となって、

サージピーク電圧発生後の電圧振動特性に支配的になる。

#### [0053]

従って、サージ電圧振動を抑制するには、共振によって生じるピークインピーダンス(fsp)の絶対値を低減すればよい。そこで、補償インピーダンス8を用いて、上記のピークインピーダンスの低減を可能にする。

#### [0054]

補償インピーダンス8は、上記の回路構成を採っている。つまり、図1に示したように第1のコンデンサ82とリアクタンス83を並列接続した回路に、さらに第2のコンデンサ81を直列配置した回路構成のものである。補償インピーダンス8の端子間のインピーダンスの周波数の依存性は、図3の点線で示す特性L2である。図3の上の特性に示すように、特性L2は、周波数の上昇とともにインピーダンス低下し、その後周波数の上昇とともにインピーダンス低下する特性を示す。この特性はインピーダンスが最大になる点と最小になる点を含んでいる。

### [0055]

さらに拡大図で最大、最小となる点を検証すると、この図3の例では、インピーダンスが最大になる点の周波数がfcpであり、最小になる点の周波数がfczである。図1の実施例1の補償インピーダンス8の構成において、補償インピーダンス8の各構成素子の定数を例えば、それぞれ第2のコンデンサ81=850(pF)、第1のコンデンサ82=210(pF)、並列リアクタンス83=15(nH)に選定したとする。

### [0056]

このとき、インピーダンスが最小になる点(零点周波数(fcz))と、インピーダンスが最大になる点(極周波数(fcp))を有し、それぞれ、零点周波数fczは39.8(MHz)、かつ1.5()の零点周波数インピーダンスであり、極周波数fcpは89.1(MHz)、71.5()の極周波数インピーダンスを取る。

#### [0057]

本発明では、補償インピーダンス8の各構成素子の定数を決定するにあたり、その結果得られる零点周波数fczと極周波数fcpが、前述の並列共振周波数fspとの関係で

零点周波数fcz<並列共振周波数fsp<極周波数fcpの周波数の関係を有するように選定する。

#### [0058]

このようにして決定された補償インピーダンス8を、パワー半導体モジュール4の正と 負の電源端子47,48間に接続する。本来は着目するスイッチング素子のドレイン・ソ ース間に接続することが最も効果的であるが、スイッチング素子41および42のいずれ にも補償インピーダンスの効果が得られるようにするため、パワー半導体モジュールの正 と負の電源端子47,48間に接続する。

## [0059]

このようにして決定した補償インピーダンス回路 8 を用いた場合には、スイッチング素子 4 2 のドレイン・ソースから電力変換器を見た場合のインピーダンスの周波数依存性は、図 3 の実線に丸シンボルの特性 L 3 となる。補償後の特性 L 3 は、全体的には高周波数域(1 0 プ以上の領域)において特性 L 1 を右側(高周波数側)にシフトし、かつ最大値を 2 つ生じており、さらに特性 L 1 の最大値を低減したものとなっている。

## [0060]

本発明の場合に、特性 L 1 の最大値を低減し、最大値を 2 つ生じたことに技術的な価値がある。図 3 下の図には、補償前後の特性の変化の様子が仔細に現れている。図 3 下の拡大図において、補償インピーダンスを用いない場合の特性 L 1 と、補償インピーダンス自身の特性 L 2 とでは、その並列合成インピーダンスはほぼ等しい。

#### [0061]

本発明の補償により、その周波数依存性は、2つの最大値を有するものとなっている。 このうち低周波数側に現れた最大値は、補償前の並列共振周波数 fspより低周波数の f 10

20

30

40

20

30

sp1で生じており、この時の周波数は25.7(MHZ)、インピーダンスは20.9 ()の点での共振となっている。また高周波数側に現れた最大値は、補償前の並列共振周波数fspより高周波数のfsp2で生じており、この時の周波数は69.1(MHZ)、75.5()の点での共振が得られている。これら2つのピーク点のインピーダンスは、補償前のピーク点でのインピーダンスよりも小さいものとされている。

#### [0062]

このように本発明では、従来の単一ピークインピーダンス特性 L 1 を、 2 つのピークインピーダンス周波数に分散し、そのピークインピーダンス値もまた低減できる。また、ピーク周波数だけでなく、補償インピーダンス回路 8 を接続する効果として、周波数約 1 5 (MHz)以降の高周波でのインピーダンスは、補償インピーダンスを用いない場合の特性にくらべて低減できる。特にfsp2以降の高周波では、fcpを設けた効果により、補償インピーダンス回路のインピーダンスの絶対値が周波数とともに低減する。そのため、fsp2以降の高周波においても補償インピーダンスを用いることで、スイッチング素子42のドレイン・ソースから電力変換器を見た場合のインピーダンスを低減することができ、スイッチングによる高調波電力の発生を抑えることができる。

#### [0063]

上記の効果を数式で簡潔に示すと以下の通りである。まず、スイッチング素子42のドレイン・ソースから電力変換器を見た場合のインピーダンスの共振インピーダンスの周波数fspを(1)式で示す。fspは電力変換装置100内の寄生インダクタンスLspと寄生コンデンサ容量Cspの並列共振回路の共振周波数である。図3の特性L1の最大値を示す周波数である。

[0064]

【数1】

$$f_{sp} = \frac{\omega_{sp}}{2\pi} = \frac{1}{2\pi\sqrt{L_{sp} \cdot C_{sp}}} \tag{1}$$

[0065]

次に、補償インピーダンスの端子間のインピーダンスの零点周波数 f c z と極周波数 f c pを (2)式で示す。これらは図3の特性 L 2の最小値と最大値を示す周波数である。なお(1)式は寄生成分 L s p、 C s pで表現されているが、(2)式は実際に補償インピーダンス回路8として装備する回路素子の値で表現されている。この式で C 8 1 は第1のコンデンサ81の容量、C82は第2のコンデンサ82の容量、L83はリアクタンス83の容量である。従って、これらは任意に選択可能な値である。

[0066]

【数2】

$$f_{cz} = \frac{\omega_{cz}}{2\pi} = \frac{1}{2\pi\sqrt{L_{83}\cdot(C_{81} + C_{82})}}$$

$$f_{cp} = \frac{\omega_{cp}}{2\pi} = \frac{1}{2\pi\sqrt{L_{83}\cdot C_{82}}}$$

(2)

[0067]

補償インピーダンスを接続した後の、スイッチング素子42のドレイン・ソースから電力変換器を見た場合のインピーダンスの、2つのピーク周波数 f s p 1 と f s p 2 を (3) 式で示す。

[0068]

【数3】

$$f_{sp1} = \frac{\omega_{sp1}}{2\pi} = \frac{1}{2\pi\sqrt{L_{sp1} \cdot C_{sp1}}}$$

$$f_{sp2} = \frac{\omega_{sp2}}{2\pi} = \frac{1}{2\pi\sqrt{L_{rr2} \cdot C_{rr2}}}$$

(3)

[0069]

10

この(3)式でLsp1、Csp1およびLsp2、Csp2は補償インピーダンス回路8の素子値を含み、また、スイッチング時の過渡電流の流れる経路のインダクタンスと容量によって決まる値である。これらは図3の特性L3の2つの最大値を示す周波数である。

[0070]

さらに、補償インピーダンスを接続しない場合の、スイッチング素子42のドレイン・ソースから電力変換器を見た場合のインピーダンスZDS1を(4)式に示す。なおZ0(f)は、本発明の効果の説明に関わらないインピーダンスを示す。周波数依存性は有するものの、本発明の効果には関わらない。

[0071]

20

【数4】

$$Z_{DSI} = Z_0(f) \frac{s \cdot L_{sp}}{1 + s^2 \cdot L_{sp} C_{sp}}$$

(4)

[0072]

(5)式は、図1に示す補償インピーダンス自体のインピーダンス特性 ZDS2を示す

[0073]

【数5】

30

40

50

$$Z_{DS2} = \frac{1}{sC_{81}} \cdot \frac{1 + s^2 \cdot L_{83}(C_{81} + C_{82})}{1 + s^2 \cdot L_{83}C_{82}}$$

(5)

[0074]

(6)式は、補償インピーダンス回路を付加した場合の、スイッチング素子42のドレイン・ソースから電力変換器を見た場合のインピーダンスZDS3を示す。ZDS1とZDS2の並列接続によって算出でき、分母のLsp1、Csp1およびLsp2、Csp2は、ZDS3に発生する2つの極周波数の角周波数を示しており、その詳細な代数表現は多項となるためここでは割愛する。

[0075]

【数6】

$$Z_{DS3} = Z_0(f) \cdot \frac{s \cdot L_{sp} \left\{ 1 + s^2 L_{83} (C_{81} + C_{82}) \right\}}{(1 + s^2 \cdot L_{spl} C_{spl})(1 + s^2 \cdot L_{sp2} C_{sp2})}$$

(6)

[0076]

( 4 ) 式と( 6 ) 式より、 L s p と C s p から決まっていた共振極周波数 ( ( 4 ) 式 )

が、Lsp1とCsp1、およびLsp2とCsp2の2つの共振極周波数((6)式)へと分散することが明らかに理解できる。また、その共振周波数でのインピーダンスの大きさについては、図3の例に示すように、補償インピーダンス回路の付加により低減することも明らかとなっている。

## [0077]

上記のように、補償インピーダンス回路 8 を、パワー半導体モジュール 4 の正と負の電源端子 4 7 , 4 8 間に接続に接続することで、サージ電圧振動の主要因であるインピーダンスの共振周波数を複数の周波数へ分散させ、同時にそのインピーダンス値を低下できることが明らかである。

## [0078]

次に、実施例 1 での効果を説明する。図 5 は補償インピーダンスを用いた場合の過渡応答波形である。この波形を図 4 の補償前の過渡応答波形と比較すると本発明の効果が明らかとなる。この過渡応答波形は、図 1 の電力変換装置の回路例において、補償インピーダンスを適用した場合の計算機解析によって算出されている。

#### [0079]

図5では、ターンオフとともに、ドレイン・ソース間の電圧VDSは、600(V)の直流電圧へと変化する過程で、約100(V)のサージピーク電圧 Vが発生する。ここまでの応答は図4と比較して大差がない。相違点は、その後のサージ共振振動が、2つの異なった周波数の混合の信号電圧になっているため、振動波形が相違している点、またその振幅の減衰が図4の補償インピーダンスを用いない場合に比較して早い点である。特に後者のメリットが大きく、例えば、600(V)を中心とした±10(V)の範囲に収束する時間は、スイッチング開始後325(ns)で、図4の415(ns)に比較して78(%)に低減できている。

#### [0800]

また、この波形の周波数解析を行った結果を図6に示す。図6は、図4および図5のドレイン・ソース間の電圧VDSの電圧波形をFFT解析したものをデシベル表示したものである。補償インピーダンス回路8を用いない場合(図4)の波形のFFT解析結果を実線で、補償インピーダンス回路8を適用した場合(図5)の波形のFFT解析結果を破線でしめす。補償インピーダンス回路8を用いない場合には42(MHz)に大きな高調波が発生しているが、補償インピーダンス回路8を適用した場合には24(MHz)と50(MHz)に高調波が分散し、そのピーク値も低減し、低減量はそれぞれ3.4(dB)と10.1(dB)である。

#### [0081]

このように、実施例 1 の構成では、補償インピーダンス回路 8 を用いない場合に比較して、過渡波形の高調波成分の低減を可能にし、インバータによる不要電磁放射のレベルを低減する効果を得られることが明らかである。

#### 【実施例2】

### [0082]

図 2 は、実施例 1 に適用できる補償インピーダンス回路 8 の実装構成を示したものである。図 1 に示すように、パワー半導体モジュール 4 の近傍には、正電源配線 3 a、負電源配線 3 b、スナバ回路 7 a、 7 b が密集して配置される構成となる。この配置で、電力変換装置の形状や体積を維持したまま実装できる補償インピーダンス回路 8 の実施例の 1 つが図 2 の構成である。

## [0083]

図2では、その上段に平面図、中段に断面図を示しており、かつ下段にこの構成で実現する回路構成を図示している。

#### [0084]

図2中段の断面図に特徴がよくあらわれているように、補償インピーダンス回路8は、 絶縁基板85を挟む導体86a、86b、86cで構成される。絶縁基板85の下面全体 には導体86cが配置され、絶縁基板85の上面には領域を分けて導体86aと86bが 10

20

30

40

配置されている。これら導体は互いに絶縁されている。導体 8 6 a は導体 8 6 c との間に、絶縁基板 8 5 を誘電体として見込む並行平板容量を構成し、導体 8 6 b も導体 8 6 c との間に、絶縁基板 8 5 を誘電体として見込む並行平板容量を構成している。これらの並行平板容量は、それぞれ図 1 に示す実施例 1 の回路で示した容量 8 1 と 8 2 に成りえる。

## [0085]

図2上段の平面図は、絶縁基板85の上面に領域を分けて配置された導体86aと86bの領域を示している。導体86aの領域で容量81を形成し、導体86bの領域で容量82を形成している。また、導体86bの一部は図2上段に示すようにインダクタンスを発生しやすいミアンダ状のパターンを構成し、さらにその一端をビアホール群84によって導体86bと接続することで、容量82と並列接続するリアクタンス83として構成することができる。

[0086]

さらに導体86aと導体86bをパワー半導体モジュール4の正と負の電源端子47,48に接続するために、接続端子80aと80bをそれぞれ導体86aと導体86bへ接続する。接続端子80aと80bの開孔部は、パワー半導体モジュール4へのネジ止めの際に利用する。

[0087]

尚、図2に実施例として示す補償インピーダンス回路8は、その容量81、82、リアクタンス83の定数を決定したのちに作成するが、電力変換装置の構成部材の変更等により、その回路定数を変更する必要が生じることがある。このような場合に、図2の実施例では、導体86aと導体86bに関して、導体切断線(81a 81a')、(81b 81b')、(82a 82a')、(82b 82b')のように切断することで、並行平板容量の平板面積を減少させ、容量81および82の値を変更し、補償インピーダンス回路8の両端子間に発生するインピーダンスの周波数依存性を変更することが可能である。

### 【実施例3】

#### [0088]

図7は、実施例2に係る電力変換装置100の構成例を示す図である。この図において、電力変換装置100は、直流電源1、平滑コンデンサ2、正電源配線3a、負電源配線3b、パワー半導体モジュール4'、ゲート駆動制御回路5、誘導性負荷6、スナバ回路7、補償インピーダンス回路8で構成される。

[0089]

[0090]

図1の電力変換装置100との相違点は、補償インピーダンス回路8をパワー半導体モジュール4<sup>'</sup>に内包する構成としたことである。その他の構成は既に説明した図1に示された同一の符号を付された構成と、同一の機能を有するので、それらの説明は省略する。

パワー半導体モジュール 4 ' は、補償インピーダンス回路 8 をモジュール内に含み、補償インピーダンス回路 8 の一端をスイッチング素子 4 1 のドレイン近傍に、他端をスイッチング素子 4 2 のソース近傍に接続する構成をとる。寄生インダクタンス 4 5 a と寄生インダクタンス 4 5 e は、パワー半導体モジュールを構成する主端子といわれる金属配線部(図示せず)を模している。

[0091]

パワー半導体モジュールの正電源端子側を正電源主端子とし、それを寄生インダクタンス45a、同じく負電源端子側を負電源主端子とし、それを寄生インダクタンス45eとする。パワー半導体モジュール4'では、補償インピーダンス回路8は寄生インダクタンス45aと45eよりスイッチング素子41,42に近く結線できるため、スイッチング素子のドレイン・ソース間電圧に印加されるサージ電圧振動をより効果的に抑制できる。

[0092]

これは、図1の構成では、寄生インダクタンス45aと45eによって生じる Vがスイッチング素子41,42のドレイン・ソース間電圧に無条件で印加されるのに対し、図

10

20

30

40

20

30

40

50

6の構成では寄生インダクタンス 4 5 a と 4 5 e も含めたインピーダンスに対して、補償インピーダンス回路が機能するからである。従って、図 6 の構成では、サージ電圧振動の振幅は、図 1 の構成に比較してより小さく抑制できる。

## 【実施例4】

## [0093]

図8は、パワー半導体モジュール4の一部と補償インピーダンス回路8の構成を示した第3の実施例である。ここでは、パワー半導体モジュール4の一部と補償インピーダンス回路8を同一基板上に形成している。

## [0094]

第3の実施例では、絶縁基板85を挟む導体として、図1の補償インピーダンス回路8を構成していた導体86a、86b、86cの他に、新たに導体4P、4N、4D2、4S2、4RTNと、半導体チップ(41から44)を追加配置し、半導体チップと導体の間をボンディングワイヤ4wで接続するように構成されている。

### [0095]

まず補償インピーダンス回路8の部分についてみると、この構成は図2で説明したものと基本的に同じである。ここでは導体86aは導体86cとの間に、絶縁基板85を誘電体として見込む並行平板容量を構成し、導体86bも導体86cとの間に、絶縁基板85を誘電体として見込む並行平板容量を構成する。これらはそれぞれ、図7に示す第2の実施例の回路で示した容量C81とC82に成りえる。また、導体86bの一部は図2に示すようにインダクタンスを発生しやすいミアンダ状のパターンを構成し、さらにその一端をビアホール群84aによって導体86bと接続することで、C82と並列接続するL83として動作する。

### [0096]

上記のようにして補償インピーダンス回路8を形成したうえで、さらに導体86aは導体4Pと接続されており、導体86bは、導体4Nと接続されている。導体4Pと導体4Nはそれぞれ図示しない主端子と接続してパワー半導体モジュール4<sup>n</sup>の正電源端子47と負電源端子48に接続される。

#### [0097]

また導体パターン4Pは、スイッチング素子41のドレインと還流ダイオード43のカソードを接続する。導体パターン4G1はボンディングワイヤ4Wを介してスイッチング素子41のゲート端子と接続する。導体パターン4D2は、スイッチング素子41のソースと還流ダイオード43のアノードを、ボンディングワイヤを介して接続されるとともに、スイッチング素子42のドレインと還流ダイオード44のカソードを接続される。さらに、パワー半導体モジュール4の中間端子49の主端子を接続する導体でもある。

## [0098]

また導体パターン 4 G 2 はボンディングワイヤ 4 w を介してスイッチング素子 4 2 のゲート端子と接続する。導体パターン 4 D 2 は、スイッチング素子 4 2 のソースと還流ダイオード 4 4 のアノードを、ボンディングワイヤを介して接続される。さらにビアホール 8 4 b を介して、裏面側導体の導体 4 R T N、さらにビアホール 8 4 c を介して導体 4 Nと接続される。

## [0099]

上記のように、図8に示す実施例では、パワー半導体モジュール4の一部と補償インピーダンス回路8を同一基板上に実現することができる。図1および図2に示す実施例に対する利点は、図7の実施例で説明したようにサージ電圧振動の振幅を図1および図2の構成に比較してより小さく抑制できる他に、若干の面積増は必要となるものの、元来の絶縁基板と導体を利用して補償インピーダンス回路を低コストに実現できることである。

#### [0100]

なお、本発明は上記した実施例に限定されるものではなく、様々な変形例が含まれる。 例えば、上記した実施例は本発明を分かりやすく説明するために詳細に説明したものであ り、必ずしも説明した全ての構成を備えるものに限定されるものではない。また、ある実 施例の構成の一部を他の実施例の構成に置き換えることが可能であり、また、ある実施例の構成に他の実施例の構成を加えることも可能である。また、各実施例の構成の一部について、他の構成の追加・削除・置換をすることが可能である。

## [0101]

例えば、スイッチング素子をMOS-FET(MOS型電界効果トランジスタ)、J-FET(接合型電界効果トランジスタ)のユニポーラデバイス、そしてIGBT(絶縁ゲートバイポーラトランジスタ)のようなバイポーラデバイスのいずれのデバイスに置き換え、さらに端子の機能のうち、例えば、ドレインをコレクタ、ソースをエミッタ、ゲートをベースに置き換えた場合であっても、本発明の効果は変わるものではない、また、還流ダイオードに関しても、同様に、PN接合ダイオードやSB(ショットキー接合)ダイオードのいずれを用いても本発明の効果は変わるものではないことは明らかである。

10

#### 【符号の説明】

## [0102]

1:直流電源

2:平滑コンデンサ

3 a:正電源配線

3 b:負電源配線

4:パワー半導体モジュール

5:ゲート駆動制御回路

6:誘導性負荷

7: スナバ回路

8:補償インピーダンス回路

11:配線

41,42:スイッチング素子

43,44: 還流ダイオード

47:正電源端子

48:負電源端子

49:中間端子

8 1 : 第 2 のコンデンサ

82:第1のコンデンサ

83:リアクタンス

84a、84b、84c:ビアホール

8 5 : 絶縁基板

86a、86b、86c:導体

100:電力変換回路

20

## フロントページの続き

## (72)発明者 石川 勝美

茨城県日立市大みか町七丁目1番1号 株式会社日立製作所 日立研究所内

## 審査官 宮本 秀一

## (56)参考文献 特開2010-041790(JP,A)

特開2012-231593(JP,A)

特開2011-172329(JP,A)

特開2013-005542(JP,A)

特開2001-274322(JP,A)

米国特許出願公開第2013/0027154(US,A1)

## (58)調査した分野(Int.CI., DB名)

B60L1/00-3/12、

7/00-13/00、

15/00-15/42

H02M1/00-3/44、

7/00-7/98