## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2013-190804 (P2013-190804A)

(43) 公開日 平成25年9月26日(2013.9.26)

(51) Int. Cl. F 1 テーマコード (参考)

**GO9F** 9/30 (2006.01) GO9F 9/30 338 2H192 **GO2F** 1/1368 (2006.01) GO2F 1/1368 5CO94

## 審査請求 有 請求項の数 1 OL (全 16 頁)

(21) 出願番号 特願2013-96716 (P2013-96716) (22) 出願日 平成25年5月2日 (2013.5.2) (62) 分割の表示 特願2011-241765 (P2011-241765)

の分割

原出願日 平成13年4月27日 (2001.4.27) (31) 優先権主張番号 特願2000-128536 (P2000-128536)

平成12年4月27日 (2000.4.27)

(33) 優先権主張国 日本国(JP)

(71) 出願人 000153878

株式会社半導体エネルギー研究所 神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 荒井 康行

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

F ターム (参考) 2H192 AA24 BA13 BC72 BC82 CB05

CB13 CB53 CC02 CC07 CC33 CC44 DA02 DA42 EA04 FB02 5C094 AA10 AA43 BA03 BA43 DA13

EA04 FA01 GB10

## (54) 【発明の名称】表示装置

## (57)【要約】

(32) 優先日

【課題】画素部に形成される画素電極やゲート配線及び ソース配線の配置を適したものと

して、かつ、マスク数及び工程数を増加させることなく 高い開口率を実現した画素構造を

有するアクティブマトリクス型表示装置を提供すること を目的とする。

【解決手段】絶縁表面上のゲート電極及びソース配線と 、前記ゲート電極及びソース配線

上の第1の絶縁層と、前記第1の絶縁膜上の半導体層と、前記半導体膜上の第2の絶縁層

と、前記第2の絶縁層上の前記ゲート電極と接続するゲート配線と、前記ソース電極と前

記半導体層とを接続する接続電極と、前記半導体層と接 続する画素電極とを有することを

特徴としている。

【選択図】図13

#### 【特許請求の範囲】

## 【請求項1】

表示装置。

【発明の詳細な説明】

#### 【技術分野】

### [0001]

本発明は薄膜トランジスタ(以下、TFTという)で構成された集積回路を有する半導 体 装 置 お よ び そ の 作 製 方 法 に 関 す る 。 例 え ば 、 液 晶 表 示 パ ネ ル に 代 表 さ れ る 電 気 光 学 装 置 およびその様な電気光学装置を部品として搭載した電子装置に関する。尚、本明細書中に おいて半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光 学装置、半導体回路および電子装置は全て半導体装置の範疇に含まれるものとする。

# 【背景技術】

## [0002]

半導体薄膜(厚さ数~数百nm程度)を用いて薄膜トランジスタ(TFT)を作製する技 術が開発されている。TFTは液晶表示装置のスイッチング素子として実用化が進み、最 近ではCMOS回路を形成し、ガラスなどの基板上に集積回路を形成することも可能とな っている。

#### [00003]

液晶表示装置では、画質の高精細化に対応するため、画素電極をマトリクス状に配置し 、 画 素 電 極 の 各 々 に 接 続 す る ス イ ッ チ ン グ 素 子 と し て T F T を 用 い た ア ク テ ィ ブ マ ト リ ク ス型液晶表示装置が主流となりつつある。このアクティブマトリクス型液晶表示装置には 、大別して透過型と反射型の二種類が知られている。

特 に 、 反 射 型 の 液 晶 表 示 装 置 は 、 透 過 型 の 液 晶 表 示 装 置 と 比 較 し て 、 バ ッ ク ラ イ ト を 使 用 しないため、消費電力が少ないといった長所を有し、携帯型情報端末やビデオカメラ用の 直視型表示装置としての需要が高まっている。

# [0004]

反射型のアクティブマトリクス型液晶表示装置は、液晶の光学変調作用を利用して、入 射 光 が 画 素 電 極 で 反 射 し て 装 置 外 部 に 出 力 さ れ る 状 態 と 、 入 射 光 が 装 置 外 部 に 出 力 さ れ な い状態とを選択し、明と暗の表示を行わせ、さらにそれらを組み合わせることで画像表示 を行うものである。一般に反射型の液晶表示装置における画素電極は、アルミニウムや銀 などの光反射率の高い導電性材料を用いている。

# [00005]

いずれにしても、画質の高精細化が進むにつれ、必然的に画素一つ当たりのサイズは微 細化する。その結果、画素部においてTFT、ソース配線、ゲート配線などが占める面積 の割合が大きくなり、開口率が低下してしまう。従って、規定の画素サイズの中で各画素 の高開口率を得るためには、画素の回路構成に必要な回路要素を効率よくレイアウトする ことが不可欠となってくる。

#### 【発明の概要】

【発明が解決しようとする課題】

## [0006]

規定の画素サイズの中で高開口率を実現するためには、画素部の回路構成に必要な要素 を効率よく配置することが不可欠となる。

## [0007]

本発明は、このような課題を鑑みて導き出されたものであり、画素部に形成される画素 電 極 や ゲ ー ト 配 線 及 び ソ ー ス 配 線 の 配 置 を 適 し た も の と し て 、 か つ 、 マ ス ク 数 及 び 工 程 数 を増加させることなく高い開口率を実現した画素構造を有するアクティブマトリクス型表 示装置を提供することを目的とする。

## 【課題を解決するための手段】

# [00008]

本 発 明 は 、 ブ ラ ッ ク マ ト リ ク ス を 形 成 す る た め の 遮 光 膜 を 用 い る こ と な く T F T を 遮 光

10

20

30

40

10

20

30

40

50

し、さらに画素と画素との間から漏洩する光を遮断する構造を特徴としている。そのような構造を有する本発明の構成は、絶縁表面上のゲート電極及びソース配線と、前記ゲート電極及びソース配線上の第 1 の絶縁膜と、前記第 1 の絶縁膜上の半導体膜と、前記半導体膜上の第 2 の絶縁膜と、前記第 2 の絶縁膜上の前記ゲート電極と接続するゲート配線と、前記ソース配線と前記半導体膜とを接続する接続電極と、前記半導体膜と接続する画素電極とを有することを特徴としている。

#### [0009]

また、他の発明の構成は、絶縁表面上の第1のゲート電極と第2のゲート電極とソース配線と、前記第1及び第2のゲート電極とソース配線上の第1の絶縁膜と、前記第1の絶縁膜上に、ソース領域及びドレイン領域とチャネル形成領域とを有る第1の半導体膜と、前記第2のゲート電極と重なる第2の半導体膜と、前記第1及び第2の半導体膜上の第2の絶縁膜と、前記第2の絶縁膜上に前記ゲート電極と接続するゲート配線と、前記ソース配線と前記ソース領域と接続する接続電極と、前記ドレイン領域と前記第2の半導体膜とに接続する画素電極とを有することを特徴としている。

#### [0010]

このような発明の構成において、前記画素電極の一方の端部は、前記ソース配線上に形成することにより、遮光膜を兼ねることができ、画素部において画素電極が占める面積の割合を大きくすることができる。

# [0011]

また、他の発明の構成は、絶縁表面上にゲート電極とソース配線を形成する第1の工程と、前記ゲート電極上に第1の絶縁膜を形成する第2の工程と、前記第1の絶縁膜上に半導体膜を形成する第3の工程と、前記半導体膜上に第2の絶縁膜を形成する第4の工程と、前記第2の絶縁膜上に、前記ゲート電極と接続するゲート配線と、前記ソース配線と前記半導体膜とを接続する接続電極と、前記半導体膜と接続する画素電極とを形成する第5の工程とを有することを特徴としている。

## [0012]

また、他の発明の構成は、絶縁表面上にゲート電極とソース配線を形成する第1の工程と、前記ゲート電極上に第1の絶縁膜を形成する第2の工程と、前記第1の絶縁膜上に半導体膜を形成する第3の工程と、前記半導体膜にソース領域及びドレイン領域を形成する第4の工程と、前記半導体膜上に第2の絶縁膜を形成する第5の工程と、前記第2の絶縁膜上に、前記ゲート電極と接続するゲート配線と、前記ソース配線と前記ソース領域とを接続する接続電極と、前記ドレイン領域と接続する画素電極とを形成する第6の工程とを有することを特徴としている。

# [ 0 0 1 3 ]

また、他の発明の構成は、絶縁表面上に第1のゲート電極と第2のゲート電極とソース 配線を形成する第1の工程と、前記第1及び第2のゲート電極上に第1の絶縁膜を形成す る第2の工程と、前記第1の絶縁膜上に、前記第1のゲート電極と重なる第1の半導体膜 と、前記第2のゲート電極と重なる第2の半導体膜とを形成する第3の工程と、前記第1 の半導体膜にソース領域及びドレイン領域を形成する第4の工程と、前記半導体膜上に第 2の絶縁膜を形成する第5の工程と、前記第2の絶縁膜上に、前記ゲート電極と接続する ゲート配線と、前記ソース配線と前記ソース領域とを接続する接続電極と、前記ドレイン 領域と前記第2の半導体膜と接続する画素電極とを形成する第6の工程とを有することを 特徴としている。

# [0014]

上記工程に従えば、画素電極の一方の端部は、ソース配線上に形成することにより、ソース配線が遮光膜を兼ねる画素構造を形成することが可能となり、画素部において画素電極が占める面積の割合を大きくすることができる。

## 【発明の効果】

## [ 0 0 1 5 ]

本発明の画素構造とすることにより、画素部に占める画素電極の割合を大きくすること

が可能となり、反射型のアクティブマトリクス型液晶表示装置において開口率を向上させることができる。その結果、反射型の液晶表示装置のいずれにおいても明るく鮮明な画像表示を可能とする。

【図面の簡単な説明】

- [0016]

- 【図1】本発明の液晶表示装置における画素の構成を説明する上面図。

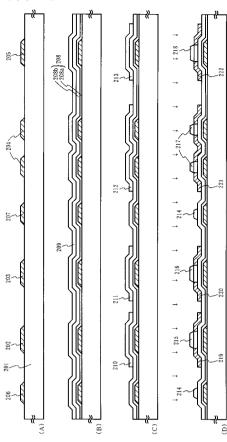

- 【図2】駆動回路のTFT、画素TFTの作製工程を説明する上面図。

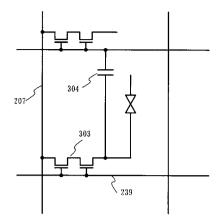

- 【図3】液晶表示装置における画素の構成を説明する回路図。

- 【図4】駆動回路のTFT、画素TFTの作製工程を説明する断面図。

- 【図5】駆動回路のTFT、画素TFTの作製工程を説明する断面図。

- 【図6】駆動回路のTFT、画素TFTの作製工程を説明する断面図。

- 【図7】反射型の液晶表示装置における画素の構成を説明する断面図。

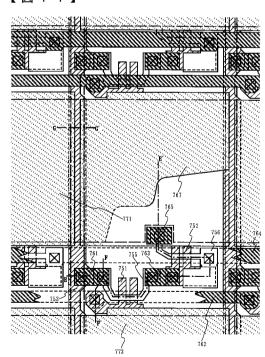

- 【図8】反射型の液晶表示装置における画素の構成を説明する上面図。

- 【図9】透過型液晶表示装置の画素部の構造を説明する断面図。

- 【図10】液晶表示装置の構成を説明する断面図。

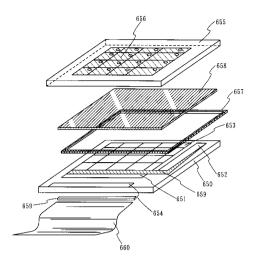

- 【図11】液晶表示装置の主要構成要素の組み立て図。

- 【図12】フロントライトを用いた反射型液晶表示装置の構成を説明する図。

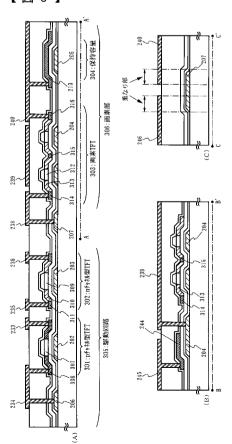

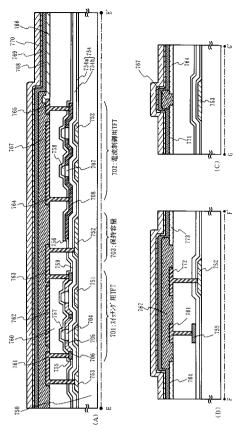

- 【図13】EL表示装置の画素部の構成を説明する断面図。

- 【図14】EL表示装置の画素部の構成を説明する上面図。

- 【図15】半導体装置の一例を説明する図。

- 【図16】半導体装置の一例を説明する図。

- 【発明を実施するための形態】

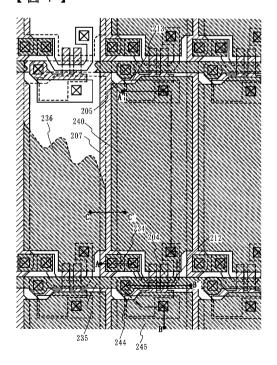

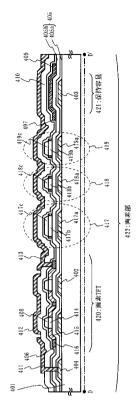

- [0017]

アクティブマトリクス型液晶表示装置に対する画素構造は、図1に示すように行方向に配置されたゲート配線235と、列方向に配置されたソース配線207と、ゲート配線とソース配線の交差部に対応して設けた画素TFTと、該画素TFTに接続する画素電極とから構成されている。

[0018]

画素毎に設けるTFT(以下、画素TFTと記す)のゲート電極204は絶縁表面上に 形成され、第1の絶縁膜を介して半導体膜212が形成されている。ソース配線207は、ゲート電極204と同じ絶縁表面上に形成されている。ゲート配線235と画素電極2 36は、半導体膜212上に形成された第2の絶縁膜の上に形成されている。そして、ゲート配線235及び画素電極236は、コンタクトホールを介してゲート電極204及び 半導体膜212とそれぞれ接続している。また、ソース配線207と半導体膜212は、ゲート配線235と同じ層に形成された接続配線234により接続されている。

[0019]

このような画素構造とすることにより、半導体膜212がゲート電極204と交差する部分(TFTにおいてチャネルが形成される部分)を、ゲート配線235で覆い遮光することができる。また、また、半導体膜212のそれ以外の領域も遮光される構造とすることが望ましい。また、図1ではゲート電極が櫛形となり複数のチャネル形成領域が存在するTFT構造を示しているが、チャネル形成領域と他のチャネル形成領域との間に存在する領域もゲート配線235によって遮光することが望ましい。

[0020]

図1における画素構造において、ゲート電極は画素に形成する保持容量を形成する一方の電極としての機能を有している。一つの画素は、半導体膜212と接続する画素電極236により形成されるが、画素電極236はまた半導体膜213と接続している。半導体膜213は容量を形成するための一方の電極として形成され、ゲート電極205と一対となって保持容量を形成する。この場合、半導体膜213にはp型の不純物(アクセプタ)が添加される。このような構成において保持容量は画素電極236と重なって形成されている。

10

20

30

40

#### [0021]

また、画素電極236の一方の端部は、ソース配線207と重ねて形成することができるので、隣接する画素電極242との間から漏洩する光を遮光することができる。

### [0022]

このような画素構造のパターンは光露光プロセスにより形成される。光露光プロセスで必要とされるフォトマスクの数は、ゲート電極形成用の第1のフォトマスク、半導体膜形成用の第2のフォトマスク、画素TFTのLDD領域形成用の第3のフォトマスク、コンタクトホール形成用の第4のフォトマスク、ゲート配線と画素電極と接続配線形成用の第5のフォトマスクであり、5枚のフォトマスクで画素部形成することができる。画素部の周辺にnチャネル型TFTとpチャネル型TFTから成るCMOS回路を応用した駆動回路を形成する場合には、nチャネル型TFTを覆うためのフォトマスクが追加される。以上のように、図1に示す画素構造とした場合、少ないマスク数で画素開口率の高い反射型液晶表示装置を実現することができる。

## [0023]

また、図1で示す画素構造は反射型の液晶表示装置を前提としたものであるが、フォトマスクを1枚追加して透明電極を所定のパターンに形成すれば、透過型の液晶表示装置を作製することもできる。以上の構成でなる本発明について、以下に示す実施例によりさらに詳細な説明を行う。

## 【実施例1】

## [ 0 0 2 4 ]

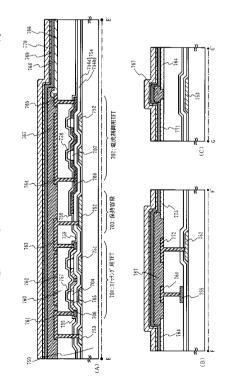

本実施例では同一基板上に画素部と、画素部の周辺に駆動回路を形成するTFT(nチャネル型TFT及びpチャネル型TFT)を同時に作製する方法について是面を参照しながら説明する。

#### [0025]

まず、図4(A)に示すように、コーニング社の#7059ガラスや#1737ガラスなどに代表されるバリウムホウケイ酸ガラス、またはアルミノホウケイ酸ガラスなどのガラスからなる基板201上に、好適には、モリブデン(Mo)

、タングステン(W)、タンタル(Ta)から選ばれた一種または複数種を成分とする導電膜からゲート電極 2 0 2 ~ 2 0 4、ソース配線 2 0 6、 2 0 7、 画素部の保持容量を形成するための容量配線 2 0 5を形成する。例えば、低抵抗化と耐熱性の観点からはMoとWの合金は適している。また、アルミニウムを用い、表面を酸化処理してゲート電極を形成しても良い。

#### [0026]

第1のフォトマスクにより作製されるゲート電極は、その厚さを200~400nm、好ましくは250nmの厚さで形成し、その上層に形成する被膜の被覆性(ステップカバレージ)を向上させるために、端部をテーパー形状となるように形成する。テーパー部の角度は5~30度、好ましくは15~25度で形成する。

テーパー部はドライエッチング法で形成され、エッチングガスと基板側に印加するバイア ス電圧により、その角度を制御する。

## [0027]

次いで、図4(B)で示すように、ゲート電極202~204、ソース配線206、207、画素部の保持容量を形成するための容量配線205を覆う第1の絶縁膜208を形成する。第1の絶縁膜208はプラズマCVD法またはスパッタ法を用い、その厚さを40~200nmとしてシリコンを含む絶縁膜で形成する。例えば、50nmの厚さの窒化シリコン膜208aと、120nmの厚さの酸化シリコン膜208bから第1の絶縁膜208を形成する。その他に、プラズマCVD法でSiH $_4$ 、N $_2$ О、NH $_3$ から作製される酸化窒化シリコン膜(SiOхNy)を適用してもよい。

#### [0028]

第 1 の絶縁膜 2 0 8 は、その上層に半導体膜を形成して、ゲート絶縁膜として用いるものであるが、基板 2 0 1 からアルカリ金属などの不純物が半導体膜に拡散するのを防ぐブ

10

20

30

40

ロッキング層としての機能も有している。

## [0029]

第 1 の絶縁膜 2 0 8 上に形成する半導体膜 2 0 9 は、多結晶半導体を用いて 3 0 ~ 1 0 0 nm、好ましくは 4 0 ~ 6 0 nmの厚さで形成する。多結晶半導体の材料に限定はないが、代表的にはシリコンまたはシリコンゲルマニウム ( S i G e )

合金などで形成すると良い。多結晶半導体は、プラズマCVD法やスパッタ法で作製される非晶質構造を有する半導体をレーザー結晶化法や熱結晶化法を用いて結晶化させて得る

### [0030]

レーザー結晶化法で多結晶半導体を作製するには、パルス発振型または連続発光型のエキシマレーザーや Y A G レーザー、 Y V O  $_4$  レーザー、 Y L F レーザーを用いる。これらのレーザーを用いる場合には、レーザー発振器から放射されたレーザー光を光学系で線状に集光し半導体膜に照射する方法を採用する。結晶化の条件は実施者が適宣選択するものであるが、エキシマレーザーを用いる場合はパルス発振周波数 3 0 Hz とし、レーザーエネルギー密度を 1 0 0 ~ 4 0 0 mJ/cm² (代表的には 2 0 0 ~ 3 0 0 mJ/cm²) とする。また、 Y A G レーザーを用いる場合にはその第 2 高調波を用いパルス発振周波数 1 ~ 1 0 kHz とし、レーザーエネルギー密度を 3 0 0 ~ 6 0 0 mJ/cm² (代表的には 3 5 0 ~ 5 0 0 mJ/cm²) とすると良い。そして幅 1 0 0 ~ 1 0 0 0  $\mu$ m、例えば 4 0 0  $\mu$ mで線状に集光したレーザー光を基板全面に渡って照射し、この時の線状レーザー光の重ね合わせ率(オーバーラップ率)を 8 0 ~ 9 8 % として行う。

#### [0031]

この段階で、半導体膜 2 0 9 には T F T のしきい値電圧を制御する目的で、ボロンに代表される p 型の不純物(アクセプタ)を 1  $\times$  1 0  $^{16}$  ~ 5  $\times$  1 0  $^{17}$  / cm  $^3$  の濃度で添加しておいても良い。

#### [0032]

多結晶半導体から成る半導体膜209は、第2のフォトマスクを用いて所定のパターンに形成する。図4(C)は島状に分割された半導体膜210~213を示す。半導体膜210~212は、ゲート電極202、204と一部が重なるように形成する。図2はこの状態における画素部の上面図を示し、図中に示すA-A'線に対応する断面が、図4(C)に対応している。

## [0033]

その後、分割された半導体膜210~213上に酸化シリコンまたは窒化シリコンから成る絶縁膜を100~200nmの厚さに形成する。図4(D)は、ゲート電極をマスクとする裏面からの露光プロセスにより、自己整合的にチャネル保護膜とする第3の絶縁層214~218を半導体膜210~212上に形成する。

#### [0034]

そして、 n チャネル型 T F T の L D D D (Lightly Doped Drain) 領域を形成するための第 1 のドーピング工程を行う。ドーピングの方法はイオンドープ法若しくはイオン注入法で行えば良い。 n 型の不純物(ドナー)としてリン(P)を添加し、第 3 の絶縁層 2 1 5 ~ 2 1 8 をマスクとして形成される第 1 の不純物領域 2 1 9 ~ 2 2 2 を形成する。この領域のドナー濃度は 1 × 1 0  $^{16}$  ~ 2 × 1 0  $^{17}$ /cm $^3$  の濃度とする。

#### [0035]

第2のドーピング工程はnチャネル型TFTのソース領域及びドレイン領域を形成する工程であり、図5 (A)で示すように第3のフォトマスクを用いて、レジストによるマスク223~225を形成する。マスク224、225はnチャネル型TFTのLDD領域を覆って形成され、第2の不純物領域226~228には1×10<sup>20</sup>~1×10<sup>21</sup>/cm<sup>3</sup>の濃度範囲でドナー不純物を添加する。

### [0036]

この第2のドーピング工程に前後して、マスク223~225が形成された状態でフッ酸によるエッチング処理を行い、第3の絶縁層214、218を除去しておくと好ましい

10

20

30

40

10

20

30

40

50

[0037]

pチャネル型TFTのソース領域及びドレイン領域は、図5(B)に示すように第3のドーピング処理により行い、イオンドープ法やイオン注入法でp型の不純物(アクセプタ)を添加して第3の不純物領域230、231を形成する。この領域のp型の不純物濃度は2×10 $^{20}$ ~2×10 $^{21}$ /cm $^{3}$ となるようにする。この工程において、半導体膜213にもp型の不純物を添加しておく。

[0038]

次に、図5(C)に示すように、半導体膜上に第2の絶縁膜を形成する。好適には、第2の絶縁膜を複数の絶縁膜で形成する。半導体膜上に形成する第2の絶縁膜の第1層目232は水素を含有する窒化シリコン膜または窒化酸化シリコン膜から成る無機絶縁物で50~200nmの厚さに形成する。その後、それぞれの半導体膜に添加された不純物を活性化する工程を行う。この工程はファーネスアニール炉を用いる熱アニール法で行う。その他に、レーザーアニール法、またはラピッドサーマルアニール法(RTA法)を適用することができる。熱アニール法は窒素雰囲気中で400~600 、代表的には450~500 で行1~4時間の熱処理を行う。

[0039]

この熱処理により、不純物元素の活性化と同時に第2の絶縁膜の第1層目232の窒化シリコン膜または窒化酸化シリコン膜の水素が放出され、半導体膜の水素化を行うことができる。この工程は水素により半導体膜のダングリングボンドを終端する工程である。水素化をより効率よく行う手段として、第2の絶縁膜の第1層目232を形成する前にプラズマ水素化(プラズマにより励起された水素を用いる)を行っても良い。

[0040]

図 6 ( A ) で示す第 2 の絶縁膜の第 2 層目 2 3 3 は、ポリイミド、アクリルなどの有機 絶縁物材料で形成し表面を平坦化する。勿論、プラズマ C V D 法で T E O S (Tetraethy I Ortho Silicate)を用いて形成される酸化シリコン膜を適用しても良いが、平坦性を高 める観点からは前記有機物材料を用いることが望ましい。

[0041]

次いで、第5のフォトマスクを用いてコンタクトホールを形成する。そして、第6のフォトマスクを用いてアルミニウム(A1)、チタン(Ti)、タンタル(Ta)などを用いて、駆動回路305において接続電極234及びソースまたはドレイン配線235~236を形成する。また、画素部306において、画素電極240、ゲート配線239、接続電極238を形成する。

[0042]

こうして、同一の基板上に p チャネル型 T F T 3 0 1 と n チャネル型 T F T 3 0 2 を有する駆動回路 3 0 5 と、画素 T F T 3 0 3 と保持容量 3 0 4 を有する画素部 3 0 6 が形成される。駆動回路 3 0 5 の p チャネル型 T F T 3 0 1 には、チャネル形成領域 3 0 7、第3 の不純物領域から成るソースまたはドレイン領域 3 0 8 が形成されている。 n チャネル型 T F T 3 0 2 には、チャネル形成領域 3 0 9、第1の不純物領域から成るLDD領域 3 1 0、第2の不純物領域から成るソースまたはドレイン領域 3 1 1 が形成されている。画素部 3 0 6 の画素 T F T 3 0 3 は、マルチゲート構造であり、チャネル形成領域 3 1 2、 L D D 領域 3 1 3、ソースまたはドレイン領域 3 1 4、 3 1 6 が形成される。 L D D 領域 3 1 3 の間に位置する第2の不純物領域は、オフ電流を低減するために有用である。保持容量 3 0 4 は、容量配線 2 0 5 と半導体膜 2 1 3 とその間に形成される第1の絶縁膜とから形成されている。

[0043]

画素部306においては、接続電極238によりソース配線207は、画素TFT303のソースまたはドレイン領域314と電気的な接続が形成される。また、ゲート配線239は、第1の電極と電気的な接続が形成される。また、画素電極240は、画素TFT303の3のソースまたはドレイン領域316及び保持容量304の半導体膜213と接続し

ている。

## [0044]

図 6 ( A ) における画素部 3 0 6 の断面図は、図 1 で示す A - A '線に対応したもので ある。また、図 1 において示す B - B '線及び C - C '線に沿った断面図は、それぞれ図 6 (B)と(C)に示されている。図6(B)はゲート電極204とゲート配線239のコ ン タ ク ト 部 を 説 明 す る 図 で あ る 。 ゲ ー ト 電 極 2 0 4 は 隣 接 す る 画 素 の 保 持 容 量 の 一 方 の 電 極 を 兼 ね 、 画 素 電 極 2 4 5 と 接 続 す る 半 導 体 膜 2 4 4 と 重 な る 部 分 で 容 量 を 形 成 し て い る 。また、図6(C)はソース配線207と画素電極240及び隣接する画素電極246と の配置関係を示し、画素電極の端部をソース配線207上に設け、重なり部を形成するこ とにより、迷光を遮り遮光性を高めている。また、図3はこのような画素の等価回路を示 している。尚、本明細書中ではこのような基板を便宜上アクティブマトリクス基板と呼ぶ

#### [0045]

TFTを逆スタガ型で形成することの利点の一つは、nチャネル型TFTにおいてゲー ト電極とオーバーラップするLDD領域を裏面露光のプロセスにより自己整合的に形成で きることにあり、ゲート絶縁膜と半導体膜を連続形成できる特徴と相まってTFTの特性 ばらつきを小さくすることができる。

#### 【実施例2】

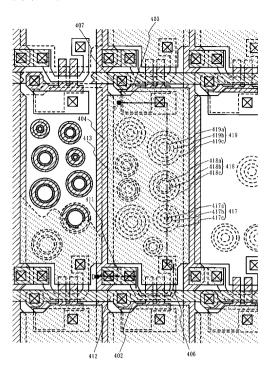

# [0046]

本実施例は、反射型の液晶表示装置に適した画素構造の一例を示し、図8で示す画素の 上面図と、その図中に示すD-D′線に対応する断面図を図7で示して説明する。図7に お い て 、 画 素 部 4 2 2 の 画 素 TFT 4 2 0 は 基 板 4 0 1 上 に ゲ ー ト 電 極 4 0 2 、 第 1 の 絶 縁 膜 4 0 5 、 半 導 体 膜 4 0 6 、 チ ャ ネ ル 保 護 膜 4 0 8 、 第 2 の 絶 縁 膜 4 0 9 、 4 1 0 ソ ー ス 配 線 4 0 4 、 ゲ ー ト 配 線 4 1 2 、 接 続 配 線 4 1 1 、 画 素 電 極 4 1 3 か ら 成 っ て い る 。 ま た、保持容量421は、容量配線403と半導体膜407とその間に形成されている第1 の 絶 縁 膜 4 0 5 か ら 成 り 、 こ れ ら の 構 成 は 図 6 ( A ) で 示 す 画 素 T F T 3 0 3 、 保 持 容 量 3 0 4 と同様な構成である。

[0047]

画素部422の画素電極413の下側には、その表面を凹凸化させる島状領域417~ 4 1 9 が形成されている。図では便宜上 3 つの島状領域を示すが、大きさを 5 ~ 1 0 μm ピッチを10~20 μ m として形成する。それぞれの島状領域は、ゲート電極402と 同じ膜を用いて形成される第1の層417a~419a、半導体膜406と同じ層から形成 される第2の層4176~4196、第3の絶縁層408と同じ層から形成される第3の 層 4 1 7 c ~ 4 1 9 c から成っている。これらの層はそれそれ別の工程でエッチング形成 されるため、端部は一致せず、上層に行くに従って小さくなるように形成する。

[0048]

その上に第 2 の絶 縁 膜 4 0 9 、 4 1 0 を 形 成 す る が 、 有 機 樹 脂 材 料 で 形 成 す る 第 2 の 絶 縁膜410は下地の凹凸を反映したものとするため、粘度が10~1000cp(好ましく は、40~200cp)のものを塗布して焼成し、表面に凹凸形状が形成されるものを用い る。有機樹脂材料から成る層を形成することにより、表面は曲率をもったなだらかな凹凸 形状が形成され、その曲率半径を 0 . 1 ~ 4 μmとなるようにする。図 8 では島状領域を 円形で示したが、形状はこれに限定される必要はなく、任意の多角形とすることができる 。このような画素の構成とすることにより、反射型の液晶表示装置において鏡面反射が防 止され、特に白表示のときの表示品位を向上させることができる。

【 実 施 例 3 】

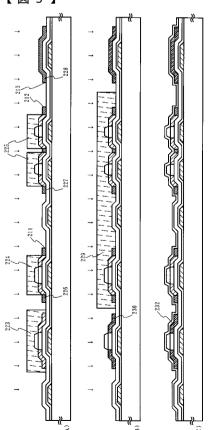

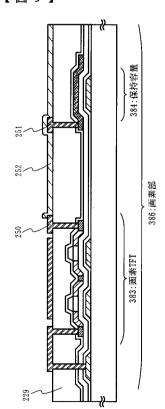

# [0049]

実 施 例 1 で は 反 射 型 の ア ク テ ィ ブ マ ト リ ク ス 型 液 晶 表 示 装 置 の 例 を 示 し た が 、 画 素 電 極 を透明導電膜で形成することにより透過型の表示装置を形成することができる。図9に示 す 画 素 部 3 8 6 の 画 素 T F T 3 8 3 は 、 実 施 例 1 で 説 明 す る 画 素 T F T 3 0 3 と 同 様 に し て作製されるものであり、本実施例ではその相違点について述べる。

10

20

30

40

### [0050]

有機樹脂材料から成る第2の絶縁膜の第2層目229を形成した後、ゲート配線及び接続電極と同時に第1の画素電極250、251を形成する。第1の画素電極250は画素TFT383の半導体膜と接続し、251は保持容量384を形成する半導体膜と接続している。その後、透明導電膜252を形成し画素電極とする。

## [0051]

透明導電膜の材料は、酸化インジウム( $In_2O_3$ )や酸化インジウム酸化スズ合金( $In_2O_3$   $SnO_2$ ; ITO)などをスパッタ法や真空蒸着法などを用いて形成する。このような材料のエッチング処理は塩酸系の溶液により行う。また、ITOのエッチングは残渣が発生しやすいので、エッチング加工性を改善するために酸化インジウム酸化亜鉛合金( $In_2O_3$  ZnO)を用いても良い。酸化インジウム酸化亜鉛合金は表面平滑性に優れ、ITOに対して熱安定性にも優れている。同様に、酸化亜鉛(ZnO)も適した材料であり、さらに可視光の透過率や導電率を高めるためにガリウム(Ga)を添加した酸化亜鉛(ZnO:Ga)などを用いることができる。

### [0052]

以上のように、実施例 1 では反射型の液晶表示装置を作製できるアクティブマトリクス 基板を 5 枚のフォトマスクにより作製したが、さらに 1 枚のフォトマスクの追加(合計 6 枚)で、透過型の液晶表示装置に対応したアクティブマトリクス基板を完成させることが できる。

# 【実施例4】

### [0053]

本実施例では実施例1で作製したアクティブマトリクス基板から、アクティブマトリクス型液晶表示装置を作製する工程を説明する。図10はアクティブマトリクス基板と対向基板454とをシール材458で貼り合わせた状態を示している。最初に、図6(A)の状態のアクティブマトリクス基板上に柱状のスペーサ451、452を形成する。画素部に設けるスペーサ451は画素電極上のコンタクト部に重ねて設ける。スペーサは用いる液晶材料にも依存するが、3~10μmの高さとする。コンタクト部では、コンタクトホールに対応した凹部が形成されるので、この部分に合わせてスペーサを形成することにより液晶の配向の乱れを防ぐことができる。その後、配向膜453を形成しラビング処理を行う。対向基板454には透明導電膜455、配向膜456を形成する。その後、アクティブマトリクス基板と対向基板とを貼り合わせ液晶を注入する。

# [0054]

図11はアクティブマトリクス基板と対向基板とを貼り合わせて組み立てる様子を模式的に示す。アクティブマトリクス基板650は、画素部653、走査線側駆動回路652、信号線側駆動回路651、外部入力端子654、外部入力端子から各回路の入力部までを接続する配線659などが形成されている。対向基板655にはアクティブマトリクス基板650の画素部及び駆動回路が形成されている領域に対応して対向電極656が形成されている。このようなアクティブマトリクス基板650と対向基板655とはシール材657を介して貼り合わせ、液晶を注入してシール材657の内側に液晶層658を設ける。さらに、アクティブマトリクス基板650の外部入力端子654にはFPC(フレキシブルプリント配線板:Flexible Printed Circuit)660を貼り付ける。FPC660の接着強度を高めるために補強板659を設けても良い。

## [0055]

以上のようにして作製されるアクティブマトリクス型の液晶表示装置は各種電子装置の表示装置として用いることができる。また、本実施例で示すアクティブマトリクス型液晶表示装置の作製方法は、実施例 2 又は実施例 3 のアクティブマトリクス基板を用いる場合においても同様に適用することができる。

## 【実施例5】

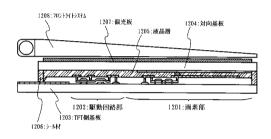

## [0056]

図12は本発明の画素構造を用いて作製される反射型液晶表示装置のアクティブマトリ

20

10

30

40

クス型液晶表示装置を直視型の表示装置として用いる例を示す。アクティブマトリクス基板 1 2 0 3 には画素部 1 2 0 1 及び駆動回路部 1 2 0 2 が形成され、シール材 1 2 0 6 により対向基板 1 2 0 4 が接着され、その間に液晶層 1 2 0 5 が形成されている。

### [0057]

図12の構成は、フロントライトを用いた反射型液晶表示装置の例であり、偏光板1207上にフロントライトシステム1208を設ける。反射型液晶表示装置は、昼間明るい場所では外光を利用して画像の表示を行うが、夜間など十分な外光を導入できない場合には、フロントライトを用いて表示を行う方式を採用することができる。いずれにしても、本発明の画素構造とすることにより、画素部における画素電極の占める割合が大きくなり、明るい画像表示を実現することができる。また、フロントライトを用いる場合には、照射する光の強度を小さくすることができ、このような液晶表示装置を組み込んだ電子装置の消費電力を少なくすることができる。このような本実施例に構成は、実施例4で作製されるアクティブマトリクス型液晶表示装置に適用することができる。

## 【実施例6】

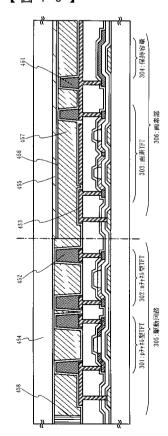

## [0058]

本実施例では、実施例 1 で示したアクティブマトリクス基板を、エレクトロルミネッセンス(EL:Electro Luminescence)材料を用いた自発光型の表示装置(以下、EL表示装置と記す)に適用する場合について説明する。尚、エレクトロルミネッセンス材料における発光には、蛍光と燐光とによる発光の両方があり、本実施例でいう発光にはそのいずれか一方、またはその両方による発光を含んでいる。

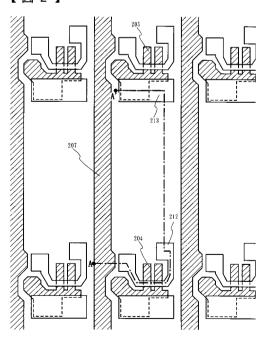

#### [0059]

図13は画素部の断面図を示し、スイッチング用TFT701、電流制御用TFT70 2、保持容量703が形成されている様子を示す。これらのTFTは実施例1と同様の工程で作製される。スイッチング用TFT701はnチャネル型TFTであり、ゲート電極751上の半導体膜755にチャネル形成領域704、LDD領域705、ソースまたはドレイン領域706を有している。そして、半導体膜755はソース配線753と接続電極761により接続されている。

#### [0060]

電流制御用TFT202はpチャネル型TFTであり、ゲート電極752上の半導体膜756にチャネル形成領域707、ソースまたはドレイン領域708を有している。そして、電流制御用TFT202のソース側は電源線764と接続し、ドレイン側はドレイン電極765と接続している。さらに、ドレイン電極765には透明導電膜で形成される画素電極766が接続している。また、容量配線752と半導体膜756とが重なる領域において保持容量703が形成される。

#### [0061]

第 1 の絶縁膜 7 5 4 ( 7 5 4 a 、 7 5 4 b )、第 2 の絶縁膜 7 5 9 、 7 6 0 は実施例 1 と同様のものとする。

## [0062]

図13(A)の断面図は、図14で示す E-E'線に対応したものである。また、図14において示す F-F'線及び G-G'線に沿った断面図は、それぞれ図13(B)と(C)に示されている。図13(B)はスイッチング用TFT701のゲート電極751とゲート配線772のコンタクト部を説明する図である。

また、図13(C)はソース配線753と画素電極767及び隣接する画素電極771と の配置関係を示し、画素電極の端部をソース配線753上に設け、重なり部を形成することにより遮光性を高めている。

# [0063]

画素部には、陽極として用いる画素電極の端部を覆う絶縁膜でなるバンク767が形成され、その上にエレクトロルミネッセンスを発現させる有機化合物層が形成される。溶液塗布によりポリビニルカルバゾールなどの材料でなる発光層、カリウムアセチルアセトネート(acacKと表記される)でなる電子注入層を含む有機化合物層768、769が

10

20

30

40

形成される。その上にはアルミニウム合金でなる陰極770が形成される。この場合、陰極770がパッシベーション膜としても機能する。こうして陽極、有機化合物層、陰極から成る自発光型のEL素子が形成される。本実施例の場合、発光層768で発生した光はアクティブマトリクス基板の方に向かって放射される。

[0064]

このように、本発明の画素構造とすることにより、アクティブマトリクス型の自発光型の表示装置においても開口率を向上させることができる。その結果、明るく鮮明な画像表示を可能とする。

- 【実施例7】

- [0065]

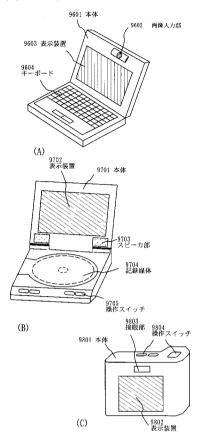

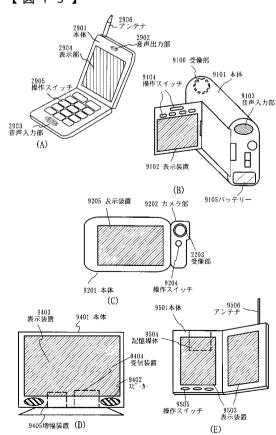

本実施例では、本発明の表示装置を組み込んだ半導体装置について示す。このような半導体装置には、携帯情報端末(電子手帳、モバイルコンピュータ、携帯電話等)、ビデオカメラ、スチルカメラ、パーソナルコンピュータ、テレビ等が挙げられる。それらの一例を図15と図16に示す。

[0066]

図15(A)は携帯電話であり、本体2901、音声出力部9002、音声入力部2903、表示装置2904、操作スイッチ2905、アンテナ2906から構成されている。本発明は表示装置2904に適用することができ、特に、実施例5で示す反射型の液晶表示装置は低消費電力化の観点から適している。

[0067]

図15(B)はビデオカメラであり、本体9101、表示装置9102、音声入力部9103、操作スイッチ9104、バッテリー9105、受像部9106から成っている。本発明は表示装置9102に適用することができる。特に、実施例5で示す反射型の液晶表示装置は低消費電力化の観点から適している。

[0068]

図 1 5 ( C ) はモバイルコンピュータ或いは携帯型情報端末であり、本体 9 2 0 1 、カメラ部 9 2 0 2 、受像部 9 2 0 3 、操作スイッチ 9 2 0 4 、表示装置 9 2 0 5 で構成されている。本発明は表示装置 9 2 0 5 に適用することができる。

特に、実施例5で示す反射型の液晶表示装置は低消費電力化の観点から適している。

[0069]

図15(D)はテレビ受像器であり、本体9401、スピーカー9402、表示装置9403、受信装置9404、増幅装置9405等で構成される。本発明は表示装置9403に適用することができる。特に、実施例5で示す反射型の液晶表示装置は低消費電力化の観点から適している。

[0070]

図15(E)は携帯書籍であり、本体9501、表示装置9502、9503、記憶媒体9504、操作スイッチ9505、アンテナ9506から構成されており、ミニディスク(MD)やDVDに記憶されたデータや、アンテナで受信したデータを表示するものである。直視型の表示装置9502、9503は特に、実施例5で示す反射型の液晶表示装置は低消費電力化の観点から適している。

[0071]

図16(A)はパーソナルコンピュータであり、本体9601、画像入力部9602、表示装置9603、キーボード9604で構成される。本発明は表示装置9603に適用することができる。特に、実施例5で示す反射型の液晶表示装置は低消費電力化の観点から適している。

[0072]

図16(B)はプログラムを記録した記録媒体(以下、記録媒体と呼ぶ)を用いるプレーヤーであり、本体9701、表示装置9702、スピーカ部9703、記録媒体9704、操作スイッチ9705で構成される。なお、この装置は記録媒体としてDVD(Digtial Versatile Disc)、CD等を用い、音楽鑑賞や映画鑑賞やゲー

10

20

30

40

ムやインターネットを行うことができる。本発明は表示装置 9 7 0 2 に適用することができる。特に、実施例 5 で示す反射型の液晶表示装置は低消費電力化の観点から適している

# [ 0 0 7 3 ]

図16(C)はデジタルカメラであり、本体9801、表示装置9802、接眼部9803、操作スイッチ9804、受像部(図示しない)で構成される。本発明は表示装置9802に適用することができる。特に、実施例5で示す反射型の液晶表示装置は低消費電力化の観点から適している。

# 【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

# 【図11】

# 【図12】

# 【図14】

# 【図13】

# 【図15】

# 【図16】