(19)日本国特許庁(JP)

**(12)特許公報(B1)**

(11)特許番号

**特許第7619541号**

**(P7619541)**

(45)発行日 令和7年1月22日(2025.1.22)

(24)登録日 令和7年1月14日(2025.1.14)

(51)国際特許分類

|        |                |        |       |       |

|--------|----------------|--------|-------|-------|

| H 01 G | 9/012(2006.01) | H 01 G | 9/012 | 3 0 5 |

| H 01 G | 9/048(2006.01) | H 01 G | 9/048 | H     |

| H 01 G | 9/15 (2006.01) | H 01 G | 9/15  |       |

| H 01 G | 4/30 (2006.01) | H 01 G | 4/30  | 5 4 0 |

請求項の数 4 (全26頁)

(21)出願番号 特願2024-564758(P2024-564758)

(86)(22)出願日 令和6年5月14日(2024.5.14)

(86)国際出願番号 PCT/JP2024/017754

審査請求日 令和6年10月31日(2024.10.31)

(31)優先権主張番号 特願2023-99240(P2023-99240)

(32)優先日 令和5年6月16日(2023.6.16)

(33)優先権主張国・地域又は機関

日本国(JP)

早期審査対象出願

(73)特許権者 000006231

株式会社村田製作所

京都府長岡京市東神足1丁目10番1号

(74)代理人 110000914

弁理士法人WisePlus

吉川 真徳

京都府長岡京市東神足1丁目10番1号

株式会社村田製作所内

(72)発明者 高橋 章友

京都府長岡京市東神足1丁目10番1号

株式会社村田製作所内

(72)発明者 審査官 木下 直哉

最終頁に続く

(54)【発明の名称】 コンデンサ素子

**(57)【特許請求の範囲】****【請求項1】**

芯部の少なくとも一方の正面に多孔質部を有する陽極板と、前記多孔質部の表面に設けられた誘電体層と、前記誘電体層の表面に設けられた陰極層と、を含むコンデンサ部と、前記コンデンサ部を覆うように設けられた封止層と、

前記陽極板に電気的に直接接続されるように前記コンデンサ部及び前記封止層を厚さ方向に貫通するように設けられ、両方の端部が前記封止層の表面に引き出された第1スルーホール導体と、

前記陰極層に電気的に直接接続されるように前記コンデンサ部及び前記封止層を前記厚さ方向に貫通するように設けられ、両方の端部が前記封止層の表面に引き出された第2スルーホール導体と、

前記第1スルーホール導体に電気的に接続されるように前記封止層の表面に設けられた第1外部電極層と、

前記第2スルーホール導体に電気的に接続されるように前記封止層の表面に設けられた第2外部電極層と、を備え、

前記第1外部電極層の少なくとも一部は、前記厚さ方向において前記陰極層に重なり、前記陰極層、前記第1外部電極層及び前記第2外部電極層は、それぞれ、銅層を含み、前記陰極層の銅層の厚みをd1、前記第1外部電極層の銅層の厚みをd2、前記第2外部電極層の銅層の厚みをd3としたとき、

d1 d2かつd1 d3を満たす、コンデンサ素子。

**【請求項 2】**

前記第1外部電極層の面積をS1、前記第2外部電極層の面積をS2としたとき、

$S_1 > S_2$ を満たす、請求項1に記載のコンデンサ素子。

**【請求項 3】**

前記封止層を前記厚さ方向に貫通するように設けられ、一方の端部が前記第2外部電極層に電気的に接続され、他方の端部が前記陰極層に電気的に接続された内部ビア導体をさらに備える、請求項1又は2に記載のコンデンサ素子。

**【請求項 4】**

前記陰極層は、前記誘電体層の表面上に設けられた固体電解質層と、前記固体電解質層の表面上に設けられた第1導電体層と、前記第2スルーホール導体に電気的に直接接続されるように前記第1導電体層の表面上に設けられた第2導電体層と、を含む、請求項1又は2に記載のコンデンサ素子。

10

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、コンデンサ素子に関する。

**【背景技術】****【0002】**

特許文献1には、少なくとも片面に多孔質部が設けられ所定の位置に貫通孔が形成された箔状の陽極と、上記陽極の多孔質部に形成された誘電体被膜と、上記誘電体被膜に形成された開口部を有する絶縁層と、上記絶縁層の開口部の上記誘電体被膜に形成された固体電解質層と、上記固体電解質層の少なくとも一部に形成され、上記陽極と略平行に配置された陰極と、上記絶縁層に形成された電極と、上記絶縁層及び上記陽極を貫通し、上記電極 - 上記陽極間を電気接続する及び / 又は、上記絶縁層及び上記陰極を貫通し、上記電極 - 上記陰極間を電気接続するスルーホール電極を備え、上記スルーホール電極の少なくとも一つが、長孔形状である固体電解コンデンサが記載されている。

20

**【先行技術文献】****【特許文献】****【0003】****【文献】特開2007-281111号公報**

30

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

近年、電子機器の小型化及び高出力化に伴い、部品の高密度化が求められている。そのため、コンデンサ素子を電源直下の基板、例えばGPU(Graphical Processing Unit)基板等に埋め込むことが検討されている。当該用途では大電流が流されるが、従来のコンデンサ素子の構造では放熱性が不充分であり、コンデンサ素子の内部抵抗により熱が発生する可能性がある。このような各種部品からの発熱は、電子機器の安全性、信頼性、性能、寿命等に悪影響を及ぼす可能性がある。

40

**【0005】**

特許文献1に記載の固体電解コンデンサについても、放熱性を向上するという点で改善の余地があった。

**【0006】**

本発明は、上記の問題を解決するためになされたものであり、放熱性を向上することが可能なコンデンサ素子を提供することを目的とする。

**【課題を解決するための手段】****【0007】**

本発明のコンデンサ素子は、芯部の少なくとも一方の主面に多孔質部を有する陽極板と、上記多孔質部の表面に設けられた誘電体層と、上記誘電体層の表面に設けられた陰極層と、を含むコンデンサ部と、上記コンデンサ部を覆うように設けられた封止層と、上記陽

50

極板に電気的に直接接続されるように上記コンデンサ部及び上記封止層を厚さ方向に貫通するように設けられ、両方の端部が上記封止層の表面に引き出された第1スルーホール導体と、上記陰極層に電気的に直接接続されるように上記コンデンサ部及び上記封止層を上記厚さ方向に貫通するように設けられ、両方の端部が上記封止層の表面に引き出された第2スルーホール導体と、上記第1スルーホール導体に電気的に接続されるように上記封止層の表面に設けられた第1外部電極層と、上記第2スルーホール導体に電気的に接続されるように上記封止層の表面に設けられた第2外部電極層と、を備え、上記第1外部電極層の少なくとも一部は、上記厚さ方向において上記陰極層に重なる。

**【発明の効果】**

**【0008】**

本発明によれば、放熱性を向上することが可能なコンデンサ素子を提供することができる。

**【図面の簡単な説明】**

**【0009】**

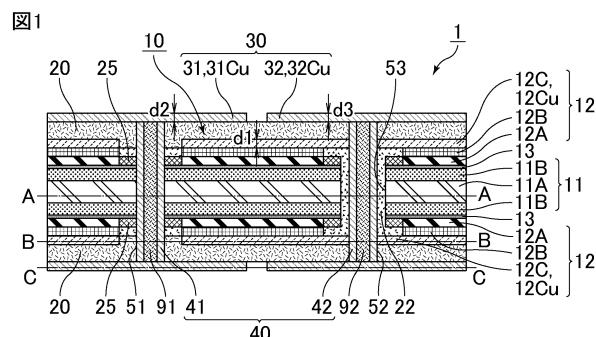

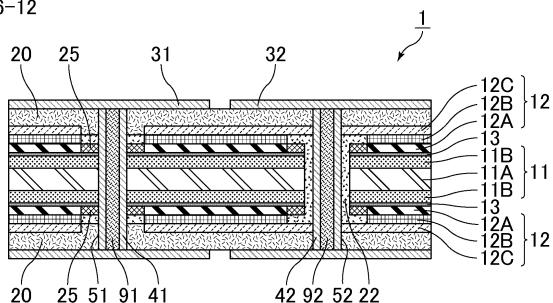

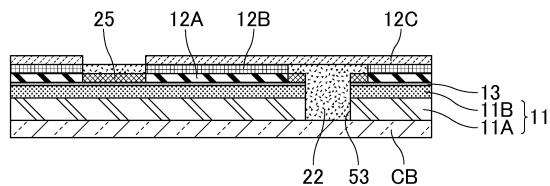

**【図1】**図1は、本発明の第1実施形態に係るコンデンサ素子の一例を模式的に示す断面図である。

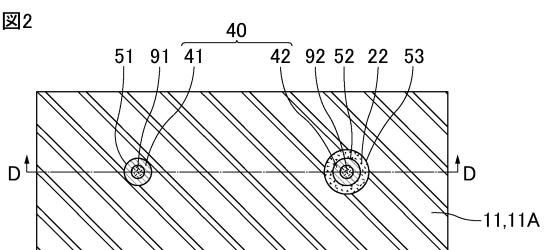

**【図2】**図2は、図1に示すコンデンサ素子のA-A線に沿った平面図である。

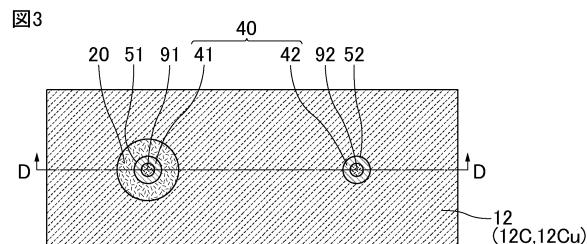

**【図3】**図3は、図1に示すコンデンサ素子のB-B線に沿った平面図である。

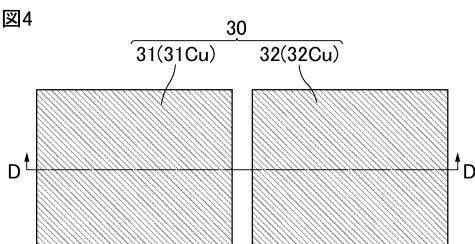

**【図4】**図4は、図1に示すコンデンサ素子のC-C線に沿った平面図である。

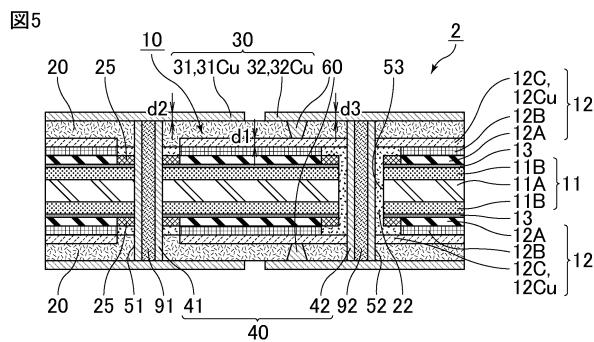

**【図5】**図5は、本発明の第1実施形態に係るコンデンサ素子の別の一例を模式的に示す断面図である。

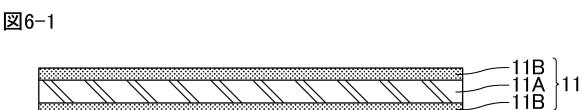

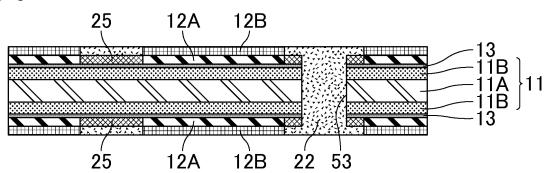

**【図6-1】**図6-1は、図1に示すコンデンサ素子の製造方法の一例を説明する断面模式図であり、陽極板を準備する工程を示す。

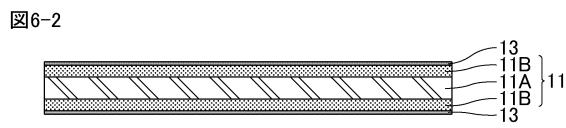

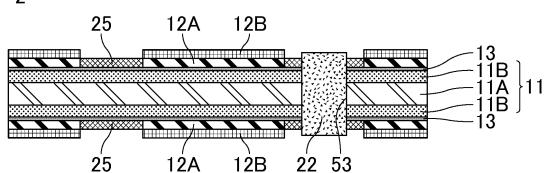

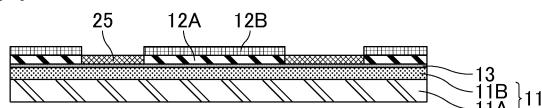

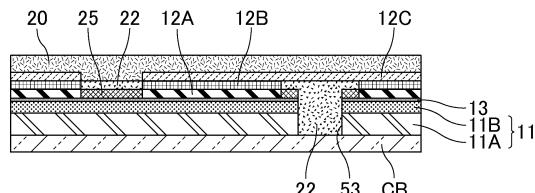

**【図6-2】**図6-2は、図1に示すコンデンサ素子の製造方法の一例を説明する断面模式図であり、誘電体層を形成する工程を示す。

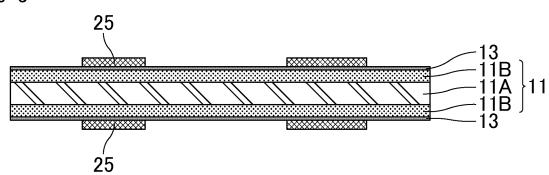

**【図6-3】**図6-3は、図1に示すコンデンサ素子の製造方法の一例を説明する断面模式図であり、絶縁マスク層を形成する工程を示す。

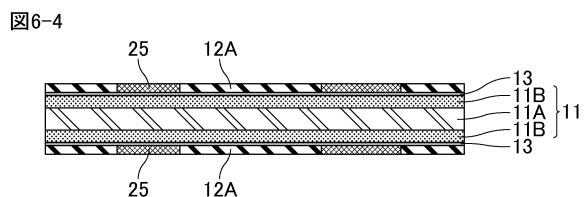

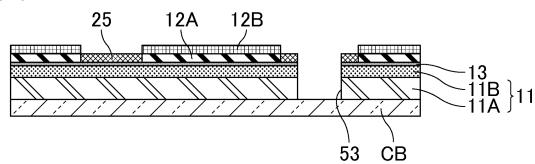

**【図6-4】**図6-4は、図1に示すコンデンサ素子の製造方法の一例を説明する断面模式図であり、固体電解質層を形成する工程を示す。

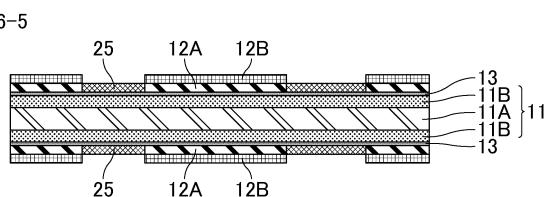

**【図6-5】**図6-5は、図1に示すコンデンサ素子の製造方法の一例を説明する断面模式図であり、第1導電体層を形成する工程を示す。

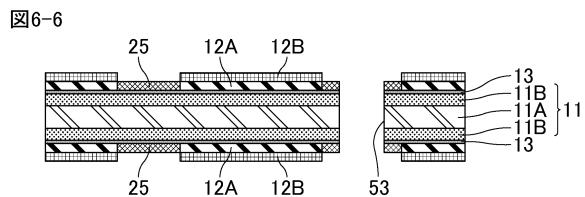

**【図6-6】**図6-6は、図1に示すコンデンサ素子の製造方法の一例を説明する断面模式図であり、貫通孔を形成する工程を示す。

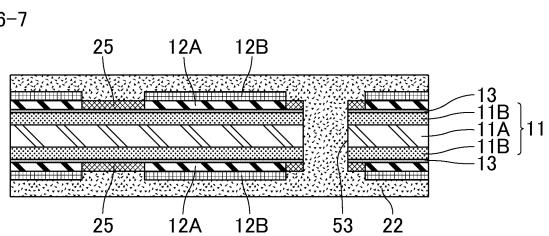

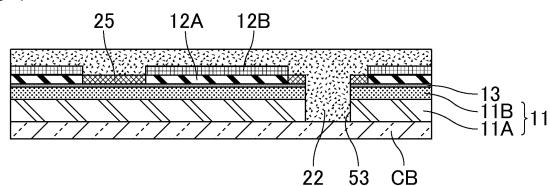

**【図6-7】**図6-7は、図1に示すコンデンサ素子の製造方法の一例を説明する断面模式図であり、絶縁性材料を形成する工程を示す。

**【図6-8】**図6-8は、図1に示すコンデンサ素子の製造方法の一例を説明する断面模式図であり、絶縁性材料を研磨する工程を示す。

**【図6-9】**図6-9は、図1に示すコンデンサ素子の製造方法の一例を説明する断面模式図であり、第2導電体層を形成する工程を示す。

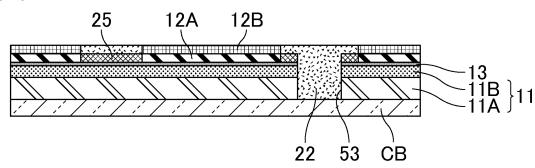

**【図6-10】**図6-10は、図1に示すコンデンサ素子の製造方法の一例を説明する断面模式図であり、封止層を形成する工程を示す。

**【図6-11】**図6-11は、図1に示すコンデンサ素子の製造方法の一例を説明する断面模式図であり、第1貫通孔及び第2貫通孔を形成する工程を示す。

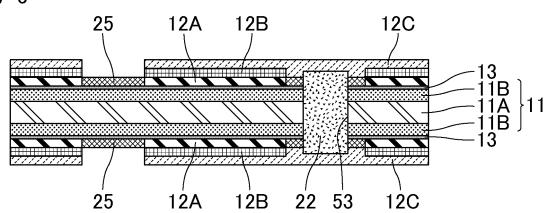

**【図6-12】**図6-12は、図1に示すコンデンサ素子の製造方法の一例を説明する断面模式図であり、スルーホール導体及び外部電極層を形成する工程を示す。

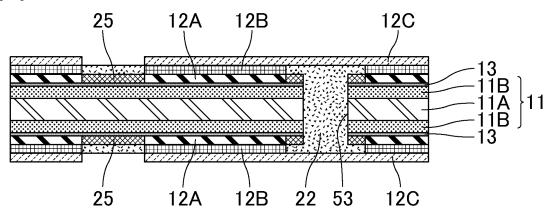

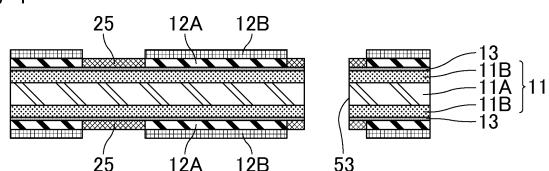

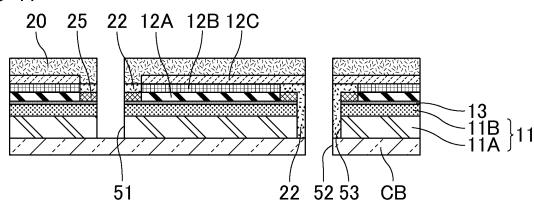

**【図7-1】**図7-1は、図1に示すコンデンサ素子の製造方法の別の一例を説明する断面模式図であり、貫通孔を形成した後の状態を示す。

**【図7-2】**図7-2は、図1に示すコンデンサ素子の製造方法の別の一例を説明する断面模式図であり、絶縁性材料を形成する工程を示す。

**【図7-3】**図7-3は、図1に示すコンデンサ素子の製造方法の別の一例を説明する断

10

20

30

40

50

面模式図であり、第2導電体層を形成する工程を示す。

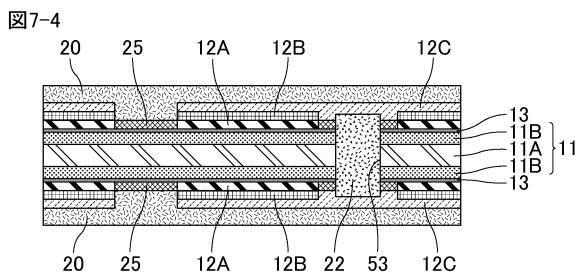

【図7-4】図7-4は、図1に示すコンデンサ素子の製造方法の別の一例を説明する断面模式図であり、封止層を形成する工程を示す。

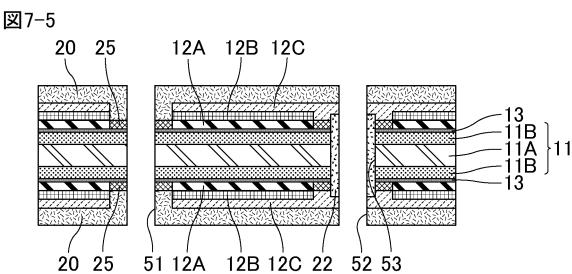

【図7-5】図7-5は、図1に示すコンデンサ素子の製造方法の別の一例を説明する断面模式図であり、第1貫通孔及び第2貫通孔を形成する工程を示す。

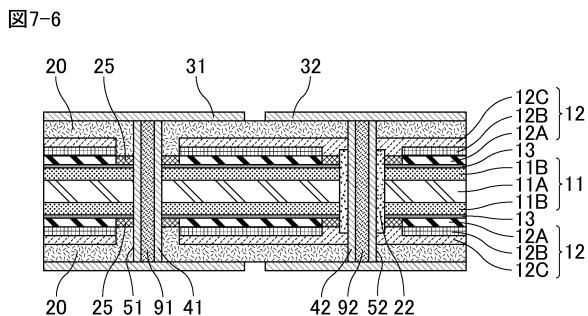

【図7-6】図7-6は、図1に示すコンデンサ素子の製造方法の別の一例を説明する断面模式図であり、スルーホール導体及び外部電極層を形成する工程を示す。

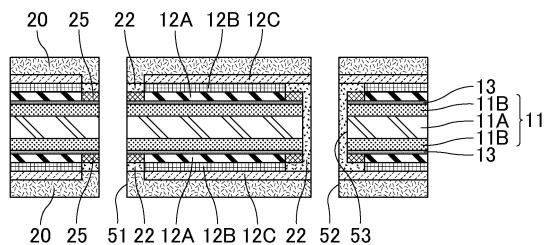

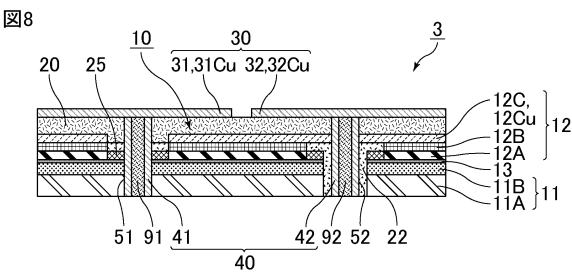

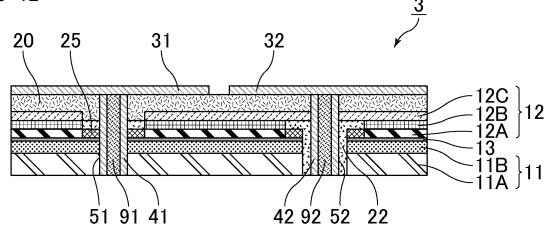

【図8】図8は、本発明の第2実施形態に係るコンデンサ素子の一例を模式的に示す平面図である。

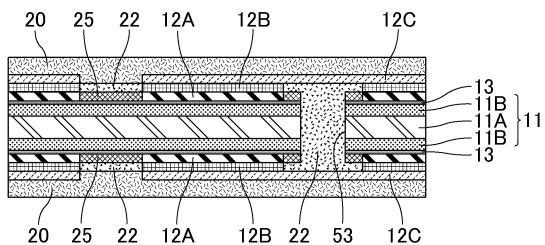

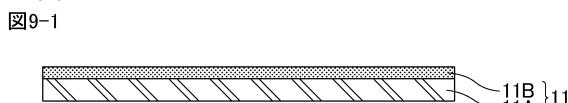

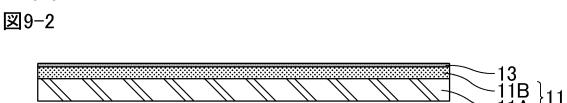

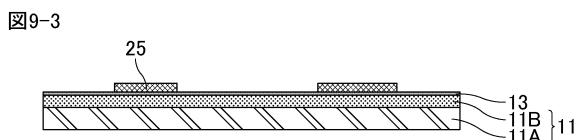

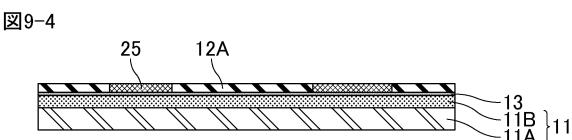

【図9-1】図9-1は、図8に示すコンデンサ素子の製造方法の一例を説明する断面模式図であり、陽極板を準備する工程を示す。 10

【図9-2】図9-2は、図8に示すコンデンサ素子の製造方法の一例を説明する断面模式図であり、誘電体層を形成する工程を示す。

【図9-3】図9-3は、図8に示すコンデンサ素子の製造方法の一例を説明する断面模式図であり、絶縁マスク層を形成する工程を示す。

【図9-4】図9-4は、図8に示すコンデンサ素子の製造方法の一例を説明する断面模式図であり、固体電解質層を形成する工程を示す。

【図9-5】図9-5は、図8に示すコンデンサ素子の製造方法の一例を説明する断面模式図であり、第1導電体層を形成する工程を示す。

【図9-6】図9-6は、図8に示すコンデンサ素子の製造方法の一例を説明する断面模式図であり、貫通孔を形成する工程を示す。 20

【図9-7】図9-7は、図8に示すコンデンサ素子の製造方法の一例を説明する断面模式図であり、絶縁性材料を形成する工程を示す。

【図9-8】図9-8は、図8に示すコンデンサ素子の製造方法の一例を説明する断面模式図であり、絶縁性材料を研磨する工程を示す。

【図9-9】図9-9は、図8に示すコンデンサ素子の製造方法の一例を説明する断面模式図であり、第2導電体層を形成する工程を示す。

【図9-10】図9-10は、図8に示すコンデンサ素子の製造方法の一例を説明する断面模式図であり、封止層を形成する工程を示す。

【図9-11】図9-11は、図8に示すコンデンサ素子の製造方法の一例を説明する断面模式図であり、第1貫通孔及び第2貫通孔を形成する工程を示す。 30

【図9-12】図9-12は、図8に示すコンデンサ素子の製造方法の一例を説明する断面模式図であり、スルーホール導体及び外部電極層を形成する工程を示す。

#### 【発明を実施するための形態】

##### 【0010】

以下、本発明のコンデンサ素子について説明する。なお、本発明は、以下の構成に限定されるものではなく、本発明の要旨を変更しない範囲において適宜変更されてもよい。また、以下において記載する個々の好ましい構成を複数組み合わせたものもまた本発明である。

##### 【0011】

以下に示す各実施形態は例示であり、異なる実施形態で示す構成の部分的な置換又は組み合わせが可能であることは言うまでもない。第2実施形態以降では、第1実施形態と共通の事項についての記載は省略し、異なる点を主に説明する。特に、同様の構成による同様の作用効果については、実施形態毎に逐次言及しない。

##### 【0012】

以下の説明において、各実施形態を特に区別しない場合、単に「本発明のコンデンサ素子」と言う。

##### 【0013】

本明細書において、要素間の関係性を示す用語（例えば「垂直」、「平行」、「直交」等）及び要素の形状を示す用語は、厳格な意味のみを表す表現ではなく、実質的に同等な

10

20

30

40

50

範囲、例えば数%程度の差異をも含むことを意味する表現である。

#### 【0014】

以下に示す図面は模式図であり、その寸法、縦横比の縮尺等は実際の製品と異なる場合がある。

#### 【0015】

##### [第1実施形態]

図1は、本発明の第1実施形態に係るコンデンサ素子の一例を模式的に示す断面図である。図2は、図1に示すコンデンサ素子のA-A線に沿った平面図である。図3は、図1に示すコンデンサ素子のB-B線に沿った平面図である。図4は、図1に示すコンデンサ素子のC-C線に沿った平面図である。なお、図1は、図2～図4に示すコンデンサ素子のD-D線に沿った断面図である。

10

#### 【0016】

図1～図4に示すコンデンサ素子1は、コンデンサ部10と、コンデンサ部10を覆うように設けられた封止層20と、コンデンサ部10及び封止層20を厚さ方向に貫通するように設けられ、両方の端部が封止層20の表面に引き出されたスルーホール導体40と、スルーホール導体40に電気的に接続されるように封止層20の表面に設けられた外部電極層30と、を備える。

#### 【0017】

図1～図4に示す例では、封止層20の内部に1個のコンデンサ部10が配置されている。封止層20の内部に配置されるコンデンサ部10の数は特に限定されず、1個でもよく、複数個でもよい。

20

#### 【0018】

コンデンサ部10は、芯部11Aの少なくとも一方の主面に多孔質部11Bを有する陽極板11と、多孔質部11Bの表面に設けられた誘電体層13と、誘電体層13の表面に設けられた陰極層12と、を含む。これにより、コンデンサ部10は、電解コンデンサを構成する。図1に示す例では、陽極板11は、芯部11Aの両方の主面に多孔質部11Bを有するが、芯部11Aのいずれか一方の主面のみに多孔質部11Bを有してもよい。

#### 【0019】

陰極層12は、例えば、誘電体層13の表面に設けられた固体電解質層12Aを含む。陰極層12が固体電解質層12Aを含む場合、コンデンサ部10は、固体電解コンデンサを構成する。

30

#### 【0020】

封止層20は、図1に示すように、コンデンサ部10の厚さ方向の相対する両方の主面に設けられていることが好ましい。封止層20によってコンデンサ部10が保護される。

#### 【0021】

封止層20は、1層のみから構成されてもよく、2層以上から構成されてもよい。封止層20が2層以上から構成される場合、各層を構成する材料は、それぞれ同じであってもよく、異なっていてもよい。

#### 【0022】

封止層20は、例えば、絶縁性樹脂シートを熱圧着する方法、絶縁性樹脂ペーストを塗工した後で熱硬化させる方法等により、コンデンサ部10を封止するように形成される。

40

#### 【0023】

図1に示す例では、スルーホール導体40は、陽極板11に電気的に接続される第1スルーホール導体41と、陰極層12に電気的に接続される第2スルーホール導体42と、を含む。

#### 【0024】

第1スルーホール導体41は、コンデンサ部10及び封止層20を厚さ方向に貫通する第1貫通孔51の少なくとも内壁面に設けられていればよい。第1スルーホール導体41は、第1貫通孔51の内壁面のみに設けられていてもよく、第1貫通孔51の内部全体に設けられていてもよい。

50

**【 0 0 2 5 】**

図3に示すように、厚さ方向からの平面視で、陰極層12の内部には、1個の第1スルーホール導体41が設けられていてもよく、2個以上の第1スルーホール導体41が設けられていてもよい。

**【 0 0 2 6 】**

第2スルーホール導体42は、コンデンサ部10及び封止層20を厚さ方向に貫通する第2貫通孔52の少なくとも内壁面に設けられていればよい。第2スルーホール導体42は、第2貫通孔52の内壁面のみに設けられていてもよく、第2貫通孔52の内部全体に設けられていてもよい。

**【 0 0 2 7 】**

図1に示すように、第2スルーホール導体42とコンデンサ部10（特に陽極板11）との間には、絶縁性材料22が充填されていることが好ましい。

**【 0 0 2 8 】**

図3に示すように、厚さ方向からの平面視で、陰極層12の内部には、1個の第2スルーホール導体42が設けられていてもよく、2個以上の第2スルーホール導体42が設けられていてもよい。

**【 0 0 2 9 】**

図1～図4には示されていないが、スルーホール導体40は、陽極板11及び陰極層12に電気的に接続されない第3スルーホール導体を含んでもよい。

**【 0 0 3 0 】**

外部電極層30は、第1スルーホール導体41及び陽極板11に電気的に接続される第1外部電極層31と、第2スルーホール導体42及び陰極層12に電気的に接続される第2外部電極層32と、を含む。

**【 0 0 3 1 】**

1個のコンデンサ部10に対して、1個の第1外部電極層31が設けられていてもよく、複数個の第1外部電極層31が設けられていてもよい。同様に、1個のコンデンサ部10に対して、1個の第2外部電極層32が設けられていてもよく、複数個の第2外部電極層32が設けられていてもよい。1個のコンデンサ部10に対して、第1外部電極層31の数は、第2外部電極層32の数と同じであってもよく、異なっていてもよい。

**【 0 0 3 2 】**

厚さ方向から見たときの外部電極層30の平面形状は特に限定されず、例えば、矩形（正方形又は長方形）、矩形以外の四角形、三角形、五角形、六角形等の多角形、円形、橢円形、これらを組み合わせた形状等が挙げられる。また、外部電極層30の平面形状は、L字型、C字型（コの字型）、階段型等であってもよい。

**【 0 0 3 3 】**

厚さ方向から見たときの第1外部電極層31の平面形状は、厚さ方向から見たときの第2外部電極層32の平面形状と同じであってもよく、異なっていてもよい。

**【 0 0 3 4 】**

陰極層12の引き出しは、後述する図5に示す例のように内部ビア導体によって行われてもよいが、図1に示す例では、第2スルーホール導体42が陰極層12に電気的に直接接続されており、陰極層12の引き出しは、第2スルーホール導体42によって行われている。このように、第2スルーホール導体42が陰極層12に電気的に直接接続されることで、内部ビア導体のみで引き出す場合に比べ、放熱の経路、すなわち放熱の面積を増加することができる。また、図1に示す例では、第1外部電極層31の少なくとも一部は、厚さ方向において陰極層12に重なっており、これによっても、放熱の面積が増加する。以上より、コンデンサ素子1の放熱性を向上することができる。また、その結果、コンデンサ素子1の発熱による温度上昇を抑制することができる。

**【 0 0 3 5 】**

また、第2スルーホール導体42が陰極層12に電気的に直接接続されることで、第2スルーホール導体42と陰極層12とが、異種材料である樹脂部を介さずに直に接するた

10

20

30

40

50

め、コンデンサ素子1の剛性を向上することができる。同様に、第1外部電極層31の少なくとも一部が厚さ方向において陰極層12に重なることで、第1外部電極層31の面積を大きくできるため、コンデンサ素子1の剛性を向上することができる。図1に示す例のように陰極層12の引き出しを内部ビア導体によって行わない場合、コンデンサ素子1の薄型化が可能となる一方、コンデンサ素子1の反りが発生する可能性があるが、第1外部電極層31が陰極層12に重なることでコンデンサ素子1の剛性が向上し、そのような反りの発生を抑制することもできる。

#### 【0036】

さらに、第1外部電極層31の少なくとも一部が厚さ方向において陰極層12に重なることで、第1外部電極層31の面積を大きくできるため、外部からコンデンサ部10に水分や酸素等が侵入するのを抑制することができる。10

#### 【0037】

本明細書中、スルーホール導体が、陰極層や陽極板等の導電体層に電気的に直接接続されると、スルーホール導体がビア導体や外部電極層を介して導電体層に電気的に接続された構造（接続経路）だけを備えた場合を除外することを意味する。この場合、スルーホール導体は、貫通孔の内壁面で導電体層に電気的に接続される、すなわち、スルーホール導体の側壁部が導電体層に電気的に接続されることになる。図1に示す例では、第2スルーホール導体42は、第2貫通孔52の内壁面で陰極層12に電気的に接続されている。

#### 【0038】

また、図1に示す例では、第1スルーホール導体41も陽極板11に電気的に直接接続されており、第1スルーホール導体41は、第1貫通孔51の内壁面で陽極板11に電気的に接続されている。20

#### 【0039】

第1外部電極層31は、図1に示すように、一部のみが厚さ方向において陰極層12に重なっていてもよい。第1外部電極層31の全体の面積に対する、厚さ方向において陰極層12に重なっている部分の面積の割合は、特に限定されないが、50%以上、90%以下であることが好ましく、60%以上、80%以下であることがより好ましい。

#### 【0040】

また、図1に示すように、陰極層12は、銅層12Cuを含み、第1外部電極層31は、銅層31Cuを含み、第2外部電極層32は、銅層32Cuを含んでもよい。この場合、陰極層12の銅層12Cuの厚みをd1、第1外部電極層31の銅層31Cuの厚みをd2、第2外部電極層32の銅層32Cuの厚みをd3とすると、d1=d2かつd1=d3を満たすことが好ましい。これにより、陰極層12への電流集中を抑制し、発熱を抑制することができる。また、陰極層12の銅層12Cuの体積を大きくして熱拡散を促進し、コンデンサ部10へのダメージを抑制することができる。30

#### 【0041】

d2に対するd1の比率、すなわちd1/d2は、 $1 < d1/d2 < 3$ を満たすことが好ましく、 $1.5 < d1/d2 < 2.5$ を満たすことがより好ましい。d3に対するd1の比率、すなわちd1/d3は、 $1 < d1/d3 < 3$ を満たすことが好ましく、 $1.5 < d1/d3 < 2.5$ を満たすことがより好ましい。40

#### 【0042】

なお、図1に示す例では、銅層12Cuは、後述する陰極層12の第2導電体層12Cであり、銅層31Cuは、第1外部電極層31であり、銅層32Cuは、第2外部電極層32である。

#### 【0043】

また、陰極層12が銅層12Cuを含む複数の層から構成される場合、銅層12Cuは、陰極層12を構成する複数の層のうち、第1外部電極層31及び第2外部電極層32に最も近い1以上の層であることが好ましい。

#### 【0044】

また、第1外部電極層31が銅層31Cuを含む複数の層から構成される場合、銅層3

10

20

30

40

50

1 Cu は、陰極層 1 2 を構成する複数の層のうち、いずれの層であってもよい。第 2 外部電極層 3 2 についても同様である。

#### 【 0 0 4 5 】

放熱性の観点からは、コンデンサ素子 1 の陽極と陰極の体積を合わせることが好ましい。そこで、陽極板 1 1 の体積と陰極層 1 2 の体積との比較に基づき、第 1 外部電極層 3 1 と第 2 外部電極層 3 2 との好ましい面積比率について説明する。

#### 【 0 0 4 6 】

陽極板 1 1 の芯部 1 1 A の厚みを例えれば 40 μm 以上、60 μm 以下とし、図 2 に示す図 1 の A - A 線に沿った平面内において、陽極板 1 1 の芯部 1 1 A の面積を略 100 % と仮定する。また、陽極板 1 1 の両方の主面側において、各陰極層 1 2 の銅層 1 2 Cu の厚みを例えれば略 30 μm とし、図 3 に示す図 1 の B - B 線に沿った平面内において、銅層 1 2 Cu の面積を略 100 % と仮定する。

10

#### 【 0 0 4 7 】

ここで、銅の熱伝導率は、陽極板 1 1 の材料として好適なアルミニウムの熱伝導率の略 1.7 倍であり、上述のように、陽極板 1 1 の芯部 1 1 A の面積と、芯部 1 1 A の両側の各陰極層 1 2 の銅層 1 2 Cu の面積とは、略同じである。したがって、芯部 1 1 A の両側の陰極層 1 2 の銅層 1 2 Cu の厚みの合計が 60 μm の場合、陽極板 1 1 の芯部 1 1 A に必要な厚みは、 $60 \times 1.7 = 102 \mu m$  となる。そのため、熱伝導性（放熱性）は陰極の方が陽極よりも有利となる。また、後述する第 2 実施形態のように、陰極層 1 2 に内部ビア導体が接続される場合は、熱伝導性（放熱性）は陰極の方がさらに有利となる。

20

#### 【 0 0 4 8 】

以上より、内部の陽極及び陰極の体積のアンバランスを是正し、放熱性をより向上する観点からは、陽極板 1 1 に電気的に接続される第 1 外部電極層 3 1 の面積を S 1 、陰極層 1 2 に電気的に接続される第 2 外部電極層 3 2 の面積を S 2 としたとき、 $S 1 > S 2$  を満たすことが好ましい。また、 $S 1 > S 2$  を満たすことで、コンデンサ素子 1 が搭載される基板のアンジュレーション（うねり）も抑制することができる。

#### 【 0 0 4 9 】

なお、本明細書中、単に「面積」という場合は、厚さ方向からの平面視における面積を意味する。

#### 【 0 0 5 0 】

30

また、図 1 に示すように、コンデンサ部 1 0 の両方の主面側にそれぞれ第 1 外部電極層 3 1 及び第 2 外部電極層 3 2 が設けられる場合は、コンデンサ部 1 0 のそれぞれの主面側において  $S 1 > S 2$  を満たすことがより好ましいが、コンデンサ部 1 0 の少なくとも一方の主面側において  $S 1 > S 2$  を満たしてもよい。

#### 【 0 0 5 1 】

$S 2$  に対する  $S 1$  の比率、すなわち  $S 1 / S 2$  は、 $1 < S 1 / S 2 < 3.5$  を満たすことが好ましく、 $1.5 < S 1 / S 2 < 3$  を満たすことがより好ましい。

#### 【 0 0 5 2 】

なお、 $S 1 > S 2$  や  $S 1 / S 2$  等の比較は、コンデンサ部 1 0 の同一主面側に設けられた第 1 外部電極層 3 1 及び第 2 外部電極層 3 2 の面積に基づき行われる。

40

#### 【 0 0 5 3 】

陰極層 1 2 は、誘電体層 1 3 の表面に設けられた固体電解質層 1 2 A と、固体電解質層 1 2 A の表面上に設けられた第 1 導電体層 1 2 B と、第 2 スルーホール導体 4 2 に電気的に直接接続されるように第 1 導電体層 1 2 B の表面上に設けられた第 2 導電体層 1 2 C と、を含むことが好ましい。これにより、第 2 スルーホール導体 4 2 を、陰極層 1 2 に容易に電気的に直接接続することができる。

#### 【 0 0 5 4 】

また、図 1 に示す例では、陽極板 1 1 の芯部 1 1 A の両方の主面側に、同様の要素（部材）が配置されている。これよっても、コンデンサ素子 1 の反りの発生を抑制することができる。また、コンデンサ部 1 0 の静電容量を向上することができる。

50

**【 0 0 5 5 】**

また、コンデンサ素子 1 に設けられる第 1 スルーホール導体 4 1 及び第 2 スルーホール導体 4 2 の面積が同じであることが好ましく、コンデンサ素子 1 に設けられる第 1 スルーホール導体 4 1 及び第 2 スルーホール導体 4 2 の個数が同じであることがより好ましい。これにより、コンデンサ素子 1 の放熱性を均一化することができる。

**【 0 0 5 6 】**

また、コンデンサ素子 1 に設けられるスルーホール導体 4 0 ( すなわち、第 1 スルーホール導体 4 1 及び第 2 スルーホール導体 4 2 を互いに区別しない。 ) は、等ピッチで配置されることが好ましい。これによっても、コンデンサ素子 1 の放熱性を均一化することができる。また、デラミネーションと呼ばれる剥離、例えば、陽極板からの陰極層の剥離等の発生を抑制することが可能である。

10

**【 0 0 5 7 】**

コンデンサ部 1 0 は、陽極板 1 1 の少なくとも一方の主面において、スルーホール導体 4 0 の周囲に設けられた絶縁マスク層 2 5 をさらに含むことが好ましい。

**【 0 0 5 8 】**

図 1 に示す例では、第 1 スルーホール導体 4 1 と陰極層 1 2 との間に絶縁マスク層 2 5 が設けられている。また、図 1 に示す例では、第 2 スルーホール導体 4 2 とコンデンサ部 1 0 ( 特に陽極板 1 1 ) との間に絶縁性材料 2 2 が充填されており、この絶縁性材料 2 2 と陰極層 1 2 ( 例えば固体電解質層 1 2 A ) との間に絶縁マスク層 2 5 が設けられている。

20

**【 0 0 5 9 】**

コンデンサ部 1 0 は、陽極板 1 1 の少なくとも一方の主面において、陰極層 1 2 ( 例えば固体電解質層 1 2 A ) の周囲を囲むように設けられた絶縁マスク層 2 5 をさらに含んでもよい。陰極層 1 2 の周囲を絶縁マスク層 2 5 で囲むことによって、陽極板 1 1 と陰極層 1 2 との間の絶縁性が確保され、両者間の短絡が防止される。絶縁マスク層 2 5 は、陰極層 1 2 の周囲の一部を囲むように設けられていてもよいが、陰極層 1 2 の周囲の全体を囲むように設けられていることが好ましい。

**【 0 0 6 0 】**

図 5 は、本発明の第 1 実施形態に係るコンデンサ素子の別の一例を模式的に示す断面図である。

30

**【 0 0 6 1 】**

図 5 に示すコンデンサ素子 2 は、封止層 2 0 を厚さ方向に貫通するように設けられ、一方の端部が第 2 外部電極層 3 2 に電気的に接続され、他方の端部が陰極層 1 2 に電気的に接続された内部ビア導体 6 0 をさらに備える。このような内部ビア導体 6 0 を設けることによって、放熱性をより向上することができる。また、層間の密着性を向上し、デラミネーションの発生を抑制することが可能である。

30

**【 0 0 6 2 】**

図 5 に示す例では、内部ビア導体 6 0 の一方の端部が封止層 2 0 の表面に引き出されている。

**【 0 0 6 3 】**

また、内部ビア導体 6 0 は、陰極層 1 2 に電気的に接続されている。これにより、陰極層 1 2 が、内部ビア導体 6 0 及び第 2 スルーホール導体 4 2 を介して封止層 2 0 の外部に電気的に導出され、封止層 2 0 の外部に電気的に接続可能となる。陰極層 1 2 に電気的に接続される内部ビア導体 6 0 は、1 個でもよく、2 個以上でもよい。

40

**【 0 0 6 4 】**

図 5 には示されていないが、コンデンサ素子 2 には、陽極板 1 1 に電気的に接続される内部ビア導体 6 0 が含まれていてもよい。この場合、陽極板 1 1 が、内部ビア導体 6 0 を介して封止層 2 0 の外部に電気的に導出され、封止層 2 0 の外部に電気的に接続可能となる。陽極板 1 1 に電気的に接続される内部ビア導体 6 0 は、1 個でもよく、2 個以上でもよい。

**【 0 0 6 5 】**

50

以下では、コンデンサ素子 1、2 等の詳細な構成について説明する。

#### 【0066】

厚さ方向から見たときのコンデンサ部 10 の平面形状としては、例えば、矩形（正方形又は長方形）、矩形以外の四角形、三角形、五角形、六角形等の多角形、円形、橢円形、これらを組み合わせた形状等が挙げられる。また、コンデンサ部 10 の平面形状は、L 字型、C 字型（コの字型）、階段型等であってもよい。

#### 【0067】

陽極板 11 は、いわゆる弁作用を示す弁作用金属からなることが好ましい。弁作用金属としては、例えば、アルミニウム、タンタル、ニオブ、チタン、ジルコニウム等の金属単体、又は、これらの金属を少なくとも 1 種含む合金等が挙げられる。これらの中では、アルミニウム又はアルミニウム合金が好ましい。10

#### 【0068】

陽極板 11 の形状は、平板状であることが好ましく、箔状であることがより好ましい。このように、本明細書中では、「板状」に「箔状」も含まれる。

#### 【0069】

陽極板 11 は、芯部 11A の少なくとも一方の主面に多孔質部 11B を有していればよい。つまり、陽極板 11 は、後述する第 2 実施形態のように芯部 11A の一方の主面のみに多孔質部 11B を有していてもよいし、芯部 11A の両方の主面に多孔質部 11B を有していてもよい。多孔質部 11B は、芯部 11A の表面に形成された多孔質層であることが好ましく、エッティング層であることがより好ましい。20

#### 【0070】

エッティング処理前の陽極板 11 の厚さは、60 μm 以上、200 μm 以下であることが好ましい。エッティング処理後にエッティングされていない芯部 11A の厚さは、15 μm 以上、70 μm 以下であることが好ましい。多孔質部 11B の厚さは要求される耐電圧、静電容量に合わせて設計されるが、芯部 11A の両側の多孔質部 11B を合わせて 10 μm 以上、180 μm 以下であることが好ましい。

#### 【0071】

多孔質部 11B の孔径は、10 nm 以上、600 nm 以下であることが好ましい。なお、多孔質部 11B の孔径とは、水銀ポロシメータにより測定されるメジアン径 D<sub>50</sub> を意味する。多孔質部 11B の孔径は、例えばエッティングにおける各種条件を調整することにより制御することができる。30

#### 【0072】

多孔質部 11B の表面に設けられる誘電体層 13 は、多孔質部 11B の表面状態を反映して多孔質になっており、微細な凹凸状の表面形状を有している。誘電体層 13 は、上記弁作用金属の酸化皮膜からなることが好ましい。例えば、陽極板 11 としてアルミニウム箔が用いられる場合、アジピン酸アンモニウム等を含む水溶液中でアルミニウム箔の表面に対して陽極酸化処理（化成処理ともいう）を行うことにより、酸化皮膜からなる誘電体層 13 を形成することができる。

#### 【0073】

誘電体層 13 の厚さは要求される耐電圧、静電容量に合わせて設計されるが、10 nm 以上、100 nm 以下であることが好ましい。40

#### 【0074】

陰極層 12 が固体電解質層 12A を含む場合、固体電解質層 12A を構成する材料としては、例えば、ポリピロール類、ポリチオフェン類、ポリアニリン類等の導電性高分子等が挙げられる。これらの中では、ポリチオフェン類が好ましく、PEDOT と呼ばれるポリ(3,4-エチレンジオキシチオフェン)が特に好ましい。また、上記導電性高分子は、ポリスチレンスルホン酸(PSS)等のドーパントを含んでいてもよい。なお、固体電解質層 12A は、誘電体層 13 の細孔（凹部）を充填する内層と、誘電体層 13 を被覆する外層とを含むことが好ましい。

#### 【0075】

10

20

30

40

50

多孔質部 11B の表面からの固体電解質層 12A の厚さは、2 μm 以上、20 μm 以下であることが好ましい。

【0076】

固体電解質層 12A は、例えば、3,4-エチレンジオキシチオフェン等のモノマーを含む処理液を用いて、誘電体層 13 の表面にポリ(3,4-エチレンジオキシチオフェン)等の重合膜を形成する方法や、ポリ(3,4-エチレンジオキシチオフェン)等のポリマーの分散液を誘電体層 13 の表面に塗布して乾燥させる方法等によって形成される。

【0077】

固体電解質層 12A は、上記の処理液又は分散液を、スponジ転写、スクリーン印刷、ディスペンサ塗布、インクジェット印刷等の方法によって誘電体層 13 の表面に塗布することにより、所定の領域に形成することができる。

10

【0078】

陰極層 12 が第 1 導電体層 12B 及び第 2 導電体層 12C を含む場合、第 1 導電体層 12B 及び第 2 導電体層 12C は、それぞれ、導電性樹脂層及び金属層のうち、少なくとも 1 層を含む。第 1 導電体層 12B 及び第 2 導電体層 12C は、それぞれ、導電性樹脂層のみでもよく、金属層のみでもよいが、第 1 導電体層 12B は、導電性樹脂層のみから構成されることが好ましく、第 2 導電体層 12C は、金属層のみから構成されることが好ましい。第 1 導電体層 12B は、固体電解質層 12A の全面を被覆することが好ましい。

【0079】

導電性樹脂層としては、例えば、銀フィラー、銅フィラー、ニッケルフィラー及びカーボンフィラーからなる群より選択される少なくとも 1 種の導電性フィラーを含む導電性接着剤層(導電性ペースト層)等が挙げられる。

20

【0080】

金属層としては、例えば、金属めっき層、金属箔層等が挙げられる。金属層は、ニッケル、銅、銀及びこれらの金属を主成分とする合金からなる群より選択される少なくとも一種の金属からなることが好ましい。なお、「主成分」とは、重量割合が最も大きい元素成分をいう。

【0081】

第 1 導電体層 12B は、例えば、固体電解質層 12A の表面に設けられたカーボンペースト層と、カーボンペースト層の表面に設けられた銅ペースト層と、を含む。

30

【0082】

第 2 導電体層 12C は、例えば、銅めっき層、銅箔層等の銅層 12Cu から構成される。

【0083】

なお、第 1 導電体層 12B が銅ペースト層を含む場合は、上述の陰極層 12 の銅層 12Cu の厚み d1 は、第 2 導電体層 12C の銅層 12Cu と、第 1 導電体層 12B の銅ペースト層とを合わせた厚みとする。

【0084】

第 1 導電体層 12B のカーボンペースト層は、固体電解質層 12A と第 1 導電体層 12B の銅ペースト層とを電気的に及び機械的に接続させるために設けられている。カーボンペースト層は、カーボンペーストをスponジ転写、スクリーン印刷、ディスペンサ塗布、インクジェット印刷等の方法によって固体電解質層 12A の表面に塗布することにより、所定の領域に形成することができる。なお、カーボンペースト層は、乾燥前の粘性のある状態で、次工程の銅ペースト層を積層することが好ましい。カーボンペースト層の厚さは、2 μm 以上、50 μm 以下であることが好ましい。

40

【0085】

第 1 導電体層 12B の銅ペースト層は、銅ペーストをスponジ転写、スクリーン印刷、スプレー塗布、ディスペンサ塗布、インクジェット印刷等の方法によってカーボンペースト層の表面に塗布することにより、所定の領域に形成することができる。銅ペースト層の厚さは、2 μm 以上、50 μm 以下であることが好ましい。

【0086】

50

第2導電体層12Cの銅めっき層は、電解めっき、無電解めっき、スパッタ、真空蒸着等で成膜後、エッチング(ドライ又はウェット)でパターニングすることにより、所定の領域に形成することができる。銅めっき層の厚さは、2μm以上、35μm以下であることが好ましい。

#### 【0087】

第2導電体層12Cの銅箔層は、先にエッチング(ドライ、ウェット)でパターニングした銅箔をプレス機で積層、又は銅箔をプレス機で積層した後にエッチング(ドライ又はウェット)でパターニングすることにより、所定の領域に形成することができる。銅箔層の厚さは、3μm以上、35μm以下であることが好ましい。

#### 【0088】

封止層20は、絶縁性材料から構成される。この場合、封止層20は、絶縁性樹脂から構成されることが好ましい。

#### 【0089】

封止層20を構成する絶縁性樹脂としては、例えば、エポキシ樹脂、フェノール樹脂等が挙げられる。

#### 【0090】

封止層20は、フィラーをさらに含むことが好ましい。

#### 【0091】

封止層20に含まれるフィラーとしては、例えば、シリカ粒子、アルミナ粒子等の無機フィラーが挙げられる。

#### 【0092】

コンデンサ部10と封止層20との間には、例えば、応力緩和層、防湿膜等の層が設けられていてもよい。

#### 【0093】

絶縁マスク層25は、絶縁性材料から構成される。この場合、絶縁マスク層25は、絶縁性樹脂から構成されることが好ましい。

#### 【0094】

絶縁マスク層25を構成する絶縁性樹脂としては、例えば、ポリフェニルスルホン樹脂、ポリエーテルスルホン樹脂、シアノ酸エステル樹脂、フッ素樹脂(テトラフルオロエチレン、テトラフルオロエチレン・パーカルオロアルキルビニルエーテル共重合体等)、ポリイミド樹脂、ポリアミドイミド樹脂、エポキシ樹脂、及び、それらの誘導体又は前駆体等が挙げられる。

#### 【0095】

絶縁マスク層25は、封止層20と同じ樹脂で構成されていてもよい。封止層20と異なり、絶縁マスク層25に無機フィラーが含有されるとコンデンサ部10の容量有効部に悪影響を及ぼすおそれがあるため、絶縁マスク層25は樹脂単独の系からなることが好ましい。

#### 【0096】

絶縁マスク層25は、例えば、絶縁性樹脂を含む組成物等のマスク材を、スポンジ転写、スクリーン印刷、ディスペンサ塗布、インクジェット印刷等の方法によって多孔質部11Bの表面に塗布することにより、所定の領域に形成することができる。

#### 【0097】

絶縁マスク層25は、多孔質部11Bに対して、誘電体層13よりも前のタイミングで形成されてもよいし、誘電体層13よりも後のタイミングで形成されてもよい。

#### 【0098】

第1外部電極層31は、陽極板11と電気的に接続されている。図1に示す例において、第1外部電極層31は、第1スルーホール導体41の表面に設けられており、コンデンサ部10の接続端子として機能する。図1に示す例において、第1外部電極層31は、第1スルーホール導体41を介して陽極板11に電気的に接続されており、陽極板11用の接続端子として機能する。

10

20

30

40

50

## 【0099】

第1外部電極層31の構成材料としては、例えば、銀、金、銅等の低抵抗の金属を含有する金属材料等が挙げられる。この場合、第1外部電極層31は、例えば、第1スルーホール導体41の表面にめっき処理を行うことにより形成される。

## 【0100】

第1外部電極層31と他の部材との間の密着性、ここでは、第1外部電極層31と第1スルーホール導体41との間の密着性を向上させるために、第1外部電極層31の構成材料として、銀フィラー、銅フィラー、ニッケルフィラー、及び、カーボンフィラーからなる群より選択される少なくとも1種の導電性フィラーと樹脂との混合材料（導電性ペースト材料）が用いられてもよい。

10

## 【0101】

第1外部電極層31は、銅ペースト層、銅めっき層、銅箔層等の銅層31Cuを含んでもよい。第1外部電極層31の銅ペースト層、銅めっき層及び銅箔層は、第1導電体層12Bの銅ペースト層、第2導電体層12Cの銅めっき層及び銅箔層と同様にして形成することができる。

## 【0102】

第2外部電極層32は、陰極層12と電気的に接続されている。図1に示す例において、第2外部電極層32は、第2スルーホール導体42の表面に設けられており、コンデンサ部10の接続端子として機能する。図1に示す例において、第2外部電極層32は、第2スルーホール導体42を介して陰極層12に電気的に接続されており、陰極層12用の接続端子として機能する。

20

## 【0103】

第2外部電極層32の構成材料としては、例えば、銀、金、銅等の低抵抗の金属を含有する金属材料等が挙げられる。この場合、第2外部電極層32は、例えば、第2スルーホール導体42の表面にめっき処理を行うことにより形成される。

## 【0104】

第2外部電極層32と他の部材との間の密着性、ここでは、第2外部電極層32と第2スルーホール導体42との間の密着性を向上させるために、第2外部電極層32の構成材料として、銀フィラー、銅フィラー、ニッケルフィラー、及び、カーボンフィラーからなる群より選択される少なくとも1種の導電性フィラーと樹脂との混合材料（導電性ペースト材料）が用いられてもよい。

30

## 【0105】

第2外部電極層32は、銅ペースト層、銅めっき層、銅箔層等の銅層32Cuを含んでもよい。第2外部電極層32の銅ペースト層、銅めっき層及び銅箔層は、第1導電体層12Bの銅ペースト層、第2導電体層12Cの銅めっき層及び銅箔層と同様にして形成することができる。

## 【0106】

第1外部電極層31及び第2外部電極層32の構成材料は、少なくとも種類の点で、互いに同じであることが好ましいが、互いに異なっていてもよい。

## 【0107】

複数のコンデンサ部10が配置される場合、複数のコンデンサ部10の各々において、陽極板11に電気的に接続された第1外部電極層31と、陰極層12に電気的に接続された第2外部電極層32とが設けられてもよいし、複数のコンデンサ部10で第1外部電極層31及び第2外部電極層32の少なくとも一方が共通するように設けられていてもよい。

40

## 【0108】

図1に示す例では、第1外部電極層31及び第2外部電極層32が、封止層20の両方の主面に設けられているが、封止層20の一方の主面のみに設けられていてもよい。

## 【0109】

第1スルーホール導体41は、第1貫通孔51の内壁面で陽極板11に電気的に接続されている。より具体的には、第1スルーホール導体41は、面方向において第1貫通孔5

50

1の内壁面に対向する陽極板11の端面に電気的に接続されていることが好ましい。これにより、陽極板11は、第1スルーホール導体41を介して外部に電気的に導出される。

#### 【0110】

第1スルーホール導体41に電気的に接続される陽極板11の端面には、芯部11A及び多孔質部11Bが露出していることが好ましい。この場合、芯部11Aに加えて多孔質部11Bでも、第1スルーホール導体41との電気的な接続がなされる。

#### 【0111】

図2に示すように、厚さ方向から見たとき、第1スルーホール導体41は、第1貫通孔51の全周にわたって陽極板11に電気的に接続されていることが好ましい。この場合、放熱の経路が増加するため、コンデンサ素子1の放熱性をより向上することができる。また、陽極板11と第1スルーホール導体41との接続抵抗が低下しやすくなるため、等価直列抵抗(ESR)が低下しやすくなる。

10

#### 【0112】

第1スルーホール導体41は、例えば、以下のようにして形成される。まず、ドリル加工、レーザー加工等を行うことにより、コンデンサ部10及び封止層20を厚さ方向に貫通する第1貫通孔51を形成する。そして、第1貫通孔51の内壁面を、銅、金、銀等の低抵抗の金属を含有する金属材料でメタライズすることにより、第1スルーホール導体41を形成する。第1スルーホール導体41を形成する際、例えば、第1貫通孔51の内壁面を、無電解銅めっき処理、電解銅めっき処理等でメタライズすることにより、加工が容易になる。なお、第1スルーホール導体41を形成する方法については、第1貫通孔51の内壁面をメタライズする方法以外に、金属材料、金属と樹脂との複合材料等を第1貫通孔51に充填する方法であってもよい。

20

#### 【0113】

面方向において陽極板11と第1スルーホール導体41との間には、陽極接続層が設けられてもよい。すなわち、陽極板11と第1スルーホール導体41とは、陽極接続層を介して電気的に接続されていてもよい。

#### 【0114】

陽極接続層が面方向において陽極板11と第1スルーホール導体41との間に設けられていることにより、陽極接続層が、陽極板11に対するバリア層、より具体的には、芯部11A及び多孔質部11Bに対するバリア層として機能する。陽極接続層が陽極板11に対するバリア層として機能すると、外部電極層30(例えば第1外部電極層31)を形成するための薬液処理時に生じる陽極板11の溶解が抑制され、ひいては、コンデンサ部10への薬液の浸入が抑制されるため、信頼性が向上しやすくなる。

30

#### 【0115】

陽極接続層は、ニッケルを主成分とする層を含むことが好ましい。この場合、陽極板11を構成する金属(例えば、アルミニウム)等へのダメージが低減されるため、陽極板11に対する陽極接続層のバリア性が向上しやすくなる。

#### 【0116】

なお、面方向において、陽極板11と第1スルーホール導体41との間には、陽極接続層が設けられていないなくてもよい。この場合、第1スルーホール導体41は、陽極板11の端面に直に接続されていてもよい。

40

#### 【0117】

図1に示す例では、第1スルーホール導体41が第1貫通孔51の内壁面のみに設けられている。この場合、第1貫通孔51には、樹脂材料が充填されてなる樹脂充填部91が設けられてもよい。樹脂充填部91は、第1貫通孔51内の第1スルーホール導体41で囲まれた空間に設けられる。樹脂充填部91が設けられることで第1貫通孔51内の空間が解消されると、第1スルーホール導体41のデラミネーションの発生が抑制される。なお、樹脂充填部91は、導体であってもよし、絶縁体であってもよい。

#### 【0118】

図1に示す例において、第2スルーホール導体42は、第2貫通孔52の内壁面で陰極

50

層 1 2 、なかでも第 2 導電体層 1 2 C に電気的に接続されている。より具体的には、第 2 スルーホール導体 4 2 は、面方向において第 2 貫通孔 5 2 の内壁面に対向する第 2 導電体層 1 2 C の端面に電気的に接続されていることが好ましい。これにより、陰極層 1 2 は、第 2 スルーホール導体 4 2 を介して外部に電気的に導出される。

#### 【 0 1 1 9 】

図 3 に示すように、厚さ方向から見たとき、第 2 スルーホール導体 4 2 は、第 2 貫通孔 5 2 の全周にわたって陰極層 1 2 、なかでも第 2 導電体層 1 2 C に電気的に接続されていることが好ましい。この場合、放熱の経路が増加するため、コンデンサ素子 1 の放熱性をより向上することができる。また、陰極層 1 2 と第 2 スルーホール導体 4 2 との接続抵抗が低下しやすくなるため、等価直列抵抗 ( E S R ) が低下しやすくなる。

10

#### 【 0 1 2 0 】

第 2 スルーホール導体 4 2 は、例えば、以下のようにして形成される。まず、ドリル加工、レーザー加工等を行うことにより、コンデンサ部 1 0 を厚さ方向に貫通する貫通孔 5 3 を形成する。次に、上述した貫通孔 5 3 に絶縁性材料 2 2 を充填する。絶縁性材料 2 2 が充填された部分に対して、ドリル加工、レーザー加工等を行うことにより、第 2 貫通孔 5 2 を形成する。この際、絶縁性材料 2 2 を充填した貫通孔 5 3 の直径よりも第 2 貫通孔 5 2 の直径を小さくすることにより、面方向において、先に形成された貫通孔 5 3 の内壁面と第 2 貫通孔 5 2 の内壁面との間に絶縁性材料 2 2 が存在する状態にする。その後、第 2 貫通孔 5 2 の内壁面を、銅、金、銀等の低抵抗の金属を含有する金属材料でメタライズすることにより、第 2 スルーホール導体 4 2 を形成する。第 2 スルーホール導体 4 2 を形成する際、例えば、第 2 貫通孔 5 2 の内壁面を、無電解銅めっき処理、電解銅めっき処理等でメタライズすることにより、加工が容易になる。なお、第 2 スルーホール導体 4 2 を形成する方法については、第 2 貫通孔 5 2 の内壁面をメタライズする方法以外に、金属材料、金属と樹脂との複合材料等を第 2 貫通孔 5 2 に充填する方法であってもよい。

20

#### 【 0 1 2 1 】

絶縁性材料 2 2 は、絶縁性樹脂から構成されることが好ましい。絶縁性材料 2 2 を構成する絶縁性樹脂としては、例えば、エポキシ樹脂、フェノール樹脂等が挙げられる。さらに、絶縁性材料 2 2 は、フィラーを含むことが好ましい。絶縁性材料 2 2 に含まれるフィラーとしては、例えば、シリカ粒子、アルミナ粒子、金属粒子等の無機フィラーが挙げられる。

30

#### 【 0 1 2 2 】

絶縁性材料 2 2 は、封止層 2 0 と同じ材料から構成されてもよい。

#### 【 0 1 2 3 】

面方向において、陰極層 1 2 、なかでも第 2 導電体層 1 2 C と第 2 スルーホール導体 4 2 との間には、陽極接続層のような陰極接続層が設けられていてもよいが、設けられていないことが好ましい。後者の場合、第 2 スルーホール導体 4 2 は、第 2 導電体層 1 2 C の端面に直に接続されていてもよい。

#### 【 0 1 2 4 】

図 1 に示す例では、第 2 スルーホール導体 4 2 が第 2 貫通孔 5 2 の内壁面のみに設けられている。この場合、第 2 貫通孔 5 2 には、樹脂材料が充填されてなる樹脂充填部 9 2 が設けられてもよい。樹脂充填部 9 2 は、第 2 貫通孔 5 2 内の第 2 スルーホール導体 4 2 で囲まれた空間に設けられる。樹脂充填部 9 2 が設けられることで第 2 貫通孔 5 2 内の空間が解消されると、第 2 スルーホール導体 4 2 のデラミネーションの発生が抑制される。なお、樹脂充填部 9 2 は、導体であってもよし、絶縁体であってもよい。

40

#### 【 0 1 2 5 】

内部ピア導体 6 0 の構成材料としては、例えば、銀、金、銅等の低抵抗の金属を含有する金属材料等が挙げられる。

#### 【 0 1 2 6 】

内部ピア導体 6 0 は、例えば、封止層 2 0 を厚さ方向に貫通する貫通孔に対して、上述した金属材料で内壁面にめっき処理を行ったり、導電性ペーストを充填した後に熱処理を

50

行ったりすることにより形成される。

**【0127】**

図6-1～図6-12は、図1に示すコンデンサ素子の製造方法の一例を説明する断面模式図である。図6-1は、陽極板を準備する工程を示す。図6-2は、誘電体層を形成する工程を示す。図6-3は、絶縁マスク層を形成する工程を示す。図6-4は、固体電解質層を形成する工程を示す。図6-5は、第1導電体層を形成する工程を示す。図6-6は、貫通孔を形成する工程を示す。図6-7は、絶縁性材料を形成する工程を示す。図6-8は、絶縁性材料を研磨する工程を示す。図6-9は、第2導電体層を形成する工程を示す。図6-10は、封止層を形成する工程を示す。図6-11は、第1貫通孔及び第2貫通孔を形成する工程を示す。図6-12は、スルーホール導体及び外部電極層を形成する工程を示す。

10

**【0128】**

図1に示すコンデンサ素子1は、例えば、以下のようにして形成される。

**【0129】**

まず、図6-1に示すように、芯部11Aの両方の主面に多孔質部11Bを有する陽極板11を準備する。

**【0130】**

次に、図6-2に示すように、多孔質部11B上に誘電体層13を形成する。

**【0131】**

次に、図6-3に示すように、誘電体層13上に絶縁マスク層25を形成する。

20

**【0132】**

次に、図6-4に示すように、絶縁マスク層25で囲まれた領域において、誘電体層13上に固体電解質層12Aを形成する。

**【0133】**

次に、図6-5に示すように、固体電解質層12A上に第1導電体層12Bを形成する。

**【0134】**

次に、図6-6に示すように、絶縁マスク層25、誘電体層13及び陽極板11を貫通する貫通孔53を形成する。

**【0135】**

次に、図6-7に示すように、絶縁マスク層25及び第1導電体層12Bを覆うように絶縁性材料22をラミネートし、貫通孔53に絶縁性材料22を充填する。

30

**【0136】**

次に、図6-8に示すように、第1導電体層12Bが露出するまで絶縁性材料22を研磨して薄くする。

**【0137】**

次に、図6-9に示すように、第1導電体層12B及び絶縁性材料22上に第2導電体層12Cを形成する。

**【0138】**

次に、図6-10に示すように、第2導電体層12C及び絶縁性材料22を覆うように封止層20を形成する。

40

**【0139】**

次に、図6-11に示すように、封止層20、絶縁性材料22、絶縁マスク層25、誘電体層13及び陽極板11を貫通する第1貫通孔51と、封止層20、第2導電体層12C及び絶縁性材料22を貫通する第2貫通孔52と、を形成する。第2貫通孔52は、貫通孔53が形成されていた領域の内側に位置する。

**【0140】**

そして、図6-12に示すように、第1貫通孔51内に第1スルーホール導体41を形成し、第2貫通孔52内に第2スルーホール導体42を形成する。第1スルーホール導体41及び第2スルーホール導体42内には、それぞれ、樹脂充填部91及び92を形成してもよい。最後に、第1スルーホール導体41を覆うように封止層20上に第1外部電極

50

層31を形成し、第2スルーホール導体42を覆うように封止層20上に第2外部電極層32を形成する。

#### 【0141】

図7-1～図7-6は、図1に示すコンデンサ素子の製造方法の別の一例を説明する断面模式図である。図7-1は、貫通孔を形成した後の状態を示す。図7-2は、絶縁性材料を形成する工程を示す。図7-3は、第2導電体層を形成する工程を示す。図7-4は、封止層を形成する工程を示す。図7-5は、第1貫通孔及び第2貫通孔を形成する工程を示す。図7-6は、スルーホール導体及び外部電極層を形成する工程を示す。

#### 【0142】

図1に示すコンデンサ素子1は、例えば、以下のようにして形成されてもよい。

10

#### 【0143】

まず、図7-1に示すように、図6-1～図6-6に示した場合と同様にして、絶縁マスク層25、誘電体層13及び陽極板11を貫通する貫通孔53を形成する。

#### 【0144】

次に、図7-2に示すように、樹脂材料を充填する方法、スクリーン印刷、ディスペンサ塗布、インクジェット印刷等により貫通孔53内のみに絶縁性材料22を形成する。

#### 【0145】

その後、図7-3～図7-6に示すように、図6-9～図6-12に示した場合と同様にして、第2導電体層12C、封止層20、第1貫通孔51、第2貫通孔52、第1スルーホール導体41、第2スルーホール導体42、第1外部電極層31及び第2外部電極層32を形成する。なお、必要に応じて樹脂充填部91及び92を形成してもよい。

20

#### 【0146】

#### [第2実施形態]

図8は、本発明の第2実施形態に係るコンデンサ素子の一例を模式的に示す平面図である。

#### 【0147】

図8に示すコンデンサ素子3は、陽極板11が芯部11Aの一方の主面のみに多孔質部11Bを有し、コンデンサ素子3の片面のみに、コンデンサ部10（陽極板11、誘電体層13及び陰極層12）、封止層20、外部電極層30（第1外部電極層31及び第2外部電極層32）等の各部材が設けられている。

30

#### 【0148】

図8に示す例では、スルーホール導体40（第1スルーホール導体41及び第2スルーホール導体42）は、一方の端部が外部電極層30に電気的に接続されるが、他方の端部はコンデンサ部10等が設けられていない方の面に露出している。

#### 【0149】

図9-1～図9-12は、図8に示すコンデンサ素子の製造方法の一例を説明する断面模式図である。図9-1は、陽極板を準備する工程を示す。図9-2は、誘電体層を形成する工程を示す。図9-3は、絶縁マスク層を形成する工程を示す。図9-4は、固体電解質層を形成する工程を示す。図9-5は、第1導電体層を形成する工程を示す。図9-6は、貫通孔を形成する工程を示す。図9-7は、絶縁性材料を形成する工程を示す。図9-8は、絶縁性材料を研磨する工程を示す。図9-9は、第2導電体層を形成する工程を示す。図9-10は、封止層を形成する工程を示す。図9-11は、第1貫通孔及び第2貫通孔を形成する工程を示す。図9-12は、スルーホール導体及び外部電極層を形成する工程を示す。

40

#### 【0150】

図8に示すコンデンサ素子3は、例えば、以下のようにして形成されてもよい。

#### 【0151】

まず、図9-1に示すように、芯部11Aの一方の主面のみに多孔質部11Bを有する陽極板11を準備する。

#### 【0152】

50

次に、図9-2～図9-5に示すように、図6-2～図6-5に示した場合と同様にして、誘電体層13、絶縁マスク層25、固体電解質層12A及び第1導電体層12Bを形成する。

#### 【0153】

次に、図9-6に示すように、図6-6に示した場合と同様にして貫通孔53が形成されたコンデンサ素子シートをキャリアボードCB上に載置する。

#### 【0154】

その後、図9-7～図9-12に示すように、図6-7～図6-12に示した場合と同様にして、絶縁性材料22をラミネートしてから研磨した後、第2導電体層12C、封止層20、第1貫通孔51、第2貫通孔52、第1スルーホール導体41、第2スルーホール導体42、第1外部電極層31及び第2外部電極層32を形成する。なお、必要に応じて樹脂充填部91及び92を形成してもよい。10

#### 【0155】

#### [その他の実施形態]

本発明のコンデンサ素子は、上記実施形態に限定されるものではなく、コンデンサ素子の構成、製造条件等に関し、本発明の範囲内において、種々の応用、変形を加えることが可能である。

#### 【0156】

本発明のコンデンサ素子では、封止層の内部に、1個のコンデンサ部が配置されていてもよく、複数個のコンデンサ部が配置されていてもよい。20

#### 【0157】

本発明のコンデンサ素子において、封止層の内部に複数個のコンデンサ部が配置されている場合、隣り合うコンデンサ部同士は、物理的に分断されていればよい。したがって、隣り合うコンデンサ部同士は、電気的に分断されてもよく、電気的に接続されてもよい。隣り合うコンデンサ部同士が分断された部分には、封止層等の絶縁性材料が充填されていることが好ましい。隣り合うコンデンサ部同士の間隔は、厚さ方向に一定でもよく、厚さ方向に小さくなってもよい。

#### 【0158】

本発明のコンデンサ素子において、封止層の内部に複数個のコンデンサ部が配置されている場合、複数個のコンデンサ部は、面方向に並ぶように配置されていてもよく、厚さ方向に積層するように配置されていてもよく、両者を組み合わせて配置されていてもよい。複数個のコンデンサ部は、規則的に配置されていてもよく、不規則に配置されていてもよい。コンデンサ素子の大きさ及び形状等は、それぞれ同じでもよく、一部又は全部が異なってもよい。コンデンサ素子の構成は、それぞれ同じであることが好ましいが、構成の異なるコンデンサ素子が含まれていてもよい。30

#### 【0159】

本発明のコンデンサ素子は、複合電子部品の構成材料として好適に使用することができる。このような複合電子部品は、例えば、本発明のコンデンサ素子と、上記コンデンサ素子の封止層の表面に設けられ、上記コンデンサ素子の陽極板及び陰極層のそれぞれに電気的に接続された外部電極層と、上記外部電極層に接続された電子部品と、を備える。

#### 【0160】

複合電子部品において、外部電極層に接続される電子部品は、受動素子でもよく、能動素子でもよい。受動素子及び能動素子の両方が外部電極層に接続されてもよく、受動素子及び能動素子のいずれか一方が外部電極層に接続されてもよい。また、受動素子及び能動素子の複合体が外部電極層に接続されてもよい。

#### 【0161】

受動素子としては、例えば、インダクタ等が挙げられる。能動素子としては、メモリ、GPU(Graphical Processing Unit)、CPU(Central Processing Unit)、MPU(Micro Processing Unit)、PMIC(Power Management IC)等が挙げられる。40

**【 0 1 6 2 】**

本発明のコンデンサ素子は、全体としてシート状の形状を有している。したがって、複合電子部品においては、コンデンサ素子を実装基板のように扱うことができ、コンデンサ素子上に電子部品を実装することができる。さらに、コンデンサ素子に実装する電子部品の形状をシート状にすることにより、各電子部品を厚さ方向に貫通するスルーホール導体を介して、コンデンサ素子と電子部品とを厚さ方向に接続することも可能である。その結果、能動素子及び受動素子を一括のモジュールのように構成することができる。

**【 0 1 6 3 】**

例えば、半導体アクティブ素子を含むボルテージレギュレータと、変換された直流電圧が供給される負荷との間に本発明のコンデンサ素子を電気的に接続し、スイッチングレギュレータを形成することができる。10

**【 0 1 6 4 】**

複合電子部品においては、本発明のコンデンサ素子がさらに複数個レイアウトされたコンデンサマトリクスシートのいずれかの一方の面に回路層を形成した上で、受動素子又は能動素子に接続されていてもよい。

**【 0 1 6 5 】**

また、予め基板に設けたキャビティ部に本発明のコンデンサ素子を配置し、樹脂で埋め込んだ後、その樹脂上に回路層を形成してもよい。同基板の別のキャビティ部には、別の電子部品（受動素子又は能動素子）が搭載されていてもよい。20

**【 0 1 6 6 】**

あるいは、本発明のコンデンサ素子をウエハ又はガラス等の平滑なキャリアの上に実装し、樹脂による外層部を形成した後、回路層を形成した上で、受動素子又は能動素子に接続されていてもよい。

**【 0 1 6 7 】**

本明細書には、以下の内容が開示されている。

**【 0 1 6 8 】**

< 1 >

芯部の少なくとも一方の正面に多孔質部を有する陽極板と、前記多孔質部の表面に設けられた誘電体層と、前記誘電体層の表面に設けられた陰極層と、を含むコンデンサ部と、前記コンデンサ部を覆うように設けられた封止層と、30

前記陽極板に電気的に直接接続されるように前記コンデンサ部及び前記封止層を厚さ方向に貫通するように設けられ、両方の端部が前記封止層の表面に引き出された第1スルーホール導体と、

前記陰極層に電気的に直接接続されるように前記コンデンサ部及び前記封止層を前記厚さ方向に貫通するように設けられ、両方の端部が前記封止層の表面に引き出された第2スルーホール導体と、

前記第1スルーホール導体に電気的に接続されるように前記封止層の表面に設けられた第1外部電極層と、

前記第2スルーホール導体に電気的に接続されるように前記封止層の表面に設けられた第2外部電極層と、を備え、40

前記第1外部電極層の少なくとも一部は、前記厚さ方向において前記陰極層に重なる、コンデンサ素子。

**【 0 1 6 9 】**

< 2 >

前記陰極層、前記第1外部電極層及び前記第2外部電極層は、それぞれ、銅層を含み、前記陰極層の銅層の厚みをd1、前記第1外部電極層の銅層の厚みをd2、前記第2外部電極層の銅層の厚みをd3としたとき、

d1 d2かつd1 d3を満たす、<1>に記載のコンデンサ素子。

**【 0 1 7 0 】**

< 3 >

10

20

30

40

50

前記第1外部電極層の面積をS1、前記第2外部電極層の面積をS2としたとき、

S1 > S2を満たす、<1>又は<2>に記載のコンデンサ素子。

## 【0171】

&lt;4&gt;

前記封止層を前記厚さ方向に貫通するように設けられ、一方の端部が前記第2外部電極層に電気的に接続され、他方の端部が前記陰極層に電気的に接続された内部ビア導体をさらに備える、<1>～<3>のいずれか1つに記載のコンデンサ素子。

## 【0172】

&lt;5&gt;

前記陰極層は、前記誘電体層の表面上に設けられた固体電解質層と、前記固体電解質層の表面上に設けられた第1導電体層と、前記第2スルーホール導体に電気的に直接接続されるように前記第1導電体層の表面上に設けられた第2導電体層と、を含む、<1>～<4>のいずれか1つに記載のコンデンサ素子。

10

## 【符号の説明】

## 【0173】

1、2、3 コンデンサ素子

10 コンデンサ部

11 陽極板

11A 芯部

11B 多孔質部

12 陰極層

12A 固体電解質層

12B 第1導電体層

12C 第2導電体層

12Cu 陰極層の銅層

13 誘電体層

20 封止層

22 絶縁性材料

25 絶縁マスク層

30 外部電極層

20

31 第1外部電極層

31Cu 第1外部電極層の銅層

32 第2外部電極層

32Cu 第2外部電極層の銅層

40 スルーホール導体

41 第1スルーホール導体

42 第2スルーホール導体

51 第1貫通孔

52 第2貫通孔

53 貫通孔

60 内部ビア導体

91、92 樹脂充填部

30

40

50

## 【要約】

コンデンサ素子 1 は、芯部 11 A の少なくとも一方の主面に多孔質部 11 B を有する陽極板 11 と、多孔質部 11 B の表面に設けられた誘電体層 13 と、誘電体層 13 の表面に設けられた陰極層 12 と、を含むコンデンサ部 10 と、コンデンサ部 10 を覆うように設けられた封止層 20 と、陽極板 11 に電気的に直接接続されるようにコンデンサ部 10 及び封止層 20 を厚さ方向に貫通するように設けられ、両方の端部が封止層 20 の表面に引き出された第 1 スルーホール導体 41 と、陰極層 12 に電気的に直接接続されるようにコンデンサ部 10 及び封止層 20 を厚さ方向に貫通するように設けられ、両方の端部が封止層 20 の表面に引き出された第 2 スルーホール導体 42 と、第 1 スルーホール導体 41 に電気的に接続されるように封止層 20 の表面に設けられた第 1 外部電極層 31 と、第 2 スルーホール導体 42 に電気的に接続されるように封止層 20 の表面に設けられた第 2 外部電極層 32 と、を備え、第 1 外部電極層 31 の少なくとも一部は、厚さ方向において陰極層 12 に重なる。

## 【図面】

## 【図 1】

## 【図 2】

## 【図 3】

## 【図 4】

10

20

30

40

50

【図5】

【図6-1】

10

【図6-2】

图6-2

【図6-3】

20

【図6-4】

图6-4

【図6-5】

图6-5

30

【図6-6】

图6-6

【図6-7】

40

50

【図 6 - 8】

図6-8

【図 6 - 9】

図6-9

【図 6 - 10】

図6-10

【図 6 - 11】

図6-11

【図 6 - 12】

図6-12

【図 7 - 1】

図7-1

【図 7 - 2】

図7-2

【図 7 - 3】

図7-3

10

20

30

40

50

【図 7 - 4】

【図 7 - 5】

【図 7 - 6】

【図 8】

【図 9 - 1】

【図 9 - 2】

【図 9 - 3】

【図 9 - 4】

10

20

30

40

50

【図9-5】

図9-5

【図9-6】

図9-6

【図9-7】

図9-7

【図9-8】

図9-8

【図9-9】

図9-9

【図9-10】

図9-10

【図9-11】

図9-11

【図9-12】

図9-12

10

20

30

40

50

---

フロントページの続き

(56)参考文献 国際公開第 2023 / 100630 (WO , A1 )

特開 2007 - 073787 (JP , A )

特開 2004 - 031641 (JP , A )

特開 2006 - 147606 (JP , A )

(58)調査した分野 (Int.Cl. , DB名)

H01G 9 / 012

H01G 9 / 048

H01G 9 / 15

H01G 4 / 30

H01G 4 / 228 - 4 / 252