(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4219964号

(P4219964)

(45) 発行日 平成21年2月4日(2009.2.4)

(24) 登録日 平成20年11月21日(2008.11.21)

(51) Int.Cl.

F 1

|                   |                  |            |      |

|-------------------|------------------|------------|------|

| <b>G06F 12/10</b> | <b>(2006.01)</b> | G06F 12/10 | 555  |

| <b>G06F 13/36</b> | <b>(2006.01)</b> | G06F 12/10 | 541  |

| <b>G06F 12/14</b> | <b>(2006.01)</b> | G06F 13/36 | 310D |

|                   |                  | G06F 12/14 | 510E |

請求項の数 11 (全 13 頁)

|               |                              |

|---------------|------------------------------|

| (21) 出願番号     | 特願2007-533803 (P2007-533803) |

| (86) (22) 出願日 | 平成19年1月11日 (2007.1.11)       |

| (86) 国際出願番号   | PCT/JP2007/050265            |

| (87) 国際公開番号   | W02007/129482                |

| (87) 国際公開日    | 平成19年11月15日 (2007.11.15)     |

| 審査請求日         | 平成19年8月23日 (2007.8.23)       |

| (31) 優先権主張番号  | 特願2006-105735 (P2006-105735) |

| (32) 優先日      | 平成18年4月6日 (2006.4.6)         |

| (33) 優先権主張国   | 日本国 (JP)                     |

| (31) 優先権主張番号  | 特願2006-121900 (P2006-121900) |

| (32) 優先日      | 平成18年4月26日 (2006.4.26)       |

| (33) 優先権主張国   | 日本国 (JP)                     |

|           |                                                          |

|-----------|----------------------------------------------------------|

| (73) 特許権者 | 000002185<br>ソニー株式会社<br>東京都港区港南1丁目7番1号                   |

| (73) 特許権者 | 395015319<br>株式会社ソニー・コンピュータエンタテインメント<br>東京都港区南青山二丁目6番21号 |

| (74) 代理人  | 100105924<br>弁理士 森下 賢樹                                   |

| (72) 発明者  | 斎藤 英幸<br>東京都港区南青山2丁目6番21号 株式会社ソニー・コンピュータエンタテインメント内       |

最終頁に続く

(54) 【発明の名称】ブリッジ、プロセッサユニット、情報処理装置およびアクセス制御方法

## (57) 【特許請求の範囲】

## 【請求項 1】

プロセッサユニットと周辺デバイスとが相互接続された情報処理装置であって、前記プロセッサユニットは、実効アドレスを物理アドレスに変換するためのアドレス変換テーブルであって、該プロセッサユニットのメモリにおいて各前記周辺デバイスにそれぞれ割り当てられたエリアの実効アドレスと、該実効アドレスに対するアクセスの許可が与えられたアクセス元を、該プロセッサユニットにおいて識別するために規定されたアクセス元識別情報を対応付けて格納したテーブルを備えたアドレス変換部を有し、

前記周辺デバイスは、前記メモリへアクセスする際に、該周辺デバイスに対応する前記実効アドレスを指定しうるアクセス要求パケットであって、該周辺デバイスを一意に識別可能なデバイス識別情報を有するアクセス要求パケットを発行し、

前記アドレス変換部は、前記アクセス要求パケットに含まれるデバイス識別情報と、前記アドレス変換テーブルにおける、該アクセス要求パケットにより指定される実効アドレスに対応するアクセス元識別情報を一致することを条件として、当該実効アドレスに対するアクセスの許可を決定することを特徴とする情報処理装置。

## 【請求項 2】

プロセッサユニットと周辺デバイスとが相互接続された情報処理装置であって、前記プロセッサユニットと周辺デバイスは、各前記周辺デバイスの入出力バスを、前記プロセッサユニットの入出力バスに中継するブリッジにより接続され、

前記プロセッサユニットは、実効アドレスを物理アドレスに変換するためのアドレス変

換テーブルであって、該プロセッサユニットのメモリにおいて各前記周辺デバイスにそれぞれ割り当てられたエリアの実効アドレスと、該実効アドレスに対するアクセスの許可が与えられたアクセス元を、該プロセッサユニットにおいて識別するために規定されたアクセス元識別情報とを対応付けて格納したテーブルを備えたアドレス変換部を有し、

前記周辺デバイスは、前記メモリへアクセスする際に、該周辺デバイスに対応する前記実効アドレスを指定しうるアクセス要求パケットであって、該周辺デバイスを一意に識別可能なデバイス識別情報を有するアクセス要求パケットを発行し、

前記ブリッジは、前記アクセス要求パケットからアクセスコマンドを得るに際し、前記デバイス識別情報から照合情報を得て、前記アクセスコマンドに照合情報が含まれるようにし、

10

前記アドレス変換部は、前記アクセスコマンドに含まれる前記照合情報と、前記アドレス変換テーブルにおける、該アクセスコマンドにより指定される実効アドレスに対応するアクセス元識別情報とが一致することを条件として、当該実効アドレスに対するアクセスの許可を決定することを特徴とする情報処理装置。

#### 【請求項3】

前記プロセッサユニットのメモリは、複数のセグメントに分けられ、該複数のセグメントはさらにそれぞれ複数のページに分けられており、

前記アドレス変換テーブルは、セグメント番号とページ番号の組み合わせを、前記アクセス元識別情報と対応付けて格納したものであり、

前記ブリッジは、前記デバイス識別情報の一部を前記照合情報に対応付けるとともに、他の部分をセグメント番号とページ番号に対応付けることを特徴とする請求項2に記載の情報処理装置。

20

#### 【請求項4】

プロセッサユニットの入出力バスに、周辺デバイスの入出力バスを中継するブリッジであって、

前記周辺デバイスから、該プロセッサユニットのメモリにおいて該周辺デバイスに割り当てられたエリアの実効アドレスを指定しうるアクセス要求パケットであって、該周辺デバイスを一意に識別可能なデバイス識別情報を有するアクセス要求パケットを受け取る上流ポートと、

前記アクセス要求パケットに含まれる前記デバイス識別情報から、前記プロセッサユニットのメモリにおいて各前記周辺デバイスにそれぞれ割り当てられたエリアの実効アドレスに対するアクセスの許可が与えられたアクセス元を、前記プロセッサユニットにおいて識別するために規定されたアクセス元識別情報と照合するための照合情報を得、該照合情報と、前記アクセス要求パケットにより指定される実効アドレスとを含むアクセスコマンドを得る識別情報変換部と、

30

実効アドレスを物理アドレスに変換するためのアドレス変換テーブルであって、前記プロセッサユニットのメモリにおいて各前記周辺デバイスにそれぞれ割り当てられたエリアの実効アドレスと、該実効アドレスに対応するアクセス元識別情報とを対応付けて格納したテーブルを参照して実効アドレスを物理アドレスに変換する際に、前記アクセスコマンドに含まれる照合情報と、前記アドレス変換テーブルにおける、該アクセスコマンドに含まれる実効アドレスに対応するアクセス元識別情報とが一致することを条件として、当該実効アドレスに対するアクセスの許可を決定する前記プロセッサユニットへ、前記アクセスコマンドを渡す下流ポートとを備えることを特徴とするブリッジ。

40

#### 【請求項5】

前記プロセッサユニットのメモリは、複数のセグメントに分けられ、該複数のセグメントはさらにそれぞれ複数のページに分けられており、

前記アドレス変換テーブルは、セグメント番号とページ番号の組み合わせを、前記アクセス元識別情報と対応付けて格納したものであり、

前記デバイス識別情報の一部を前記照合情報に対応付けるとともに、他の部分をセグメント番号とページ番号に対応付けて前記アクセスコマンドを得ることを特徴とする請求項

50

4に記載のプリッジ。

【請求項6】

周辺デバイスと接続されたプロセッサユニットであって、

メモリと、

実効アドレスを物理アドレスに変換するためのアドレス変換テーブルであって、前記メモリにおいて各前記周辺デバイスにそれぞれ割り当てられたエリアの実効アドレスと、該実効アドレスに対するアクセスの許可が与えられたアクセス元を、該プロセッサユニットにおいて識別するために規定されたアクセス元識別情報とを対応付けて格納したテーブルを備えたアドレス変換部とを有し。

該アドレス変換部は、前記周辺デバイスから発行されたアクセス要求パケットに含まれるデバイス識別情報であって、該周辺デバイスを一意に識別可能なデバイス識別情報と、前記アドレス変換テーブルにおける、前記アクセス要求パケットに含まれる実効アドレスに対応するアクセス元識別情報とが一致することを条件として、当該実効アドレスに対するアクセスの許可を決定することを特徴とするプロセッサユニット。 10

【請求項7】

周辺デバイスの入出力バスを、プロセッサユニットの入出力バスに中継するプリッジにより前記周辺デバイスと接続された前記プロセッサユニットであって、

メモリと、

実効アドレスを物理アドレスに変換するためのアドレス変換テーブルであって、前記メモリにおいて各前記周辺デバイスにそれぞれ割り当てられたエリアの実効アドレスと、該実効アドレスに対するアクセスの許可が与えられたアクセス元を、該プロセッサユニットにおいて識別するために規定されたアクセス元識別情報とを対応付けて格納したテーブルを備えたアドレス変換部とを有し。 20

該アドレス変換部は、前記周辺デバイスから発行されたデバイス識別情報を含むアクセス要求パケットを、前記プリッジにより変換して得たアクセスコマンドに含まれる照合情報であって、該周辺デバイスを一意に識別可能なデバイス識別情報に対応付けられる照合情報と、前記アドレス変換テーブルにおける、前記アクセスコマンドに含まれる実効アドレスに対応するアクセス元識別情報とが一致することを条件として、当該実効アドレスに対するアクセスの許可を決定することを特徴とするプロセッサユニット。

【請求項8】

前記プロセッサユニットのメモリは、複数のセグメントに分けられ、該複数のセグメントはさらにそれぞれ複数のページに分けられており、

前記アドレス変換テーブルは、セグメント番号とページ番号の組み合わせを、前記アクセス元識別情報と対応付けて格納したものであり、

前記アクセスコマンドは、前記プリッジにより、前記デバイス識別情報の一部からアクセス元識別情報と照合するための照合情報を得るとともに、他の部分をセグメント番号とページ番号に対応付けるようにして得られたものであることを特徴とする請求項7に記載のプロセッサユニット。

【請求項9】

プロセッサユニットと周辺デバイスとが接続された情報処理装置におけるアクセス制御方法であって、 40

前記周辺デバイスから、該プロセッサユニットのメモリにおいて該周辺デバイスに割り当てられたエリアの実効アドレスを指定しうるアクセス要求パケットであって、該周辺デバイスを一意に識別可能なデバイス識別情報を有するアクセス要求パケットを受け取るステップと、

実効アドレスを物理アドレスに変換するためのアドレス変換テーブルであって、該プロセッサユニットのメモリにおいて各前記周辺デバイスにそれぞれ割り当てられたエリアの実効アドレスと、該実効アドレスに対するアクセスの許可が与えられたアクセス元を、該プロセッサユニットにおいて識別するために規定されたアクセス元識別情報とを対応付けて格納したテーブルを参照して、前記アクセス要求パケットに含まれるデバイス識別情報 50

と、前記アドレス変換テーブルにおける、該アクセス要求パケットにより指定される実効アドレスに対応するアクセス元識別情報とが一致することを条件として、当該実効アドレスに対するアクセスの許可を決定するステップとを有することを特徴とするアクセス制御方法。

#### 【請求項 10】

プロセッサユニットと周辺デバイスとが、前記周辺デバイスの入出力バスを前記プロセッサユニットの入出力バスに中継するブリッジにより接続された情報処理装置におけるアクセス制御方法であって、

前記周辺デバイスから前記ブリッジが、該プロセッサユニットのメモリにおいて該周辺デバイスに割り当てられたエリアの実効アドレスを指定しうるアクセス要求パケットであって、該周辺デバイスを一意に識別可能なデバイス識別情報を有するアクセス要求パケットを受け取るステップと、

前記ブリッジが、前記アクセス要求パケットからアクセスコマンドを得るに際し、前記デバイス識別情報から照合情報を得て、前記アクセスコマンドに照合情報が含まれるようにするステップと、

実効アドレスを物理アドレスに変換するためのアドレス変換テーブルであって、該プロセッサユニットのメモリにおいて各前記周辺デバイスにそれぞれ割り当てられたエリアの実効アドレスと、該実効アドレスに対するアクセスの許可が与えられたアクセス元を、該プロセッサユニットにおいて識別するために規定されたアクセス元識別情報を対応付けて格納したテーブルを参照して、前記アクセスコマンドに含まれる前記照合情報と、前記アドレス変換テーブルにおける、該アクセスコマンドにより指定される実効アドレスに対応するアクセス元識別情報とが一致することを条件として、当該実効アドレスに対するアクセスの許可を決定するステップとを有することを特徴とするアクセス制御方法。

#### 【請求項 11】

前記プロセッサユニットのメモリは、複数のセグメントに分けられ、該複数のセグメントはさらにそれぞれ複数のページに分けられており、

前記アドレス変換テーブルは、セグメント番号とページ番号の組み合わせを、前記アクセス元識別情報と対応付けて格納したものであり、

前記デバイス識別情報の一部を前記照合情報に対応付けるとともに、他の部分をセグメント番号とページ番号に対応付けることを特徴とする請求項 10 に記載のアクセス制御方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、プロセッサユニットに接続された周辺デバイスから、プロセッサユニットへのアクセス技術に関する。

##### 【背景技術】

##### 【0002】

パーソナルコンピュータやサーバには、たとえば PCI ( Peripheral Component Interconnect ) バスを介して各種の周辺デバイスが接続され、情報処理システムが構成される。

##### 【0003】

周辺デバイスからプロセッサのメモリへアクセスする際に、プロセッサの負担を減らすために、DMA ( ダイレクト・メモリ・アクセス ) アーキテクチャを用いることが考えられる。こうすることによって、たとえば、プロセッサのメモリ領域において、各周辺デバイスが使用するエリアを割り当てておき、周辺デバイスは、自身に割り当てられたエリアに直接アクセスすることができる。

##### 【発明の開示】

##### 【発明が解決しようとする課題】

##### 【0004】

10

20

30

40

50

しかし、周辺デバイスからの直接アクセスを実現するために、プロセッサのD M A C (ダイレクト・メモリ・アクセス・コントローラ)をユーザソフトウェアに開放してしまうと、悪意のあるユーザソフトウェアにより、周辺デバイスに割り当てられたエリアがアクセスされてしまうことが起こりうる。

【0005】

本発明は、上記事情に鑑みてなされたものであり、その目的は、周辺デバイスからプロセッサのメモリへのアクセスにおいて、効率を追求しながら安全性を図ることができる技術を提供することにある。

【課題を解決するための手段】

【0006】

10

本発明のある態様は、ブリッジである。このブリッジは、プロセッサユニットの入出力バスと周辺デバイスの入出力バスを中継するブリッジであり、上流ポートと、識別情報変換部と、下流ポートを有する。

【0007】

上流ポートは、周辺デバイスから、該プロセッサユニットのメモリにおいて該周辺デバイスに割り当てられたエリアの実効アドレスを指定しうるアクセス要求パケットであって、該周辺デバイスを一意に識別可能なデバイス識別情報を有するアクセス要求パケットを受け取る。

【0008】

20

識別情報変換部は、アクセス要求パケットに含まれるデバイス識別情報から、プロセッサユニットのメモリにおいて各周辺デバイスにそれぞれ割り当てられたエリアの実効アドレスに対するアクセスの許可が与えられたアクセス元を、プロセッサユニットにおいて識別するために規定されたアクセス元識別情報と照合するための照合情報を得、該照合情報と、アクセス要求パケットにより指定される実効アドレスとを含むアクセスコマンドを得る。 下流ポートは、実効アドレスを物理アドレスに変換するためのアドレス変換テーブルであって、プロセッサユニットのメモリにおいて各周辺デバイスにそれぞれ割り当てられたエリアの実効アドレスと、該実効アドレスに対応するアクセス元識別情報とを対応付けて格納したテーブルを参照して実効アドレスを物理アドレスに変換する際に、アクセスコマンドに含まれる照合情報と、アドレス変換テーブルにおける、該アクセスコマンドに含まれる実効アドレスに対応するアクセス元識別情報とが一致することを条件として、当該実効アドレスに対するアクセスの許可を決定する該プロセッサユニットへ、識別情報変換部により得られたアクセスコマンドを渡す。

30

【0009】

また、プロセッサユニットのメモリは、複数のセグメントに分けられ、該複数のセグメントはさらにそれぞれ複数のページに分けられており、アドレス変換テーブルは、セグメント番号とページ番号の組み合わせを、アクセス元識別情報とを対応付けて格納したものであるようにし、識別情報変換部は、デバイス識別情報の一部をアクセス元識別情報に対応付けるとともに、他の部分をセグメント番号とページ番号に対応付けてアクセスコマンドを得るようにしてもよい。

【0010】

40

本発明の別の態様は、プロセッサユニットである。このプロセッサユニットは、周辺デバイスの入出力バスを、プロセッサユニットの入出力バスに中継するブリッジにより周辺デバイスと接続されている。

【0011】

該プロセッサユニットは、メモリと、アドレス変換部を有する。

【0012】

アドレス変換部は、実効アドレスを物理アドレスに変換するためのアドレス変換テーブルであって、メモリにおいて各周辺デバイスにそれぞれ割り当てられたエリアの実効アドレスと、該実効アドレスに対するアクセスの許可が与えられたアクセス元を、該プロセッサユニットにおいて識別するために規定されたアクセス元識別情報とを対応付けて格納し

50

たテーブルを備える。アドレス変換部は、ブリッジにより、周辺デバイスから発行されたアクセス要求パケットを変換して得たアクセスコマンドに含まれるデバイス識別情報であって、該周辺デバイスを一意に識別可能なデバイス識別情報と、アドレス変換テーブルにおける、アクセスコマンドに含まれる実効アドレスに対応するアクセス元識別情報とが一致することを条件として、当該実効アドレスに対するアクセスの許可を決定する。

#### 【0013】

なお、以上の構成要素の任意の組合せ、本発明の表現を方法、装置、システム、コンピュータプログラム、コンピュータプログラムを記憶した記憶媒体などの間で相互に置換したものもまた、本発明の態様として有効である。

#### 【発明の効果】

10

#### 【0014】

本発明は、プロセッサユニットに接続された周辺デバイスから、プロセッサユニットのメモリへのアクセスにおいて、効率を追求しながら安全性を図ることができる。

#### 【図面の簡単な説明】

#### 【0015】

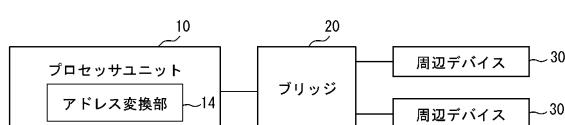

【図1】本発明の概要の説明に用いた情報処理システムを示す図である。

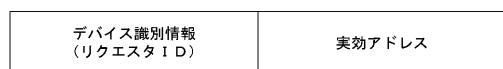

【図2】アクセス要求パケットの例（その1）を示す図である。

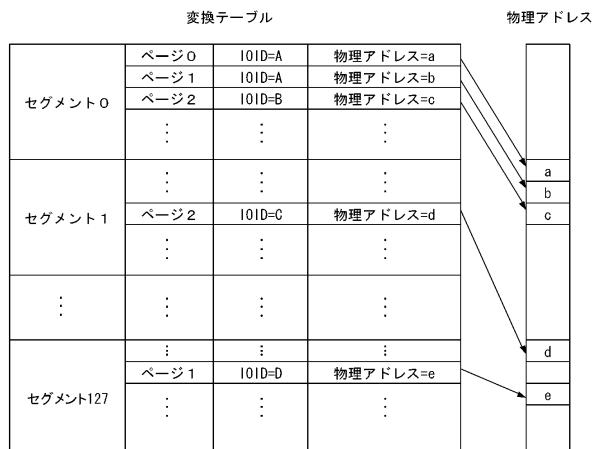

【図3】実効アドレスを物理アドレスに変換するためのアドレス変換テーブルの例（その1）を示す図である。

【図4】実効アドレスを物理アドレスに変換するためのアドレス変換テーブルの例（その2）を示す図である。

20

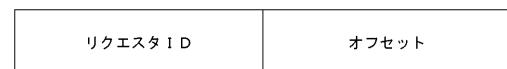

【図5】アクセス要求パケットの例（その2）を示す図である。

【図6】図5に示すアクセス要求パケットを変換して得たアクセスコマンドを示す図である。

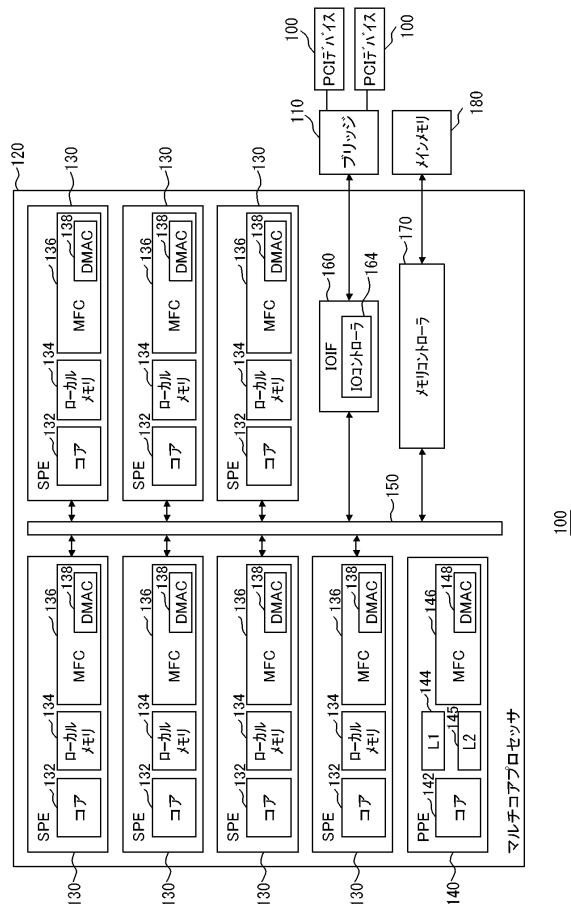

【図7】本発明にかかる実施の形態による情報処理システムの構成を示す図である。

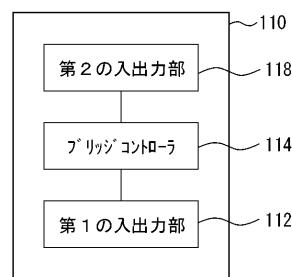

【図8】図7に示す情報処理システムにおけるブリッジの構成例を示す図である。

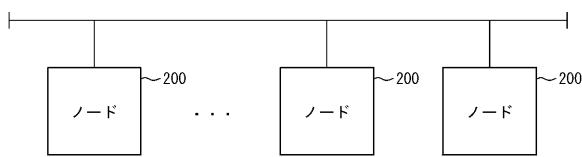

【図9】本発明の技術思想を適用可能な分散アプリケーションシステムの例を示す図である。

#### 【符号の説明】

#### 【0016】

30

10 プロセッサユニット、 14 アドレス変換部、 16 アドレス変換テーブル

、 18 アドレス変換テーブル、 20 ブリッジ、 30 周辺デバイス、 32

アクセス要求パケット、 34 アクセス要求パケット、 100 PCIデバイス、

110 ブリッジ、 112 第1の入出力部、 114 ブリッジコントローラ、 1

18 第2の入出力部、 120 マルチコアプロセッサ、 130 SPE、 132

コア、 134 ローカルメモリ、 136 MFC、 138 DMAc、 140

PPE、 142 コア、 144 キャッシュ、 145 キャッシュ、 146

MFC、 148 DMAc、 150 リングバス、 160 IOIF、 164

IOコントローラ、 170 メモリコントローラ、 180 メインメモリ、 200

ノード。

40

#### 【発明を実施するための最良の形態】

#### 【0017】

本発明の実施の形態の詳細を説明する前に、まず、本発明者が提案する技術の概要を説明する。

#### 【0018】

図1に示す情報処理システムについて考える。この情報処理システムは、プロセッサユニット10と、複数ここでは例として2つの周辺デバイス30を有し、プロセッサユニット10と周辺デバイス30は、ブリッジ20により接続される。プロセッサユニット10は、単一のプロセッサを有するシングルプロセッサシステムであってもよいし、複数のプロセッサを含むマルチプロセッサシステムであってもよい。なお、プロセッサユニット1

50

0は、図示しないメモリを備え、マルチプロセッサシステムの場合においては、このメモリは、各プロセッサからアクセス可能な共有メモリである。また、プロセッサユニット10は、アドレス変換部14を有し、その詳細については後述する。

#### 【0019】

周辺デバイス30は、プロセッサユニット10のメモリにアクセスするのに当たり、アクセス要求パケットを発行する。このアクセス要求パケットは、周辺デバイス30のアクセス先のメモリ領域の実効アドレスを指定可能なものであり、周辺デバイス30のデバイス識別情報を含む。図2は、アクセス要求パケットの例を示す。

#### 【0020】

ここで、実効アドレスとは実効アドレス空間内の所定の位置を示すアドレスである。さらに実効アドレス空間とは、プロセッサユニット10が備えるメモリから部分的に切り取られたメモリ空間の一部同士を集合させ、結合したものである。実効アドレス空間の内部構成を最適化することにより、プロセッサユニット10において動作するアプリケーションプログラムは最大パフォーマンスで動作できる。

10

#### 【0021】

図2に示す例のアクセス要求パケット32は、デバイス識別情報と実効アドレスを含む。デバイス識別情報は、図1に示す情報処理システムにおいて、周辺デバイス30を一意に識別可能な情報であり、たとえば、周辺デバイスが接続されたバスの番号など周辺デバイスの物理位置を特定可能な情報や、周辺デバイスの種類などを示す情報とすることができる。また、情報処理システムの機能拡張や性能強化を図るために、グラフィックプロセッサや高速なメモリデバイスを周辺デバイスとして接続することがあり、より多くの周辺デバイスを接続できるようにするために要請されている背景において、ブリッジの先にスイッチを多段接続して、デバイスのネットワークを構成することもある。この場合において、デバイス識別情報は、スイッチ番号も含む。以下、説明の便宜のため、デバイス識別情報をリクエスタIDという。

20

#### 【0022】

プロセッサユニット10のアドレス変換部14は、アクセス要求パケット32に含まれる実効アドレスを、メモリの物理アドレスに変換することによって、アクセス要求パケットを発行した周辺デバイス30によるメモリへのアクセスを可能にする。ここで、アドレス変換部14について説明する。

30

#### 【0023】

アドレス変換部14は、図3に示すアドレス変換テーブル16を用いてアドレスの変換を行う。

#### 【0024】

プロセッサユニット10のメモリにおいて、各周辺デバイス30が使用するエリアを割り当てられており、アドレス変換テーブル16は、それぞれのエリアに対するアクセスの許可が与えられたアクセス元を、プロセッサユニット10において識別するアクセス元識別情報（以下IOIDという）と、これらのエリアに対応した、実効アドレス空間におけるエリア（以下実効エリアという）を示す実効アドレスと、物理アドレス空間におけるこれらのエリア（以下物理エリアという）を示す物理アドレスとを対応付けて格納している。なお、1つのIOIDは、1つ以上の実効アドレスに対応する。

40

#### 【0025】

アドレス変換部14は、アクセス要求パケット32に含まれる実効アドレスを物理アドレスに変換する際に、まず、アクセス要求パケット32に含まれるリクエスタIDと、アドレス変換テーブル16におけるIOIDとを用いて照合を行う。具体的には、アドレス変換テーブル16における、アクセス要求パケット32に含まれる実効アドレスに対応するIOIDが、リクエスタIDと一致するか否かを照合する。照合の結果、一致すればアクセスを許可し、この実効アドレスを対応する物理アドレスに変換する一方、一致しなければエラーを返し、アクセスを拒否する。

#### 【0026】

50

こうすることによって、周辺デバイス30から、プロセッサユニット10のメモリにおいてこの周辺デバイス30に割り当てられたエリアへの直接アクセスを実現する。それとともに、周辺デバイスが、自身に対して割り当てられた領域以外の領域へアクセスできないようにしているので、プロセッサユニット10に図示しないDMAをユーザソフトウェアに開放しても、悪意のあるデバイスやユーザソフトウェアから、周辺デバイス30へ割り当てられたメモリ領域へのアクセスを防ぐことができ、安全である。

#### 【0027】

一方、多くの場合において、プロセッサユニットの入出力バスと、周辺デバイスの入出力バスの規格が異なる。そのため、周辺デバイスの入出力バスを、プロセッサユニットの入出力バスへ中継するブリッジが用いられる。この場合において、規格の制約から、リクエスタIDのビット数と、IOIDのビット数は一般に異なり、IOIDのビット数がリクエスタIDのビット数より少ないとときに問題が生じる。10

#### 【0028】

そこで、リクエスタIDをそのままIOIDと照合する代わりに、ブリッジによって、リクエスタIDを、そのビット数がIOIDのビット数に合致するようにIOIDと照合するようすれば、この場合においてもIOIDによるメモリの保護ができる。

#### 【0029】

これについて、本発明者は下記の技術を提案する。ここでも、図1に示す情報処理システムを利用して説明する。

#### 【0030】

この場合において、プロセッサユニット10のアドレス変換部14は、図4に示すアドレス変換テーブル18を用いる。図示のように、IOIDは、セグメント番号とページ番号の組み合わせに対応して格納されている。20

#### 【0031】

プロセッサユニット10のメモリはセグメントに分けられており、各セグメントはさらに複数のページに分けられている。セグメント番号とページ番号の組み合わせは、実効エリアを示す。

#### 【0032】

アドレス変換テーブル18は、セグメントに含まれる各ページ毎に物理アドレスをマッピングするとともに、IOIDに基づいたアクセスの許否を示している。30

#### 【0033】

図5は、この場合において、周辺デバイス30から発行されるアクセス要求パケットの例を示す。この例のアクセス要求パケット34は、リクエスタIDと、アクセス先のメモリ領域におけるオフセットを含む。

#### 【0034】

ブリッジ20は、アクセス要求パケット34を、IOIDと実効アドレスを含むアクセスコマンドに変換する。具体的には、アクセス要求パケット34に含まれるリクエスタIDの一部たとえば下位の、IOIDのビット数分のビットをIOIDに対応付けるとともに、他の部分たとえば上位のビットを、セグメント番号とページ番号に対応付ける。

#### 【0035】

図6は、ブリッジ20により得られたアクセスコマンドを示す。アクセスコマンドは、セグメント番号、ページ番号、IOID、オフセットを含む。

#### 【0036】

プロセッサユニット10のアドレス変換部14は、ブリッジ20からのアクセスコマンドに含まれる実効アドレス（ここでは、セグメント番号、ページ番号、オフセットの組合せ）を物理アドレスに変換する際に、まず、アクセスコマンドに含まれるIOIDと、アドレス変換テーブル18におけるIOIDとを照合する。具体的には、アドレス変換テーブル18における、アクセスコマンドに含まれるセグメント番号とページ番号の組合せに対応するIOIDが、アクセスコマンドに含まれるIOIDと一致するか否かを照合する。照合の結果、一致すればアクセスを許可し、アクセスコマンドに含まれる実効アドレス4050

を対応する物理アドレスに変換する一方、一致しなければエラーを返し、アクセスを拒否する。

#### 【0037】

こうすることによって、周辺デバイスのリクエスタIDのビット数が、プロセッサユニット10のアドレス変換部14が使用するIOIDのビット数より多い場合においても、IOIDによるメモリの保護ができる。

#### 【0038】

以下、本発明の実施の形態について、以上の概要を具現化してシステムを説明する。

#### 【0039】

図7は、本発明にかかる実施の形態による情報処理システムの構成を示す。この情報処理システムは、複数の周辺デバイスたとえばPCIデバイス100、マルチコアプロセッサ120、メインメモリ180、PCIデバイス100とマルチコアプロセッサ120とを接続するブリッジ110を有する。マルチコアプロセッサ120とメインメモリ180は、1つのプロセッサユニットを構成する。

10

#### 【0040】

PCIデバイス100の接続インターフェイスとして、PCIバスを用いる。ここで、PCIバスは、PCI、PCIX、PCI Express（登録商標）のいずれの仕様によるものでもよい。

#### 【0041】

マルチコアプロセッサ120は、ワンチップで形成されており、主処理ユニットPPE（Power Processing Element）140と、複数、図示の例では8つのサブ処理ユニットSPE（Synergistic Processing Element）130と、IOインターフェイス（以下IOIFという）160と、メモリコントローラ170とを有し、これらは、リングバス150によって接続される。

20

#### 【0042】

メインメモリ180は、マルチコアプロセッサ120の各処理ユニットの共有メモリであり、メモリコントローラ170と接続されている。なお、メインメモリ180は、複数のセグメントに分けられており、各セグメントは、さらに複数のページに分けられている。

。

#### 【0043】

メモリコントローラ170は、PPE140および各SPE130がメインメモリ180にアクセスする仲介を行う。なお、図7に示す例では、メインメモリ180はマルチコアプロセッサ120の外部に設けられているが、マルチコアプロセッサ120内に含まれるように設けられてもよい。

30

#### 【0044】

IOIF160は、図示しないIOIFバスによってブリッジ110と接続され、ブリッジ110と協働して、PCIデバイス100からメインメモリ180へのアクセスを可能にする。IOIF160には、IOコントローラ164が含まれている。

#### 【0045】

SPE130は、コア132と、ローカルメモリ134と、メモリフローコントローラ（以下MFCという）136とを備え、MFC136には、DMAC（ダイレクトメモリアクセスコントローラ）138が含まれている。なお、ローカルメモリ134は、従来のハードウェアキャッシュメモリではないことが望ましく、それには、ハードウェアキャッシュメモリ機能を実現するための、チップ内蔵またはチップ外に置かれたハードウェアキャッシュ回路、キャッシュレジスタ、キャッシュメモリコントローラなどが無い。

40

#### 【0046】

PPE140は、コア142と、L1キャッシュ144と、L2キャッシュ145と、MFC146とを備え、MFC146には、DMAC148が含まれている。

#### 【0047】

通常、マルチコアプロセッサ120のオペレーティングシステム（以下OSともいう）

50

は、PPE140において動作し、OSの基本処理に基づいて、各SPE130で動作するプログラムが決定される。また、SPE130で動作するプログラムは、OSの機能の一部をなすようなプログラム（たとえばデバイスドライバや、システムプログラムの一部など）であってもよい。なお、PPE140とSPE130の命令セットアーキテクチャは、異なる命令セットを有する。

#### 【0048】

図7に示す情報処理システムの初期化時において、マルチコアプロセッサ120のデバイスドライバは、デバイスの探索を行ってそれぞれのPCIデバイス100のリクエスタIDを取得する。この例において、リクエスタIDは、PCIの規格によりビット数が16ビットに定められている。これによって、マルチコアプロセッサ120のOSは、各PCIデバイス100が利用可能なセグメントと、各PCIデバイス100のI/OIDを得る。ここで、マルチコアプロセッサ120の仕様によってI/OIDのビット数がたとえば11ビットであり、OSはリクエスタIDの下位11ビットをI/OIDとして取得する。

#### 【0049】

そして、OSは、PCIデバイス100に対するメモリ割り当て要求に応じて、セグメントに対してページエントリを生成する。ページのサイズはここで選択することができる。この割当てによって、図4に示すアドレス変換テーブル18が生成される。OSは、このアドレス変換テーブル18をメインメモリ180に格納し、これによってPCIデバイス100からメインメモリ180へのアクセスが可能になる。

#### 【0050】

PCIデバイス100は、メインメモリ180にアクセスするのにあたり、アクセス要求パケットを発行する。ここで、このアクセス要求パケットとして、図5に示すアクセス要求パケット34を用いる。

#### 【0051】

図8は、ブリッジ110の構成を示す。ブリッジ110は、第1の入出力部112、ブリッジコントローラ114と、第2の入出力部118を有する。

#### 【0052】

第1の入出力部112は、PCIデバイス100により発行されたアクセス要求パケットを受け取り、ブリッジコントローラ114は、このアクセス要求パケットをアクセスコマンドに変換する。そして、第2の入出力部118は、このアクセスコマンドをマルチコアプロセッサ120のI/OIF160に渡す。

#### 【0053】

ブリッジコントローラ114は、アクセス要求パケットに含まれるPCIデバイス100のリクエスタIDの下位11ビットをI/OIDとして取得し、リクエスタIDの上位5ビットを、セグメント番号とページ番号に対応づける。この変換によって、図6に示すアクセスコマンドが得られる。

#### 【0054】

I/OIF160のI/Oコントローラ164は、図4に示すアドレス変換テーブル18を参照して、ブリッジ110から渡されたアクセスコマンドに含まれる実効アドレス（セグメント番号、ページ番号、オフセットの組合せ）を、メインメモリ180における物理アドレスに変換する。ページサイズが4KBであるときに、36ビットのアクセスコマンドの各ビットは下記のように規定される：[34:28] = セグメント、[27:12] = ページ、Address[11:0] = オフセット。

#### 【0055】

I/Oコントローラ164は、変換するのに際し、まず、アクセスコマンドに含まれるセグメント番号、ページ番号について、変換テーブルを参照して、アクセスが許可されているか否かを見出す。たとえば、「セグメント = 1、ページ = 2、オフセット = 0」を示すアクセスコマンドとともに受信したI/OIDがCである場合には、アドレス変換テーブル18はセグメント = 1、ページ = 2に対して、アクセスを許可するI/OIDとしてCを対

10

20

30

40

50

応づけているので、I/Oコントローラ164は、「セグメント=1、ページ=2」に対応する物理アドレスdへのアクセスを許可する。一方、「セグメント=127、ページ=1、オフセット=0」を示すアクセスコマンドとともに受信したI/OIDがCである場合には、変換テーブルはセグメント=127、ページ=1に対して、アクセスを許可するI/OIDとしてDを対応づけているため、I/Oコントローラ164は、エラー信号を返して、アクセスを拒否する。

#### 【0056】

以上、本発明を実施の形態をもとに説明した。実施の形態は例示であり、それらの各構成要素や各処理プロセスの組合せにいろいろな変形例が可能であること、またそうした変形例も本発明の範囲にあることは当業者に理解されるところである。

10

#### 【0057】

たとえば、図7に示す情報処理システムにおいて、周辺デバイスはPCIデバイス100であるが、PCI規格以外の周辺デバイスを用いてもよい。

#### 【0058】

また、本発明の技術思想を、ネットワーク上の複数のノードが並列に同じアプリケーションを処理可能な分散アプリケーションシステムに適用し、デバイス識別情報をアプリケーション識別情報に置き換えることによって、異なるノード上で動作する同じアプリケーション間のアクセスを可能にするとともに、それぞれのノード上においてこのアプリケーションに対して割り当てられたメモリ空間の保護を図ることができる。具体的には、たとえば図9に示す分散処理アプリケーションシステムにおいて、各ノード200は、プロセッサユニットとメモリを備える。動作中のアプリケーション毎に、このアプリケーションを一意に識別可能なアプリケーション識別情報を付与するとともに、各ノード200のメモリにおいて、動作中の各アプリケーション毎に、このアプリケーションが使用可能なエリアを割り当てる。アクセス元のノード200からアクセス先のノード200にアクセスする際に、アクセス要求パケットに、アプリケーション識別情報を付加する。アクセス先のノード200においてアクセス要求パケットに含まれる実効アドレスを物理アドレスに変換する際に、アプリケーション識別情報をもとに、この実効アドレスに対するアクセスの許否を決定する。こうすることによって、ネットワーク上の異なるノードで動作する同じアプリケーションは、互いのノードにおいて、このアプリケーションに対して割り当てられたエリアにアクセスできるとともに、他のアプリケーションによって、自身のエリアをアクセスされることを防ぐことができる。

20

#### 【産業上の利用可能性】

#### 【0059】

本発明は、周辺デバイスからプロセッサのメモリへのアクセス技術に適用することができる。

30

【 义 1 】

【 図 2 】

| 【図 5】 | アクセス元識別情報<br>(I O I D) | 実効アドレス | 物理アドレス |

|-------|------------------------|--------|--------|

| .     | .                      | .      | .      |

| .     | .                      | .      | .      |

| ⋮     | ⋮                      | ⋮      | ⋮      |

16

〔 四 〕

18

【圖 5】

34

【図6】

(セグメント番号, ページ番号, I O I D, オフセット)

【 四 7 】

【 図 8 】

〔 9 〕

---

フロントページの続き

(72)発明者 山崎 剛

東京都港区南青山2丁目6番21号 株式会社ソニー・コンピュータエンタテインメント内

(72)発明者 高橋 祐治

東京都港区港南1丁目7番1号 ソニー株式会社内

(72)発明者 三林 秀樹

東京都港区港南1丁目7番1号 ソニー株式会社内

審査官 清木 泰

(56)参考文献 特開昭62-115554(JP,A)

特開平04-130553(JP,A)

特開昭57-189384(JP,A)

特開平04-348442(JP,A)

特開2005-242598(JP,A)

特開2006-172474(JP,A)

特開2005-339401(JP,A)

特開2002-304364(JP,A)

特開2000-148665(JP,A)

特開平10-187539(JP,A)

特開平06-187286(JP,A)

特開平05-035582(JP,A)

特開昭63-040953(JP,A)

特開昭60-089266(JP,A)

特開昭58-169611(JP,A)

(58)調査した分野(Int.Cl., DB名)

G06F12/08-12/12

G06F13/10-13/14

G06F13/20-13/378

G06F12/14

G06F21/02-21/24