(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2012-4269

(P2012-4269A)

(43) 公開日 平成24年1月5日(2012.1.5)

(51) Int.Cl.

H01L 29/78 (2006.01)

H01L 21/336 (2006.01)

F 1

H01L 29/78 652H

H01L 29/78 652K

H01L 29/78 658F

テーマコード(参考)

審査請求 未請求 請求項の数 8 O L (全 19 頁)

(21) 出願番号

特願2010-136866 (P2010-136866)

(22) 出願日

平成22年6月16日 (2010.6.16)

(71) 出願人 000002130

住友電気工業株式会社

大阪府大阪市中央区北浜四丁目5番33号

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

(74) 代理人 100083703

弁理士 仲村 義平

(74) 代理人 100096781

弁理士 堀井 豊

(74) 代理人 100109162

弁理士 酒井 将行

(74) 代理人 100111246

弁理士 荒川 伸夫

最終頁に続く

(54) 【発明の名称】炭化珪素半導体装置の製造方法および炭化珪素半導体装置の製造装置

## (57) 【要約】

【課題】高品質なSiC半導体装置の製造方法を提供する。

【解決手段】SiC半導体装置を製造する方法は、少なくとも一部に不純物が注入された第1の表面を含む炭化珪素半導体を準備する工程と、炭化珪素半導体の第1の表面を、水素ガスを含むガスを用いてドライエッティングすることにより、第2の表面を形成する工程と、第2の表面上に、SiC半導体装置を構成する酸化膜を形成する工程とを備える。

【選択図】図1

## 【特許請求の範囲】

## 【請求項 1】

炭化珪素半導体装置を製造する方法であって、少なくとも一部に不純物が注入された第1の表面を含む炭化珪素半導体を準備する工程と、

前記炭化珪素半導体の前記第1の表面を、水素ガスを含むガスを用いてドライエッチングすることにより、第2の表面を形成する工程と、

前記第2の表面上に、前記炭化珪素半導体装置を構成する酸化膜を形成する工程とを備えた、炭化珪素半導体装置の製造方法。

## 【請求項 2】

前記第2の表面を形成する工程後に、液相を用いた洗浄をせずに、前記酸化膜を形成する工程を実施する、請求項1に記載の炭化珪素半導体装置の製造方法。

## 【請求項 3】

前記第2の表面を形成する工程において、前記ドライエッチングを1300以上1650以下の温度範囲で行なう、請求項1または2に記載の炭化珪素半導体装置の製造方法。

## 【請求項 4】

前記酸化膜を形成する工程は、前記第2の表面上に珪素元素を含む膜を形成し、前記珪素元素を含む膜を酸化することにより、前記酸化膜を形成する、請求項1～3のいずれか1項に記載の炭化珪素半導体装置の製造方法。

## 【請求項 5】

前記第2の表面を形成する工程において、前記ガスは塩化水素ガスをさらに含む、請求項1～4のいずれか1項に記載の炭化珪素半導体装置の製造方法。

## 【請求項 6】

前記第2の表面を形成する工程において、前記ガスは炭化水素ガスをさらに含む、請求項1～5のいずれか1項に記載の炭化珪素半導体装置の製造方法。

## 【請求項 7】

前記第2の表面を形成する工程と前記酸化膜を形成する工程との間では、前記炭化珪素半導体は大気が遮断された雰囲気内に配置される、請求項1～6のいずれか1項に記載の炭化珪素半導体装置の製造方法。

## 【請求項 8】

炭化珪素半導体において、少なくとも一部に不純物が注入された第1の表面を水素ガスを含むガスを用いたドライエッチングによって除去するための除去部と、

前記炭化珪素半導体において前記第1の表面が除去されることにより形成された第2の表面上に前記炭化珪素半導体装置を構成する酸化膜を形成するための形成部と、

前記炭化珪素半導体を搬送可能に前記除去部と前記形成部とを接続する接続部とを備え、

前記接続部における前記炭化珪素半導体を搬送させる領域は、大気の遮断が可能である、炭化珪素半導体装置の製造装置。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、炭化珪素(SiC)半導体装置の製造方法およびSiC半導体装置の製造装置に関し、より特定的には酸化膜を有するSiC半導体装置の製造方法およびこの製造方法に用いられる製造装置に関する。

## 【背景技術】

## 【0002】

従来より、半導体装置を構成する材料として珪素(Si)が広く採用されている。Si半導体デバイス、たとえば、MOSFET(Metal Oxide Semiconductor Field Effect Transistor:電界効果トランジスタ)は、以下のようにして製造することができる。

10

20

30

40

50

## 【0003】

すなわち、まず、シリコン(Si)基板上にエピタキシャル層を形成して、Si半導体を作製する。次に、Si半導体に不純物(ドーパント)を導入する目的でイオン注入工程を行ない、次いで、導入された不純物を活性化させる目的で、当該Si半導体を加熱処理(活性化アニール処理)する。そして、加熱処理後のSi半導体の表面にゲート酸化膜を形成し、その上に電極を形成する。

## 【0004】

上記のような従来のSi半導体装置の製造においては、Si基板の表面に付着している、パーティクルや金属不純物などの不純物といった付着物を除去するための洗浄が行なわれている。このような洗浄方法として、RCA洗浄のような、薬液を用いた洗浄方法が広く採用されている。

10

## 【0005】

RCA洗浄においては、まず、Si基板の表面を硫酸および過酸化水素を含む薬液で洗浄することによってSi基板の表面にSi酸化膜を形成する。このSi酸化膜の内部や表面にはパーティクルおよび金属不純物が取り込まれる。次に、このSi基板を希フッ酸水溶液で洗浄して、Si酸化膜をエッチャリング除去すると共にパーティクルおよび金属不純物を除去する。

## 【0006】

また、他の洗浄方法として、たとえば、特開平6-314679号公報(特許文献1)、特許第3261683号明細書(特許文献2)には、オゾン水を用いてSi基板の表面を酸化し、その後酸化膜を除去することによってSi基板上のパーティクルおよび金属不純物を除去する方法が開発されている。

20

## 【先行技術文献】

## 【特許文献】

## 【0007】

## 【特許文献1】特開平6-314679号公報

## 【特許文献2】特許第3261683号明細書

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0008】

30

SiCは、バンドギャップが大きく、また最大絶縁破壊電界および熱伝導率はSiと比較して大きい一方、キャリアの移動度はSiと同程度に大きく、電子の飽和ドリフト速度および耐圧も大きい。そのため、高効率化、高耐圧化、および大容量化を要求される半導体装置への適用が期待される。そこで、本発明者はSiC半導体を半導体装置に用いることに着目した。そして、本発明者は、より品質の高いSiC半導体装置を製造すべく、SiC半導体において、SiC半導体装置を構成する酸化膜を形成するための表面を清浄化することに着想した。

## 【0009】

しかし、上記の従来の洗浄方法をSiC半導体に適用すると、SiCはSiよりも熱的に安定な化合物であるので、SiC半導体の表面が酸化されにくいことを本発明者は初めて明らかにした。つまり、上記洗浄方法は、Siの表面を酸化することはできるが、SiCの表面を十分に酸化できない。このため、SiCの表面から、パーティクルや不純物を除去することができず、SiC表面を十分に清浄化することはできていない。SiC半導体の表面が清浄化されないと、清浄化されたSiC半導体上に酸化膜を形成することができないため、結果的に、製造されるSiC半導体装置の品質が低下してしまう。

40

## 【0010】

したがって、本発明の目的は、高品質なSiC半導体装置を製造する方法およびこの方法に用いられる製造装置を提供することである。

## 【課題を解決するための手段】

## 【0011】

50

高品質なSiC半導体装置を製造するために、SiC半導体の表面を清浄化することに着目して鋭意研究したところ、本発明の完成に至った。すなわち、本発明は、SiC半導体装置を製造する方法であって、少なくとも一部に不純物（ドーパント）が注入された第1の表面を含むSiC半導体を準備する工程と、SiC半導体の第1の表面を、水素ガスを含むガスを用いてドライエッティングすることにより、第2の表面を形成する工程と、第2の表面上に、SiC半導体装置を構成する酸化膜を形成する工程とを備える、SiC半導体装置の製造方法である。

## 【0012】

本発明のSiC半導体装置の製造方法によれば、SiC半導体の少なくとも一部に不純物が注入された第1の表面を水素ガスを含むガスを用いてドライエッティング（以下、「水素エッティング」ともいう。）する。これにより、第1の表面に付着していた不純物、パーティクルなどを除去することができ、清浄化された第2の表面を形成することができる。そして、この清浄化された第2の表面上に、SiC半導体装置を構成する酸化膜を形成することにより、高品質なSiC半導体装置を製造することができる。また、SiC半導体は、安定な化合物であるので、水素エッティングを行なっても、SiC半導体へのダメージが少ない。よって、表面特性が良好になるように、SiC半導体を清浄化することができる。したがって、高品質なSiC半導体装置を製造することができる。

10

## 【0013】

上記SiC半導体装置の製造方法において好ましくは、第2の表面を形成する工程後に、液相を用いた洗浄をせずに、酸化膜を形成する工程を実施する。

20

## 【0014】

これにより、第2の表面を形成する工程後に、液相を用いた洗浄をせずに、酸化膜を形成することができるため、液相を用いた洗浄に起因する不純物の付着を防ぐことができる。したがって、より高品質なSiC半導体装置を製造することができる。

20

## 【0015】

上記SiC半導体装置の製造方法において好ましくは、第2の表面を形成する工程において、水素エッティングを1300以上1650以下の温度範囲で行なう。

30

## 【0016】

水素エッティングを1300以上の温度で行なうことにより、エッティングレートを高めることができ、1650以下の温度で行なうことにより、エッティングレートが高くなりすぎることを抑制できるので、容易に制御できる。すなわち、水素エッティングを上記温度範囲内で行なうことにより、好適なエッティングレートに制御できるので、精度を高めて第1の表面をエッティングすることができるため、SiC半導体装置の品質をより高めることができる。

## 【0017】

上記SiC半導体装置の製造方法において好ましくは、酸化膜を形成する工程は、第2の表面上に珪素元素を含む膜を形成し、該珪素元素を含む膜を酸化することにより、酸化膜を形成する。

30

## 【0018】

本発明者は、SiC半導体の少なくとも一部に不純物（ドーパント）が注入された第2の表面は、不純物（ドーパント）濃度および不純物（ドーパント）の種類が異なるため、深さ方向の酸化レートにばらつきが生じ、結果的に、不均一な酸化膜が形成されることに着目し、上記発明を完成させた。Si元素を含む膜は第2の表面上に形成されるので、Si元素を含む膜の品質について第2の表面状態の影響を低減できる。このため、Si元素を含む膜の品質の均一化を図ることができる。したがって、SiC半導体装置の品質をさらに高めることができる。

40

## 【0019】

上記SiC半導体装置の製造方法において好ましくは、第2の表面を形成する工程において、ガスは塩化水素ガスをさらに含む。

## 【0020】

50

SiC半導体の第1の表面を水素エッティングする際に、水素ガスと共に塩化水素ガスを用いることによって、SiC半導体のエッティングレートを大きくすることができる。したがって、SiC半導体装置の製造タクトを短くすることができる。

【0021】

上記SiC半導体装置の製造方法において好ましくは、第2の表面を形成する工程において、ガスは炭化水素ガスをさらに含む。

【0022】

SiC半導体の第1の表面を水素エッティングする際に、水素ガスと共に炭化水素ガスを用いることによって、SiC半導体の表面モフォロジーを良好にすることができます。したがって、SiC半導体装置の品質をより高めることができます。

10

【0023】

上記SiC半導体装置の製造方法において好ましくは、第2の表面を形成する工程と酸化膜を形成する工程との間では、SiC半導体は大気が遮断された雰囲気内に配置される。

【0024】

これにより、清浄な第2の表面が形成されたSiC半導体を、大気にさらすことなく、次の工程のSiC半導体装置を構成する酸化膜を形成する工程に供することができます。このため、清浄化されたSiC半導体の表面が大気によって汚染されるのを防ぐことができ、SiC半導体装置の品質をさらに高めることができます。

【0025】

また、本発明は、SiC半導体において、少なくとも一部に不純物（ドーパント）が注入された第1の表面を水素ガスを含むガスを用いた水素エッティングによって除去するための除去部と、SiC半導体において第1の表面が除去されることにより形成された第2の表面にSiC半導体装置を構成する酸化膜を形成するための形成部と、SiC半導体を搬送可能に除去部と形成部とを接続する接続部とを備え、接続部におけるSiC半導体を搬送させる領域は、大気の遮断が可能であるSiC半導体装置の製造装置である。

20

【0026】

この製造装置によれば、SiC半導体において、少なくとも一部に不純物が注入された第1の表面を除去部で水素エッティングすることができる。そして、除去部で水素エッティングされた後のSiC半導体を、大気から遮断された雰囲気下の接続部を介して形成部へと搬送することができる。さらに、形成部において、第2の表面に、SiC半導体装置を構成する酸化膜を形成することができる。すなわち、水素エッティングによってSiC半導体を清浄化する工程から酸化膜を形成する工程までの一連の工程を大気から遮断された状態で行なうことができる。したがって、この製造装置によれば、高品質のSiC半導体装置を製造することができる。

30

【発明の効果】

【0027】

以上説明したように、本発明のSiC半導体装置の製造方法およびこれに用いる製造装置によれば、SiC半導体の清浄化を発現できるSiC半導体の洗浄方法を用いて、高品質なSiC半導体装置を製造することができる。

40

【図面の簡単な説明】

【0028】

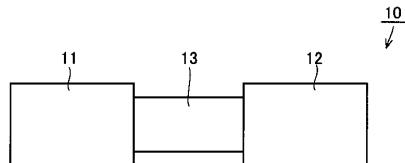

【図1】本発明の実施の形態1におけるSiC半導体装置の製造装置の模式図である。

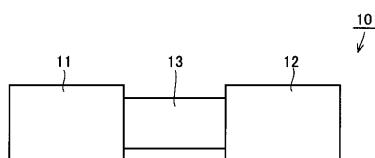

【図2】本発明の実施の形態1におけるSiC半導体装置の製造方法を示すフローチャートである。

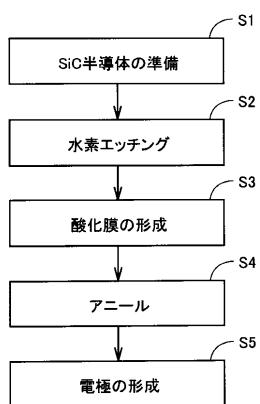

【図3】本発明の実施の形態1において準備するSiC半導体を概略的に示す断面図である。

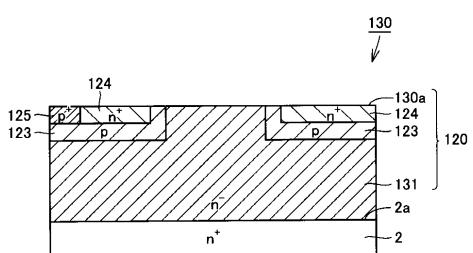

【図4】本発明の実施の形態1において準備するSiC半導体の作製工程を説明するための図である。

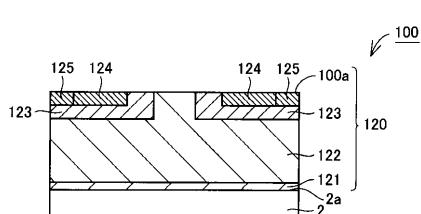

【図5】本発明の実施の形態1において酸化膜が形成されたSiC半導体を概略的に示す

50

断面図である。

【図6】本発明の実施の形態1においてソースコンタクト電極およびドレイン電極が形成されたSiC半導体を概略的に示す断面図である。

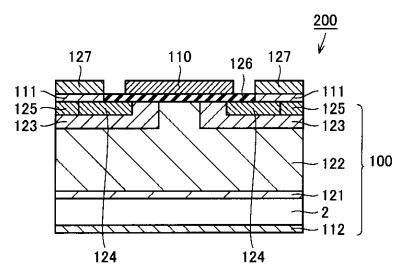

【図7】本発明の実施の形態1において製造されるSiC半導体装置を概略的に示す断面図である。

【図8】本発明の実施の形態2においてSiC半導体の主面上に半導体膜が形成されたSiC半導体を概略的に示す断面図である。

【図9】実施例1、比較例1および比較例2で用いるエピタキシャルウエハを概略的に示す断面図である。

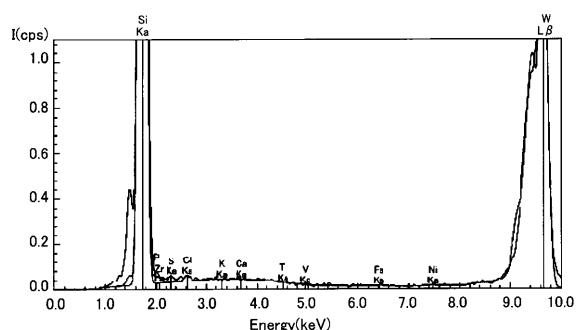

【図10】比較例1のSiC半導体の表面をTXRFで測定した結果を示すスペクトルである。 10

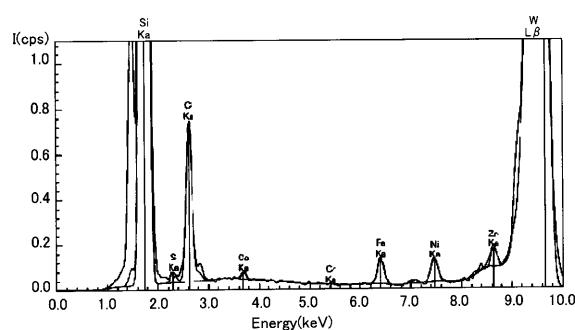

【図11】比較例2のSiC半導体の表面をTXRFで測定した結果を示すスペクトルである。

#### 【発明を実施するための形態】

##### 【0029】

以下、図面に基づいて本発明の実施の形態を説明する。なお、以下の図面において同一または相当する部分には、同一の参照符号を付し、その説明は繰り返さない。

##### 【0030】

###### (実施の形態1)

図1は、本発明の実施の形態1におけるSiC半導体装置の製造装置の模式図である。 20

図1を参照して、本発明の一実施の形態におけるSiC半導体装置の製造装置を説明する。

##### 【0031】

図1に示すように、SiC半導体装置の製造装置10は、除去部11と、形成部12と、接続部13とを備えている。除去部11と形成部12とは、接続部13により接続されている。除去部11、形成部12および接続部13の内部は大気から遮断されており、内部は互いに連通可能である。

##### 【0032】

除去部11は、SiC半導体における少なくとも一部に不純物が注入された第1の表面を水素エッチングすることで、第2の表面を形成する。除去部11には、水素エッチング装置が用いられる。除去部11で用いる水素エッチング装置は、特に限定されず、たとえば、高周波加熱炉などを用いることができる。 30

##### 【0033】

形成部12は、第2の表面上にSiC半導体装置を構成する酸化膜を形成する。形成部12には、酸化膜形成装置が用いられる。形成部12で用いる酸化膜形成装置は、特に限定されず、たとえば、ドライ酸化(熱酸化)装置、スパッタ装置、およびCVD(Chemical Vapor Deposition: 化学蒸着)装置、水蒸気を含む酸素雰囲気中で加熱するウェット酸化装置、パイロジェニック酸化装置を用いることができ、ドライ酸化装置を用いることが好ましい。

##### 【0034】

接続部13は、SiC半導体を搬送可能に除去部11と形成部12とを接続する。接続部13においてエピタキシャルウエハ100を搬送させる領域(内部空間)は、大気の遮断が可能である。 40

##### 【0035】

ここで、大気の遮断(大気を遮断した雰囲気)とは、大気が混入しない雰囲気を意味し、たとえば窒素ガス、水素ガスおよび不活性ガスの少なくとも1種類のガスよりなる雰囲気、または真空である。具体的には、大気を遮断した雰囲気は、たとえば窒素(N<sub>2</sub>)、水素(H<sub>2</sub>)、ヘリウム(He)、ネオン(Ne)、アルゴン(Argon)、クリプトン(Kr)、キセノン(Xe)、ラドン(Rn)、またはこれらの組み合わせからなるガスが充填された雰囲気、または真空である。 50

## 【0036】

接続部13は、除去部11の内部と形成部12の内部とを連結している。接続部13は、除去部11から搬出されるSiC半導体を形成部12へ搬送するための空間を内部に有する。つまり、接続部13は、SiC半導体を大気に開放しないように、除去部11から形成部12へ搬送するために設置されている。

## 【0037】

接続部13は、内部でSiC半導体が搬送可能であるような大きさを有する。また接続部13は、SiC半導体をサセプタに載置した状態で搬送可能である大きさを有していてもよい。接続部13は、たとえば除去部11の出口と、形成部12の入口とを連結するコードロック室である。

10

## 【0038】

また、製造装置10は、接続部13の内部に配置されるとともに、SiC半導体を除去部11から形成部12へ搬送するための第1の搬送部をさらに備えていてもよい。製造装置10は、形成部12でゲート酸化膜126を形成したSiC半導体を、製造装置10の外部へ取り出す、あるいは電極を形成する電極形成部へ大気を遮断した雰囲気で搬送するための第2の搬送部をさらに備えていてもよい。第1の搬送部と第2の搬送部とは、同一であっても異なっていてもよい。

## 【0039】

また、製造装置10は、除去部11と接続部13との間に配置され、かつ除去部11の内部と接続部13の内部とを遮断するための遮断部をさらに備えていてもよい。また、製造装置10は、形成部12と接続部13との間に配置され、かつ形成部12の内部と接続部13の内部とを遮断するための遮断部をさらに備えていてもよい。遮断部は、たとえばそれぞれの連通部を塞ぐことが可能な弁や扉などを用いることができる。

20

## 【0040】

また、製造装置10は、内部の雰囲気ガスを排出するための真空ポンプや、内部の雰囲気ガスを置換するための置換ガスボンベをさらに備えていてもよい。真空ポンプや置換ガスボンベは、除去部11、形成部12および接続部13のそれぞれに接続されていてもよく、少なくともいずれか1つに接続されていてもよい。

## 【0041】

なお、製造装置10は、上記以外の様々な要素、たとえば酸化膜上に電極を形成するための電極形成部を含んでいてもよいが、説明の便宜上、これらの要素の図示および説明は省略する。

30

## 【0042】

また、図1では、接続部13として除去部11と形成部12との間のみを連結する形状を示したが、特にこれに限定されない。たとえば接続部13として、たとえば大気を遮断したチャンバを用い、このチャンバ内に除去部11および形成部12が配置されていてよい。

## 【0043】

続いて、図1～図7を参照して、本実施の形態におけるSiC半導体装置の製造方法について説明する。図2は、本発明の実施の形態1におけるSiC半導体装置の製造方法を示すフローチャートである。図3～図6は、本発明の実施の形態1におけるSiC半導体装置の製造方法の各工程で形成されるSiC半導体の構成を示す図である。具体的には、図3は、準備するSiC半導体を概略的に示す断面図であり、図4は、準備するSiC半導体の作製工程を説明するための図である。図5は、酸化膜が形成されたSiC半導体を概略的に示す断面図であり、図6は、ソースコンタクト電極およびドレイン電極が形成されたSiC半導体を概略的に示す断面図である。そして、図7は、本発明の実施の形態1において製造されるSiC半導体装置を概略的に示す断面図である。本実施の形態では、SiC半導体として、図7に示すSiC半導体装置200を製造する方法を説明する。また、本実施の形態では、図1に示すSiC半導体装置の製造装置10を用いる。

40

## 【0044】

50

図2および図3に示すように、まず、少なくとも一部に不純物が注入された第1の表面100aを含むSiC半導体としてのエピタキシャルウェハ100を準備する(ステップS1)。本工程では、SiC半導体として、図2に示すように、SiC基板2の表面2a上に、不純物が注入された領域を有するエピタキシャル層120が形成されたエピタキシャルウェハ100を準備する。上記SiC基板2は、特に限定されないが、たとえば以下の方法により準備することができる。

#### 【0045】

具体的には、たとえば、昇華法、CVD法などの気相成長法、液相成長法などにより成長されたSiCインゴットを準備する。その後、SiCインゴットから表面を有するSiC基板を切り出す。切り出す方法は特に限定されず、SiCインゴットからスライスなどによりSiC基板を切り出す。

10

#### 【0046】

次いで、切り出したSiC基板の表面を研磨する。研磨する面は、表面のみでもよく、表面と反対側の裏面をさらに研磨してもよい。研磨する方法は特に限定されないが、表面を平坦にするとともに、傷などのダメージを低減するために、たとえばCMP(Chemical Mechanical Polishing: 化学機械研磨)を行なう。CMPでは、研磨剤としてコロイダルシリカ、固定剤として接着剤、ワックスなどを用いる。なお、CMPと併せて、あるいは代わりに、電界研磨法、化学研磨法、機械研磨法などの他の研磨をさらに行なってよい。また研磨を省略してもよい。以上の操作により、表面2aを有するSiC基板2を準備することができる。このようなSiC基板2として、たとえば導電型がn型であり、抵抗が0.02cmの基板を用いる。

20

#### 【0047】

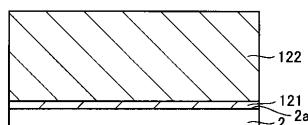

また、上記SiC基板2上のエピタキシャル層120は、たとえば以下の方法により形成することができる。まず、図4に示すように、SiC基板2の表面2a上に、バッファ層121を形成する。バッファ層121は、たとえば導電型がn型のSiCからなり、たとえば厚さが0.5μmのエピタキシャル層である。またバッファ層121におけるn型の導電性不純物の濃度は、たとえば $5 \times 10^{17} \text{ cm}^{-3}$ である。その後、バッファ層121上にドリフト層122を形成する。ドリフト層122として、気相成長法、液相成長法などにより、導電型がn型のSiCからなる層を形成する。ドリフト層122の厚さは、たとえば10μmである。またドリフト層122におけるn型の導電性不純物の濃度は、たとえば $5 \times 10^{15} \text{ cm}^{-3}$ である。

30

#### 【0048】

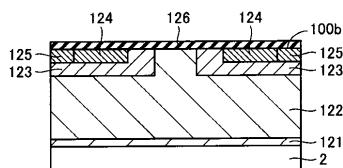

次に、エピタキシャル層に不純物を注入する。本実施の形態では、図3に示すように、pボディ領域123と、nソース領域124と、p<sup>+</sup>領域125とを、以下のように形成する。まず導電型がp型の不純物をドリフト層122の一部に選択的に注入することで、ボディ領域123を形成する。その後、n型の導電性不純物を所定の領域に選択的に注入することによってソース領域124を形成し、また導電型がp型の導電性不純物を所定の領域に選択的に注入することによってp<sup>+</sup>領域125を形成する。なお導電性不純物の選択的な注入は、たとえば酸化膜からなるマスクを用いて行なわれる。

40

#### 【0049】

上記の不純物の注入工程において、各注入プロファイルは、後述するステップS2における水素エッチングによって除去される厚みが考慮される。つまり、水素エッチングするステップS42においてエピタキシャル層の第1の表面を除去したときに、上記不純物拡散領域が所望の配置になるように、イオン注入を制御する。

#### 【0050】

このような注入工程の後、活性化アニール処理が行なわってよい。たとえば、アルゴン雰囲気中、加熱温度1700で30分間のアニールが行なわれる。

#### 【0051】

これらの工程により、SiC基板2と、SiC基板2上に形成されたエピタキシャル層120とを備えたエピタキシャルウェハ100を準備することができる。

50

## 【0052】

図2に戻り、次に、準備されたエピタキシャルウェハ100の第1の表面100aを水素エッチングすることにより、第2の表面を形成する(ステップS2)。本実施の形態のステップS2では、図1に示す製造装置10の除去部11で第2の表面を形成する。

## 【0053】

このステップS2を実施すると、エピタキシャル層120の第1の表面100aが水素エッチングされ、これにより、第1の表面100aに付着している不純物、パーティクルなどを第1の表面100aと共に除去することができる。そして、エピタキシャルウェハ100において、不純物、パーティクルなどが除去されることによって清浄な第2の表面100bが形成される。

10

## 【0054】

ステップS2において、容易に制御されるエッチング量のため、エッチング深さ(第1の表面100aからSiC基板2に向けた方向のエッチング量)は、0.1μm以上0.5μm以下であることが好ましい。

## 【0055】

また、不純物、パーティクルなどの除去という観点からは、エッチング深さは1分子層以上10nm以下であることが好ましい。この範囲の厚みで第1の表面100aを水素エッチングすることによって、第1の表面100aに付着している不純物、パーティクルなどを確実に除去し、清浄化された第2の表面100bを形成することができる。

20

## 【0056】

また、上述した注入工程によってSi半導体の表面領域がダメージを受けて荒れことがあるが、たとえば、エッチング深さを10nmより大きく500nm以下にすることによって、不純物、パーティクルなどを除去するとともに荒れた表面領域を除去することができる。したがって、この範囲の厚みで第1の表面100aを水素エッチングすることによって、表面特性の良好な第2の表面100bを形成することができる。

## 【0057】

また、水素エッチングを1300以上の温度で行なうことにより、エッチングレートを高めるが、1650以下の温度で行なうことにより、エッチングレートが高くなりすぎることを抑制できるので、容易に制御できる。したがって、水素エッチングの温度条件を1300以上1650以下に調整することによって、好適なエッチングレートに制御できるので、精度を高めて第1の表面をエッチングすることができるため、SiC半導体装置の品質をより高めることができる。このような温度設定は、たとえば、エッチング装置内に配置されたエピタキシャルウェハ100を1300以上1650以下に加熱する、1300以上1650以下のエッチング用のガス(以下、「エッチングガス」という。)を装置内に導入する、または装置内を1300以上1650以下に保持することで可能となる。なお、これらを組み合わせても良い。

30

## 【0058】

また、水素エッチング時の水素ガスの流量は特に制限されないが、数百slm(standard liter per minute)程度であることが好ましく、水素エッチング時の圧力は数十hPa～数百hPa程度であることが好ましい。この場合、好ましい速度でエッチングを行なうことが可能となる。

40

## 【0059】

また、エッチングガスとして、水素ガスと他のガスとの混合ガスを用いてもよい。特に、水素ガスに塩化水素(HCl)ガスを混合した混合ガスを用いることが好ましい。このような混合ガスを用いることによって、エッチングレートを大きくすることができる。混合ガス中の塩化水素ガスの含有率が高すぎると、エッチングレートが大きくなりすぎ、エッチングの制御が困難となるため、混合ガス中の塩化水素ガスの含有率は10%以下であることが好ましく、塩化水素ガスと水素ガスとからなる混合ガス中の塩化水素ガスの含有率(塩化水素ガス/(塩化水素ガス+水素ガス)×100)が10%以下であることがより好ましい。

50

## 【0060】

また、水素ガスに炭化水素ガスを混合した混合ガスを用いてもよい。このような混合ガスを用いることによって、エピタキシャルウェハ100の表面モフォロジーを良好にしながらエッチングすることができ、表面状態の良好な第2の表面を形成することができる。炭化水素としては、アルカン、アルケンなどの低級炭化水素を用いることができ、たとえば、アセチレン( $C_2H_2$ )やプロパン( $C_3H_8$ )などを用いることができる。このような炭化水素ガスは、Siの液滴が生じるのを抑える効果を効果的に発揮するために、1000 ppm以下で混合させることが好ましい。また、当然に、水素ガス、塩化水素ガス、炭化水素ガスそれぞれを混合した混合したガスをエッチングガスとしてもよい。

## 【0061】

次に、図1を参照して、除去部11で第2の表面100bを形成したエピタキシャルウェハ100を、形成部12へ搬送する。このとき、エピタキシャルウェハ100は大気が遮断された雰囲気である接続部13内で搬送される。言い換えると、第2の表面100bを形成するステップS2とゲート酸化膜126を形成するステップS3との間では、エピタキシャルウェハ100は、大気が遮断された雰囲気内に配置される。これにより、清浄化された第2の表面100bが形成された後に、該第2の表面100bに大気に含まれる不純物が付着することを抑制できる。

## 【0062】

また、図1に示す製造装置10を用いることにより、第2の表面100bを形成する工程(ステップS2)の後に、液相を用いた洗浄をせずに、後述する酸化膜を形成するステップS3を実施することができる。これにより、液相を用いた洗浄に起因する不純物(特に重金属イオン、アルカリイオン)の付着を抑制できる。なお、液相を用いた洗浄とは、SiC半導体としてのエピタキシャルウェハ100を液相中で洗浄することを意味し、意図しない気相成分を含んでいてもよい。

## 【0063】

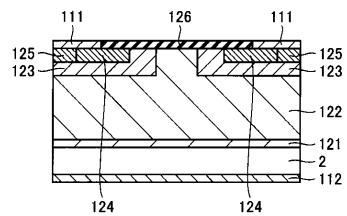

次に、図2および図5に示すように、第2の表面100b上に、SiC半導体装置200を構成するゲート酸化膜126を形成する(ステップS3)。

## 【0064】

このステップS3では、酸化膜を形成する公知の方法を用いることができる。公知の方法としては、たとえば、ドライ酸化法、スパッタ法、CVD法、ウエット酸化法、パイロジェニック酸化法などが挙げられる。

## 【0065】

ステップS3において、第2の表面100bは清浄化されているため、ゲート酸化膜126の絶縁特性を向上できるとともに、エピタキシャルウェハ100とゲート酸化膜126との界面やゲート酸化膜126中に存在する不純物、パーティクルなどを低減することができる。したがって、SiC半導体装置200の逆方向電圧印加時の耐圧を向上できるとともに、順方向電圧印加時の動作の安定性および長期信頼性を向上することができる。

## 【0066】

次に、図2に示すように、ゲート酸化膜126をアニール処理する(ステップS4)。このステップS4では、たとえば、ゲート酸化膜126に対して、窒化処理と、不活性ガスアニール処理とを行なうことができる。

## 【0067】

窒化処理は、窒素元素を含む雰囲気で熱処理する。窒化処理として、たとえば、一酸化窒素(NO)雰囲気中または二窒化酸素( $N_2O$ )雰囲気中、加熱温度1200で120分間のアニールを行なうことができる。これにより、エピタキシャル層120とゲート酸化膜126との界面を含む領域に、当該領域に隣接する領域に比べて窒素濃度の高い高窒素濃度領域(不図示)が形成される。

## 【0068】

不活性ガスアニール処理は、不活性ガスを含む雰囲気で熱処理する。不活性ガスアニール処理として、たとえば、アルゴン(Ar)などの不活性ガス雰囲気中、加熱温度110

10

20

30

40

50

0 で 60 分間のアニールを行なうことができる。

【0069】

上記窒化処理および不活性ガスアニール処理を行なった場合、SiC半導体装置200において、高いチャネル移動度を再現性良く実現することができる傾向が大きくなる。なお、窒化処理および不活性ガスアニール処理のいずれかのみを行なってもよく、本工程(ステップS4)が省略されてもよい。

【0070】

次に、図2および図7に示すように、ゲート酸化膜126が形成されたエピタキシャルウエハ100に対して、ゲート電極110、ソース電極127およびドレイン電極112を形成する(ステップS5)。

10

【0071】

ゲート電極110およびソース電極127は、たとえば以下の方法により形成することができる。すなわち、フォトリソグラフィ法によりゲート酸化膜126上にパターンを有するレジスト膜を形成する。このレジスト膜をマスクとして用いて、ゲート酸化膜126を部分的に除去し、その後、公知の方法、たとえば蒸着法によって金属からなる導電膜を形成する。次に、上記レジスト膜を除去(リフトオフ)することにより、レジスト膜上の導電膜を除去してソースコンタクト電極111を形成する(図6参照)。その後、ソース電極127を公知の方法、たとえば蒸着法によってソースコンタクト電極111上に形成し、ゲート電極110を公知の方法、たとえば蒸着法によってゲート酸化膜126上に形成する。また、ドレイン電極112は、SiC基板2の表面2aと反対の面に、公知の方法、たとえば蒸着法によって形成することができる。以上の工程(ステップS1～S5)を実施することにより、図7に示すSiC半導体装置200が製造される。

20

【0072】

ここで、本実施の形態では、ステップS2とステップS3との間では、ウエット洗浄など他の洗浄をしない方法を例に挙げて説明したが、特に限定されず、ウエット洗浄、ドライ洗浄などの他の洗浄をしてもよい。他の洗浄をする場合には、エピタキシャルウエハ100を搬送する際に、大気が遮断された雰囲気内に配置することが好ましい。

30

【0073】

なお、ステップS1後に必要に応じて、薬液での洗浄工程、純水リノス工程、乾燥工程などを追加して実施してもよい。薬液は、たとえば硫酸と過酸化水素水とを含むSPMが挙げられる。ステップS2前にSPMで洗浄する場合には有機物を除去することもできる。また、ステップS2前にRCA洗浄などを行なってもよい。

【0074】

以上説明したように、本実施の形態におけるSiC半導体装置の製造方法は、少なくとも一部に不純物が注入された第1の表面100aを含むエピタキシャルウエハ100を準備する工程(ステップS1)と、エピタキシャルウエハ100の第1の表面100aを水素エッティングすることにより、第2の表面100bを形成する工程(ステップS2)と、第2の表面100b上にSiC半導体装置200を構成するゲート酸化膜126を形成する工程(ステップS3)とを備える。

40

【0075】

本発明者は、上記従来の洗浄方法をエピタキシャルウエハ100に適用すると、SiCがSiよりも安定な化合物であるために、エピタキシャルウエハ100の表面が酸化されにくく、そのため、エピタキシャルウエハ100の表面を十分に清浄化できないことを初めて明らかにした。

【0076】

しかし、エピタキシャルウエハ100は化学的に安定していることに本発明者は着目して、Siではダメージが生じる方法をエピタキシャルウエハ100に用いても、エピタキシャルウエハ100にはダメージが生じにくいことを見い出した。そこで、エピタキシャルウエハ100の表面を清浄化する条件を鋭意研究した結果、上述した本実施の形態におけるエピタキシャルウエハ100の製造方法を本発明者は見い出した。

50

## 【0077】

したがって、本実施の形態では、ステップS2においてエピタキシャルウエハ100の第1の表面100aを水素エッチングすることによって、第1の表面100aに付着していた不純物、パーティクルなどを除去し、清浄化された第2の表面100bを形成することができる。さらに、ステップS3によって、イオン注入され、かつ清浄化された第2の表面100b上にゲート酸化膜126を形成することができるため、半導体デバイスにおけるゲート酸化膜126の絶縁特性を向上できるとともに、エピタキシャルウエハ100とゲート酸化膜126との界面やゲート酸化膜126中に存在する不純物、パーティクルなどを低減することができる。したがって、SiC半導体装置200の逆方向電圧印加時の耐圧を向上できるとともに、順方向電圧印加時の動作の安定性および長期信頼性を向上することができる。このように、本実施の形態に係るSiC半導体装置の製造方法によれば、高品質のSiC半導体装置200を製造することができる。さらに、水素エッチングによるエピタキシャルウエハ100のダメージは少ないため、表面特性が良好な第2の表面100bを形成することができる。したがって、結果的に、高品質のSiC半導体装置200を製造することができる。

10

## 【0078】

また、イオン注入工程や活性化アニール処理により第1の表面100aがダメージを受けた場合、従来は、液相を用いた洗浄によって、犠牲酸化膜の形成および犠牲酸化膜の除去が行われていた。この液相を用いた洗浄によって第1の表面100aに形成されたダメージ層を除去するには、15時間程度の洗浄時間が必要とされていた。これに対し、液相を用いた洗浄を含まない水素エッチングでは、4時間程度で第1の表面100aに形成されたダメージ層を、パーティクル、不純物などとともに除去することができる。したがって、本実施の形態に係るSiC半導体装置の製造方法において、ステップS2とステップS3との間に液相を用いた洗浄を行なわないことによって、製造タクトを短縮することができる。

20

## 【0079】

なお、「第2の表面100bを形成する工程（ステップS2）の後に、液相を用いた洗浄をせずに、ゲート酸化膜126を形成する工程（ステップS3）を実施する」とは、ステップS2とステップS3との間に液相を用いた洗浄工程を含まないことを意味し、ステップS2とステップS3との間とが断続的に行なわれても（時間が経過していても）よい。また、ステップS2とステップS3とを連続して行なってもよい。

30

## 【0080】

また、本発明者は、鋭意検討を重ねたところ、エピタキシャルウエハ100を液相を用いて洗浄した場合、エピタキシャルウエハ100の洗浄が不十分であるだけでなく、かえって不純物を付着させてしまうことを明らかにした。

## 【0081】

したがって、本実施の形態に係るSiC半導体装置の製造方法において、第2の表面100bを形成する工程（ステップS2）の後に、液相を用いた洗浄をせずに、ゲート酸化膜126を形成する工程（ステップS3）を実施することが好ましい。第2の表面100bを形成する工程後に、液相を用いた洗浄をせずに、ゲート酸化膜126を形成することによって、液相を用いた洗浄に起因する不純物の付着を防ぐことができる。これにより、より高品質なSiC半導体装置200を製造することができる。

40

## 【0082】

本実施の形態に係るSiC半導体装置の製造方法は、清浄化されたエピタキシャルウエハの表面に酸化膜を形成することで酸化膜の特性を向上できるので、酸化膜を有する半導体デバイスに好適に用いることができる。したがって、本実施の形態では、MOSFETを製造する場合について説明したが、他に、IGBT（Insulated Gate Bipolar Transistor：絶縁ゲートバイポーラトランジスタ）などの絶縁ゲート型電界効果部を有する半導体デバイスや、JFET（Junction Field-Effect Transistor：接合電界効果トランジスタ）などに好適に用いることができる。

50

## 【0083】

(実施の形態2)

図8は、本発明の実施の形態2においてSiC半導体の主面上に半導体膜が形成されたSiC半導体を概略的に示す断面図である。図2～図8を参照して、実施の形態2のSiC半導体装置の製造方法を説明する。

## 【0084】

まず、図2および図3に示すように、SiC基板2の表面2a上に、不純物(ドーパント)が注入された領域を有するエピタキシャル層120が形成されたエピタキシャルウエハ100を準備する(ステップS1)。ステップS1は実施の形態1と同様であるため、その説明は繰り返さない。

10

## 【0085】

次に、図2に示すように、準備されたエピタキシャルウエハ100の第1の表面100aを水素エッチングすることにより、第2の表面100bを形成する(ステップS2)。ステップS2は実施の形態1と同様であるため、その説明は繰り返さない。

## 【0086】

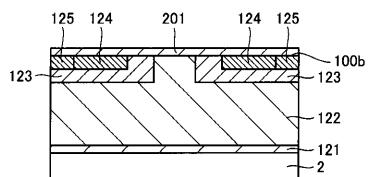

次に、図2および図8に示すように、エピタキシャルウエハ100の正面である第2の表面100b上に珪素(Si)元素を含む半導体膜201を形成し、その後、図5に示すように、当該半導体膜201を酸化してゲート酸化膜126を形成する(ステップS3)。

## 【0087】

第2の表面100b上にSi元素を含む半導体膜201を形成する方法には、公知のエピタキシャル成長法、たとえば、CVD法を用いることができる。

20

## 【0088】

本工程において、Siからなる半導体膜201を形成してもよく、炭化珪素(SiC)からなる半導体膜201を形成してもよい。半導体膜201がSiである場合、エピタキシャルウエハ100とゲート酸化膜126との界面やゲート酸化膜126中に炭素が存在することを抑制できるので、製造する半導体装置の品質をより高めることができる。半導体膜201がSiCである場合、下地のエピタキシャル層120と形成する半導体膜201との結晶が同じであるため、半導体膜201を容易に形成することができる。

30

## 【0089】

このステップS3では、ゲート酸化膜126の厚みを決定し、半導体膜201をすべて酸化したとき(半導体膜201下のエピタキシャルウエハ100を酸化させずに)に、決定したゲート酸化膜126の厚みになるように、半導体膜201の厚みを制御することが好ましい。つまり、半導体膜201をすべて酸化してなるゲート酸化膜126の厚みに応じて、半導体膜201の厚みを決定することが好ましい。これは、たとえば、半導体膜201が酸化されてゲート酸化膜126となる際に、酸素(O)を取り込むことによる膜厚の増加が生じることを考慮して、半導体膜201の厚みを計算などにより制御することで実現する。

## 【0090】

たとえば、半導体膜201がSiからなる場合、所望の酸化膜の厚さの0.44倍程度の厚さとなるように形成することが好ましい。このように半導体膜201の厚みを設計することによって、半導体膜201が酸化されてゲート酸化膜126となる場合に、酸素を取り込むことによる膜厚の増加が生じても、ゲート酸化膜126の厚みを設計の厚みとすることができる。また、このとき、イオン注入されたエピタキシャルウエハ100の不純物を含まないように、エピタキシャルウエハ100を酸化させずに、半導体膜201のみを酸化して、ゲート酸化膜126を形成することが好ましい。これにより、エピタキシャルウエハ100のイオン注入プロファイルへの影響を低減することができる。

40

## 【0091】

半導体膜201の酸化の方法は特に限定されず、たとえば、ドライ酸化法、ウェット酸化法、パイロジェニック酸化法などを用いることができる。

50

## 【0092】

次に、図2に示すように、ゲート酸化膜126をアニール処理する(ステップS4)。ステップS4は、実施の形態1と同様であるため、その説明は繰り返さない。

## 【0093】

次に、図2および図7に示すように、ゲート酸化膜126が形成されたエピタキシャルウエハ100に対して、ゲート電極110、ソース電極127およびドレイン電極112を形成する(ステップS5)。ステップS5は、実施の形態1と同様であるため、その説明は繰り返さない。以上の工程(ステップS1~S5)を実施することにより、図7に示すSiC半導体装置200が製造される。

## 【0094】

以上説明したように、本実施の形態におけるSiC半導体装置の製造方法は、少なくとも一部に不純物が注入された第1の表面100aを含むエピタキシャルウエハ100を準備する工程(ステップS1)と、エピタキシャルウエハ100の第1の表面100aを水素エッチングすることにより、第2の表面100bを形成する工程(ステップS2)と、第2の表面100b上にSiC半導体装置200を構成するゲート酸化膜126を形成する工程(ステップS3)とを備える。そして、ゲート酸化膜126を形成する工程(ステップS3)は、第2の表面100b上にSi元素を含む半導体膜201を形成し、半導体膜201を酸化することにより、ゲート酸化膜126を形成する。

10

## 【0095】

本発明者は、少なくとも一部に不純物が注入された第2の表面100bを酸化してゲート酸化膜126を形成する際に、ゲート酸化膜126が均一に形成されない場合があることに着目した。具体的には、イオン注入領域を有する第2の表面100bは、不純物が注入されている領域と不純物が注入されていない領域とがある。また、不純物が注入されている領域においても、注入される不純物が異なり、またその濃度も異なっている。不純物の濃度、不純物の種類によってSiC半導体の酸化レートは異なるため、上記のような第2の表面100bを有するエピタキシャルウエハ100を酸化する場合、面内の各位置において、深さ方向の酸化レートにばらつきが生じてしまう。

20

## 【0096】

そこで、本発明者はゲート酸化膜126を均一に形成するために、さらに鋭意検討を重ねたところ、第2の表面100b上にSi元素を含む膜を形成し、これを酸化してゲート酸化膜126を形成することによって、均一なゲート酸化膜126が形成できることを見い出した。

30

## 【0097】

したがって、本実施の形態では、ステップS2においてエピタキシャルウエハ100の第1の表面100aを水素エッチングして第2の表面100bを形成した後、第2の表面100b上にSi元素を含む半導体膜201を形成する。そして、この半導体膜201を酸化してゲート酸化膜126にする。これにより、清浄化された第2の表面100bに、第2の表面100bの不純物の濃度や種類に依存せずに、半導体膜201を形成できる。また半導体膜201には不純物が注入されていないため、半導体膜201の品質は均一となり、半導体膜201の面内の各位置における深さ方向の酸化レートは均一となる。したがって、清浄な第2の表面100b上に、より均一な品質のゲート酸化膜126を形成することができ、SiC半導体装置200の品質をより向上することができる。

40

## 【0098】

このように、本実施の形態によれば、ゲート酸化膜126の絶縁特性を向上できるとともに、エピタキシャルウエハ100とゲート酸化膜126との界面やゲート酸化膜126中に存在する不純物、パーティクルなどを低減することができる。さらに、ゲート酸化膜126の品質の均一性を向上することができる。したがって、SiC半導体装置200の品質をより向上することができる。

## 【0099】

本実施の形態において、図1の製造装置10を用いる場合には、除去部11および形成

50

部12のいずれかに、Si元素を含む半導体膜201を形成する装置、好ましくはCVD装置が含まれる。なお、当該半導体膜201を形成する装置を設ける位置は、除去部11内または形成部12に限られず、たとえば、除去部11と接続部13との間、または接続部13と形成部12との間に別途設けられてもよい。この場合、半導体膜201を形成する装置の内部と連結する他の部との間で、エピタキシャルウェハ100が大気に遮断された雰囲気内に配置されることが好ましい。

#### 【0100】

これにより、第2の表面100bを大気にさらすことなく、半導体膜201を形成することができ、また、半導体膜201を大気にさらすことなく酸化することができる。したがって、より高品質なSiC半導体装置200を製造することができる。

10

#### 【実施例】

##### 【0101】

###### (実施例1)

本実施例1では、SiC半導体として、図9に示すエピタキシャルウェハ130を用い、該エピタキシャルウェハ130の第1の表面130aを水素エッチングして清浄化することの効果について調べた。なお、図9は、実施例1、比較例1および比較例2で用いるエピタキシャルウェハを概略的に示す断面図である。

##### 【0102】

具体的には、まず、SiC基板2として、表面2aを有する4H-SiC基板を準備した。次に、エピタキシャル層120を構成する層として、 $10\text{ }\mu\text{m}$ の厚みを有し、 $1 \times 10^{16}\text{ cm}^{-3}$ の不純物濃度を有するn型SiC層131をCVD法により成長した。

20

##### 【0103】

次に、 $\text{SiO}_2$ をマスクとして用いて、アルミニウム(A1)をp型不純物として $2 \times 10^{16}\text{ cm}^{-3}$ のドーパント濃度を有するpボディ領域123を形成し、さらに、リン(P)をn型不純物として $1 \times 10^{19}\text{ cm}^{-3}$ の不純物濃度を有するn<sup>+</sup>ソース領域124を形成した。また、アルミニウム(A1)をp型不純物として $1 \times 10^{19}\text{ cm}^{-3}$ の不純物濃度を有するp<sup>+</sup>領域125を形成した。

##### 【0104】

次に、活性化アニール処理を行なった。この活性化アニール処理としては、Arガスを雰囲気ガスとして用いて、加熱温度1700～1800、加熱時間30分の条件とした。これにより、第1の表面130aを有するエピタキシャルウェハ130を準備した(ステップS1)。

30

##### 【0105】

次に、準備されたエピタキシャルウェハ100の主面の第1の表面130aを水素エッチングによって除去した(ステップS2)。

##### 【0106】

具体的には、エピタキシャルウェハ130を反応炉内に収容し、該エピタキシャルウェハ130を1300以上1650以下に制御された載置台で加熱しながら、第1の表面130aを水素エッチングした。水素エッチングの条件は、反応炉内に導入される水素ガスの流量が50～200s1mであり、炉内圧力が20～150hPaであり、反応時間は1時間とした。

40

##### 【0107】

###### (比較例1)

比較例1は、基本的には実施例1と同様であったが、ステップS2の水素エッチングを行なわなかった点において異なっていた。すなわち、比較例1では、ステップS1で準備したエピタキシャルウェハ130に対しては、洗浄処理を行わなかった。

##### 【0108】

###### (比較例2)

比較例2は基本的には実施例1と同様であったが、ステップS2において、水素エッチングのかわりに液相を用いた薬液洗浄によってSiC半導体の表面を洗浄した点において

50

異なっていた。液相として、硫酸 (H<sub>2</sub>SO<sub>4</sub>) : 過酸化水素水 (H<sub>2</sub>O<sub>2</sub>) を 5 : 1 の体積比で混合した混合溶液 1 と、アンモニア水 : 過酸化水素水 : 純水を 1 : 1 : 5 の体積比で混合した混合溶液 2 と、塩化水素 (HCl) : 過酸化水素 : 純水を 1 : 1 : 6 の体積比で混合した混合溶液 3 と、10 % のフッ化水素 (HF) 溶液を用いた。すなわち、比較例 2 では、準備したエピタキシャルウエハ 130 を混合溶液 1 に 0.5 時間浸漬した後、混合溶液 2 に 10 分間浸漬し、HF 溶液に 10 分間浸漬し、混合溶液 3 に 10 分間浸漬し、混合溶液 2 に 10 分間浸漬し、HF 溶液に 10 分間浸漬して、薬液洗浄を行なった。なお、薬液洗浄後のエピタキシャルウエハ 130 は、Ar ガンまたは N<sub>2</sub> ガンを用いて、アルゴンガスまたは N<sub>2</sub> ガスでブローすることによって乾燥させた。

## 【0109】

10

(表面の不純物の測定)

実施例 1、比較例 1 および比較例 2 のエピタキシャルウエハ 130 の表面を、TXRF (全反射蛍光 X 線分析法) に供した。なお、TXRFにおいて、励起源として W (タンゲステン) - L 線を用いた。

## 【0110】

TXRF によって実施例 1、比較例 1 および比較例 2 のエピタキシャルウエハ 130 の表面の不純物を測定した。実施例 1 における水素エッチング後のエピタキシャルウエハ 130 の表面は、水素エッチングを行わなかった比較例 1 の表面と比較して、不純物が低減されていた。したがって、水素エッチング後のエピタキシャルウエハ 130 にゲート酸化膜および電極を形成して SiC 半導体装置を製造することによって、高品質の SiC 半導体装置を製造できることがわかる。

20

## 【0111】

また、比較例 2 における液相を用いて洗浄した後のエピタキシャルウエハ 130 の表面は、比較例 1 よりもさらに不純物が多くなっていることがわかった。この結果を図 10 および図 11 に示す。

## 【0112】

30

図 10 は、比較例 1 の SiC 半導体の表面を TXRF で測定した結果を示すスペクトルであり、図 11 は、比較例 2 の SiC 半導体の表面を TXRF で測定した結果を示すスペクトルである。各図において、横軸はエネルギー強度を、縦軸はスペクトル強度を示しており、ピークの高さが大きいほど、その元素が多く検出されたことになる。また、たとえば、図 10 中の縦に記載される「C 1, K<sub>a</sub>」とは、C 1 - K 線が検出されたことを示し、他の記載も同様である。また、エネルギー強度が 9.67 eV 付近のピークは励起線源である W - L 線のピークである。

## 【0113】

図 10 および図 11 を比較すると、比較例 1 において、塩素 (Cl) 元素のみが検出されているのに対し、比較例 2 では、塩素 (Cl) 元素、カルシウム (Ca) 元素、ニッケル (Ni) 元素および鉄 (Fe) 元素が検出された。これにより、エピタキシャルウエハ 130 の表面を従来の洗浄処理に供した場合、表面が清浄化されないだけでなく、逆に不純物が付着してしまうことが分かった。

40

## 【0114】

したがって、実施例 1 における水素エッチング後のエピタキシャルウエハ 130 に対して液相を用いた洗浄をせずに、酸化膜および電極を形成して SiC 半導体装置を製造することによって、比較例 2 の SiC 半導体装置と比較して、より高品質の SiC 半導体装置を製造できることがわかった。

## 【0115】

50

以上のように本発明の実施の形態および実施例について説明を行なったが、各実施の形態および実施例の特徴を適宜組み合わせることも当初から予定している。また、今回開示された実施の形態および実施例はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した実施の形態および実施例ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含

まれることが意図される。

【符号の説明】

【0 1 1 6】

2 SiC 基板、2 a 表面、10 製造装置、11 除去部、12 形成部、13 接続部、100, 130 エピタキシャルウェハ、100a, 130a 第1の表面、100b 第2の表面、110 ゲート電極、111 ソースコンタクト電極、112 ドレイン電極、120 エピタキシャル層、121 バッファ層、122 ドリフト層、123 ボディ領域、124 ソース領域、125 p<sup>+</sup>領域、126 ゲート酸化膜、127 ソース電極、200 SiC 半導体装置、201 半導体膜。

【図 1】

【図 2】

【図 3】

【図 4】

【図 5】

【図6】

【図8】

【図7】

【図9】

【図10】

【図11】

---

フロントページの続き

(74)代理人 100124523

弁理士 佐々木 真人

(72)発明者 伊藤 里美

大阪市此花区島屋一丁目1番3号 住友電気工業株式会社大阪製作所内

(72)発明者 塩見 弘

大阪市此花区島屋一丁目1番3号 住友電気工業株式会社大阪製作所内

(72)発明者 並川 靖生

兵庫県伊丹市昆陽北一丁目1番1号 住友電気工業株式会社伊丹製作所内

(72)発明者 和田 圭司

大阪市此花区島屋一丁目1番3号 住友電気工業株式会社大阪製作所内

(72)発明者 嶋津 充

大阪市此花区島屋一丁目1番3号 住友電気工業株式会社大阪製作所内

(72)発明者 日吉 透

大阪市此花区島屋一丁目1番3号 住友電気工業株式会社大阪製作所内