(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4698722号

(P4698722)

(45) 発行日 平成23年6月8日(2011.6.8)

(24) 登録日 平成23年3月11日(2011.3.11)

(51) Int.Cl.

H01L 23/12 (2006.01)

H01L 21/60 (2006.01)

F 1

H01L 23/12 F

H01L 21/60 311S

H01L 23/12 501B

請求項の数 7 (全 25 頁)

(21) 出願番号 特願2008-273591 (P2008-273591)

(22) 出願日 平成20年10月23日 (2008.10.23)

(65) 公開番号 特開2009-135458 (P2009-135458A)

(43) 公開日 平成21年6月18日 (2009.6.18)

審査請求日 平成22年3月30日 (2010.3.30)

(31) 優先権主張番号 特願2007-291342 (P2007-291342)

(32) 優先日 平成19年11月8日 (2007.11.8)

(33) 優先権主張国 日本国 (JP)

早期審査対象出願

(73) 特許権者 000001889

三洋電機株式会社

大阪府守口市京阪本通2丁目5番5号

(74) 代理人 100105924

弁理士 森下 賢樹

(74) 代理人 100123102

弁理士 宗田 悟志

(72) 発明者 山本 哲也

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

(72) 発明者 岡山 芳央

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

最終頁に続く

(54) 【発明の名称】 素子搭載用基板、半導体モジュールおよびその製造方法、ならびに携帯機器

## (57) 【特許請求の範囲】

## 【請求項 1】

絶縁樹脂層と、

前記絶縁樹脂層の一方の表面に設けられた配線層と、

前記配線層の前記絶縁樹脂層側の表面に設けられた突起電極と、

前記突起電極の頂部面と、側面のうち前記配線層と接する領域を除いた前記頂部面と連

続する領域とを被覆し、金属層よりなる被覆部と、

を備え、

前記被覆部とは不連続であり、前記配線層の表面と前記突起電極の側面とが接する基端

部を含む前記基端部からの一部を少なくとも被覆し、金属層よりなる他の被覆部を備える

10

## 【請求項 2】

前記金属層は、前記突起電極の降伏応力の40%より大きく100%以下の降伏応力を有することを特徴とする請求項1に記載の素子搭載用基板。

## 【請求項 3】

前記金属層は、前記突起電極の降伏応力の50%以上75%以下の降伏応力を有し、且

つ前記被覆部は、前記突起電極の側面のうち前記突起電極の前記頂部面から前記配線層の

前記突起電極が設けられた側の表面までの高さの1/2以下の領域を被覆していることを

特徴とする請求項1または2に記載の素子搭載用基板。

## 【請求項 4】

20

前記突起電極は、側面に前記配線層側が細くなるような段差を有することを特徴とする請求項 1 ~ 3 のいずれか 1 項に記載の素子搭載用基板。

**【請求項 5】**

前記突起電極は、側面の前記段差よりも前記配線層側に、前記配線層側が太くなるような段差を有し、当該段差により太くなった領域が前記配線層まで延在していることを特徴とする請求項 1 ~ 4 のいずれか 1 項に記載の素子搭載用基板。

**【請求項 6】**

請求項 1 ~ 5 のいずれか 1 項に記載の素子搭載用基板と、

前記素子搭載用基板の前記突起電極に対向する素子電極が設けられた半導体素子と、

前記配線層と前記半導体素子との間に設けられた絶縁樹脂層と、

を備え、

前記突起電極が前記絶縁樹脂層を貫通し、前記突起電極と前記素子電極とが電気的に接続されていることを特徴とする半導体モジュール。

**【請求項 7】**

前記絶縁樹脂層は、加圧によって塑性流動を起こすことを特徴とする請求項 6 に記載の半導体モジュール。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、素子搭載用基板、半導体モジュールおよびその製造方法、ならびに携帯機器に関する。 20

**【背景技術】**

**【0002】**

近年、電子機器の小型化、高機能化に伴い、電子機器に使用される半導体素子の、さらなる小型化が求められている。半導体素子の小型化に伴い、素子搭載用基板に実装するための電極間の狭ピッチ化が不可欠となっている。半導体素子の表面実装方法として、半導体素子の電極にはんだバンプを形成し、はんだバンプと素子搭載用基板の電極パッドとをはんだ付けするフリップチップ実装方法が知られている。フリップチップ実装方法では、はんだバンプ自体の大きさや、はんだ付け時のブリッジ発生などが制約となり、電極の狭ピッチ化に限界があった。このような限界を克服するための構造として、基材に形成した突起構造を電極またはビアとし、基材にエボキシ樹脂などの絶縁樹脂を介して半導体素子を実装し、突起構造に半導体素子の電極を接続する構造が知られている（特許文献 1 参照）。 30

**【0003】**

一方、素子搭載用基板の電極上に突起構造を設け、素子搭載用基板に半導体素子を実装して突起構造と半導体素子の電極とを接続する構成において、素子搭載用基板の電極と突起構造とを金属めっき層で被覆することで突起構造と半導体素子の電極との接続信頼性を向上させる構造が知られている（特許文献 2 参照）。

**【特許文献 1】特開 2004 - 193297 号公報**

**【特許文献 2】特開 2006 - 173463 号公報**

40

**【発明の開示】**

**【発明が解決しようとする課題】**

**【0004】**

上述の各特許文献のように、素子搭載用基板の電極上に設けられた突起構造と半導体素子の電極とが圧着されて素子搭載用基板と半導体素子とが積層された構造においては、置かれた環境の温度変化によって生じる応力が、突起構造と半導体素子の電極との界面に集中し、半導体素子の電極にダメージを与えるおそれがある。そして、半導体素子の電極がダメージを受けた場合には、突起構造と半導体素子の電極との接続信頼性が低下してしまう。

**【0005】**

50

本発明はこうした状況に鑑みてなされたものであり、その目的は、突起構造を絶縁樹脂に埋め込むようにして配線層、絶縁樹脂および半導体素子を積層した半導体モジュールにおいて、半導体素子の電極にダメージを与えるおそれを低減し、突起構造と半導体素子の電極との接続信頼性を向上させる技術の提供にある。

【課題を解決するための手段】

【0006】

上記課題を解決するために、本発明のある態様は素子搭載用基板である。この素子搭載用基板は、絶縁樹脂層と、絶縁樹脂層の一方の表面に設けられた配線層と、配線層の絶縁樹脂層側の表面に設けられた突起電極と、突起電極の頂部面と、側面のうち前記配線層と接する領域を除いた前記頂部面と連続する領域とを被覆し、金属層よりなる被覆部と、を備える。

10

【0007】

この態様によれば、素子搭載用基板に半導体素子が搭載された状態において、温度変化によって被覆部と素子電極との界面に生じる応力が、被覆部によって分散されるため、半導体素子の電極にダメージを与えるおそれが低減し、被覆部と素子電極との接続信頼性が向上する。

【0008】

上記態様において、被覆部とは不連続であり、配線層の表面と突起電極の側面とが接する基端部を含む基端部からの一部を少なくとも被覆し、金属層よりなる他の被覆部を備えていてもよい。

20

【0009】

上記態様において、金属層は、突起電極の降伏応力の40%より大きく100%以下の降伏応力を有するものであってもよい。

【0010】

また、上記態様において、金属層は、突起電極の降伏応力の50%以上75%以下の降伏応力を有し、且つ被覆部は、突起電極の側面のうち突起電極の頂部面から配線層の突起電極が設けられた側の表面までの高さの1/2以下の領域を被覆してもよい。

30

【0011】

本発明の他の態様もまた、素子搭載用基板である。この素子搭載用基板は、絶縁樹脂層と、絶縁樹脂層の一方の表面に設けられた配線層と、配線層の絶縁樹脂層側の表面に設けられた突起電極と、を備え、突起電極は、側面に配線層側が細くなるような段差を有する

【0012】

この態様によれば、素子搭載用基板に半導体素子を搭載された状態において、温度変化によって突起電極と素子電極との界面に生じる応力が、段差の存在によって分散されるため、半導体素子の電極にダメージを与えるおそれが低減し、突起電極と半導体素子の電極との接続信頼性が向上する。

【0013】

上記態様において、突起電極は、側面の段差よりも配線層側に、配線層側が太くなるような段差を有し、当該段差により太くなった領域が配線層まで延在していてもよい。

【0014】

40

本発明のさらに他の態様は、半導体モジュールである。この半導体モジュールは、上述したいすれかの態様の素子搭載用基板と、素子搭載用基板の突起電極に対向する素子電極が設けられた半導体素子と、配線層と半導体素子との間に設けられた絶縁樹脂層と、を備え、突起電極が絶縁樹脂層を貫通し、突起電極と素子電極とが電気的に接続されている。

【0015】

上記態様において、絶縁樹脂層は、加圧によって塑性流動を起こしてもよい。

【0016】

本発明のさらに他の態様は、半導体モジュールの製造方法である。この半導体モジュールの製造方法は、突起電極が設けられた金属板を準備する工程と、突起電極の頂部面と、側面のうち前記金属板と接する領域を除いた前記頂部面と連続する領域とを金属を用いて

50

被覆する被覆工程と、突起電極が形成された金属板と、突起電極に対応する素子電極が設けられた半導体素子とを、絶縁樹脂層を介して圧着し、突起電極が絶縁樹脂層を貫通することにより、突起電極と素子電極とを電気的に接続させる圧着工程と、金属板を選択的に除去して配線層を形成する工程と、を含む。

【0017】

本発明のさらに他の態様もまた、半導体モジュールの製造方法である。この半導体モジュールの製造方法は、突起電極が設けられた金属板を準備する工程と、突起電極の頂部面と、側面のうち前記金属板と接する領域を除いた前記頂部面と連続する領域とを金属を用いて被覆する被覆工程と、突起電極が形成された金属板に、突起電極を被覆する金属が露出するように絶縁樹脂層を積層する工程と、突起電極に対応する素子電極が設けられた半導体素子を絶縁樹脂層が積層された金属板に圧着して、突起電極と素子電極とを電気的に接続する圧着工程と、金属板を選択的に除去して配線層を形成する工程と、を含む。10

【0018】

上記態様の被覆工程において、金属は、突起電極の降伏応力の40%より大きく100%以下の降伏応力を有するものであってもよい。

【0019】

上記態様の被覆工程において、金属は、突起電極の降伏応力の50%以上75%以下の降伏応力を有し、且つ突起電極の頂部面から配線層の突起電極が設けられた側の表面までの高さの1/2以下の領域を被覆するようにしてもよい。

【0020】

上記態様において、絶縁樹脂層は、加圧によって塑性流動を起こしてもよい。

【0021】

本発明のさらに他の態様は、携帯機器である。この携帯機器は、上述したいずれかの態様の半導体モジュールを搭載している。

【発明の効果】

【0022】

本発明によれば、突起構造を絶縁樹脂に埋め込むようにして配線層、絶縁樹脂および半導体素子を積層した半導体モジュールにおいて、半導体素子の電極にダメージを与えるおそれが低減し、突起構造と半導体素子の電極との接続信頼性が向上する。

【発明を実施するための最良の形態】

【0023】

以下、本発明を好適な実施の形態をもとに図面を参照しながら説明する。各図面に示される同一または同等の構成要素、部材、処理には、同一の符号を付するものとし、適宜重複した説明は省略する。また、実施の形態は、発明を限定するものではなく例示であって、実施の形態に記述されるすべての特徴やその組み合わせは、必ずしも発明の本質的なものであるとは限らない。

【0024】

(実施形態1)

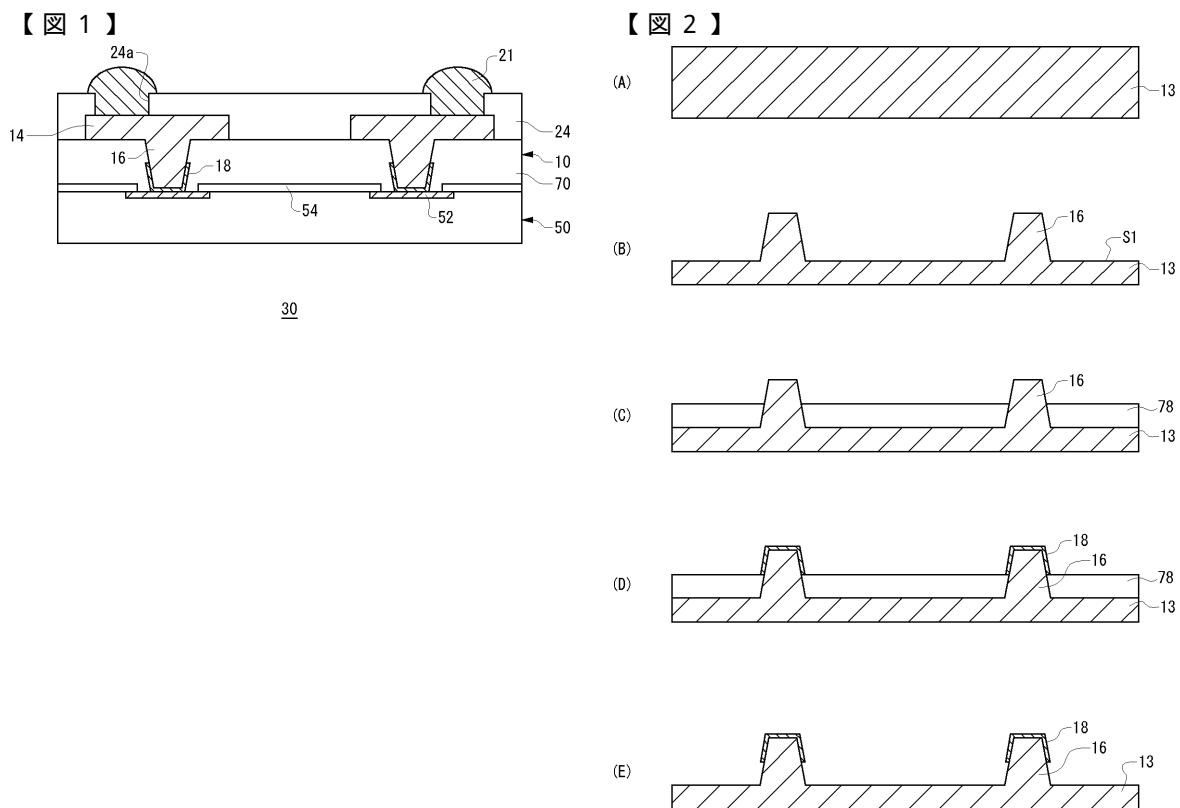

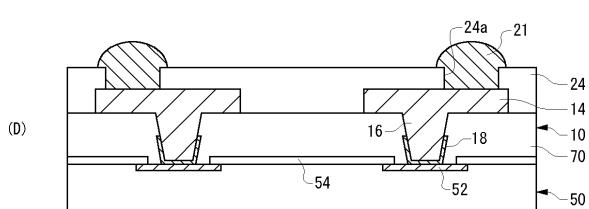

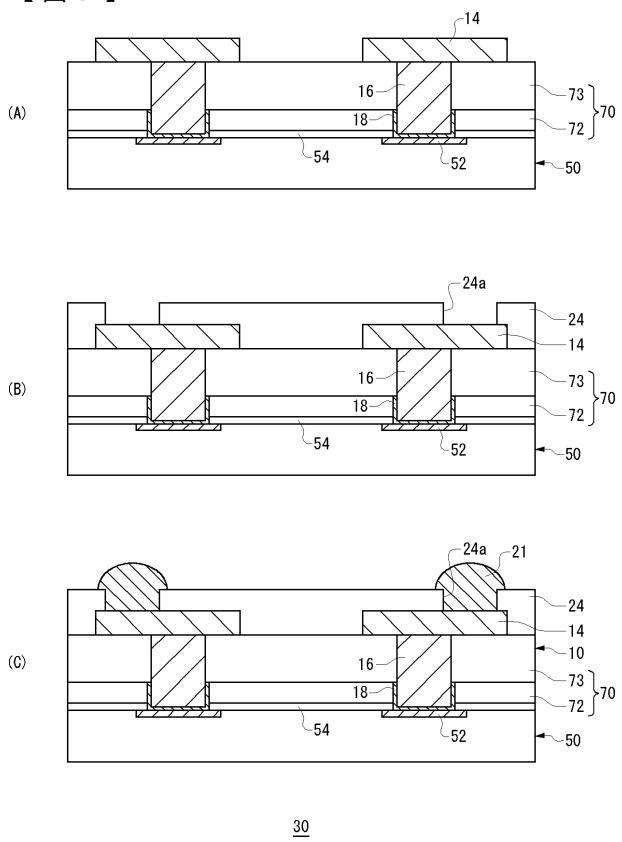

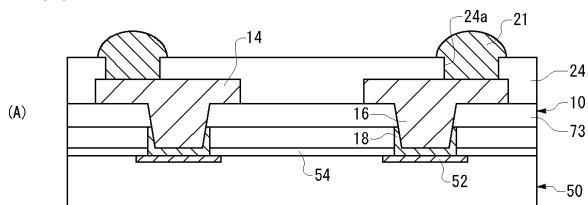

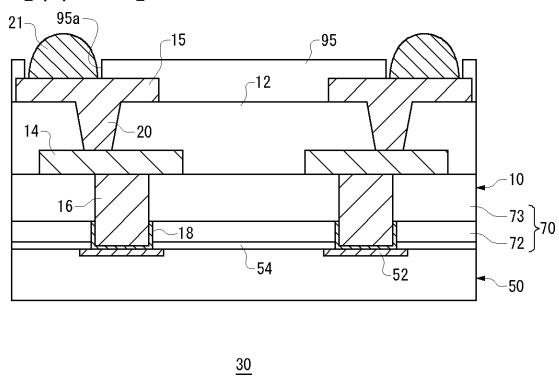

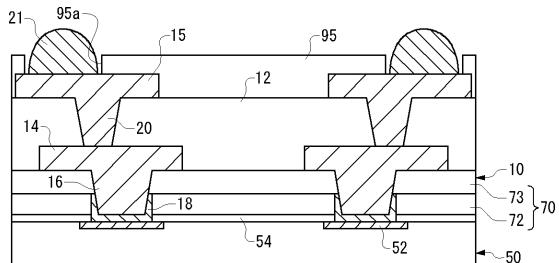

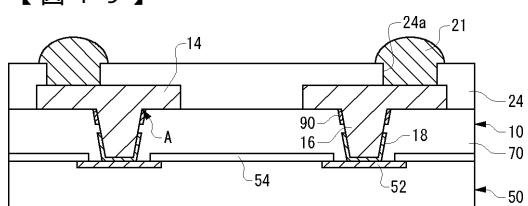

図1は、実施形態1に係る素子搭載用基板10およびこれを用いた半導体モジュール30の構成を示す概略断面図である。半導体モジュール30は、素子搭載用基板10およびこれに搭載された半導体素子50を備える。40

【0025】

素子搭載用基板10は、絶縁樹脂層70と、絶縁樹脂層70の一方の表面に設けられた配線層14と、配線層14の絶縁樹脂層70側の表面に設けられた突起電極16と、突起電極16の頂部面と、側面のうち前記配線層と接する領域を除いた前記頂部面と連続する領域とを被覆する被覆部18と、を備える。

【0026】

絶縁樹脂層70は、加圧したときに塑性流動を引き起こす材料で形成されている。加圧したときに塑性流動を引き起こす材料としては、エポキシ系熱硬化型樹脂が挙げられる。絶縁樹脂層70に用いられるエポキシ系熱硬化型樹脂は、たとえば、温度160℃、圧力50

8 MPa の条件下で、粘度が 1 kPa · s の特性を有する材料であればよい。また、このエポキシ系熱硬化型樹脂は、たとえば温度 160 の条件下で、5 ~ 15 MPa で加圧した場合に、加圧しない場合と比較して、樹脂の粘度が約 1 / 8 に低下する。これに対して、熱硬化前の B ステージのエポキシ樹脂は、ガラス転移温度 Tg 以下の条件下では、樹脂を加圧しない場合と同程度に、粘性がなく、加圧しても粘性は生じない。

#### 【0027】

本実施形態の半導体モジュール 30 では、絶縁樹脂層 70 は、配線層 14 と半導体素子 50 との間に設けられ、一方の面が配線層 14 と圧着し、他方の面が半導体素子 50 と圧着している。ここで、本実施形態では、絶縁樹脂層 70 として加圧により塑性流動を起こす材料が用いられているため、後述するように、素子搭載用基板 10、絶縁樹脂層 70 および半導体素子 50 がこの順で一体化された状態において、被覆部 18 と素子電極 52 との間に絶縁樹脂層 70 の残膜が介在することが抑制され、接続信頼性の向上が図られる。10

#### 【0028】

配線層 14 は導電材料、好ましくは圧延金属、さらには圧延銅により形成される。配線層 14 の絶縁樹脂層 70 と反対側の表面には、配線保護層 24 が設けられ、配線保護層 24 によって、配線層 14 の酸化などが防止される。配線保護層 24 は、たとえばフォトソルダーレジストからなる。配線保護層 24 の所定の位置には、配線層 14 が露出するよう開口 24a が形成されており、開口 24a において露出した配線層 14 上にはんだバンプ 21 が形成されている。開口 24a の位置、すなわち、はんだバンプ 21 を形成する位置は、たとえば再配線で引き回した先の位置である。20

#### 【0029】

また、配線層 14 には、半導体素子 50 の各素子電極 52 と対応する位置に突起電極 16 が設けられている。本実施形態においては、配線層 14 と突起電極 16 とは一体的に形成されている。突起電極 16 は、平面視で丸型であり、頂部に近づくにつれて径が細くなるように形成された側面を備えている。なお、突起電極 16 の形状は特に限定されず、たとえば、所定の径を有する円柱状であってもよい。また、平面視で四角形などの多角形であってもよい。

#### 【0030】

突起電極 16 の頂部面と、側面のうち前記配線層と接する領域を除いた前記頂部面と連続する領域とには、被覆部 18 が設けられている。具体的には、被覆部 18 は、たとえば突起電極 16 の降伏応力の 40 % より大きく 100 % 以下の降伏応力を有する金属材料を用いて電解めっき法あるいは無電解めっき法により形成された金属めっき層である。あるいは導電ペーストを用いて形成された導電ペースト層である。金属層は複数層であってもよく、たとえば Ni めっき層と Au めっき層との積層が例示される。本実施形態においては、銅からなる突起電極 16 の降伏応力に対して 60 % の降伏応力を有する金 (Au) およびニッケル (Ni) からなる Ni / Au めっき層である。30

#### 【0031】

さらに突起電極 16 と被覆部 18 とが同一材料からなる場合には、突起電極 16 と被覆部 18 とは一体的に形成されるものであってもよく、この場合には突起電極 16 は、側面に配線層 14 側が細くなるような段差を有した形状となる。40

#### 【0032】

また、本実施形態において被覆部 18 は、突起電極 16 の頂部面と、側面のうち突起電極 16 の頂部面から配線層 14 の突起電極 16 が設けられた側の表面までの高さの 1 / 2 以下の頂部面側の領域とを被覆している。ここで、突起電極 16 の高さの一方の基準面となる、配線層 14 の突起電極 16 が設けられた側の表面は、配線層 14 の表面に微細な凹凸が形成されている場合、たとえば、これらの微細凹凸の平均高さの位置を通る面とする。同様に、突起電極 16 の高さの他方の基準面となる突起電極 16 の頂部面は、頂部面に微細凹凸が形成されている場合、これらの微細凹凸の平均高さの位置を通る面とする。

#### 【0033】

突起電極 16 は、絶縁樹脂層 70 を貫通し、半導体素子 50 に設けられた素子電極 52

50

と電気的に接続されている。突起電極 16 に被覆部 18 を設けることで、素子搭載用基板 10 に半導体素子 50 が搭載された状態において、温度変化によって被覆部 18 と素子電極 52 との界面に生じる応力が分散される。すなわち、素子電極 52 における最大応力の値を小さくすることができる。これにより素子電極 52 にダメージを与えるおそれがある低減し、被覆部 18 と素子電極 52 との接続信頼性が向上する。

#### 【0034】

半導体素子 50 は、素子電極 52 が設けられた電極面を絶縁樹脂層 70 側に向けて絶縁樹脂層 70 に圧着されている。また、半導体素子 50 には、素子電極 52 が開口するよう 10 に設けられた半導体素子 50 の保護層 54 が積層されている。半導体素子 50 の具体例としては、集積回路 (IC) 、大規模集積回路 (LSI) などの半導体チップが挙げられる。保護層 54 の具体例としては、ポリイミド層が挙げられる。また、素子電極 52 としては、たとえばアルミニウムが用いられる。

#### 【0035】

(半導体モジュールの製造方法)

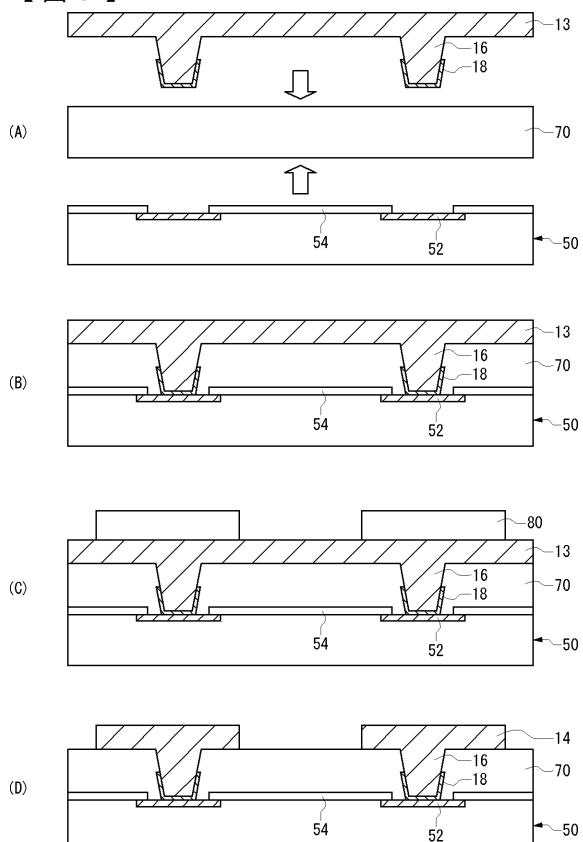

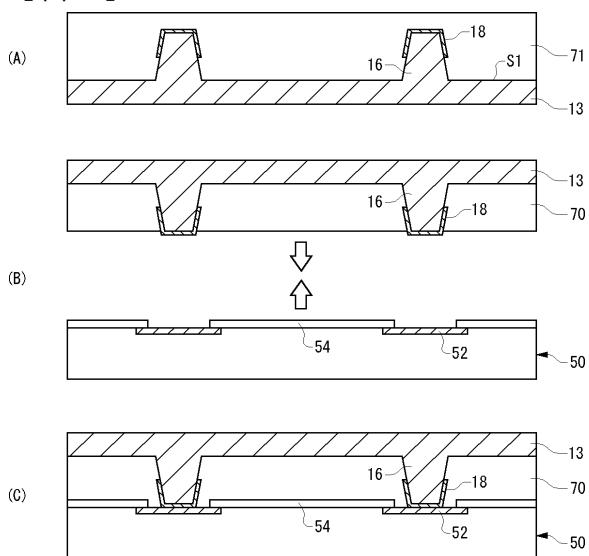

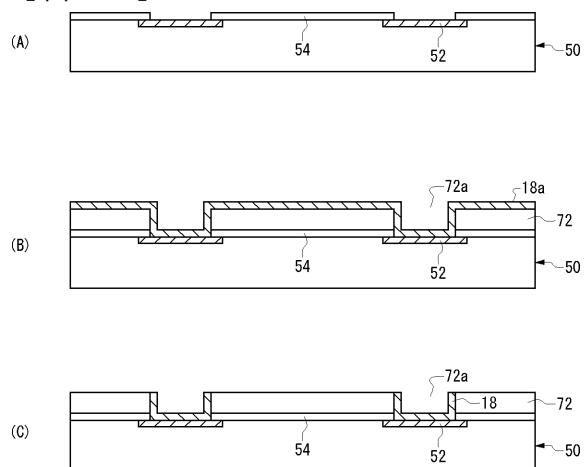

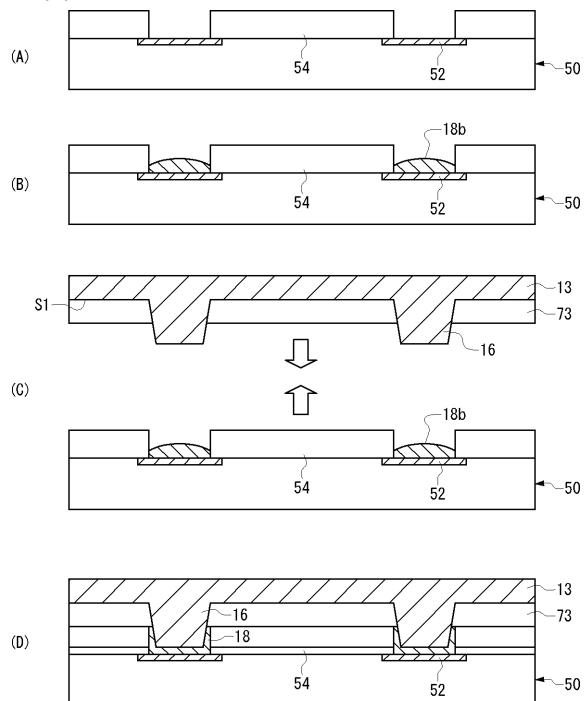

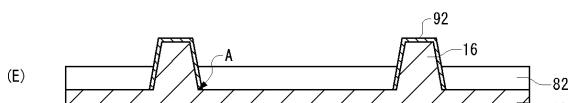

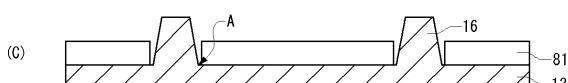

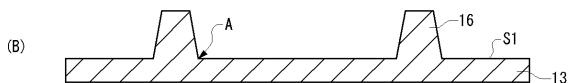

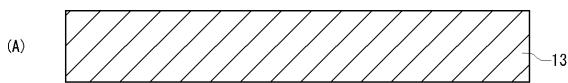

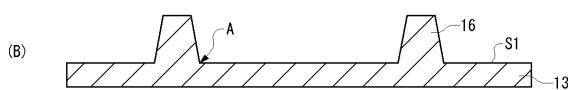

図 2 (A) ~ (E) は、突起電極 16 および被覆部 18 の形成方法を示す工程断面図である。

#### 【0036】

図 2 (A) に示すように、少なくとも、突起電極 16 の高さと配線層 14 の厚さとの和より大きい厚さを有する金属板としての銅板 13 を用意する。

#### 【0037】

次に、図 2 (B) に示すように、リソグラフィ法により、電極形成領域にレジスト (図示せず) を選択的に形成し、レジストをマスクとして、銅板 13 に所定のパターンの突起電極 16 を形成する。各突起電極 16 は、半導体素子 50 に形成された各素子電極 52 の位置に対応して設けられる (図 3 (A) 参照)。

#### 【0038】

次に、図 2 (C) に示すように、銅板 13 の一方の主表面 S1 側に、所定の高さまでレジスト 78 を積層する。積層するレジスト 78 の高さは、後述する被覆部 18 の被覆領域に応じた高さである。具体的には、レジスト 78 の高さは、突起電極 16 の頂部面と、側面のうち突起電極 16 の頂部面から銅板 13 の突起電極 16 が設けられた側の表面までの高さの 1/2 以下の頂部面側の領域とが露出する高さである。

#### 【0039】

次に、図 2 (D) に示すように、突起電極 16 の露出している部分に被覆部 18 を形成する。被覆部 18 は、たとえばレジスト 78 をマスクとして、電解めっき法または無電解めっき法により Au / Ni の金属層として形成する。電解めっき法または無電解めっき法により被覆部 18 を形成すると、被覆部 18 を形成する金属の結晶粒の向きが、素子電極 52 の接触面に対して垂直方向に並ぶ。このため、素子電極 52 と圧着した際に素子電極 52 にかかる圧力を被覆部 18 が吸収することができ、これにより素子電極 52 にダメージを与えるおそれを低減することができる。また電解めっき法もしくは無電解めっき法により被覆部 18 を形成することで、スパッタ法で形成した場合などに比べると低コストで形成することができる。また、被覆部 18 を構成する金属層は、Ni 層が突起電極 16 と接する側に、Au 層が素子電極 52 と接する側となるように形成される。なお、被覆部 18 の形成方法としては、特にこれに限定されず、たとえば銅ペースト、銀ペースト、金ペーストなどの導電性ペーストを用いて形成してもよい。

#### 【0040】

次に、図 2 (E) に示すように、レジスト 78 を除去する。以上説明した工程により、突起電極 16 および被覆部 18 が形成される。

#### 【0041】

本実施形態における突起電極 16 の配線層 14 側底面の径、頂部面の径、高さは、それぞれ、40 μm 、30 μm 、40 μm である。また、被覆部 18 の厚さは 5 μm であり、そのうち Au 層の厚さが 1 μm 、Ni 層の厚さが 4 μm である。突起電極 16 の側面

10

20

30

40

50

を覆う被覆部 18 の範囲は、突起電極 16 の頂部面からの高さが 20 μm 以下の領域である。

#### 【0042】

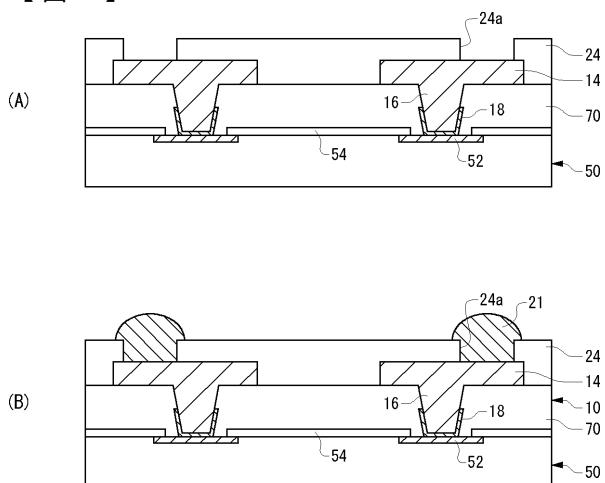

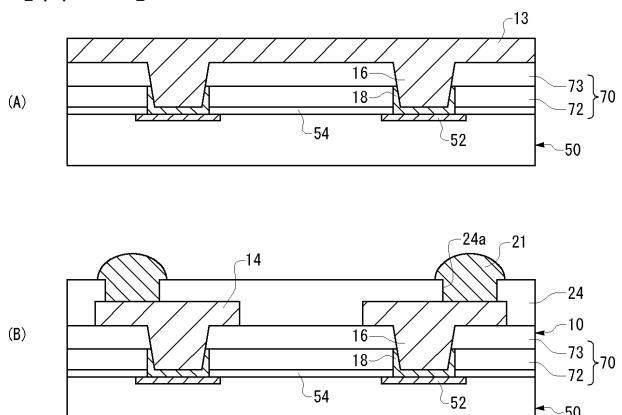

図 3 (A) ~ (D) および図 4 (A)、(B) は、突起電極 16 と素子電極 52 との接続方法を示す工程断面図である。

#### 【0043】

図 3 (A) に示すように、所定パターンの素子電極 52 が形成された半導体素子 50 と、上述の方法で形成された銅板 13 との間に、絶縁樹脂層 70 を挟持する。絶縁樹脂層 70 の厚さは、突起電極 16 の高さ程度であり、約 40 μm である。

#### 【0044】

次に、図 3 (B) に示すように、プレス装置を用いて加圧成形することにより、半導体素子 50、絶縁樹脂層 70 および銅板 13 を一体化する。プレス加工時の圧力および温度は、それぞれ約 5 MPa および 180 °C である。プレス加工により、突起電極 16 および被覆部 18 が絶縁樹脂層 70 を貫通し、被覆部 18 と素子電極 52 とが圧着して、突起電極 16 と素子電極 52 とが電気的に接続される。突起電極 16 および被覆部 18 は、その全体的な形状が先端に近づくにつれて細くなるような形状であるため、突起電極 16 および被覆部 18 が絶縁樹脂層 70 をスムースに貫通する。

10

#### 【0045】

次に、図 3 (C) に示すように、リソグラフィ法により、配線層 14 のパターンに合わせてレジスト 80 を選択的に形成する。具体的には、ラミネーター装置を用いて銅板 13 に所定膜厚のレジスト膜を貼り付け、配線層 14 のパターンを有するフォトマスクを用いて露光した後、Na<sub>2</sub>CO<sub>3</sub> 溶液を用いて現像し、未露光領域のレジストを除去することによって、銅板 13 の上にレジストが選択的に形成される。なお、レジストとの密着性向上のために、レジスト膜のラミネート前に、銅板 13 の表面に研磨、洗浄等の前処理を必要に応じて施すことが望ましい。また、レジスト 80 のラミネート前に、必要に応じて、銅板 13 の裏面側の全体をエッチングして、銅板 13 を配線層 14 の厚さに調整するようにもよい。

20

#### 【0046】

次に、図 3 (D) に示すように、塩化第二鉄溶液を用いて、銅板 13 の露光部分をエッチングすることにより、所定の配線パターンを有する配線層 14 を形成する。そして、レジスト 80 を NaOH 溶液などの剥離剤を用いて剥離する。本実施形態における配線層 14 の厚さは 15 μm である。

30

#### 【0047】

次に、図 4 (A) に示すように、リソグラフィ法により、配線層 14 の絶縁樹脂層 70 と反対側の表面に、開口 24a を有する配線保護層 24 を積層する。

#### 【0048】

次に、図 4 (B) に示すように、開口 24a において露出している配線層 14 上にはんだバンプ 21 を形成する。はんだバンプ 21 を形成する位置は、再配線で引き回した先の位置であってもよい。

40

#### 【0049】

以上説明した製造工程により、半導体モジュール 30 が得られる。また、半導体素子 50 が積層されなかった場合には、素子搭載用基板 10 が得られる。

#### 【0050】

以下に、突起電極 16 に被覆部 18 を設けた効果について説明する。

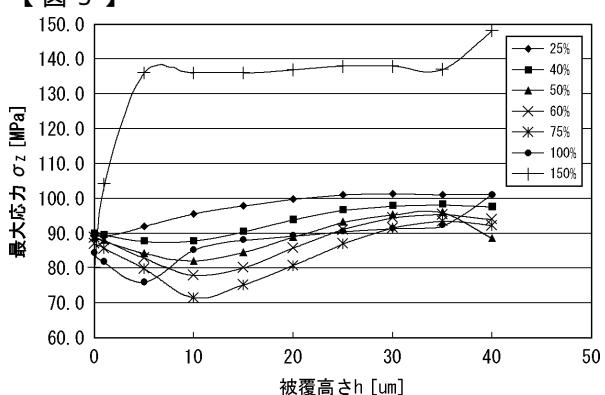

#### 【0051】

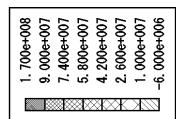

図 5 は、降伏応力の異なる金属材料で形成した被覆部 18 のそれについて、温度を 25 °C から 125 °C まで変化させた雰囲気下における、被覆部 18 の形成領域（被覆高さ）と、被覆部 18 と素子電極 52 との界面に生じる最大応力との関係をシミュレーションにより算出したグラフである。突起電極 16 を形成する材料を銅とし、被覆部 18 を形成する金属材料の降伏応力が突起電極 16 の降伏応力の 25 % から 150 % までについて検

50

討した。

#### 【0052】

図5に示されるように、突起電極16の頂部面と、側面のうち前記配線層と接する領域を除いた前記頂部面と連続する領域とを被覆部18により被覆することで、被覆部18と素子電極52との界面に生じる応力が分散され、素子電極52における最大応力の値を小さくすることができることが分かる。また、被覆部18の降伏応力が突起電極の降伏応力の40%より大きく、100%以下の場合に、最大応力の極小値が存在する。したがって、被覆部18の降伏応力が突起電極の降伏応力の40%より大きく、100%以下の場合に、被覆部18と突起電極16との界面にかかる応力を効果的に制御できることが分かる。また、被覆高さ $h$ が0μmあるいは突起電極16の高さと同一の40μmの場合には、理論上は被覆部18を設けていない状態と同様になる。そこで、降伏応力の異なる被覆部18それぞれの被覆高さ0μmおよび40μmの値をそれぞれの基準として比較すると、降伏応力が50%以上、75%以下の場合であって、且つ被覆高さが突起電極16の高さの1/2以下の場合に、被覆部18と突起電極16との界面における最大応力を小さくすることができることが分かる。10

#### 【0053】

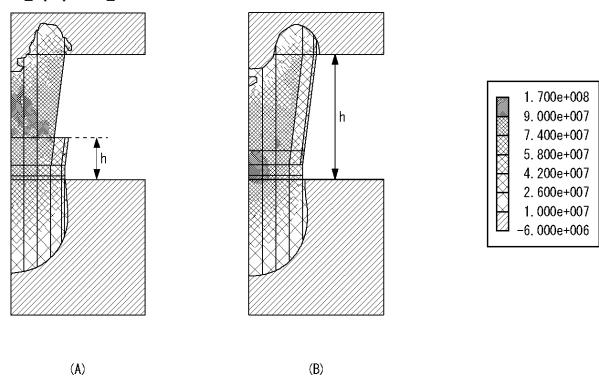

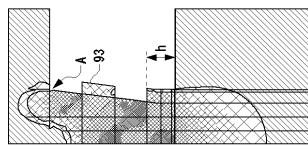

図6(A)、(B)はそれぞれ、降伏応力が50%で、被覆高さ $h$ が10μm(突起電極16の高さの1/4)あるいは40μm(突起電極16の高さと同等)の被覆部18が設けられた突起電極16について、温度を25から125まで変化させた雰囲気下において発生する応力の分布をシミュレーションにより算出した模式図である。20

#### 【0054】

図6(B)に示されるように、被覆高さ $h$ が突起電極16の高さと同じ場合には、被覆部18と素子電極52との界面に応力が集中している。一方、図6(A)に示されるように、被覆部18の被覆高さ $h$ が突起電極16の高さの1/4の場合には、応力が突起電極16内部に集中している。すなわち、被覆部18を設けることで、温度変化によって生じる応力が集中する領域を、被覆部18と素子電極52との界面から突起電極16内部に移動させることができる。これにより被覆部18と素子電極52との界面にかかる応力が分散され、界面における最大応力を小さくすることができる。

#### 【0055】

以上より、本実施形態によれば、突起電極16に被覆部18を設けることで、温度変化によって生じる応力が集中する位置を被覆部18と素子電極52との界面から突起電極16側に移動させて、界面における最大応力を小さくすることができる。これにより、素子搭載用基板10に半導体素子50が搭載された状態において、素子電極52にダメージを与えるおそれが低減し、突起電極16と素子電極52との接続信頼性が向上し、ひいては素子搭載用基板10と半導体素子50との接続信頼性が向上する。また、半導体素子50の破壊を防ぐことができるため、半導体モジュール30の製造歩留まりを高くでき、半導体モジュール30の製造コストを低減することができる。30

#### 【0056】

##### (実施形態2)

上述した実施形態1では、銅板13と半導体素子50との間に絶縁樹脂層70を挟持し、加圧成形することで半導体素子50、絶縁樹脂層70および銅板13を一体化して半導体モジュール30を形成したが、本実施形態に示すように、以下のように半導体モジュール30を形成してもよい。なお、半導体モジュール30のその他の構成、および、突起電極16および被覆部18の製造方法などについては、実施形態1と基本的には同様であるため、その説明は適宜省略する。40

#### 【0057】

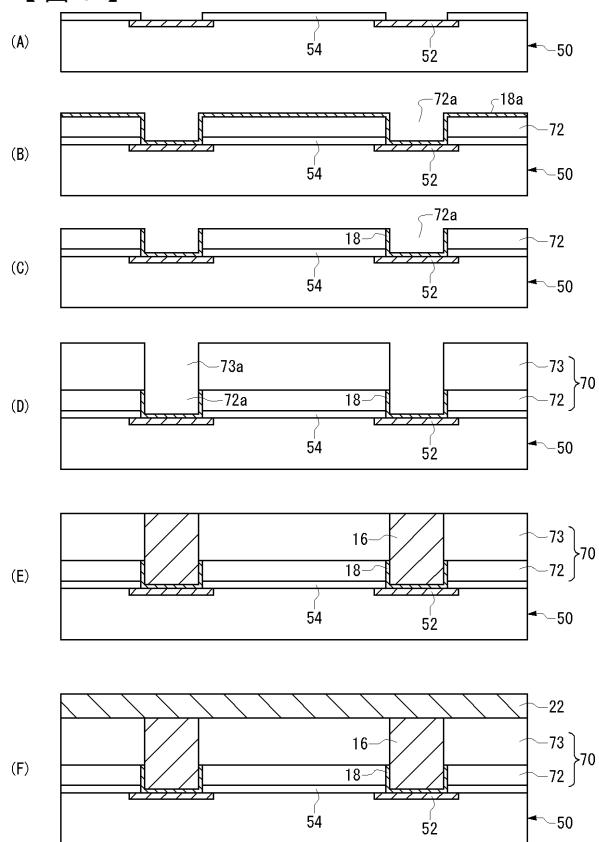

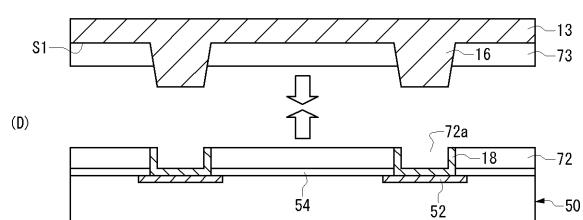

図7(A)～(D)は、実施形態2に係る半導体モジュール30の製造方法の工程断面図である。

#### 【0058】

図7(A)に示すように、銅板13の一方の主表面S1に上述のエポキシ系熱硬化性樹

脂 7 1 を積層する。

**【 0 0 5 9 】**

次に、図 7 ( B ) に示すように、エポキシ系熱硬化性樹脂 7 1 をエッティングして、被覆部 1 8 を露出させて、絶縁樹脂層 7 0 を形成する。そして、絶縁樹脂層 7 0 の形成された銅板 1 3 と半導体素子 5 0 とを加圧成形し、図 7 ( C ) に示すように半導体素子 5 0 、絶縁樹脂層 7 0 および銅板 1 3 を一体化する。

**【 0 0 6 0 】**

次に、図 7 ( D ) に示すように、実施形態 1 と同様の手順で銅板 1 3 をエッティングして配線層 1 4 を形成し、配線層 1 4 の絶縁樹脂層 7 0 と反対側の表面に、開口 2 4 a を有する配線保護層 2 4 を積層する。そして、開口 2 4 a において露出している配線層 1 4 上にはんだバンプ 2 1 を形成する。10

**【 0 0 6 1 】**

以上説明した製造工程により、半導体モジュール 3 0 が得られる。また、半導体素子 5 0 が積層されなかった場合には、素子搭載用基板 1 0 が得られる。

**【 0 0 6 2 】**

これによれば、実施形態 1 の上述の効果に加えて、さらに次のような効果が得られる。すなわち、本実施形態においては、被覆部 1 8 が絶縁樹脂層 7 0 から露出しているために、素子搭載用基板 1 0 と半導体素子 5 0 との加圧成形の際の位置決めを正確に行うことができるとともに、被覆部 1 8 と素子電極 5 2 との接続性が向上する。これにより素子搭載用基板 1 0 と半導体素子 5 0 との接続信頼性がさらに向上する。20

**【 0 0 6 3 】**

( 実施形態 3 )

上述した実施形態 1 では、いわゆる貼り合わせプロセスにより半導体モジュール 3 0 を形成したが、本実施形態に示すように、いわゆるビルドアッププロセスにより半導体モジュール 3 0 を形成してもよい。その他の実施形態 1 と同様の構成については、その説明を適宜省略する。

**【 0 0 6 4 】**

図 8 ( A ) ~ ( F ) および図 9 ( A ) ~ ( C ) は、実施形態 3 に係る半導体モジュール 3 0 の製造方法の工程断面図である。

**【 0 0 6 5 】**

図 8 ( A ) に示すように、所定パターンの素子電極 5 2 が形成された半導体素子 5 0 を準備する。30

**【 0 0 6 6 】**

次に、図 8 ( B ) に示すように、半導体素子 5 0 の保護層 5 4 上に樹脂層 7 2 を積層する。樹脂層 7 2 は、上述のエポキシ系熱硬化性樹脂を半導体素子 5 0 の素子電極 5 2 側全面に積層し、素子電極 5 2 の上方領域の樹脂をエッティングして開口部 7 2 a を設けることで形成することができる。樹脂層 7 2 の厚さ(高さ)は、被覆部 1 8 の被覆領域に応じた厚さ(高さ)である。続いて、半導体素子 5 0 の樹脂層 7 2 を積層した側に、たとえばスパッタ法などにより金属の被覆膜 1 8 a を形成する。

**【 0 0 6 7 】**

次に、図 8 ( C ) に示すように、被覆膜 1 8 a のうち、開口部 7 2 a の内面以外の領域の被覆膜を除去し、被覆部 1 8 を形成する。40

**【 0 0 6 8 】**

次に、図 8 ( D ) に示すように、樹脂層 7 2 上に上述のエポキシ系熱硬化性樹脂からなる樹脂層 7 3 を積層する。樹脂層 7 3 の、開口部 7 2 a の存在領域上方部分には、開口部 7 3 a が設けられる。樹脂層 7 2 と樹脂層 7 3 とにより絶縁樹脂層 7 0 が形成される。樹脂層 7 3 は、たとえば開口部 7 2 a にマスクを設けて樹脂層 7 3 を積層し、その後マスクを除去することで設けることができる。あるいは、半導体素子 5 0 の樹脂層 7 2 を積層した側全面にエポキシ系熱硬化性樹脂を積層し、開口部 7 2 a の設けられていた領域(素子電極 5 2 の上方の領域)以外の領域をマスキングして、エッティングにより開口部 7 2 a 、50

7 3 a を形成して樹脂層 7 3 を設けてよい。

**【 0 0 6 9 】**

次に、図 8 ( E ) に示すように、開口部 7 2 a 、 7 3 a 内に突起電極 1 6 を形成する。突起電極 1 6 は、たとえば電解または無電解めつき法により、あるいは銅ペーストなどを用いて形成することができる。

**【 0 0 7 0 】**

次に、図 8 ( F ) に示すように、半導体素子 5 0 の樹脂層 7 3 側全面に銅板 2 2 を積層する。

**【 0 0 7 1 】**

次に、図 9 ( A ) に示すように、銅板 2 2 の配線層形成領域に、リソグラフィ法により 10 レジスト ( 図示せず ) を選択的に形成し、レジストをマスクとして、所定パターンの配線層 1 4 を形成する。

**【 0 0 7 2 】**

次に、図 9 ( B ) に示すように、配線層 1 4 の絶縁樹脂層 7 0 と反対側の表面に、開口 2 4 a を有する配線保護層 2 4 を積層する。

**【 0 0 7 3 】**

次に、図 9 ( C ) に示すように、開口 2 4 a において露出している配線層 1 4 上にはんだパンプ 2 1 を形成する。

**【 0 0 7 4 】**

以上説明した製造工程により、半導体モジュール 3 0 が得られる。また、半導体素子 5 0 が用いられなかった場合には、素子搭載用基板 1 0 が得られる。

**【 0 0 7 5 】**

これによれば、実施形態 1 の上述の効果に加えて、さらに次のような効果が得られる。すなわち、本実施形態のようにビルドアッププロセスによって半導体モジュール 3 0 を形成する場合には、貼り合わせプロセスのように素子搭載用基板 1 0 と半導体素子 5 0 とを圧着することはないため、半導体モジュール 3 0 の製造時に半導体素子 5 0 にダメージを与えるおそれを低減することができる。また、配線層 1 4 の銅、絶縁樹脂層 7 0 の樹脂、および半導体素子 5 0 のシリコンはそれぞれ熱膨張率が大きく異なるため、貼り合わせプロセスではプレス加工時の熱処理により各部材の反りが発生するおそれがある。一方、本実施形態に係るビルドアッププロセスでは貼り合わせプロセスのような熱処理を行わないため、このような反りの発生を抑えることができ、素子搭載用基板 1 0 と半導体素子 5 0 との接続信頼性をより高めることができる。

**【 0 0 7 6 】**

( 実施形態 4 )

本実施形態においては、貼り合わせプロセスとビルドアッププロセスとを組み合わせて半導体モジュール 3 0 を形成する。なお、半導体モジュール 3 0 のその他の構成、および突起電極 1 6 の形成方法などについては、実施形態 1 と基本的には同様であるため、その説明は適宜省略する。

**【 0 0 7 7 】**

図 1 0 ( A ) ~ ( D ) および図 1 1 ( A ) 、 ( B ) は、実施形態 4 に係る半導体モジュール 3 0 の製造方法の工程断面図である。

**【 0 0 7 8 】**

図 1 0 ( A ) に示すように、所定パターンの素子電極 5 2 が形成された半導体素子 5 0 を準備する。

**【 0 0 7 9 】**

次に、図 1 0 ( B ) に示すように、半導体素子 5 0 の保護層 5 4 上に樹脂層 7 2 を積層する。樹脂層 7 2 は、上述のエポキシ系熱硬化性樹脂を半導体素子 5 0 の素子電極 5 2 側全面に積層し、素子電極 5 2 の上方領域の樹脂をエッチングして開口部 7 2 a を設けることで形成することができる。樹脂層 7 2 の層厚 ( 高さ ) は、被覆部 1 8 の被覆領域に応じた厚さ ( 高さ ) である。続いて、半導体素子 5 0 の樹脂層 7 2 を積層した側に、たとえば 50

スパッタ法などにより金属の被覆膜 18a を形成する。

**【0080】**

次に、図 10 (C) に示すように、被覆膜 18a のうち、開口部 72a の内面以外の領域の被覆膜を除去し、被覆部 18 を形成する。

**【0081】**

次に、図 10 (D) に示すように、突起電極 16 の形成された銅板 13 の一方の主表面 S1 側に所定の高さまで樹脂層 73 を積層する。そして、被覆部 18 の形成された半導体素子 50 と、樹脂層 73 を積層した銅板 13 とを加圧成形して、図 11 (A) に示すように半導体素子 50 、絶縁樹脂層 70 および銅板 13 を一体化する。

**【0082】**

次に、図 11 (B) に示すように、実施形態 1 と同様の手順で銅板 13 をエッチングして配線層 14 を形成し、配線層 14 の絶縁樹脂層 70 と反対側の表面に、開口 24a を有する配線保護層 24 を積層する。そして、開口 24a において露出している配線層 14 上にはんだバンプ 21 を形成する。

**【0083】**

以上説明した製造工程により、半導体モジュール 30 が得られる。また、半導体素子 50 が用いられなかった場合には、素子搭載用基板 10 が得られる。

**【0084】**

これによれば、実施形態 1 の上述の効果に加えて、さらに次のような効果が得られる。すなわち、ビルドアッププロセスにより素子電極 52 に被覆部 18 を形成した後に、突起電極 16 の頂部を樹脂層 73 から露出させた素子搭載用基板 10 と半導体素子 50 とを圧着しているため、絶縁樹脂層 70 を素子搭載用基板 10 と半導体素子 50 とで挟持して圧着する場合に比べて、突起電極 16 の頂部と被覆部 18 との界面にかかる応力を分散させることができる。これにより半導体モジュール 30 の製造時に素子電極 52 にダメージを与えるおそれが低減し、突起電極 16 と素子電極 52 との接続信頼性がさらに向上する。

**【0085】**

(実施形態 5)

本実施形態においては、貼り合わせプロセスとビルドアッププロセスとを組み合わせて半導体モジュール 30 を形成する。被覆部 18 の形成方法が上述の実施形態 4 と異なる。なお、半導体モジュール 30 のその他の構成、および、突起電極 16 の形成方法などについては、実施形態 1 と基本的には同様であるため、その説明は適宜省略する。

**【0086】**

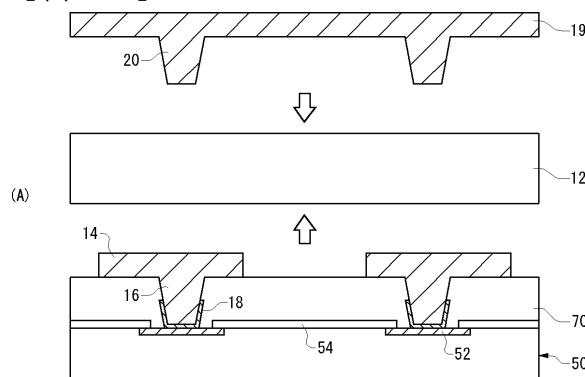

図 12 (A) ~ (D) および図 13 (A) は、実施形態 5 に係る半導体モジュール 30 の製造方法の工程断面図である。

**【0087】**

図 12 (A) に示すように、所定パターンの素子電極 52 が形成された半導体素子 50 を準備する。本実施形態においては、半導体素子 50 に設けられた保護層 54 の厚さ（高さ）は、被覆部 18 の被覆領域に応じた厚さ（高さ）となっている。

**【0088】**

次に、図 12 (B) に示すように、保護層 54 に形成されている開口内に、たとえば銅ペースト、銀ペースト、金ペーストなどの導電性ペースト 18b を塗布する。

**【0089】**

次に、図 12 (C) に示すように、突起電極 16 の形成された銅板 13 の一方の主表面 S1 側に、所定の高さまで上述のエポキシ系熱硬化性樹脂からなる樹脂層 73 を積層する。そして、被覆部 18 の形成された半導体素子 50 と、樹脂層 73 を積層した銅板 13 とを加圧成形して、図 12 (D) に示すように半導体素子 50 、樹脂層 73 および銅板 13 を一体化する。加圧成形の際、突起電極 16 は保護層 54 の開口内に進入し、その先端部が導電性ペースト 18b に没入する。これにより導電性ペースト 18b は塑性変形して保護層 54 の開口内面と突起電極 16 との間を延伸し、被覆部 18 が形成される。

**【0090】**

10

20

30

40

50

次に、図13(A)に示すように、実施形態1と同様の手順で銅板13をエッチングして配線層14を形成し、配線層14の樹脂層73と反対側の表面に、開口24aを有する配線保護層24を積層する。そして、開口24aにおいて露出している配線層14上にはんだバンプ21を形成する。

#### 【0091】

以上説明した製造工程により、半導体モジュール30が得られる。また、半導体素子50が用いられなかった場合には、素子搭載用基板10が得られる。

#### 【0092】

これによれば、実施形態1の上述の効果に加えて、さらに次のような効果が得られる。

すなわち、導電性ペーストを突起電極16との圧着により塑性変形させて被覆部18を形成しているため、簡単に被覆部18を形成することができる。また、圧着により生じる応力を導電性ペーストが吸収することができるため、半導体モジュール30の製造時に素子電極52にダメージを与えるおそれが低減し、突起電極16と素子電極52との接続信頼性が向上する。

10

#### 【0093】

##### (実施形態6)

本実施形態に係る半導体モジュール30は、絶縁樹脂層12と、配線層14を第1配線層とした場合に第2配線層としての配線層15と、配線層15の絶縁樹脂層12側の表面に設けられた突起電極20と、を備えている点が実施形態1または2と異なる。半導体モジュール30のその他の構成、および突起電極16および被覆部18の製造方法などについては、実施形態1または2と基本的には同様であるため、その説明は適宜省略する。

20

#### 【0094】

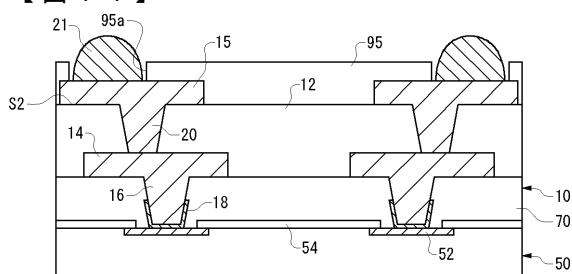

図14は、実施形態6に係る素子搭載用基板10およびこれを用いた半導体モジュール30の構成を示す概略断面図である。

#### 【0095】

本実施形態の半導体モジュール30は、第1配線層としての配線層14の絶縁樹脂層70と反対側の表面に設けられた絶縁樹脂層12と、絶縁樹脂層12の配線層14と反対側の表面に形成された第2配線層としての配線層15と、配線層15の絶縁樹脂層12側の表面に設けられた突起電極20と、をさらに備える。

#### 【0096】

絶縁樹脂層12を形成する材料としては、たとえば、BTRレジンなどのメラミン誘導体、液晶ポリマー、エポキシ樹脂、PPE樹脂、ポリイミド樹脂、フッ素樹脂、フェノール樹脂、ポリアミドビスマレイミドなどの熱硬化性樹脂が例示される。半導体モジュール30の放熱性向上の観点から、絶縁樹脂は高熱伝導性を有することが望ましい。このため、絶縁樹脂層12は、銀、ビスマス、銅、アルミニウム、マグネシウム、錫、亜鉛およびこれらの合金などを高熱伝導性フィラーとして含有することが好ましい。

30

#### 【0097】

配線層15は導電材料、好ましくは圧延金属、さらには圧延銅により形成される。配線層14と配線層15とは、配線層15に設けられた突起電極20を介して電気的に接続されている。また、配線層15には、所定の位置にはんだバンプ21が形成されている。はんだバンプ21を形成する位置は、たとえば再配線で引き回した先の位置である。配線層15の絶縁樹脂層12と反対側の表面には、配線保護層95が設けられ、配線保護層95に形成された開口95aにおいて、はんだバンプ21が配線層15に接続されている。

40

#### 【0098】

##### (半導体モジュールの製造方法)

図15(A)、(B)は、半導体モジュール30の形成方法を示す工程断面図である。

#### 【0099】

図2(A)～(E)、および、図3(A)～(D)に示す工程に続いて、図2(A)、(B)に示す工程と同様にして突起電極20が形成された銅板19を準備する。そして、図15(A)に示すように、絶縁樹脂層70および配線層14が圧着された半導体素子5

50

0と、銅板19との間に、絶縁樹脂層12を挟持し、図3(A)、(B)に示す工程と同様にしてプレス加工により配線層14、絶縁樹脂層12および銅板19を加熱圧着する。

#### 【0100】

次に、図15(B)に示すように、銅板19の配線層形成領域に、配線層14と同様にして、所定パターンの配線層15を形成する。配線層15の形成に用いたレジストを剥離した後、図4(A)、(B)に示す工程と同様にして開口95aを有する配線保護層95を積層し、開口95aにおいて露出している配線層15上にはんだバンプ21を形成する。

#### 【0101】

以上説明した製造工程により、半導体モジュール30が得られる。なお、実施形態2の製造方法に対して本実施形態の製造方法を適用しても、同一の半導体モジュール30を得ることができる。このような多層配線構造とした場合でも、実施形態1または2と同様の効果を得ることができる。10

#### 【0102】

##### (実施形態7)

本実施形態に係る半導体モジュール30は、絶縁樹脂層12と、配線層14を第1配線層とした場合に第2配線層としての配線層15と、配線層15の絶縁樹脂層12側の表面に設けられた突起電極20と、を備えている点が実施形態3と異なる。半導体モジュール30のその他の構成、および突起電極16および被覆部18の製造方法などについては、実施形態1または3と基本的には同様であり、また絶縁樹脂層12や配線層15、突起電極20の構成および形成方法は実施形態6と同様であるため、その説明は適宜省略する。20

#### 【0103】

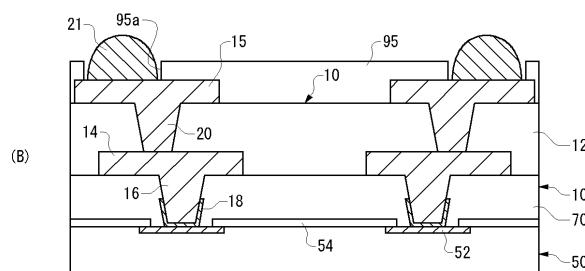

図16は、実施形態7に係る素子搭載用基板10およびこれを用いた半導体モジュール30の構成を示す概略断面図である。

#### 【0104】

本実施形態の半導体モジュール30は、第1配線層としての配線層14の絶縁樹脂層70と反対側の表面に設けられた絶縁樹脂層12と、絶縁樹脂層12の配線層14と反対側の表面に形成された第2配線層としての配線層15と、配線層15の絶縁樹脂層12側の表面に設けられた突起電極20と、をさらに備える。配線層14と配線層15とは、突起電極20を介して電気的に接続されている。また、配線層15の表面には開口95aを有する配線保護層95が積層されている。このような多層配線構造とした場合でも、実施形態3と同様の効果を得ることができる。30

#### 【0105】

##### (実施形態8)

本実施形態に係る半導体モジュール30は、絶縁樹脂層12と、配線層14を第1配線層とした場合に第2配線層としての配線層15と、配線層15の絶縁樹脂層12側の表面に設けられた突起電極20と、を備えている点が実施形態4と異なる。半導体モジュール30のその他の構成、および突起電極16および被覆部18の製造方法などについては、実施形態1または4と基本的には同様であり、また絶縁樹脂層12や配線層15、突起電極20の構成および形成方法は実施形態6と同様であるため、その説明は適宜省略する。40

#### 【0106】

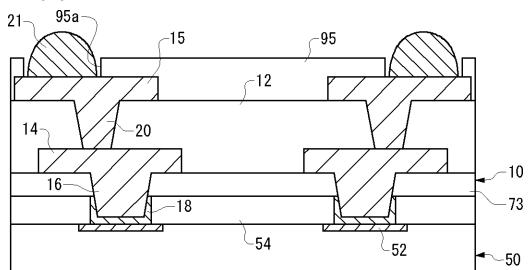

図17は、実施形態8に係る素子搭載用基板10およびこれを用いた半導体モジュール30の構成を示す概略断面図である。

#### 【0107】

本実施形態の半導体モジュール30は、第1配線層としての配線層14の絶縁樹脂層70と反対側の表面に設けられた絶縁樹脂層12と、絶縁樹脂層12の配線層14と反対側の表面に形成された第2配線層としての配線層15と、配線層15の絶縁樹脂層12側の表面に設けられた突起電極20と、をさらに備える。また、配線層15の表面には開口95aを有する配線保護層95が積層されている。このような多層配線構造とした場合でも、実施形態4と同様の効果を得ることができる。50

## 【0108】

(実施形態9)

本実施形態に係る半導体モジュール30は、絶縁樹脂層12と、配線層14を第1配線層とした場合に第2配線層としての配線層15と、配線層15の絶縁樹脂層12側の表面に設けられた突起電極20と、を備えている点が実施形態5と異なる。半導体モジュール30のその他の構成、および突起電極16および被覆部18の製造方法などについては、実施形態1または5と基本的には同様であり、また絶縁樹脂層12や配線層15の構成および形成方法は実施形態6と同様であるため、その説明は適宜省略する。

## 【0109】

図18は、実施形態9に係る素子搭載用基板10およびこれを用いた半導体モジュール30の構成を示す概略断面図である。

10

## 【0110】

本実施形態の半導体モジュール30は、第1配線層としての配線層14の絶縁樹脂層73と反対側の表面に設けられた絶縁樹脂層12と、絶縁樹脂層12の配線層14と反対側の表面に形成された第2配線層としての配線層15と、配線層15の絶縁樹脂層12側の表面に設けられた突起電極20と、をさらに備える。また、配線層15の表面には開口95aを有する配線保護層95が積層されている。このような多層配線構造とした場合でも、実施形態5と同様の効果を得ることができる。

## 【0111】

(実施形態10)

20

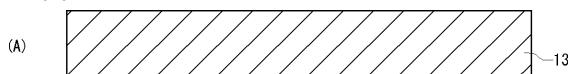

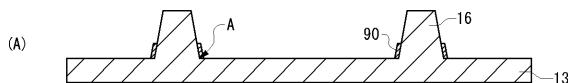

実施形態10は、素子搭載用基板が基端部Aを被覆する他の被覆部を備えた点が実施形態1と異なる。以下、本実施形態について説明する。なお、素子搭載用基板のその他の構成、半導体モジュールの構成、素子搭載用基板の製造工程を除く半導体モジュールの製造工程は実施形態1と基本的に同一である。実施形態1と同一の構成については同一の符号を付し、その説明は適宜省略する。

## 【0112】

図19は、実施形態10に係る素子搭載用基板10およびこれを用いた半導体モジュール30の構成を示す概略断面図である。半導体モジュール30は、素子搭載用基板10およびこれに搭載された半導体素子50を備える。

## 【0113】

30

素子搭載用基板10は、絶縁樹脂層70と、配線層14と、突起電極16と、突起電極16の頂部面と側面のうち配線層14と接する領域を除いた頂部面と連続する領域とを被覆する被覆部18とを備える。配線層14の絶縁樹脂層70と反対側の表面には、配線保護層24が設けられ、開口24aにおいて、配線層14にはんだバンプ21が形成されている。突起電極16は、絶縁樹脂層70を貫通し、半導体素子50に設けられた素子電極52と電気的に接続されている。

## 【0114】

また、素子搭載用基板10は、被覆部18とは不連続であり、かつ配線層14の表面と突起電極16の側面とが接する基端部Aを含む、基端部Aからの一部を少なくとも被覆する他の被覆部90を備える。基端部Aは、配線層14と突起電極16との境界であり、他の被覆部90は、基端部Aを含む領域を被覆している。他の被覆部90は、基端部Aと隣接する配線層14上の領域を被覆していてもよい。

40

## 【0115】

他の被覆部90は、被覆部18と同様の金属材料からなる金属層であり、たとえば突起電極16の降伏応力の40%より大きく100%以下の降伏応力を有する金属材料を用いて電解めっき法あるいは無電解めっき法により形成された金属めっき層である。あるいは導電ペーストを用いて形成された導電ペースト層である。金属層は複数層であってもよく、たとえばNiめっき層とAuめっき層との積層が例示される。本実施形態においては、銅からなる突起電極16の降伏応力に対して60%の降伏応力を有する金(Au)およびニッケル(Ni)からなるNi/Auめっき層である。さらに突起電極16と他の被覆部

50

90とが同一材料からなる場合には、突起電極16と他の被覆部90とは一体的に形成されるものであってもよく、この場合には突起電極16は、その側面の被覆部18よりも配線層14側（基端部A側）に、配線層14側が太くなるような段差を有し、当該段差により太くなった領域が配線層14まで延在する形状となる。

#### 【0116】

半導体素子50は、素子電極52が設けられた電極面を絶縁樹脂層70側に向けて絶縁樹脂層70に圧着されている。また、半導体素子50には、保護層54が積層されている。

#### 【0117】

(半導体モジュールの製造方法)

10

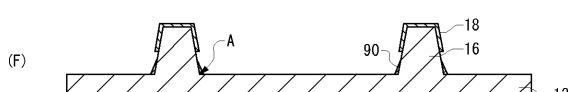

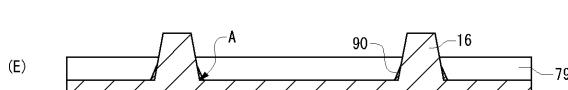

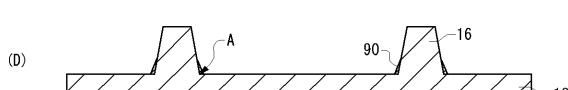

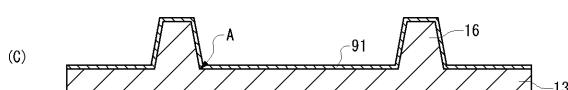

図20(A)～(F)は、突起電極16と、被覆部18および他の被覆部90の形成方法を示す工程断面図である。

#### 【0118】

図20(A)に示すように、少なくとも、突起電極16の高さと配線層14の厚さとの和より大きい厚さを有する銅板13を用意する。

#### 【0119】

次に、図20(B)に示すように、周知のフォトリソグラフィ法およびエッティング法を用いて、銅板13の一方の主表面S1に突起電極16を形成する。銅板13の表面と突起電極16の側面とが接する部分が基端部Aである。

#### 【0120】

20

次に、図20(C)に示すように、たとえば電解めっき法により、銅板13の突起電極16が形成された側の主表面にめっき層91を形成する。

#### 【0121】

次に、図20(D)に示すように、周知の異方性ドライエッティングにより他の被覆部90を形成する。ここで、異方性ドライエッティングのエッティング方向を、銅板13の突起電極16が形成された側の主表面に対して略垂直な方向として、エッティング方向から見た層厚の違いにより基端部A上にめっき層が残り、この残存しためっき層が他の被覆部90となる。

#### 【0122】

次に、図20(E)に示すように、銅板13の突起電極16が形成された側の主表面に、所定の高さまでレジスト79を積層する。積層するレジスト79の高さは、被覆部18の被覆領域に応じた高さである。

30

#### 【0123】

次に、図20(F)に示すように、たとえば電解めっき法または無電解めっき法により、突起電極16の露出している部分に被覆部18を形成する。被覆部18を形成した後、レジスト79を除去する。以上説明した工程により、突起電極16と、被覆部18および他の被覆部90とが形成される。

#### 【0124】

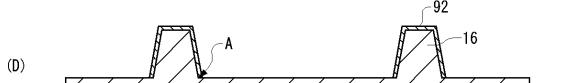

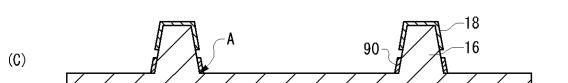

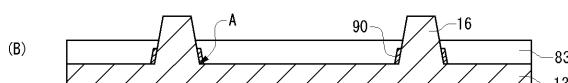

また、突起電極16と、被覆部18および他の被覆部90は、図21(A)～(E)および図22(A)～(C)に示す手順で形成することもできる。図21(A)～(E)および図22(A)～(C)は、突起電極16と、被覆部18および他の被覆部90の形成方法を示す工程断面図である。

40

#### 【0125】

図21(A)に示すように、少なくとも、突起電極16の高さと配線層14の厚さとの和より大きい厚さを有する銅板13を用意する。

#### 【0126】

次に、図21(B)に示すように、周知のフォトリソグラフィ法およびエッティング法を用いて、銅板13の一方の主表面S1に突起電極16を形成する。銅板13の表面と突起電極16の側面とが接する部分が基端部Aである。

#### 【0127】

50

次に、図21(C)に示すように、周知のフォトリソグラフィ法を用いて、銅板13の突起電極16が形成された側の主表面のうち、突起電極16の形成領域を除く領域にレジスト81を形成する。

#### 【0128】

次に、図21(D)に示すように、レジスト81をマスクとして、たとえば電解めっき法により、突起電極16の表面にめっき層92を形成する。めっき層92を形成した後、レジスト81を除去する。

#### 【0129】

次に、図21(E)に示すように、銅板13の突起電極16が形成された側の主表面に、所定の高さまでレジスト82を積層する。レジスト82の高さは、他の被覆部90の被覆領域に応じた高さである。

10

#### 【0130】

次に、図22(A)に示すように、レジスト82をマスクとして、周知のエッチング法によりめっき層91をエッチングして他の被覆部90を形成する。他の被覆部90を形成した後、レジスト82を除去する。

#### 【0131】

次に、図22(B)に示すように、銅板13の突起電極16が形成された側の主表面に、所定の高さまでレジスト83を積層する。レジスト83の高さは、被覆部18の被覆領域に応じた高さである。

#### 【0132】

次に、図22(C)に示すように、たとえば電解めっき法または無電解めっき法により、突起電極16の露出している部分に被覆部18を形成する。被覆部18を形成した後、レジスト83を除去する。以上説明した工程により、突起電極16と、被覆部18および他の被覆部90とが形成される。

20

#### 【0133】

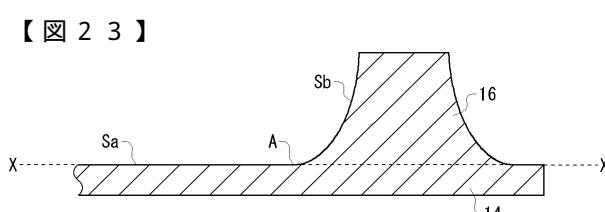

その後、実施形態1と同様に、図3(A)～(D)および図4(A)、(B)に示す手順で半導体モジュール30が形成される。なお、図23に示すように、突起電極16の側面が、配線層14と接する領域において曲率が連続的に変化するような形状であった場合、配線層14の表面と突起電極16の側面とが接する基端部Aは、配線層14の突起電極16が設けられた側の表面Saと同じ高さの基準面Xと、突起電極16の側面Sbとが交わる線あるいは点の位置に相当する。ここで、上述のように、表面Saに微細な凹凸が形成されている場合、表面Saはこれらの微細凹凸の平均高さの位置を通る面とする。

30

#### 【0134】

以下に、突起電極16に他の被覆部90を設けた効果について説明する。

#### 【0135】

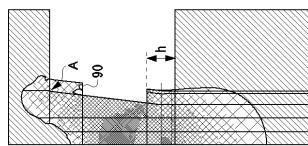

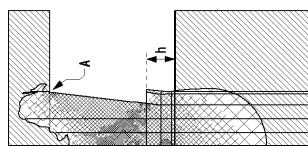

図24(A)～(C)は、降伏応力が50%で、被覆高さhが5μm(突起電極16の高さの1/8)の被覆部18が設けられた突起電極16であって、他の被覆部90の有無の点で異なるものについて、温度を25から125まで変化させた雰囲気下において発生する応力の分布をシミュレーションにより算出した模式図である。図24(A)は、突起電極16に被覆部18のみが設けられた構成における応力分布を示している。図24(B)は、突起電極16に被覆部18および他の被覆部90が設けられた構成における応力分布を示している。図24(C)は、突起電極16に被覆部18が設けられると共に、突起電極16の側面のうち基端部Aを含まない領域に被覆部18とは非連続の金属層93が設けられた構成における応力分布を示している。

40

#### 【0136】

図24(A)に示すように、被覆部18のみが設けられた構成では、基端部Aに応力が集中している。一方、図24(B)に示すように、被覆部18の基端部Aを被覆する他の被覆部90が設けられた構成では、被覆部18と素子電極52との界面における応力の集中が緩和された状態のままで、基端部Aにかかる応力の集中が緩和されている。したがって、突起電極16に、被覆部18に加えて他の被覆部90を設けることで、被覆部18と

50

素子電極 52との界面における最大応力を小さくするとともに、突起電極 16の基端部 Aにかかる応力を小さくすることができる。

#### 【0137】

また、図 24 (C) に示すように、突起電極 16の側面のうち基端部 Aを含まない領域に被覆部 18とは非連続の金属層 93が設けられた構成では、基端部 Aにかかる応力の集中は緩和されているが、被覆部 18と素子電極 52との界面における応力が増大してしまっている。また、被覆部 18の基端部 Aに近い領域に応力が集中している。このことから、突起電極 16の側面のうち基端部 Aを含む領域を被覆する他の被覆部 90を設けることで、被覆部 18と素子電極 52との界面における最大応力を小さくするとともに、突起電極 16の基端部 Aにかかる応力を小さくすることができる。 10

#### 【0138】

以上より、本実施形態によれば、実施形態 1の上述の効果に加えて、さらに次のような効果が得られる。すなわち、本実施形態では、突起電極に基端部を含む領域を被覆する他の被覆部を設けることで、温度変化によって生じる応力が集中する位置を被覆部と突起電極との界面から突起電極側に移動させて、界面における最大応力を小さくすることができるとともに、基端部への応力の集中を緩和することができる。これにより、素子搭載用基板に半導体素子が搭載された状態において、素子電極にダメージを与えるおそれが低減するとともに、突起電極にクラックなどが発生するおそれが低減し、突起電極と素子電極との接続信頼性がさらに向上し、ひいては素子搭載用基板と半導体素子との接続信頼性がさらに向上する。 20

#### 【0139】

##### (実施形態 11)

次に、本発明の半導体モジュールを備えた携帯機器について説明する。なお、携帯機器として携帯電話に搭載する例を示すが、たとえば、個人用携帯情報端末 (PDA)、デジタルビデオカメラ (DVC)、及びデジタルスチルカメラ (DSC) といった電子機器であってもよい。

#### 【0140】

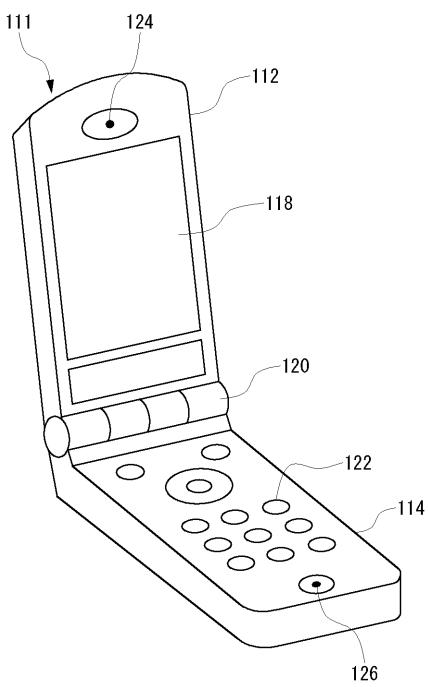

図 25 は本発明の実施形態に係る半導体モジュール 30 を備えた携帯電話の構成を示す図である。携帯電話 111 は、第 1 の筐体 112 と第 2 の筐体 114 が可動部 120 によって連結される構造になっている。第 1 の筐体 112 と第 2 の筐体 114 は可動部 120 を軸として回動可能である。第 1 の筐体 112 には文字や画像等の情報を表示する表示部 118 やスピーカ部 124 が設けられている。第 2 の筐体 114 には操作用ボタンなどの操作部 122 やマイク部 126 が設けられている。なお、本発明の各実施形態に係る半導体モジュールはこうした携帯電話 111 の内部に搭載されている。 30

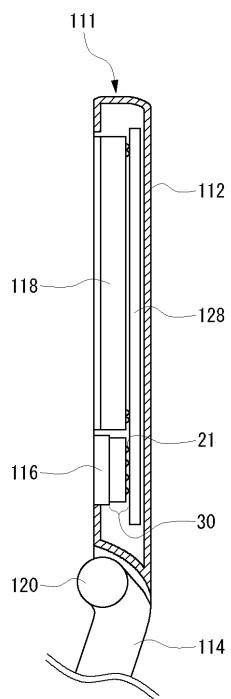

#### 【0141】

図 26 は図 25 に示した携帯電話の部分断面図 (第 1 の筐体 112 の断面図) である。本発明の各実施形態に係る半導体モジュール 30 は、はんだバンプ 21 を介してプリント基板 128 に搭載され、こうしたプリント基板 128 を介して表示部 118 などと電気的に接続されている。また、半導体モジュール 30 の裏面側 (はんだバンプ 21 とは反対側の面) には金属基板などの放熱基板 116 が設けられ、たとえば、半導体モジュール 30 から発生する熱を第 1 の筐体 112 内部に籠もらすことなく、効率的に第 1 の筐体 112 の外部に放熱することができるようになっている。 40

#### 【0142】

本発明の実施形態に係る半導体モジュール 30 を備えた携帯機器によれば、被覆部 18 と素子電極 52との接続信頼性が向上し、ひいては半導体モジュール 30 の接続信頼性が向上するので、こうした半導体モジュール 30 を搭載した携帯機器の信頼性が向上する。

#### 【0143】

本発明は、上述の各実施形態に限定されるものではなく、当業者の知識に基づいて各種の設計変更等の変形を加えることも可能であり、そのような変形が加えられた実施形態も本発明の範囲に含まれうるものである。 50

## 【0144】

たとえば、上述の各実施形態では、素子搭載用基板の配線層は単層または2層であったが、これに限定されず、配線層はさらに多層構造であってもよい。また、配線層の最外面にはんだバンプが形成されているが、これに限定されない。たとえば、配線層にMOSトランジスタを接着し、MOSトランジスタのソース電極、ドレイン電極およびゲート電極を配線層に電気的に接続してもよい。

## 【0145】

さらに、上述したような突起電極を用いて加圧により塑性流動を引き起こす絶縁樹脂層を介して異なる配線層間を電気的に接続する手段は、ウェハレベルCSP (Chip Size Package) プロセスと呼ばれる半導体パッケージの製造プロセスに適用することができる。これによれば、半導体モジュールの薄型化・小型化を図ることができる。

10

## 【図面の簡単な説明】

## 【0146】

【図1】実施形態1に係る素子搭載用基板および半導体モジュールの構成を示す概略断面図である。

【図2】図2(A)～(E)は、突起電極および被覆部の形成方法を示す工程断面図である。

【図3】図3(A)～(D)は、突起電極と素子電極との接続方法を示す工程断面図である。

20

【図4】図4(A)、(B)は、突起電極と素子電極との接続方法を示す工程断面図である。

【図5】温度変化により被覆部と素子電極との界面に生じる最大応力の変化を示すグラフである。

【図6】(A)、(B)は、温度変化により生じる応力の分布の変化を示す模式図である。

【図7】図7(A)～(D)は、実施形態2に係る半導体モジュールの製造方法の工程断面図である。

【図8】図8(A)～(F)は、実施形態3に係る半導体モジュールの製造方法の工程断面図である。

30

【図9】図9(A)～(C)は、実施形態3に係る半導体モジュールの製造方法の工程断面図である。

【図10】図10(A)～(D)は、実施形態4に係る半導体モジュールの製造方法の工程断面図である。

【図11】図11(A)、(B)は、実施形態4に係る半導体モジュールの製造方法の工程断面図である。

【図12】図12(A)～(D)は、実施形態5に係る半導体モジュールの製造方法の工程断面図である。

【図13】図13(A)は、実施形態5に係る半導体モジュールの製造方法の工程断面図である。

40

【図14】実施形態6に係る素子搭載用基板10および半導体モジュールの構成を示す概略断面図である。

【図15】図15(A)、(B)は、半導体モジュールの形成方法を示す工程断面図である。

【図16】実施形態7に係る素子搭載用基板および半導体モジュールの構成を示す概略断面図である。

【図17】実施形態8に係る素子搭載用基板および半導体モジュールの構成を示す概略断面図である。

【図18】実施形態9に係る素子搭載用基板および半導体モジュールの構成を示す概略断面図である。

50

【図19】実施形態10に係る素子搭載用基板および半導体モジュールの構成を示す概略断面図である。

【図20】図20(A)～(F)は、突起電極、被覆部および他の被覆部の形成方法を示す工程断面図である。

【図21】図21(A)～(E)は、突起電極、被覆部および他の被覆部の形成方法を示す工程断面図である。

【図22】図22(A)～(C)は、突起電極、被覆部および他の被覆部の形成方法を示す工程断面図である。

【図23】基端部を説明するための図である。

【図24】図24(A)～(C)は、温度変化により生じる応力の分布の変化を示す模式図である。 10

【図25】実施形態11に係る携帯機器の構成を示す図である。

【図26】携帯機器の部分断面図である。

#### 【符号の説明】

##### 【0147】

A 基端部、 10 素子搭載用基板、 12 絶縁樹脂層、 14, 15 配線層、

16 突起電極、 18 被覆部、 20 突起電極、 21 はんだバンプ、 24

配線保護層、 24a 開口、 30 半導体モジュール、 50 半導体素子、 5

2 素子電極、 54 保護層、 70 絶縁樹脂層、 72, 73 樹脂層、 90

他の被覆部、 93 金属層、 95 配線保護層、 95a 開口。 20

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

30

【図10】

【図11】

30

【図 1 2】

【図 1 3】

30

【図 1 4】

【図 1 5】

【図 1 6】

【図 1 7】

3030

【図18】

【図19】

30

【図21】

【図20】

【図22】

【図24】

(a)

(b)

(c)

【図25】

【図26】

---

フロントページの続き

(72)発明者 柳瀬 康行

大阪府守口市京阪本通2丁目5番5号 三洋電機株式会社内

審査官 今井 淳一

(56)参考文献 特開平08-111574 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/12

H01L 21/60