(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4615707号

(P4615707)

(45) 発行日 平成23年1月19日(2011.1.19)

(24) 登録日 平成22年10月29日(2010.10.29)

(51) Int.Cl.

H01L 21/768 (2006.01)

F 1

H01L 21/90

A

請求項の数 8 (全 15 頁)

(21) 出願番号 特願2000-510165 (P2000-510165)

(86) (22) 出願日 平成10年8月17日 (1998.8.17)

(65) 公表番号 特表2001-516146 (P2001-516146A)

(43) 公表日 平成13年9月25日 (2001.9.25)

(86) 國際出願番号 PCT/US1998/017010

(87) 國際公開番号 WO1999/009593

(87) 國際公開日 平成11年2月25日 (1999.2.25)

審査請求日 平成17年8月1日 (2005.8.1)

(31) 優先権主張番号 08/914,521

(32) 優先日 平成9年8月19日 (1997.8.19)

(33) 優先権主張国 米国(US)

前置審査

(73) 特許権者 390040660

アプライド マテリアルズ インコーポレイテッド

APPPLIED MATERIALS, INCORPORATED

アメリカ合衆国 カリフォルニア州 95054 サンタクララ バウアーズ アベニュー 3050

(74) 代理人 100088155

弁理士 長谷川 芳樹

(74) 代理人 100094318

弁理士 山田 行一

(74) 代理人 100107456

弁理士 池田 成人

最終頁に続く

(54) 【発明の名称】デュアルダマシン金属化方法

## (57) 【特許請求の範囲】

## 【請求項1】

デュアルダマシンバイア及びワイヤ輪郭を有する誘電体層中にデュアルダマシン相互接続部を形成する方法において、前記方法が：

- a ) 前記誘電体層の露出表面上にバリヤ層を堆積するステップと；

- b ) 前記バリヤ層上で導電性材料の第1部分を電気メッキして、前記バイア輪郭を充填するステップと；

- c ) 前記導電性材料の前記第1部分上に前記導電性材料の第2部分を物理的気相堆積して、前記ワイヤ輪郭を充填するステップと；

- d ) 前記導電性材料と前記バリヤ層とを平坦化するステップと；

物理的気相堆積法によって堆積された前記導電性材料の前記第2部分がドーピングされた導電性材料を含み、

前記導電性材料の前記第2部分を堆積する前に、電気メッキによって堆積された前記導電性材料の前記第1部分がアニールされる方法。

## 【請求項2】

デュアルダマシンバイア及びワイヤ輪郭を有する誘電体層中にデュアルダマシン相互接続部を形成する方法において、前記方法が：

- a ) 前記誘電体層の露出表面上にバリヤ層を堆積するステップと；

- b ) 前記バリヤ層上に導電性材料の第1部分を電気メッキするステップと；

10

20

c ) 前記導電性材料の前記第 1 部分をアニールして、前記バイア輪郭を充填するステップと；

d ) 前記導電性材料の前記第 1 部分上に前記導電性材料の第 2 部分を物理的気相堆積して、前記ワイヤ輪郭を充填するステップと；

e ) 前記導電性材料と前記バリヤ層とを平坦化するステップと；

を含む方法。

**【請求項 3】**

前記物理的気相堆積された導電性材料が銅又はドーピングされた銅である請求項 2 に記載の方法。 10

**【請求項 4】**

前記バリヤ層がチタン、窒化チタン、窒化シリコンチタン、窒化タングステン、窒化シリコンタングステン、タンタル、窒化タンタル、窒化シリコンタンタル、ドーピングされたシリコン、アルミニウム及び酸化アルミニウムからなる群から選択された材料を含む請求項 3 に記載の方法。 20

**【請求項 5】**

デュアルダマシンバイア及びワイヤ輪郭を有する誘電体層中にデュアルダマシン相互接続部を形成する方法において、前記方法が： 20

a ) 前記誘電体層の露出表面上にバリヤ層を堆積するステップと；

b ) 前記バリヤ層上に導電性金属のコンフォーマルな第 1 部分を化学的気相堆積するステップと；

c ) 前記導電性金属のコンフォーマルな前記第 1 部分をアニールして、前記導電性金属のコンフォーマルな前記第 1 部分の表面を平滑化するステップと；

d ) 前記導電性金属の前記第 1 部分上に前記導電性金属の第 2 部分を電気メッキして前記バイア及びワイヤ輪郭を充填するステップと；

e ) 前記導電性金属と前記バリヤ層とを平坦化するステップと；

を含む方法。 30

**【請求項 6】**

前記導電性金属が銅又はドーピングされた銅である請求項 5 に記載の方法。

**【請求項 7】**

前記バリヤ層がチタン、窒化チタン、窒化シリコンチタン、窒化タングステン、窒化シリコンタングステン、タンタル、窒化タンタル、窒化シリコンタンタル、ドーピングされたシリコン、アルミニウム及び酸化アルミニウムからなる群から選択された材料を含む請求項 5 に記載の方法。 30

**【請求項 8】**

前記導電性金属のコンフォーマルな第 1 部分を化学的気相堆積する前に、前記バリヤ層をプラズマ処理に晒すステップをさらに含む請求項 5 に記載の方法。

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

本発明は半導体デバイスを製造するための金属化方法に関する。より詳細には、本発明は誘電体層中のデュアルダマシンバイア／ワイヤ輪郭を金属化して金属製の相互接続部と金属バイアプラグを形成する方法に関する。 40

**【0002】**

**【従来の技術】**

サブ半（ハーフ）ミクロンの多レベル金属化方法は、次世代の超大規模集積回路（VLSI）にとって鍵となる技術の 1 つである。この技術の核心を成す多レベル相互接続では、コンタクト、バイア又は他の外形物を含む、高アスペクト比のアパー チュア内に形成された相互接続部の外形物を平坦化する必要がある。これらの相互接続部外形物を高い信頼性で形成することは、VLSI の成功と、個々の基板とダイス上での回路密度と品質と向上させるための継続的な努力と、にとって非常に重要なことである。 50

## 【0003】

回路密度が高まるに連れて、バイアとコンタクトと他の外形物と、さらにこれら同士間に

ある誘電体材料との幅は減少しなければならず、この結果、外形物のアスペクト比が増大

することになる。したがって、外形物幅対外形物高さの比が4:1以上である高アスペクト

比を有する空隙のない外形物を形成しようとする大変な努力が継続されている。このような

方法の1つでは、基板表面上にある露出した核生成表面上にある材料に対してだけ選

択的に化学的気相堆積法(CVD)が実行される。選択的CVDでは、化学的気相の成分

と導電性基板とが接触するところに膜の層が堆積される。この成分はこのような基板上に

核生成して金属表面を生成し、この上にさらに堆積プロセスが続く。

## 【0004】

選択的CVD金属堆積法は、CVD金属前駆気体を分解するには通常は導電性核生成膜か

らの電子発生源を必要とするという事実に基づいている。従来の選択的CVD金属堆積プロ

セスによれば、金属は、金属膜と、下地の導電層から出ているドーピングされたシリコ

ン又は金属シリサイドと、のどちらかが露出しているアパーチュアの底部に成長しなけれ

ばならないのであって、フィールドやアパーチュアの壁などの誘電体表面上に成長しては

ならない。下地を成す金属膜又はドーピングされたシリコンは、誘電体フィールドやアパ

ーチュアの壁と違って導電性であり、したがって、金属前駆気体の分解に必要な電子を供

給し、その結果、金属が堆積される。選択的な堆積をすることによって、非常に小さいデ

イメンジョン( $< 0.25 \mu m$ )と高いアスペクト比( $> 5:1$ )を持つバイアやコンタ

クトの開口を充填することが可能なCVD金属をアパーチュア中で「上昇型」(bottom-up)

エピタキシャル成長させることができる。

10

## 【0005】

単体アルミニウム(A1)とその合金が半導体処理に置いてラインとプラグを形成するた

めに用いられる伝統的な金属であったが、それはアルミニウムの抵抗率が低く、酸化シリ

コン(SiO<sub>2</sub>)に対する固着性が優れ、パターン化がし易く、純度が高いからである。

さらに、上記の選択的なCVDプロセスを容易化するアルミニウムの前駆気体が入手可能

である。しかしながら、アルミニウムは抵抗率が高く電子移動に関して問題がある。電子

移動は、金属回路の、その製作の途中で発生する故障に対して、動作中に発生する現象で

ある。電子移動は、回路中で確立された電場で金属が拡散することによって引き起こされ

る。金属は何時間も動作するうちに一方の端から他方の端に移送し、ついには完全に剥離

して回路に開口を空ける。この問題は場合によっては銅のドーピングとテクスチャを改善

することによって解決する。しかしながら、電子移動は電流密度が増加するに連れて悪化

する問題である。

20

## 【0006】

一方、銅とその合金はアルミニウムより抵抗率がさらに低く、電子移動抵抗性はかなり高

い。これらの特徴は集積密度が高くなりデバイス速度が速くなるに連れて増す電流密度を

支えるためには重要な特徴である。しかしながら、銅金属を多レベル金属化システムに組

み込むことにまつわる主要な問題として、(1)エッチング技法を用いて金属をパターン化

するのが困難であることと、(2)成熟したCVDプロセスがないのでPVDを用いて

小さいバイアを充填するのが困難であること、が挙げられる。サブミクロンという最小外

形物寸法であるデバイスにとって、銅のパターン化のために湿式エッチングを用いるこ

とは、液体の表面張力のためと、等方性エッチングプロファイルのためと、過剰エッチ

ングの制御が困難であるためと、信頼性の高い乾式エッチングプロセスがないためと、によ

つて受け入れることができなかった。

30

## 【0007】

選択的無電解メッキ法や選択的化学的気相堆積法や高温反応性イオンエッチング法やリフ

トオフ処理を含む、パターン化された銅製の相互接続部を発生するための方法がいくつか

提案されている。無電解メッキ法では、相互接続部の床を床導電性にするように促す必要

がある。これで、導電性床を帯電させて、溶液又は浴槽から銅を引き付ける。

40

## 【0008】

50

選択的化学的気相堆積法では一般的には、電導性表面上で金属前駆気体を分解させる。しかしながら、選択的気相堆積法のための、信頼性の高い成熟したプロセスはない。

#### 【0009】

高温反応性イオンエッティング法（R I E）すなわちスパッタエッティング法もまた銅層をパターン化するために用いられてきた。さらに、R I Eは、余分の金属を解放層によって構造体からリフトオフして銅の外形物を内部に形成した表面を残すリフトオフ処理法と一緒に用いることができる。

#### 【0010】

銅製の金属配線のためのさらに別のある方法は、 $\text{SiO}_2$ などの絶縁性材料製の厚い層内になる溝及び／又はコンタクトをパターン化してエッティングする。この後で、Ti、TiW又はTiNなどのバリヤ金属製の薄い層を絶縁層の頂部並びに溝及び／又はコンタクト内部に設けて拡散バリヤとし、これによって、次いでシリコン中とこのような金属と酸化物間に堆積される予定の金属を内部拡散させてもよい。バリヤ金属が堆積された後で、銅製の層を堆積させて溝を完全に充填する。10

#### 【0011】

ある周知の金属化技法は、バイアが下地の層を露出させる床を有する、デュアルダマシンバイア／ワイヤの輪郭を有する誘電体層中にデュアルダマシン相互接続部を形成する方法である。この方法は、バリヤ層に物理的気相堆積法（P V D）を実施するステップと、好みしくは銅である導電性金属に物理的気相堆積法を実施するステップと、次いで、この導電性金属を電気メッキしてバイアと溝を充填するステップと、を含んでいる。最後に、この堆積層と誘電体層とは、化学機械的研磨法などによって平坦化されて導電性ワイヤを輪郭決め（画成）する。20

#### 【0012】

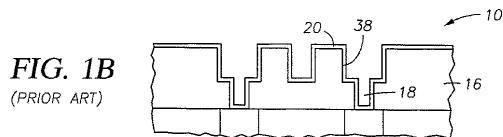

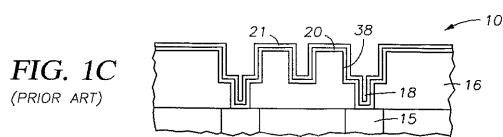

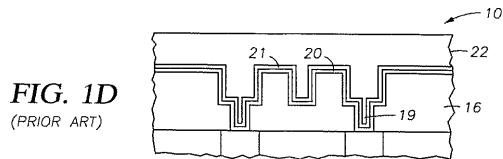

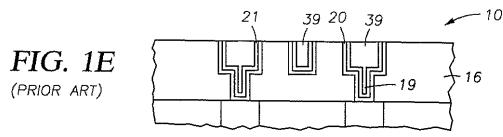

図1（a）～（e）を参照すると、導電性外形物15を含んでいる下地層14の上方に形成された誘電体層16を含む、層化された構造体10の断面図が示されている。下地層14はドーピングされたシリコン基板という形態をとったり又は基板上に最初に形成された又は次いで形成された導電性層であったりする。誘電体層16は技術上周知の手順に従つて下地層14の上方に形成し、これによって集積回路全体の1部を形成する。誘電体層16は、ひとたび形成されるとエッティングされてデュアルダマシンバイア／ワイヤ輪郭を形成するが、この場合、バイアは、導電性外形物15の小さい部分を露出する床30を有している。誘電体層16のエッティングは、プラズマエッティングを含むなんらかの誘電体エッティングプロセスによって遂行される。二酸化シリコンと有機材料をエッティングする具体的な技法には、それぞれ緩衝されたフッ化水素酸及びアセトンすなわちE K Cなどの化合物を用いる。しかしながら、パターン化は技術上周知の方法を用いて実行され得る。30

#### 【0013】

図1（a）を参照すると、誘電体層16中に形成されたデュアルダマシンのバイアとワイヤの輪郭の断面図が図示されている。このバイアとワイヤの輪郭によって、下地導電性外形物15との電気的接続部となる導電性相互接続部の堆積が容易となる。この輪郭は、バイア壁34と、導電性外形物15の少なくとも1部分を露出させている床30と、を有するバイア32と；溝壁38を有する溝17と；を提供する。40

#### 【0014】

図1（b）を参照すると、P V DによるTa N製のバリヤ層20がバイアとワイヤの輪郭上に堆積されてバイア32に穴18を残している。このバリヤ層はチタン、チッ化チタン、タンタル又はチッ化タンタルから形成するのが好ましい。ここで用いられるプロセスはP V DやC V Dや合成C V D／P V Dであり、これによってテクスチャと膜の特性を向上させる。このバリヤ層が銅の拡散を制限して、相互接続部の信頼性を劇的に向上させる。このバリヤ層は厚さ約25オングストローム（）から約400であるのが好ましく、約100であるのが最も好ましい。

#### 【0015】

図1（c）を参照すると、P V Dによる銅製の層21がワイヤ輪郭の壁34及び38及び50

床 3 0 の上方でバリヤ層 2 0 上に堆積されている。ここで用いられる金属もまたアルミニウム又はタングステンである。PVD 銅層 2 1 は追加の金属層に対して良好な固着性を持つ。

#### 【 0 0 1 6 】

図 1 ( d ) を参照すると、銅 2 2 は PVD 銅層 2 1 の上方で電気メッキされてバイア 3 2 を銅プラグ 1 9 で充填する。電気メッキは技術上良く知られており、様々な技法によって実行可能である。

#### 【 0 0 1 7 】

図 1 ( e ) を参照すると、次に、構造体 1 0 の頂部部分が、好ましくは化学機械的研磨法 ( C M P ) によって平坦化される。この平坦化プロセスの際に、銅層 2 1 、 2 2 、バリヤ層 2 0 及び誘電体 1 6 のそれぞれ 1 部分が構造体の頂部から除去されて、溝を形成された導電性ワイヤ 3 9 を持った完全に平坦化された表面を残す。

10

#### 【 0 0 1 8 】

PVD 銅堆積と比較して、プランケット CVD プロセスによって堆積された薄膜は通常は コンフォーマル であり、段差を優れて覆うようになる、すなわち、基板上に形成されたあらゆるアーチュア、それが非常に小さな形状のアーチュアであっても、その側部及び基底部上の層の厚さが均一になる。したがって、通常は、プランケット CVD がアーチュアを充填するために用いられる方法である。しかしながら、プランケット CVD プロセスに関連して 2 つの主要な困難な点がある。第 1 に、プランケット CVD による膜はアーチュア中のすべての側部から成長し、この結果、堆積層はアーチュアの上部の角から上向きにして外向きに成長し、これによって、アーチュアが完全に充填される前にアーチュアの上部表面を橋渡しする（すなわち、橋渡し又はクラウニングする）ので、充填されたアーチュアに空隙を残す。また、連続核生成層、すなわち、 CVD 層を上に確実に堆積するためのアーチュア壁上に堆積された基板の全表面の上方で核生成がなされることを保証するための連続膜層によってアーチュアの幅がさらに減少し、このため、空隙無しでアーチュアを充填する困難さが増す。第 2 に、プランケット CVD によって堆積された膜は、膜が堆積される表面の微細構造に、それが非方向性であったりランダム方向性であったりすると、適合しやすく、この結果、膜の結晶構造の方位がランダムになり、また、低反射性特性となり、電子移動性能が悪化する。

20

#### 【 0 0 1 9 】

選択的 CVD は、堆積膜を提供する CVD 前駆気体の分解には通常は、導電性核生成膜からの電子の発生源を必要とするという事実に基づいている。従来の選択的 CVD プロセスによれば、堆積は、下地層からの導電性膜又はドーピングされたシリコンが露出しているアーチュアの底部で発生すべきであって、核生成部位が全くない絶縁性のフィールドや絶縁性のアーチュア壁で発生してはならない。アーチュアの基底部で露出しているこれらの導電性膜及び / 又はドーピングされたシリコンは、誘電体表面とは異なって、前駆気体の分解とこの結果としての膜層の堆積に必要とされる電子を供給する。選択的堆積によって得られる結果は、非常に小さいディメンジョン ( $< 0.25 \mu m$ ) と高いアスペクト比 ( $> 5 : 1$ ) のバイア又はコンタクトを充填することができる、アーチュア中の膜の「上昇型」成長である。しかしながら、選択的 CVD プロセスでは、その表面中の欠陥が存在するフィールド上に好ましくない結節が形成される。

30

40

#### 【 0 0 2 0 】

一方、 PVD プロセスによって、反射性の向上した高方向性膜を堆積できるが、高アスペクト比の場合に適用する場合にはアーチュアの充填性、すなわち段差の被覆性は良好ではない。目標とする材料を物理的にスパッタリングすると、粒子が基板表面に対して鋭角で走行することになる。その結果、高アスペクト比のアーチュアを充填している場合、スパッタリングされた粒子は上部壁表面に堆積されて、アーチュアが堆積材料によって完全に充填される以前にアーチュアの開口を覆ってしまう傾向がある。この結果得られる構造は一般的に内部に空隙を含んでおり、このため基板上に形成されるデバイスの一貫性を損なう。

50

**【 0 0 2 1 】**

高アスペクト比のアパーチュアは、膜を高温で堆積させることによって PVD プロセスを用いて充填することができる。1例として、アルミニウムを400以上で堆積させて、表面上でとアパーチュア全体にわたるアルミニウムの流れを良くすることができる。この高温アルミニウムプロセスによって段差被覆性が向上することが分かっている。しかしながら、高温アルミニウムプロセスでは、バイアの充填性の信頼性が低く、堆積温度が高く、充填時間が長く、膜の反射性が悪いことがわかった。

**【 0 0 2 2 】****【発明が解決しようとする課題】**

これらの技法は利用可能であるが、なんらかの堆積材料からなる床を有するデュアルダマシン相互接続部とバイアを製作するための金属化プロセスを必要とするものである。このような高度に集積された相互接続部は、特にコンタクト他バイア形成用の高アスペクト比でサブ1/4ミクロン幅のアパーチュアでは空隙のないバイアを提供しなければならない。さらに、より高い電導性と向上した電子移動抵抗性を回路に与えるプロセスが必要である。バイア中に金属プラグを形成し溝中にワイヤを形成するための処理ステップをほとんど必要としない単純なプロセスを有することが好ましい。これがすべて、上記のプロセスによって金属エッチング技法を用いることなく達成されればさらに好ましい。

10

**【 0 0 2 3 】****【課題を解決するための手段】**

本発明はデュアルバイア／ワイヤ輪郭を有する非導電性層中にデュアルダマシン相互接続部を形成する方法を提供する。本方法は、デュアルダマシンバイア／ワイヤの輪郭内の表面を含む非導電性層の露出表面上にバリヤ層を堆積するステップを含む。次に、このバイア／ワイヤ輪郭を、空隙を防止するアニールステップを間に挟むことが望ましい2つ以上の堆積技法を用いて銅やアルミニウムなどの導電性金属で充填する。最後に、導電性金属とバリヤ層と誘電体層とを、化学機械研磨法などによって平坦化して、下層の導電性領域に対してバイアによって接続される導電性ワイヤを輪郭決めする。

20

**【 0 0 2 4 】****【発明の実施の形態】**

本発明に関する上記の特徴、利点及び目的が達成される方式が詳細に理解されるように、上記に要約した本発明を添付図面に図示する実施形態を参照して具体的により詳細に説明する。

30

**【 0 0 2 5 】**

しかしながら、添付図面は本発明の一般的な実施形態を図示するだけであり、したがって、その範囲を限定するものと考えるべきではなく、本発明は他の等しく効果的な実施形態を含むことに注意されたい。

**【 0 0 2 6 】**

本発明は一般的に、相互接続抵抗を減少させ電子移動性能を向上させた交互に集積された構造体中に相互接続部を設ける現場金属化プロセスを提供するものである。より特定的には、本発明は、バイア／ワイヤ輪郭の露出表面上にバリヤ層を組み込んだデュアルダマシン相互接続部と、このバイア／ワイヤ輪郭を充填する2つ以上の堆積技法と、を提供する。非統合技法でも適切な金属相互接続部と金属バイアプラグを提供するとはいえ、好ましい堆積技法を統合処理システムと組み合わせることが可能である。

40

**【 0 0 2 7 】**

分かりやすいように、本発明は以下に銅堆積技法を参照して説明する。しかしながら、PVD アルミニウム又はアルミニウム／銅などの他の金属プロセスを用いて本発明の利点を遂行してもよい。

**【 0 0 2 8 】**

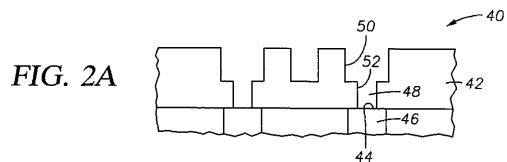

図2(a)を参照すると、本発明に従ってIC構造体40を形成するには、誘電体層42をパターン化された層の導電性層、すなわち導電性領域46の表面44の上方に従来の技法を用いて形成する。この誘電体層の厚さは単一の金属化層の約2倍であるが、それは、

50

デュアルダマシンバイア／ワイヤ輪郭がその中を通ってエッチングされるからである。現在周知であろうとまだ発見されていなかろうと、フッ素化炭素 SiO<sub>2</sub>や有機ポリマーなどの低誘電体材料を含むいかなる誘電体材料でも用いてよく、それは本発明の範囲内にある。この誘電体層はなんらかの適切な堆積向上性材料の上に体積させてよいが、好ましい堆積向上性材料には、導電性金属やドーピングされたシリコンなどがある。

#### 【0029】

誘電体層は、ひとたび堆積されると、エッチングされてデュアルダマシンバイア／ワイヤ輪郭を形成するが、この場合、バイア48は低導電性領域46を、充填されるとワイヤ又は相互接続部を形成する溝50に接続している。このバイアは一般的には急峻な側壁52による高アスペクト比を有している。誘電体層42のエッチングは、プラズマエッチングを含むいかなる誘電体エッチングプロセスによって遂行してもよい。二酸化シリコンや有機材料エッチングする具体的な技法には、それぞれ緩衝化されたフッ化水素酸とアセトンすなわちEKCなどの化合物が用いられる。しかしながら、パターン化は技術上周知ないかなる方法を用いて実行してもよい。

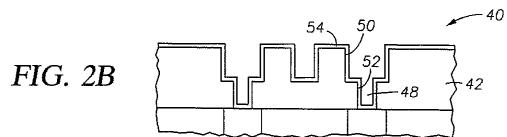

#### 【0030】

図2(b)を参照すると、バリヤ層54がバイア48／ワイヤ50輪郭内の表面を含む露出表面上に堆積されている。本発明によれば、好ましいバリヤ／ぬれ性層には、耐火材(例えば、タンゲステン(W)、窒化タンゲステン(WN)、ニオブ(Nb)、アルミニウムシリケートなど)、タンタル(Ta)、窒化タンタル(TaN)、窒化チタン(TiN)、もしくはPCV-Ti/N<sub>2</sub>詰めされた3元化合物(例えば、TiSiN、WSiNなど)などの層又はこれらの層の合成物がある。好ましいバリヤ材料には、チタン、窒化チタン、窒化シリコンチタン、窒化タンゲステン、窒化シリコンタンゲステン、タンタル、窒化タンタル、窒化シリコンタンタル、ドーピングされたシリコン、アルミニウム、酸化アルミニウムなどがある。最も好ましいバリヤ／ぬれ性材料は、約50から約100の厚さを有するPVD層として一般的に提供されるTaやTaNである。逆に、CVD-TiN又はWN製のバリヤ／ぬれ性層は一般的に、約100から約400の厚さを有する。バリヤ／ぬれ性層は堆積されると、誘電体層の上方に実質的に連続したキャップを形成して窒素で処理される。代替法としては、酸化シリコンの露出表面を窒素で処理して、銅に対するバリヤ層として有効なSi<sub>x</sub>O<sub>y</sub>N<sub>z</sub>を形成する。

#### 【0031】

バリヤ層とぬれ性層の合成層は、プロセス気体の流れを変えて、CVD銅に対する固着性を向上させることによって生成することができる。例えばWF<sub>6</sub>、N<sub>2</sub>、H<sub>2</sub>及びSiH<sub>4</sub>を反応させてWNをCVD堆積させることによって、誘電体層に対する固着性が優れたものとなる。堆積の間に窒素の流れを遮断することによって、CVDによるWN層と続いて得られるCVDによる銅層に固着するCVDによるWの最終的なバリヤ／ぬれ性層が得られる。同様に、窒素流を遮断することによって、TaN層をTa層と組み合わせたりTiN層をTi層と組み合わせたりできる。この合成層はCVDによる銅に対する固着性が向上し、これによって、バイア又は溝中に堆積した材料に対するテクスチャが向上する。代替例としては、WN、TaN又はTiNのバリヤ／ぬれ性層をH<sub>2</sub>、Ar又はHeのプラズマで事前処理してCVDによる銅層を核生成して固着性を向上させることもできる。

CVD/PVD充填

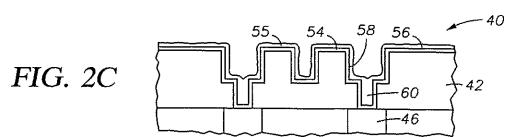

本発明による一実施形態40では、図2(c)～(e)にさらに示すように、より低い抵抗率とより大きい電子移動抵抗性を有するデュアルダマシンプラグと相互接続部とを形成する方法が提供される。このサブ半ミクロンのバイアはコンフォーマルCVDによる銅によって空隙無しで充填され、次に溝が、ドーパントとして錫を包含するのが好ましいPVD銅で充填される。堆積後は、このドーパントがCVD銅層中に移動して電子移動抵抗性を向上させる。ワイヤは構造体を平坦化することによって完了される。

#### 【0032】

図2(c)を参照すると、コンフォーマルバリヤ層54を有するデュアルシンバイア／ワイヤ輪郭の断面図が、バイアが銅プラグ60によって完全に充填されるまではフィール

10

20

30

40

50

ド領域 5 6 と側壁 5 8 との上に均一に堆積されるコンフォーマル C V D 銅層 5 5 を含んでいるところが図示されている。

#### 【 0 0 3 3 】

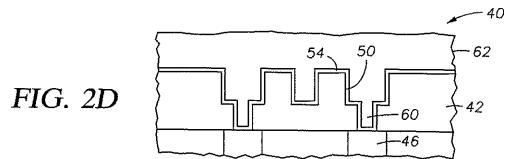

図 2 ( d ) を参照すると、銅層 6 2 が C V D 銅層の上方に物理的気相堆積されてワイヤ輪郭 5 0 を充填している。ワイヤ輪郭を充填するために、一般的に、構造体の全フィールドが P V D 銅によって覆われることになる。

#### 【 0 0 3 4 】

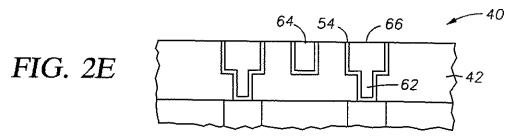

図 2 ( e ) を参照すると、次に、望ましくは化学機械的研磨法 ( C M P ) ( 例えは、カリフォルニア州サンタクララのアプライドマテリアルズ社 ( A p p l i e d M a t e r i a l s ) から入手可能な M i r r a ( 登録商標 ) システム ) によって構造体の頂部部分が平坦化される。この平坦化プロセス中に、銅 6 2 とバリヤ材料 5 4 と誘電体 4 2 との各部分が構造体の頂部から除去されて、導電性ワイヤ 6 4 と 6 6 が内部に形成された完全に平坦化された表面が残る。

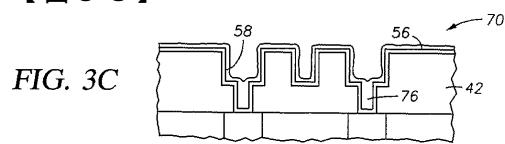

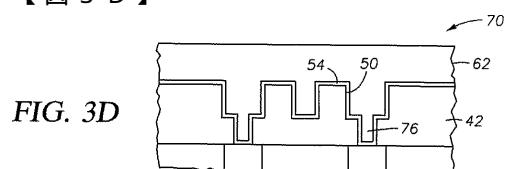

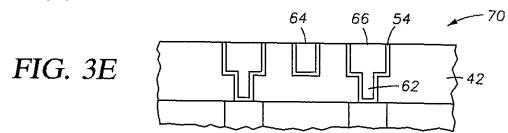

#### C V D / アニール / P V D 充填

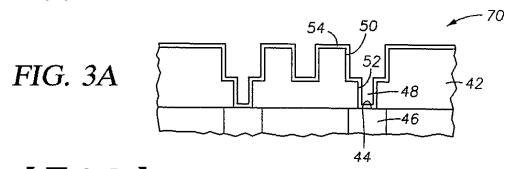

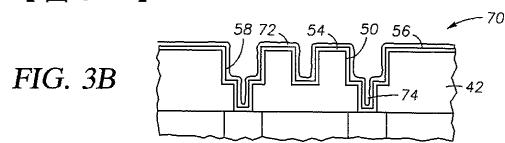

本発明による別の実施形態 7 0 では、図 3 ( a ) ~ ( e ) に示すように、サブ半ミクロンのバイアがコンフォーマル C V D 銅によって部分的に充填されて次にアニールされてバイアを充填している。次に、既述したように溝が P V D 銅で充填される。溝の幅が小さい場合、このアニールステップもまた溝を充填する。溝は、溝を下地層に接続するバイアと同じ幅を有してもよい。 P V D 銅ステップはまた用いてドーパントを提供したり、構造体を平坦化するのに十分な厚さを提供する。

#### 【 0 0 3 5 】

図 3 ( a ) に、図 2 ( b ) に示すものと類似のバリヤ層 5 4 を上部に形成したパターン化された誘電体を示す。図 3 ( b ) を参照すると、コンフォーマル バリヤ層 5 4 を有するデュアルダマシンバイア / ワイヤ輪郭の断面図が、バイアが部分的に充填されて穴 7 4 が残るまでフィールド領域 5 6 と側壁 5 8 上に均一に堆積されるコンフォーマル C V D 銅層 7 2 を含んでいる。図 3 ( c ) を参照すると、次に、C V D 銅層が約 3 0 0 から約 4 5 0 の温度にウエハを加熱することによってアニールされて、銅を穴 7 4 中にリフローさせて銅プラグ 7 6 を形成する。

#### 【 0 0 3 6 】

図 3 ( d ) を参照すると、銅層 6 2 を C V D 銅層の上方に物理的気相堆積されてワイヤ輪郭 5 0 を充填する。ワイヤ輪郭を充填するには、一般的に、構造体の全フィールドが P V D 銅によって覆われることになる。

#### 【 0 0 3 7 】

図 3 ( e ) を参照すると、次に、構造体 7 0 の頂部部分が、好ましくは化学機械的研磨法 ( C M P ) によって平坦化される。この平坦化プロセスの間に、銅 6 2 とバリヤ材料 5 4 と誘電体 4 2 との各部分が構造体の頂部から除去されて、導電性ワイヤ 6 4 と 6 6 を内部に形成した完全に平面状の表面を残す。

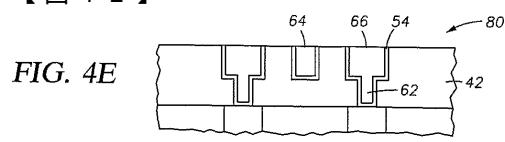

#### 電子メッキ / P V D 又は C V D / P V D 充填

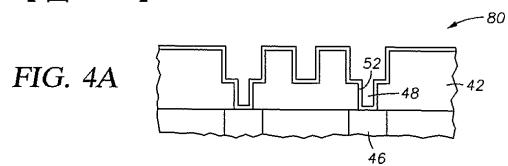

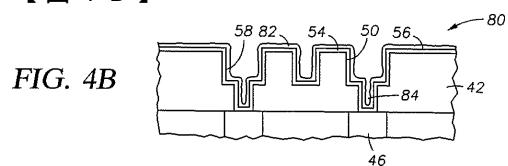

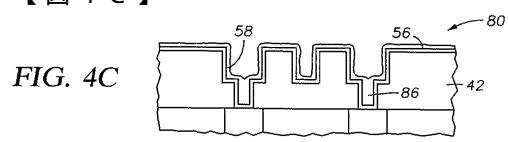

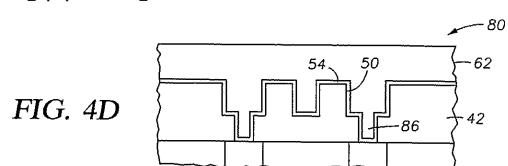

本発明の別の実施形態 8 0 では、図 4 ( a ) ~ ( e ) に示すように、サブ半ミクロンのバイアが銅の電子メッキ又はコンフォーマル P V D 銅によって部分的又は全面的に充填されている。次に、既述したように溝が P V D 銅によって非統合システム中で充填される。銅の電子メッキに続いて、P V D 銅をドーピングして電子移動性を改善するのが好ましい。ワイヤは構造を平坦化することによって完了される。

#### 【 0 0 3 8 】

図 4 ( a ) に、図 2 ( b ) に示すものと類似のバリヤ層 5 4 を上に形成したパターン化された誘電体を示す。図 4 ( b ) を参照すると、コンフォーマル バリヤ層 5 4 を有するデュアルダマシンバイア / ワイヤ輪郭の断面図が、バイアが部分的に充填されて穴 8 4 が残るまで、フィールド領域 5 6 と側壁 5 8 上に均一に堆積されるコンフォーマル 銅電気メッキ層 8 2 を含んでいる。図 4 ( c ) を参照すると、次に、銅電気メッキ層を約 3 0 0 から約 4 5 0 の間の温度でウエハを加熱することによってアニールして、銅を穴 8 4 中に

10

20

30

40

50

リフローさせて銅プラグ 8 6 を形成する。

**【 0 0 3 9 】**

図 4 ( d ) を参照すると、銅層 6 2 が銅電気メッキ層の上方に物理的気相堆積されてワイヤ輪郭 5 0 を充填している。ワイヤ輪郭を充填するためには、一般的に、構造体の全フィールドが C V D 銅によって覆われるということになる。

**【 0 0 4 0 】**

図 4 ( e ) を参照すると、次に、構造体 8 0 の頂部部分が、好ましくは化学機械的研磨法 ( C M P ) によって平坦化される。この平坦化プロセスの間に、銅 6 2 とバリヤ材料 5 4 と誘電体 4 2 との各部分が構造体の頂部から除去されて、導電性ワイヤ 6 4 と 6 6 を内部に形成した完全に平面状の表面を残す。

10

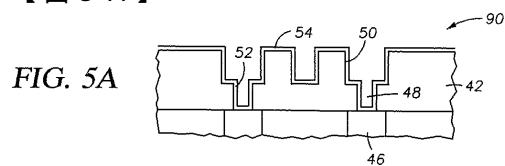

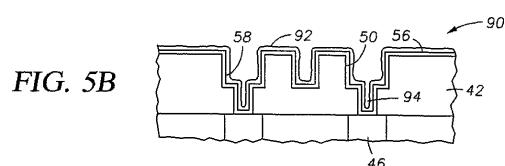

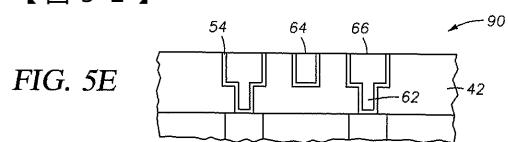

**C V D / アニール / 電気メッキ**

本発明による別の実施形態 9 0 では、図 5 ( a ) ~ ( e ) に示すように、サブ半ミクロンのバイアが コンフォーマル C V D 銅によって部分的に充填され、次に、約 3 0 0 から約 4 0 0 の間の温度にウエハを加熱することによってアニールされて、銅層の表面を平滑化する。次に、バイアと溝が銅電気メッキで、非統合システム中で充填される。

**【 0 0 4 1 】**

図 5 ( a ) に、図 2 ( b ) に示すものと類似のバリヤ層 5 4 を上に形成したパターン化された誘電体を示す。図 5 ( b ) を参照すると、コンフォーマル バリヤ層 5 4 を有するデュアルダムシンバイア / ワイヤ輪郭の断面図が、バイアが部分的に充填されて穴 9 4 が残るまで、フィールド領域 5 6 と側壁 5 8 上に均一に堆積される コンフォーマル C V D 銅層 9 2 を含んでいる。図 5 ( c ) を参照すると、次に、C V D 銅層 9 2 がアニールされて、穴 9 4 を充填することなく銅層を平滑化する。

20

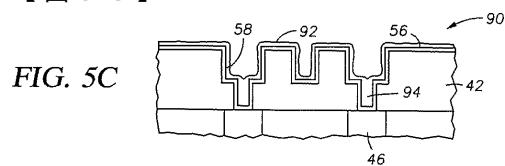

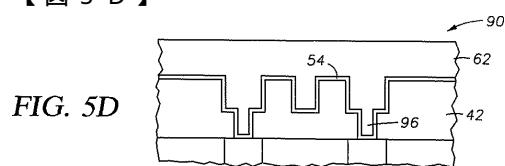

**【 0 0 4 2 】**

図 5 ( d ) を参照すると、銅層 6 2 が電気メッキによって堆積されてバイア / ワイヤ輪郭を充填し、これによって銅プラグ 9 6 を形成する。ワイヤ輪郭を形成するためには、一般に、構造体の全フィールドが銅で覆われることになる。

**【 0 0 4 3 】**

図 5 ( e ) を参照すると、次に、構造体 9 0 の頂部部分が、好ましくは化学機械的研磨法 ( C M P ) によって平坦化される。この平坦化の間に、銅 6 2 とバリヤ材料 5 4 と誘電体 4 2 との各部分が構造体の頂部から除去されて、導電性ワイヤ 6 4 と 6 6 を内部に形成した完全に平面状の表面を残す。

30

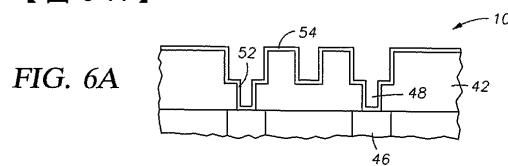

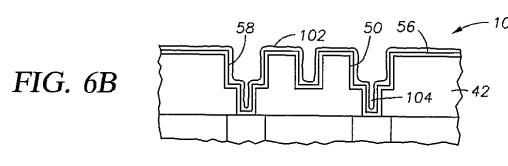

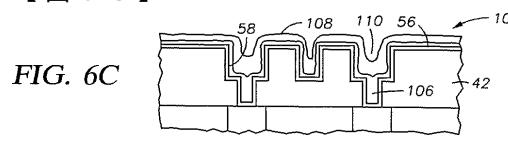

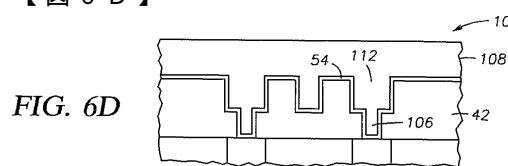

**C V D / アニール / C V D / アニール充填**

本発明の別の実施形態 1 0 0 では、図 6 ( a ) ~ ( e ) に示すように、サブ半ミクロンのバイアが コンフォーマル C V D 銅によって部分的に充填され次にアニールされてバイアを充填する。次に、溝が C V D 銅によって充填され、次にバイアに対して上記のようにアニールがなされる。ワイヤは構造体を平坦化することによって形成される。

**【 0 0 4 4 】**

図 6 ( a ) に、図 2 ( b ) に示すものと類似のバリヤ層 5 4 を上に形成したパターン化された誘電体を示す。図 6 ( b ) を参照すると、コンフォーマル バリヤ層 5 4 を有するデュアルダムシンバイア / ワイヤ輪郭の断面図が、バイアが部分的に充填されて穴 1 0 4 が残るまで、フィールド領域 5 6 と側壁 5 8 上に均一に堆積される コンフォーマル C V D 銅層 1 0 2 を含む。図 6 ( c ) を参照すると、次に、C V D 銅層を、約 3 0 0 から約 4 5 0 までの温度にウエハを加熱することによってアニールして、銅を穴 1 0 4 中にリフローして銅プラグ 1 0 6 を形成する。次に、第 2 の コンフォーマル C V D 銅層 1 0 8 が、溝が部分的に充填されて穴 1 1 0 が残るまで、アニール済みの C V D 層上に均一に堆積される。図 6 ( d ) を参照すると、次に、第 2 の C V D 銅層 1 0 8 を約 3 0 0 から約 4 5 0

40

の温度にウエハを加熱することによってアニールして、銅を溝穴 1 1 0 中にリフローして銅ワイヤ 1 1 2 を形成する。図 6 ( e ) を参照すると、銅ワイヤ 1 1 2 が前述したように平坦化によって完了される。

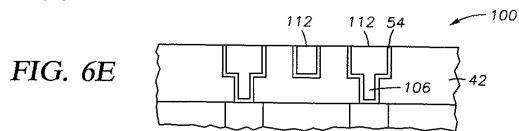

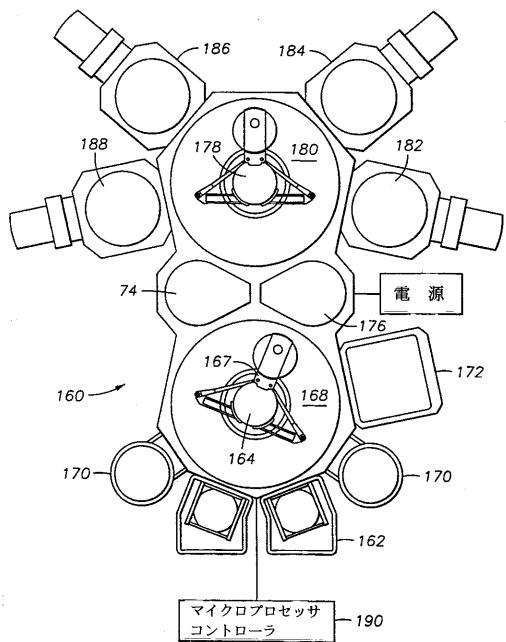

図7を参照すると、上記の統合プロセスをその内部で実現できるPVDチャンバとCVDチャンバの双方と有する統合処理システム160の略図が示されている。一般的には、基板を処理システム160からカセットロードロック162を介して導入して引き込まれる。ブレード167を有するロボット164が処理システム160内に置かれて、基板をシステム160内を移動させる。1つのロボット164がバッファチャンバ168中の一般的な位置に置かれると、カセットロードロック162、脱気ウエハ方向付けチャンバ170、事前清浄化チャンバ172、PVDTiNチャンバ174、冷却チャンバ176の間で基板を伝達する。第2のロボット178が伝達チャンバ180中に位置して、冷却チャンバ176、干渉性のTiチャンバ182、CVDTiNチャンバ184、CVD銅チャンバ186及びPVD IMP銅処理チャンバ188との間で基板をやりとりする。統合システム中の伝達チャンバ180は $10^{-3}$ から $10^{-8}$ Torrという低圧又は高圧に維持するのが好ましい。図6に示すチャンバのこの構成は、単一のクラスタツール中でCVDプロセスとPVDプロセスの双方が可能な統合処理システムを含んでいる。この特殊なチャンバ構成すなわち配置は単に図示目的であり、これ以外のPVDプロセスとCVDプロセスの構成が本発明によって考察されている。10

#### 【0045】

一般的に、処理システム160中で処理された基板はカセットロードロック162からバッファチャンバ168に送られ、そこで、ロボット164が最初に基板を脱気チャンバ170中に移動させる。次に、基板は事前清浄化チャンバ172、PVDTiNチャンバ174そして次に冷却チャンバ176に伝達される。冷却チャンバ176から、ロボット178は一般的に、基板を冷却チャンバ176に戻す前に、基板を1つ以上の処理チャンバ中とこれら同士間に移動させる。基板が、基板上に所望の構造体を製作するために1つ以上のチャンバ中で何回もそして何らの順序で処理されたり冷却されたりすることが予測される。基板は処理が終わったら処理システム160からバッファチャンバ168を介して取り除かれてロードロック162に移される。マイクロプロセッサコントローラ190が基板上に層を連続して形成するプロセスを制御する。20

#### 【0046】

本発明によれば、処理システム160は基板をロードロック162から脱気チャンバ170に移し、基板はここに導入されると汚染物質を脱気する。次に基板は事前清浄化チャンバ172中に移動し、ここで基板表面を清浄化してそのあらゆる汚染物質を除去する。次に基板はCVD-TiNチャンバ175中で処理されて誘電層上にバリヤ層を堆積する。次に、ロボット178は基板をCVD銅174のところに伝達する。基板は2つ以上の金属層を受容して金属製のプラグと相互接続部とを形成する。アニール処理は加熱されたどのチャンバでも発生し得る。金属層が完全に堆積されたら、基板は平坦化ユニットに送られる。30

#### 【0047】

多段式真空ウエハ処理システムが、参考してここに組み込まれる、1993年2月16日に発行されたテップマン(Teppman)による「多段式真空ウエハ処理のためのシステムと方法(Staged-Vacuum Wafer Processing System and Method)」という名称の米国特許第5,186,718号に開示されている。このシステムはCVDチャンバを収納できるように改良されている。40

#### 【0048】

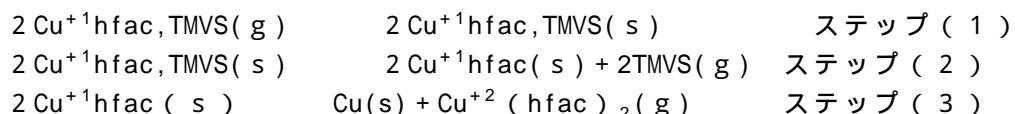

CVD銅層は、Cu<sup>+2</sup>(hfac)<sub>2</sub>及びCu<sup>+2</sup>(fod)<sub>2</sub>(fodは、ヘプタフルオロジメチルオクタンジエンの略語)を含むなんらかの周知のCVD銅プロセス又は前駆気体を用いて堆積してもよいが、好ましいプロセスでは、揮発性液体錯Cu<sup>+1</sup>(hfac)とTMVS(hfacはヘキサフルオロアセチルアセトネートアニオンの略語であり、TMVSはトリメチルビニルシランの略語である)を単体気体としてのアルゴンと一緒に用いる。この錯体は周辺状態下の液体であるので、半導体作成に現在用いられている標準のCVD気泡系前駆体送出システムで用いることができる。TMVSとCu<sup>+2</sup>(hfac)<sub>2</sub>は双方共がチャンバから排出される堆積反応の揮発性副産物である。この堆積反応は、(50

s) が表面との相互作用を意味し (g) が気相を意味する次のメカニズムに従って進行すると信じられている：

ステップ1では、錯体は気相から金属表面上に吸収される。ステップ2では、配位されたオレフィン（この特定の場合ではTMVS）が錯体から自由気体として解離して、 $\text{Cu}^{+1}\text{hfac}$ を不安定化合物として残す。ステップ3では、 $\text{Cu}^{+1}\text{hfac}$ が解離して銅金属と揮発性 $\text{Cu}^{+2}(\text{hfac})_2$ を生じる。CVD温度での解離は金属表面すなわち電導性表面によって最も強く触媒されるようである。代替の反応では、有機金属銅錯体を水素で還元して金属銅を生じさせることができる。

#### 【0049】

揮発性液体錯体である $\text{Cu}^{+1}\text{hfac}$ とTMVSとを用いて、銅を熱ベース又はプラズマベースのプロセスのプロセスによって堆積させることができると、熱ベースのプロセスが最も好ましいものである。プラズマ強化プロセスの場合の基板温度は約100と約400の間であるのが好ましいが、一方、熱プロセスの場合の基板温度は約50から約300の間であるが、約170が最も好ましい。これらのプロセスの内どちらかに続いて、CVD銅ぬれ性層を核生成層の上方に備えてもよい。代替例として、電気メッキされた銅をCVD銅ぬれ性層と組み合わせて又はこの代わりに用いてもよい。

#### 【0050】

CVD銅層が堆積されるとそれに続いて、基板がPVD銅チャンバに送られてPVD銅をCVD銅とPVD銅の融点未満の温度で堆積させる。軟金属が銅である場合、PVD銅を約550未満、好ましくは約400未満のウエハ温度で堆積させるのが好ましい。銅層は約200でPVD堆積プロセスの間に流れ始め、タンタルバリヤ／ぬれ性層は本来の場所に固体金属層として固く残る。タンタルは銅とのぬれ性が良好であるので、CVD銅は約400ではタンタルを脱ぬれ性することなく、したがって、先行する技術によるCVDプロセスで教示されるように、アルミニウムの融点を越えるウエハ温度（660を越える温度）は必要ない。したがって、薄いタンタル層を付着させることによって、銅の融点の遙か未満の温度で銅の平坦化を達成することができる。

#### 【0051】

本発明のどの態様の場合でも、堆積された銅層を $\text{H}_2$ でアニールしてこの層を酸化銅の形成に対する抵抗性を強化する。

#### 【0052】

銅の電気メッキはPVD又はCVDより遙かに安価であるが、統合処理システムでは実行できない。幸運にも、基板を別々の処理装置間で伝達する際に基板を空気に露出させて金属層には顕著な界面は形成されなかった。約0.5重量%から約2重量%の錫を包含する目標としての銅を、 $10^{-7}\text{Torr}$ という真空中度と150ECという基板温度でデュアル電子銃を用いて気相堆積すなわち電気メッキさせることができる。

#### 【0053】

前述の説明は本発明の好ましい実施形態を参照したが、本発明の他のそしてさらなる実施形態が本発明の基本的範囲から逸脱することなく可能である。本発明の範囲は以下の請求の範囲によって決定されるものである。

#### 【図面の簡単な説明】

【図1】(a)～(e)は、デュアルダマシンバイア／ワイヤ輪郭と、バリヤ層、PVD金属堆積法及び金属電気メッキ法を用いて金属相互接続部を提供する先行技術によるステップと、を示す図である。

【図2】(a)～(e)は、本発明の第1の実施形態による、デュアルダマシンバイア／ワイヤ輪郭と、導電性金属でデュアルダマシンバイア／ワイヤ輪郭を充填するに先立つてバリヤ層を堆積するステップと、を示す図である。

【図3】(a)～(e)は、本発明の第2の実施形態による、バリヤ層を有するデュア

10

20

30

40

50

ルダマシンバイア／ワイヤ輪郭と、導電性金属を堆積するステップと、を示す図である。

【図4】(a)～(e)は、本発明の第3の実施形態による、バリヤ層を有するデュアルダマシンバイア／ワイヤ輪郭と、導電性金属を堆積するステップと、を示す図である。

【図5】(a)～(e)は、本発明の第4の実施形態による、バリヤ層を有するデュアルダマシンバイア／ワイヤ輪郭と、導電性金属を堆積するステップと、を示す図である。

【図6】(a)～(e)は、本発明の第5の実施形態による、バリヤ層を有するデュアルダマシンバイア／ワイヤ輪郭と、導電性金属を堆積するステップと、を示す図である。

【図7】本発明の好ましい実施形態による連続金属化用に構成された統合処理システムを示す図である。

【図1A】

【図1B】

【図1C】

【図1D】

【図1E】

【図2A】

【図2B】

【図2C】

【図2D】

【図2E】

【図 3 A】

【図 3 B】

【図 3 C】

【図 3 D】

【図 4 E】

【図 5 A】

【図 5 B】

【図 5 C】

【図 5 D】

【図 3 E】

【図 4 A】

【図 4 B】

【図 4 C】

【図 4 D】

【図 5 E】

【図 6 A】

【図 6 B】

【図 6 C】

【図 6 D】

【図 6 E】

【図 7】

---

フロントページの続き

(74)代理人 100140453

弁理士 戸津 洋介

(74)代理人 100139000

弁理士 城戸 博兒

(74)代理人 100152191

弁理士 池田 正人

(72)発明者 チャン , リヤン - ユ

アメリカ合衆国 , カリフォルニア州 , サン ノゼ , フェアウェイ エントランス ドライヴ

1304

(72)発明者 タオ , ロン

アメリカ合衆国 , カリフォルニア州 , サン ノゼ , アーリントン レーン 1311

(72)発明者 グオ , テッド

アメリカ合衆国 , カリフォルニア州 , パロ アルト , エー タンランド ドライヴ 107

9

(72)発明者 モーズリー , ロデリック , クレイグ

アメリカ合衆国 , カリフォルニア州 , プレザントン , ダイアヴィラ アヴェニュー 433

7

審査官 井原 純

(56)参考文献 特開平10-074763(JP,A)

特開平11-017008(JP,A)

特開平10-079389(JP,A)

(58)調査した分野(Int.Cl. , DB名)

H01L 21/28-21/288

H01L 21/3205

H01L 21/3213

H01L 21/44-21/445

H01L 21/768

H01L 23/52-23/522

H01L 29/40-29/49

H01L 29/872