(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-101985

(P2005-101985A)

(43) 公開日 平成17年4月14日(2005.4.14)

(51) Int.Cl.<sup>7</sup>

H04N 5/335

H01L 27/146

F 1

H04N 5/335

H01L 27/14

テーマコード(参考)

4M118

5C024

A

審査請求 未請求 請求項の数 9 O L (全 23 頁)

(21) 出願番号

特願2003-334188 (P2003-334188)

(22) 出願日

平成15年9月25日 (2003. 9. 25)

(71) 出願人 000002185

ソニー株式会社

東京都品川区北品川6丁目7番35号

(74) 代理人 100094053

弁理士 佐藤 隆久

(72) 発明者 松本 静徳

神奈川県横浜市保土ヶ谷区神戸町134番

地 ソニー・エルエスアイ・デザイン株式会社内

(72) 発明者 小関 賢

神奈川県横浜市保土ヶ谷区神戸町134番

地 ソニー・エルエスアイ・デザイン株式会社内

最終頁に続く

(54) 【発明の名称】 固体撮像装置および画像入力装置

## (57) 【要約】

【課題】カラム処理回路により並列処理し、シリアル信号に変換するCMOSイメージセンサなどで、クランプレベルが必要以上に高く設定され、ADコンバータなどの後段回路の有効な信号の入力レンジが狭くなる。

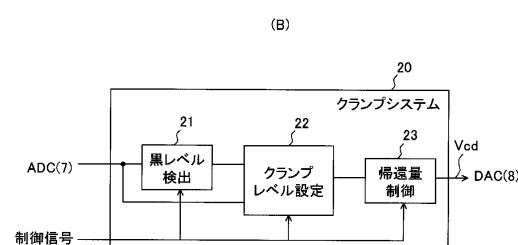

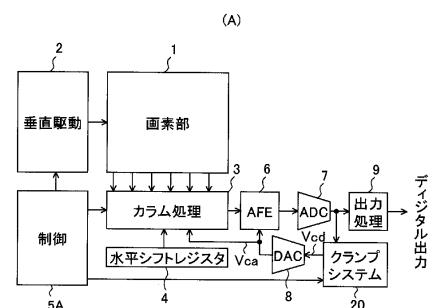

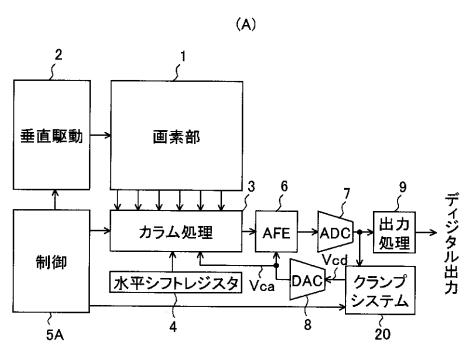

【解決手段】クランプシステム20内に、シリアル信号の最小の黒レベルを検出する黒レベル検出回路21と、最小の黒レベルを基準にクランプレベルVcdを設定するクランプレベル設定回路22とを有する。設定されたクランプレベルVcdは、アナログに変換された後、カラム処理回路3またはアナログフロントエンド回路6内のクランプ回路にフィードバックされ、そこで通過信号の黒レベルが変更される。

【選択図】図1

## 【特許請求の範囲】

## 【請求項 1】

画素部内の画素列ごとに垂直信号線が接続されている固体撮像装置であって、複数の前記垂直信号線に前記画素部から一斉に読み出された信号を並列処理し、並列処理後のパラレル信号をシリアル信号に変換するカラム処理回路と、

前記シリアル信号で黒レベルが白レベルより電位として低いときに、当該シリアル信号の少なくとも 1 行分の画素に対応した部分で最小の黒レベルを検出する黒レベル検出回路と、

前記最小の黒レベルを基準にクランプレベルを設定するクランプレベル設定回路と、

前記画素部の出力から前記黒レベル検出回路の入力までの信号経路に設けられ、通過信号の黒レベルを前記クランプレベルでクランプするクランプ回路と、

を有する固体撮像装置。

## 【請求項 2】

前記クランプレベル設定回路は、前記最小の黒レベル、または、前記最小の黒レベルより一定のマージンだけ高いレベルにクランプレベルを設定する

請求項 1 に記載の固体撮像装置。

## 【請求項 3】

前記画素部は、

入力した光を光電変換するフォトセンサを有する複数行の有効画素部と、

当該有効画素部の垂直方向の少なくとも一方側に配置され、フォトセンサが形成されていない、少なくとも 1 行のセンサなし画素部と、を有し、

前記黒レベル検出回路は、前記センサなし画素部に対応した前記シリアル信号の部分で前記最小の黒レベルを検出する

請求項 1 に記載の固体撮像装置。

## 【請求項 4】

前記クランプレベル設定回路は、

前記センサなし画素部で黒レベルの平均値を複数回算出する平均値算出回路と、

前記平均値と前記最小の黒レベルとの差を求める第 1 の演算回路と、

前記複数回算出された平均値のうち最小の平均値に対し前記差を加算または減算する第 2 の演算回路と、を有し、

当該第 2 の演算回路の出力に応じて前記クランプレベルを設定する

請求項 3 に記載の固体撮像装置。

## 【請求項 5】

前記画素部は、

入力した光を光電変換するフォトセンサを有する複数行の有効画素部と、

当該有効画素部の垂直方向の少なくとも一方側に配置され、フォトセンサが形成されていない、少なくとも 1 行のセンサなし画素部と、

前記有効画素部の垂直方向の少なくとも一方側に配置され、フォトセンサが遮光されている、少なくとも 1 行の遮光画素部と、を有し、

前記黒レベル検出回路は、前記センサなし画素部に対応した前記シリアル信号の部分で前記最小の黒レベルを検出し、

前記クランプレベル設定回路は、

前記センサなし画素部と前記遮光画素部のそれぞれで黒レベルの平均値を算出する平均値算出回路と、

前記センサなし画素部の黒レベルの平均値と前記最小の黒レベルとの差を求める第 1 の演算回路と、

前記平均値算出回路で算出した 2 つの平均値を比較する比較器と、

前記比較の結果、より低い平均値に対し前記差を加算または減算する第 2 の演算回路と、を有し、

前記第 2 の演算回路の出力に応じて前記クランプレベルを設定する

10

20

30

40

50

請求項 1 に記載の固体撮像装置。

【請求項 6】

前記クランプレベルをさらに増減して、前記クランプレベル回路にフィードバックする帰還量を調整する帰還量制御回路を、さらに有する

請求項 1 に記載の固体撮像装置。

【請求項 7】

前記クランプレベル設定回路は、

前記センサなし画素部で最小の黒レベルを保持する第 1 の保持回路と、

前記センサなし画素部の黒レベルの平均値を保持する第 2 の保持回路と、をさらに有し、

前記第 1 および第 2 の保持回路のそれぞれは、保持した情報を新たな情報と置き換えるリフレッシュレートを、入力した制御信号に応じて独立に設定可能に構成されている

請求項 4 に記載の固体撮像装置。

【請求項 8】

前記クランプレベル設定回路は、

前記センサなし画素部で最小の黒レベルを保持する第 1 の保持回路と、

前記センサなし画素部の黒レベルの平均値を保持する第 2 の保持回路と、

前記遮光画素部の黒レベルの平均値を保持する第 3 保持回路と、をさらに有し、

前記第 1 から第 3 の保持回路のそれぞれは、保持した情報を新たな情報と置き換えるリフレッシュレートを、入力した制御信号に応じて独立に設定可能に構成されている

請求項 5 に記載の固体撮像装置。

【請求項 9】

画素部内の画素列ごとに垂直信号線が接続されている固体撮像装置を有する画像入力装置であつて、

複数の前記垂直信号線に前記画素部から一斉に読み出された信号を並列処理し、並列処理後のパラレル信号をシリアル信号に変換するカラム処理回路と、

前記シリアル信号で黒レベルが白レベルより電位として低いとしたときに、当該シリアル信号の少なくとも 1 行分の画素に対応した部分で最小の黒レベルを検出する黒レベル検出回路と、

前記最小の黒レベルを基準にクランプレベルを設定するクランプレベル設定回路と、

前記画素部の出力から前記黒レベル検出回路の入力までの信号経路に設けられ、通過信号の黒レベルを前記クランプレベルでクランプするクランプ回路と、

を有する画像入力装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、画素内に複数の MOS ( 金属酸化膜半導体 ) ツランジスタを有し、当該 MOS ツランジスタを制御することにより画素電荷に応じた信号を増幅して読み出す固体撮像装置に関するものである。

【背景技術】

【0002】

固体撮像装置は、MOS ( 金属酸化膜半導体 ) 型イメージセンサと CCD ( 電荷結合素子 ) イメージセンサがある。MOS 型イメージセンサと CCD イメージセンサはほぼ同時期に開発され、実用化されていた。このうち高感度で低雑音であるという理由によって、現在までに製品化されているものの多くは CCD イメージセンサであった。

【0003】

近年、MOS 型集積回路として CMOS ( 相補型 MOS ) 構成が全盛となり、この CMOS 集積回路と同様のプロセスで製造できる CMOS イメージセンサが開発された。CMOS イメージセンサは CMOS プロセスで製造できることにより、撮像部 ( 画素部 ) とその駆動回路、さらに画素から出力された信号の処理回路を同一チップ内に構成できるとい

10

20

30

40

50

う小型化および低コスト化に有利な特徴をもっている。

このタイプのイメージセンサは、後述するように画素ごとに複数のMOSトランジスタを有しており、CMOS集積回路におけるMOSトランジスタや配線の微細化技術の進歩は、CMOSイメージセンサにおいても画素の小型化および高感度化（トランジスタサイズの縮小による受光面積率の増大）に大きな進歩をもたらした。また、CMOSイメージセンサではフォトセンサで光電変換した画素信号の電荷を画素単位で一度増幅するアクティブ型の画素構造が主流となり、これによって、ノイズに対して強い信号出力が画素から得られるようになった。その結果、CMOSイメージセンサが再び注目され、多くの研究開発がなされるようになってきた。一方、CMOSイメージセンサは、画素ごとに配置された増幅用トランジスタのしきい値電圧等に起因した画素信号のばらつきによって画面ムラ、すなわち画面全体にスリガラスを通したようなムラ状のノイズがのるという課題を有している。近年、この画素信号のばらつきを低減する技術として、信号処理回路のうちとくにCDS（相関2重サンプリング）回路が進歩したこと、CMOSイメージセンサが、CCDイメージセンサを置き換える可能なデバイスとして注目されてきた要因である。

#### 【0004】

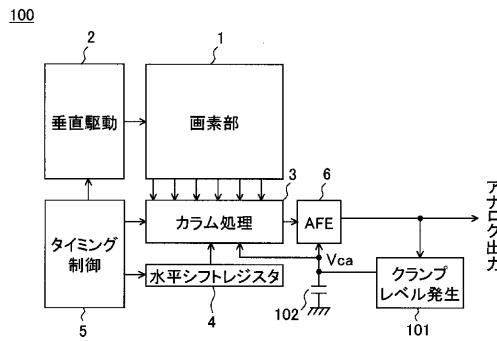

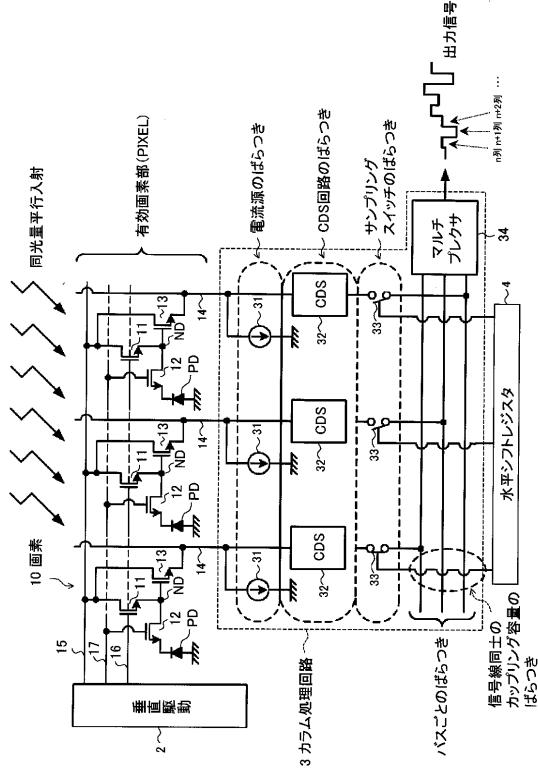

図9に、CMOSイメージセンサの基本的な構成を示す。また、図10に、このCMOSイメージセンサの構成のうち主に画素部とカラム処理回路の詳細を示す。

図9に示すCMOSイメージセンサ100は、画素がマトリクス状に配置された画素部1を有している。図10では簡略化のため同一行に属する3つの画素10のみ示しているが、実際の画素部の有効画素部（PIXEL）は、同じ構成の画素10が行列状に多数配置された構成を有する。有効画素部（PIXEL）を構成する各画素10は、図10に示す3トランジスタ型の場合、入力した光を光電変換するフォトセンサPDと3つのトランジスタ11～13とを有する。3つのトランジスタは、ノードNDをフローティング状態から電源線15への接続状態に切り替え、ノードNDに電源電圧を充電して、その電荷量をリセットするリセットトランジスタ11と、リセット後に再びフローティング状態となったノードNDにフォトセンサPDの蓄積電荷（通常、電子）を転送する転送トランジスタ12と、ノードNDに転送された蓄積電荷に応じた画素信号を増幅して垂直信号線14に出力する読み出しトランジスタ13とからなる。

#### 【0005】

リセットトランジスタ11のゲートに、同一行内の画素に共通なリセット制御線16が接続されている。また、転送トランジスタ12のゲートに、同一行内の画素に共通な転送制御線17が接続されている。

これらの制御線16と17、ならびに、電源線15のそれぞれに各種信号を供給する垂直駆動回路2が接続されている。また、垂直信号線14に一斉に読み出された画素信号を並列処理してノイズを除去し、時系列の信号に変換するカラム処理回路3および水平シフトレジスタ4が設けられている。これらの垂直駆動回路2、カラム処理回路3および水平シフトレジスタ4は、図9に示すタイミング制御回路5により制御されて動作する。

#### 【0006】

カラム処理回路3は、垂直信号線14ごとに設けられた電流源31、CDS回路32およびサンプリングスイッチ33を有している。電流源31は、読み出しトランジスタ13に一定電流を供給するために設けられている。また、CDS回路32は、有効画素部（PIXEL）の画素信号に対し、その黒レベルでサンプル・ホールドした電圧と、蓄積電荷に応じた画素信号レベルでサンプル・ホールドした電圧との差分をとって、両電圧に重畠したノイズ成分をキャンセルする回路である。このノイズ除去後の画素信号レベルはCDS回路32の出力で保持された後、さらに、水平シフトレジスタ4から供給されるパルスによって順次オンされるサンプリングスイッチ33により、点順次でサンプリングされる。

このような画素行で一斉に読み出され、その後、点順次で時系列の信号に変換される方法を、以下「カラム読み出し方式」と称する。

#### 【0007】

10

20

30

40

50

図10に示すカラム処理回路3は、この点順次サンプリング後の画素信号を複数本のバスに供給し、内蔵のマルチプレクサ34で1つの時系列信号（出力信号）に変換する構成が採用されている。他の構成としては、点順次サンプリング後の画素信号を1本の信号線に供給し、時系列の出力信号としてそのまま出力する方法もある（たとえば、特許文献1参照）。

#### 【0008】

時系列の出力信号は、図9に示すように、アナログフロントエンド（AFE）と称されるアナログ信号処理回路6に入力される。入力される時系列の信号は信号レベルが無信号の基準レベルより低いので、アナログ信号処理回路6内で反転され、また、必要に応じてゲイン調整や高周波成分の除去が行われた後、出力される。アナログ信号処理回路6から出力される信号はアナログであり、図示しない後段のA/Dコンバータによりデジタル化され、デジタル処理信号回路に渡される。

#### 【0009】

ところで、画素信号に重畳されるノイズは、時間的にランダムに発生するランダムノイズと、出力画面の同じところに縦縞、横縞または画面ムラなどの固定パターンとして発生する固定パターンノイズとに大別できる。ランダムノイズは、主に、光ショットノイズや熱雑音など、画素のフォトセンサ内や増幅箇所、その他の増幅箇所などで生じ、環境温度などで容易に変化する。一方、固定パターンノイズは、画素のMOSトランジスタのしきい値電圧の違い、その他の回路や配線などで、電気特性上のアンバランスに起因して生じるものが多い。

前述したCDS回路32により画面ムラが抑圧できる。また、CDSのサンプリング周波数にもよるが、CDSで高速なサンプル・ホールドができる場合、ランダムノイズ（1/fノイズ）もCDS回路32により抑圧できる。ただし、CDS回路32は、前述したようにサンプル・ホールド電圧の差をとってノイズを除去することから画素信号全体に重畳したノイズは除去できるが、外光の影響等で黒レベル自体が変動するようなノイズ成分は除去できない。したがって、以後、黒レベルをそのまま画素信号の基準レベルとして用いると、CDSごとに黒レベルが異なり画像が安定せず、また、黒レベルの変動の仕方によつては、これが固定パターンノイズとなって画面に現れる。

#### 【0010】

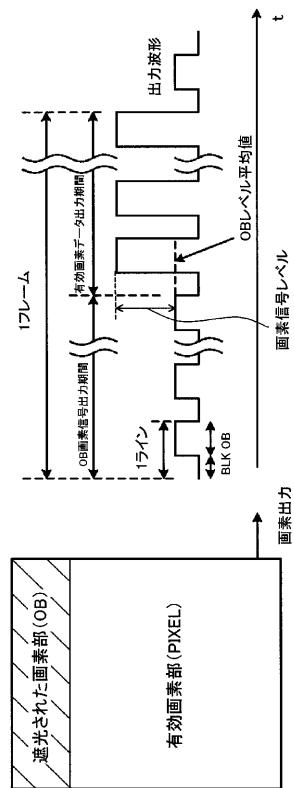

そこで、CMOSイメージセンサ100に、図9に示すように、黒レベルを示す信号にクランプをかけて画像の安定化を行うアナログクランプレベル（Vca）の発生回路101を搭載することが多い。このクランプレベルVcaの発生時に用いる黒レベルを示す信号は、図11に示すように、外光の影響を防止するために、通常、遮光された画素部（オペティカルブラック（OB）ともいう）から読み出される。

クランプレベル発生回路101は、アナログ信号処理後の画素信号からOBレベルを検出し、検出したOBレベルが予め決められた基準レベルVrefに近づくように、キャパシタ102に出力する電圧レベル（アナログクランプレベルVca）を制御する。そして、このクランプレベルVcaが、CDS回路32内で黒レベルと信号レベルの電圧差をとるオペアンプの出力の基準電位として、さらには、アナログ信号処理回路6の反転増幅器の反転入力（および/または内蔵のゲインコントロールアンプ）に印加される基準電位としてフィードバックされる。このフィードバック処理の収束目標である基準レベルVrefは、通常、OBレベルの平均値に設定される。したがって、図11に示すように、オペティカルブラック部（OB）のOBレベルの平均値を基準として、有効画像部（PIXEL）の画素信号の電位が決定され、アナログ信号処理後の信号レベルが安定する。また、図9に示すクランプ方式では、キャパシタ102から高周波成分が接地電位に散逸するので、これがローパスフィルタとしても働き、そのため高周波のノイズを除去することができる。

#### 【0011】

しかし、あまり大容量のキャパシタ102を用いると応答が遅くなり、スタート時やゲイン変更時にクランプレベルVcaが安定するまでに時間がかかりすぎるという問題が発

10

20

30

40

50

生する。

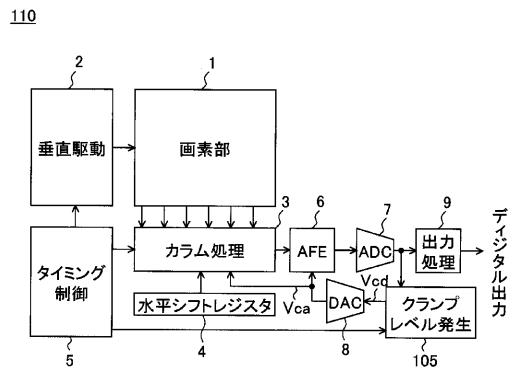

このような問題を解決するために、クランプレベルV<sub>c a</sub>の保持にキャパシタ102を用いてアナログ量を保持する図9に示す方式の他に、図12に示すように、クランプレベルをデジタルで保持する方式がある。図12に示すCMOSイメージセンサ110は、図9と比較すると、大容量のキャパシタ102に代えて、アナログ信号処理回路6の出力をデジタル化するADCコンバータ(ADC)7と、デジタルクランプレベルV<sub>c d</sub>をアナログ値V<sub>c a</sub>に変換するDACコンバータ(DAC)8と、出力処理回路9とを有している。この場合のクランプレベル発生回路105は、ADCコンバータ7から出力されるデジタル画素信号のOBレベルが、その平均値に近づくように、出力するデジタルクランプレベルV<sub>c d</sub>を制御する。このクランプレベルV<sub>c d</sub>はDACコンバータ8によりアナログ値V<sub>c a</sub>に変換され、図9の場合と同様な目的で、カラム処理回路3内のCDS回路32やアナログ信号処理回路(AFE)6にフィードバックされる。

このような方式を用いればクランプキャパシタによって制限されるスピードの問題は解決することができるところから、ADCコンバータを搭載したCMOSイメージセンサにおいては有効な方式である。

#### 【0012】

しかし近年、半導体微細加工技術の進歩によって、数百万画素もしくは1千万を超える画素といった高解像度の固体撮像装置が開発されるようになった。ここで問題となってくることは画素の高密度化によって引き起こされる画素信号の読み出し速度の増加にいかに対応して画像データを処理し、後段のICに出力するかである。この問題を解決するためには画素行ごとに信号の処理を一括して行い、数ラインのバスで信号を処理するといった並列処理を行うことが有効となってくる。そこで、図10に示すカラム読み出し方式が有効であり、さらに、これと図12に示すデジタルクランプ方式とを組み合わせると、高解像度の画素部を高速に読み出すことが可能となる。

#### 【0013】

なお、前述した特許文献1は、カラム読み出し方式を採用しているが、クランプレベル発生回路がアナログ方式であるかデジタル方式であるかの記載がない。このクランプレベル発生回路に入力されるOBレベルは、その変動を考慮し、OB部の垂直信号線を相互接続してOBレベルを平均化している。また、フォトダイオードを形成したOB部と、フォトダイオードを形成していないOB部とを2種類用意し、後段の信号処理回路の回路マージンをできるだけ小さくする目的で、その2種類のOB部から読み出されるOBレベルを垂直信号線の相互接続により平均化する技術が開示されている(特許文献1の第4の実施の形態参照)。

#### 【0014】

ところで、図9～図12、または、特許文献1に記載されたようなカラム読み出し方式では、列ごとに信号を処理するため、その列ごとの回路のばらつきがノイズとなって画像に現れるという問題がある。

#### 【0015】

たとえば図10の構成では、2次元的に配置された画素10に同じ光量の光が平行に入射してきたとすると、各画素10に発生する電荷の量は同じであり出力される信号も一定となるはずである。ところが、図10に示す電流源31のばらつき、CDS回路32内のキャパシタンス等のばらつき、サンプリングスイッチ33のフィードスルーばらつき、水平シフトレジスタ4から出力されるパルス信号の配線と出力バスとのカップリング容量のばらつきといった様々な要因によって、画素信号は列によってばらつきを持って出力されてしまう。このばらつきに起因したノイズは、ランダムノイズではなく、常に同じ量だけ列ごとに発生する固定パターンノイズであり画像に縦筋として現れる。この固定パターンノイズは、信号の発生場所が有効画素部(PIXEL)であるかオプティカルブラック部(OB)であるかに関係なく同様に発生する。

#### 【0016】

一方、特許文献1では、垂直信号線を画素部内で相互接続してOBレベルを平均化して

10

20

30

40

50

いるが、平均化された O B レベルが、その後、ノイズキャンセラ内のキャパシタやトランジスタのばらつき、サンプリングスイッチのフィードスルーばらつきなどで列ごとに再びばらついてしまう。しかも、そのばらつきは平均化されないままイメージセンサから出力され、後段のクランプレベル発生回路のクランプレベルとして用いられてしまう。その意味では、O B レベルをクランプレベル発生回路のフィードバックループで平均値（基準値）に収束させながらクランプレベルとして用いる図 9 や図 12 の場合より、特許文献 1 の場合のクランプレベルの変動は大きい。

また、この特許文献 1 に記載された C M O S イメージセンサでは、画素信号全体に重畠したノイズを除去する C D S 回路がイメージセンサの外部に 1 つ設けられ、イメージセンサから出力される時系列の信号に対して C D S が実行される。この場合、C D S 回路起因の列ごとに異なるノイズは発生しないが、カラム読み出し方式により並列処理とした読み出し動作の高速性が、この C D S 回路の動作で阻害されてしまう。

#### 【 0 0 1 7 】

図 9 や図 12 の構成では、前述したように、クランプレベルの制御目標が O B レベルの平均値に設定されていたため、この O B レベルの平均値を基準として、上記した列ごとに異なる固定パターンノイズにより O B レベルが最大で変化する電位までを、後段の処理回路の黒レベル側のマージン設計において確保する必要があった。しかも、この列ごとの固定パターンノイズに、ランダムノイズが重畠するため、後段の処理回路のノイズマージンはさらに余裕をみておく必要があった。

#### 【 0 0 1 8 】

この点に関し、特許文献 1 に記載された技術では、画素起因のランダムノイズ（暗電流によるノイズ）による変動を抑制したり、高温時にランダムノイズが突出することを抑制したりでき、その意味では、後段の処理回路におけるノイズマージンを幾らかでも小さくできる。

しかし、特許文献 1 では列ごとに異なる固定パターンノイズを全く考慮していない上、O B レベルの平均化を、列ごとに異なる固定パターンノイズの発生箇所の前で行うため、その効果はきわめて限定的であり、また、高速読み出しに対応していない。

#### 【 特許文献 1 】特開 2 0 0 0 - 0 3 1 4 5 0 号公報

#### 【 発明の開示 】

#### 【 発明が解決しようとする課題 】

#### 【 0 0 1 9 】

解決しようとする課題は、同一行の画素を並列に列方向の垂直信号線に読み出し、各列で信号処理を並列に行った後、シリアル信号に変換して読み出す高速読み出し方式に対応した固体撮像装置、および、これを用いた画像入力装置において、垂直信号線に画素信号を読み出した後、これをシリアル信号に変換するまでの経路で発生する列ごとに異なるノイズを考慮して、それより後段の処理回路のノイズマージンを確保する際に、その処理回路の能力（入力レンジ）が必要以上に制限されていたこと、あるいは、誤動作しないように処理回路の能力を必要以上に大きくしなければならないことである。

#### 【 課題を解決するための手段 】

#### 【 0 0 2 0 】

本発明にかかる固体撮像装置は、画素部内の画素列ごとに垂直信号線が接続されている固体撮像装置であって、複数の前記垂直信号線に前記画素部から一斉に読み出された信号を並列処理し、並列処理後のパラレル信号をシリアル信号に変換するカラム処理回路と、前記シリアル信号で黒レベルが白レベルより電位として低いとしたときに、当該シリアル信号の少なくとも 1 行分の画素に対応した部分で最小の黒レベルを検出する黒レベル検出回路と、前記最小の黒レベルを基準にクランプレベルを設定するクランプレベル設定回路と、前記画素部の出力から前記黒レベル検出回路の入力までの信号経路に設けられ、通過信号の黒レベルを前記クランプレベルでクランプするクランプ回路と、を有する。

#### 【 0 0 2 1 】

本発明では、好適に、前記クランプレベル設定回路は、前記最小の黒レベル、または、

10

20

30

40

50

前記最小の黒レベルより一定のマージンだけ高いレベルにクランプレベルを設定する。

【0022】

本発明では、好適に、前記画素部は、入力した光を光電変換するフォトセンサを有する複数行の有効画素部と、当該有効画素部の垂直方向の少なくとも一方側に配置され、フォトセンサが形成されていない、少なくとも1行のセンサなし画素部と、を有し、前記黒レベル検出回路は、前記センサなし画素部に対応した前記シリアル信号の部分で前記最小の黒レベルを検出する。

さらに好適に、前記クランプレベル設定回路は、前記センサなし画素部で黒レベルの平均値を複数回算出する平均値算出回路と、前記平均値と前記最小の黒レベルとの差を求める第1の演算回路と、前記複数回算出された平均値のうち最小の平均値に対し前記差を加算または減算する第2の演算回路と、を有し、当該第2の演算回路の出力に応じて前記クランプレベルを設定する。10

また、さらに好適に、前記クランプレベル設定回路は、前記センサなし画素部で最小の黒レベルを保持する第1の保持回路と、前記センサなし画素部の黒レベルの平均値を保持する第2の保持回路と、をさらに有し、前記第1および第2の保持回路のそれぞれは、保持した情報を新たな情報と置き換えるリフレッシュレートを、入力した制御信号に応じて独立に設定可能に構成されている。

【0023】

本発明では、好適に、前記画素部は、入力した光を光電変換するフォトセンサを有する複数行の有効画素部と、当該有効画素部の垂直方向の少なくとも一方側に配置され、フォトセンサが形成されていない、少なくとも1行のセンサなし画素部と、前記有効画素部の垂直方向の少なくとも一方側に配置され、フォトセンサが遮光されている、少なくとも1行の遮光画素部と、を有し、前記黒レベル検出回路は、前記センサなし画素部に対応した前記シリアル信号の部分で前記最小の黒レベルを検出し、前記クランプレベル設定回路は、前記センサなし画素部と前記遮光画素部のそれぞれで黒レベルの平均値を算出する平均値算出回路と、前記センサなし画素部の黒レベルの平均値と前記最小の黒レベルとの差を求める第1の演算回路と、前記平均値算出回路で算出した2つの平均値を比較する比較器と、前記比較の結果、より低い平均値に対し前記差を加算または減算する第2の演算回路と、を有し、前記第2の演算回路の出力に応じて前記クランプレベルを設定する。20

さらに好適に、前記クランプレベル設定回路は、前記センサなし画素部で最小の黒レベルを保持する第1の保持回路と、前記センサなし画素部の黒レベルの平均値を保持する第2の保持回路と、前記遮光画素部の黒レベルの平均値を保持する第3保持回路と、をさらに有し、前記第1から第3の保持回路のそれぞれは、保持した情報を新たな情報と置き換えるリフレッシュレートを、入力した制御信号に応じて独立に設定可能に構成されている。30

【0024】

本発明では、好適に、前記クランプレベルをさらに増減して、前記クランプ回路にフィードバックする帰還量を調整する帰還量制御回路を、さらに有する。

【0025】

本発明にかかる画像入力装置は、画素部内の画素列ごとに垂直信号線が接続されている固体撮像装置を有する画像入力装置であって、複数の前記垂直信号線に前記画素部から一斉に読み出された信号を並列処理し、並列処理後のパラレル信号をシリアル信号に変換するカラム処理回路と、前記シリアル信号で黒レベルが白レベルより電位として低いとしたときに、当該シリアル信号の少なくとも1行分の画素に対応した部分で最小の黒レベルを検出する黒レベル検出回路と、前記最小の黒レベルを基準にクランプレベルを設定するクランプレベル設定回路と、前記画素部の出力から前記黒レベル検出回路の入力までの信号経路に設けられ、通過信号の黒レベルを前記クランプレベルでクランプするクランプ回路と、を有する。40

【0026】

本発明によれば、画素部から信号が複数の垂直信号線に一斉に読み出されると、カラム

50

処理回路で、この信号が並列処理され、また、シリアル・パラレル変換される。カラム処理回路から出力されたシリアル信号は、1フレーム分を見ると、たとえば画素部の先頭部分にセンサなし画素部（および遮光画素部）からの信号が出力され、その後、映像信号として有効な有効画素部から信号が出力される。センサなし画素部（および遮光画素部）のそれぞれは、少なくとも1行分存在するので、カラム処理回路での黒レベルのばらつきを反映したものである。

【0027】

そこで、本発明では、シリアル信号で黒レベルが白レベルより電位として低いとしたときに、黒レベル検出回路によって最小の黒レベルが検出される。たとえばCMOSイメージセンサでは、画素電荷が電子であり、画素部から出力されたときの信号は黒レベルが白レベルより電位として高いので、最小の黒レベルの検出は、画素信号を反転処理した後の段階で実行される。なお、請求項の記載では黒レベルが白レベルより電位として低いことを述べているが、この記載の存在が、その逆の前提を排除したものでないことに注意を要する。つまり、黒レベルが白レベルより電位として高いときは、黒レベル検出回路によって、逆に、最大の黒レベルを検出してもよい。

【0028】

続いて、クランプレベル設定回路により、この検出した最小の黒レベルを基準にクランプレベルが設定される。十分に広い範囲で最小の黒レベルが検出されたときは、検出した最小の黒レベルをそのままクランプレベルとする。たとえば、数フレームで複数回の黒レベルを検出するときは、その最小値をそのままクランプレベルとすることが可能である。逆に、たとえば、黒レベルの検出範囲が1フレームと狭く、しかも、一定のばらつきマージンが既知のときは、検出した最小の黒レベルに、一定のマージンを加えたレベルにクランプレベルが設定される。

設定したクランプレベルはクランプ回路にフィードバックされる。ここで、クランプ回路は、たとえば、ノイズ除去やパラレル・シリアル変換を目的として信号をサンプル・ホールドする回路のほか、出力の基準電圧を変更可能な増幅器も、信号のDCレベルを変えることができる意味ではクランプ回路の一種である。このようなクランプ回路は、画素部の出力から黒レベル検出回路の入力までの信号経路に存在するため、このクランプ回路にクランプレベルをフィードバックすることにより、通過信号の黒レベルが、検出した最小値、あるいは、それに一定のマージンを加えた値に変更される。

【0029】

センサなし画素部からの信号は、光電変換機能を有せず暗電流等の誤差となる要因がないため、カラム処理によるばらつき（固定パターンノイズ）を最もよく反映した信号である。そのため、本発明では、最小の黒レベルの検出をセンサなし画素部で行うことが望ましい。

本発明では、検出した最小の黒レベルをクランプレベルとしてもよいが、より望ましくは、平均の黒レベルを算出し、平均の黒レベルと最小の黒レベルとの差をとる。この差は、プラスの値でもマイナスの値でもよく、その絶対値がカラム処理回路固有の最大変動幅とみなすことができる。一方、平均の黒レベルは、その検出範囲の画素欠陥（黒点欠陥または白点欠陥）の頻度、プロセスのばらつき、電気的印加条件のばらつき等で必ずしも全体の平均を表しているとは限らない場合がある。そこで、平均を複数回とって、そのうち最小の平均値に対し上記差を加算（差がマイナス値の場合）または減算（差がプラス値の場合）することにより、全体のばらつきを考慮して、より精度が高いクランプレベルを設定することができる。

また、本発明では、センサなし画素部の黒レベルの平均値と遮光画素部の黒レベルの平均値をそれぞれとった場合、より低い平均値に対し上記差を加減算することによりクランプレベルを算出する。

【0030】

また、本発明では、黒レベルの最小値や平均値を保持する保持回路に制御信号が入力されると、それぞれ保持する情報のリフレッシュレートが個別に変更されるようになってい

る。このため、たとえばスタートアップ時やゲイン変更時に最小値や平均値に誤差要因が混入する場合でも、それぞれリフレッシュレートを最適化して用いると、このような非定常時の誤差要因の影響が有効に排除される。

### 【0031】

さらに、本発明では、帰還量制御回路によりクランプレベルが増減されると、帰還量が調整された後、これがクランプ回路にフィードバックされる。このため、たとえばクランプレベルの大幅な変動が抑制され、クランプ回路より後段の回路（たとえばA/Dコンバータ）がクランプレベルの変化に追従しやすくなる。

### 【発明の効果】

### 【0032】

本発明にかかる固体撮像装置および画像入力装置では、このようにして、カラム処理回路のばらつきに起因した誤差要因（固定パターンノイズ）を考慮して、信号の黒レベルが必要な範囲で最小の値に設定される。このため、本発明では、信号の黒レベルが必要以上に高いレベルに設定されることによる不利益、つまり、後段の回路で取り扱うことができる信号のレンジが必要以上に狭くなるという不利益が解消される。

また、本発明では、センサなし画素部で黒レベルを検出し、その平均値からの差をとり、また、そのとき用いる平均値の取り方を工夫し、さらには、リフレッシュレートの変更が可能なことから、設定するクランプレベルの精度が高くできるという利点がある。

さらに、本発明では、クランプレベルの出力を調整して帰還量を変えることができるこことから、本発明の適用による黒レベルの急激な変化が抑制できる。また、その結果として、クランプ回路より後段の回路で、その入力レンジを一時的に越えて信号が印加されるような不具合を防止できるという利点がある。

### 【発明を実施するための最良の形態】

### 【0033】

本発明は、画素信号を垂直信号線に読み出す、いわゆるX-Yアドレス方式の固体撮像装置に広く適用できる。このような固体撮像装置の代表的なものとしてCMOSイメージセンサがある。以下、CMOSイメージセンサを例として説明する。

### 【0034】

#### 【第1の実施の形態】

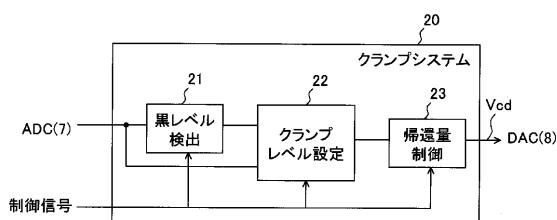

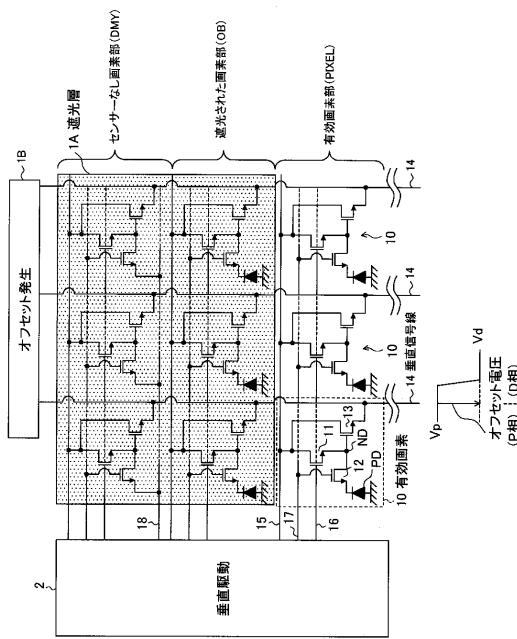

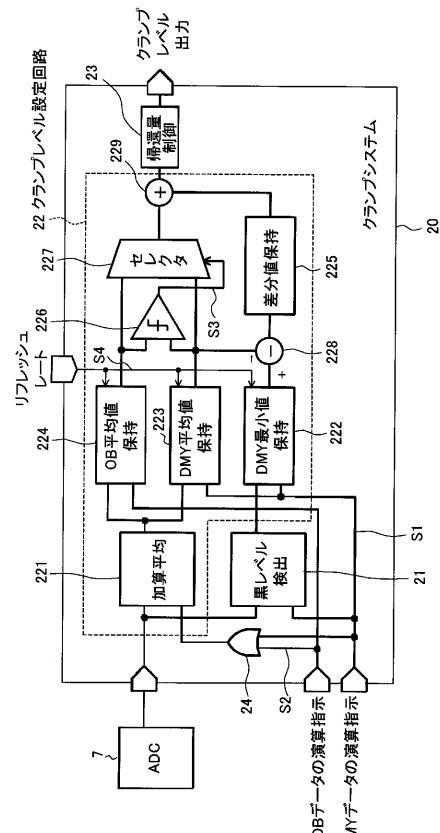

図1(A)はCMOSイメージセンサの構成図、図1(B)はクランプシステムの概略構成図である。また、図2は画素部の構成図、図3は画素部の回路図である。

図1(A)、従来例を示す図イメージセンサではデジタルクランプ方式が採用され、従来例を示す図12と基本的な構成は共通する。ただし、本実施の形態では、図12に示すクランプレベル発生回路105と異なる新たなクランプレベルの設定方法が採用され、クランプレベル発生回路105に代えて、新たな方法が実施可能な構成のクランプシステム20が設けられている。クランプシステム20は、制御回路5Aに制御されて動作する。また、詳細は後述するが、画素部1にフォトセンサが形成されていない「センサなし画素部」が設けられている点でも従来と異なる。

### 【0035】

他の構成、すなわち、画素部1の有効画素10の基本構成や接続関係、垂直駆動回路2、カラム処理回路3、水平シフトレジスタ4、アナログ信号処理回路（アナログフロントエンド：AFE）6、A/Dコンバータ（ADC）7、D/Aコンバータ（DAC）8および出力処理回路9の構成と基本的な動作は、従来と共通する。したがって、カラム処理回路3の構成を示す図10を、以下の説明でも用いることとする。

なお、制御回路5Aはマイクロコンピュータを内蔵し、図12に示すタイミング制御回路5と同様なタイミング制御機能に加え、クランプシステム20を含む全ての構成の制御、さらには電源の管理なども行うことができるものとする。

### 【0036】

画素部1の有効画素部（PIXEL）を構成する各有効画素10は、図3に示す3トランジスタ型の場合、入力した光を光電変換するフォトセンサPDと3つのトランジスタ1

1～13とを有する。3つのトランジスタは、ノードNDをフローティング状態から電源線15への接続状態に切り替え、ノードNDに電源電圧を充電して、その電荷量をリセットするリセットトランジスタ11と、リセット後に再びフローティング状態となったノードNDにフォトセンサPDの蓄積電荷（通常、電子）を転送する転送トランジスタ12と、ノードNDに転送された蓄積電荷に応じた画素信号を増幅して垂直信号線14に出力する読み出しトランジスタ13とからなる。

#### 【0037】

リセットトランジスタ11のゲートに、同一行内の画素に共通なりセット制御線16が接続されている。また、転送トランジスタ12のゲートに、同一行内の有効画素に共通な転送制御線17が接続されている。10

なお、4トランジスタ型の場合、読み出しトランジスタ13と電源線15との間に、さらに選択トランジスタが接続される。このため、選択トランジスタのゲート電圧を制御する選択制御線が必要となる。

これらの制御線16と17、ならびに、電源線15（および選択制御線）のそれぞれに各種信号または各種電圧を供給する垂直駆動回路2が接続されている。また、垂直信号線14に一斉に読み出された有効画素信号を並列処理してノイズを除去し、時系列のシリアル信号に変換するカラム処理回路3および水平シフトレジスタ4が設けられている。これらの垂直駆動回路2、カラム処理回路3および水平シフトレジスタ4は制御回路5Aにより制御されて動作する。

#### 【0038】

カラム処理回路3は、図10に示すように、垂直信号線14ごとに設けられた電流源31、CDS回路32およびサンプリングスイッチ33を有している。電流源31は、読み出しトランジスタ13に一定電流を供給するために設けられている。また、CDS回路32は、有効画素部（PIXEL）の画素信号に対し、その黒レベルでサンプル・ホールドした電圧と、蓄積電荷に応じた画素信号レベルでサンプル・ホールドした電圧との差分をとって、両電圧に重畠したノイズ成分（たとえば画面ムラとなるノイズ）をキャンセルする回路である。このノイズ除去後の画素信号レベルはCDS回路32の出力で保持された後、さらに、水平シフトレジスタ4から供給されるパルスによって順次オンされるサンプリングスイッチ33により、点順次でサンプリングされる。20

#### 【0039】

図10に示すカラム処理回路3は、この点順次サンプリング後の画素信号を複数本のバスに供給し、内蔵のマルチプレクサ34で1つの時系列信号（シリアル信号）に変換する構成が採用されている。他の構成として、点順次サンプリング後の画素信号を1本の信号線に供給し、時系列のシリアル信号としてそのまま出力する方法を採用してもよい。30

#### 【0040】

シリアル信号は、図1(A)に示すアナログ信号処理回路(AFE)6に入力される。入力されるシリアル信号は黒レベルが白レベルより電位として高いので、アナログ信号処理回路6内で反転され、黒レベルが白レベルより電位として低い信号に変換される。また、この信号は、必要に応じてゲイン調整や高周波成分の除去が施された後、アナログ信号処理回路6から出力される。アナログ信号処理回路6から出力されたシリアル信号は、ADCコンバータ(ADC)7によりデジタル化される。そして、AD変換後のシリアル信号は出力処理回路9でデジタル信号処理された後、外部に出力される。40

#### 【0041】

ADCコンバータ7の出力は、出力処理回路9のほかにクランプシステム20にも入力される。クランプシステム20は、前述した新たな方法によりデジタルのクランプレベルVcdを設定し、これをDACコンバータ(DAC)8に出力する。デジタルのクランプレベルVcdは、DACコンバータ8により、アナログのクランプレベルVcaに変換される。このクランプレベルVcaは、カラム処理回路3およびアナログ信号処理回路(AFE)6の内部に存在するクランプ回路にフィードバックされる。ここで、「クランプ回路」とは、たとえば、カラム処理回路3のCDS回路32内で黒レベルと信号レベルの電圧

差をとるオペアンプ、アナログ信号処理回路6内の反転増幅器やゲインコントロールアンプなど、出力の基準電位が黒レベルに設定され、かつ、この基準電位が変更可能な回路の全てをいう。クランプ回路が複数あり、そのうち幾つかにクランプレベルV<sub>c a</sub>をフィードバックする場合、クランプ回路の選択は任意である。また、全てのクランプ回路にクランプレベルV<sub>c a</sub>をフィードバックしてもよい。ただし、最終的にA/Dコンバータ(A/D C)7に出力される信号の黒レベルを補正することが目的であることから、クランプレベルV<sub>c a</sub>がフィードバックされるクランプ回路に、アナログ信号処理回路6の最も後段側のクランプ回路を含むことが望ましい。

#### 【0042】

クランプシステム20の内部構成を除くと、以上説明した各構成と信号の基本的な流れは従来と共通する。

つぎに、本実施の形態の特徴である、有効画素以外の画素とクランプシステムの構成と、クランプレベル設定動作を説明する。

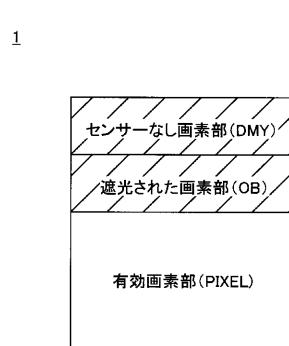

#### 【0043】

図2に示すように、有効画素部(PIXEL)の列方向の一方に、センサなし画素部(DMY)と遮光画素部(OB)が配置されている。センサなし画素部(DMY)と遮光画素部(OB)は、図3に示すように、有効画素部(PIXEL)と全ての垂直信号線14を共有している。このため、センサなし画素部(DMY)や遮光画素部(OB)から読み出された信号は、有効画素信号と同様にカラム処理回路3固有のばらつき(固定パターンノイズ)の影響を受けることになる。

なお、図2に示す配置例では、有効画素部(PIXEL)の上側にセンサなし画素部(DMY)と遮光画素部(OB)が配置されているが、これらを有効画素部(PIXEL)の下側に配置する、あるいは、上側と下側の両側に配置してもよい。各画素部(DMY)と(OB)は、1ラインのドット数(行方向の画素数)は有効画素部(PIXEL)に合わせて決められるが、ライン数(列方向の画素数)は任意である。また、センサなし画素部(DMY)と遮光画素部(OB)の相互の位置関係も任意である。

#### 【0044】

遮光画素部(OB)の各画素は、有効画素部(PIXEL)の画素と同じ構成であるが、その表面が遮光層1Aに覆われ、外光の影響が防止されている。ただし、外光の入力がない場合でも暗電流の発生があり、その影響は免れることができない。

これに対し、センサなし画素部(DMY)の各画素は、有効画素部(PIXEL)の画素と比較すると、センサとなるフォトダイオードPDが形成されていないため光電変換機能を有していない。有効画素ではフォトダイオードPDに接続される、転送トランジスタ12のソースは、センサなし画素部(DMY)の各画素では、画素行ごとに共通な一定電圧の供給線18に接続されている。この一定電圧の供給線18は、垂直駆動回路2に接続されて、そこから一定電圧が供給される。このような構成のセンサなし画素部(DMY)からは、暗電流の影響を完全に排除した出力が得られる。なお、図2に示す例では、センサなし画素部(DMY)も遮光層1Aで覆われているが、そのこと自体は必須ではない。ただし、各種トランジスタ11～13においても外光の影響を排除する意味で、図2のように、センサなし画素部(DMY)を遮光することが望ましい。

#### 【0045】

前述したクランプシステム20は、これらの画素部のうちセンサなし画素部(DMY)を用いてデジタルのクランプレベルV<sub>c d</sub>を決定する。

そのための構成としてクランプシステム20は、図1(B)に示すように、A/Dコンバータ(A/D C)7からシリアル信号を入力し、当該シリアル信号の少なくとも1行分の画素に対応した部分で最小の黒レベルを検出する黒レベル検出回路21と、検出した最小の黒レベルを基準にクランプレベルを設定するクランプレベル設定回路22と、設定したクランプレベルを増減し、クランプ回路にフィードバックする帰還量を調整する帰還量制御回路23とを有する。帰還量制御回路23からは、帰還量(すなわち、大きさ)が調整されたクランプレベルがD/Aコンバータ(D/A C)8に出力される。

10

20

30

40

50

## 【0046】

黒レベル検出回路21は、たとえば数フレームにわたって最小の黒レベルを複数回検出し、検出した複数の最小の黒レベルから最も低い黒レベルを検出することが可能である。これにより、精度が高い黒レベルが検出されることになり、その場合、クランプレベル設定回路22は、たとえば数フレームで最小の黒レベルをそのままクランプレベルとして設定する。なお、このような制御は、黒レベルを保持する保持回路のリフレッシュレートを変更することによっても達成できる。リフレッシュレートを変更可能な構成については後述する。

あるいは、最小の黒レベルのばらつき程度を示すマージンが経験的に分かっている場合、クランプレベル設定回路22は、黒レベル検出回路21で検出した最小の黒レベルに一定のマージンを加算し、その加算後の値をクランプレベルに設定することも可能である。

## 【0047】

つぎに、本実施の形態でセンサなし画素部(DMY)で最小の黒レベルを検出する理由を、遮光画素部(OB)で検出する従来のクランプレベル発生回路の問題点を明らかにすることにより説明する。

## 【0048】

前述したように、図12に示す従来のクランプレベル発生回路105でクランプレベルを設定し、これを前段のクランプ回路にフィードバックする目的は、クランプ回路より後段の回路、たとえばADコンバータ(ADC)7に入力する信号の最低レベルを、ADコンバータ7固有の入力レンジに適合させるためである。クランプのかけ方は、ADコンバータ7を搭載したCMOSイメージセンサにおいては、ADコンバータ7の入力レンジの下限値より若干マージンを持たせた高いレベルでクランプをかける必要がある。そのため、従来のクランプレベル発生回路105は、遮光画素部(OB)から出力される黒レベルの平均をクランプレベルとして設定する。このように平均化することで、環境温度や素子動作に起因して時間的に変化するランダムノイズの影響を除去できる。また、画素欠陥により、他の正常な画素よりも常に高い信号を出す白点欠陥画素、または、その逆に常に低い信号を出す黒点欠陥画素の影響を除去することができる。

## 【0049】

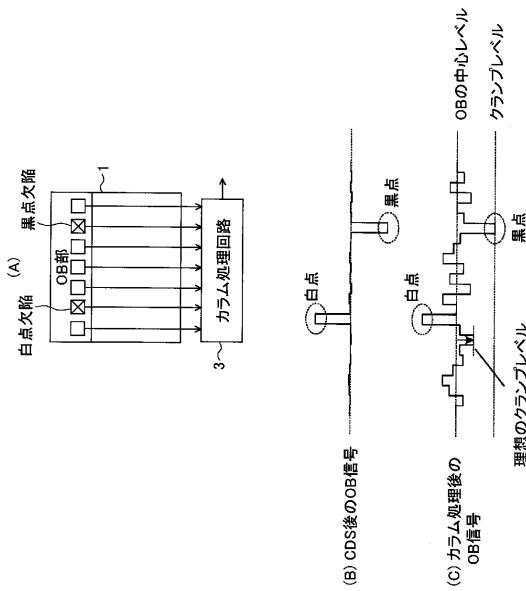

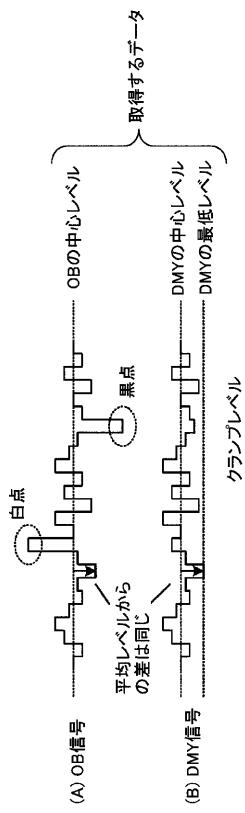

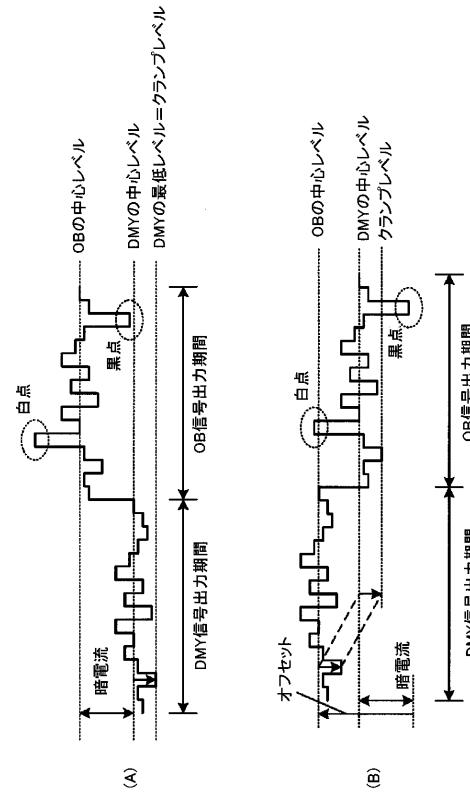

図4(A)に、遮光画素部(OB)から読み出された信号(以下、OB信号という)がカラム処理回路3に入力され、処理後に出力されるときのOB信号の流れを示す。また、図4(B)は、遮光画素部(OB)からのOB信号と、これに続く有効画素部(PIXEL)からの有効画素信号との反転後の信号を示す図であり、その横軸は時間tである。

また、図4(C)に、CDS回路32による処理後のOB信号を示し、図4(D)に、カラム処理回路3から出力されるカラム処理後のOB信号を示す。なお、図4(C)は、ある時間で見たときに多数のカラム処理回路32から出力される1ライン分のOB信号をつなげて示すものであり、その意味では、図4(C)の横軸は垂直信号線の番号に対応している。これに対し、図4(D)は、図4(C)に示す信号がシリアル信号に変換された後の時系列のOB信号を示すことから、その横軸は時間tであることに注意を要する。

## 【0050】

前述したようにCDS回路32の固定パターンノイズの除去効果により、図4(C)に示すCDS後のOB信号は列ごとのばらつきが抑圧されたものとなる。ただし、多少の抑圧残しが生じ、あるいは、CDS回路32自体のばらつきを反映して、列ごとのばらつきが完全に除去されるわけではない。カラム読み出し方式でない場合は、OB信号の中心レベルをサンプリングレベルに設定しても、ADコンバータの入力レンジの下限値とのマージン量M1は比較的小さくできる。

## 【0051】

ところが、カラム読み出し方式を採用した特許文献1の場合や、カラム読み出し方式を採用し、かつ、高速CDS処理のために列ごとにCDS回路を挿入した本実施の形態の場合、図4(D)に示すように、その後のカラム処理で列ごとのばらつきが再び発生することになる。

したがって、カラム処理後の信号を単に平均化して得られた黒レベルを用いてクランプをかける場合には、その生産ばらつきを考慮して図4(D)に示すようにA/Dコンバータ7の入力レンジの下限値より、より大きい量M2のマージンを持たせてクランプをかけないと、図4(C)と同じマージン量M1ではA/Dコンバータ7の入力レンジに入らないOB信号の列が生じてしまう可能性がある。

しかし、マージン量を大きくすることはそれだけA/Dコンバータ7の入力レンジを狭めてしまうことになる。

#### 【0052】

このようなカラム処理に起因した生産ばらつきは、量産の際に歩留まりを決定する要因となることから、マージンをみた設計だけでなく、システム的にばらつきを考慮した回路にすることが望ましい。そこで、本実施の形態では、平均値を用いるのではなく黒レベルの最も低いレベルでクランプをかけるクランプシステム20を搭載している。このようにすることで、出来上がった製品や製造ロットで異なるカラム回路起因のばらつきに常に追従できるようになる。黒レベルの最も低いレベルの検出は、A/Dコンバータ7から出力されるデジタルのシリアル信号を用いるため、デジタル信号処理で容易に行うことができる。

#### 【0053】

以上のように、最小の黒レベルにクランプレベルを設定することの優位性は明らかになったが、では、どの信号で最小の黒レベルを検出するかが、つぎに問題となる。考えられる信号は、遮光画素部(OB)からのOB信号と、センサなし画素部(DMY)からの信号(以下、DMY信号という)である。以下、本実施の形態でDMY信号を用いる理由を、OB信号を用いた場合の問題点を明らかにすることで説明する。

#### 【0054】

遮光画素部(OB)は、フォトダイオードPDを有するため有効画素部(PIXEL)と同様な確率で、白点や黒点の欠陥画素が発生する可能性がある。

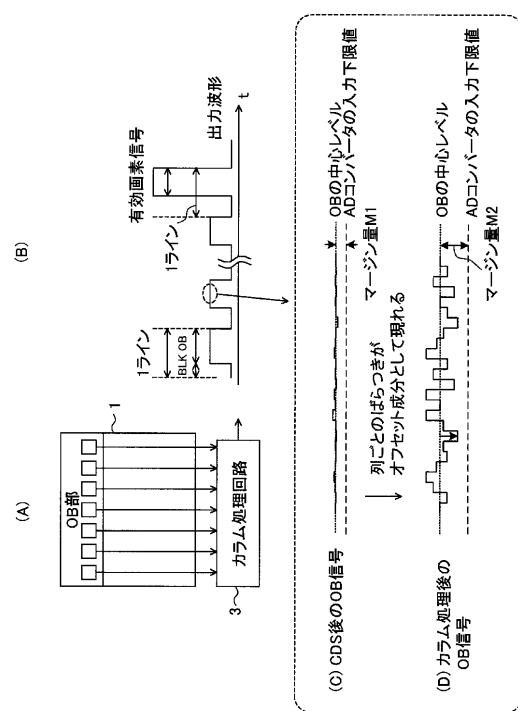

図5(A)に、白点欠陥と黒点欠陥がそれぞれ1つずつ存在する遮光画素部(OB)から読み出されたOB信号がカラム処理回路3に入力され、処理後に出力されるときのOB信号の流れを示す。また、図5(B)に、CDS回路32による処理後のOB信号を示し、図5(C)に、カラム処理回路3から出力されるカラム処理後のOB信号を示す。

#### 【0055】

遮光画素部(OB)に画素欠陥、とくに黒点欠陥があった場合、黒点欠陥では通常の画素に存在する暗電流成分が発生しないため、そのOBレベルは異常に低いものとなる。この黒点欠陥レベルはノイズではないため、図5(B)に示すようにCDS回路32後の信号でも同様に存在し、カラム処理後の信号では、図5(C)に示すようにカラム処理起因のばらつきと重畳された状態になる。いま、かりに黒点欠陥がないとすると、理想とするクランプレベルは、図5(C)に示すように、カラム処理起因のばらつきの最低レベルである。ところが、黒点欠陥が1つでも存在すると、そこが最低レベルであるので、黒点欠陥レベルが検出されて、そのレベルにクランプレベルが設定されてしまう。この場合に検出された列は、必ずしもカラム処理起因のばらつきの最低レベルの列に対応していない。また、黒点欠陥の有無に応じたその時々で、クランプレベルが変動し画質が安定しない。さらに、このようにクランプレベルが欠陥の有無に依存して切り替わると、その切り替え直後などで信号がA/Dコンバータの入力レンジを超えてしまう可能性もある。

#### 【0056】

これに対し本実施の形態では、センサなし画素部(DMY)からのOB信号を用いて最小の黒レベルを検出することから、欠陥を考慮しなくてもよく、カラム処理起因のばらつきによる最低レベルを最小の黒レベルとして検出することができる。その結果、欠陥の有無に左右されてクランプレベルが大きく変動することなく画質が安定する。また、急激なクランプレベルの切り替えがなく、そのために信号がA/Dコンバータ7の入力レンジを超える不具合が生じない。

#### 【0057】

10

20

30

40

50

ところで、センサなし画素部（D M Y）からのD M Y信号は暗電流がない画素からの信号であるため、その意味で本実施の形態の方法は、一見、遮光画素部（O B）からのO B信号を用い、暗電流がない黒点欠陥を最小の黒レベルとして検出した上記の場合と余り変わらないように思われる。しかし、上記のO B信号を検出する場合は、欠陥がない場合の理想のクランプレベルと異なる列、すなわちカラム処理起因のばらつきの最低レベルを検出しているわけではないことから、D M Y信号を用いる本実施の形態の方法で検出した最小の黒レベルよりも、多くの場合、高いレベルを検出してしまう。その結果、その分だけ信号のダイナミックレンジを狭めてしまうことになる。

これに対し、本実施の形態では、ダイナミックレンジを最大限確保できる最小の黒レベルを安定して検出できるという大きな利点を有する。

10

#### 【0058】

##### [第2の実施の形態]

上述した第1の実施の形態では、センサなし画素部（D M Y）を新たに設け、D M Y信号で最小の黒レベルを検出した。センサなし画素部（D M Y）のライン数を増やすと、それだけ画素部1の面積が大きくなり、好ましくない。その意味では、センサなし画素部（D M Y）を最小の1ライン分設けるとする。ところが、その場合、以下の問題がある。

#### 【0059】

従来のO B信号の黒レベルを平均化する場合は、たとえば1ラインで1000列の画素を考えた場合、1フレームで1000列分のデータを取得し、これを平均化することでランダムノイズが十分抑圧された値を得ることができる。ところが、D M Y信号から最小の黒レベルを検出する場合、1フレームで1つのデータしか取得することができないため、ランダム性の雑音が十分抑圧された正しい値の黒レベルを検出するためには数10フレーム以上のデータを取得する必要がある。したがって、その数10フレーム以上のデータを取得してからクランプレベルを設定するようでは、後段のA Dコンバータの入力レンジを常に超えない高速なフィードバック制御が行えない。

20

#### 【0060】

第2の実施の形態は、1フレームで1つしか黒レベルを検出しない場合でも、数10フレームにわたって最低の黒レベルを保持でき安定して動作するクランプシステムに関する。このクランプシステムでは、センサなし画素部（D M Y）からのD M Y信号のほかに、遮光画素部（O B）からのO B信号を用いている。

30

#### 【0061】

図6に、第2の実施の形態にかかるクランプシステム20の構成図を示す。

このクランプシステム20内のクランプレベル設定回路22は、D M Y信号またはO B信号を加算平均する加算平均回路221、4つの保持回路222～225、比較器226、セレクタ227、および、2つの演算回路228と229とを有する。

4つの保持回路222～225は、D M Yデータの演算指示を示す制御信号S1を受けて、黒レベル検出回路21からの最小の黒レベルを保持するD M Y最小値保持回路（第1の保持回路）222と、制御信号S1を受けて、加算平均回路221からのD M Y信号の黒レベルの平均値を保持するD M Y平均値保持回路（第2の保持回路）223と、O Bデータの演算指示を示す制御信号S2を受けて、加算平均回路221からのO B信号の黒レベルの平均値を保持するO B平均値保持回路（第3の保持回路）224と、第1の演算回路228の演算結果（差分値）を保持する差分値保持回路225とからなる。

40

第1の演算回路228は、本例では減算器であり、D M Y最小値をD M Y最小値保持回路222から入力し、また、D M Y平均値をD M Y平均値保持回路223から入力し、D M Y最小値からD M Y平均値を引いた差分値を求め、差分値保持回路225に出力する。

比較器226は、D M Y平均値保持回路223の保持内容と、O B平均値保持回路224の保持内容を比較し、その小さい方が選択されるように指示する制御信号S3をセレクタ227に出力する。セレクタ227は、制御信号S3の入力に応じてD M Y平均値またはO B平均値の小さい方を選択して第2の演算回路229に出力する。

第2の演算回路229は、本例では加算器であり、セレクタ227から出力されたD M

50

Y 平均値またはOB 平均値に、差分値保持回路225 で保持された差分値を読み出して加算する。この加算後の値がクランプレベルであるが、さらに、クランプレベルの値が帰還量制御回路23 により増減された後、図示を省略したDA コンバータ8 に出力される。

#### 【0062】

以下、このような構成で実現できるクランプレベルの設定方法について説明する。

前述したようにセンサなし画素部(DMY) は、フォトダイオードPD がないので暗電流は発生しない。したがって画素欠陥による黒点が存在しない。言い換えると、センサなし画素部(DMY) から得られるすべてのDMY 信号が黒点のレベルとなる。したがって、DMY 信号のばらつきはカラム処理回路3 に起因した列のばらつき、そのものとなる。

一方、遮光画素部(OB) は、フォトダイオードPD があるので暗電流が発生し、通常、そこから出力されるOB 信号は、上記DMY 信号より暗電流分だけ全体的にオフセットがのった信号になる。ただし、画素欠陥によって暗電流の発生しない黒点、もしくは暗電流の多く発生する白点も存在する可能性がある。OB 信号は、これらの暗電流起因のばらつきに加え、カラム処理回路3 に起因した列のばらつきが加算された信号となる。

#### 【0063】

上記のことを簡単にまとめると、つぎの【表1】のようになる。

##### 【表1】

$$(n \text{ 列目 DMY データ}) = (\text{DMY データの平均値}) \pm (n \text{ 列目の列ばらつき})$$

(n 列目 OB データ) = (OB データの平均値) ± (n 列目の列ばらつき) ただし、白点と黒点のデータを含む

$$(OB データの平均値) = (DMY データの平均値) + (\text{暗電流オフセット})$$

#### 【0064】

ここで、(DMY データの平均値) は各列で読み出されたDMY 信号の黒レベルの平均値を表し、(OB データの平均値) は各列で読み出されたOB 信号の黒レベルの平均値を表す。また、(n 列目のばらつき) は、複数の垂直信号線のうちn 番目(n は任意の自然数) にカラム処理回路で処理される過程で生じた黒レベルのばらつきの、その平均値を基準にした列ごとのばらつき量を表す。

#### 【0065】

DMY 信号およびOB 信号は、図6 に示す加算平均回路221 に入力されると平均化され、ここで、時間的なばらつきである熱雑音のようなランダムノイズは十分に抑圧される。また、そのとき、たとえばOB 信号に黒点により黒レベルが異常に低い黒点OB データが1000列に1つ存在していても、平均化され1/1000の寄与であるので平均値にはほとんど影響がない。白点も同様である。加算平均回路221 から出力されたDMY 平均値(DMY 信号の黒レベルの平均値) はDMY 平均値保持回路223 で保持され、加算平均回路221 から出力されたOB 平均値(OB 信号の黒レベルの平均値) はOB 平均値保持回路224 で保持される。

#### 【0066】

また、黒レベル検出回路21 で検出されたDMY 信号の最小の黒レベルは、DMY 最小値としてDMY 最小値保持回路222 で保持される。第1の演算回路228 により、このDMY 最小値と上記DMY 平均値が、それぞれ対応する保持回路から読み出され、DMY 最小値からDMY 最小値を引いた差分値が求められる。なお、この差分値は負の値であるが、後述する第2の演算回路229 でセレクタ出力に加算されるので、その第2の演算回路からは、セレクタ出力から差分(差分値の絶対値)を引いた出力が得られる。これは、通常減算器の規模が加算器の規模より大きいので、できるだけ加算器を1つでも多く用いる回路的工夫の結果である。したがって、このようなことを考慮しない場合は、第1の演算回路228 は、DMY 平均値からDMY 最小値を引くように構成すると、第2の演算回路229 は、セレクタ出力から差分(正の値)を引く減算器で構成される。

#### 【0067】

比較器226 は、DMY 保持回路223 とOB 保持回路224 の保持データを比較する。その結果、DMY 平均値の方がOB 平均値より低ければ、DMY 平均値がセレクタ22

10

20

20

30

40

50

7により選択されて出力され、逆に、O B 平均値の方が低ければO B 平均値がセレクタ 227 から出力される。

このようにセレクタ 227 は 2 つの平均値のうち低い方を選択して出力するので、第 2 の演算回路 229 は、実質的に、差分値保持回路 225 から読み出した差分値の絶対値を、この値が低い方の平均値から差し引く演算が実行される。第 2 の演算回路 229 により設定されたクランプレベルが、必要に応じて帰還量制御回路 23 で調整されアナログ化された後に、クランプ回路にフィードバックされる。このとき、O B 平均値より D M Y 平均値の方が低くければ D M Y 信号の黒レベルの最低レベルでクランプがかけられ、逆に、O B 平均値の方が低ければ O B 信号の平均から、D M Y 信号から抽出された差分値を引いた値でクランプがかけられる。

#### 【0068】

図 7 (A) および図 7 (B) に、上記したクランプレベルの設定方法で取得するデータをまとめて示す。

この方法のポイントは、カラム処理回路起因のばらつきの低い方の最大ばらつきを示す差分値を、D M Y 信号で抽出し、O B 平均値 ( 中心レベル ) を基準にクランプレベルを決める場合でも、この抽出した差分値を用いることである。そのため、O B 信号に黒点が存在するような場合でも、黒点に依存しない最低レベルを検出できる。

しかし、先ほど述べたように D M Y 信号には暗電流がないために O B 信号より低く、このシステムでは、図 8 (A) に示すように、いつも D M Y 平均値から差分値を引いた D M Y 信号の最低レベルでクランプをかけてしまう。そのため、暗電流分だけ、信号のダイナミックレンジを常に損してしまう。

#### 【0069】

ここで、図 3 に示すように垂直信号線 14 ( 一定電圧の供給線 18 でも可能 ) にオフセット発生回路 1B を設け、この問題を解決する。図 3 では、読み出しトランジスタ 13 のゲートに転送トランジスタ 12 を介してフォトダイオード P D を接続する代わりに、転送トランジスタ 12 のソースを一定電圧で保持し、垂直信号線 14 の電位をオフセット発生回路 1B により 2 段階の電圧で制御する構成が採用されている。

#### 【0070】

画素のデータ読み出しは、読み出しトランジスタ 13 のしきい値電圧ばらつきを抑制するため、通常、リセット信号を始めに読み出し ( P 相期間 ) 、次に、フォトダイオード P D から転送トランジスタ 12 を介して読み出しトランジスタ 13 のゲートに画素信号を入力して、この画素信号を增幅して垂直信号線 14 読み出す ( D 相期間 ) 。そして、C D S 回路 32 によって P 相と D 相の垂直信号線電圧の差分をとる動作が行われる。

#### 【0071】

オフセット発生回路 1B は、センサなし画素部 ( D M Y ) からの信号の読み出し期間に限って、この P 相期間、D 相期間で図 3 に示すようなパルスを入力する。これにより、このパルスの電圧差だけ D M Y 信号に任意の直流電圧オフセットを持たせることができる。したがって、図 8 (B) に示すように、常に O B 信号よりも D M Y 信号が十分高くなるよう調整することができる。このようにすることで D M Y 平均値は O B 平均値よりも大きくなるので、クランプレベルは、次の [ 表 2 ] のようになる。

#### [ 表 2 ]

$$( \text{クランプレベル} ) = ( \text{O B の平均値} ) - \{ ( \text{ダミーの平均値} ) - ( \text{ダミーの最小値} ) \}$$

#### 【0072】

その結果、黒点が存在したとしても O B 信号の最低レベルで常にクランプし、その分信号のダイナミックレンジを広げることができる。

#### 【0073】

このように O B 信号の中心レベルを基準にクランプをとる構成にすると、暗電流によりクランプレベルが変動することになり、環境温度変化に対するクランプレベルの追従性を高める必要がある。また、D M Y 信号の最低レベルでクランプする場合にも共通することであるが、スタートアップ時やゲイン変更時の追従性も高めておく必要がある。

そこで、図6に示すクランプシステム20では、DMY最小値保持回路222、DMY平均値保持回路223、および、OB平均値保持回路224のリフレッシュレートが、制御回路5Aからの制御信号S4により任意に変更可能に構成されている。

#### 【0074】

図6に示すクランプシステム20では、デジタル信号処理であるため、加算平均回路221で行なう加算平均は、たとえばビット数にあわせて加算数を決めてシフト演算することで簡単に行なうことができる。また、黒レベル検出回路21で行なう最小値検出では、1ラインで最も値の低いDMY信号の黒レベルを検出する。

このとき、最小値は1フレームに1データしか得られないことから、ランダムノイズを十分に抑圧したデータを得るためにには数フレームのデータを取得してその平均値を求める必要がある。すなわち、最小値は数フレームのリフレッシュレートを持つことになる。

これに対して、平均値は1フレームで列分のデータを取得できることから、ランダムノイズは1フレームで十分抑圧することができるため1フレームごとのリフレッシュレートを与えることができる。

このように、最小値の値と平均値の値に別々のリフレッシュレートを与えておくことと、スタートアップ時やゲイン変更時における黒レベルの変動に対して平均値は1フレームでそれに追従することができ、クランプレベルもその平均値の変動に応じて追従することが可能となる。

さらに、クランプ量に帰還率をかけることでクランプ後、ADCコンバータ7の入力レンジから入力信号が外れないような制御をかけることができる。

本実施の形態では、このようなクランプフィードバックシステムを用いることで、ADCコンバータ7の入力レンジを最大限に活用したCMOSイメージセンサを実現することができる。

#### 【図面の簡単な説明】

#### 【0075】

【図1】第1および第2の実施の形態にかかるCMOSイメージセンサの全体の構成図とクランプシステムの構成図

#### 【図2】画素部の構成図

#### 【図3】画素部の回路構成を示す図

【図4】OB信号の流れと構成、ならびに、そのCDS処理後の列ばらつきとカラム処理後の列ばらつきを示す図

【図5】白点欠陥と黒点欠陥がそれぞれ1つずつ存在する場合のOB信号の流れと、そのCDS処理後の列ばらつきおよびカラム処理後の列ばらつきを示す図

#### 【図6】第2の実施の形態にかかるクランプシステムの構成図

#### 【図7】クランプレベルの設定で取得するデータを示す図

【図8】DMY信号でクランプをかける場合と、OB信号でクランプをかける場合を示す図

#### 【図9】従来のアナログクランプ方式のCMOSイメージセンサの構成図

#### 【図10】画素部とカラム処理回路の詳細を示す図

#### 【図11】OB信号の平均値を基準とした画素信号の説明図

#### 【図12】従来のデジタルクランプ方式のCMOSイメージセンサの構成図

#### 【符号の説明】

#### 【0076】

1...画素部、1B...オフセット発生回路、2...垂直駆動回路、3...カラム処理回路、4...水平シフトレジスタ、5...制御回路、6...アナログ信号処理回路、7...DAコンバータ、8...ADCコンバータ、9...出力回路、10...有効画素、11...リセットトランジスタ、12...転送トランジスタ、13...読み出しトランジスタ、14...垂直信号線、18...一定電圧の供給線、20...クランプシステム、21...黒レベル検出回路、22...クランプレベル設定回路、23...帰還量制御回路、221...加算平均回路、222...DMY最小値保持回路(第1の保持回路)、223...DMY平均値保持回路(第2の保持回路)、224...

10

20

40

50

O B 平均値保持回路 (第3の保持回路)、225...差分値保持回路、226...比較器、227...セレクタ、228...第1の演算回路、229...第2の演算回路、PIXEL...有効画素部、DMY...センサなし画素部、OB...遮光画素部、Vca, Vcd...クランプレベル

【図1】

【図2】

(B)

【 図 3 】

【 図 5 】

【 図 4 】

【 図 6 】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

---

フロントページの続き

(72)発明者 久松 康秋

神奈川県横浜市保土ヶ谷区神戸町134番地 ソニー・エルエスアイ・デザイン株式会社内

FターM(参考) 4M118 AB01 BA14 CA02 FA06 FA33 FA42 FA50 GB09

5C024 AX01 CX04 GY31 HX10 HX13 HX28 HX29