(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-244204

(P2005-244204A)

(43) 公開日 平成17年9月8日(2005.9.8)

(51) Int.Cl.<sup>7</sup>

**H01L 21/336**

**G02F 1/1368**

**H01L 21/288**

**H01L 21/3213**

**H01L 29/786**

F 1

H01L 29/78 627C

G02F 1/1368

H01L 21/288

H05B 33/14

H01L 29/78 617J

テーマコード(参考)

2H092

3K007

4M104

5F033

5F110

審査請求 未請求 請求項の数 12 O L (全 55 頁) 最終頁に続く

(21) 出願番号 特願2005-18883 (P2005-18883)

(22) 出願日 平成17年1月26日 (2005.1.26)

(31) 優先権主張番号 特願2004-17583 (P2004-17583)

(32) 優先日 平成16年1月26日 (2004.1.26)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2004-17608 (P2004-17608)

(32) 優先日 平成16年1月26日 (2004.1.26)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 前川 慎志

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 小路 博信

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】電子機器、半導体装置およびその作製方法

## (57) 【要約】

【課題】 現状では、製造プロセスにスピノコート法を用いる成膜方法が多く用いられている。今後、さらに基板が大型化すると、スピノコート法を用いる成膜方法では、大型の基板を回転させる機構が大規模となる点、材料液のロスおよび廃液量が多い点で大量生産上、不利と考えられる。

【解決手段】 本発明は、半導体装置の製造プロセスにおいて、液滴吐出法で感光性の導電膜材料液を選択的に吐出し、レーザー光などで選択的に露光した後、現像することによって微細な配線パターンを実現する。本発明は、導体パターンを形成するプロセスにおいて、パテニング工程が短縮でき、材料の使用量の削減も図れるため大幅なコストダウンが実現でき、大面積基板にも対応できる。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

絶縁表面を有する基板上に、感光性材料を含む導電膜材料を液滴吐出法で吐出して第1の導電膜パターンを形成する工程と、

前記第1の導電膜パターンに対してレーザー光を選択的に照射して露光する工程と、

露光された第1の導電膜パターンを現像して、該第1の導電膜パターンよりも幅の狭い第2の導電膜パターンを形成する工程と、

前記第2の導電膜パターンを覆うゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に半導体膜を形成する工程と、を有することを特徴とする半導体装置の作製方法。

10

**【請求項 2】**

請求項1において、前記感光性材料を含む導電膜材料は、Ag、Au、Cu、Ni、Al、Ptの化合物あるいは単体のいずれかが含まれていることを特徴とする半導体装置の作製方法。

**【請求項 3】**

請求項1または請求項2において、前記感光性材料は、ネガ型であることを特徴とする半導体装置の作製方法。

**【請求項 4】**

請求項1または請求項2において、前記感光性材料は、ポジ型であることを特徴とする半導体装置の作製方法。

20

**【請求項 5】**

絶縁表面を有する基板表面上に、ゲート電極を形成する工程と、

前記ゲート電極を覆うゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に第1の半導体膜を形成する工程と、

前記第1の半導体膜上にn型またはp型を付与する不純物元素を含む第2の半導体膜を形成する工程と、

前記第2の半導体膜上にポジ型の感光性材料を含む導電膜材料を液滴吐出法で吐出して第1の導電膜パターンを形成する工程と、

前記第1の導電膜パターンに対して、前記基板の表面側からレーザー光を選択的に照射して露光する工程と、

露光された第1の導電膜パターンを現像して、ソース電極およびドレイン電極を形成する工程と、

前記ソース電極およびドレイン電極をマスクとして、前記第1の半導体膜および第2の半導体膜のエッチングを行う工程と、を有することを特徴とする半導体装置の作製方法。

30

**【請求項 6】**

絶縁表面を有する基板表面上に、ゲート電極を形成する工程と、

前記ゲート電極を覆うゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に第1の半導体膜を形成する工程と、

前記第1の半導体膜上にn型またはp型を付与する不純物元素を含む第2の半導体膜を形成する工程と、

前記第2の半導体膜上にネガ型の感光性材料を含む導電膜材料を液滴吐出法で吐出して第1の導電膜パターンを形成する工程と、

前記第1の導電膜パターンに対して、前記基板の裏面側から前記ゲート電極をマスクとしてレーザー光を照射して露光する工程と、

露光された第1の導電膜パターンを現像して、前記ゲート電極の幅と同一間隔を有して自己整合的にソース電極およびドレイン電極を形成する工程と、

前記ソース電極およびドレイン電極をマスクとして、前記第1の半導体膜および第2の半導体膜のエッチングを行う工程と、を有することを特徴とする半導体装置の作製方法。

40

**【請求項 7】**

絶縁表面を有する第1の基板上にゲート配線またはゲート電極と、

50

前記ゲート配線またはゲート電極上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上にチャネル形成領域を含む半導体層と、

前記半導体層上に形成されたソース電極またはドレイン電極と、

前記ソース電極または前記ドレイン電極上に形成された画素電極とを有し、

前記チャネル形成領域は、前記ゲート電極の幅と同一のチャネル長を有し、且つ、前記ゲート電極は、前記ソース電極と前記ドレイン電極との間隔と同一であることを特徴とする半導体装置。

#### 【請求項 8】

請求項 7において、前記チャネル形成領域を含む半導体層は、水素またはハロゲン水素が添加された非単結晶半導体膜、または多結晶半導体膜であることを特徴とする半導体装置。 10

#### 【請求項 9】

請求項 7 または請求項 8 において、前記ソース電極または前記ドレイン電極は、感光性材料を含んでいることを特徴とする半導体装置。

#### 【請求項 10】

請求項 7 乃至 9 のいずれか一において、前記半導体装置は、第 1 の基板と、第 2 の基板と、前記第 1 の基板と前記第 2 の基板とからなる一対の基板間に保持された液晶とを有していることを特徴とする半導体装置。

#### 【請求項 11】

請求項 7 乃至 9 のいずれか一において、前記半導体装置は、陰極と、有機化合物を含む層と、陽極と、薄膜トランジスタとを有する発光素子を複数有することを特徴とする半導体装置。 20

#### 【請求項 12】

請求項 7 乃至 11 のいずれか一において、前記半導体装置は、映像音声双方向通信装置、または汎用遠隔制御装置であることを特徴とする電子機器。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は薄膜トランジスタ（以下、TFT という）で構成された回路を有する半導体装置およびその作製方法に関する。例えば、有機発光素子を有する発光表示装置や、液晶表示パネルに代表される電気光学装置を部品として搭載した電子機器に関する。 30

#### 【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用して機能しうる装置全般を指し、電気光学装置、半導体回路および電子機器は全て半導体装置である。

#### 【背景技術】

#### 【0003】

近年、絶縁表面を有する基板上に形成された半導体薄膜（厚さ数～数百 nm 程度）を用いて薄膜トランジスタ（TFT）を構成する技術が注目されている。薄膜トランジスタは IC や電気光学装置のような電子デバイスに広く応用され、特に画像表示装置のスイッチング素子として開発が急がれている。 40

#### 【0004】

画像表示装置として、液晶表示装置が一般によく知られている。パッシブ型の液晶表示装置に比べ高精細な画像が得られることからアクティブマトリクス型の液晶表示装置が多く用いられるようになっている。アクティブマトリクス型の液晶表示装置においては、マトリクス状に配置された画素電極を駆動することによって、画面上に表示パターンが形成される。詳しくは選択された画素電極と該画素電極に対応する対向電極との間に電圧が印加されることによって、画素電極と対向電極との間に配置された液晶層の光学変調が行われ、この光学変調が表示パターンとして観察者に認識される。

#### 【0005】

これまで、一枚のマザーガラス基板から複数の液晶表示パネルを切り出して、大量生産を効率良く行う生産技術が採用されてきた。マザーガラス基板のサイズは、1990年初頭における第1世代の300×400mmから、2000年には第4世代となり680×880mm、若しくは730×920mmへと大型化して、一枚の基板から多数の表示パネルが取れるように生産技術が進歩してきた。

#### 【0006】

また、近年、自発光型の発光素子としてEL素子を有した発光装置の研究が活発化している。この発光装置は有機ELディスプレイ、又は有機発光ダイオードとも呼ばれている。これらの発光装置は、動画表示に適した速い応答速度、低電圧、低消費電力駆動などの特徴を有しているため、新世代の携帯電話や携帯情報端末(PDA)をはじめ、次世代ディスプレイとして大きく注目されている。10

#### 【0007】

有機化合物を含む層を発光層とするEL素子は、有機化合物を含む層(以下、EL層と記す)が陽極と、陰極との間に挟まれた構造を有し、陽極と陰極とに電界を加えることにより、EL層からルミネッセンス(Electro Luminescence)が発光する。また、EL素子からの発光は、一重項励起状態から基底状態に戻る際の発光(蛍光)と三重項励起状態から基底状態に戻る際の発光(リン光)とがある。

#### 【0008】

アクティブマトリクス型の表示装置の用途は広がっており、画面サイズの大面積化とともに、高精細化や高開口率化や高信頼性の要求が高まっている。20

#### 【0009】

特許文献1には、複数のパネルをタイル状に配置して1つの表示画面を形成することによって大型ディスプレイを実現している。しかし、複数のパネルを使用するためコスト高となり、駆動方法も特殊なものとなってしまう。

#### 【0010】

また、画面サイズの大面積化と同時に、生産性の向上や低コスト化の要求も高まっている。

#### 【0011】

また、成膜に要する液体の歩留まりを高めるため、レジスト液をノズルから細径の線状に連続吐出できる装置を用いて半導体ウェハ上に成膜を行う技術が特許文献2に記載されている。30

【特許文献1】特開2000-298446

【特許文献2】特開2000-188251

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0012】

現状では、製造プロセスにスピンコート法を用いる成膜方法が多く用いられている。今後、さらに基板が大型化すると、スピンコート法を用いる成膜方法では、大型の基板を回転させる機構が大規模となる点、材料液のロスおよび廃液量が多い点で大量生産上、不利と考えられる。また、矩形の基板をスピンコートさせると回転軸を中心とする円形のムラが塗布膜に生じやすい。本発明は、大量生産上、大型の基板に適している液滴吐出法を用いた製造プロセスを提供する。40

#### 【0013】

また、本発明は、液滴吐出法で形成された配線を用いた大画面ディスプレイ、およびその作製方法を提供する。また、本発明は、液滴吐出法で形成された配線を所望の電極幅としてチャネル長が10μm以下のTFTを画素に配置した発光装置をも提供する。

#### 【0014】

また、本発明は、液滴吐出法で形成された配線を所望の電極幅としてチャネル長が10μm以下のTFTをスイッチング素子とした液晶表示装置をも提供する。

#### 【課題を解決するための手段】

10

20

30

40

50

## 【0015】

本発明は、液滴吐出法で感光性の導電膜材料液を選択的に吐出し、レーザー光などで選択的に露光した後、現像することによって微細な配線パターンを実現する。本発明は、導体パターンを形成するプロセスにおいて、パターニング工程が短縮でき、材料の使用量の削減も図れるため大幅なコストダウンが実現でき、大面積基板にも対応できる。

## 【0016】

導電膜材料液は、Ag、Au、Cu、Ni、Al、Ptなどの金属或いは合金と、有機高分子樹脂、光重合開始剤、光重合单量体、または溶剤などからなる感光性樹脂とを含んでいる。有機高分子樹脂としては、ノボラック樹脂、アクリル系コポリマー、メタクリル系コポリマー、セルローズ誘導体、環化ゴム系樹脂などを用いる。

10

## 【0017】

感光性材料には大きくわけてネガ型とポジ型がある。ネガ型の場合は、露光された部分で化学反応が生じ、現像液によって化学反応が生じた部分のみが残されてパターンが形成される。また、ポジ型の場合は、露光された部分で化学反応が生じ、現像液によって化学反応が生じた部分が溶解され、露光されなかった部分のみが残されてパターンが形成される。

## 【0018】

また、配線幅は、レーザー光の照射精度によって決定されるため、滴下する液滴量や粘度や、ノズル径に関係なく、所望の配線幅を得ることができる。通常、配線幅は、ノズルから吐出された材料液と基板の接触角で変化する。例えば、標準的なインクジェット装置の一つのノズル径( $50\text{ }\mu\text{m} \times 50\text{ }\mu\text{m}$ )から吐出される量は $30\text{ p1} \sim 200\text{ p1}$ であり、得られる配線幅は $60\text{ }\mu\text{m} \sim 300\text{ }\mu\text{m}$ であるが、レーザー光で露光する本発明により幅(例えば電極幅 $3\text{ }\mu\text{m} \sim 10\text{ }\mu\text{m}$ )が狭い配線を得ることができる。また、標準より細いノズル径では、一つのノズルから吐出される量は $0.1\text{ p1} \sim 40\text{ p1}$ であり、得られる配線幅は $5\text{ }\mu\text{m} \sim 100\text{ }\mu\text{m}$ である。

20

## 【0019】

また、液滴吐出法により配線パターンを形成する場合、ノズルから間欠的に吐出されて導電膜材料液滴がドット状に滴下される場合と、ノズルから連続的に吐出されて繋がったまま紐状の材料が付着される場合の両方がある。本発明においては、適宜、いずれか一方で配線パターンを形成すればよい。比較的幅の大きい配線パターンを形成する場合には、ノズルから連続的に吐出されて繋がったまま紐状の材料を付着させるほうが生産性に優れている。

30

## 【0020】

また、液滴吐出法により配線パターンを形成する前に、予め基板上に密着性を向上させる下地層の形成(または下地前処理)を全面または選択的に行なうことが好ましい。下地層の形成としては、スプレー法またはスパッタ法によって光触媒物質(酸化チタン( $\text{TiO}_x$ )、チタン酸ストロンチウム( $\text{SrTiO}_3$ )、セレン化カドミウム( $\text{CdSe}$ )、タンタル酸カリウム( $\text{KTaO}_3$ )、硫化カドミウム( $\text{CdS}$ )、酸化ジルコニア( $\text{ZrO}_2$ )、酸化ニオブ( $\text{Nb}_2\text{O}_5$ )、酸化亜鉛( $\text{ZnO}$ )、酸化鉄( $\text{Fe}_2\text{O}_3$ )、酸化タンゲステン( $\text{WO}_3$ ))を全面に滴下する処理、またはインクジェット法やゾルゲル法を用いて有機材料(ポリイミド、アクリル、或いは、シリコン( $\text{Si}$ )と酸素( $\text{O}$ )との結合で骨格構造が構成され、置換基に水素、フッ素、アルキル基、または芳香族炭化水素のうち少なくとも1種を有する材料を用いた塗布絶縁膜)を選択的に形成する処理を行えばよい。

40

## 【0021】

光触媒物質は、光触媒機能を有する物質を指し、紫外光領域の光(波長 $400\text{ nm}$ 以下、好ましくは $380\text{ nm}$ 以下)を照射し、光触媒活性を生じさせるものである。光触媒物質上に、インクジェット法で代表される液滴吐出法により、溶媒に混入された導電体を吐出すると、微細な描画を行うことができる。

## 【0022】

例えば、 $\text{TiO}_x$ に光照射する前、親油性はあるが、親水性はない、つまり撥水性の状

50

態にある。光照射を行うことにより、光触媒活性が起こり、親水性にかわり、逆に親油性がない状態となる。なお光照射時間により、親水性と親油性を共に有する状態にもなりうる。

【0023】

更に光触媒物質へ遷移金属(Pd、Pt、Cr、Ni、V、Mn、Fe、Ce、Mo、W等)をドーピングすることにより、光触媒活性を向上させたり、可視光領域(波長400nm~800nm)の光により光触媒活性を起こすことができる。このように光の波長は光触媒物質によって決定することができるため、光照射とは光触媒物質の光触媒活性化せる波長の光を照射することを指す。

【0024】

また、光照射を行いながら、インクジェット法で代表される液滴吐出法により、溶媒に混入された導電体を吐出してもよい。

【0025】

また、レーザー光の波長により光触媒活性を起こす光触媒物質を全面に形成した後、選択的にレーザー光を照射することによって、照射した領域のみを改質することも可能である。また、レーザー光照射を行いながら、インクジェット法で代表される液滴吐出法により、溶媒に混入された導電体を吐出してもよい。

【0026】

なお、親水性とは、水に濡れやすい状態を指し、接触角が30度以下、特に接触角が5度以下を超親水性という。一方、撥水性とは、水に濡れにくい状態を指し、接触角が90度以上のものを指す。同様に親油性とは、油に濡れやすい状態を指し、撥油性とは油に濡れにくい状態を指す。なお接触角とは、滴下したドットのふちにおける、形成面と液滴の接線がなす角度のことを指す。

【0027】

導電膜材料液を用いて液滴吐出法で配線を形成する際、導電膜材料液が流動性を有していたり、ベーク時に流動性が増加するものであった場合、液だれによって精細なパターンとすることが困難となる恐れがある。また、配線間隔が狭い場合、パターン同士が繋がってしまう恐れもある。本発明においては、液だれによって幅広のパターンとなっても、導電膜材料液に感光性材料を含ませて、レーザー光で精密に露光、現像を行うことで精細なパターンを得ている。

【0028】

例えば、大面積の表示を行うディスプレイを製造する際、ゲート配線のようなバスラインは液滴吐出法で得られる幅の広い配線とすることが好ましいが、ゲート電極は幅の狭い配線とすることが好ましい。このような場合、ポジ型の感光性材料を含ませた導電膜材料液でゲート配線および第1のゲート電極を形成し、第1のゲート電極の部分(除去したい部分)のみレーザー光を選択的に照射して、現像させることによって細く加工された第2のゲート電極を形成することができる。また、ネガ型の感光性材料を含ませた導電膜材料液でゲート配線および第1のゲート電極を形成した場合、ゲート配線および第1のゲート電極の部分(残したい部分)のみレーザー光を選択的に照射して、現像させることによって細く加工された第2のゲート電極を形成することができる。

【0029】

また、TFTのゲート電極だけでなく、ソース電極、ドレイン電極、発光素子の陽極、発光素子の陰極、電源線、引き回し配線などを形成することもできる。

【0030】

また、レーザー光の波長によっては、ガラス基板を通過させることができ、そのレーザー光を用いて裏面露光を行うことができる。基板の裏面から露光することによって、先に界面付近の導電膜材料を露光することができ、配線と下地層との密着性、または配線と基板との密着性を向上させることができる。

【0031】

また、ボトムゲート型TFTを作製する場合、裏面露光によってゲート電極をマスクと

して、自己整合的（セルフアラインにソース電極、ドレイン電極を形成することもできる。

【0032】

本明細書で開示する発明の構成は、

絶縁表面を有する基板上にゲート配線またはゲート電極と、

前記ゲート配線またはゲート電極上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上にチャネル形成領域を含む半導体層と、

前記半導体層上に形成されたソース電極またはドレイン電極と、

前記ソース電極または前記ドレイン電極上に形成された画素電極とを有し、

前記チャネル形成領域は、前記ゲート電極の幅と同一のチャネル長を有し、且つ、前記ゲート電極は、前記ソース電極と前記ドレイン電極との間隔と同一であることを特徴とする半導体装置である。

【0033】

上記構成において、前記薄膜トランジスタの活性層は、水素またはハロゲン水素が添加された非単結晶半導体膜、または多結晶半導体膜であることを特徴としている。

【0034】

また、TFT構造に関係なく本発明を適用することが可能であり、例えば、ボトムゲート型（逆スタガ型）TFTや、トップゲート型（順スタガ型）TFTを用いることが可能である。また、シングルゲート構造のTFTに限定されず、複数のチャネル形成領域を有するマルチゲート型TFT、例えばダブルゲート型TFTとしてもよい。

【0035】

また、TFTの活性層としては、非晶質半導体膜、結晶構造を含む半導体膜、非晶質構造を含む化合物半導体膜などを適宜用いることができる。さらにTFTの活性層として、非晶質と結晶構造（単結晶、多結晶を含む）の中間的な構造を有し、自由エネルギー的に安定な第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する結晶質な領域を含んでいるセミアモルファス半導体膜（微結晶半導体膜、マイクロクリスタル半導体膜とも呼ばれる）も用いることができる。

【0036】

また、上記各構成において、前記ソース電極または前記ドレイン電極は、感光性材料を含んでいることを特徴としている。

【0037】

液滴吐出法を用いた導電層などのパターン形成方法では、粒子状に加工されたパターン形成材料を吐出し、焼成によって融合や融着接合させ固化することでパターンを形成する。よって、そのパターンは、スパッタ法などで形成したパターンが、多くは柱状構造を示すのに対し、多くの粒界を有する多結晶状態を示すことが多い。

【0038】

また、液滴吐出法を用いて得られた導電層は、樹脂を含む材料であることを特徴の一つとしている。この樹脂は導電材料を含む液滴に含まれるバインダーなどの材料であり、この樹脂と、溶媒と、金属のナノ粒子とを混合させることによってインクジェット法で吐出可能なものとしている。

【0039】

また、上記各構成において、前記半導体装置は、第1の基板と、第2の基板と、前記第1の基板と前記第2の基板とからなる一対の基板間に保持された液晶とを有している。あるいは、前記半導体装置は、陰極と、有機化合物を含む層と、陽極と、薄膜トランジスタとを有する発光素子を複数有することを特徴としている。

【0040】

また、上記各構成において、前記半導体装置は、図33(D)にその一例を示す映像音声双方通信装置、または汎用遠隔制御装置である。

【0041】

また、作製方法に関する発明の構成は、

10

20

30

40

50

絶縁表面を有する基板上に、感光性材料を含む導電膜材料を液滴吐出法で吐出して第1の導電膜パターンを形成する工程と、

前記第1の導電膜パターンに対してレーザー光を選択的に照射して露光する工程と、

露光された第1の導電膜パターンを現像して、第1の導電膜パターンよりも幅の狭い第2の導電膜パターンを形成する工程と、

前記第2の導電膜パターンを覆うゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に半導体膜を形成する工程と、を有することを特徴とする半導体装置の作製方法。

【0042】

また、上記構成において、前記感光性材料を含む導電膜材料は、Ag、Au、Cu、Ni、Al、Ptの化合物あるいは単体のいずれかが含まれていることを特徴としている。 10

【0043】

また、上記構成において、前記感光性材料は、ネガ型、或いはポジ型であることを特徴としている。

【0044】

また、作製方法に関する他の発明の構成は、

絶縁表面を有する基板表面上に、ゲート電極を形成する工程と、

前記ゲート電極を覆うゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に第1の半導体膜を形成する工程と、

前記第1の半導体膜上にn型またはp型を付与する不純物元素を含む第2の半導体膜を形成する工程と、 20

前記第2の半導体膜上にポジ型の感光性材料を含む導電膜材料を液滴吐出法で吐出して第1の導電膜パターンを形成する工程と、

前記第1の導電膜パターンに対して、前記基板の表面側からレーザー光を選択的に照射して露光する工程と、

露光された第1の導電膜パターンを現像して、ソース電極およびドレイン電極を形成する工程と、

前記ソース電極およびドレイン電極をマスクとして、前記第1の半導体膜および第2の半導体膜のエッチングを行う工程と、

を有することを特徴とする半導体装置の作製方法である。 30

【0045】

また、作製方法に関する他の発明の構成は、

絶縁表面を有する基板表面上に、ゲート電極を形成する工程と、

前記ゲート電極を覆うゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に第1の半導体膜を形成する工程と、

前記第1の半導体膜上にn型またはp型を付与する不純物元素を含む第2の半導体膜を形成する工程と、

前記第2の半導体膜上にネガ型の感光性材料を含む導電膜材料を液滴吐出法で吐出して第1の導電膜パターンを形成する工程と、

前記第1の導電膜パターンに対して、前記基板の裏面側から前記ゲート電極をマスクとしてレーザー光を照射して露光する工程と、 40

露光された第1の導電膜パターンを現像して、前記ゲート電極の幅と同一間隔を有して自己整合的にソース電極およびドレイン電極を形成する工程と、

前記ソース電極およびドレイン電極をマスクとして、前記第1の半導体膜および第2の半導体膜のエッチングを行う工程と、

を有することを特徴とする半導体装置の作製方法である。

【発明の効果】

【0046】

本発明により液滴吐出法でも微細な配線パターンを得ることができる。また、本発明によりパターニング工程が短縮でき、材料の使用量の削減も図れるため大幅なコストダウンが

実現でき、大面積基板にも対応できる。

【発明を実施するための最良の形態】

【0047】

本発明の実施形態について、以下に説明する。

【0048】

(実施の形態1)

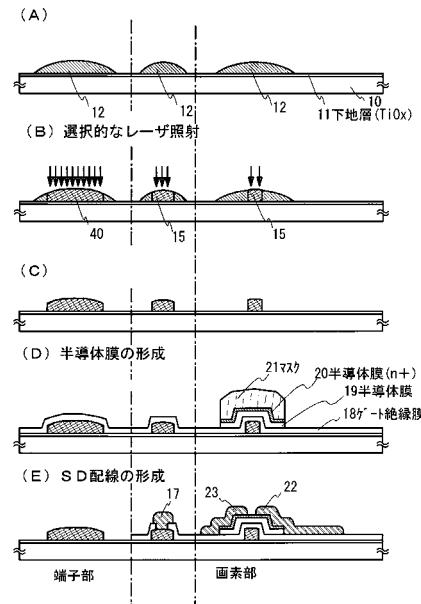

ここではチャネルエッチ型のTFTをスイッチング素子とするアクティブマトリクス型発光表示装置の作製例を図1、図2に示す。

【0049】

まず、基板10上に後に形成する液滴吐出法による材料層と密着性を向上させるための下地層11を形成する。下地層11は、極薄く形成すれば良いので、必ずしも層構造を持っていなくても良く、下地前処理とみなすこともできる。スプレー法またはスパッタ法によって光触媒物質(酸化チタン( $TiO_x$ )、チタン酸ストロンチウム( $SrTiO_3$ )、セレン化カドミウム( $CdSe$ )、タンタル酸カリウム( $KTaO_3$ )、硫化カドミウム( $CdS$ )、酸化ジルコニウム( $ZrO_2$ )、酸化ニオブ( $Nb_2O_5$ )、酸化亜鉛( $ZnO$ )、酸化鉄( $Fe_2O_3$ )、酸化タンゲステン( $WO_3$ ))を全面に滴下する処理、またはインクジェット法やゾルゲル法を用いて有機材料(ポリイミド、アクリル、或いは、シリコン( $Si$ )と酸素( $O$ )との結合で骨格構造が構成され、置換基に水素、フッ素、アルキル基、または芳香族炭化水素のうち少なくとも1種を有する材料を用いた塗布絶縁膜)を選択的に形成する処理を行えばよい。

【0050】

また、ここでは基板上に導電性材料を吐出する場合に密着性を良くする下地前処理を行う例を示したが、特に限定されず、材料層(例えば、有機層、無機層、金属層)、或いは、吐出した導電性層の上にさらに液滴吐出法で材料層(例えば、有機層、無機層、金属層)を形成する場合において、材料層と材料層との密着性向上のための $TiO_x$ 成膜処理を行っても良い。つまり、液滴吐出法で導電性材料を吐出して描画する場合、その導電性材料層の上下界面で下地前処理を挟み、その密着性を良くすることが望ましい。

【0051】

また、下地層11は、光触媒材料に限らず、3d遷移金属( $Sc$ 、 $Ti$ 、 $Cr$ 、 $Ni$ 、 $V$ 、 $Mn$ 、 $Fe$ 、 $Co$ 、 $Cu$ 、 $Zn$ 等)、または、その酸化物、窒化物、酸窒化物を用いることができる。

【0052】

なお、基板10は、バリウムホウケイ酸ガラス、アルミノホウケイ酸ガラス若しくはアルミノシリケートガラスなど、フュージョン法やフロート法で作製される無アルカリガラス基板の他、本作製工程の処理温度に耐えうる耐熱性を有するプラスチック基板等を用いることができる。

【0053】

次いで、液滴吐出法、代表的にはインクジェット法により導電膜材料液を滴下して導電膜パターン12を形成する。(図1(A))導電膜材料液に含まれる導電材料としては、金( $Au$ )、銀( $Ag$ )、銅( $Cu$ )、白金( $Pt$ )、パラジウム( $Pd$ )、タンゲステン( $W$ )、ニッケル( $Ni$ )、タンタル( $Ta$ )、ビスマス( $Bi$ )、鉛( $Pb$ )、インジウム( $In$ )、錫( $Sn$ )、亜鉛( $Zn$ )、チタン( $Ti$ )、若しくはアルミニウム( $Al$ )、これらからなる合金、これらの分散性ナノ粒子、又はハロゲン化銀の微粒子を用いる。特に、ゲート配線は、低抵抗化することが好ましいので、比抵抗値を考慮して、金、銀、銅のいずれかの材料を溶媒に溶解又は分散させたものを用いることが好適であり、より好適には、低抵抗な銀、銅を用いるとよい。但し、銀、銅を用いる場合には、不純物拡散防止対策のため、合わせてバリア膜を設けるとよい。溶媒は、酢酸ブチル等のエスチル類、イソプロピルアルコール等のアルコール類、アセトン等の有機溶剤等に相当する。表面張力と粘度は、溶媒の濃度を調整したり、界面活性剤等を加えたりして適宜調整する。

10

20

30

40

50

## 【0054】

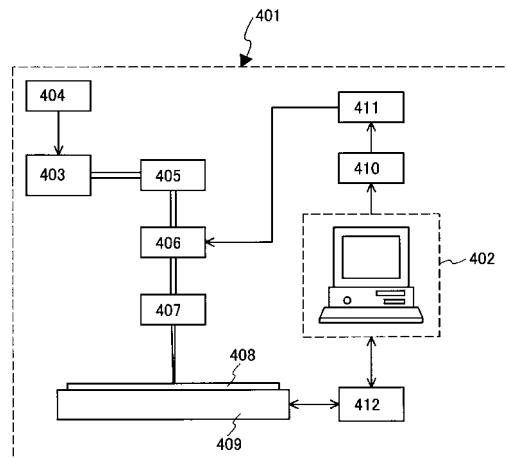

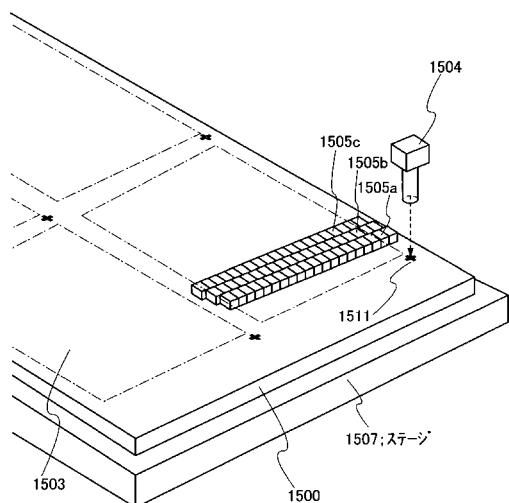

ここで、液滴吐出装置の一例を図16に示す。

## 【0055】

図16において、1500は大型基板、1504は撮像手段、1507はステージ、1511はマーカー、1503は1つのパネルが形成される領域を示している。1つのパネルの幅と同じ幅のヘッド1505a、1505b、1505cを備え、ステージを移動させてこれらのヘッドを走査、例えばジグザグまたは往復させて適宜、材料層のパターンを形成する。大型基板の幅と同じ幅のヘッドとすることも可能であるが、図16のように1つのパネルサイズに合わせるほうが操作しやすい。また、スループット向上のためには、ステージを動かしたままで材料の吐出を行うことが好ましい。

10

## 【0056】

また、ヘッド1505a、1505b、1505cやステージ1507には温度調節機能を持たせることが好ましい。

## 【0057】

なお、ヘッド(ノズル先端)と大型基板との間隔は、約1mmとする。この間隔を短くすることによって着弾精度を高めることができる。

## 【0058】

図16において、走査方向に対して3列としたヘッド1505a、1505b、1505cはそれぞれ異なる材料層を形成することを可能としてもよいし、同一材料を吐出してよい。3つのヘッドで同一材料を吐出して層間絶縁膜をパターン形成する場合にはスループットが向上する。

20

## 【0059】

なお、図16に示す装置は、ヘッド部を固定し、基板1500を移動させて走査させることも、基板1500を固定し、ヘッド部を移動させて走査させることも可能である。

## 【0060】

液滴吐出手段の個々のヘッド1505a、1505b、1505cは制御手段に接続され、それがコンピュータで制御することにより予めプログラミングされたパターンを描画することができる。吐出量は印加するパルス電圧により制御する。描画するタイミングは、例えば、基板上に形成されたマーカーを基準に行えば良い。或いは、基板の縁を基準にして基準点を確定させても良い。これをCCDなどの撮像手段で検出し、画像処理手段にてデジタル信号に変換したものをコンピュータで認識して制御信号を発生させて制御手段に送る。勿論、基板上に形成されるべきパターンの情報は記憶媒体に格納されたものであり、この情報を基にして制御手段に制御信号を送り、液滴吐出手段の個々のヘッドを個別に制御することができる。

30

## 【0061】

次いで、レーザー光を選択的に照射して、導電膜パターンの一部を露光させる。(図1(B))吐出する導電膜材料液には、予め感光性材料を含ませておき、照射するレーザー光によって化学反応させる。ここで感光性材料は、照射して化学反応させた部分を残すネガ型とした例を示している。レーザー光の照射によって、正確なパターン形状、特に細い幅の配線を得ることができる。

40

## 【0062】

ここで、レーザビーム描画装置について、図4を用いて説明する。レーザビーム描画装置401は、レーザビームを照射する際の各種制御を実行するパーソナルコンピュータ(以下、PCと示す。)402と、レーザビームを出力するレーザ発振器403と、レーザ発振器403の電源404と、レーザビームを減衰させるための光学系(NDフィルタ)405と、レーザビームの強度を変調するための音響光学変調器(AOM)406と、レーザビームの断面の拡大又は縮小をするためのレンズ、光路の変更するためのミラー等で構成される光学系407、Xステージ及びYステージを有する基板移動機構409と、PCから出力される制御データをデジタル-アナログ変換するD/A変換部410と、D/A変換部から出力されるアナログ電圧に応じて音響光学変調器406を制御するドライバ4

50

11と、基板移動機構409を駆動するための駆動信号を出力するドライバ412とを備えている。

【0063】

レーザ発振器403としては、紫外光、可視光、又は赤外光を発振することが可能なレーザ発振器を用いることができる。レーザー発振器としては、KrF、ArF、KrF、XeCl、Xe等のエキシマレーザ発振器、He、He-Cl、Ar、He-Ne、HF等の気体レーザ発振器、YAG、GdVO<sub>4</sub>、YVO<sub>4</sub>、YLF、YAlO<sub>3</sub>などの結晶にCr、Nd、Er、Ho、Ce、Co、Ti又はTmをドープした結晶を使った固体レーザー発振器、GaN、GaAs、GaAlAs、InGaAsP等の半導体レーザ発振器を用いることができる。なお、固体レーザ発振器においては、基本波の第1高調波～第5高調波を適用するのが好ましい。

【0064】

レーザビーム直接描画装置を用いた感光材料の感光方法について以下に述べる。なお、ここで言う感光材料とは、導電膜パターンとなる導電膜材料（感光材料含む）を指している。

【0065】

基板408が基板移動機構409に装着されると、PC402は図外のカメラによって、基板に付されているマーカの位置を検出する。次いで、PC402は、検出したマーカの位置データと、予め入力されている描画パターンデータとに基づいて、基板移動機構409を移動させるための移動データを生成する。この後、PC402が、ドライバ411を介して音響光学変調器406の出力光量を制御することにより、レーザ発振器403から出力されたレーザビームは、光学系405によって減衰された後、音響光学変調器406によって所定の光量になるように光量が制御される。一方、音響光学変調器406から出力されたレーザビームは、光学系407で光路及びビーム形を変化させ、レンズで集光した後、基板上に形成された感光材料に対して該ビームを照射して、感光材料を感光する。このとき、PC402が生成した移動データに従い、基板移動機構409をX方向及びY方向に移動制御する。この結果、所定の場所にレーザビームが照射され、感光材料の露光が行われる。

【0066】

なお、感光材料に照射されたレーザ光のエネルギーの一部は、熱に変換され、感光材料の一部を反応させる。従って、パターン幅は、レーザビームの幅より若干大きくなる。また、短波長のレーザ光ほど、ビーム径を小さく集光することができるため、微細な幅のパターンを形成するためには、短波長のレーザビームを照射することが好ましい。

【0067】

また、レーザビームの感光材料表面でのスポット形状は、点状、円形、橢円形、矩形、または線状（厳密には細長い長方形状）となるように光学系で加工されている。なお、スポット形状は円形であっても構わないが、線状にした方が、幅が均一なパターンを形成することができる。

【0068】

また、図4に示した装置は、基板の表面側からレーザー光を照射して露光する例を示したが、光学系や基板移動機構を適宜変更し、基板の裏面側からレーザー光を照射して露光するレーザビーム描画装置としてもよい。

【0069】

なお、ここでは、基板を移動して選択的にレーザビームを照射しているが、これに限定されず、レーザビームをX-Y軸方向に走査してレーザビームを照射することができる。この場合、光学系407にポリゴンミラー やガルバノミラーを用いることが好ましい。

【0070】

次いで、エッチャント（または現像液）を用いて現像を行い、余分な部分を除去して、本焼成を行ってゲート電極またはゲート配線となる金属配線15を形成する。（図1（C））

## 【0071】

また、金属配線15と同様に端子部に伸びる配線40も形成する。なお、ここでは図示しないが、発光素子に電流を供給するための電源線も形成してもよい。また、保持容量を形成するための容量電極または容量配線も必要であれば形成する。

## 【0072】

なお、ポジ型の感光性材料を用いる場合には、除去したい部分にレーザー照射を行って化学反応させ、その部分をエッチャントで溶解させればよい。

## 【0073】

また、導電膜材料液を滴下した後、室温乾燥または仮焼成を行ってからレーザー光の照射による露光を行ってもよい。

10

## 【0074】

次いで、プラズマCVD法やスパッタリング法を用いて、ゲート絶縁膜18、半導体膜、n型の半導体膜を順次、成膜する。

## 【0075】

ゲート絶縁膜18としては、PCVD法により得られる酸化珪素、窒化珪素、または窒化酸化珪素を主成分とする材料を用いる。また、ゲート絶縁膜18をシリコサン系ポリマーを用いた液滴吐出法により吐出、焼成してアルキル基を含むSiO<sub>x</sub>膜としてもよい。

## 【0076】

半導体膜は、シランやゲルマンに代表される半導体材料ガスを用いて気相成長法やスパッタリング法や熱CVD法で作製されるアモルファス半導体膜、或いはセミアモルファス半導体膜で形成する。

20

## 【0077】

アモルファス半導体膜としては、SiH<sub>4</sub>、若しくはSiH<sub>4</sub>とH<sub>2</sub>の混合気体を用いたPCVD法により得られるアモルファスシリコン膜を用いることができる。また、セミアモルファス半導体膜としては、SiH<sub>4</sub>をH<sub>2</sub>で3倍～1000倍に希釈した混合気体、Si<sub>2</sub>H<sub>6</sub>とGeF<sub>4</sub>のガス流量比を20～40:0.9(Si<sub>2</sub>H<sub>6</sub>:GeF<sub>4</sub>)で希釈した混合気体、或いはSi<sub>2</sub>H<sub>6</sub>とF<sub>2</sub>の混合気体、或いはSiH<sub>4</sub>とF<sub>2</sub>の混合気体を用いたPCVD法により得られるセミアモルファスシリコン膜を用いることができる。なお、セミアモルファスシリコン膜は、下地との界面により結晶性を持たせることができるため好ましい。

30

## 【0078】

また、SiH<sub>4</sub>とF<sub>2</sub>の混合気体を用いたPCVD法により得られるセミアモルファスシリコン膜にレーザー光を照射して、さらに結晶性を向上させてもよい。

## 【0079】

n型の半導体膜は、シランガスとフォスフィンガスを用いたPCVD法で形成すれば良く、アモルファス半導体膜、或いはセミアモルファス半導体膜で形成することができる。n型の半導体膜20を設けると、半導体膜と電極(後の工程で形成される電極)とのコンタクト抵抗が低くなり好ましいが、必要に応じて設ければよい。

## 【0080】

次いで、マスク21を設け、半導体膜と、n型の半導体膜とを選択的にエッティングして島状の半導体膜19、n型の半導体膜20を得る。(図1(D))マスク21の形成方法は、液滴吐出法や印刷法(凸版、平板、凹版、スクリーンなど)を用いて形成する。直接、所望のマスクパターンを液滴吐出法や印刷法で形成してもよいが、高精細度に形成するために液滴吐出法や印刷法で大まかなレジストパターンを形成した後、レーザー光を用いて選択的に露光を行って精細なレジストパターンを形成してもよい。

40

## 【0081】

図4に示すレーザビーム描画装置を用いれば、レジストの露光も行うことができる。その場合、感光材料をレジストとしてレーザー光により露光を行ってレジストマスク21を形成すればよい。

## 【0082】

50

次いで、マスク 21 を除去した後、マスク（図示しない）を設けてゲート絶縁膜を選択的にエッチングしてコンタクトホールを形成する。また、端子部においてはゲート絶縁膜を除去する。マスクの形成方法は、通常のフォトリソ技術、或いは、液滴吐出方法によるレジストパターン形成、或いは、全面にポジ型のレジスト塗布を行った後、レーザー光による露光、現像を行うレジストパターン形成でもよい。アクティブマトリクス型の発光装置においては一つの画素に複数の TFT が配置され、ゲート電極とゲート絶縁膜を介して上層の配線との接続箇所を有する。

## 【0083】

次いで、液滴吐出法により導電性材料（Ag（銀）、Au（金）、Cu（銅）、W（タンゲステン）、Al（アルミニウム）等）を含む組成物を選択的に吐出して、ソース配線またはドレイン配線 22、23、および引出電極 17 を形成する。なお、同様に、発光素子に電流を供給するための電源線や、端子部において接続配線（図示しない）も形成する。（図 1（E））

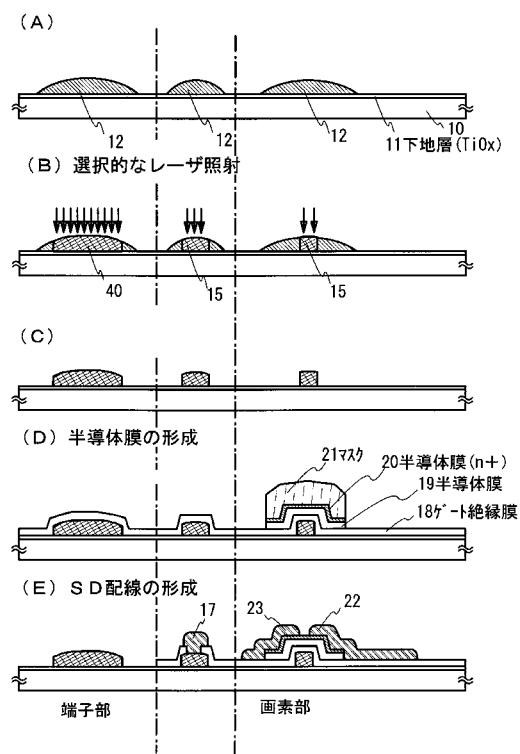

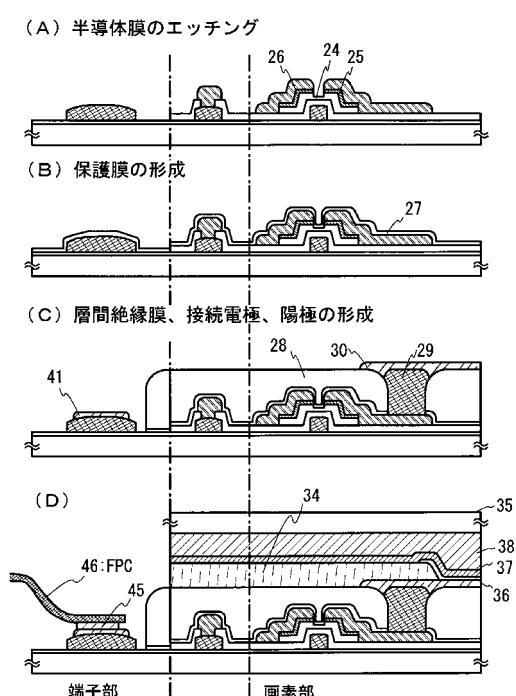

## 【0084】

次いで、ソース配線またはドレイン配線 22、23 をマスクとして n 型の半導体膜、および半導体膜の上層部をエッチングして、図 2（A）の状態を得る。この段階で、活性層となるチャネル形成領域 24、ソース領域 26、ドレイン領域 25 を備えたチャネルエッチ型の TFT が完成する。

## 【0085】

次いで、チャネル形成領域 24 を不純物汚染から防ぐための保護膜 27 を形成する。（図 2（B））保護膜 27 としては、スパッタ法、または P C V D 法により得られる窒化珪素、または窒化酸化珪素を主成分とする材料を用いる。ここでは保護膜を形成した例を示したが、特に必要でなければ設ける必要はない。

## 【0086】

次いで、液滴吐出法により層間絶縁膜 28 を選択的に形成する。層間絶縁膜 28 は、エポキシ樹脂、アクリル樹脂、フェノール樹脂、ノボラック樹脂、アクリル樹脂、メラミン樹脂、ウレタン樹脂等の樹脂材料を用いる。また、ベンゾシクロブテン、パリレン、フレア、透過性を有するポリイミドなどの有機材料、シロキサン系ポリマー等の重合によってできた化合物材料、水溶性ホモポリマーと水溶性共重合体を含む組成物材料等を用いて液滴吐出法で形成する。層間絶縁膜 28 の形成方法は、特に液滴吐出法に限定されず、塗布法や P C V D 法などを用いて全面に形成してもよい。

## 【0087】

次いで、層間絶縁膜 28 をマスクとして保護膜をエッチングし、ソース配線またはドレイン配線 22、23 上の一部に導電性部材からなる凸状部（ピラー）29 を形成する。凸状部（ピラー）29 は、導電性材料（Ag（銀）、Au（金）、Cu（銅）、W（タンゲステン）、Al（アルミニウム）等）を含む組成物の吐出と焼成を繰り返すことによって積み重ねてもよい。

## 【0088】

次いで、層間絶縁膜 28 上に凸状部（ピラー）29 と接する第 1 の電極 30 を形成する。（図 2（C））なお、同様に配線 40 と接する端子電極 41 も形成する。ここでは駆動用の TFT は n チャネル型とした例であるので第 1 の電極 30 は陰極として機能させることが好ましい。発光を通過させる場合、第 1 の電極 30 としては、液滴吐出法または印刷法によりインジウム錫酸化物（ITO）、酸化珪素を含むインジウム錫酸化物（ITSO）、酸化亜鉛（ZnO）、酸化スズ（SnO<sub>2</sub>）などを含む組成物からなる所定のパターンを形成し、焼成して第 1 の電極 30 および端子電極 41 を形成する。また、発光を第 1 の電極で反射させる場合、液滴吐出法により Ag（銀）、Au（金）、Cu（銅）、W（タンゲステン）、Al（アルミニウム）等の金属の粒子を主成分とした組成物からなる所定のパターンを形成し、焼成して第 1 の電極 30 および端子電極 41 を形成する。他の方法としては、スパッタリング法により透明導電膜、若しくは光反射性の導電膜を形成して、液滴吐出法によりマスクパターンを形成し、エッチングを組み合わせて第 1 の電極 30

10

20

30

40

50

を形成しても良い。

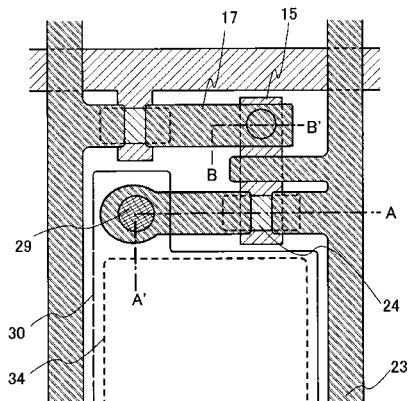

【0089】

図2(C)の段階での画素の上面図の一例を図3に示す。図3中において、鎖線A-A'、断面が図2(C)中の画素部右側の断面図と対応し、鎖線B-B'が図2(C)中の画素部左側の断面図と対応している。なお、図3中において、図1および図2に対応する部位には同じ符号を用いている。また、図3において、後に形成される隔壁34の端部となる箇所は点線で示している。

【0090】

また、ここでは保護膜27を設けた例としたため、層間絶縁膜28と凸状部(ピラー)29とを別々に形成したが、保護膜を設けない場合、液滴吐出法により同じ装置で形成することもできる。

【0091】

次いで、第1の電極30の周縁部を覆う隔壁34を形成する。隔壁(土手ともいう)34は、珪素を含む材料、有機材料及び化合物材料を用いて形成する。また、多孔質膜を用いても良い。但し、アクリル、ポリイミド等の感光性、非感光性の材料を用いて形成すると、その側面は曲率半径が連続的に変化する形状となり、上層の薄膜が段切れせずに形成されるため好ましい。

【0092】

以上の工程により、基板10上にボトムゲート型(逆スタガ型ともいう)のTFTおよび第1の電極が形成された発光表示パネル用のTFT基板が完成する。

【0093】

次いで、電界発光層として機能する層、即ち、有機化合物を含む層36の形成を行う。有機化合物を含む層36は、積層構造であり、それぞれ蒸着法または塗布法を用いて形成する。例えば、陰極上に電子輸送層(電子注入層)／発光層／正孔輸送層／正孔注入層と順次積層する。

【0094】

電子輸送層は、電荷注入輸送物質を含んでおり、特に電子輸送性の高い電荷注入輸送物質としては、例えばトリス(8-キノリノラト)アルミニウム(略称:Alq<sub>3</sub>)、トリス(5-メチル-8-キノリノラト)アルミニウム(略称:Almq<sub>3</sub>)、ビス(10-ヒドロキシベンゾ[h]-キノリナト)ベリリウム(略称:BeBq<sub>2</sub>)、ビス(2-メチル-8-キノリノラト)-4-フェニルフェノラト-アルミニウム(略称:BA1q)など、キノリン骨格またはベンゾキノリン骨格を有する金属錯体等が挙げられる。また正孔輸送性の高い物質としては、例えば4,4'-ビス[N-(1-ナフチル)-N-フェニル-アミノ]-ビフェニル(略称:-NPD)や4,4'-ビス[N-(3-メチルフェニル)-N-フェニル-アミノ]-ビフェニル(略称:TPD)や4,4',4''-トリス(N,N-ジフェニル-アミノ)-トリフェニルアミン(略称:TDATA)、4,4',4'''-トリス[N-(3-メチルフェニル)-N-フェニル-アミノ]-トリフェニルアミン(略称:MTDATA)などの芳香族アミン系(即ち、ベンゼン環-窒素の結合を有する)の化合物が挙げられる。

【0095】

また、電荷注入輸送物質のうち、特に電子注入性の高い物質としては、フッ化リチウム(LiF)、フッ化セシウム(CsF)、フッ化カルシウム(CaF<sub>2</sub>)等のようなアルカリ金属又はアルカリ土類金属の化合物が挙げられる。また、この他、Alq<sub>3</sub>のような電子輸送性の高い物質とマグネシウム(Mg)のようなアルカリ土類金属との混合物であってもよい。

【0096】

また、発光層は、有機化合物又は無機化合物を含む電荷注入輸送物質及び発光材料で形成し、その分子数から低分子系有機化合物、中分子系有機化合物(昇華性を有さず、且つ分子数が20以下、又は連鎖する分子の長さが10μm以下の有機化合物を指している)、高分子系有機化合物から選ばれた一種又は複数種の層を含み、電子注入輸送性又は正孔

10

20

30

40

50

注入輸送性の無機化合物と組み合わせても良い。

【0097】

発光材料には様々な材料がある。低分子系有機発光材料では、4-ジシアノメチレン-2-メチル-6-(1,1,7,7-テトラメチルジュロリジル-9-エニル)-4H-ピラン(略称:DCJT)、4-ジシアノメチレン-2-t-ブチル-6-(1,1,7,7-テトラメチルジュロリジル-9-エニル)-4H-ピラン(略称:DPA)、ペリフランテン、2,5-ジシアノ-1,4-ビス(10-メトキシ-1,1,7,7-テトラメチルジュロリジル-9-エニル)ベンゼン、N,N'-ジメチルキナクリドン(略称:DMQd)、クマリン6、クマリン545T、トリス(8-キノリノラト)アルミニウム(略称:Alq<sub>3</sub>)、9,9'-ビアントリル、9,10-ジフェニルアントラセン(略称:DPA)や9,10-ビス(2-ナフチル)アントラセン(略称:DNA)等を用いることができる。また、この他の物質でもよい。

【0098】

高分子系有機発光材料は低分子系に比べて物理的強度が高く、素子の耐久性が高い。また塗布により成膜することが可能であるので、素子の作製が比較的容易である。高分子系有機発光材料を用いた発光素子の構造は、低分子系有機発光材料を用いたときと基本的には同じであり、陰極/有機発光層/陽極となる。しかし、高分子系有機発光材料を用いた発光層を形成する際には、低分子系有機発光材料を用いたときのような積層構造を形成させることは難しく、多くの場合2層構造となる。具体的には、陰極/発光層/正孔輸送層/陽極という構造である。

【0099】

発光色は、発光層を形成する材料で決まるため、これらを選択することで所望の発光を示す発光素子を形成することができる。発光層の形成に用いることができる高分子系の電界発光材料は、ポリパラフェニレンビニレン系、ポリパラフェニレン系、ポリチオフェン系、ポリフルオレン系が挙げられる。

【0100】

ポリパラフェニレンビニレン系には、ポリ(パラフェニレンビニレン)[PPV]の誘導体、ポリ(2,5-ジアルコキシ-1,4-フェニレンビニレン)[RO-PPV]、ポリ(2-(2'-エチル-ヘキソキシ)-5-メトキシ-1,4-フェニレンビニレン)[MEH-PPV]、ポリ(2-(ジアルコキシフェニル)-1,4-フェニレンビニレン)[ROPh-PPV]等が挙げられる。ポリパラフェニレン系には、ポリパラフェニレン[PPP]の誘導体、ポリ(2,5-ジアルコキシ-1,4-フェニレン)[RO-PPP]、ポリ(2,5-ジヘキソキシ-1,4-フェニレン)等が挙げられる。ポリチオフェン系には、ポリチオフェン[PT]の誘導体、ポリ(3-アルキルチオフェン)[PAT]、ポリ(3-ヘキシルチオフェン)[PHT]、ポリ(3-シクロヘキシルチオフェン)[PCHT]、ポリ(3-シクロヘキシル-4-メチルチオフェン)[PCHMT]、ポリ(3,4-ジシクロヘキシルチオフェン)[PDCHT]、ポリ[3-(4-オクチルフェニル)-2,2ビチオフェン][POPT]、ポリ[3-(4-オクチルフェニル)-2,2ビチオフェン][PTOPT]等が挙げられる。ポリフルオレン系には、ポリフルオレン[PF]の誘導体、ポリ(9,9-ジアルキルフルオレン)[PDAF]、ポリ(9,9-ジオクチルフルオレン)[PDOF]等が挙げられる。

【0101】

なお、正孔輸送性の高分子系有機発光材料を、陽極と発光性の高分子系有機発光材料の間に挟んで形成すると、陽極からの正孔注入性を向上させることができる。一般にアクセプター材料と共に水に溶解させたものをスピンドル法などで塗布する。また、有機溶媒には不溶であるため、上述した発光性の有機発光材料との積層が可能である。正孔輸送性の高分子系有機発光材料としては、PEDOTとアクセプター材料としてのショウノウスルホン酸(CSA)の混合物、ポリアニリン[PANI]とアクセプター材料としてのポリスチレンスルホン酸[PSS]の混合物等が挙げられる。

【0102】

10

20

30

40

50

さらに、発光層は、一重項励起発光材料の他、金属錯体などを含む三重項励起材料を用いても良い。例えば、赤色の発光性の画素、緑色の発光性の画素及び青色の発光性の画素のうち、輝度半減時間が比較的短い赤色の発光性の画素を三重項励起発光材料で形成し、他を一重項励起発光材料で形成する。三重項励起発光材料は発光効率が良いので、同じ輝度を得るのに消費電力が少なくて済むという特徴がある。すなわち、赤色画素に適用した場合、発光素子に流す電流が少なくて済むので、信頼性を向上させることができる。低消費電力化として、赤色の発光性の画素と緑色の発光性の画素とを三重項励起発光材料で形成し、青色の発光性の画素を一重項励起発光材料で形成しても良い。人間の視感度が高い緑色の発光素子も三重項励起発光材料で形成することで、より低消費電力化を図ることができる。

10

#### 【0103】

三重項励起発光材料の一例としては、金属錯体をドーパントとして用いたものがあり、第三遷移系列元素である白金を中心金属とする金属錯体、イリジウムを中心金属とする金属錯体などが知られている。三重項励起発光材料としては、これらの化合物に限られることはなく、上記構造を有し、且つ中心金属に周期表の8～10属に属する元素を有する化合物を用いることも可能である。

#### 【0104】

また、正孔輸送層は、電荷注入輸送物質を含んでおり、正孔注入性の高い物質としては、例えば、モリブデン酸化物( $\text{MoO}_x$ )やバナジウム酸化物( $\text{VO}_x$ )、ルテニウム酸化物( $\text{RuO}_x$ )、タンゲステン酸化物( $\text{WO}_x$ )、マンガン酸化物( $\text{MnO}_x$ )等の金属酸化物が挙げられる。また、この他、フタロシアニン(略称: $\text{H}_2\text{Pc}$ )や銅フタロシアニン( $\text{CuPc}$ )等のフタロシアニン系の化合物が挙げられる。

20

#### 【0105】

なお、有機化合物を含む層36の形成前に、酸素雰囲気中のプラズマ処理や真空雰囲気下での加熱処理を行うとよい。蒸着法を用いる場合、予め、抵抗加熱により有機化合物は気化されており、蒸着時にシャッターが開くことにより基板の方向へ飛散する。気化された有機化合物は、上方に飛散し、メタルマスクに設けられた開口部を通って基板に蒸着される。また、フルカラー化するためには、発光色(R、G、B)ごとにマスクのアライメントを行えばよい。

30

#### 【0106】

発光層は、発光波長帯の異なる発光層を画素毎に形成して、フルカラー表示を行う構成とすれば良い。典型的には、R(赤)、G(緑)、B(青)の各色に対応した発光層を形成する。この場合に、画素の光放射側にその発光波長帯の光を透過するフィルター(着色層)を設けた構成とすることで、色純度の向上や、画素部の鏡面化(映り込み)の防止を図ることができる。フィルター(着色層)を設けることで、従来必要であるとされていた円偏光版などを省略することが可能となり、発光層から放射される光の損失を無くすことができる。さらに、斜方から画素部(表示画面)を見た場合に起こる色調の変化を低減することができる。

#### 【0107】

また、塗り分けを行わず、有機化合物を含む層36として単色の発光を示す材料を用い、カラーフィルターや色変換層を組み合わせることによりフルカラー表示を行うことができる。例えば、白色又は橙色の発光を示す電界発光層を形成する場合、画素の光放射側にカラーフィルター、又はカラーフィルター、色変換層、カラーフィルターと色変換層とを組み合わせたものを別途設けることによってフルカラー表示ができる。カラーフィルターや色変換層は、例えば第2の基板(封止基板)に形成し、基板へ張り合わせればよい。また上述したように、単色の発光を示す材料、カラーフィルター、及び色変換層のいずれも液滴吐出法により形成することができる。

40

#### 【0108】

白色に発光する発光層を形成するには、例えば、Alq<sub>3</sub>、部分的に赤色発光色素であるナイルレッドをドープしたAlq<sub>3</sub>、Alq<sub>3</sub>、p-EtTAZ、TPD(芳香族ジアミン

50

) を蒸着法により順次積層することで白色を得ることができる。また、スピンドルコートを用いた塗布法によりELを形成する場合には、塗布した後、真空加熱で焼成することが好ましい。例えば、正孔注入層として作用するポリ(エチレンジオキシチオフェン)/ポリ(スチレンスルホン酸)水溶液(PEDOT/PSS)を全面に塗布、焼成し、その後、発光層として作用する発光中心色素(1,1,4,4-テトラフェニル-1,3-ブタジエン(TPB)、4-ジシアノメチレン-2-メチル-6-(p-ジメチルアミノ-スチリル)-4H-ピラン(DCM1)、ナイルレッド、クマリン6など)ドープしたポリビニルカルバゾール(PVK)溶液を全面に塗布、焼成すればよい。

#### 【0109】

発光層は単層で形成することもでき、ホール輸送性のポリビニルカルバゾール(PVK)に電子輸送性の1,3,4-オキサジアゾール誘導体(PBD)を分散させてもよい。また、30wt%のPBDを電子輸送剤として分散し、4種類の色素(TPB、クマリン6、DCM1、ナイルレッド)を適当量分散することで白色発光が得られる。

#### 【0110】

以上に掲げる有機化合物を含む層を形成する物質は一例であり、正孔注入輸送層、正孔輸送層、電子注入輸送層、電子輸送層、発光層、電子ブロック層、正孔ブロック層などの機能性の各層を適宜積層することで発光素子を形成することができる。また、これらの各層を合わせた混合層又は混合接合を形成しても良い。発光層の層構造は変化しうるものであり、特定の電子注入領域や発光領域を備えていない代わりに、もっぱらこの目的用の電極を備えたり、発光性の材料を分散させて備えたりする変形は、本発明の趣旨を逸脱しない範囲において許容されうるものである。

#### 【0111】

もちろん単色発光の表示を行ってもよい。例えば、単色発光を用いてエリアカラータイプの発光表示装置を形成してもよい。エリアカラータイプは、パッシブマトリクス型の表示部が適しており、主に文字や記号を表示することができる。

#### 【0112】

次いで、第2の電極37を形成する。発光素子の陽極として機能する第2の電極37は光を透過する透明導電膜を用いて形成し、例えばITO、ITSOの他、酸化インジウムに2~20%の酸化亜鉛(ZnO)を混合した透明導電膜を用いる。発光素子は、有機化合物を含む層36を第1の電極と第2の電極で挟んだ構成になっている。なお、第1の電極及び第2の電極は仕事関数を考慮して材料を選択する必要があり、そして第1の電極及び第2の電極は、画素構成によりいずれも陽極、又は陰極となりうる。

#### 【0113】

上記のような材料で形成した発光素子は、順方向にバイアスすることで発光する。発光素子を用いて形成する表示装置の画素は、単純マトリクス方式、若しくはアクティブマトリクス方式で駆動することができる。いずれにしても、個々の画素は、ある特定のタイミングで順方向バイアスを印加して発光させることとなるが、ある一定期間は非発光状態となっている。この非発光時間に逆方向のバイアスを印加することで発光素子の信頼性を向上させることができる。発光素子では、一定駆動条件下で発光強度が低下する劣化や、画素内で非発光領域が拡大して見かけ上輝度が低下する劣化モードがあるが、順方向及び逆方向にバイアスを印加する交流的な駆動を行うことで、劣化の進行を遅くすることができ、発光装置の信頼性を向上させることができる。

#### 【0114】

また、第2の電極37の低抵抗化を図るため、発光領域とならない領域の第2の電極上に補助電極を設けてもよい。

#### 【0115】

また、第2の電極37を保護する保護層を形成してもよい。例えば、珪素からなる円盤状のターゲットを用い、成膜室雰囲気を窒素雰囲気または窒素とアルゴンを含む雰囲気とすることによって窒化珪素膜からなる保護膜を形成することができる。また、炭素を主成分とする薄膜(DLC膜、CN膜、アモルファスカーボン膜)を保護膜として形成しても

10

20

30

40

50

よく、別途、CVD法を用いた成膜室を設けてもよい。ダイヤモンドライクカーボン膜(DLC膜とも呼ばれる)は、プラズマCVD法(代表的には、RFプラズマCVD法、マイクロ波CVD法、電子サイクロトロン共鳴(ECR)CVD法、熱フィラメントCVD法など)、燃焼炎法、スパッタ法、イオンビーム蒸着法、レーザー蒸着法などで形成することができる。成膜に用いる反応ガスは、水素ガスと、炭化水素系のガス(例えばCH<sub>4</sub>、C<sub>2</sub>H<sub>2</sub>、C<sub>6</sub>H<sub>6</sub>など)とを用い、グロー放電によりイオン化し、負の自己バイアスがかかったカソードにイオンを加速衝突させて成膜する。また、CN膜は反応ガスとしてC<sub>2</sub>H<sub>4</sub>ガスとN<sub>2</sub>ガスとを用いて形成すればよい。なお、DLC膜やCN膜は、可視光に対して透明もしくは半透明な絶縁膜である。可視光に対して透明とは可視光の透過率が80~100%であることを指し、可視光に対して半透明とは可視光の透過率が50~80%であることを指す。なお、この保護膜は、必要がなければ特に設けなくともよい。

10

## 【0116】

次いで、封止基板35をシール材(図示しない)で貼り合わせて発光素子を封止する。なお、シール材で囲まれた領域には透明な充填材38を充填する。充填材38としては、透光性を有している材料であれば特に限定されず、代表的には紫外線硬化または熱硬化のエポキシ樹脂を用いればよい。ここでは屈折率1.50、粘度500cps、ショアD硬度90、テンシル強度3000psi、Tg点150、体積抵抗 $1 \times 10^{15}$ ·cm、耐電圧450V/milである高耐熱のUVエポキシ樹脂(エレクトロライト社製:2500Clear)を用いる。また、充填材38を一対の基板間に充填することによって、全体の透過率を向上させることができる。

20

## 【0117】

最後にFPC46を異方性導電膜45により公知の方法で端子電極41と貼りつける。(図2(D))

## 【0118】

以上の工程により、アクティブマトリクス型発光装置が作製できる。

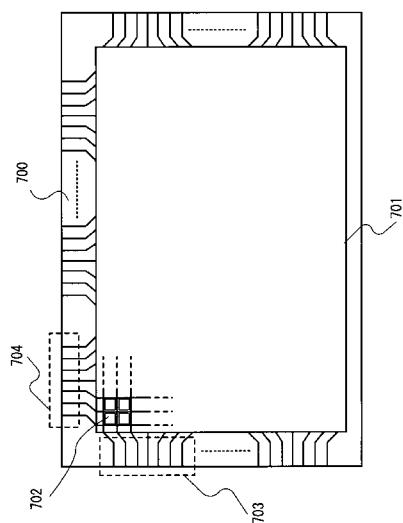

## 【0119】

図10はEL表示パネル構成の一例を示す上面図である。図10は、走査線及び信号線へ入力する信号を、外付けの駆動回路により制御する発光表示パネルの構成を示している。絶縁表面を有する基板700上に画素702をマトリクス上に配列させた画素部701、走査線側入力端子703、信号線側入力端子704が形成されている。画素数は種々の規格に従って設ければ良く、XGAであれば $1024 \times 768 \times 3$ (RGB)、UXGAであれば $1600 \times 1200 \times 3$ (RGB)、フルスペックハイビジョンに対応させるのであれば $1920 \times 1080 \times 3$ (RGB)とすれば良い。

30

## 【0120】

画素702は、走査線側入力端子703から延在する走査線と、信号線側入力端子704から延在する信号線とが交差することで、マトリクス状に配設される。画素702のそれぞれには、スイッチング素子とそれに接続する画素電極が備えられている。スイッチング素子の代表的な一例はTFTであり、TFTのゲート電極側が走査線と、ソース若しくはドレイン側が信号線と接続されることにより、個々の画素を外部から入力する信号によって独立して制御可能としている。

40

## 【0121】

なお、第1の電極を透明材料、第2の電極を金属材料とすれば、基板10を通過させて光を取り出す構造、即ちボトムエミッショントン型となる。また、第1の電極を金属材料、第2の電極を透明材料とすれば、封止基板35を通過させて光を取り出す構造、即ちトップエミッショントン型となる。また、第1の電極および第2の電極を透明材料とすれば、基板10と封止基板35の両方を通過させて光を取り出す構造とすることができます。本発明は、適宜、いずれか一の構造とすればよい。

## 【0122】

以上示したように、本実施の形態では、液滴吐出法を用いた導電膜パターンに対してレーザー光で露光し、現像することによって微細なパターンを実現している。また、液滴吐出

50

法を用いて基板上に直接的に各種のパターンを形成することにより、1辺が1000mmを超える第5世代以降のガラス基板を用いても、EL表示パネルの製造を容易なものとすることができる。

【0123】

また、本実施の形態では、スピンドルコートを行わず、フォトマスクを利用した光露光工程を極力行わない工程を示したが、特に限定されず、一部のパターニングをフォトマスクを利用した光露光工程により行ってもよい。

【0124】

(実施の形態2)

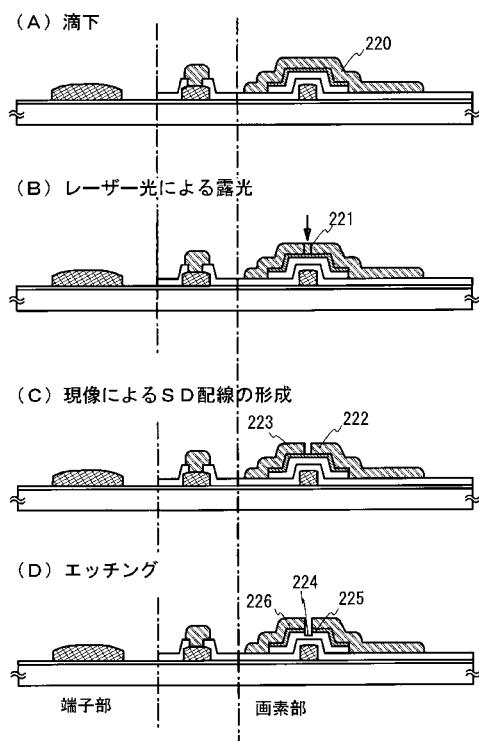

実施の形態1では、ゲート配線をレーザービーム描画装置で露光した例を示したが、ここではソース配線やドレイン配線の形成にレーザービーム描画装置を用いる工程例を図5に示す。

【0125】

なお、実施の形態1とは工程が一部異なるだけであるので、同一工程である説明は簡略化のため省略する。

【0126】

まず、実施の形態1と同様に半導体膜のパターニング工程までを行う。次いで、液滴吐出法により導電膜パターン220を形成する。(図5(A))導電膜パターン220にはポジ型の感光性材料を含ませておく。

【0127】

次いで、図4に示す装置を用いてレーザー光で選択的に露光する。(図5(B))この際、レーザー光照射した部分221は化学反応を起こす。

【0128】

次いで、現像を行ってレーザー光照射した部分221を除去してソース配線またはドレイン配線222、223を形成する。(図5(C))

【0129】

こうして形成されたソース配線またはドレイン配線222、223の間隔は、レーザー光の照射により決定されるため、実施者が自由に設定することができる。ソース配線またはドレイン配線222、223の間隔は、チャネル形成領域の長さ(L)を決定するため、自由に設定することは有用である。

【0130】

次いで、ソース配線またはドレイン配線222、223をマスクとしてn型の半導体膜、および半導体膜の上層部をエッティングして、図5(D)の状態を得る。この段階で、活性層となるチャネル形成領域224、ソース領域226、ドレイン領域225を備えたチャネルエッチ型のTFTが完成する。以降の工程は実施の形態1と同一であるため、詳細な説明は省略する。

【0131】

液滴吐出法を用いてソース配線またはドレイン配線を形成した場合、液だれなどのマージンを考慮すると、ある程度間隔を確保しなければならず、チャネル形成領域の長さ(L)を短くすることが困難であった。本実施の形態で示したようにレーザー光で露光すれば、チャネル形成領域の長さ(L)を短くする、例えば10μm以下とすることが実現できる。

【0132】

また、本実施の形態は実施の形態1と自由に組み合わせることができる。

【0133】

(実施の形態3)

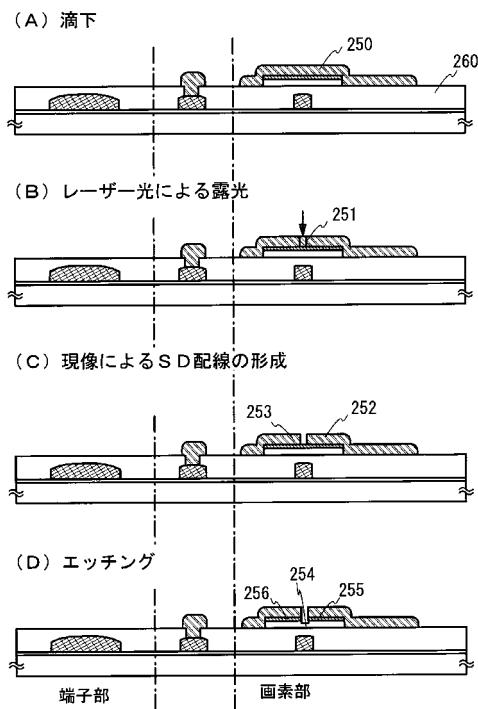

また、他の工程例を図6に示す。図6では、ゲート絶縁膜260として平坦化膜を用いた例を示している。その他の部分は実施の形態2と同一である。

【0134】

ここでは、ゲート電極を形成した後、スパッタ法、CVD法で得られる膜に施す平坦化

10

20

30

40

50

処理、または塗布法によって表面が平坦なゲート絶縁膜 260 を形成している。なお、平坦化処理は、代表的には C M P 処理などである。

【0135】

大面積の画面を有する発光表示装置を形成する場合には、低抵抗なゲート配線を形成することが望ましく、厚さを厚く、例えば  $1 \mu\text{m} \sim 5 \mu\text{m}$  とすればよい。また、配線膜厚を厚くして断面積を増大させた場合には基板表面と厚膜配線表面との間に段差が生じ、カバーレッジ不良の原因となる。このようにゲート配線の厚さを厚くする場合に平坦なゲート絶縁膜 260 は有用である。

【0136】

通常、金属配線が形成された基板の表面は、金属配線がその厚さ分だけ凸状に突き出た構造となるが、本実施の形態では平坦なゲート絶縁膜 260 としており基板の表面は平坦であるため、半導体膜を薄膜化してもカバーレッジ不良なども生じにくい。

【0137】

次いで、実施の形態 1 と同様に半導体膜、n 型の半導体膜を順次、成膜する。そして、マスクを設け、半導体膜と、n 型の半導体膜とを選択的にエッチングして島状の半導体膜、n 型の半導体膜を得る。

【0138】

次いで、実施の形態 2 と同様に、液滴吐出法により導電膜パターン 250 を形成する。

(図 6 (A))

【0139】

次いで、図 4 に示す装置を用いてレーザー光で選択的に露光する。(図 6 (B))

【0140】

次いで、現像を行ってレーザー光照射した部分 251 を除去してソース配線またはドレイン配線 252、253 を形成する。(図 6 (C))

【0141】

次いで、ソース配線またはドレイン配線 252、253 をマスクとして n 型の半導体膜、および半導体膜の上層部をエッチングして、図 6 (D) の状態を得る。この段階で、活性層となるチャネル形成領域 254、ソース領域 256、ドレイン領域 255 を備えたチャネルエッチ型の TFT が完成する。以降の工程は実施の形態 1 と同一であるため、詳細な説明は省略する。

【0142】

また、本実施の形態は実施の形態 1、または実施の形態 2 と自由に組み合わせができる。

【0143】

(実施の形態 4)

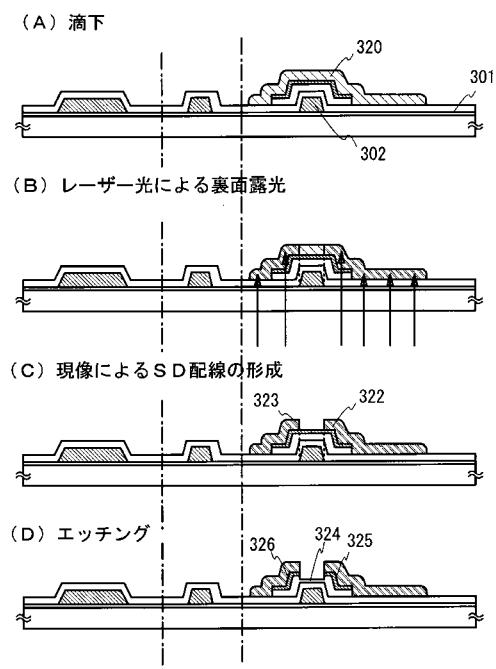

ここでは、ゲート電極をマスクとして、ソース配線またはドレイン配線の形成を裏面露光によって自己整合的に形成する工程例を図 7 に示す。

【0144】

まず、基板上に下地絶縁膜 301 を形成する。下地絶縁膜 301 としては、酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜などの絶縁膜から成る下地膜を形成する。なお、必要でなければ、特に下地絶縁膜を形成しなくてもよい。

【0145】

次いで、下地絶縁膜 301 上に膜厚  $100 \sim 600 \text{ nm}$  の導電膜をスパッタ法で形成する。なお、導電膜は、Ta、W、Ti、Mo、Al、Cu から選ばれた元素、または前記元素を主成分とする合金材料若しくは化合物材料の単層、またはこれらの積層で形成してもよい。また、リン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜を用いてもよい。

【0146】

次いで、フォトマスクを用いてレジストマスクを形成し、ドライエッチング法またはウェットエッチング法を用いてエッチングを行う。このエッチング工程によって、導電膜を

10

20

30

40

50

エッチングして、図 7 ( A ) に示すように、ゲート電極 302 を得る。

【 0147 】

次いで、実施の形態 1 と同様にプラズマ CVD 法やスパッタリング法を用いて、ゲート絶縁膜、半導体膜、n 型の半導体膜を順次、成膜する。次いで、マスクを設け、半導体膜と、n 型の半導体膜とを選択的にエッチングして島状の半導体膜、n 型の半導体膜を得る。

【 0148 】

次いで、実施の形態 2 と同様にして、液滴吐出法により導電膜パターン 320 を形成する。(図 7 ( A )) 導電膜パターン 320 にはネガ型の感光性材料を含ませておく。

【 0149 】

次いで、レーザビーム描画装置を用いてレーザー光で自己整合的に裏面露光する。(図 7 ( B )) この際、導電膜パターンにおいてレーザー光照射した部分は化学反応を起こす。なお、基板は透光性の基板を用い、レーザー光はその基板を通過する波長のものを選択する。また、レーザー光の波長によっては半導体膜や n 型の半導体膜にもレーザー光が照射され、レーザーアニールを行うことができる。

【 0150 】

次いで、現像を行ってレーザー光が照射されなかった部分を除去してソース配線またはドレイン配線 322、323 を形成する。(図 7 ( C ))

【 0151 】

こうして形成されたソース配線またはドレイン配線 322、323 の間隔は、ゲート電極幅により決定される。

【 0152 】

次いで、ソース配線またはドレイン配線 322、323 をマスクとして n 型の半導体膜、および半導体膜の上層部をエッチングして、図 7 ( D ) の状態を得る。この段階で、活性層となるチャネル形成領域 324、ソース領域 326、ドレイン領域 325 を備えたチャネルエッチ型の TFT が完成する。以降の工程は実施の形態 1 と同一であるため、詳細な説明は省略する。

【 0153 】

本発明により、TFT のチャネル形成領域が自己整合的に形成されるため、パターンずれが生じず、個々の TFT のバラツキを低減することができる。また、本発明により、作製工程も簡略なものとすることができます。

【 0154 】

また、本実施の形態は実施の形態 1 、実施の形態 2 、または実施の形態 3 と自由に組み合わせることができる。

【 0155 】

(実施の形態 5 )

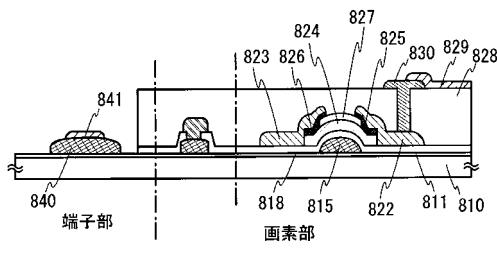

本実施の形態では、チャネルストップ型の TFT をスイッチング素子とするアクティブマトリクス型発光表示装置の作製方法を示す。

【 0156 】

まず、図 8 に示すように、上記実施の形態 1 と同様に基板 810 上に下地膜 811 を形成する。下地膜 811 として光触媒物質 TiO<sub>2</sub> を全体に形成する。

【 0157 】

次いで、所望の領域、本実施の形態では配線を形成する領域の両端の TiO<sub>2</sub> に光触媒活性させる波長を有する光を照射し、照射領域を形成する。光触媒活性させる波長を有する光はレーザー光であってもよく、図 4 の装置を用いて所望の領域へ選択的に照射する。すると照射領域は撥油性を示す。

【 0158 】

インクジェット法を用いて、非照射領域上から又は非照射領域にむかって、溶媒中に導電体が混入したドットを滴下して、ゲート電極 815 として機能する導電膜を形成する。同時に端子部においては端子電極 840 を形成する。

## 【0159】

次いで、ゲート電極を覆ってゲート絶縁膜818を形成する。その後、プラズマCVD法等により半導体膜を形成する。そしてチャネル保護膜827を形成するため、例えば、プラズマCVD法により絶縁膜を形成し、所望の領域に、所望の形状となるようにパターニングする。このとき、ゲート電極をマスクとして基板の裏面から露光することにより、チャネル保護膜827を形成することができる。またチャネル保護膜は、インクジェット法を用いてポリイミド又はポリビニルアルコール等を滴下してもよい。その結果、露光工程を省略することができる。

## 【0160】

その後、プラズマCVD法等により一導電型を有する半導体膜、例えばN型を有する半導体膜を形成する。

## 【0161】

次いで、N型半導体膜上に、インクジェット法によりポリイミドからなるマスクを形成する。該マスクを用いて、半導体膜824、N型を有する半導体膜825、826をパターニングする。その後、マスクを除去するため洗浄する。

## 【0162】

次いで、配線823、822を形成する。配線823、822は、インクジェット法により形成することができる。配線823、822は、いわゆるソース配線、又はドレイン配線として機能する。

## 【0163】

次いで、層間絶縁膜828を形成する。そして、層間絶縁膜に配線822に達するコンタクトホールを形成し、コンタクトホールに電極830を形成する。

## 【0164】

次いで、電極830を介して配線822と電気的に接続する電極829を形成する。同時に端子部において電極841を形成する。電極829、841はインクジェット法により形成することができる。電極829は、発光表示装置において発光素子の陽極または陰極として機能する。電極829として、水系の溶媒中に導電体が混入したドットを用いることができ、特に透明導電体を用いることにより透明導電膜を形成することができる。

## 【0165】

この段階で、図8に示すチャネルトップ型のTFTおよび第1の電極が形成された発光パネル用のTFT基板が完成する。以降の工程は実施の形態1と同一であるため、詳細な説明は省略する。

## 【0166】

本実施の形態において、インクジェット法で得られる配線、または電極は、実施の形態1で示したように、感光材料を含ませた導電膜材料液を用いて吐出した後、レーザー光で露光を行うことによって形成することもできる。また、レジストマスクもレーザー光で露光を行うことによって形成することもできる。

## 【0167】

また、本実施の形態は、実施の形態1乃至4のいずれか一と自由に組み合わせができる。

## 【0168】

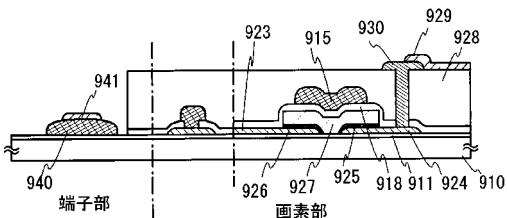

## (実施の形態6)

本実施の形態では、液滴吐出法により作製される順スタガ型のTFTをスイッチング素子とするアクティブマトリクス型発光表示装置の作製方法を示す。

## 【0169】

まず、基板910上に後に形成する液滴吐出法による材料層と密着性を向上させるための下地膜911を形成する。

## 【0170】

次いで、下地膜911上に液滴吐出法により、ソース配線層923及びドレイン配線層924を形成する。

10

20

30

40

50

## 【0171】

また、端子部において端子電極940を形成する。これらの層を形成する導電性材料としては、Ag(銀)、Au(金)、Cu(銅)、W(タンゲステン)、Al(アルミニウム)等の金属の粒子を主成分とした組成物を用いることができる。特に、ソース及びドレイン配線層は、低抵抗化することが好ましいので、比抵抗値を考慮して、金、銀、銅のいずれかの材料を溶媒に溶解又は分散させたものを用いることが好適であり、より好適には、低抵抗な銀、銅を用いるとよい。溶媒は、酢酸ブチル等のエステル類、イソプロピルアルコール等のアルコール類、アセトン等の有機溶剤等に相当する。表面張力と粘度は、溶媒の濃度を調整したり、界面活性剤等を加えたりして適宜調整する。

## 【0172】

次いで、n型の半導体層を全面に形成した後、ソース配線層923及びドレイン配線層924の間にあるn型の半導体層をエッチングして除去する。

## 【0173】

次いで、半導体膜を全面に形成する。半導体膜は、シランやゲルマンに代表される半導体材料ガスを用いて気相成長法やスパッタリング法で作製されるアモルファス半導体膜、或いはセミアモルファス半導体膜で形成する。

## 【0174】

次いで、液滴吐出法により形成したマスクを形成し、半導体膜とn型の半導体層のパターニングを行って、図9に示す半導体層927、n型の半導体層925、926を形成する。半導体層927は、ソース配線層923及びドレイン配線層924の両方に跨るように形成される。また、ソース配線層923及びドレイン配線層924と半導体層927の間にはn型の半導体層925、926が介在している。

## 【0175】

次いで、プラズマCVD法やスパッタリング法を用いて、ゲート絶縁膜を単層又は積層構造で形成する。特に好ましい形態としては、窒化珪素からなる絶縁層、酸化珪素からなる絶縁層、窒化珪素からなる絶縁層の3層の積層体をゲート絶縁膜として構成させる。

## 【0176】

次いで、液滴吐出法により形成したマスクを形成し、ゲート絶縁層918のパターニングを行う。

## 【0177】

次いで、ゲート配線915を液滴吐出法で形成する。ゲート配線915を形成する導電性材料としては、Ag(銀)、Au(金)、Cu(銅)、W(タンゲステン)、Al(アルミニウム)等の金属の粒子を主成分とした組成物を用いることができる。ゲート配線915は端子部まで延在させ、対応する端子部の端子電極940と接して形成される。

## 【0178】

次いで、塗布法による平坦な層間絶縁膜928を形成する。また、層間絶縁膜は、塗布法に限定されず、気相成長法やスパッタリング法により形成された酸化珪素膜などの無機絶縁膜も用いることができる。また、保護膜として窒化珪素膜をPCVD法やスパッタ法で形成した後、塗布法による平坦な絶縁膜を積層してもよい。

## 【0179】

次いで、層間絶縁膜に配線924に達するコンタクトホールを形成し、コンタクトホールに電極930を形成する。

## 【0180】

次いで、電極930を介して配線924と電気的に接続する電極929を形成する。同時に端子部において電極941を形成する。電極929、941はインクジェット法により形成することができる。電極929は、発光表示装置において発光素子の陽極または陰極として機能する。電極929として、水系の溶媒中に導電体が混入したドットを用いることができ、特に透明導電体を用いることにより透明導電膜を形成することができる。

## 【0181】

この段階で、図9に示すトップゲート型(順スタガ型)のTFTおよび第1の電極が形

10

20

30

40

50

成された発光パネル用の TFT 基板が完成する。以降の工程は実施の形態 1 と同一であるため、詳細な説明は省略する。

【 0 1 8 2 】

本実施の形態において、インクジェット法で得られる配線、または電極は、実施の形態 1 で示したように、感光材料を含ませた導電膜材料液を用いて吐出した後、レーザー光で露光を行うことによって形成することもできる。また、レジストマスクもレーザー光で露光を行うことによって形成することもできる。

【 0 1 8 3 】

また、本実施の形態は、実施の形態 1 乃至 4 のいずれか一と自由に組み合わせができる。

【 0 1 8 4 】

(実施の形態 7 )

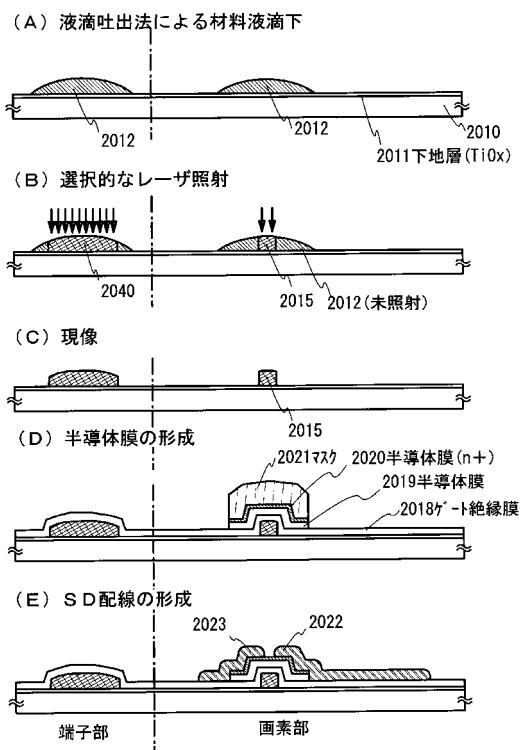

ここではチャネルエッチ型の TFT をスイッチング素子とするアクティブマトリクス型液晶表示装置の作製例を図 17 、図 18 に示す。

【 0 1 8 5 】

実施の形態 1 と同様にして、基板 2010 上に後に形成する液滴吐出法による材料層と密着性を向上させるための下地層 2011 を形成する。

【 0 1 8 6 】

なお、基板 2010 は、バリウムホウケイ酸ガラス、アルミノホウケイ酸ガラス若しくはアルミノシリケートガラスなど、フュージョン法やフロート法で作製される無アルカリガラス基板の他、本作製工程の処理温度に耐えうる耐熱性を有するプラスチック基板等を用いることができる。また、反射型の液晶表示装置とする場合、単結晶シリコンなどの半導体基板、ステンレスなどの金属基板、またはセラミック基板の表面に絶縁層を設けた基板を適用しても良い。

【 0 1 8 7 】

次いで、実施の形態 1 と同様に、液滴吐出法、代表的にはインクジェット法を用いた図 16 に示す装置により導電膜材料液を滴下して導電膜パターン 2012 を形成する。(図 17 ( A ))

【 0 1 8 8 】

次いで、実施の形態 1 と同様に、図 4 に示す装置を用いてレーザー光を選択的に照射して、導電膜パターンの一部を露光させる。(図 17 ( B ))

【 0 1 8 9 】

次いで、エッチャント(または現像液)を用いて現像を行い、余分な部分を除去して、本焼成を行ってゲート電極またはゲート配線となる金属配線 2015 を形成する。(図 17 ( C ))

【 0 1 9 0 】

また、金属配線 2015 と同様に端子部に伸びる配線 2040 も形成する。なお、ここでは図示しないが、保持容量を形成するための容量電極または容量配線も必要であれば形成する。

【 0 1 9 1 】

なお、ポジ型の感光性材料を用いる場合には、除去したい部分にレーザー照射を行って化学反応させ、その部分をエッチャントで溶解させればよい。

【 0 1 9 2 】

また、導電膜材料液を滴下した後、室温乾燥または仮焼成を行ってからレーザー光の照射による露光を行ってもよい。

【 0 1 9 3 】

次いで、プラズマ CVD 法やスパッタリング法を用いて、ゲート絶縁膜 2018 、半導体膜、n 型の半導体膜を順次、成膜する。

【 0 1 9 4 】

ゲート絶縁膜 2018 としては、PCVD 法により得られる酸化珪素、窒化珪素、また

は窒化酸化珪素を主成分とする材料を用いる。また、ゲート絶縁膜 2018 をシリコサン系ポリマーを用いた液滴吐出法により吐出、焼成してアルキル基を含む SiO<sub>x</sub> 膜としてもよい。

#### 【0195】

半導体膜は、シランやゲルマンに代表される半導体材料ガスを用いて気相成長法やスパッタリング法や熱 CVD 法で作製されるアモルファス半導体膜、或いはセミアモルファス半導体膜で形成する。

#### 【0196】

n 型の半導体膜は、シランガスとフォスフィンガスを用いた PCVD 法で形成すれば良く、アモルファス半導体膜、或いはセミアモルファス半導体膜で形成することができる。n 型の半導体膜 2020 を設けると、半導体膜と電極（後の工程で形成される電極）とのコンタクト抵抗が低くなり好ましいが、必要に応じて設ければよい。

#### 【0197】

次いで、マスク 2021 を設け、半導体膜と、n 型の半導体膜とを選択的にエッチングして島状の半導体膜 2019 、n 型の半導体膜 2020 を得る。（図 17 (D)）マスク 2021 の形成方法は、液滴吐出法や印刷法（凸版、平板、凹版、スクリーンなど）を用いて形成する。

#### 【0198】

次いで、マスク 2021 を除去した後、液滴吐出法により導電性材料（Ag（銀）、Au（金）、Cu（銅）、W（タンゲステン）、Al（アルミニウム）等）を含む組成物を選択的に吐出して、ソース配線またはドレイン配線 2022 、2023 を形成する。なお、同様に、端子部において接続配線（図示しない）も形成する。（図 17 (E)）

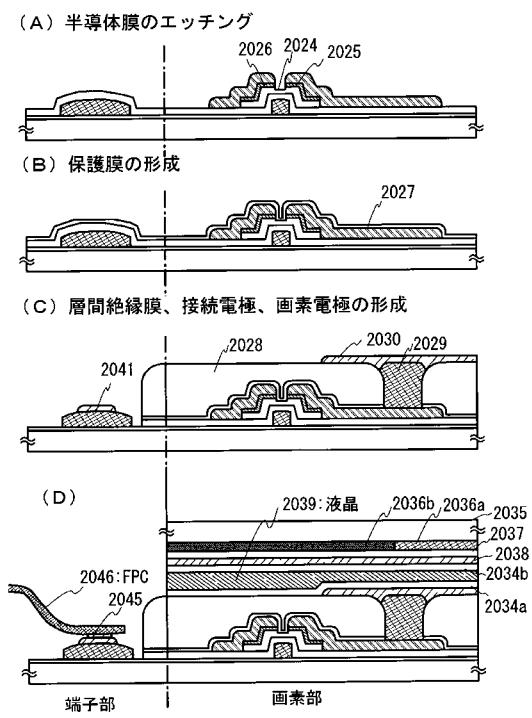

#### 【0199】

次いで、ソース配線またはドレイン配線 2022 、2023 をマスクとして n 型の半導体膜、および半導体膜の上層部をエッチングして、図 18 (A) の状態を得る。この段階で、活性層となるチャネル形成領域 2024 、ソース領域 2026 、ドレイン領域 2025 を備えたチャネルエッチ型の TFT が完成する。

#### 【0200】

次いで、チャネル形成領域 2024 を不純物汚染から防ぐための保護膜 2027 を形成する。（図 18 (B)）保護膜 2027 としては、スパッタ法、または PCVD 法により得られる窒化珪素、または窒化酸化珪素を主成分とする材料を用いる。ここでは保護膜を形成した例を示したが、特に必要でなければ設ける必要はない。

#### 【0201】

次いで、液滴吐出法により層間絶縁膜 2028 を選択的に形成する。層間絶縁膜 2028 は、エポキシ樹脂、アクリル樹脂、フェノール樹脂、ノボラック樹脂、アクリル樹脂、メラミン樹脂、ウレタン樹脂等の樹脂材料を用いる。層間絶縁膜 2028 の形成方法は、特に液滴吐出法に限定されず、塗布法や PCVD 法などを用いて全面に形成してもよい。

#### 【0202】

次いで、層間絶縁膜 2028 をマスクとして保護膜をエッチングし、ソース配線またはドレイン配線 2022 、2023 上の一部に導電性部材からなる凸状部（ピラー）2029 を形成する。凸状部（ピラー）2029 は、導電性材料（Ag（銀）、Au（金）、Cu（銅）、W（タンゲステン）、Al（アルミニウム）等）を含む組成物の吐出と焼成を繰り返すことによって積み重ねてもよい。また、保護膜をエッチングした後、端子部においては、さらに層間絶縁膜をマスクとしてエッチングを行って、ゲート絶縁膜も選択的に除去する。

#### 【0203】

次いで、層間絶縁膜 2028 上に凸状部（ピラー）29 と接する画素電極 2030 を形成する。（図 18 (C)）なお、同様に配線 2040 と接する端子電極 2041 も形成する。透過型の液晶表示パネルを作製する場合には、液滴吐出法または印刷法によりインジウム錫酸化物（ITO）、酸化珪素を含むインジウム錫酸化物（ITSO）、酸化亜鉛

10

20

30

40

50

(ZnO)、酸化スズ(SnO<sub>2</sub>)などを含む組成物からなる所定のパターンを形成し、焼成して画素電極2030および端子電極2041を形成しても良い。

#### 【0204】

また、反射型の液晶表示パネルを作製する場合には、画素電極2030および端子電極2041を液滴吐出法によりAg(銀)、Au(金)、Cu(銅)、W(タンゲステン)、Al(アルミニウム)等の金属の粒子を主成分とした組成物を用いて形成することができる。他の方法としては、スパッタリング法により透明導電膜、若しくは光反射性の導電膜を形成して、液滴吐出法によりマスクパターンを形成し、エッチングを組み合わせて画素電極を形成しても良い。

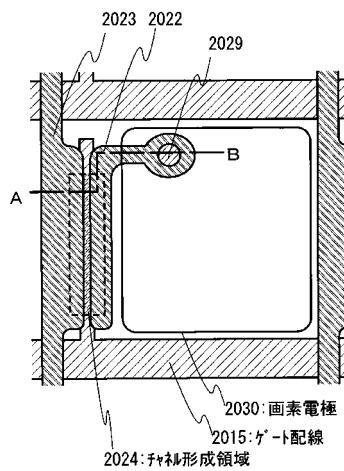

#### 【0205】

図18(C)の段階での画素の上面図の一例を図19に示す。図19中において、鎖線A-B断面が図18(C)の断面図と対応している。なお、対応する部位には同じ符号を用いている。

#### 【0206】

以上の工程により、基板2010上にボトムゲート型(逆スタガ型ともいう。)のTFTおよび画素電極が形成された液晶表示パネル用のTFT基板が完成する。

#### 【0207】

次いで、画素電極2030を覆うように、配向膜2034aを形成する。なお、配向膜2034aは、液滴吐出法やスクリーン印刷法やオフセット印刷法を用いればよい。その後、配向膜2034aの表面にラビング処理を行う。

#### 【0208】

そして、対向基板2035には、着色層2036a、遮光層(ブラックマトリクス)2036b、及びオーバーコート層2037からなるカラーフィルタを設け、さらに透明電極からなる対向電極2038と、その上に配向膜2034bを形成する。そして、閉パターンであるシール材(図示しない)を液滴吐出法により画素部と重なる領域を囲むように形成する。ここでは液晶2039を滴下するため、閉パターンのシール材を描画する例を示すが、開口部を有するシールパターンを設け、TFT基板を貼りあわせた後に毛細管現象を用いて液晶を注入するディップ式(汲み上げ式)を用いてもよい。また、カラーフィルタも液滴吐出法により形成することができる。

#### 【0209】

次いで、気泡が入らないように減圧下で液晶の滴下を行い、両方の基板を貼り合わせる。閉ループのシールパターン内に液晶を1回若しくは複数回滴下する。液晶の配向モードとしては、液晶分子の配列が光の入射から出射に向かって90°ツイスト配向したTNモードを用いる場合が多い。TNモードの液晶表示装置を作製する場合には、基板のラビング方向が直交するように貼り合わせる。

#### 【0210】

なお、一対の基板間隔は、球状のスペーサを散布したり、樹脂からなる柱状のスペーサを形成したり、シール材にフィラーを含ませることによって維持すればよい。上記柱状のスペーサは、アクリル、ポリイミド、ポリイミドアミド、エポキシの少なくとも1つを主成分とする有機樹脂材料、もしくは酸化珪素、窒化珪素、酸化窒化珪素のいずれか一種の材料、或いはこれらの積層膜からなる無機材料であることを特徴としている。

#### 【0211】

次いで、必要でない基板の分断を行う。多面取りの場合、それぞれのパネルを分断する。また、1面取りの場合、予めカットされている対向基板を貼り合わせることによって、分断工程を省略することもできる。

#### 【0212】

そして、異方性導電体層2045を介し、公知の技術を用いてFPC2046を貼りつける。以上の工程で液晶モジュールが完成する。(図18(D))また、必要があれば光学フィルムを貼り付ける。透過型の液晶表示装置とする場合、偏光板は、アクティブマトリクス基板と対向基板の両方に貼り付ける。

10

20

30

40

50

## 【0213】

以上示したように、本実施の形態では、液滴吐出法を用いた導電膜パターンに対してレーザー光で露光し、現像することによって微細なパターンを実現している。また、液滴吐出法を用いて基板上に直接的に各種のパターンを形成することにより、1辺が1000mmを超える第5世代以降のガラス基板を用いても、液晶表示パネルの製造を容易なものとすることができる。

## 【0214】

また、本実施の形態では、スピンドルコートを行わず、フォトマスクを利用した光露光工程を極力行わない工程を示したが、特に限定されず、一部のパターニングをフォトマスクを利用した光露光工程により行ってもよい。

10

## 【0215】

また、本実施の形態は実施の形態1と組み合わせることができる。

## 【0216】

## (実施の形態8)

実施の形態7では、ゲート配線をレーザービーム描画装置で露光した例を示したが、ここではソース配線やドレイン配線の形成にレーザービーム描画装置を用いる工程例を図20に示す。

## 【0217】

なお、実施の形態7とは工程が一部異なるだけであるので、同一工程である説明は簡略化のため省略する。

20

## 【0218】

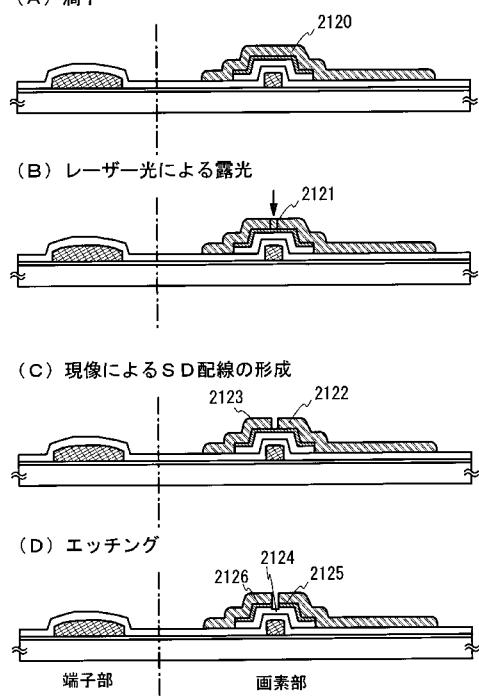

まず、実施の形態7と同様に半導体膜のパターニング工程までを行う。次いで、液滴吐出法により導電膜パターン2120を形成する。(図20(A))導電膜パターン2120にはポジ型の感光性材料を含ませておく。

## 【0219】

次いで、図4に示す装置を用いてレーザー光で選択的に露光する。(図20(B))この際、レーザー光照射した部分2121は化学反応を起こす。

## 【0220】

次いで、現像を行ってレーザー光照射した部分2121を除去してソース配線またはドレイン配線2122、2123を形成する。(図20(C))

30

## 【0221】

こうして形成されたソース配線またはドレイン配線2122、2123の間隔は、レーザー光の照射により決定されるため、実施者が自由に設定することができる。ソース配線またはドレイン配線2122、2123の間隔は、チャネル形成領域の長さ(L)を決定するため、自由に設定することは有用である。

## 【0222】

次いで、ソース配線またはドレイン配線2122、2123をマスクとしてn型の半導体膜、および半導体膜の上層部をエッチングして、図20(D)の状態を得る。この段階で、活性層となるチャネル形成領域2124、ソース領域2126、ドレイン領域2125を備えたチャネルエッチ型のTFTが完成する。以降の工程は実施の形態7と同一であるため、詳細な説明は省略する。

40

## 【0223】

液滴吐出法を用いてソース配線またはドレイン配線を形成した場合、液だれなどのマージンを考慮すると、ある程度間隔を確保しなければならず、チャネル形成領域の長さ(L)を短くすることが困難であった。本実施の形態で示したようにレーザー光で露光すれば、チャネル形成領域の長さ(L)を短くする、例えば10μm以下とすることが実現できる。

## 【0224】

また、本実施の形態は実施の形態1と実施の形態7と自由に組み合わせることができる。

50

## 【0225】

(実施の形態9)

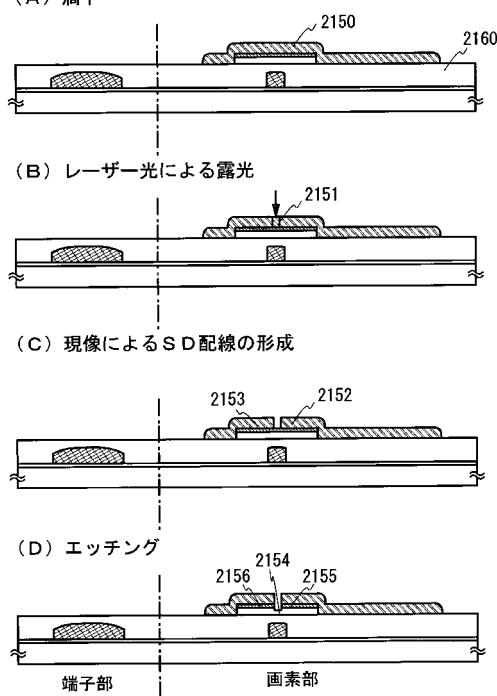

また、他の工程例を図21に示す。図21では、ゲート絶縁膜2160として平坦化膜を用いた例を示している。その他の部分は実施の形態8と同一である。

## 【0226】

ここでは、ゲート電極を形成した後、スパッタ法、CVD法で得られる膜に施す平坦化処理、または塗布法によって表面が平坦なゲート絶縁膜2160を形成している。なお、平坦化処理は、代表的にはCMP処理などである。

## 【0227】

大面積の画面を有する液晶表示装置を形成する場合には、低抵抗なゲート配線を形成することが望ましく、厚さを厚く、例えば1μm～5μmとすればよい。また、配線膜厚を厚くして断面積を増大させた場合には基板表面と厚膜配線表面との間に段差が生じ、液晶の配向不良の原因となる。このようにゲート配線の厚さを厚くする場合に平坦なゲート絶縁膜2160は有用である。

## 【0228】

通常、金属配線が形成された基板の表面は、金属配線がその厚さ分だけ凸状に突き出た構造となるが、本実施の形態では平坦なゲート絶縁膜2160としており基板の表面は平坦であるため、半導体膜を薄膜化してもカバレッジ不良なども生じにくい。

## 【0229】

次いで、実施の形態1と同様に半導体膜、n型の半導体膜を順次、成膜する。そして、マスクを設け、半導体膜と、n型の半導体膜とを選択的にエッチングして島状の半導体膜、n型の半導体膜を得る。

## 【0230】

次いで、実施の形態8と同様に、液滴吐出法により導電膜パターン2150を形成する。(図21(A))

## 【0231】

次いで、図4に示す装置を用いてレーザー光で選択的に露光する。(図21(B))

## 【0232】

次いで、現像を行ってレーザー光照射した部分2151を除去してソース配線またはドレイン配線2152、2153を形成する。(図21(C))

## 【0233】

次いで、ソース配線またはドレイン配線2152、2153をマスクとしてn型の半導体膜、および半導体膜の上層部をエッチングして、図21(D)の状態を得る。この段階で、活性層となるチャネル形成領域2154、ソース領域2156、ドレイン領域2155を備えたチャネルエッチ型のTFTが完成する。以降の工程は実施の形態7と同一であるため、詳細な説明は省略する。

## 【0234】

また、本実施の形態は実施の形態1、実施の形態7、または実施の形態8と自由に組み合わせることができる。

## 【0235】

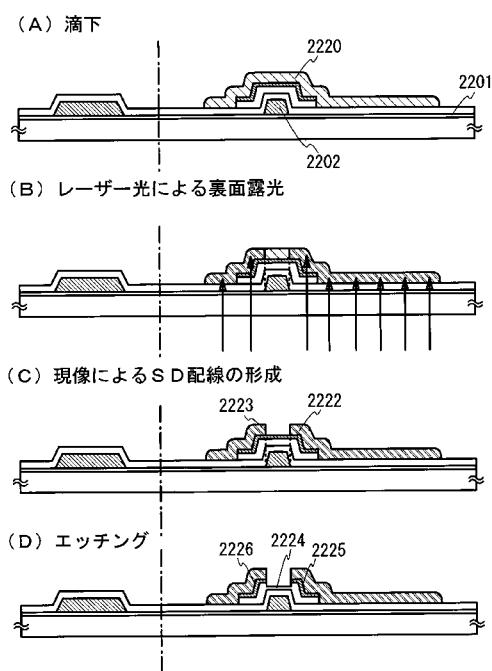

(実施の形態10)

ここでは、ゲート電極をマスクとして、ソース配線またはドレイン配線の形成を裏面露光によって自己整合的に形成する工程例を図22に示す。

## 【0236】

まず、基板上に下地絶縁膜2201を形成する。下地絶縁膜2201としては、酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜などの絶縁膜から成る下地膜を形成する。なお、必要でなければ、特に下地絶縁膜を形成しなくてもよい。

## 【0237】

次いで、下地絶縁膜2201上に膜厚100～600nmの導電膜をスパッタ法で形成する。なお、導電膜は、Ta、W、Ti、Mo、Al、Cuから選ばれた元素、または前

10

20

30

40

50

記元素を主成分とする合金材料若しくは化合物材料の単層、またはこれらの積層で形成してもよい。また、リン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜を用いてもよい。

#### 【0238】

次いで、フォトマスクを用いてレジストマスクを形成し、ドライエッチング法またはウェットエッチング法を用いてエッチングを行う。このエッチング工程によって、導電膜をエッチングして、図22(A)に示すように、ゲート電極2202を得る。

#### 【0239】

次いで、実施の形態7と同様にプラズマCVD法やスパッタリング法を用いて、ゲート絶縁膜、半導体膜、n型の半導体膜を順次、成膜する。次いで、マスクを設け、半導体膜と、n型の半導体膜とを選択的にエッチングして島状の半導体膜、n型の半導体膜を得る。

#### 【0240】

次いで、実施の形態8と同様にして、液滴吐出法により導電膜パターン2220を形成する。(図22(A))導電膜パターン2220にはネガ型の感光性材料を含ませておく。

#### 【0241】

次いで、レーザビーム描画装置を用いてレーザー光で自己整合的に裏面露光する。(図22(B))この際、導電膜パターンにおいてレーザー光照射した部分は化学反応を起こす。なお、基板は透光性の基板を用い、レーザー光はその基板を通過する波長のものを選択する。

#### 【0242】

次いで、現像を行ってレーザー光が照射されなかった部分を除去してソース配線またはドレイン配線2222、2223を形成する。(図22(C))

#### 【0243】

こうして形成されたソース配線またはドレイン配線2222、2223の間隔は、ゲート電極幅により決定される。

#### 【0244】

次いで、ソース配線またはドレイン配線2222、2223をマスクとしてn型の半導体膜、および半導体膜の上層部をエッチングして、図22(D)の状態を得る。この段階で、活性層となるチャネル形成領域2224、ソース領域2226、ドレイン領域2225を備えたチャネルエッチ型のTFTが完成する。以降の工程は実施の形態7と同一であるため、詳細な説明は省略する。

#### 【0245】

本発明により、TFTのチャネル形成領域が自己整合的に形成されるため、パターンずれが生じず、個々のTFTのバラツキを低減することができる。また、本発明により、作製工程も簡略なものとすることができます。

#### 【0246】

また、本実施の形態は実施の形態1、実施の形態7、実施の形態8、または実施の形態9と自由に組み合わせることができる。

#### 【0247】

(実施の形態11)

本実施の形態では、チャネルトップ型のTFTをスイッチング素子とするアクティブマトリクス型液晶表示装置の作製方法を示す。

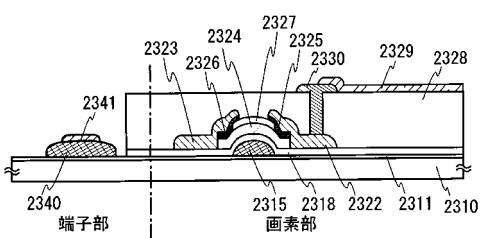

#### 【0248】

まず、図23に示すように、上記実施の形態7と同様に基板2310上に下地膜2311を形成する。下地膜2311として光触媒物質TiO<sub>2</sub>を全体に形成する。

#### 【0249】

次いで、所望の領域、本実施の形態では配線を形成する領域の両端のTiO<sub>2</sub>に光触媒活性させる波長を有する光を照射し、照射領域を形成する。光触媒活性させる波長を有す

10

20

30

40

50

る光はレーザー光であってもよく、図4の装置を用いて所望の領域へ選択的に照射する。すると照射領域は撥油性を示す。

【0250】

インクジェット法を用いて、非照射領域上から又は非照射領域にむかって、溶媒中に導電体が混入したドットを滴下して、ゲート電極2315として機能する導電膜を形成する。同時に端子部においては端子電極2340を形成する。

【0251】

次いで、ゲート電極を覆ってゲート絶縁膜2318を形成する。その後、プラズマCVD法等により半導体膜を形成する。そしてチャネル保護膜2327を形成するため、例えば、プラズマCVD法により絶縁膜を形成し、所望の領域に、所望の形状となるようにパターニングする。このとき、ゲート電極をマスクとして基板の裏面から露光することにより、チャネル保護膜2327を形成することができる。またチャネル保護膜は、インクジェット法を用いてポリイミド又はポリビニルアルコール等を滴下してもよい。その結果、露光工程を省略することができる。

【0252】

その後、プラズマCVD法等により一導電型を有する半導体膜、例えばN型を有する半導体膜を形成する。

【0253】

次いで、N型半導体膜上に、インクジェット法によりポリイミドからなるマスクを形成する。該マスクを用いて、半導体膜2324、N型を有する半導体膜2325、2326をパターニングする。その後、マスクを除去するため洗浄する。

【0254】

次いで、配線2323、2322を形成する。配線2323、2322は、インクジェット法により形成することができる。配線2323、2322は、いわゆるソース配線、又はドレイン配線として機能する。

【0255】

次いで、層間絶縁膜2328を形成する。そして、層間絶縁膜に配線2322に達するコンタクトホールを形成し、コンタクトホールに電極2330を形成する。

【0256】

次いで、電極2330を介して配線2322と電気的に接続する電極2329を形成する。同時に端子部において電極2341を形成する。電極2329、2341はインクジェット法により形成することができる。電極2329は、液晶表示装置において画素電極として機能する。電極2329として、水系の溶媒中に導電体が混入したドットを用いることができ、特に透明導電体を用いることにより透明導電膜を形成することができる。

【0257】

この段階で、図23に示すチャネルトップ型のTFTおよび画素電極が形成された液晶表示パネル用のTFT基板が完成する。以降の工程は実施の形態7と同一であるため、詳細な説明は省略する。

【0258】

本実施の形態において、インクジェット法で得られる配線、または電極は、実施の形態7で示したように、感光材料を含ませた導電膜材料液を用いて吐出した後、レーザー光で露光を行うことによって形成することもできる。また、レジストマスクもレーザー光で露光を行うことによって形成することもできる。

【0259】

また、本実施の形態は、実施の形態1、実施の形態7乃至11のいずれか一と自由に組み合わせることができる。

【0260】

(実施の形態12)

本実施の形態では、液滴吐出法により作製される順スタガ型のTFTをスイッチング素子とするアクティブマトリクス型液晶表示装置の作製方法を図24に示す。

10

20

30

40

50

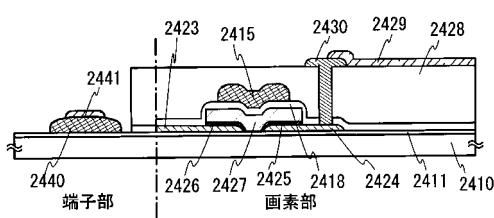

## 【0261】

まず、基板2410上に後に形成する液滴吐出法による材料層と密着性を向上させるための下地膜2411を形成する。

## 【0262】

次いで、下地膜2411上に液滴吐出法により、ソース配線層2423及びドレイン配線層2424を形成する。

## 【0263】

また、端子部において端子電極2440を形成する。これらの層を形成する導電性材料としては、Ag(銀)、Au(金)、Cu(銅)、W(タンゲステン)、Al(アルミニウム)等の金属の粒子を主成分とした組成物を用いることができる。特に、ソース及びドレイン配線層は、低抵抗化することが好ましいので、比抵抗値を考慮して、金、銀、銅のいずれかの材料を溶媒に溶解又は分散させたものを用いることが好適であり、より好適には、低抵抗な銀、銅を用いるとよい。溶媒は、酢酸ブチル等のエステル類、イソプロピルアルコール等のアルコール類、アセトン等の有機溶剤等に相当する。表面張力と粘度は、溶媒の濃度を調整したり、界面活性剤等を加えたりして適宜調整する。

10

## 【0264】

次いで、n型の半導体層を全面に形成した後、ソース配線層2423及びドレイン配線層2424の間にあるn型の半導体層をエッチングして除去する。

## 【0265】

次いで、半導体膜を全面に形成する。半導体膜は、シランやゲルマンに代表される半導体材料ガスを用いて気相成長法やスパッタリング法で作製されるアモルファス半導体膜、或いはセミアモルファス半導体膜で形成する。

20

## 【0266】

次いで、液滴吐出法により形成したマスクを形成し、半導体膜とn型の半導体層のパターニングを行って、図24に示す半導体層2427、n型の半導体層2425、2426を形成する。半導体層2427は、ソース配線層2423及びドレイン配線層2424の両方に跨るように形成される。また、ソース配線層2423及びドレイン配線層2424と半導体層2427の間にはn型の半導体層2425、2426が介在している。

## 【0267】

次いで、プラズマCVD法やスパッタリング法を用いて、ゲート絶縁膜を単層又は積層構造で形成する。特に好ましい形態としては、窒化珪素からなる絶縁層、酸化珪素からなる絶縁層、窒化珪素からなる絶縁層の3層の積層体をゲート絶縁膜として構成させる。

30

## 【0268】

次いで、液滴吐出法により形成したマスクを形成し、ゲート絶縁層2418のパターニングを行う。

## 【0269】

次いで、ゲート配線2415を液滴吐出法で形成する。ゲート配線2415を形成する導電性材料としては、Ag(銀)、Au(金)、Cu(銅)、W(タンゲステン)、Al(アルミニウム)等の金属の粒子を主成分とした組成物を用いることができる。ゲート配線2415は端子部まで延在させ、対応する端子部の端子電極2440と接して形成される。

40

## 【0270】

次いで、塗布法による平坦な層間絶縁膜2428を形成する。また、層間絶縁膜は、塗布法に限定されず、気相成長法やスパッタリング法により形成された酸化珪素膜などの無機絶縁膜も用いることができる。また、保護膜として窒化珪素膜をPCVD法やスパッタ法で形成した後、塗布法による平坦な絶縁膜を積層してもよい。

## 【0271】

次いで、層間絶縁膜にドレイン配線層2424に達するコンタクトホールを形成し、コンタクトホールに電極2430を形成する。

## 【0272】

50

次いで、電極 2430 を介してドレイン配線層 2424 と電気的に接続する電極 2429 を形成する。同時に端子部において電極 2441 を形成する。電極 2429、2441 はインクジェット法により形成することができる。電極 2429 は、液晶表示装置において画素電極として機能する。電極 2429 として、水系の溶媒中に導電体が混入したドットを用いることができ、特に透明導電体を用いることにより透明導電膜を形成することができる。

#### 【0273】

この段階で、図 24 に示すトップゲート型（順スタガ型）の TFT および画素電極が形成された液晶表示パネル用の TFT 基板が完成する。以降の工程は実施の形態 7 と同一であるため、詳細な説明は省略する。

10

#### 【0274】

本実施の形態において、インクジェット法で得られる配線、または電極は、実施の形態 7 で示したように、感光材料を含ませた導電膜材料液を用いて吐出した後、レーザー光で露光を行うことによって形成することもできる。また、レジストマスクもレーザー光で露光を行うことによって形成することもできる。

#### 【0275】

また、本実施の形態は、実施の形態 1、実施の形態 7 乃至 10 のいずれか一と自由に組み合わせることができる。

#### 【0276】

以上の構成でなる本発明について、以下に示す実施例でもってさらに詳細な説明を行うこととする。

20

#### 【実施例 1】

#### 【0277】

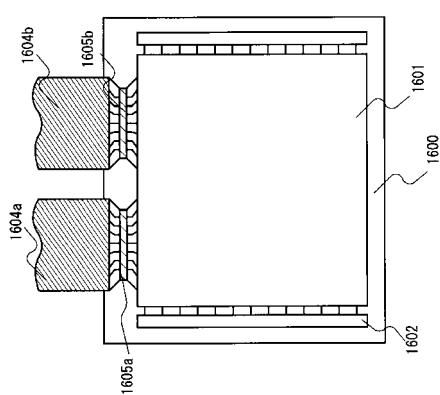

本実施例は、最良の形態によって作製される EL 表示パネルに駆動用のドライバ回路を実装する例について説明する。

#### 【0278】

まず、COG 方式を採用した表示装置について、図 11 を用いて説明する。基板 1600 上には、文字や画像などの情報を表示する画素部 1601、走査側の駆動回路 1602 が設けられる。複数の駆動回路が設けられた基板を、矩形状に分断し、分断後の駆動回路（以下ドライバ IC と表記）1605a、1605b は、基板 1600 上に実装される。図 11 は複数のドライバ IC 1605a、1605b、該ドライバ IC 1605a、1605b の先にテープ 1604 を実装する形態を示す。また、分割する大きさを画素部の信号線側の辺の長さとほぼ同じにし、単数のドライバ IC に、該ドライバ IC の先にテープを実装してもよい。

30

#### 【0279】

また、TAB 方式を採用してもよく、その場合は、複数のテープを貼り付けて、該テープにドライバ IC を実装すればよい。COG 方式の場合と同様に、単数のテープに単数のドライバ IC を実装してもよく、この場合には、強度の問題から、ドライバ IC を固定する金属片等と一緒に貼り付けるとよい。

#### 【0280】

これらの EL 表示パネルに実装されるドライバ IC は、生産性を向上させる観点から、一辺が 300 mm から 1000 mm 以上の矩形状の基板上に複数個作り込むとよい。

40

#### 【0281】

つまり、基板上に駆動回路部と入出力端子を一つのユニットとする回路パターンを複数個形成し、最後に分割して取り出せばよい。ドライバ IC の長辺の長さは、画素部の一辺の長さや画素ピッチを考慮して、長辺が 15 ~ 80 mm、短辺が 1 ~ 6 mm の矩形状に形成してもよいし、画素領域の一辺、又は画素部の一辺と各駆動回路の一辺とを足した長さに形成してもよい。

#### 【0282】

ドライバ IC の IC チップに対する外形寸法の優位性は長辺の長さにあり、長辺が 15

50

~80mmで形成されたドライバICを用いると、画素部に対応して実装するのに必要な数がICチップを用いる場合よりも少なくて済み、製造上の歩留まりを向上させることができる。また、ガラス基板上にドライバICを形成すると、母体として用いる基板の形状に限定されないので生産性を損なうことがない。これは、円形のシリコンウェハからICチップを取り出す場合と比較すると、大きな優位点である。

#### 【0283】

図11において、画素領域1601の外側の領域には、駆動回路が形成されたドライバIC1605a、1605bが実装される。これらのドライバIC1605a、1605bは、信号線側の駆動回路である。RGBフルカラーに対応した画素領域を形成するためには、XGAクラスで信号線の本数が3072本必要であり、UXGAクラスでは4800本が必要となる。このような本数で形成された信号線は、画素領域1601の端部で数プロック毎に区分して引出線を形成し、ドライバIC1605a、1605bの出力端子のピッチに合わせて集められる。

#### 【0284】

ドライバICは、基板上に形成された結晶質半導体により形成されることが好適であり、該結晶質半導体は連続発光のレーザ光を照射することで形成されることが好適である。従って、当該レーザ光を発生させる発振器としては、連続発光の固体レーザ又は気体レーザを用いる。連続発光のレーザを用いると、結晶欠陥が少なく、大粒径の多結晶半導体層を用いて、トランジスタを作成することが可能となる。また移動度や応答速度が良好なために高速駆動が可能で、従来よりも素子の動作周波数を向上させることができ、特性バラツキが少ないために高い信頼性を得ることができる。なお、さらなる動作周波数の向上を目的として、トランジスタのチャネル長方向とレーザ光の走査方向と一致させるとよい。これは、連続発光レーザによるレーザ結晶化工程では、トランジスタのチャネル長方向とレーザ光の基板に対する走査方向とが概ね並行（好ましくは-30°～30°）であるときに、最も高い移動度が得られるためである。なおチャネル長方向とは、チャネル形成領域において、電流が流れる方向、換言すると電荷が移動する方向と一致する。このように作製したトランジスタは、結晶粒がチャネル方向に延在する多結晶半導体層によって構成される活性層を有し、このことは結晶粒界が概ねチャネル方向に沿って形成されていることを意味する。

#### 【0285】

レーザ結晶化を行うには、レーザ光の大幅な絞り込みを行うことが好ましく、そのビームスポットの幅は、ドライバICの短辺の同じ幅の1～3mm程度とすることがよい。また、被照射体に対して、十分に且つ効率的なエネルギー密度を確保するために、レーザ光の照射領域は、線状であることが好ましい。但し、ここでいう線状とは、厳密な意味で線を意味しているのではなく、アスペクト比の大きい長方形もしくは長楕円形を意味する。例えば、アスペクト比が2以上（好ましくは10～10000）のものを指す。このように、レーザ光のビームスポットの幅をドライバICの短辺と同じ長さとすることで、生産性を向上させた表示装置の作製方法を提供することができる。

#### 【0286】

図11では、走査線駆動回路は画素部と共に一体形成し、信号線駆動回路としてドライバICを実装した形態を示した。しかしながら、本発明はこの形態に限定されず、走査線駆動回路及び信号線駆動回路の両方として、ドライバICを実装してもよい。その場合には、走査線側と信号線側で用いるドライバICの仕様を異なるものにするとよい。

#### 【0287】

画素領域1601は、信号線と走査線が交差してマトリクスを形成し、各交差部に対応してトランジスタが配置される。本発明は、画素領域1601に配置されるトランジスタとして、非晶質半導体又はセミアモルファス半導体をチャネル部としたTFTを用いることを特徴とする。非晶質半導体は、プラズマCVD法やスパッタリング法等の方法により形成する。セミアモルファス半導体は、プラズマCVD法で300以下の温度で形成することが可能であり、例えば、外寸550×650mmの無アルカリガラス基板であって

10

20

30

40

50

も、トランジスタを形成するのに必要な膜厚を短時間で形成するという特徴を有する。このような製造技術の特徴は、大画面の表示装置を作製する上で有効である。また、セミアモルファス TFT は、S A S でチャネル形成領域を構成することにより  $2 \sim 10 \text{ cm}^2 / \text{V} \cdot \text{sec}$  の電界効果移動度を得ることができる。従って、この TFT を画素のスイッチング用素子や、走査線側の駆動回路を構成する素子として用いることができる。従って、システムオンパネル化を実現した E L 表示パネルを作製することができる。

#### 【0288】

なお、図 11 では、半導体層を S A S で形成した TFT を用いることにより、走査線側駆動回路も基板上に一体形成することを前提として示している。半導体層を A S で形成した TFT を用いる場合には、走査線側駆動回路及び信号線側駆動回路の両方をドライバ IC を実装してもよい。

#### 【0289】

その場合には、走査線側と信号線側で用いるドライバ IC の仕様を異なるものにすることが好適である。例えば、走査線側のドライバ IC を構成するトランジスタには 30 V 程度の耐圧が要求されるものの、駆動周波数は 100 kHz 以下であり、比較的高速動作は要求されない。従って、走査線側のドライバを構成するトランジスタのチャネル長 (L) は十分大きく設定することが好適である。一方、信号線側のドライバ IC のトランジスタには、12 V 程度の耐圧があれば十分であるが、駆動周波数は 3 V にて 65 MHz 程度であり、高速動作が要求される。そのため、ドライバを構成するトランジスタのチャネル長などはミクロルールで設定することが好適である。

#### 【0290】

ドライバ IC の実装方法は、特に限定されるものではなく、公知の COG 方法やワイヤボンディング方法、或いは TAB 方法を用いることができる。

#### 【0291】

ドライバ IC の厚さは、対向基板と同じ厚さとすることで、両者の間の高さはほぼ同じものとなり、表示装置全体としての薄型化に寄与する。また、それぞれの基板を同じ材質のもので作製することにより、この表示装置に温度変化が生じても熱応力が発生することなく、TFT で作製された回路の特性を損なうことはない。その他にも、本実施例で示すように IC チップよりも長尺のドライバ IC で駆動回路を実装することにより、1 つの画素領域に対して、実装されるドライバ IC の個数を減らすことができる。

#### 【0292】

以上のようにして、EL 表示パネルに駆動回路を組み入れることができる。

#### 【0293】

また、本実施例は、実施の形態 1 乃至 6 のいずれか一と自由に組み合わせることができる。

#### 【実施例 2】

#### 【0294】

本実施例では、薄膜トランジスタを有する発光装置について図 12 に説明する。

#### 【0295】

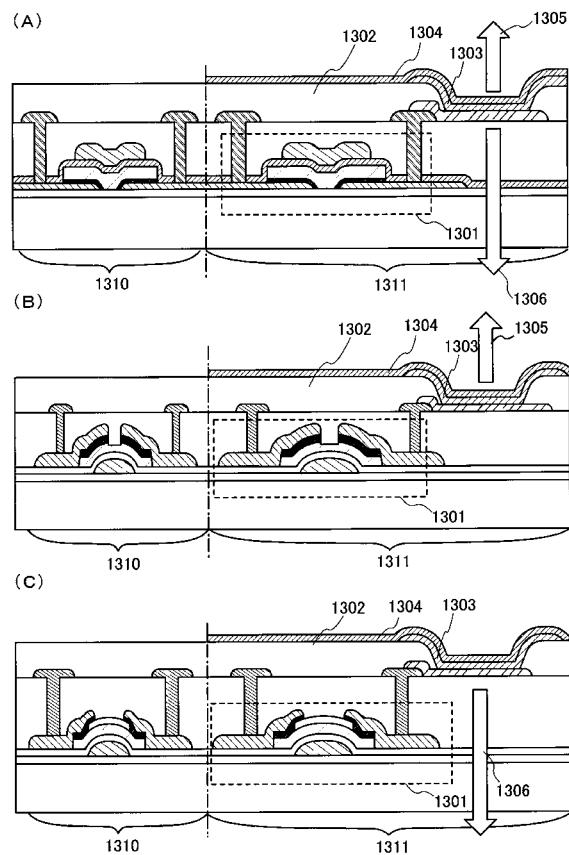

図 12 (A) に示すように、駆動回路部 1310 及び画素部 1311 に、セミアモルファスシリコン膜を活性層とするトップゲート型の N チャネル型 TFT を設けている。

#### 【0296】

このトップゲート型 TFT の作製方法は、実施の形態 6 に示したため、ここでは詳細な説明は省略することとする。

#### 【0297】

本実施例では、画素部 1311 に形成された発光素子と接続される N チャネル型 TFT は、駆動用 TFT 1301 と表記する。駆動用 TFT 1301 が有する電極 (第 1 の電極と表記する) の端部を覆うように、土手や隔壁と呼ばれる絶縁膜 1302 を形成する。絶縁膜 1302 には、無機材料 (酸化シリコン、窒化シリコン、酸化窒化シリコンなど)、感光性又は非感光性の有機材料 (ポリイミド、アクリル、ポリアミド、ポリイミドアミド

10

20

30

40

50

、レジスト又はベンゾシクロブテン)、珪素(Si)と酸素(O)との結合で骨格構造が構成され、置換基に少なくとも水素を含む、又は置換基にフッ素、アルキル基、又は芳香族炭化水素のうち少なくとも1種を有する材料、いわゆるシロキサン、及びそれらの積層構造を用いることができる。有機材料として、ポジ型感光性有機樹脂又はネガ型感光性有機樹脂を用いることができる。

## 【0298】

第1の電極上において、絶縁膜1302に開口部を形成する。開口部には、電界発光層1303が設けられ、電界発光層及び絶縁膜1302を覆うように発光素子の第2の電極1304が設けられる。

## 【0299】

なお、電界発光層が形成する分子励起子の種類としては一重項励起状態と三重項励起状態が可能であり、基底状態は通常一重項状態であるため、一重項励起状態からの発光は蛍光、三重項励起状態からの発光は燐光と呼ばれる。電界発光層からの発光とは、どちらの励起状態が寄与する場合も含まれる。更には、蛍光と燐光を組み合わせて用いてもよく、各RGBの発光特性(発光輝度や寿命等)により選択することができる。

## 【0300】

電界発光層1303は、第1の電極側から順に、HIL(ホール注入層)、HTL(ホール輸送層)、EML(発光層)、ETL(電子輸送層)、EIL(電子注入層)の順に積層されている。なお電界発光層は、積層構造以外に単層構造、又は混合構造をとることができる。

## 【0301】

また、電界発光層1303として、フルカラー表示とする場合、赤色(R)、緑色(G)、青色(B)の発光を示す材料を、それぞれ蒸着マスクを用いた蒸着法、又はインクジェット法などによって選択的に形成すればよい。

## 【0302】

具体的には、HILとしてCuPcやPEDOT、HTLとして-NPD、ETLとしてBCPやAlq<sub>3</sub>、EILとしてBCP:LiやCaF<sub>2</sub>をそれぞれ用いる。また例えばEMLは、R、G、Bのそれぞれの発光色に対応したドーパント(Rの場合DCM等、Gの場合DMQD等)をドープしたAlq<sub>3</sub>を用いればよい。なお、電界発光層は上記積層構造の材料に限定されない。例えば、CuPcやPEDOTの代わりに酸化モリブデン(MoO<sub>x</sub>:x=2~3)等の酸化物と-NPDやルブレンを共蒸着して形成し、ホール注入性を向上させることもできる。このような材料は、有機材料(低分子又は高分子を含む)、又は有機材料と無機材料の複合材料を用いることができる。

## 【0303】

また白色の発光を示す電界発光層を形成する場合、カラーフィルター、又はカラーフィルター及び色変換層などを別途設けることによってフルカラー表示を行うことができる。カラーフィルター又は色変換層は、例えば第2の基板(封止基板)に設けた後、張り合わせればよい。カラーフィルター又は色変換層はインクジェット法により形成することができる。勿論、白色以外の発光を示す電界発光層を形成して単色の発光装置を形成してもよい。また単色表示が可能なエリアカラータイプの表示装置を形成してもよい。

## 【0304】

また第1の電極及び第2の電極1304は仕事関数を考慮して材料を選択する必要がある。但し第1の電極及び第2の電極は、画素構成によりいずれも陽極、又は陰極となりうる。本実施例では、駆動用TFTの極性がNチャネル型であるため、第1の電極を陰極、第2の電極を陽極とすると好ましい。また駆動用TFTの極性がpチャネル型である場合、第1の電極を陽極、第2の電極を陰極とするとよい。

## 【0305】

本実施例では、駆動用TFTの極性がNチャネル型であるため、電子の移動方向を考慮すると、第1の電極を陰極、EIL(電子注入層)、ETL(電子輸送層)、EML(発光層)、HTL(ホール輸送層)、HIL(ホール注入層)、第2の電極を陽極とすると

10

20

30

40

50

好ましい。

【0306】

第2の電極を覆うパッシベーション膜として、DLC等をスパッタリング法やCVD法により絶縁膜を形成するとよい。その結果、水分や酸素の侵入を防止することができる。また第1の電極、第2の電極、その他の電極により、表示手段の側面を覆って酸素や水分の侵入を防ぐこともできる。次いで、封止基板を張り合わせる。封止基板により形成される空間には、窒素を封入したり、乾燥剤を配置してもよい。また、封止基板により形成される空間には、透光性を有し、吸水性の高い樹脂を充填してもよい。

【0307】

またコントラストを高めるため、偏光板又は円偏光板を設けてもよい。例えば、表示面の一面又は両面に偏光板、若しくは円偏光板を設けることができる。

【0308】

このように形成された構造を有する発光装置において、本実施例では第1の電極及び第2の電極に透光性を有する材料(ITO若しくはITSO)を用いる。そのため、信号線から入力されるビデオ信号に応じた輝度で電界発光層から光が出射方向1305、および出射方向1306に出射する。

【0309】

また、図12(A)とは一部構成が異なる他の構造例を図12(B)に示す。

【0310】

図12(B)に示す発光装置の構造は、駆動回路部1310及び画素部1311に、チャネルエッチ型のNチャネル型TFTを設けている。

【0311】

このチャネルエッチ型のTFTの作製方法は、実施の形態1に示したため、ここでは詳細な説明は省略することとする。

【0312】

図12(A)と同様に、画素部1311に形成された発光素子と接続されるNチャネル型TFTは、駆動用TFT1301と表記する。第1の電極は非透光性、好ましくは反射性の高い導電膜とし、第2の電極1304は透光性を有する導電膜とする点が図12(A)と異なる。そのため、光の出射方向1305は封止基板側のみである。

【0313】

また、図12(A)とは一部構成が異なる他の構造例を図12(C)に示す。

【0314】

図12(C)に示す発光装置の構造は、駆動回路部1310及び画素部1311に、チャネルトップ型のNチャネル型TFTを設けている。

【0315】

このチャネルトップ型のTFTの作製方法は、実施の形態5に示したため、ここでは詳細な説明は省略することとする。

【0316】

図12(A)と同様に、画素部1311に形成された発光素子と接続されるNチャネル型TFTは、駆動用TFT1301と表記する。第1の電極は透光性を有する導電膜とし、第2の電極1304は非透光性、好ましくは反射性の高い導電膜とする点が図12(A)と異なる。そのため、光の出射方向1306が基板側のみである。

【0317】

以上、各薄膜トランジスタを用いて発光装置の構造について説明したが、薄膜トランジスタの構成と、発光装置の構造はどのように組み合わせてもよい。

【0318】

また、本実施例は、実施の形態1乃至6、実施例1のいずれか一と自由に組み合わせることができる。

【実施例3】

【0319】

10

20

30

40

50

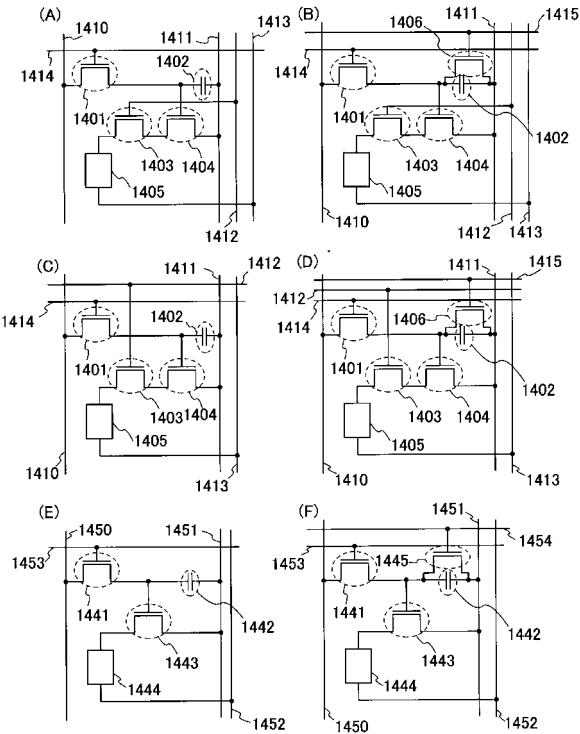

本実施例では E L 表示パネルの画素の構成について、図 13 に示す等価回路図を参照して説明する。

【0320】

図 13 (A) に示す画素は、列方向に信号線 1410 及び電源線 1411 ~ 1413、行方向に走査線 1414 が配置される。また、スイッチング用 TFT1401、駆動用 TFT1403、電流制御用 TFT1404、容量素子 1402 及び発光素子 1405 を有する。

【0321】

図 13 (C) に示す画素は、TFT1403 のゲート電極が、行方向に配置された電源線 1412 に接続される点が異なっており、それ以外は図 13 (A) に示す画素と同じ構成である。つまり、図 13 (A) と図 13 (C) に示す両画素は、同じ等価回路図を示す。しかしながら、列方向に電源線 1412 が配置される場合 (図 13 (A)) と、行方向に電源線 1412 が配置される場合 (図 13 (C)) では、各電源線は異なるレイヤーの導電体層で形成される。ここでは、駆動用 TFT1403 のゲート電極が接続される配線に注目し、これらを作製するレイヤーが異なることを表すために、図 13 (A)、図 13 (C) として分けて記載する。

【0322】

図 13 (A)、図 13 (C) に示す画素の特徴として、画素内に TFT1403、1404 が直列に接続されており、TFT1403 のチャネル長  $L_3$ 、チャネル幅  $W_3$ 、TFT1404 のチャネル長  $L_4$ 、チャネル幅  $W_4$  は、 $L_3 / W_3 : L_4 / W_4 = 5 ~ 6000 : 1$  を満たすように設定される点が挙げられる。6000 : 1 を満たす場合の一例としては、 $L_3$  が 500  $\mu\text{m}$ 、 $W_3$  が 3  $\mu\text{m}$ 、 $L_4$  が 3  $\mu\text{m}$ 、 $W_4$  が 100  $\mu\text{m}$  の場合がある。

【0323】

なお、TFT1403 は、飽和領域で動作し発光素子 1405 に流れる電流値を制御する役目を有し、TFT1404 は線形領域で動作し発光素子 1405 に対する電流の供給を制御する役目を有する。両 TFT は同じ導電型を有していると作製工程上好ましい。また TFT1403 には、エンハンスマント型だけでなく、ディブリーション型の TFT を用いてもよい。上記構成を有する本発明は、TFT1404 が線形領域で動作するために、TFT1404 の  $V_{GS}$  の僅かな変動は発光素子 1405 の電流値に影響を及ぼさない。つまり、発光素子 1405 の電流値は、飽和領域で動作する TFT1403 により決定される。上記構成を有する本発明は、TFT の特性バラツキに起因した発光素子の輝度ムラを改善して画質を向上させた表示装置を提供することができる。

【0324】

図 13 (A) ~ 図 13 (D) に示す画素において、TFT1401 は、画素に対するビデオ信号の入力を制御するものであり、TFT1401 がオンして、画素内にビデオ信号が入力されると、容量素子 1402 にそのビデオ信号が保持される。なお、図 13 (A)、図 13 (C) には、容量素子 1402 を設けた構成を示したが、本発明はこれに限定されず、ビデオ信号を保持する容量がゲート容量などでまかうことが可能な場合には、明示的に容量素子 1402 を設けなくてもよい。

【0325】

発光素子 1405 は、2 つの電極間に電界発光層が挟まれた構造を有し、順バイアス方向の電圧が印加されるように、画素電極と対向電極の間 (陽極と陰極の間) に電位差が設けられる。電界発光層は有機材料や無機材料等の広汎に渡る材料により構成され、この電界発光層におけるルミネッセンスには、一重項励起状態から基底状態に戻る際の発光 (蛍光) と、三重項励起状態から基底状態に戻る際の発光 (リン光) とが含まれる。

【0326】

図 13 (B) に示す画素は、TFT1406 と走査線 1415 を追加している以外は、図 13 (A) に示す画素構成と同じである。同様に、図 13 (D) に示す画素は、TFT1406 と走査線 1415 を追加している以外は、図 13 (C) に示す画素構成と同じである。

10

20

30

40

50

## 【0327】

TFT1406は、新たに配置された走査線1415によりオン又はオフが制御される。TFT1406がオンになると、容量素子1402に保持された電荷は放電し、TFT1406がオフする。つまり、TFT1406の配置により、強制的に発光素子1405に電流が流れない状態を作ることができる。従って、図13(B)、図13(D)の構成は、全ての画素に対する信号の書き込みを待つことなく、書き込み期間の開始と同時に直後に点灯期間を開始することができるため、デューティ比を向上することが可能となる。

## 【0328】

図13(E)に示す画素は、列方向に信号線1450、電源線1451、1452、行方向に走査線1453が配置される。また、スイッチング用TFT1441、駆動用TFT1443、容量素子1442及び発光素子1444を有する。図13(F)に示す画素は、TFT1445と走査線1454を追加している以外は、図13(E)に示す画素構成と同じである。なお、図13(F)の構成も、TFT1445の配置により、デューティ比を向上することが可能となる。

## 【0329】

また、本実施例は、実施の形態1乃至6、実施例1、実施例2のいずれか一と自由に組み合わせることができる。

## 【実施例4】

## 【0330】

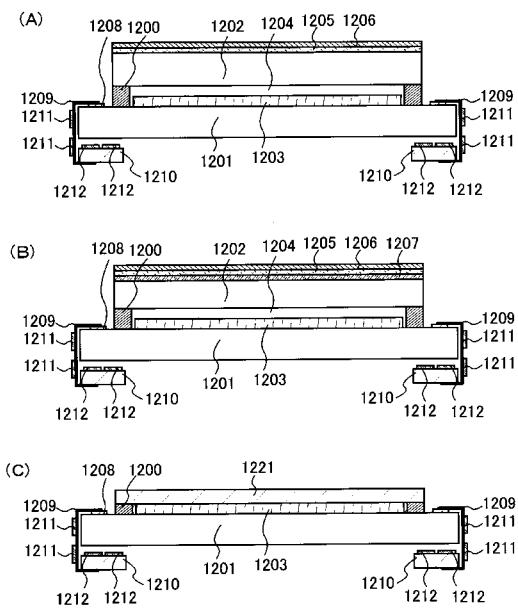

本実施例では、表示モジュールについて説明する。表示モジュールの一例として、発光表示モジュールの断面図を図14を用いて示す。

## 【0331】

図14(A)は、アクティブマトリクス基板1201と封止基板1202とが、シール材1200により固定された発光表示モジュールの断面を示しており、これらの間には画素部1203とが設けられ表示領域を形成している。

## 【0332】

封止基板1202と、画素部1203との間には、空間1204が形成される。空間には、不活性ガス、例えば窒素ガスを充填したり、吸水性の高い材料を有する透光性樹脂を形成して、さらに水分や酸素の侵入の防止を高めることができる。また透光性を有し、吸水性の高い樹脂を形成してもよい。透光性を有する樹脂により、発光素子からの光が第2の基板側へ出射される場合であっても、透過率を低減することなく形成することができる。

## 【0333】

また、コントラクタスを高めるため、モジュールの少なくとも画素部に偏光板、又は円偏光板(偏光板、1/4板及び1/2板)を備えるとよい。封止基板1202側から表示を認識する場合、封止基板1202から順に、1/4板及び1/2板1205、偏光板1206を設けるとよい。さらに偏光板上に反射防止膜を設けてもよい。

## 【0334】

また、封止基板1202及びアクティブマトリクス基板1201の両方から表示を認識する場合、アクティブマトリクス基板の表面にも同様に、1/4板及び1/2板、偏光板を設けるとよい。

## 【0335】

アクティブマトリクス基板1201に設けられた接続端子1208には、FPC1209を介して配線基板1210が接続されている。FPC又は接続配線には画素駆動回路( I Cチップ、ドライバI C等)1211が設けられ、配線基板1210には、コントローラ回路や電源回路などの外部回路1212が組み込まれている。

## 【0336】

また、図14(B)に示すように、画素部1203と偏光板の間、又は画素部と円偏光板の間に着色層1207を設けることができる。この場合、画素部に白色発光が可能な発

10

20

30

40

50

光素子を設け、RGBを示す着色層を別途設けることでフルカラー表示することができる。また、画素部に青色発光が可能な発光素子を設け、色変換層などを別途設けることによってフルカラー表示することができる。また、各画素部、赤色、緑色、青色の発光を示す発光素子を形成し、且つ着色層を用いることもできる。このような表示モジュールは、各RGBの色純度が高く、高精細な表示が可能となる。

### 【0337】

図14(C)においては、図14(A)と異なり、対向基板を用いずフィルム又は樹脂等の保護膜1221を用いてアクティブマトリクス基板及び発光素子を封止する場合を示す。画素部1203の第2の画素電極を覆って、保護膜1221が設けられている。第2の保護膜として、エポキシ樹脂、ウレタン樹脂、又はシリコーン樹脂等の有機材料を用いることができる。また第2の保護膜は、液滴吐出法によりポリマー材料を滴下して形成してもよい。本実施例では、ディスペンサを用いてエポキシ樹脂を吐出し、乾燥させる。さらに保護膜上に、対向基板を設けてもよい。その他の構成は、図14(A)と同様である。

10

### 【0338】

このように対向基板を用いず封止すると、表示装置の軽量化、小型化、薄膜化を向上させることができる。

### 【0339】

本実施例のモジュールは、プリント基板1210がFPC1209を用いて実装されているが、必ずしもこの構成に限定されない。COG(Chip on Glass)方式を用い、画素駆動回路1211、外部回路1212を直接基板上に実装させるようにしてもよい。

20

### 【0340】

また、本実施例は、実施の形態1乃至6、実施例1乃至3のいずれか一と自由に組み合わせることができる。

### 【実施例5】

### 【0341】

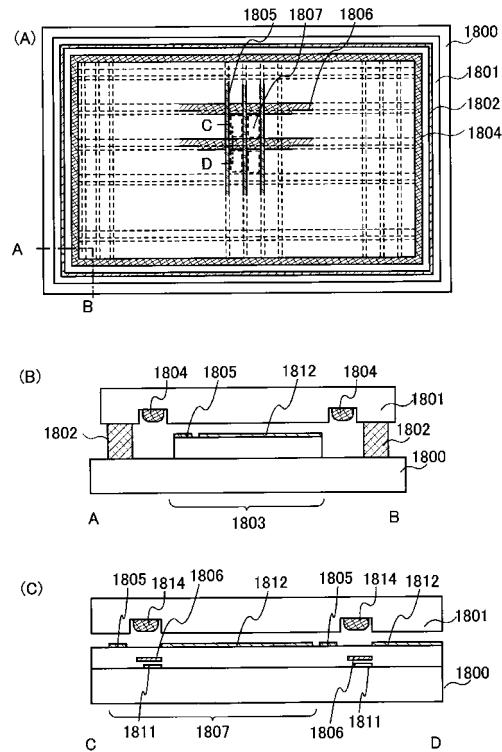

本実施例では、上記実施例で示す表示パネルの乾燥剤について、図15を用いて説明する。

30

### 【0342】

図15(A)は、表示パネルの上面図であり、図15(B)は、図28(A)のA-Bにおける断面図、図15(C)は図15(A)のC-Dにおける断面図を示す。

### 【0343】

図15(A)に示すように、アクティブマトリクス基板1800と対向基板1801とが、シール材1802によって封止されている。第1の基板と第2の基板との間には、画素領域が設けられている。画素領域には、ソース配線1805及びゲート配線1806が交差する領域において、画素1807が形成されている。画素領域とシール材1802との間には、乾燥剤1804が設けられている。また、画素領域において、ゲート配線又はソース配線、上に乾燥剤1814が設けられている。なお、ここは、ゲート配線上に乾燥剤1814を設けているが、ゲート配線及びソース配線上に設けることもできる。

40

### 【0344】

乾燥剤1804としては、酸化カルシウム(CaO)や酸化バリウム(BaO)等のようなアルカリ土類金属の酸化物のような化学吸着によって水(H<sub>2</sub>O)を吸着する物質を用いるのが好ましい。但し、これに限らずゼオライトやシリカゲル等の物理吸着によって水を吸着する物質を用いても構わない。

### 【0345】

また、乾燥剤を、透湿性の高い樹脂に粒状の物質として含まれた状態で基板に固定することができる。ここで、透湿性の高い樹脂としては、例えば、エステルアクリレート、エーテルアクリレート、エステルウレタンアクリレート、エーテルウレタンアクリレート、ブタジエンウレタンアクリレート、特殊ウレタンアクリレート、エポキシアクリレート、

50

アミノ樹脂アクリレート、アクリル樹脂アクリレート等のアクリル樹脂を用いることができる。この他、ビスフェノールA型液状樹脂、ビスフェノールA型固形樹脂、含ブロムエポキシ樹脂、ビスフェノールF型樹脂、ビスフェノールAD型樹脂、フェノール型樹脂、クレゾール型樹脂、ノボラック型樹脂、環状脂肪族エポキシ樹脂、エピビス型エポキシ樹脂、グリシジルエステル樹脂、グリジシルアミン系樹脂、複素環式エポキシ樹脂、変性エポキシ樹脂等のエポキシ樹脂を用いることができる。また、この他の物質を用いても構わない。また、例えばシロキサン等の無機物等を用いてもよい。

【0346】

さらに、吸水性を有する物質としては、化学吸着によって水を吸着することができる分子を有機溶媒中に混合した組成物を固化させたもの等を用いることができる。

10

【0347】

なお、上記のような透湿性の高い樹脂若しくは無機物としては、前記シール材として用いる物質よりも透湿性の高い物質を選択することが好ましい。

【0348】

以上のような、本発明の発光装置では、外部から発光装置内部に混入した水を、当該水が発光素子が形成された領域に至る前に吸水することができる。その結果、水に起因した画素に設けられた素子、代表的には発光素子の劣化を抑制することができる。

【0349】

図15(B)に示すように、表示パネルの周辺部において、乾燥剤1804はシール材1802と画素領域1803の間に設けられている。また、対向基板又はアクティブマトリクス基板に凹部を設け、そこに乾燥剤1804を設けることにより、表示パネルを薄型化することが可能となる。

20

【0350】

また、図15(C)に示すように、画素1807においては、表示素子を駆動する半導体素子の一部である半導体領域1811、ゲート配線1806、ソース配線1805、及び画素電極1812が形成されている。表示パネルの画素部において、乾燥剤1814は、対向基板においてゲート配線1806と重畳する領域に設けられている。ソース配線と比較して、ゲート配線の幅は2~4倍であるため、非表示領域であるゲート配線1806上に乾燥剤1814を設けることにより、開口率を低下せず、かつ表示素子への水分の侵入及びそれに起因する劣化を抑制することができる。また、対向基板に凹部を設け、そこに乾燥剤を設けることにより、表示パネルを薄型化することが可能である。

30

【0351】

また、本実施例は、実施の形態1乃至6、実施例1乃至4のいずれか一と自由に組み合わせることができる。

【実施例6】

【0352】

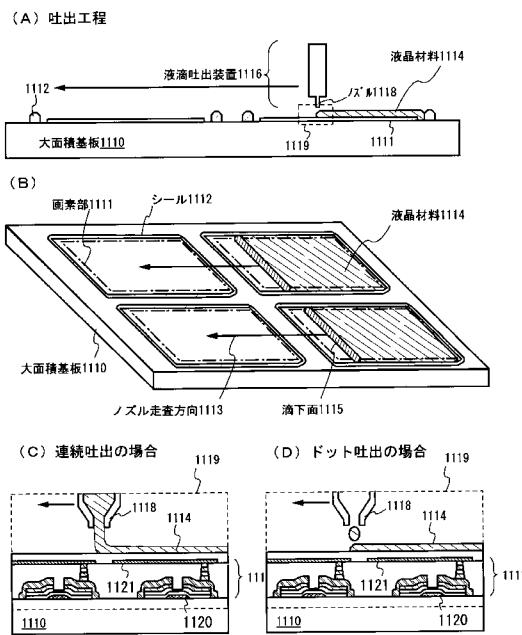

本実施例では、液晶滴下に液滴吐出法を用いる例を示す。本実施例では、大面積基板1110を用い、パネル4枚取りの作製例を図25に示す。

【0353】

図25(A)は、ディスペンサ(またはインクジェット)による液晶層形成の途中の断面図を示しており、シール材1112で囲まれた画素部1111を覆うように液晶材料1114を液滴吐出装置1116のノズル1118から吐出、噴射、または滴下させている。液滴吐出装置1116は、図25(A)中の矢印方向に移動させる。なお、ここではノズル1118を移動させた例を示したが、ノズルを固定し、基板を移動させることによって液晶層を形成してもよい。

40

【0354】

また、図25(B)には斜視図を示している。シール材1112で囲まれた領域のみに選択的に液晶材料1114を吐出、噴射、または滴下させ、ノズル走査方向1113に合わせて滴下面1115が移動している様子を示している。

【0355】

50

また、図25(A)の点線で囲まれた部分1119を拡大した断面図が図25(C)、図25(D)である。液晶材料の粘性が高い場合は、連続的に吐出され、図25(C)のように繋がったまま付着される。一方、液晶材料の粘性が低い場合には、間欠的に吐出され、図25(D)に示すように液滴が滴下される。

【0356】

なお、図25(C)中、1120は実施の形態1で得られる逆スタガ型TFT、1121は画素電極をそれぞれ指している。画素部1111は、マトリクス状に配置された画素電極と、該画素電極と接続されているスイッチング素子、ここでは逆スタガ型TFTと、保持容量(図示しない)とで構成されている。

【0357】

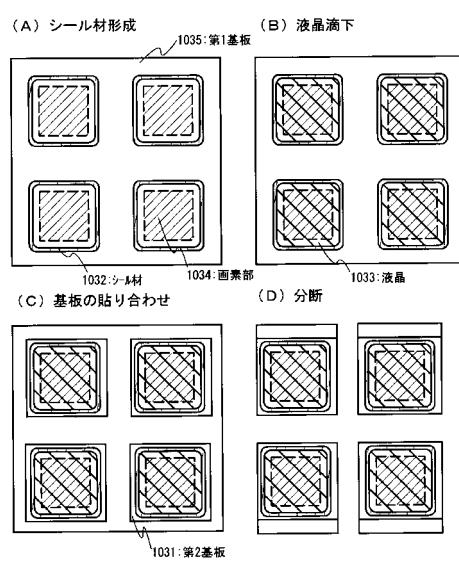

ここで、図26(A)～図26(D)を用いて、パネル作製の流れを以下に説明する。

【0358】

まず、絶縁表面に画素部1034が形成された第1基板1035を用意する。第1基板1035は、予め、配向膜の形成、ラビング処理、球状スペーサ散布、或いは柱状スペーサ形成、またはカラーフィルタの形成などを行っておく。次いで、図26(A)に示すように、不活性気体雰囲気または減圧下で第1基板1035上にディスペンサ装置またはインクジェット装置でシール材1032を所定の位置(画素部1034を囲むパターン)に形成する。半透明なシール材1032としてはフィラー(直径6μm～24μm)を含み、且つ、粘度40～400Pa・sのものを用いる。なお、後に接する液晶に溶解しないシール材料を選択することが好ましい。シール材としては、アクリル系光硬化樹脂やアクリル系熱硬化樹脂を用いればよい。また、簡単なシールパターンであるのでシール材1032は、印刷法で形成することもできる。

【0359】

次いで、シール材1032に囲まれた領域に液晶1033をインクジェット法により滴下する。(図26(B))液晶1033としては、インクジェット法によって吐出可能な粘度を有する公知の液晶材料を用いればよい。また、液晶材料は温度を調節することによって粘度を設定することができるため、インクジェット法に適している。インクジェット法により無駄なく必要な量だけの液晶1033をシール材1032に囲まれた領域に保持することができる。

【0360】

次いで、画素部1034が設けられた第1基板1035と、対向電極や配向膜が設けられた第2基板1031とを気泡が入らないように減圧下で貼りあわせる。(図26(C))ここでは、貼りあわせると同時に紫外線照射や熱処理を行って、シール材1032を硬化させる。なお、紫外線照射に加えて、熱処理を行ってもよい。

【0361】

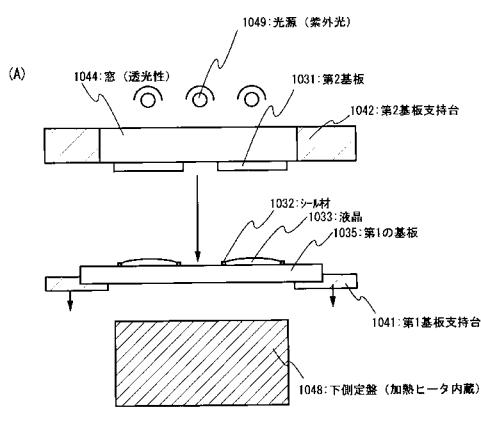

また、図27に貼り合わせ時または貼り合わせ後に紫外線照射や熱処理が可能な貼り合わせ装置の例を示す。

【0362】

図27中、1041は第1基板支持台、1042は第2基板支持台、1044は窓、1048は下側定盤、1049は光源である。なお、図27において、図26と対応する部分は同一の符号を用いている。

【0363】

下側定盤1048は加熱ヒータが内蔵されており、シール材を硬化させる。また、第2基板支持台には窓1044が設けられており、光源1049からの紫外光などを通過させるようになっている。ここでは図示していないが窓1044を通して基板の位置アライメントを行う。また、対向基板となる第2の基板1031は予め、所望のサイズに切断しておき、台1042に真空チャックなどで固定しておく。図27(A)は貼り合わせ前の状態を示している。

【0364】

貼り合わせ時には、第1基板支持台と第2基板支持台とを下降させた後、圧力をかけて第

10

20

30

40

50

1基板1035と第2基板1031を貼り合わせ、そのまま紫外光を照射することによって硬化させる。貼り合わせ後の状態を図27(B)に示す。

【0365】

次いで、スクライバー装置、ブレイカー装置、ロールカッターなどの切断装置を用いて第1基板1035を切断する。(図26(D))こうして、1枚の基板から4つのパネルを作製することができる。そして、公知の技術を用いてFPCを貼りつける。

【0366】

なお、第1基板1035、第2基板1031としてはガラス基板、またはプラスチック基板を用いることができる。

【0367】

以上の工程によって得られた液晶モジュールの上面図を図28(A)に示すとともに、他の液晶モジュールの上面図の例を図28(B)に示す。

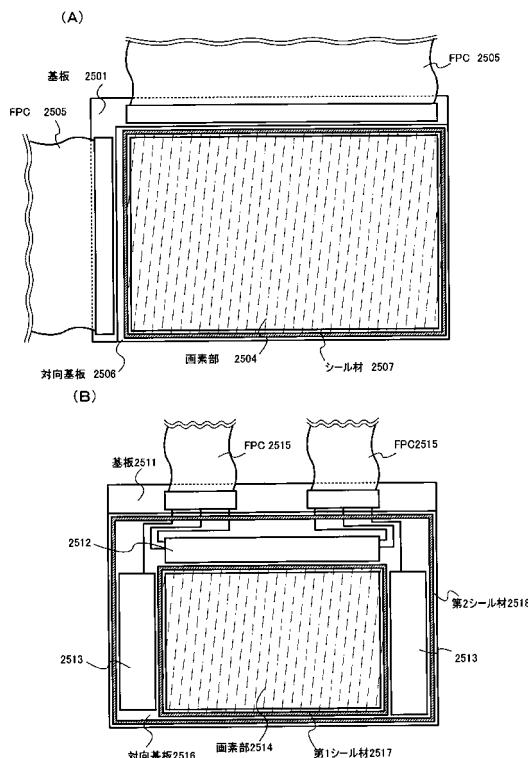

【0368】

図28(A)中、2501は、アクティブマトリクス基板、2506は対向基板、2504は画素部、2507はシール材、2505はFPCである。なお、液晶を液滴吐出法により吐出させ、減圧下で一対の基板2501、2506をシール材2507で貼り合わせている。

【0369】

セミアモルファスシリコン膜からなる活性層を有するTFTを用いた場合、駆動回路の一部を作製することもでき、図28(B)のような液晶モジュールを作製することができる。

【0370】

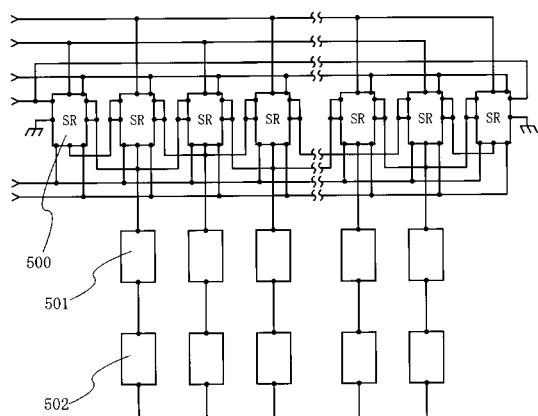

図30は、 $5 \sim 50 \text{ cm}^2 / \text{V} \cdot \text{sec}$ の電界効果移動度が得られるSAS(セミアモルファスシリコン)を使ったnチャネル型のTFTで構成する走査線側駆動回路のブロック図を示している。

【0371】

図30において500で示すブロックが1段分のサンプリングパルスを出力するパルス出力回路に相当し、シフトレジスタはn個のパルス出力回路により構成される。501はバッファ回路であり、その先に画素502が接続される。

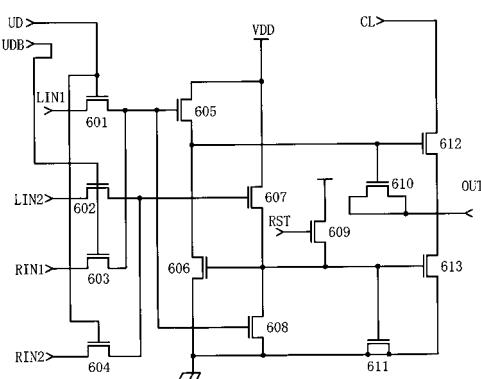

【0372】

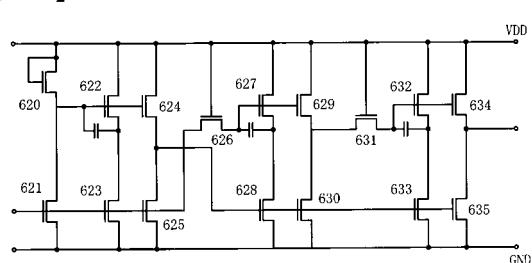

図31は、パルス出力回路500の具体的な構成を示したものであり、nチャネル型のTFT601～613で回路が構成されている。このとき、SASを使ったnチャネル型のTFTの動作特性を考慮して、TFTのサイズを決定すれば良い。例えば、チャネル長を $8 \mu\text{m}$ とすると、チャネル幅は $10 \sim 80 \mu\text{m}$ の範囲で設定することができる。

【0373】

また、バッファ回路501の具体的な構成を図32に示す。バッファ回路も同様にnチャネル型のTFT620～635で構成されている。このとき、SASを使ったnチャネル型のTFTの動作特性を考慮して、TFTのサイズを決定すれば良い。例えば、チャネル長を $10 \mu\text{m}$ とすると、チャネル幅は $10 \sim 1800 \mu\text{m}$ の範囲で設定することとなる。

【0374】

なお、セミアモルファスシリコン膜からなる活性層を有するTFTで形成できない駆動回路は、ICチップ(図示しない)を実装する。

【0375】

図28(B)中、2511は、アクティブマトリクス基板、2516は対向基板、2512はソース信号線駆動回路、2513はゲート信号線駆動回路、2514は画素部、2517は第1シール材、2515はFPCである。なお、液晶を液滴吐出法により吐出させ、一対の基板2511、2516を第1シール材2517および第2シール材で貼り合わせている。駆動回路部2512、2513には液晶は不要であるため、画素部2514のみに液晶を保持させており、第2シール材2518はパネル全体の補強のために設けら

10

20

30

40

50

れている。

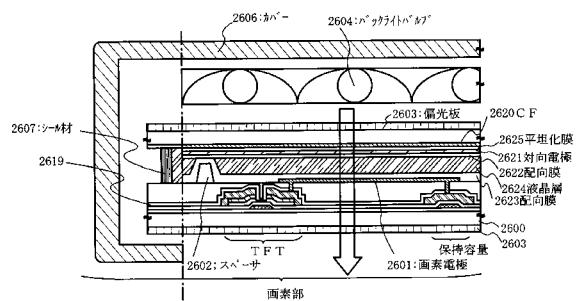

【0376】

また、得られた液晶モジュールにバックライトバルブ2604およびミラーを設け、カバー2606で覆えば、図29にその断面図の一部を示したようなアクティブマトリクス型液晶表示装置（透過型）が完成する。また、バックライトを表示領域の外側に配置して、導光板を用いてもよい。なお、カバーと液晶モジュールは接着剤や有機樹脂を用いて固定する。また、透過型であるので偏光板2603は、アクティブマトリクス基板と対向基板の両方に貼り付ける。また、他の光学フィルム（反射防止フィルムや偏光性フィルムなど）や、保護フィルム（図示しない）を設けてもよい。

【0377】

なお、図29中、2600は基板、2601は画素電極、2602は柱状スペーサ、2607はシール材、2620は着色層、遮光層が各画素に対応して配置されたカラーフィルタ、2625は平坦化膜、2621は対向電極、2622、2623は配向膜、2624は液晶層、2619は保護膜である。

【0378】

また、本実施例は実施の形態1、実施の形態7乃至12のいずれか一と自由に組み合わせることができる。

【実施例7】

【0379】

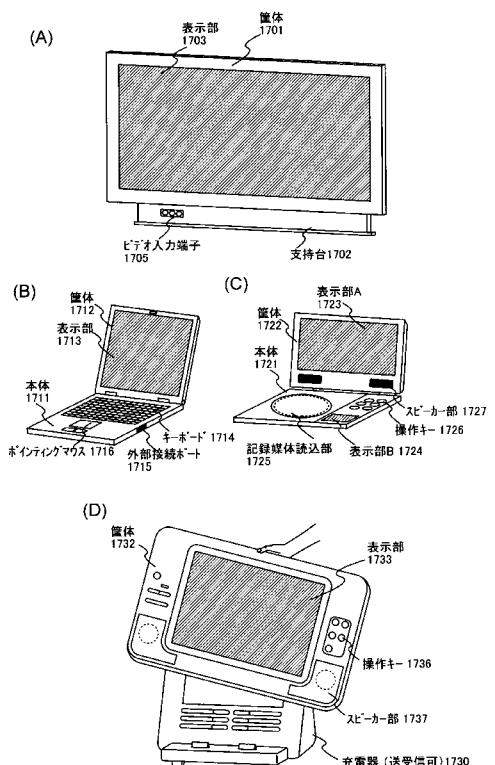

本発明の液晶表示装置、発光表示装置、及び電子機器として、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーオーディオ、オーディオコンポ等）、ノート型パソコンコンピュータ、ゲーム機器、携帯情報端末（モバイルコンピュータ、携帯電話、携帯型ゲーム機又は電子書籍等）、記録媒体を備えた画像再生装置（具体的にはDigital Versatile Disc（DVD）等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置）などが挙げられる。特に、大型画面を有する大型テレビ等に本発明を用いることが望ましい。それら電子機器の具体例を図33に示す。

【0380】

図33（A）は22インチ～50インチの大画面を有する大型の表示装置であり、筐体1701、支持台1702、表示部1703、ビデオ入力端子1705等を含む。なお、表示装置は、パソコンコンピュータ用、TV放送受信用、双方向TV用などの全ての情報表示用表示装置が含まれる。本発明により、1辺が1000mmを超える第5世代以降のガラス基板を用いても、比較的安価な大型表示装置を実現できる。

【0381】

図33（B）はノート型パソコンコンピュータであり、本体1711、筐体1712、表示部1713、キーボード1714、外部接続ポート1715、ポインティングマウス1716等を含む。本発明により、比較的安価なノート型パソコンコンピュータを実現できる。

【0382】

図33（C）は記録媒体を備えた携帯型の画像再生装置（具体的にはDVD再生装置）であり、本体1721、筐体1722、表示部A1723、表示部B1724、記録媒体（DVD等）読み込み部1725、操作キー1726、スピーカー部1727等を含む。表示部A1723は主として画像情報を表示し、表示部B1724は主として文字情報を表示する。なお、記録媒体を備えた画像再生装置には家庭用ゲーム機器なども含まれる。本発明により、比較的安価な画像再生装置を実現できる。

【0383】

図33（D）は、ワイヤレスでディスプレイのみを持ち運び可能なTVである。筐体1732にはバッテリー及び信号受信器が内蔵されており、そのバッテリーで表示部1733やスピーカ部1737を駆動させる。バッテリーは充電器1730で繰り返し充電が可能となっている。また、充電器1730は映像信号を送受信することが可能で、その映像信

10

20

30

40

50

号をディスプレイの信号受信器に送信することができる。筐体 1732 は操作キー 1736 によって制御する。また、図 33 (D) に示す装置は、操作キー 1736 を操作することによって、筐体 1732 から充電器 1730 に信号を送ることも可能であるため映像音声双方向通信装置とも言える。また、操作キー 1736 を操作することによって、筐体 1732 から充電器 1730 に信号を送り、さらに充電器 1730 が送信できる信号を他の電子機器に受信させることによって、他の電子機器の通信制御も可能であり、汎用遠隔制御装置とも言える。本発明により、比較的大型 (22 インチ ~ 50 インチ) の持ち運び可能な TV を安価な製造プロセスで提供できる。

#### 【0384】

以上の様に、本発明を実施して得た発光装置や液晶表示装置は、あらゆる電子機器の表示部として用いても良い。 10

#### 【0385】

また、本実施例は、実施の形態 1 乃至 12、実施例 1 乃至 6 のいずれか一と自由に組み合わせることができる。

#### 【産業上の利用可能性】

#### 【0386】

本発明は、導体パターンを形成する発光装置製造プロセスや液晶表示装置プロセスにおいて、パターニング工程が短縮でき、材料の使用量の削減も図れるため、大幅なコストダウンを基板サイズに関わらず実現できる。

#### 【図面の簡単な説明】

#### 【0387】

【図 1】アクティブマトリクス型の発光装置の作製工程を示す断面図。

【図 2】アクティブマトリクス型の発光装置の作製工程を示す断面図。

【図 3】画素上面図を示す図。

【図 4】レーザビーム描画装置を示す図。

【図 5】発光装置の作製工程を示す図。(実施の形態 2)

【図 6】発光装置の作製工程を示す図。(実施の形態 3)

【図 7】発光装置の作製工程を示す図。(実施の形態 4)

【図 8】チャネルトップ型 TFT を示す断面図。(実施の形態 5)

【図 9】順スタガ型 TFT を示す断面図。(実施の形態 6)

20

【図 10】本発明の発光表示装置の上面図。(実施の形態 1)

【図 11】本発明の発光表示装置の上面図。(実施例 1)

【図 12】発光装置の一例を示す断面図。(実施例 2)

【図 13】本発明の E-L 表示パネルに適用できる画素の構成を説明する回路図。(実施例 3)

【図 14】発光表示モジュールの断面図である。(実施例 4)

【図 15】表示パネルの上面図および断面図である。(実施例 5)

【図 16】液滴吐出装置を示す斜視図。

【図 17】AM-LCD の作製工程を示す断面図。(実施の形態 7)

【図 18】AM-LCD の作製工程を示す断面図。(実施の形態 7)

【図 19】画素上面図を示す図。(実施の形態 7)

30

【図 20】液晶表示装置の作製工程を示す図。(実施の形態 8)

【図 21】液晶表示装置の作製工程を示す図。(実施の形態 9)

【図 22】液晶表示装置の作製工程を示す図。(実施の形態 10)

【図 23】チャネルトップ型 TFT を示す断面図。(実施の形態 11)

【図 24】順スタガ型 TFT を示す断面図。(実施の形態 12)

【図 25】液晶滴下を液滴吐出法で行う斜視図および断面図である。(実施例 6)

【図 26】プロセス上面図を示す図。(実施例 6)

【図 27】貼りあわせ装置および貼りあわせ工程を示す断面図。(実施例 6)

【図 28】液晶モジュールの上面図。(実施例 6)

40

50

【図29】アクティブマトリクス型液晶表示装置の断面構造図。（実施例6）

【図30】駆動回路を示すブロック図。（実施例6）

【図31】駆動回路を示す回路図。（実施例6）

【図32】駆動回路を示す回路図。（実施例6）

【図33】電子機器の一例を示す図。（実施例7）

【符号の説明】

【0388】

10 基板, 11 下地層, 12 導電膜パターン, 15 ゲート電極, 17 引出電極, 18 ゲート絶縁膜, 19 半導体膜, 20 半導体膜, 21 マスク, 22 ソース配線またはドレイン配線, 23 ソース配線またはドレイン配線, 24 チャネル形成領域, 25 ドレイン領域, 26 ソース領域, 27 保護膜, 28 層間絶縁膜, 29

凸状部（ピラー）, 30 第1の電極, 34 隔壁, 35 封止基板, 36 有機化合物を含む層, 37 第2の電極, 38 充填材, 40 配線, 41 端子電極, 45 異方性導電膜, 46 FPC, 220 導電膜パターン, 221 レーザー光照射した部分, 222 ソース配線またはドレイン配線, 223 ソース配線またはドレイン配線, 224 チャネル形成領域, 225 ドレイン領域, 226 ソース領域, 250 導電膜パターン, 251 レーザー光照射した部分, 252 ソース配線またはドレイン配線, 253 ソース配線またはドレイン配線, 254 チャネル形成領域, 255 ドレイン領域, 256 ソース領域, 260 ゲート絶縁膜, 301 下地絶縁膜, 302 ゲート電極, 320 導電膜パターン, 322 ソース配線またはドレイン配線, 323 ソース配線またはドレイン配線, 324 チャネル形成領域, 325 ドレイン領域, 326 ソース領域, 401 レーザビーム直接描画装置, 402 パーソナルコンピュータ, 403 レーザ発振器, 404 電源, 405 光学系, 406 音響光学変調器, 407 光学系, 408 基板, 409 基板移動機構, 410 D/A変換部, 411 ドライバ, 412 ドライバ, 500 パルス出力回路, 501 バッファ回路, 502 画素, 601 nチャネル型のTFT, 602 nチャネル型のTFT, 603 nチャネル型のTFT, 604 nチャネル型のTFT, 605 nチャネル型のTFT, 606 nチャネル型のTFT, 607 nチャネル型のTFT, 608 nチャネル型のTFT, 609 nチャネル型のTFT, 610 nチャネル型のTFT, 611 nチャネル型のTFT, 612 nチャネル型のTFT, 613, 620 nチャネル型のTFT, 621 nチャネル型のTFT, 622 nチャネル型のTFT, 623 nチャネル型のTFT, 624 nチャネル型のTFT, 625 nチャネル型のTFT, 626 nチャネル型のTFT, 627 nチャネル型のTFT, 628 nチャネル型のTFT, 629 nチャネル型のTFT, 630 nチャネル型のTFT, 631 nチャネル型のTFT, 632 nチャネル型のTFT, 633 nチャネル型のTFT, 634 nチャネル型のTFT, 635 nチャネル型のTFT, 700 基板, 701 画素部, 702 画素, 703 走査線側入力端子, 704 信号線側入力端子, 810 基板, 811 下地膜, 815 ゲート電極, 818 ゲート絶縁膜, 822 配線, 823 配線, 824 半導体膜, 825 N型を有する半導体膜, 826 N型を有する半導体膜, 827 チャネル保護膜, 828 層間絶縁膜, 829 電極, 830 電極, 840 端子電極, 841 電極, 910 基板, 911 下地膜, 915 ゲート配線, 918 ゲート絶縁層, 923 ソース配線層, 924 ソース配線層, 925 n型の半導体層, 926 n型の半導体層, 927 半導体層, 928 層間絶縁膜, 929 電極, 930 電極, 940 端子電極, 941 電極, 1031 第2基板, 1032 シール材, 1033 液晶, 1034 画素部, 1035 第1基板, 1041 第1基板支持台, 1042 第2基板支持台, 1044 窓, 1048 下側定盤, 1049 光源, 1110 大面積基板, 1111 画素部, 1112 シール材, 1113 ノズル走査方向, 1114 液晶材料, 1115 滴下面, 1116 液滴吐出装置, 1118 ノズル, 1119 点線で囲まれた部分, 1120 逆スタガ型TFT, 1121 画素電極, 1200 シール材, 1201 アクティブマトリクス基板, 1202 10

20

30

40

50

封止基板, 1203 画素部, 1204 空間, 1205 1/4 板及び1/2 板, 1206 偏光板, 1207 着色層, 1208 接続端子, 1209 FPC, 1210 プリント基板, 1211 画素駆動回路, 1212 外部回路, 1221 保護膜, 1301 駆動用TFT, 1302 絶縁膜, 1303 電界発光層, 1304 第2の電極, 1305 出射方向, 1306 両矢印方向, 1310 駆動回路部, 1311 画素部, 1401 スイッチング用TFT, 1402 容量素子, 1403 駆動用TFT, 1404 電流制御用TFT, 1405 発光素子, 1406 TFT, 1410 信号線, 1411 電源線, 1412 電源線, 1413 電源線, 1414 走査線, 1415 電源線, 1441 スイッチング用TFT, 1442 容量素子, 1443 駆動用TFT, 1444 発光素子, 1445 TFT, 1450 信号線, 1451 10 電源線, 1452 電源線, 1453 走査線, 1454 走査線, 1500 大型基板, 1503 領域, 1504 撮像手段, 1505a ヘッド, 1505b ヘッド, 1505c ヘッド, 1507 ステージ, 1511 マーカー, 1600 基板, 1601 画素領域, 1602 走査側の駆動回路, 1604a, 1604b, 1605 a 駆動回路, 1605b 駆動回路, 1701 筐体, 1702 支持台, 1703 表示部, 1705 ビデオ入力端子, 1711 本体, 1712 筐体, 1713 表示部, 1714 キーボード, 1715 外部接続ポート, 1716 ポインティングマウス, 1721 本体, 1722 筐体, 1723 表示部A, 1724 表示部B, 1725 記録媒体読込部, 1726 操作キー, 1727 スピーカー部, 1730 充電器, 1732 筐体, 1733 表示部, 1736 操作キー, 1737 スピーカー部 20 , 1800 アクティブマトリクス基板, 1801 対向基板, 1802 シール材, 1803 画素領域, 1804 乾燥剤, 1805 ソース配線, 1806 ゲート配線, 1807 画素, 1811 画素, 1812 画素電極, 1814 乾燥剤, 2010 基板, 2011 下地層, 2012 導電膜パターン, 2015 ゲート配線, 2018 ゲート絶縁膜, 2019 半導体膜, 2020 半導体膜, 2021 マスク, 2022 ソース配線またはドレイン配線, 2023 ソース配線またはドレイン配線, 2024 チャネル形成領域, 2025 ドレイン領域, 2026 ソース領域, 2027 保護膜, 2028 層間絶縁膜, 2029 凸状部(ピラー), 2030 画素電極, 2034a 配向膜, 2034b 配向膜, 2035 対向基板, 2036a 着色層, 2036b 遮光層(ブラックマトリクス), 2037 オーバーコート層, 2038 , 2039 液晶, 2040 配線, 2045 異方性導電体層, 2046 FPC, 2120 導電膜パターン, 2121 レーザー光照射した部分, 2122 ソース配線またはドレイン配線, 2123 ソース配線またはドレイン配線, 2124 チャネル形成領域, 2125 ドレイン領域, 2126 ソース領域, 2150 導電膜パターン, 2151 レーザー光照射した部分, 2152 ソース配線またはドレイン配線, 2153 ソース配線またはドレイン配線, 2154 チャネル形成領域, 2155 ドレイン領域, 2156 ソース領域, 2160 ゲート絶縁膜, 2201 下地絶縁膜, 2202 ゲート電極, 2220 導電膜パターン, 2222 ソース配線またはドレイン配線, 2223 ソース配線またはドレイン配線, 2224 チャネル形成領域, 2225 ドレイン領域, 2226 ソース領域, 2310 基板, 2311 下地膜, 2315 ゲート電極, 2318 ゲート絶縁膜, 2322 配線, 2323 配線, 2324 半導体膜, 2325 N型を有する半導体膜, 2326 N型を有する半導体膜, 2327 チャネル保護膜, 2328 層間絶縁膜, 2329 電極, 2330 電極, 2340 端子電極, 2341 電極, 2410 , 2411 下地膜, 2415 ゲート配線, 2418 ゲート絶縁層, 2423 ソース配線層, 2424 ドレイン配線層, 2425 n型の半導体, 2426 n型の半導体, 2427 半導体層, 2428 層間絶縁膜, 2429 電極, 2430 電極, 2440 端子電極, 2441 電極, 2501 基板, 2504 画素部, 2505 FPC, 2506 対向基板, 2507 シール材, 2511 基板, 2512 ソース信号線駆動回路, 2513 ゲート信号線駆動回路, 2514 画素部, 2515 FPC, 2516 対向基板, 2517 シール材, 251 10 10 20 30 40 50

8 第2シール材, 2600 基板, 2601 画素電極, 2602 スペーサ, 260

3 偏光板, 2604 バックライトバルブ, 2606 カバー, 2607 シール材,

2620 CF, 2621 対向電極, 2622 配向膜, 2623 配向膜, 2624

液晶層, 2625 平坦化膜

【図1】

【図2】

【図3】

【図4】

- 401: レーザーム直接描画装置

- 402: パーソナルコンピュータ

- 403: レーザ発振器

- 404: 電源

- 405: 光学系

- 406: 音響光学変調器

- 407: 光学系

- 408: 基板

- 409: 基板移動機構

- 410: D/A変換部

- 411: ドライバ

- 412: ドライバ

【図5】

【 図 6 】

【図7】

【図8】

【図9】

【図10】

【図11】

【 図 1 2 】

【 図 1 3 】

【 図 1 4 】

|                       |             |

|-----------------------|-------------|