(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3792363号

(P3792363)

(45) 発行日 平成18年7月5日(2006.7.5)

(24) 登録日 平成18年4月14日(2006.4.14)

(51) Int.C1.

F 1

HO3M 1/14 (2006.01)

HO3M 1/14

A

請求項の数 5 (全 11 頁)

(21) 出願番号 特願平9-237318

(22) 出願日 平成9年9月2日(1997.9.2)

(65) 公開番号 特開平11-88171

(43) 公開日 平成11年3月30日(1999.3.30)

審査請求日 平成16年3月15日(2004.3.15)

(73) 特許権者 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1番

1号

(74) 代理人 100108187

弁理士 横山 淳一

(74) 代理人 100068755

弁理士 恩田 博宣

(72) 発明者 山本 紳一

愛知県春日井市高蔵寺町二丁目1844番

2 富士通ヴィエルエスアイ株式会社内

審査官 柳下 勝幸

最終頁に続く

(54) 【発明の名称】 A／D変換器

## (57) 【特許請求の範囲】

## 【請求項1】

アナログ入力信号をサンプリングし、上位ビット側のデジタル信号を生成する上位側の変換部と、

アナログ入力信号をサンプリングし、前記上位側の変換部の処理結果に基づいて下位ビット側のデジタル信号を生成する下位側の変換部と、

前記各変換部が生成したデジタル信号を合成しアナログ入力信号をデジタル出力信号とする出力部と

を備えたA／D変換器であって、

前記下位側の変換部は前記上位側の変換部がサンプリングを終了するまでの間にサンプリングを開始し、かつ前記上位側の変換部のデジタル信号を生成する動作中にサンプリングを終了することを特徴とするA／D変換器。

## 【請求項2】

アナログ入力信号をサンプリングし、サンプリングしたアナログ入力信号と基準電圧とを比較判定して上位ビット側のデジタル信号を生成する上位側の変換部と、

アナログ入力信号をサンプリングし、前記上位側の変換部の比較判定結果に基づいて下位側基準電圧を設定し、サンプリングしたアナログ入力信号と該下位側基準電圧とを比較判定して下位ビット側のデジタル信号を生成する下位側の変換部と、

前記各変換部が生成したデジタル信号を合成しアナログ入力信号をデジタル出力信号とする出力部と

を備えた A / D 変換器であって、

前記下位側の変換部は、前記上位側の変換部がサンプリングを終了するまでの間にサンプリングを開始し、かつ前記上位側の変換部の比較判定動作中にサンプリングを終了することを特徴とする A / D 変換器。

【請求項 3】

アナログ入力信号をサンプリングし、サンプリングしたアナログ入力信号と基準電圧とを比較判定して上位ビット側のデジタル信号を生成する上位側の変換部と、

アナログ入力信号をサンプリングし、サンプリングしたアナログ入力信号と前記上位ビット側のデジタル信号を再びアナログ信号にした値と前記上位側の変換部の比較判定結果とに基づいて、下位ビット側のデジタル信号を生成する下位側の変換部と、

前記各変換部が生成したデジタル信号を合成しアナログ入力信号をデジタル出力信号とする出力部と

を備えた A / D 変換器であって、

前記下位側の変換部は、前記上位側の変換部がサンプリングを終了するまでの間にサンプリングを開始し、かつ前記上位側の変換部の比較判定動作中にサンプリングを終了することを特徴とする A / D 変換器。

【請求項 4】

前記下位側の変換部は、

前記上位ビット側のデジタル信号が示す電位の範囲を拡大した範囲から下位ビット側のデジタル信号を生成することを特徴とする請求項 1 又は請求項 3 のいずれか 1 項に記載の A / D 変換器。

【請求項 5】

前記下位側の変換部は、

前記上位ビット側のデジタル信号が示す電位を拡大した値を前記下位側基準電圧として設定することを特徴とする請求項 2 に記載の A / D 変換器。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、アナログ信号をデジタル信号に変換する A / D 変換器に関するものである。

【0002】

近年の半導体集積回路装置は、益々高集積化及び高速化が進められている。そして、該装置には A / D 変換器を搭載するものがある。このような A / D 変換器としては、並列型に對して回路面積を小さくすることができる直並列型のものがあり、その A / D 変換器においても、変換速度を向上させることが要求されている。

【0003】

【従来の技術】

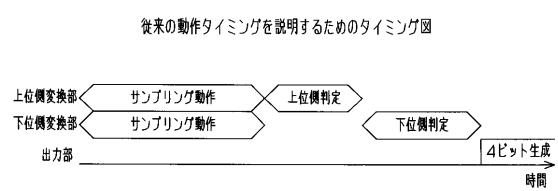

従来の 4 ビットの直並列型の A / D 変換器は、上位側変換部及び下位側変換部を備えている。上位側変換部は、サンプルホールド回路（以下、S / H 回路という）及び上位 2 ビット用の並列型の A / D 変換回路から構成されている。下位側変換部は、S / H 回路及び下位 2 ビット用の並列型の A / D 変換回路から構成されている。

【0004】

上位側及び下位側変換部の両 S / H 回路には、制御部から同一のサンプリングパルス信号が入力される。すると、両 S / H 回路は、図 8 に示すように、該サンプリングパルス信号に基づいたサンプリング時間で同時にアナログ入力信号の瞬時値をサンプリングする。従って、両 S / H 回路は、同一の瞬時値をホールドする。

【0005】

両 S / H 回路がホールド状態となると、上位 2 ビット用の A / D 変換回路が動作し、上位 2 ビットの粗判定（上位側判定）を行なう。即ち、上位側変換部は S / H 回路がホールドした瞬時値と比較基準電圧を 4 等分した 3 段階の電位とをそれぞれ比較し、その比較結果に基づく信号を出力部及び下位側変換部に出力する。

10

20

30

40

50

## 【0006】

下位側変換部は、上位側変換部の比較結果に基づく信号が入力されると、その信号に基づいて比較基準電圧を設定し、下位2ビット用のA/D変換回路にて下位2ビットの密判定（下位側判定）を行なう。即ち、下位側変換部はS/H回路がホールドした瞬時値と、上位側変換部の比較結果に基づいて設定した比較基準電圧を4等分した3段階の電位とをそれぞれ比較し、その比較結果に基づく信号を出力部に出力する。

## 【0007】

出力部は、上位側変換部の比較結果に基づく信号と下位側変換部の比較結果に基づく信号が入力されると、両信号を合成し4ビットのデジタル信号を生成して出力する。

## 【0008】

10

## 【発明が解決しようとする課題】

前記A/D変換器において、変換速度を高速化するためにはサンプリング時間を短くすることが効果的である。

## 【0009】

しかしながら、S/H回路で必要とするサンプリング時間は、アナログ信号を出力する外部回路の出力インピーダンスと、S/H回路の入力インピーダンスとの値に応じて決まる。従って、外部回路の出力インピーダンスが高い場合にサンプリング時間を短くすると、S/H回路のコンデンサにサンプリングされる電圧がアナログ信号の瞬時値に達する前にサンプリング動作が終了され、正確な瞬時値をサンプリングできなくなる。この場合、A/D変換器の変換速度を維持させるためには、外部回路にドライバー回路を付加する必要があり、外部回路の面積が増大してしまうとともに、コストが増加するという問題がある。

20

## 【0010】

又、前記A/D変換器では、外部回路にドライバー回路を付加しサンプリング時間を短くして変換速度を向上させても、上位側変換部の上位2ビット用のA/D変換回路が動作中は、下位側変換部の動作が停止しているため、変換速度に限界がある。

## 【0011】

30

この発明の目的は、A/D変換器の回路構成を変更することなく、入力インピーダンスを実質的に上昇させることにより、アナログ信号出力回路の回路面積の縮少、あるいはサンプリング時間の短縮によるA/D変換速度の向上を図り得るA/D変換器を提供することにある。

## 【0012】

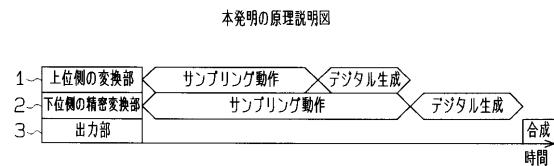

## 【課題を解決するための手段】

図1は請求項1に記載した発明の原理説明図である。すなわち、A/D変換器は上位側の変換部1と下位側の（精密）変換部2と出力部3を備える。上位側の変換部1は、アナログ入力信号をサンプリングし、上位ビット側のデジタル信号を生成する。

## 【0013】

40

下位側の（精密）変換部2は、上位側の変換部1がサンプリングを終了するまでの間にサンプリングを開始し、かつ上位側の変換部1のデジタル信号を生成する動作中にサンプリングを終了する。そして、そのサンプリングしたアナログ入力信号と上位側の変換部の処理結果に基づいて下位ビット側のデジタル信号を生成する。出力部3は、両変換部1, 2が生成したデジタル信号を合成しデジタル出力信号を生成する。

## 【0014】

請求項2では、アナログ入力信号をサンプリングし、サンプリングしたアナログ入力信号と基準電圧とを比較判定して上位ビット側のデジタル信号を生成する上位側の変換部と、アナログ入力信号をサンプリングし、前記上位側の変換部の比較判定結果に基づいて下位側基準電圧を設定し、サンプリングしたアナログ入力信号と該下位側基準電圧とを比較判定して下位ビット側のデジタル信号を生成する下位側の変換部と、前記各変換部が生成したデジタル信号を合成しアナログ入力信号をデジタル出力信号とする出力部とを備えたA/D変換器であって、前記下位側の変換部は、前記上位側の変換部がサンプリングを終

50

了するまでの間にサンプリングを開始し、かつ前記上位側の変換部の比較判定動作中にサンプリングを終了することを要旨としている。

【0015】

請求項3では、アナログ入力信号をサンプリングし、サンプリングしたアナログ入力信号と基準電圧とを比較判定して上位ビット側のデジタル信号を生成する上位側の変換部と、アナログ入力信号をサンプリングし、サンプリングしたアナログ入力信号と前記上位ビット側のデジタル信号を再びアナログ信号にした値と前記上位側の変換部の比較判定結果とに基づいて、下位ビット側のデジタル信号を生成する下位側の変換部と、前記各変換部が生成したデジタル信号を合成しアナログ入力信号をデジタル出力信号とする出力部とを備えたA/D変換器であって、前記下位側の変換部は、前記上位側の変換部がサンプリングを終了するまでの間にサンプリングを開始し、かつ前記上位側の変換部の比較判定動作中にサンプリングを終了することを要旨としている。

【0016】

請求項4では、前記下位側の変換部は、前記上位ビット側のデジタル信号が示す電位の範囲を拡大した範囲から下位ビット側のデジタル信号を生成することを要旨としている。

【0017】

請求項5では、前記下位側の変換部は、前記上位ビット側のデジタル信号が示す電位を拡大した値を前記下位側基準電圧として設定することを要旨としている。

【0018】

請求項1に記載の発明によれば、上位側の変換部1では、アナログ入力信号がサンプリングされ、上位ビット側のデジタル信号が生成される。下位側の(精密)変換部2では、上位側の変換部1のデジタル信号を生成する動作中にサンプリングする動作が行なわれ、アナログ入力信号がサンプリングされる。そして、そのサンプリングしたアナログ入力信号と上位側の変換部の処理結果に基づいて下位ビット側のデジタル信号が生成される。出力部3では、両変換部1, 2が生成したデジタル信号が合成されデジタル出力信号が生成される。

【0019】

請求項2に記載の発明によれば、上位側の変換部では、アナログ入力信号がサンプリングされ、サンプリングしたアナログ入力信号と基準電圧とが比較判定されて上位ビット側のデジタル信号が生成される。下位側の変換部では、上位側の変換部の比較判定動作中にサンプリングする動作が行なわれ、アナログ入力信号がサンプリングされる。又、上位側の変換部の比較判定結果に基づいて下位側基準電圧が設定される。そして、サンプリングしたアナログ入力信号と下位側基準電圧とが比較判定されて下位ビット側のデジタル信号が生成される。出力部では、両変換部が生成したデジタル信号が合成されデジタル出力信号が生成される。

【0020】

請求項3に記載の発明によれば、上位側の変換部では、アナログ入力信号がサンプリングされ、サンプリングしたアナログ入力信号と基準電圧とが比較判定されて上位ビット側のデジタル信号が生成される。下位側の変換部では、上位側の変換部の比較判定動作中にサンプリングする動作が継続され、アナログ入力信号がサンプリングされる。又、そのサンプリングしたアナログ入力信号と前記上位ビット側のデジタル信号を再びアナログ信号にした値と前記上位側の変換部の比較判定結果とに基づいて、下位ビット側のデジタル信号が生成される。出力部では、両変換部が生成したデジタル信号が合成されデジタル出力信号が生成される。

【0021】

請求項4に記載の発明によれば、前記下位側の変換部では、前記上位ビット側のデジタル信号が示す電位の範囲を拡大した範囲から下位ビット側のデジタル信号が生成される。

【0022】

請求項5に記載の発明によれば、前記下位側の変換部では、前記上位ビット側のデジタル信号が示す電位を拡大した値が前記下位側基準電圧として設定される。

10

20

30

40

50

## 【0023】

## 【発明の実施の形態】

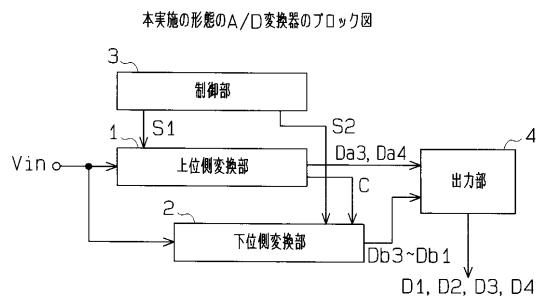

以下、本発明を4ビットのA/D変換器に具体化した一実施の形態を図2～図6に従って説明する。

## 【0024】

図2は、A/D変換器のブロック図を示す。A/D変換器は、上位側変換部1、精密変換部としての下位側変換部2、制御部3及び出力部4から構成されている。

## 【0025】

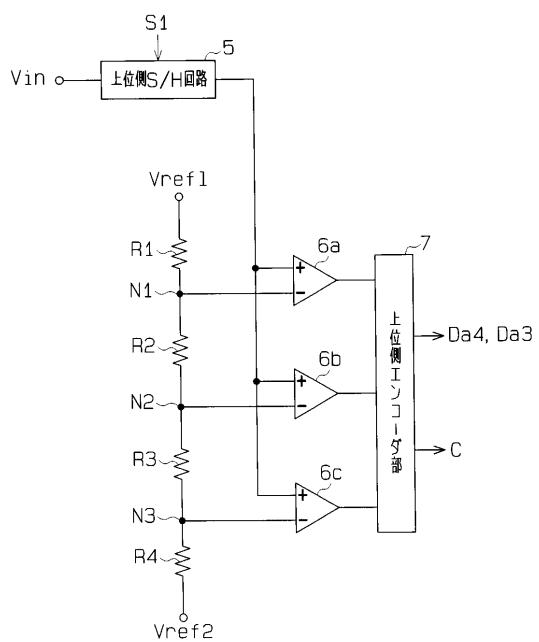

上位側変換部1は、図3に示すように、抵抗ラダーを構成する直列に接続された4つの抵抗R1～R4を備えている。抵抗R1～R4は同一抵抗値である。抵抗R1側の端部には高電位側の基準電圧Vref1が供給され、抵抗R4側の端部には低電位側の基準電圧Vref2が供給される。

10

## 【0026】

従って、前記抵抗R1～R4間の各ノードN1～N3では、基準電圧Vref1と同Vref2の電位差を4等分した電位が生成される。

上位側サンプルホールド回路(以下、上位側S/H回路という)5には、アナログ入力信号Vinが入力される。上位側S/H回路5は、制御部3から出力されるサンプリングパルス信号S1に基づいてアナログ入力信号Vinの瞬時値をサンプリングする。詳述すると、サンプリングパルス信号S1の立ち上がりに基づいて上位側S/H回路5に備えられるコンデンサの充電又は放電動作を開始し、同パルス信号S1のパルス幅に基づいた時間だけ充電又は放電動作を行なう。

20

## 【0027】

上位側S/H回路5はサンプリングパルス信号S1が立ち下がると、前記サンプリングした瞬時値をホールドする。

従って、3個の比較器6a～6cの一方の入力端子には上位側S/H回路5がサンプリングした瞬時値が入力される。

## 【0028】

前記比較器6aの他方の入力端子はノードN1に接続され、前記比較器6bの他方の入力端子はノードN2に接続され、前記比較器6cの他方の入力端子はノードN3に接続されている。

30

## 【0029】

従って、比較器6a～6cはアナログ入力信号Vinをサンプリングした瞬時値と基準電圧Vref1と同Vref2の電位差を4等分した電位とをそれぞれ比較して、その比較結果信号を上位側エンコーダ部7に出力する。

## 【0030】

上位側エンコーダ部7は比較器6a～6cの比較結果信号に基づいて、上位側2ビットのデジタル信号Da4, Da3を出力部4に出力する。又、上位側データ出力回路は比較器6a～6cの比較結果信号に基づいて、下位側変換部2の比較基準電圧を設定するための基準電圧設定信号Cを下位側変換部2に出力する。

40

## 【0031】

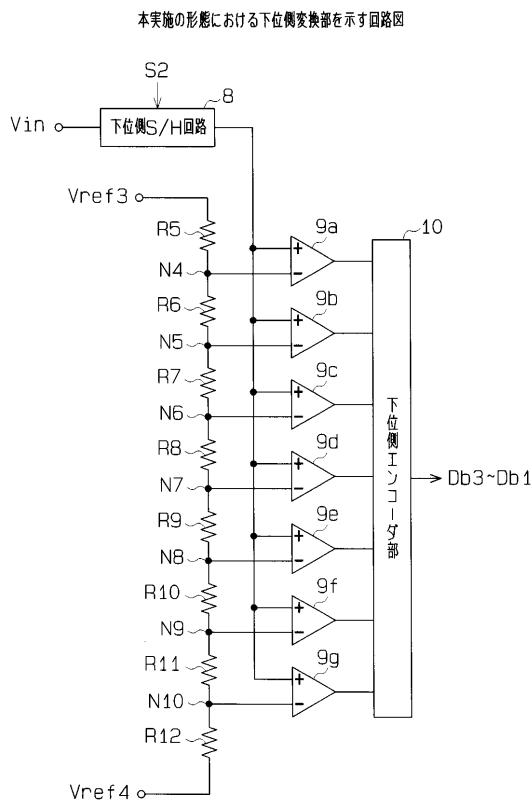

下位側変換部2は、図4に示すように、抵抗ラダーを構成する直列に接続された8つの抵抗R5～R12を備えている。抵抗R5～R12は同一抵抗値である。

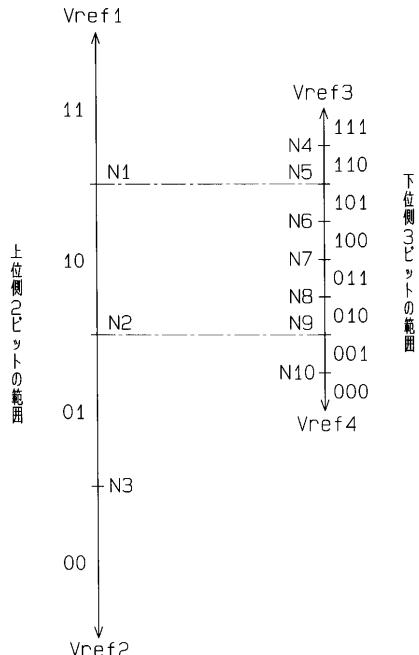

## 【0032】

抵抗R5側の端部には上位側変換部1の基準電圧設定信号Cに基づいて設定される高電位側の基準電圧Vref3が供給され、抵抗R12側の端部には同様に設定される低電位側の基準電圧Vref4が供給される。

## 【0033】

従って、前記抵抗R5～R12間の各ノードN4～N10では、基準電圧Vref3と同Vref4の電位差を8等分した電位が生成される。

基準電圧Vref3, Vref4は、例えば図5に示すように、上位側変換部1のデジタル信号D

50

a 4 , D a 3 が「10」となる場合、ノードN 1 とノードN 2 の電位差を高電位側及び低電位側に1.5倍ずつ拡大した値に設定される。

【0034】

下位側サンプルホールド回路（以下、下位側S / H回路という）8には、アナログ入力信号V inが入力される。下位側S / H回路8は、制御部3から出力されるサンプリングパルス信号S 2に基づいてアナログ入力信号V inの瞬時値をサンプリングする。詳述すると、サンプリングパルス信号S 2の立ち上がりに基づいて下位側S / H回路8に備えられるコンデンサの充電又は放電動作を開始し、同パルス信号S 2のパルス幅に基づいた時間だけ充電又は放電動作を行なう。

【0035】

下位側S / H回路8はサンプリングパルス信号S 2が立ち下がると、前記サンプリングした瞬時値をホールドする。

従って、7個の比較器9a ~ 9gの一方の入力端子には下位側S / H回路8がサンプリングした瞬時値が入力される。

【0036】

前記比較器9a ~ 9gの他方の入力端子はそれぞれ前記ノードN 4 ~ N 10に接続されている。

従って、比較器9a ~ 9gはアナログ入力信号V inをサンプリングした瞬時値と基準電圧V ref3と同V ref4の電位差を8等分した電位とをそれぞれ比較して、その比較結果信号を下位側エンコーダ部10に出力する。

【0037】

下位側エンコーダ部10は比較器9a ~ 9gの比較結果信号に基づいて、下位側3ビットのデジタル信号D b 3 ~ D b 1を出力部4に出力する。

出力部4は、上位側変換部1のデジタル信号D a 4 , D a 3及び、下位側変換部2のデジタル信号D b 3 ~ D b 1が入力されると、両デジタル信号D a 4 , D a 3 , D b 3 ~ D b 1を加算して4ビットのデータを求める。尚、この場合、最上位ビットから2番目のデジタル信号D a 3及びデジタル信号D b 3のみオーバーラップしている数値なので、その最上位ビットから2番目のビット以上の数値について2進数の加算を行えばよいことになる。

【0038】

ここで、基準電圧V ref4は、デジタル信号D a 4 , D a 3が示す電位の範囲を低電位側に1.5倍ずつ拡大した値に設定されるため、下位側変換部2から出力されるデジタル信号D b 3 ~ D b 1は、上位側2ビットのデジタル信号D a 4 , D a 3から「0010」を減算した値が基準値「000」となる数値である。従って、デジタル信号D a 4 , D a 3 , D b 3 ~ D b 1を加算した4ビットのデータは、デジタル出力信号D 4 ~ D 1に「0010」を余分に加算した値となる。

【0039】

従って、出力部4は、前記求めた4ビットのデータから「0010」を減算して4ビットのデジタル出力信号D 4 ~ D 1を生成し出力する。

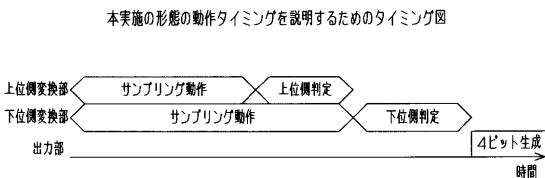

次に、上記のようなA / D変換器の動作を図6に従って説明する。

【0040】

上位側及び下位側変換部1 , 2の両S / H回路5 , 8には、制御部3から同時に立ち上がるサンプリングパルス信号が入力される。上位側変換部1のS / H回路5は、従来と同様のサンプリング時間でアナログ入力信号V inの瞬時値をサンプリングし、ホールドする。すると、上位側変換部1は、上位側2ビットのデジタル信号D a 4 , D a 3の粗判定（上位側判定）を行なう。

【0041】

下位側変換部2のS / H回路8は、上位側変換部1の上位側判定中もサンプリング動作を継続し、従来より長いサンプリング時間でアナログ入力信号V inの瞬時値をサンプリングし、ホールドする。詳述すると、制御部3から出力されるサンプリングパルス信号S 2は

10

20

30

40

50

上位側判定の終了時に立ち下がり、S / H回路8は上位側判定の終了時までサンプリング動作を行なう。

【0042】

すると、下位側変換部2は、下位側3ビットのデジタル信号D<sub>b3</sub>～D<sub>b1</sub>の密判定（下位側判定）を行なう。

ここで、下位側変換部2のS / H回路8は、上位側判定の終了時までサンプリング動作を行なっているため、アナログ入力信号V<sub>in</sub>の瞬時値を精密にサンプリングする。従って、下位側変換部2は密判定（下位側判定）を精度良く行なうことができる。

【0043】

出力部4はデジタル信号D<sub>a4</sub>，D<sub>a3</sub>，D<sub>b3</sub>～D<sub>b1</sub>が入力されると、4ビットのデジタル出力信号D<sub>4</sub>～D<sub>1</sub>を生成し出力する。 10

上記のように構成されたA / D変換器では、次に示す作用効果を得ることができる。

【0044】

（1）本実施の形態では、上位側変換部1のS / H回路5は従来と同様のサンプリング時間でアナログ入力信号V<sub>in</sub>の瞬時値をサンプリングし、下位側変換部2のS / H回路8は上位側変換部1が上位側判定を行なっているときもサンプリング動作を継続するようにした。従って、アナログ入力信号V<sub>in</sub>を出力する外部回路の出力インピーダンスが高い場合等でも、下位側変換部2のS / H回路8はアナログ入力信号V<sub>in</sub>の瞬時値を精密にサンプリングすることができる。従って、下位側変換部2は密判定（下位側判定）を精度良く行なうことができる。その結果、このA / D変換器では、入力インピーダンスを実質的に高くすることができるので、アナログ入力信号V<sub>in</sub>を出力する外部回路の出力インピーダンスが高い場合等に、外部回路にドライバー回路を付加しなくても、変換速度を低下させることなく、変換精度を向上させることができる。 20

【0045】

（2）本実施の形態では、基準電圧V<sub>ref3</sub>，V<sub>ref4</sub>は、デジタル信号D<sub>a4</sub>，D<sub>a3</sub>が示す電位の範囲を高電位側及び低電位側に1.5倍に拡大した値に設定した。従って、下位側変換部2のデジタル信号D<sub>b3</sub>～D<sub>b1</sub>は、上位側2ビットのデジタル信号D<sub>a4</sub>，D<sub>a3</sub>から「0010」を減算した値から、上位側2ビットのデジタル信号D<sub>a4</sub>，D<sub>a3</sub>から「0010」を加算した値までの範囲の密判定結果を示す信号となる。その結果、デジタル信号D<sub>a4</sub>，D<sub>a3</sub>の補正をしながら正確な4ビットのデジタル出力信号D<sub>4</sub>～D<sub>1</sub>を生成することができる。 30

【0046】

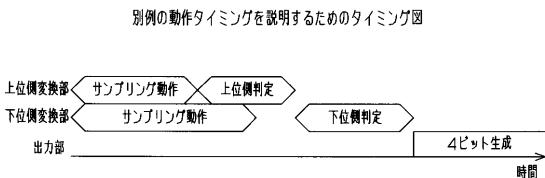

上記実施の形態は以下のように変更して実施してもよい。

図7に示すように、上位側変換部1のS / H回路5は、従来より短いサンプリング時間でサンプリングし、下位側変換部2のS / H回路8は、上位側変換部1の上位側判定中もサンプリング動作を継続し、従来と同様のサンプリング時間でサンプリングするようにしてもよい。そして、アナログ入力信号V<sub>in</sub>を出力する外部回路の出力インピーダンスが高い場合等には、外部回路にドライバー回路を付加する。このようにすると、下位側変換部2のS / H回路8はアナログ入力信号V<sub>in</sub>の瞬時値を精密にサンプリングすることができる。従って、下位側変換部2は密判定（下位側判定）を精度良く行なうことができる。そして、上位側変換部1のサンプリング時間を従来より短くしたため、上位側判定及び下位側判定も従来より速く終了し、4ビットのデジタル出力信号D<sub>4</sub>～D<sub>1</sub>を従来より速く生成することができる。 40

【0047】

上記実施の形態では、S / H回路8は上位側判定の終了時までサンプリング動作を行なうとしたが、アナログ入力信号V<sub>in</sub>の瞬時値を精密にサンプリングすることができるまでサンプリング動作を行なえば、上位側判定の終了時までサンプリング動作を行なわなくてよい。

【0048】

上記実施の形態では、上位側及び下位側変換部1，2の2つの変換部を備えたものとし 50

たが、例えば上位側、中位側及び下位側変換部の3つの変換部を備えたもの等、いくつの変換部を備えたものであってもよい。この場合、例えば、最上位側の変換部のみサンプリング時間を短くし、下位側の変換部は最上位側の比較判定動作時にもサンプリング動作を継続する等、少なくとも1つの下位側の変換部が上位側の変換部の比較判定動作時もサンプリングするようにすればよい。

【0049】

基準電圧  $V_{ref3}$ ,  $V_{ref4}$ は、デジタル信号  $D_{a4}$ ,  $D_{a3}$  が示す電位の範囲を高電位側及び低電位側に1.25倍に拡大した値、高電位側にのみ1.5倍拡大した値等、上位側のデジタルデータ信号  $D_{a4}$ ,  $D_{a3}$  の補正を必要とする方向に必要な値まで拡大して変更してもよい。また、拡大しなくてもよい。

10

【0050】

上記実施の形態では、上位側変換部1の比較判定結果に基づいて基準電圧  $V_{ref3}$ ,  $V_{ref4}$ を設定し、下位側判定を行なうA/D変換器としたが、変換部を2つ以上もつ他の種のA/D変換器に実施してもよい。

【0051】

例えば、下位側変換部は、上位側変換部で生成されたデジタル信号を再びアナログ化し、下位側S/H回路がサンプリングしたアナログ信号の瞬時値から再びアナログ化した信号を比較器にて減算し、その減算したアナログ信号を基準電圧と比較し下位側のデジタル信号とするA/D変換器に実施してもよい。この場合も上記実施の形態と同様に、上位側変換部の上位側判定時に下位側S/H回路のサンプリング動作を継続させるようにすれば、上記実施の形態と同様の効果を得ることができる。

20

【0052】

上記実施の形態では、4ビットのA/D変換器に具体化したが、例えば8ビット、16ビット等、何ビットのA/D変換器に具体化してもよい。

【0053】

【発明の効果】

以上詳述したように本発明によれば、A/D変換器の回路構成を変更することなく、入力インピーダンスを実質的に上昇させることにより、アナログ信号出力回路の回路面積の縮少、あるいはサンプリング時間の短縮によるA/D変換速度の向上を図り得るA/D変換器を提供することができる。

30

【図面の簡単な説明】

【図1】本発明の原理説明図。

【図2】本実施の形態のA/D変換器のブロック図。

【図3】本実施の形態における上位側変換部を示す回路図。

【図4】本実施の形態における下位側変換部を示す回路図。

【図5】下位側変換部における基準電圧を説明するための説明図。

【図6】本実施の形態の動作タイミングを説明するためのタイミング図。

【図7】別例の動作タイミングを説明するためのタイミング図。

【図8】従来の動作タイミングを説明するためのタイミング図。

【符号の説明】

40

1 上位側の変換部（上位側変換部）

2 下位側の精密変換部（下位側変換部）

3 出力部

【図1】

【図2】

【図3】

本実施の形態における上位側変換部を示す回路図

【図4】

【図5】

下位側変換部における基準電圧を説明するための説明図

【図6】

【図8】

【図7】

---

フロントページの続き

(56)参考文献 特開平2 - 94816 (JP, A)

特開平6 - 291660 (JP, A)

特開平7 - 7425 (JP, A)

特開平2 - 94816 (JP, A)

特開平6 - 132824 (JP, A)

特開平4 - 129424 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H03M1/00-1/88