(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3804907号

(P3804907)

(45) 発行日 平成18年8月2日(2006.8.2)

(24) 登録日 平成18年5月19日(2006.5.19)

(51) Int.C1.

F 1

G 11 C 11/22 (2006.01)

G 11 C 11/22 501A

G 11 C 11/22 501Z

請求項の数 10 (全 14 頁)

(21) 出願番号 特願平11-375671

(22) 出願日 平成11年12月28日(1999.12.28)

(65) 公開番号 特開2001-189082(P2001-189082A)

(43) 公開日 平成13年7月10日(2001.7.10)

審査請求日 平成15年12月19日(2003.12.19)

(73) 特許権者 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1番

1号

(74) 代理人 100104190

弁理士 酒井 昭徳

(72) 発明者 竹島 徹

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

(72) 発明者 野呂 幸一

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

審査官 須原 宏光

最終頁に続く

(54) 【発明の名称】半導体記憶装置

## (57) 【特許請求の範囲】

## 【請求項1】

残留分極によってデータを保持する複数の第1の強誘電体記憶素子、および製造段階においてデータを書き込むための、前記第1の強誘電体記憶素子よりも容量の大きい第2の強誘電体記憶素子を備えたメモリセルアレイと、

前記メモリセルアレイに対して行方向の選択をおこなうための複数の行選択線と、

前記メモリセルアレイに対して列方向の選択をおこなうための複数の列選択線と、

を具備し、

前記第2の強誘電体記憶素子は、複数の前記第1の強誘電体記憶素子により構成されることを特徴とする半導体記憶装置。

## 【請求項2】

前記第2の強誘電体記憶素子を構成する複数の前記第1の強誘電体記憶素子に対応した複数の行選択線が短絡されることを特徴とする請求項1に記載の半導体記憶装置。

## 【請求項3】

短絡される複数の行選択線を選択するための選択回路をさらに備えたことを特徴とする請求項2に記載の半導体記憶装置。

## 【請求項4】

短絡される複数の行選択線を選択するためのプログラムを記憶した記憶手段と、

前記プログラムに基づいて、短絡対象となる複数の行選択線を選択するための選択信号を生成して前記選択回路に供給する制御手段と、

をさらに備えたことを特徴とする請求項 3 に記載の半導体記憶装置。

【請求項 5】

前記第 2 の強誘電体記憶素子を構成する複数の前記第 1 の強誘電体記憶素子に対応した複数の列選択線が短絡されることを特徴とする請求項 1 に記載の半導体記憶装置。

【請求項 6】

短絡される複数の列選択線を選択するための選択回路をさらに備えたことを特徴とする請求項 5 に記載の半導体記憶装置。

【請求項 7】

短絡される複数の行選択線を選択するためのプログラムを記憶した記憶手段と、

前記プログラムに基づいて、短絡対象となる複数の行選択線を選択するための選択信号 10 を生成して前記選択回路に供給する制御手段と、

をさらに備えたことを特徴とする請求項 6 に記載の半導体記憶装置。

【請求項 8】

残留分極によってデータを保持する複数の第 1 の強誘電体記憶素子、および製造段階においてデータを書き込むための、前記第 1 の強誘電体記憶素子よりも容量の大きい第 2 の強誘電体記憶素子を備えたメモリセルアレイと、

前記メモリセルアレイに対して行方向の選択をおこなうための複数の行選択線と、

前記メモリセルアレイに対して列方向の選択をおこなうための複数の列選択線と、

を具備し、

前記第 1 の強誘電体記憶素子は複数の強誘電体キャパシタを有しており、

前記第 2 の強誘電体記憶素子は、前記第 1 の強誘電体記憶素子に含まれる複数の前記強誘電体キャパシタを並列に接続した構成となっていることを特徴とする半導体記憶装置。

【請求項 9】

残留分極によってデータを保持する複数の第 1 の強誘電体記憶素子、および製造段階においてデータを書き込むための、前記第 1 の強誘電体記憶素子よりも容量の大きい第 2 の強誘電体記憶素子を備えたメモリセルアレイと、

前記メモリセルアレイに対して行方向の選択をおこなうための複数の行選択線と、

前記メモリセルアレイに対して列方向の選択をおこなうための複数の列選択線と、

を具備し、

前記第 1 の強誘電体記憶素子は複数の強誘電体キャパシタを有しており、

前記第 2 の強誘電体記憶素子は、前記第 1 の強誘電体記憶素子の隣接するメモリセルに含まれる複数の前記強誘電体キャパシタを並列に接続した構成になっていることを特徴とする半導体記憶装置。

【請求項 10】

残留分極によってデータを保持する複数の第 1 の強誘電体記憶素子、および前記第 1 の強誘電体記憶素子よりも容量の大きい第 2 の誘電体記憶素子を備え、

製造段階において、前記第 2 の強誘電体記憶素子にデータを記憶させることを特徴とする半導体記憶装置におけるデータ記憶方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、半導体記憶装置、特に不揮発性強誘電体メモリ (Ferroelectric RAM、以下 F R A M とする) に関する。F R A M は、D R A M のキャパシタ部分に強誘電体を用いたものであり、そのキャパシタ部分の残留分極によってデータを記憶するため、データ保持のための電源を設けなくてもデータを保持することができる。そのため、たとえば、I C カードなどにおいて暗号や機密性の高いコードなど (以下、暗号等とする) を記憶させるのに F R A M が使用されることがある。

【0002】

【従来の技術】

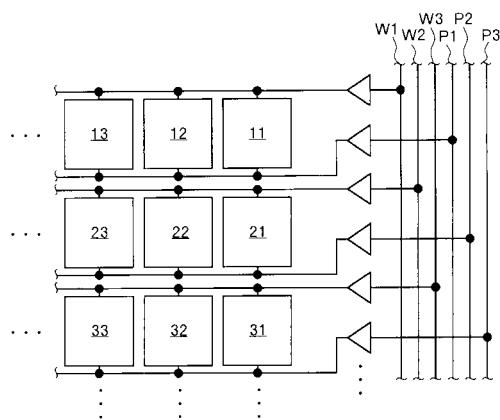

図 9 は、従来の F R A M において、メモリセルとワード線およびプレート線との接続状態 50

を模式的に示す図である。また、図10は、従来のF R A Mにおいて、メモリセルとピット線との接続状態を模式的に示す図である。

【0003】

図9に示すように、従来のF R A Mでは、ワード線Wとプレート線Pとからなる行選択線対と、行方向のメモリセル群（以下、メモリセル行とする）とは、1対1の関係で接続されている。つまり、図9において、第1番目の行選択線対W1, P1は第1行目のメモリセル11, 12, 13, …に接続される。第2番目の行選択線対W2, P2は第2行目のメモリセル21, 22, 23, …に接続される。第3番目の行選択線対W3, P3は第3行目のメモリセル31, 32, 33, …に接続される。

【0004】

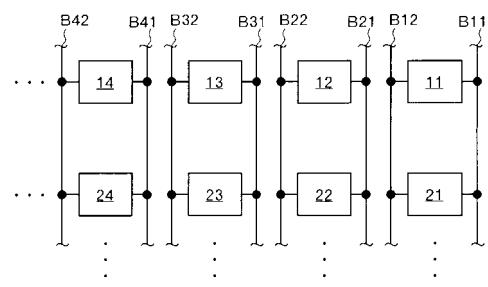

また、図10に示すように、従来のF R A Mでは、一対のピット線B, Bからなる列選択線対と、列方向のメモリセル群（以下、メモリセル列とする）とは、1対1の関係で接続されている。つまり、図10において、第1番目の列選択線対B11, B12は第1列目のメモリセル11, 21, …に接続される。第2番目の列選択線対B21, B22は第2列目のメモリセル12, 22, …に接続される。第3番目の列選択線対B31, B32は第3列目のメモリセル13, 23, …に接続される。第4番目の列選択線対B41, B42および第4列目のメモリセル14, 24, …についても同様である。

【0005】

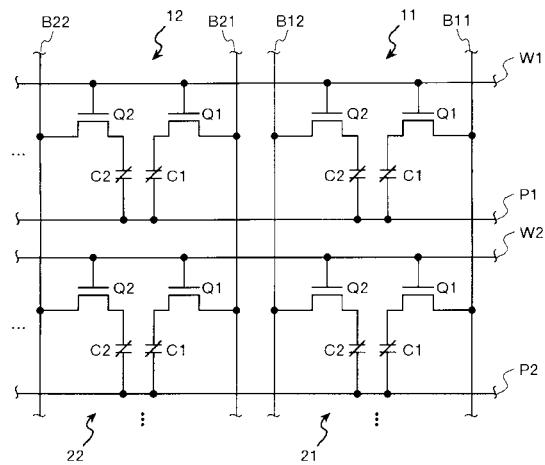

たとえば、メモリセルが2個のトランジスタと2個の強誘電体素子（強誘電体キャパシタ）で構成されているF R A Mの場合、各メモリセルは、図11に示すような構成となる。すなわち、各メモリセル11, 12, …, 21, 22, …内の2個の強誘電体素子C1, C2は、それぞれ、その一端を別々のトランジスタQ1, Q2に接続し、他端をプレート線P1, P2に接続した構成となっている。

【0006】

一般に、F R A Mを製造するにあたって、その製造プロセスのウエハ段階で強誘電体による記憶素子に対する暗号等の書き込みをおこなう必要がある。これは、完成したF R A Mチップのパッケージを回路基板に実装した後に書き込みをおこなうのは、機密保護上好ましくないからである。

【0007】

ところで、強誘電体素子は、熱や水素等の外部的要因により素子特性の劣化を生じることが知られている。したがって、ウエハ段階で強誘電体記憶素子に暗号等を書き込んでも、その後の製造プロセスにおいて強誘電体素子が熱の影響を受けたり水素等にさらされたりすると、素子特性の劣化により記憶情報が消失してしまうおそれがある。記憶情報の消失は、信頼性の点で極めて重大な問題である。そこで、従来は、製造プロセスにおいて、熱や水素等の外部的要因を極力排除するように配慮がなされている。

【0008】

【発明が解決しようとする課題】

しかしながら、上述したように、従来は、製造プロセスにおいて、熱や水素等の外部的要因を極力排除する必要があるため、製造プロセスに制約が生じるという問題点がある。また、通常のD R A M等の製造設備と異なり、熱や水素等の影響を排除するための設備が必要となるため、製造コストが上昇する。したがって、F R A Mのパッケージが高価になるという問題点がある。

【0009】

本発明は、上記問題点に鑑みてなされたものであって、製造段階で熱や水素等の影響を受けても記憶情報を保持しつづける強誘電体記憶素子を備えた半導体記憶装置を提供することを目的とする。

【0010】

【課題を解決するための手段】

上記目的を達成するため、本発明は、強誘電体記憶素子を備えた半導体記憶装置において、基板実装後にデータを書き込むための第1の強誘電体記憶素子と、その第1の強誘電体

10

20

30

40

50

記憶素子よりも容量の大きい第2の強誘電体記憶素子を設け、その第2の強誘電体記憶素子を、製造段階において暗号等を書き込むための記憶素子として用いるものである。

【0011】

強誘電体素子の特性はその容量の大小によって決まる。したがって、製造段階において、容量がより大きい第2の強誘電体記憶素子に暗号等を書き込めば、製造中に強誘電体素子が熱の影響を受けたり水素等にさらされても、記憶情報が消失してしまうほどには素子の特性が劣化しないので、製造終了後においても記憶情報を保持しつづけることができる。

【0012】

ここで、第2の強誘電体記憶素子は、複数の第1の強誘電体記憶素子を組み合わせることによって構成されていてもよい。また、第1の強誘電体記憶素子が複数の強誘電体キャパシタ（強誘電体素子）を備えている場合には、その第1の強誘電体記憶素子に含まれる複数の強誘電体キャパシタを並列に接続することによって第2の強誘電体記憶素子が構成されていてもよい。このようにすれば、第2の強誘電体記憶素子の容量を第1の強誘電体記憶素子の容量よりも大きくすることができる。

【0013】

具体的には、複数の第1の強誘電体記憶素子によって第2の強誘電体記憶素子を構成する場合、複数の行選択線（ワード線、プレート線）または複数の列選択線（ビット線）を短絡する。そうすれば、行選択線（ワード線、プレート線）が短絡された複数の第1の強誘電体記憶素子には、同じ情報が書き込まれることになるため、第2の強誘電体記憶素子に書き込まれた情報は、第1の強誘電体記憶素子に書き込まれる場合の複数倍の容量を有する強誘電体記憶素子で保持されることになる。したがって、製造中に強誘電体記憶素子が熱や水素等の影響を受けても記憶情報を保持しつづけることができる。列選択線（ビット線）を短絡した場合も同様である。

【0014】

また、選択回路を設け、その選択回路により、短絡させる行選択線（ワード線、プレート線）または列選択線（ビット線）を選択する構成としてもよい。そうすれば、短絡させる行選択線（ワード線、プレート線）または列選択線（ビット線）を、書き込む暗号等のデータ量などに応じて変更することができる。

【0015】

さらに、ROM等の記憶手段（プログラム格納部）に、短絡させる行選択線（ワード線、プレート線）または列選択線（ビット線）を選択するためのプログラムを格納し、そのプログラムに基づいて、短絡対象となる複数の行選択線（ワード線、プレート線）または列選択線（ビット線）を選択する制御手段（プログラムコントロール回路）を設けた構成としてもよい。そうすれば、短絡させる行選択線（ワード線、プレート線）または列選択線（ビット線）をプログラムブルに選択することができる。

【0016】

【発明の実施の形態】

以下に、本発明にかかる半導体記憶装置の実施の形態について図面を参照しつつ詳細に説明する。

【0017】

（実施の形態1）

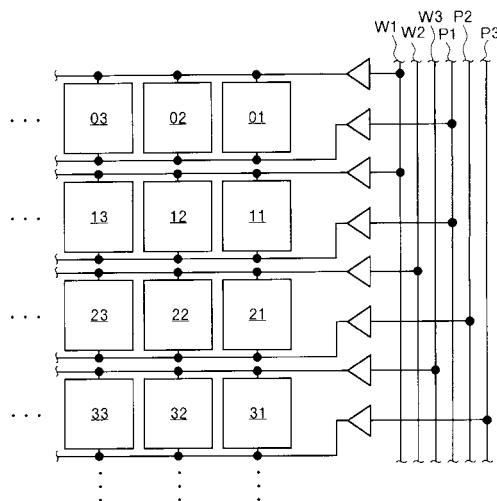

図1は、実施の形態1にかかる半導体記憶装置において、メモリセルとワード線およびプレート線との接続状態を模式的に示す図である。この半導体記憶装置は、たとえば、第1の強誘電体記憶素子として複数のメモリセル01, 02, ..., 11, 12, ..., 21, 22, ..., 31, 32, ...を備えている。第1行目のメモリセル行と第2行目のメモリセル行は、第1番目のワード線W1および第1番目のプレート線P1に共通接続されている。

【0018】

したがって、第1行目のメモリセル行と第2行目のメモリセル行において、同じ列に配置されたメモリセル対が、それぞれ単独の場合よりも容量が大きい第2の強誘電体記憶素子を構成していることになる。すなわち、図示例では、第1行第1列目（図に示すメモリセ

10

20

20

30

40

50

ルアレイにおいて右上)のメモリセル01と第2行第1列目のメモリセル11によって、第1列目の第2の強誘電体記憶素子が構成されている。

【0019】

同様に、第1行第2列目のメモリセル02と第2行第2列目のメモリセル12によって、第2列目の第2の強誘電体記憶素子が構成されている。また、第1行第3列目のメモリセル03と第2行第3列目のメモリセル13によって、第3列目の第2の強誘電体記憶素子が構成されている。図示省略したが、第4列目以降も同様である。

【0020】

第3行目のメモリセル行は、第2番目のワード線W2および第2番目のプレート線P2に接続されている。第4行目のメモリセル行は、第3番目のワード線W3および第3番目のプレート線P3に接続されている。第5行目以降も同様である。

10

【0021】

つぎに、実施の形態1にかかる半導体記憶装置の作用について説明する。第1番目のワード線W1および第1番目のプレート線P1は、第1行目のメモリセル行と第2行目のメモリセル行の両方に接続されている。そのため、第1番目のワード線W1および第1番目のプレート線P1により第1行目と第2行目のメモリセル行が同時に選択される。つまり、同じビット線に接続された第1行目のメモリセルと第2行目のメモリセルに対して同時にデータの書き込みまたは読み出しがおこなわれる。

【0022】

したがって、第1行目のメモリセルと第2行目のメモリセルに書き込まれた同一の情報は、単独のメモリセルの2倍の容量を有する強誘電体記憶素子で保持されることになる。したがって、製造段階において、その容量が2倍の強誘電体記憶素子に暗号等のデータを書き込めば、その暗号等のデータは通常の2倍の容量で保持されることになる。

20

【0023】

以上説明したように、実施の形態1によれば、製造段階において、暗号等のデータは、通常の強誘電体記憶素子の2倍の容量を有する強誘電体記憶素子に書き込まれるため、製造中に熱や水素等の影響を受けてもそのデータが消失してしまうほどには素子の特性が劣化しないので、製造終了後においても暗号等のデータを保持しつづけることができる。

【0024】

したがって、製造プロセスにおいて、熱や水素等の外部的要因を極力排除する必要がないので、製造プロセスの制約をなくすことができる。また、熱や水素等の影響を排除するための設備が不要となるため、製造コストを抑えることができるので、安価なF R A Mパッケージが得られる。また、ウエハの段階でID番号などを強誘電体メモリに記憶させることができることができる。

30

【0025】

(実施の形態2)

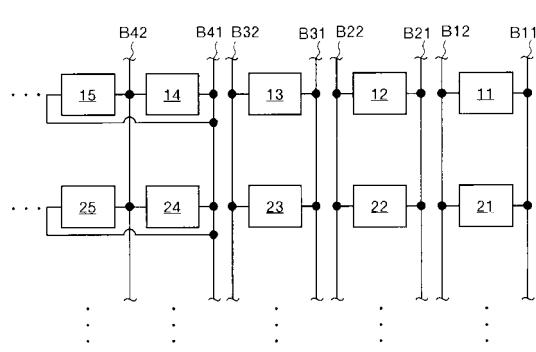

図2は、実施の形態2にかかる半導体記憶装置において、メモリセルとビット線との接続状態を模式的に示す図である。この半導体記憶装置は、たとえば、第1の強誘電体記憶素子として複数のメモリセル11, ..., 14, 15, ..., 21, ..., 24, 25, ...を備えている。第4列目のメモリセル列と第5列目のメモリセル列は、符号B41と符号B42で示す第4番目のビット線対に共通接続されている。

40

【0026】

したがって、第4列目のメモリセル列と第5列目のメモリセル列において、同じ行に配置されたメモリセル対が、それぞれ単独の場合よりも容量が大きい第2の強誘電体記憶素子を構成していることになる。すなわち、図示例では、第1行第4列目のメモリセル14と第1行第5列目(図に示すメモリセルアレイにおいて左上)のメモリセル15によって、第1行目の第2の強誘電体記憶素子が構成されている。同様に、第2行第4列目のメモリセル24と第2行第5列目のメモリセル25によって、第2行目の第2の強誘電体記憶素子が構成されている。また、第3行目以降も同様である。

【0027】

50

第1列目のメモリセル列は、第1番目のビット線対B11, B12に接続されている。第2列目のメモリセル列は、第2番目のビット線対B21, B22に接続されている。第3列目のメモリセル列は、第3番目のビット線対B31, B32に接続されている。第6列以降も同様である。

【0028】

実施の形態2にかかる半導体記憶装置の作用について説明する。第4番目のビット線対B41, B42は、第4列目のメモリセル列と第5列目のメモリセル列の両方に接続されている。そのため、第4番目のビット線対B41, B42により第4列目と第5列目のメモリセル列が同時に選択される。つまり、同じワード線およびプレート線に接続された第4列目のメモリセルと第5列目のメモリセルに対して同時にデータの書き込みまたは読み出しがおこなわれる。

【0029】

したがって、第4列目のメモリセルと第5列目のメモリセルに書き込まれた同一の情報は、単独のメモリセルの2倍の容量を有する強誘電体記憶素子で保持されることになる。したがって、製造段階において、その容量が2倍の強誘電体記憶素子に暗号等のデータを書き込めば、その暗号等のデータは通常の2倍の容量で保持されることになる。

【0030】

以上説明したように、実施の形態2によれば、製造段階において、暗号等のデータは、通常の強誘電体記憶素子の2倍の容量を有する強誘電体記憶素子に書き込まれるため、製造中に熱や水素等の影響を受けてもそのデータが消失してしまうほどには素子の特性が劣化しないので、製造終了後においても暗号等のデータを保持しつづけることができる。

【0031】

したがって、製造プロセスにおいて、熱や水素等の外部的要因を極力排除する必要がないので、製造プロセスの制約をなくすことができる。また、熱や水素等の影響を排除するための設備が不要となるため、製造コストを抑えることができるので、安価なF R A Mパッケージが得られる。

【0032】

(実施の形態3)

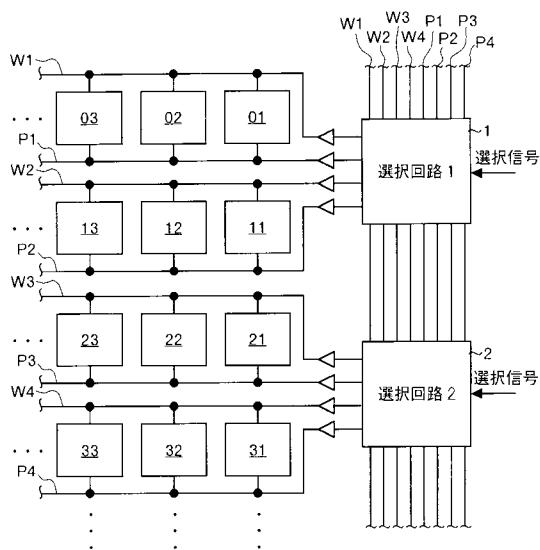

図3は、実施の形態3にかかる半導体記憶装置において、メモリセルとワード線およびプレート線との接続状態を模式的に示す図である。実施の形態3は、実施の形態1の半導体記憶装置において、短絡させるワード線およびプレート線を選択するための複数(図示例では2個だけ示されている)の選択回路1, 2, ...を備えたものである。

【0033】

すなわち、たとえば図示例では、第1番目のワード線W1および第1番目のプレート線P1は第1行目のメモリセル行に接続される。第2番目のワード線W2および第2番目のプレート線P2は第2行目のメモリセル行に接続される。そして、第1の選択回路1は、外部から入力する選択信号に基づいて、第1番目のワード線W1と第2番目のワード線W2、および第1番目のプレート線P1と第2番目のプレート線P2を同時に短絡させるか否かの選択をおこなう。

【0034】

また、第3番目のワード線W3および第3番目のプレート線P3は第3行目のメモリセル行に接続される。第4番目のワード線W4および第4番目のプレート線P4は第4行目のメモリセル行に接続される。そして、第2の選択回路2は、外部から入力する選択信号に基づいて、第3番目のワード線W3と第4番目のワード線W4、および第3番目のプレート線P3と第4番目のプレート線P4を同時に短絡させるか否かの選択をおこなう。第5行目のメモリセル行以降についても同様である。

【0035】

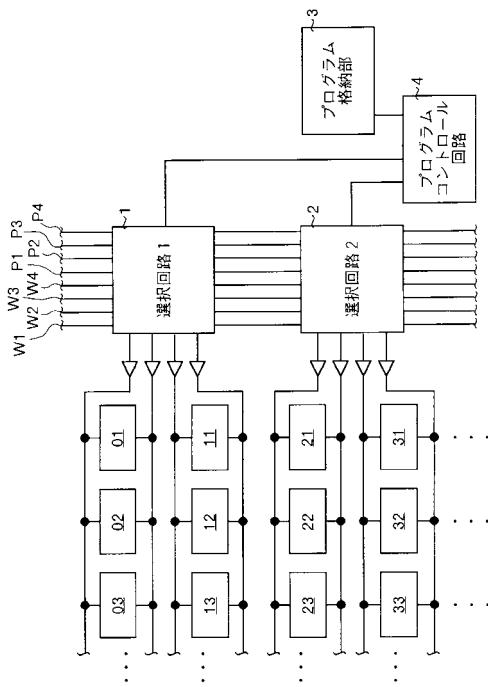

図4は、実施の形態3にかかる半導体記憶装置において、メモリセルとワード線およびプレート線との接続状態の他の例を模式的に示す図である。図4に示す例は、図3に示す半導体記憶装置において、記憶手段であるプログラム格納部3および制御手段であるプログ

10

20

30

40

50

ラムコントロール回路 4 を備え、短絡させるワード線 W の組およびプレート線 P の組をプログラマブルに選択することができる構成としたものである。

【 0 0 3 6 】

プログラム格納部 3 は、短絡させるワード線の組およびプレート線の組を選択するためのプログラムを格納する。プログラム格納部 3 は、ROM、EEPROM、FRAM、SRAM またはDRAMなどのメモリにより構成される。プログラムコントロール回路 4 、プログラム格納部 3 に格納されたプログラムに基づいて選択信号を生成し、対象となる選択回路 1, 2, ... へ出力する。各選択回路 1, 2, ... は、選択信号に応じてワード線 W の組およびプレート線 P の組の短絡動作をおこなう。

【 0 0 3 7 】

実施の形態 3 にかかる半導体記憶装置の作用について説明する。図 3 に示す例においては、外部から入力された選択信号に基づいて、いずれか 2 つのメモリセル行について、ワード線 W およびプレート線 P がともに短絡される。また、図 4 に示す例においては、プログラム格納部 3 に格納されたプログラムに基づいて、いずれか 2 つのメモリセル行について、ワード線 W およびプレート線 P がともに短絡される。

【 0 0 3 8 】

ワード線 W およびプレート線 P がともに短絡された 2 つのメモリセル行では、単独のメモリセル行における強誘電体容量の 2 倍の容量を有することになる。したがって、製造段階において、その容量が 2 倍の強誘電体記憶素子に暗号等のデータを書き込めば、その暗号等のデータは通常の 2 倍の容量で保持されることになる。

【 0 0 3 9 】

以上説明したように、実施の形態 3 によれば、実施の形態 1 と同様に、製造段階において書き込まれた暗号等のデータを製造終了後においても保持しつづけることができるという効果に加えて、その暗号等を書き込むための記憶領域を暗号等のデータ量などに応じてメモリセルアレイの中で変更することができる。また、選択回路 1, 2 が設けられていることによって、ワード線 W またはプレート線 P の配線経路をたどり難くなる。したがって、第三者がワード線 W またはプレート線 P の配線経路をたどって暗号等が書き込まれた記憶領域を調べ、不正に暗号等を取得してしまうのを防ぐことができる。つまり、機密性が高くなる。

【 0 0 4 0 】

( 実施の形態 4 )

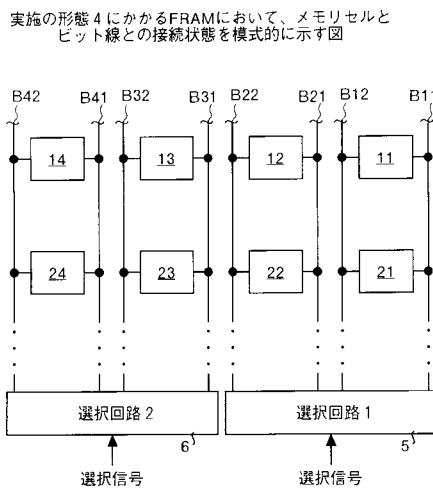

図 5 は、実施の形態 4 にかかる半導体記憶装置において、メモリセルとビット線との接続状態を模式的に示す図である。実施の形態 4 は、実施の形態 2 の半導体記憶装置において、短絡させるビット線対を選択するための複数 ( 図示例では 2 個だけ示されている ) の選択回路 5, 6, ... を備えたものである。

【 0 0 4 1 】

すなわち、たとえば図示例では、第 1 番目のビット線対 B 1 1, B 1 2 は第 1 列目のメモリセル列に接続される。第 2 番目のビット線対 B 2 1, B 2 2 は第 2 列目のメモリセル列に接続される。そして、第 1 の選択回路 5 は、外部から入力する選択信号に基づいて、第 1 番目のビット線対 B 1 1, B 1 2 の一方と第 2 番目のビット線対 B 2 1, B 2 2 の一方、および第 1 番目のビット線対 B 1 1, B 1 2 の他方と第 2 番目のビット線対 B 2 1, B 2 2 の他方を同時に短絡させるか否かの選択をおこなう。

【 0 0 4 2 】

また、第 3 番目のビット線対 B 3 1, B 3 2 は第 3 列目のメモリセル列に接続される。第 4 番目のビット線対 B 4 1, B 4 2 は第 4 列目のメモリセル列に接続される。そして、第 2 の選択回路 6 は、外部から入力する選択信号に基づいて、第 3 番目のビット線対 B 3 1, B 3 2 の一方と第 4 番目のビット線対 B 4 1, B 4 2 の一方、および第 3 番目のビット線対 B 3 1, B 3 2 の他方と第 4 番目のビット線対 B 4 1, B 4 2 の他方を同時に短絡させるか否かの選択をおこなう。第 5 列目のメモリセル列以降についても同様である。

【 0 0 4 3 】

10

20

30

40

50

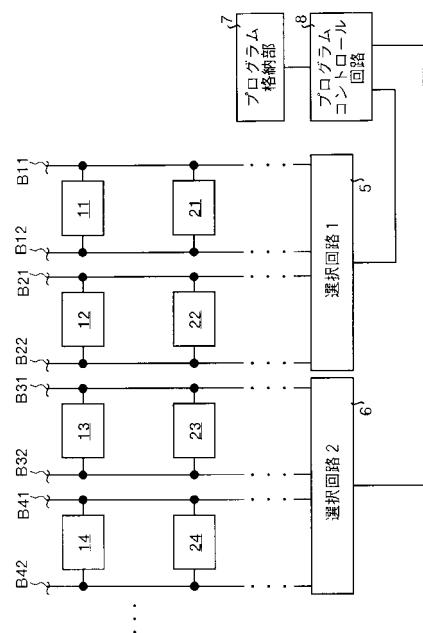

図6は、実施の形態4にかかる半導体記憶装置において、メモリセルとビット線対との接続状態の他の例を模式的に示す図である。図6に示す例は、図5に示す半導体記憶装置において、記憶手段であるプログラム格納部7および制御手段であるプログラムコントロール回路8を備え、短絡させるビット線対B<sub>1</sub>、B<sub>2</sub>の組をプログラマブルに選択することができる構成としたものである。

【0044】

プログラム格納部7は、短絡させるビット線対B<sub>1</sub>、B<sub>2</sub>の組を選択するためのプログラムを格納する。プログラム格納部7は、ROM、EEPROM、FRAM、SRAMまたはDRAMなどのメモリにより構成される。プログラムコントロール回路8は、プログラム格納部7に格納されたプログラムに基づいて選択信号を生成し、対象となる選択回路5<sub>1</sub>、6<sub>1</sub>、…へ出力する。各選択回路5<sub>1</sub>、6<sub>1</sub>、…は、選択信号に応じてビット線対B<sub>1</sub>、B<sub>2</sub>の組の短絡動作をおこなう。 10

【0045】

実施の形態4にかかる半導体記憶装置の作用について説明する。図5に示す例においては、外部から入力された選択信号に基づいて、いずれか2つのメモリセル列について、ビット線対B<sub>1</sub>、B<sub>2</sub>が短絡される。また、図6に示す例においては、プログラム格納部7に格納されたプログラムに基づいて、いずれか2つのメモリセル列について、ビット線対B<sub>1</sub>、B<sub>2</sub>が短絡される。

【0046】

ビット線対B<sub>1</sub>、B<sub>2</sub>がともに短絡された2つのメモリセル列では、単独のメモリセル列における強誘電体容量の2倍の容量を有することになる。したがって、製造段階において、その容量が2倍の強誘電体記憶素子に暗号等のデータを書き込めば、その暗号等のデータは通常の2倍の容量で保持されることになる。 20

【0047】

以上説明したように、実施の形態4によれば、実施の形態2と同様に、製造段階において書き込まれた暗号等のデータを製造終了後においても保持しつづけることができるという効果に加えて、その暗号等を書き込むための記憶領域を暗号等のデータ量などに応じてメモリセルアレイの中で変更することができる。

【0048】

また、選択回路5<sub>1</sub>、6<sub>1</sub>が設けられることによって、ビット線B<sub>1</sub>の配線経路をたどり難くなる。したがって、第三者がビット線B<sub>1</sub>の配線経路をたどって暗号等が書き込まれた記憶領域を調べ、不正に暗号等を取得してしまうのを防ぐことができる。つまり、機密性が高くなる。 30

【0049】

(実施の形態5)

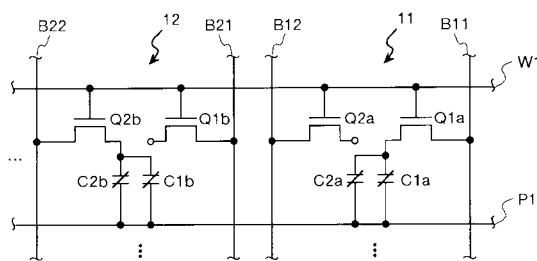

図7は、実施の形態5にかかる半導体記憶装置において、メモリセル内の強誘電体素子との接続状態を模式的に示す図である。実施の形態5は、たとえば図示例のように、各メモリセルに複数、たとえば2個の強誘電体素子(強誘電体キャパシタ)が設けられている場合、メモリセル1<sub>1</sub>において一方のトランジスタQ1<sub>a</sub>とプレート線P<sub>1</sub>との間に2個の強誘電体素子C1<sub>a</sub>、C2<sub>a</sub>を並列に接続するとともに、それに隣接するメモリセル1<sub>2</sub>において一方のトランジスタQ2<sub>b</sub>とプレート線P<sub>1</sub>との間に2個の強誘電体素子C1<sub>b</sub>、C2<sub>b</sub>を並列に接続したものである。 40

【0050】

メモリセル1<sub>1</sub>において強誘電体素子C2<sub>a</sub>ともう一方のトランジスタQ2<sub>a</sub>とは絶縁される。同様に、メモリセル1<sub>2</sub>において強誘電体素子C1<sub>b</sub>ともう一方のトランジスタQ1<sub>b</sub>とは絶縁される。このような構成とすることによって、メモリセル1<sub>1</sub>とメモリセル1<sub>2</sub>の2つのセルで、単独のメモリセルの場合の2倍の強誘電体容量を有する単一のメモリセルと同等になる。この2個のメモリセル1<sub>1</sub>、1<sub>2</sub>よりなるメモリセルに対しては、4本のビット線B1<sub>1</sub>、B1<sub>2</sub>、B2<sub>1</sub>、B2<sub>2</sub>のうちトランジスタQ1<sub>a</sub>に接続されたビット線B1<sub>1</sub>とトランジスタQ2<sub>b</sub>に接続されたビット線B2<sub>2</sub>が有効となる。 50

## 【0051】

以上説明したように、実施の形態5によれば、他の実施の形態と同様に、製造段階において書き込まれた暗号等のデータを製造終了後においても保持しつづけることができるという効果を有する。また、強誘電体容量が2倍の記憶領域におけるセル構造が、通常の容量の記憶領域におけるセル構造と見かけ上同じであるため、第三者が暗号等が書き込まれた記憶領域を調べ、不正に暗号等を取得してしまうのを防ぐことができる。つまり、機密性を向上させることができることになる。

## 【0052】

## (実施の形態6)

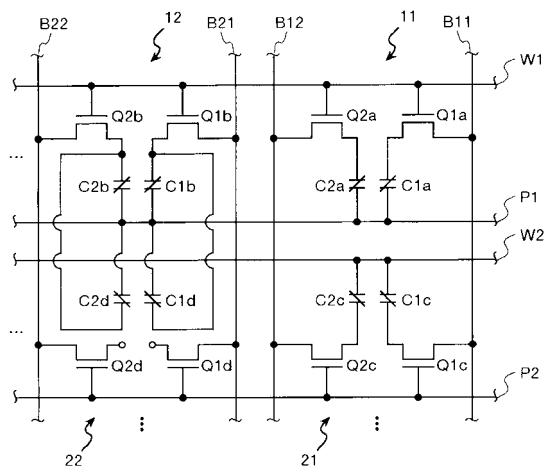

図8は、実施の形態6にかかる半導体記憶装置において、隣接するメモリセル間における強誘電体素子の接続状態を模式的に示す図である。実施の形態6は、各メモリセルに複数、たとえば2個の強誘電体素子(強誘電体キャパシタ)が設けられている場合、たとえば図示例のような構成としたものである。

10

## 【0053】

すなわち、メモリセル12の一方のトランジスタQ1bとプレート線P1との間に、メモリセル12内の強誘電体素子C1bと、メモリセル12に隣接する別のメモリセル22の強誘電体素子C1dとが並列に接続される。また、メモリセル12のもう一方のトランジスタQ2bとプレート線P1との間に、メモリセル12内の別の強誘電体素子C2bと、メモリセル22の別の強誘電体素子C2dとが並列に接続される。

## 【0054】

20

メモリセル22において、トランジスタQ1dと強誘電体素子C1dとは絶縁される。トランジスタQ2dと強誘電体素子C2dとは絶縁される。また、メモリセル22において、ワード線W2と強誘電体素子C1dおよび強誘電体素子C2dとは絶縁される。

## 【0055】

このような構成とすることによって、メモリセル12とメモリセル22の2つのセルで、単独のメモリセルの場合の2倍の強誘電体容量を有する単一のメモリセルと同等になる。この2個のメモリセル12, 22よりなるメモリセルに対しては、2本のワード線W1, W2および2本のプレート線P1, P2のうちメモリセル12に接続されたワード線W1およびプレート線P1が有効となる。

## 【0056】

30

以上説明したように、実施の形態6によれば、他の実施の形態と同様に、製造段階において書き込まれた暗号等のデータを製造終了後においても保持しつづけることができるという効果を有する。

## 【0057】

また、強誘電体容量が2倍の記憶領域におけるセル構造が、通常の容量の記憶領域におけるセル構造と見かけ上同じであるため、第三者が暗号等が書き込まれた記憶領域を調べ、不正に暗号等を取得してしまうのを防ぐことができる。つまり、機密性が高くなる。

## 【0058】

以上において本発明は、3行以上のメモリセル行または3列以上のメモリセル列にわたってワード線やプレート線、またはピット線対を短絡してもよい。また、一部のメモリセルにおいて強誘電体素子の面積を通常の面積よりも大きくする構成としてもよい。強誘電体素子の面積を大きくすれば一部のメモリセルの強誘電体容量を大きくすることができる。したがって、データ保持特性が向上するが、その代わりに、暗号等のデータが書き込まれた記憶領域の識別が容易となってしまう。

40

## 【0059】

## 【発明の効果】

本発明によれば、製造段階において暗号等を書き込むための強誘電体記憶素子の容量を、他の強誘電体記憶素子の容量よりも大きくしたため、製造中に強誘電体素子が熱の影響を受けたり水素等にさらされても、暗号等の記憶情報が消失してしまうほどには素子の特性が劣化しないので、製造終了後においても記憶情報を保持しつづけることができる。

50

## 【0060】

したがって、製造プロセスにおいて、熱や水素等の外部的要因を極力排除する必要がないので、製造プロセスの制約をなくすことができる。また、熱や水素等の影響を排除するための設備が不要となるため、製造コストを抑えることができるので、安価な半導体記憶装置が得られる。

## 【図面の簡単な説明】

【図1】実施の形態1にかかるF R A Mにおいて、メモリセルとワード線およびプレート線との接続状態を模式的に示す図である。

【図2】実施の形態2にかかるF R A Mにおいて、メモリセルとビット線との接続状態を模式的に示す図である。

【図3】実施の形態3にかかるF R A Mにおいて、メモリセルとワード線およびプレート線との接続状態を模式的に示す図である。

【図4】実施の形態3にかかるF R A Mにおいて、メモリセルとワード線およびプレート線との接続状態の他の例を模式的に示す図である。

【図5】実施の形態4にかかるF R A Mにおいて、メモリセルとビット線との接続状態を模式的に示す図である。

【図6】実施の形態4にかかるF R A Mにおいて、メモリセルとビット線との接続状態の他の例を模式的に示す図である。

【図7】実施の形態5にかかるF R A Mにおいて、メモリセル内の強誘電体素子との接続状態を模式的に示す図である。

【図8】実施の形態6にかかるF R A Mにおいて、隣接するメモリセル間における強誘電体素子の接続状態を模式的に示す図である。

【図9】従来のF R A Mにおいて、メモリセルとワード線およびプレート線との接続状態を模式的に示す図である。

【図10】従来のF R A Mにおいて、メモリセルとビット線との接続状態を模式的に示す図である。

【図11】従来のF R A Mにおいて、メモリセルが2個のトランジスタと2個の強誘電体素子で構成されている例を示す図である。

## 【符号の説明】

B 列選択線（ビット線）

30

W 行選択線（ワード線）

P 行選択線（プレート線）

C 強誘電体キャパシタ（強誘電体素子）

0 1 ~ 3 3 強誘電体記憶素子（メモリセル）

1 , 2 , 5 , 6 選択回路

3 , 7 記憶手段（プログラム格納部）

4 , 8 制御手段（プログラムコントロール回路）

10

20

20

30

【図1】

実施の形態1にかかるFRAMにおいて、メモリセルとワード線およびプレート線との接続状態を模式的に示す図

【図2】

実施の形態2にかかるFRAMにおいて、メモリセルとビット線との接続状態を模式的に示す図

【図3】

実施の形態3にかかるFRAMにおいて、メモリセルとワード線およびプレート線との接続状態を模式的に示す図

【図4】

実施の形態3にかかるFRAMにおいて、メモリセルとワード線およびプレート線との接続状態の他の例を模式的に示す図

【図5】

【図6】

【図7】

実施の形態5にかかるFRAMにおいて、メモリセル内の強誘電体素子との接続状態を模式的に示す図

【図8】

実施の形態6にかかるFRAMにおいて、隣接するメモリセル間における強誘電体素子の接続状態を模式的に示す図

【図9】

従来のFRAMにおいて、メモリセルとワード線および

プレート線との接続状態を模式的に示す図

【図10】

従来のFRAMにおいて、メモリセルとビット線との

接続状態を模式的に示す図

【図11】

従来のFRAMにおいて、メモリセルが2個のトランジスタと

2個の強誘電体素子で構成されている例を示す図

---

フロントページの続き

(56)参考文献 特開平10-070248 (JP, A)

国際公開第97/036300 (WO, A1)

(58)調査した分野(Int.Cl., DB名)

G11C 11/22