(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4140575号

(P4140575)

(45) 発行日 平成20年8月27日(2008.8.27)

(24) 登録日 平成20年6月20日(2008.6.20)

(51) Int.Cl.

G 06 T 15/00 (2006.01)

F 1

G 06 T 15/00 300

請求項の数 12 (全 12 頁)

(21) 出願番号 特願2004-224209 (P2004-224209)

(22) 出願日 平成16年7月30日 (2004.7.30)

(65) 公開番号 特開2006-48140 (P2006-48140A)

(43) 公開日 平成18年2月16日 (2006.2.16)

審査請求日 平成17年7月27日 (2005.7.27)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100122884

弁理士 角田 芳末

(74) 代理人 100113516

弁理士 磯山 弘信

(72) 発明者 高島 彰博

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

(72) 発明者 山内 裕司

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

最終頁に続く

(54) 【発明の名称】 画像変形装置、画像変形回路及び画像変形方法

## (57) 【特許請求の範囲】

## 【請求項 1】

画像の貼付け対象となるモデルについて、各ポリゴンの頂点の座標を算出するとともに、各ポリゴンの頂点の位置での縮小率に応じたプリフィルタ係数を算出するモデリング手段と、

前記モデリング手段で算出された各ポリゴンの頂点の座標を各ピクセルの座標に変換し、前記各ピクセルの座標から、前記モデルに画像を貼り付けるためのリードアドレスを設定するリードアドレス設定手段と、

前記モデリング手段で算出されたプリフィルタ係数を、各ピクセルの位置でのプリフィルタ係数に変換するプリフィルタ係数変換手段と、

入力される画像データを、前記プリフィルタ係数変換手段で変換されたプリフィルタ係数でフィルタリングするプリフィルタ処理手段と、

前記プリフィルタ処理手段でフィルタリングされた画像データが書き込まれる画像記憶手段と、

前記リードアドレス設定手段で設定されたリードアドレスが書き込まれるとともに、前記画像データから分離された垂直同期信号に同期して1フレーム毎にリードアドレスが読み出されるアドレス記憶手段と、

前記アドレス記憶手段から読み出されるリードアドレスに応じて前記画像記憶手段から画像データを読み出す読出し手段と、

を備える画像変形装置。

10

20

## 【請求項 2】

請求項1に記載の画像変形装置において、

前記アドレス記憶手段から読み出されるリードアドレスに応じて前記画像記憶手段から複数個の近傍の画像データが読み出され、当該画像データを用いて、前記リードアドレスの画像データを生成するインターポレーション手段

をさらに備える画像変形装置。

## 【請求項 3】

請求項2に記載の画像変形装置において、

前記複数個の近傍の画像データは、4個又は8個の画像データである

画像変形装置。

10

## 【請求項 4】

請求項3に記載の画像変形装置において、

前記リードアドレス設定手段における、前記各ピクセルの座標は、前記入力される画像データよりも高解像度であり、

前記プリフィルタ係数変換手段における、前記各ピクセルの位置は、前記入力される画像データと同じ解像度である

画像変形装置。

## 【請求項 5】

単一の基板上に搭載されており、

画像の貼付け対象となるモデルについて、各ポリゴンの頂点の座標を算出するとともに、各ポリゴンの頂点の位置での縮小率に応じたプリフィルタ係数を算出するモデリング手段と、

前記モデリング手段で算出された各ポリゴンの頂点の座標を各ピクセルの座標に変換し、前記各ピクセルの座標から、前記モデルに画像を貼り付けるためのリードアドレスを設定するリードアドレス設定手段と、

前記モデリング手段で算出されたプリフィルタ係数を、各ピクセルの位置でのプリフィルタ係数に変換するプリフィルタ係数変換手段と、

入力した画像データを、前記プリフィルタ係数変換手段で変換されたプリフィルタ係数でフィルタリングするプリフィルタ処理手段と、

前記プリフィルタ処理手段でフィルタリングされた画像データが書き込まれる画像記憶手段と、

前記リードアドレス設定手段で設定されたリードアドレスが書き込まれるとともに、前記画像データから分離された垂直同期信号に同期して1フレーム毎にリードアドレスが読み出されるアドレス記憶手段と、

前記アドレス記憶手段から読み出されるリードアドレスに応じて前記画像記憶手段から画像データを読み出す読み出し手段と、

を備える画像変形回路。

## 【請求項 6】

請求項5に記載の画像変形回路において、

前記アドレス記憶手段から読み出されるリードアドレスに応じて前記画像記憶手段から複数個の近傍の画像データが読み出され、当該画像データを用いて、前記リードアドレスの画像データを生成するインターポレーション手段

をさらに備える画像変形回路。

40

## 【請求項 7】

請求項6に記載の画像変形回路において、

前記複数個の近傍の画像データは、4個又は8個の画像データである

画像変形回路。

## 【請求項 8】

請求項7に記載の画像変形回路において、

前記リードアドレス設定手段における、前記各ピクセルの座標は、前記入力される画像

50

データよりも高解像度であり、

前記プリフィルタ係数変換手段における、前記各ピクセルの位置は、前記入力される画像データと同じ解像度である

画像変形回路。

【請求項 9】

画像の貼付け対象となるモデルについて、各ポリゴンの頂点の座標を算出するとともに、各ポリゴンの頂点の位置での縮小率に応じたプリフィルタ係数を算出する第1のステップと、

前記第1のステップで算出された各ポリゴンの頂点の座標を各ピクセルの座標に変換し、前記各ピクセルの座標から、前記モデルに画像を貼り付けるためのリードアドレスを設定する第2のステップと、

前記第2のステップで設定されたリードアドレスをアドレス記憶手段に書き込む第3のステップと、

前記第1のステップで算出されたプリフィルタ係数を、各ピクセルの位置でのプリフィルタ係数に変換する第4のステップと、

入力される画像データを、前記第4のステップで変換されたプリフィルタ係数でフィルタリングする第5のステップと、

前記第5のステップでフィルタリングされた画像データを画像記憶手段に書き込む第6のステップと、

前記画像データから分離された垂直同期信号に同期して1フレーム毎に前記アドレス記憶手段からリードアドレスを読み出す第7のステップと、

前記第7のステップで読み出されたリードアドレスに応じて前記画像記憶手段から画像データを読み出す第8のステップと、

を有する画像変形方法。

【請求項 10】

請求項9に記載の画像変形方法において、

前記アドレス記憶手段から読み出されるリードアドレスに応じて前記画像記憶手段から複数個の近傍の画像データが読み出され、当該画像データを用いて、インターポレーションにより、前記リードアドレスの画像データを生成する第9のステップ

をさらに含む画像変形方法。

【請求項 11】

請求項10に記載の画像変形方法において、

前記複数個の近傍の画像データは、4個又は8個の画像データである

画像変形方法。

【請求項 12】

請求項11に記載の画像変形方法において、

前記第2のステップにおける、前記各ピクセルの座標は、前記入力される画像データよりも高解像度であり、

前記第4のステップにおける、前記各ピクセル位置は、前記入力される画像データと同じ解像度である

画像変形方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、テクスチャマッピングによって画像を変形する装置、回路及び方法に関する。

【背景技術】

【0002】

コンピュータグラフィックス分野においては、仮想3次元空間上における画像の変形方法として、ポリゴンと呼ばれる三角形の組み合わせで構成した物体形状(モデル)を作成

10

20

30

40

50

し、そのモデルに画像を貼り付けるテクスチャマッピングという手法を用いている。ここで、仮想3次元空間において、モデルがカメラ視点より遠方にある場合には、モデルが縮小される。

#### 【0003】

このとき、あらかじめ同じ画像を段階的(離散的)に低解像度にしたテクスチャデータを用意し、モデルの縮小率に近いテクスチャデータをモデルに貼り付けることでエイリアシングの少ないテクスチャマッピングを行っている。一般に本手法による画像のアンチエイリアシング方法をミップマップ方式と呼び、段階的に低解像度にしたテクスチャデータをミップマップ画像と呼ぶ。

#### 【0004】

画像が縮小されていないオリジナル状態のときの縮小率を1.0、及び縮小した時を0.0~0.999...と定義すると、ミップマップ方式では、テクスチャデータとして、縮小率が1.0, 0.5, 0.25, 0.125, 0.0625...といった具合に有限回数で、かつ、 $1/2^n$ (2のべき乗分の1)毎に縮小した画像データをメモリに用意する。その後、モデルの縮小率が、例えば0.75であれば、縮小率が1.0と0.5のミップマップデータをメモリから読み出し、さらにこれらのミップマップデータを $1/2$ ずつの重み付けで直線補間することで縮小率0.75のテクスチャデータを算出する(例えば、特許文献1参照)。

【特許文献1】特開2002-83316号公報(段落番号0004)

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0005】

しかし、従来のようにミップマップ方式によってアンチエイリアシングを行うことには、次の(1)~(3)のような問題点があった。

(1) モデルの縮小率がミップマップデータの縮小率以外の場合、前述した通り、2枚のミップマップデータを直線補間するので、最適なアンチエイリアス処理が行えない。このため、出力画像にエイリアスが発生したり、ボケが生じる。

#### 【0006】

(2) 入力画像に対して $1/2^n$ 毎に縮小されたテクスチャデータを用意する必要があるので、処理時間が長くなるとともに回路規模が大きくなる。

#### 【0007】

(3) 入力画像 + (入力画像の $1/2$ の画像) + (入力画像の $1/4$ の画像) + (入力画像の $1/8$ の画像) + ...、といったように、入力画像の約2倍の量がテクスチャデータ量となるので、大容量のメモリが必要になる。

#### 【0008】

本発明は、上述の点に鑑み、テクスチャマッピングによって画像を変形する際に、モデルの縮小率にかかわらずエイリアスの少ない高画質な出力画像を得、且つ、処理時間の短縮や回路規模の小型化やメモリの容量を削減を実現することを課題としてなされたものである。

#### 【課題を解決するための手段】

#### 【0009】

この課題を解決するために、本発明に係る画像変形装置は、画像の貼付け対象となるモデルについて、各ポリゴンの頂点の座標を算出するとともに、各ポリゴンの頂点の位置での縮小率に応じたプリフィルタ係数を算出するモデリング手段と、モデリング手段で算出された各ポリゴンの頂点の座標を各ピクセルの座標に変換し、各ピクセルの座標から、モデルに画像を貼り付けるためのリードアドレスを設定するリードアドレス設定手段と、モデリング手段で算出されたプリフィルタ係数を、各ピクセルの位置でのプリフィルタ係数に変換するプリフィルタ係数変換手段と、入力した画像データを、プリフィルタ係数変換手段で変換されたプリフィルタ係数でフィルタリングするプリフィルタ処理手段と、プリフィルタ処理手段でフィルタリングされた画像データが書き込まれる画像記憶手段と、リ

10

20

30

40

50

ードアドレス設定手段で設定されたリードアドレスに応じて画像記憶手段から画像データを読み出す読み出し手段とを備えたことを特徴とする。

【0010】

この画像変形装置では、画像の貼付け対象となるモデルについて、各ポリゴンの頂点の座標が算出された後、各ポリゴンの頂点の座標が各ピクセルの座標に変換されて、各ピクセルの座標から、モデルに画像を貼り付けるためのリードアドレスが設定される。

【0011】

また、このモデルについて、各ポリゴンの頂点の位置での縮小率に応じたプリフィルタ係数が算出された後、このプリフィルタ係数が各ピクセルの位置でのプリフィルタ係数に変換される。

10

【0012】

そして、入力した画像データが、各ピクセルの位置でのプリフィルタ係数でフィルタリングされて画像記憶手段に書き込まれた後、設定されたリードアドレスに応じて画像記憶手段から読み出されることによって、モデルへの画像の貼付け（画像の変形）が行われる。

【0013】

このように、この画像変形装置によれば、入力した画像データを、モデルの各ピクセル位置での縮小率に応じたプリフィルタ係数でプリフィルタリングしたものがテクスチャデータとして用いられる。これにより、モデルの縮小率に応じた最適なプリフィルタリングが行われるので、モデルの縮小率にかかわらずエイリアスの少ない高画質な出力画像が得られる。

20

【0014】

また、テクスチャデータをモデルの縮小率に応じて1つだけ用意すればよいので、処理時間を短縮できるとともに回路規模を小型化することができる。

【0015】

そして、このようにテクスチャデータが1つだけであり、入力した画像データの量がテクスチャデータの量となるので、メモリ（画像記憶手段）の容量を削減することができる。

【0016】

なお、この画像変形装置において、一例として、プリフィルタ処理手段には画像データが入力され、リードアドレス設定手段で設定されたリードアドレスが書き込まれるとともに、画像データから分離された垂直同期信号に同期して1フレーム毎にリードアドレスが読み出されるアドレス記憶手段をさらに備え、読み出し手段は、このアドレス記憶手段から読み出されるリードアドレスに応じて画像記憶手段から画像データを読み出すことが好適である。

30

【0017】

それにより、入力するビデオデータに対してリアルタイムにテクスチャマッピングを行うことができるようになる。

【0018】

次に、本発明に係る画像変形回路は、单一の基板上に搭載されており、画像の貼付け対象となるモデルについて、各ポリゴンの頂点の座標を算出するとともに、各ポリゴンの頂点の位置での縮小率に応じたプリフィルタ係数を算出するモデリング手段と、モデリング手段で算出された各ポリゴンの頂点の座標を各ピクセルの座標に変換し、各ピクセルの座標から、モデルに画像を貼り付けるためのリードアドレスを設定するリードアドレス設定手段と、モデリング手段で算出されたプリフィルタ係数を、各ピクセルの位置でのプリフィルタ係数に変換するプリフィルタ係数変換手段と、入力した画像データを、プリフィルタ係数変換手段で変換されたプリフィルタ係数でフィルタリングするプリフィルタ処理手段と、プリフィルタ処理手段でフィルタリングされた画像データが書き込まれる画像記憶手段と、リードアドレス設定手段で設定されたリードアドレスに応じて画像記憶手段から画像データを読み出す読み出し手段とを備えたことを特徴とする。

40

50

なお、この画像変形回路において、一例として、プリフィルタ処理手段には画像データが入力され、リードアドレス設定手段で設定されたリードアドレスが書き込まれるとともに、画像データから分離された垂直同期信号に同期して1フレーム毎にリードアドレスが読み出されるアドレス記憶手段をさらに備え、読み出し手段は、このアドレス記憶手段から読み出されるリードアドレスに応じて画像記憶手段から画像データを読み出すことが好適である。

#### 【0019】

また、本発明に係る画像変形方法は、画像の貼付け対象となるモデルについて、各ポリゴンの頂点の座標を算出するとともに、各ポリゴンの頂点の位置での縮小率に応じたプリフィルタ係数を算出する第1のステップと、第1のステップで算出された各ポリゴンの頂点の座標を各ピクセルの座標に変換し、各ピクセルの座標から、モデルに画像を貼り付けるためのリードアドレスを設定する第2のステップと、第1のステップで算出されたプリフィルタ係数を、各ピクセルの位置でのプリフィルタ係数に変換する第3のステップと、入力した画像データを、第3のステップで変換されたプリフィルタ係数でフィルタリングする第4のステップと、第4のステップでフィルタリングされた画像データを画像記憶手段に書き込む第5のステップと、第2のステップで設定されたリードアドレスに応じて画像記憶手段から画像データを読み出す第6のステップとを有することを特徴とする。

なお、この画像変形方法において、一例として、設定したリードアドレスをアドレス記憶手段に書き込むステップと、画像データから分離された垂直同期信号に同期して1フレーム毎にアドレス記憶手段からリードアドレスを読み出すステップと、アドレス記憶手段から読み出されるリードアドレスに応じて画像記憶手段から画像データを読み出すステップと、をさらに含むことが好適である。

#### 【0020】

これらの回路、方法によれば、前述の本発明に係る画像変形装置について説明したのと全く同様にして、テクスチャマッピングによって画像を変形する際に、モデルの縮小率にかかわらずエイリアスの少ない高画質な出力画像を得ることができ、且つ、処理時間の短縮や回路規模の小型化やメモリの容量を削減を実現することができる。

#### 【発明の効果】

#### 【0021】

本発明によれば、テクスチャマッピングによって画像を変形する際に、モデルの縮小率にかかわらずエイリアスの少ない高画質な出力画像を得ることができ、且つ、処理時間の短縮や回路規模の小型化やメモリの容量を削減を実現できるという効果が得られる。

#### 【0022】

また、入力するビデオデータに対してリアルタイムにテクスチャマッピングを行うことができるという効果も得られる。

#### 【発明を実施するための最良の形態】

#### 【0023】

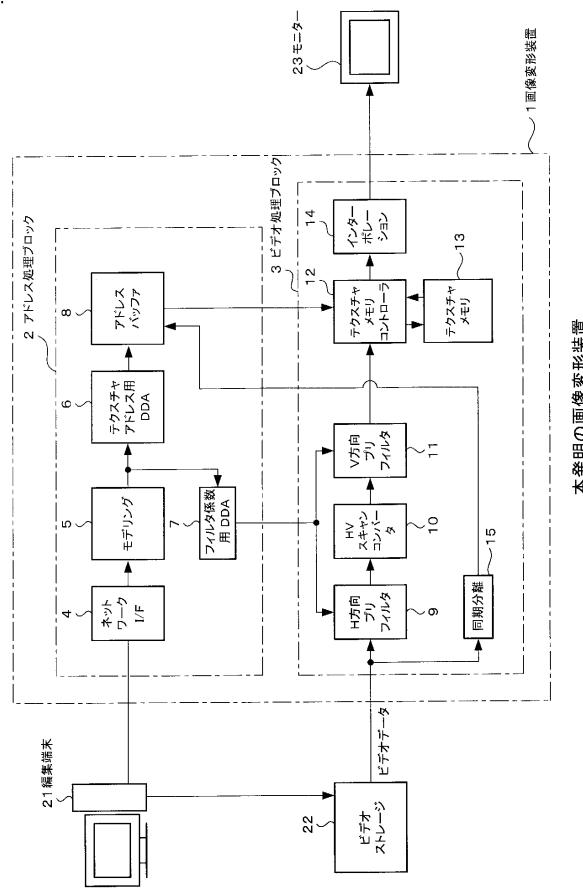

以下、本発明を図面を用いて具体的に説明する。図1は、本発明に係る画像変形装置の構成例を示すブロック図である。この画像変形装置1は、筐体に収納された単体としての装置であり、大別してアドレス処理ブロック2とビデオ処理ブロック3とで構成されている。

#### 【0024】

アドレス処理ブロック2は、モデルの縮小や変形を行うブロックであり、イーサネット（イーサネット：Ethernetは登録商標）経由で通信を行うためのネットワークインターフェース4と、モデリング部5と、テクスチャアドレス用DDA（Digital Differential Analyzer=デジタル微分回路）6と、フィルタ係数用DDA7と、アドレスバッファ8などで構成されている。

#### 【0025】

ビデオ処理ブロック3は、アドレス処理ブロック2で変形されたモデルに画像を貼り付けるためにアンチエイリアスを行うブロックであり、H方向プリフィルタ9と、HVスキ

10

20

30

40

50

ヤンコンバータ10と、V方向プリフィルタ11と、テクスチャメモリコントローラ12と、テクスチャメモリ13と、インターポレーション部14と、同期分離部15とで構成されている。

【0026】

この画像変形装置1は、テレビ放送局においてノンリニア編集システムの一部であるエフェクタ(画像に特殊効果を施す装置)として用いられており、アドレス処理ブロック2がイーサネットで編集端末(編集用ソフトウェアをインストールしたコンピュータ)21に接続されるとともに、ビデオ処理ブロック3がビデオストレージ(例えばVTRまたはAVサーバー)22及びモニター23に接続されている。

【0027】

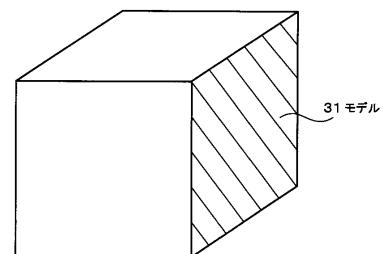

編集端末21では、オペレータの操作に基づき、画像を貼り付ける対象となるモデルと、変形させようとする画像(ビデオデータ)とが指定される。図2は、編集端末21で指定されるモデルの一例を示す。斜め方向から見た立方体の側面(斜線で描いた面)が、モデル31として指定されている。

【0028】

図1に示すように、編集端末21からは、この指定されたモデルの形状を示すデータ(ワイヤーフレームデータ)が、画像変形装置1のアドレス処理ブロック2に送られる。

【0029】

また、編集端末21からは、この指定されたビデオデータの読み出しを指示するコマンドが、ビデオストレージ22に送られる。ビデオストレージ22からは、このコマンドに従って読み出されたビデオデータが、画像変形装置1のビデオ処理ブロック3に送られる。

【0030】

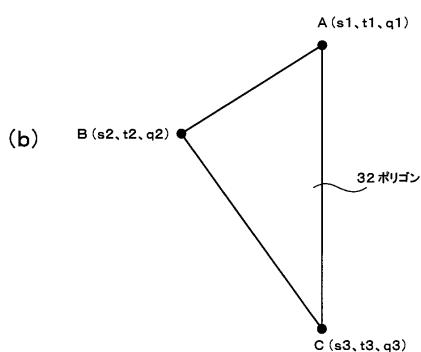

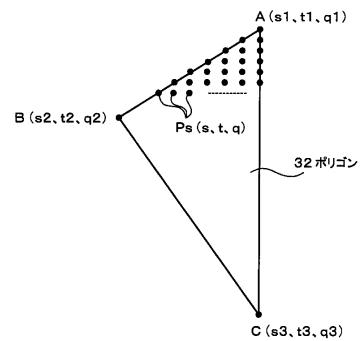

アドレス処理ブロック2内では、モデリング部5が、編集端末21から送られたワイヤーフレームデータに基づき、モデルを複数のポリゴンに分割する。そして、各ポリゴンの頂点のテクスチャ座標を算出するとともに、各ポリゴンの頂点の位置での縮小率に応じたプリフィルタ係数を算出する。図3(a)は、図2に示したモデル(立方体の側面)を複数のポリゴン32に分割した様子を示し、図3(b)は、このうちの1つのポリゴン32の頂点A, B, Cのテクスチャ座標(s1, t1, q1), (s2, t2, q2), (s3, t3, q3)を示す。

【0031】

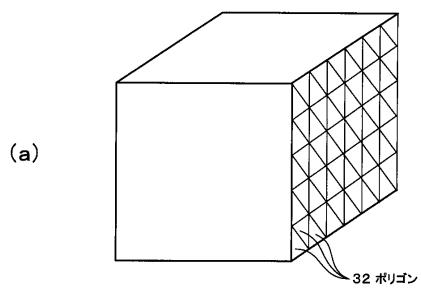

図1に示すように、モデリング部5で算出されたテクスチャ座標のデータは、テクスチャアドレス用DDA6に送られる。テクスチャアドレス用DDA6は、図4に示すように、各ポリゴンの頂点A, B, Cのテクスチャ座標(s1, t1, q1), (s2, t2, q2), (s3, t3, q3)を、直線補間により、各サブピクセルPs(ビデオストレージ22内のビデオデータよりも高解像度なピクセル)のテクスチャ座標(s, t, q)に変換する。そして、u = s / q, v = t / qの計算を行うことにより、各サブピクセルのテクスチャアドレス(u, v)を設定する。このテクスチャアドレス(u, v)は、アドレスバッファ8に書き込まれる。

【0032】

モデリング部5で算出されたプリフィルタ係数は、フィルタ係数用DDA7に送られる。フィルタ係数用DDA7は、各ポリゴンの頂点の位置での縮小率に応じたプリフィルタ係数を、直線補間により、各ピクセル(ビデオストレージ22内のビデオデータと同じ解像度のピクセル)の位置での縮小率に応じたプリフィルタ係数に変換する。フィルタ係数用DDA7で変換されたプリフィルタ係数は、ビデオ処理ブロック3内のH方向プリフィルタ9及びV方向プリフィルタ11に送られる。

【0033】

ビデオ処理ブロック3内では、H方向プリフィルタ9が、ビデオストレージ22から送られたビデオデータを、フィルタ係数用DDA7からのプリフィルタ係数でピクセル毎に画面水平方向にフィルタリングする。

【0034】

10

20

30

40

50

H方向プリフィルタ9でフィルタリングされたビデオデータは、HVスキャンコンバータ10に送られる。HVスキャンコンバータ10は、内部のメモリに1フレーム分の画像データを書き込んだ後そのメモリから画面垂直方向に各ピクセルのデータを読み出すことにより、ビデオデータをスキャンコンバートする。

【0035】

HVスキャンコンバータ10でスキャンコンバートされたビデオデータは、V方向プリフィルタ11に送られる。V方向プリフィルタ11は、フィルタ係数用DDA7からのプリフィルタ係数で、ビデオデータをピクセル毎に垂直方向にフィルタリングする。

【0036】

V方向プリフィルタ11でフィルタリングされたビデオデータは、テクスチャメモリコントローラ12を介してテクスチャメモリ13に書き込まれる。 10

【0037】

また、ビデオ処理ブロック3内では、同期分離部15が、ビデオストレージ22から送られたビデオデータから、垂直同期信号を分離してアドレス処理ブロック2内のアドレスバッファ8に送る。アドレスバッファ8からは、この垂直同期信号に同期して、1フレーム毎に各サブピクセルのテクスチャアドレス(u, v)が読み出されてビデオ処理ブロック3内のテクスチャメモリコントローラ12に送られる。

【0038】

テクスチャメモリコントローラ12は、アドレスバッファ8からの各サブピクセルのテクスチャアドレス(u, v)をリードアドレスとして、テクスチャメモリ13から、それぞれそのサブピクセルの近傍の複数(4つあるいは8つ)のピクセルのデータを読み出す。 20

【0039】

テクスチャメモリ13から読み出されたデータは、テクスチャメモリコントローラ12からインターポレーション部14に送られる。インターポレーション部14は、各サブピクセルの近傍の複数のピクセルのデータを直線補間することにより、それぞれそのサブピクセルのデータを生成する。図5は、サブピクセルのデータの生成例を示す。この例では、テクスチャメモリ13からサブピクセルPsの近傍の4つのピクセルP0～P3のデータD0～D3が読み出されており、サブピクセルPsと各ピクセルP0～P3との距離に応じた重み付け係数K0～K3でデータD0～D3を直線補間することにより、サブピクセルPsのデータDsが生成される。 30

【0040】

図1に示すように、インターポレーション部14で生成された各サブピクセルのデータは、画像変形装置1からモニター23に送られて、モニター23に表示される。

【0041】

この画像変形装置1では、画像の貼付け対象となるモデルについて、モデリング部5によってポリゴンの頂点の座標が算出された後、テクスチャアドレス用DDA6により、各ポリゴンの頂点の座標が各ピクセルの座標に変換されて、各ピクセルの座標から、モデルに画像を貼り付けるためのリードアドレスであるテクスチャアドレスが設定される。 40

【0042】

また、このモデルについて、モデリング部5によって各ポリゴンの頂点の位置での縮小率に応じたプリフィルタ係数が算出された後、このプリフィルタ係数がフィルタ係数用DDA7によって各ピクセルの位置でのプリフィルタ係数に変換される。

【0043】

そして、入力したビデオデータが、H方向プリフィルタ9及びV方向プリフィルタ11によって各ピクセルの位置でのプリフィルタ係数でフィルタリングされてテクスチャメモリ13に書き込まれた後、設定されたテクスチャアドレスに応じてテクスチャメモリ13から読み出されることによって、モデルへの画像の貼付け(画像の変形)が行われる。

【0044】

このように、この画像変形装置1によれば、入力した画像データを、モデルの各ピクセ 50

ル位置での縮小率に応じたプリフィルタ係数でプリフィルタリングしたものがテクスチャデータとして用いられる。これにより、モデルの縮小率に応じた最適なプリフィルタリングが行われるので、段階的（離散的）な縮小率のテクスチャデータを用意するミップマップ方式と違って、モデルの縮小率にかかわらずエイリアスの少ない高画質な出力画像が得られる。

【0045】

また、テクスチャデータをモデルの縮小率に応じて1つだけ用意すればよいので、入力画像に対して $1/2^n$ 毎に縮小されたテクスチャデータを用意するミップマップ方式と比較して、処理時間を短縮できるとともに回路規模を小型化することができる。

【0046】

そして、このようにテクスチャデータが1つだけであり、入力した画像データの量がテクスチャデータの量となるので、テクスチャデータ量が入力画像の約2倍の量となるミップマップ方式と比較して、メモリ（テクスチャメモリ13）の容量を削減することができる。

【0047】

さらに、この画像変形装置1によれば、テクスチャアドレスが、アドレスバッファ8に書き込まれた後、入力するビデオデータから分離された垂直同期信号に同期して1フレーム毎にアドレスバッファ8から読み出されてテクスチャメモリコントローラ12に送られるので、入力するビデオデータに対してリアルタイムにテクスチャマッピングを行うことができる。

【0048】

なお、以上の例ではビデオデータを画像変形装置1に入力させているが、これに限らず、静止画データやコンピュータグラフィックによって作成したデータを画像変形装置1に入力させるようにしてもよい。静止画データを入力させる場合には、リアルタイム性は必要なくなるので、アドレスバッファ8を省略し、テクスチャアドレス用DDA6で設定されたテクスチャアドレスを直接テクスチャメモリコントローラ12に送るようにしてよい。

【0049】

また、以上の例では、編集端末1とイーサネットで接続される単体の装置としての画像変形装置1について説明した。しかし、別の例として、この画像変形装置1と同一の構成要素を单一の基板上に搭載した画像変形回路を製作し、その画像変形回路を編集端末1のスロットに装着するようにしてもよい。

【0050】

また、以上の例では、ノンリニア編集システムの一部であるエフェクタに本発明を適用している。しかし、これに限らず、本発明は、例えばコンピュータゲーム機にも適用してよい。

【図面の簡単な説明】

【0051】

【図1】本発明に係る画像変形装置の構成例を示すブロック図である。

【図2】画像を貼り付ける対象となるモデルを例示する図である。

【図3】ポリゴン及びその頂点のテクスチャ座標を示す図である。

【図4】各サブピクセルのテクスチャ座標を示す図である。

【図5】サブピクセルのデータの生成例を示す図である。

【符号の説明】

【0052】

1 画像変形装置、 2 アドレス処理ブロック、 3 ビデオ処理ブロック、 4 ネットワークインターフェース、 5 モデリング部、 6 テクスチャアドレス用DDA、 7 フィルタ係数用DDA、 8 アドレスバッファ、 9 H方向プリフィルタ、 10 HVスキャンコンバータ、 11 V方向プリフィルタ、 12 テクスチャメモリコントローラ、 13 テクスチャメモリ、 14 インターポレーション部、 1

10

20

30

40

50

## 5 同期分離部

【図1】

【図2】

画像貼付け対象のモデルの例

【図3】

【図4】

各サブピクセルのテクスチャ座標

【図5】

ポリゴン及びその頂点のテクスチャ座標

サブピクセルのデータの生成例

---

フロントページの続き

(72)発明者 清水 英之

東京都品川区北品川6丁目7番35号 ソニー株式会社内

審査官 伊知地 和之

(56)参考文献 特開2002-083316 (JP, A)

特開平01-131976 (JP, A)

特開2002-042159 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 06 T 15 / 00

G 09 G 5 / 00 - 5 / 36

C S D B (日本国特許庁)