(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5396335号

(P5396335)

(45) 発行日 平成26年1月22日(2014.1.22)

(24) 登録日 平成25年10月25日(2013.10.25)

(51) Int.Cl.

G06F 3/041 (2006.01)

F 1

G06F 3/041 330A

G06F 3/041 350C

請求項の数 7 (全 35 頁)

(21) 出願番号 特願2010-118946 (P2010-118946)

(22) 出願日 平成22年5月25日 (2010.5.25)

(65) 公開番号 特開2011-8775 (P2011-8775A)

(43) 公開日 平成23年1月13日 (2011.1.13)

審査請求日 平成25年4月29日 (2013.4.29)

(31) 優先権主張番号 特願2009-128549 (P2009-128549)

(32) 優先日 平成21年5月28日 (2009.5.28)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 田村 植

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 上妻 宗広

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 佐藤 匡

最終頁に続く

(54) 【発明の名称】タッチパネル

## (57) 【特許請求の範囲】

## 【請求項 1】

微小構造体と、トランジスタと、前記トランジスタに電気的に接続された発光素子と、

スペーサとを有し、

前記微小構造体は、下部電極と、前記下部電極と対向して設けられた上部電極と、前記

下部電極と前記上部電極との間に設けられた充填層とを有し、

前記下部電極は、前記トランジスタのゲート電極と同材料で形成され、

前記上部電極は、前記発光素子の第1の電極と同材料で形成され、

前記スペーサは、前記発光素子の第1の電極を覆う隔壁よりも硬い材料を用いて、前記

上部電極上に前記充填層と重なるように形成され、

前記隔壁は、前記充填層よりも硬い材料で形成されることを特徴とするタッチパネル。

## 【請求項 2】

微小構造体と、トランジスタと、前記トランジスタに電気的に接続された発光素子と、

スペーサとを有し、

前記微小構造体は、下部電極と、前記下部電極と対向して設けられた上部電極と、前記

下部電極と前記上部電極との間に設けられた充填層とを有し、

前記下部電極は、前記トランジスタのソース電極またはドレイン電極と同材料で形成され、

前記上部電極は、前記発光素子の第1の電極と同材料で形成され、

前記スペーサは、前記発光素子の第1の電極を覆う隔壁よりも弾性率の高い材料を用い

10

20

て、前記上部電極上に前記充填層と重なるように形成され、

前記隔壁は、前記充填層よりも弾性率の高い材料で形成されることを特徴とするタッチパネル。

#### 【請求項 3】

請求項 1 または請求項 2 において、

前記充填層は、圧力により可逆変形可能な多孔質の絶縁性材料を含むことを特徴とするタッチパネル。

#### 【請求項 4】

請求項 3 において、

前記多孔質の絶縁性材料はブロックコポリマーであることを特徴とするタッチパネル。

10

#### 【請求項 5】

請求項 1 乃至 4 のいずれか一において、

前記充填層の空隙率は 20 % 以上 80 % 以下であることを特徴とするタッチパネル。

#### 【請求項 6】

請求項 1 または請求項 2 において、

前記充填層は、圧力により可逆変形可能な弾性を有する絶縁性材料を含むことを特徴とするタッチパネル。

#### 【請求項 7】

請求項 6 において、

前記弾性を有する絶縁性材料はエラストマーまたは熱可塑性エラストマーであることを特徴とするタッチパネル。

20

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明はタッチセンサと表示部とを有するタッチパネルに関する。

#### 【背景技術】

#### 【0002】

近年、タッチセンサを搭載した表示装置が注目されている。タッチセンサを搭載した表示装置は、タッチパネルまたはタッチスクリーン等と呼ばれる（以下、これらを単に「タッチパネル」と呼ぶ）。タッチセンサには、抵抗膜方式、音響パルス認識方式、超音波表面弾性波方式、赤外遮光方式、静電容量方式、電磁誘導方式、画像認識方式などの種類があり、その違いは動作原理によるものである。いずれの方式であっても被検出物となる物が表示装置に接触することでデータを入力することができる。

30

#### 【0003】

従来のタッチセンサは発光層を含む E L 層の上層又は下層に形成されていた。特許文献 1 のようにタッチセンサが E L 層の上層に形成される場合、表示面に保護膜や保護基板を設ける必要があるため、いくら高精細な表示装置を作製したとしても視認性が低下し、画質が劣化する。一方、特許文献 2 のようにタッチセンサが E L 層の下層に形成される場合には、表示の高精細化は実現できるが、タッチセンサに圧力をかけることが困難であるため、タッチセンサの精度の低下が問題であった。

40

#### 【先行技術文献】

#### 【特許文献】

#### 【0004】

【特許文献 1】特開 2000-331557 号公報

【特許文献 2】特開 2003-296022 号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0005】

本発明の一態様は、表示部と一体形成できるタッチセンサを提供することを課題とする

50

。また、本発明の一態様は、表示部に表示される画像の画質の劣化を起こさないタッチセンサを提供することを課題とする。

【課題を解決するための手段】

【0006】

本発明の一態様は、微小構造体と、薄膜トランジスタと、前記薄膜トランジスタに電気的に接続された発光素子と、スペーサとを有するタッチパネルであって、前記微小構造体は、下部電極と、前記下部電極と対向して設けられ、圧力の印加により前記下部電極に向かう方向に可動する上部電極と、前記下部電極と前記上部電極との間に設けられた充填層とを有し、前記下部電極は、前記薄膜トランジスタのゲート電極と同材料で形成され、前記上部電極は、前記発光素子の第1の電極と同材料で形成され、前記充填層は、前記圧力により可逆変形可能な多孔質の絶縁性材料からなり、前記スペーサは、前記発光素子の第1の電極を覆う隔壁よりも硬い材料を用いて前記上部電極上に形成され、前記隔壁は、前記充填層よりも硬い材料で形成されることを特徴とするタッチパネルである。

【0007】

本発明の一態様は、微小構造体と、薄膜トランジスタと、前記薄膜トランジスタに電気的に接続された発光素子と、スペーサとを有するタッチパネルであって、前記微小構造体は、下部電極と、前記下部電極と対向して設けられ、圧力の印加により前記下部電極に向かう方向に可動する上部電極と、前記下部電極と前記上部電極との間に設けられた充填層とを有し、前記下部電極は、前記薄膜トランジスタのソース電極又はドレイン電極と同材料で形成され、前記上部電極は、前記発光素子の第1の電極と同材料で形成され、前記充填層は、前記圧力により可逆変形可能な多孔質の絶縁性材料からなり、前記スペーサは、前記発光素子の第1の電極を覆う隔壁よりも硬い材料を用いて前記上部電極上に形成され、前記隔壁は、前記充填層よりも硬い材料で形成されることを特徴とするタッチパネルである。

【0008】

前記充填層の空隙率は20%以上80%以下であることが好ましい。

【0009】

前記多孔質の絶縁性材料はブロックコポリマーにより形成されると好ましい。

【0010】

本発明の一態様は、微小構造体と、薄膜トランジスタと、前記薄膜トランジスタに電気的に接続された発光素子と、スペーサとを有するタッチパネルであって、前記微小構造体は、下部電極と、前記下部電極と対向して設けられ、圧力の印加により前記下部電極に向かう方向に可動する上部電極と、前記下部電極と前記上部電極との間に設けられた充填層とを有し、前記下部電極は、前記薄膜トランジスタのゲート電極と同材料で形成され、前記上部電極は、前記発光素子の第1の電極と同材料で形成され、前記充填層は、前記圧力により可逆変形可能な弹性を有する絶縁性材料からなり、前記スペーサは、前記発光素子の第1の電極を覆う隔壁よりも硬い材料を用いて前記上部電極上に形成され、前記隔壁は、前記充填層よりも硬い材料で形成されることを特徴とするタッチパネルである。

【0011】

本発明の一態様は、微小構造体と、薄膜トランジスタと、前記薄膜トランジスタに電気的に接続された発光素子と、スペーサとを有するタッチパネルであって、前記微小構造体は、下部電極と、前記下部電極と対向して設けられ、圧力の印加により前記下部電極に向かう方向に可動する上部電極と、前記下部電極と前記上部電極との間に設けられた充填層とを有し、前記下部電極は、前記薄膜トランジスタのソース電極又はドレイン電極と同材料で形成され、前記上部電極は、前記発光素子の第1の電極と同材料で形成され、前記充填層は、前記圧力により可逆変形可能な弹性を有する絶縁性材料からなり、前記スペーサは、前記発光素子の第1の電極を覆う隔壁よりも硬い材料を用いて前記上部電極上に形成され、前記隔壁は、前記充填層よりも硬い材料で形成されることを特徴とするタッチパネルである。

【0012】

10

20

30

40

50

前記弾性を有する絶縁性材料はエラストマー又は熱可塑性エラストマーであることが好ましい。

【発明の効果】

【0013】

本発明の一態様は、タッチセンサが発光素子と並置されているため、画質劣化の少ない、薄型のタッチパネルを提供することができる。

【0014】

本発明の一態様は、充填層、隔壁、及びスペーサに硬さの異なる材料を用いることによって、効率的にタッチセンサに入力ができる、且つ、発光素子に圧力が加わりにくい構造のタッチパネルを提供することができる。また、スペーサをタッチセンサの上部に設けることで、タッチセンサの耐久度及びセンサ感度を向上することができる。

10

【図面の簡単な説明】

【0015】

【図1】本発明の一態様に係る断面図。

【図2】本発明の一態様に係る断面図。

【図3】本発明の一態様に係る回路図。

【図4】本発明の一態様に係る位置検出方法を説明する図。

【図5】本発明の一態様に係る回路図。

【図6】本発明の一態様に係る位置検出方法を説明する図。

【図7】本発明の一態様に係るブロックコポリマーを説明する図。

20

【図8】本発明の一態様に係る上面図。

【図9】本発明の一態様に係る上面図。

【図10】本発明の一態様に係る上面図。

【図11】本発明の一態様に係る上面図。

【図12】本発明の一態様に係る上面図。

【図13】本発明の一態様に係る上面図。

【図14】本発明の一態様に係る上面図。

【図15】本発明の一態様に係る断面図。

【図16】本発明の一態様に係る断面図。

【図17】本発明の一態様に係る断面図。

30

【図18】本発明の一態様に係る上面図。

【図19】本発明の一態様に係る上面図。

【図20】本発明の一態様に係る上面図。

【図21】本発明の一態様に係る上面図。

【図22】本発明の一態様に係る上面図。

【図23】本発明の一態様に係る上面図。

【図24】本発明の一態様に係る上面図。

【図25】本発明の一態様に係る断面図。

【図26】本発明の一態様に係る断面図。

【図27】本発明の一態様に係る断面図。

【図28】本発明の一態様に係る外観図。

40

【発明を実施するための形態】

【0016】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の一態様の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

【0017】

50

### (実施の形態 1)

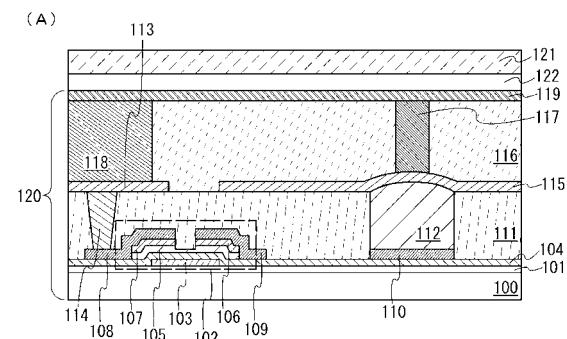

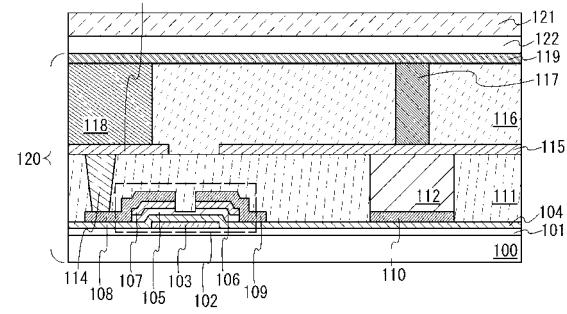

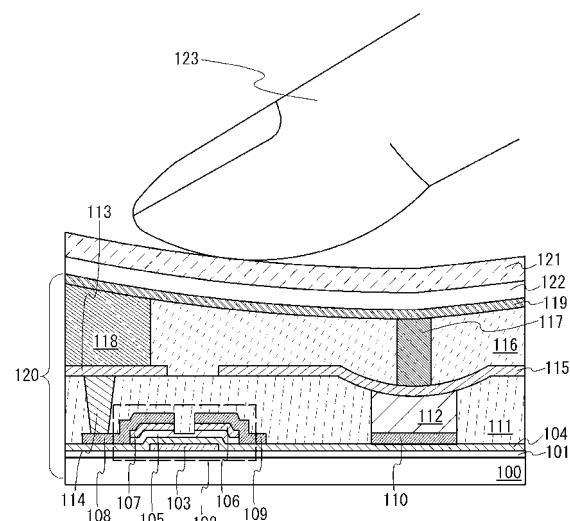

本実施の形態では、本発明の一態様のタッチパネルの構造について図1(A)、図1(B)及び図2を用いて説明する。

#### 【0018】

タッチセンサは、上部電極と下部電極との接触又は距離の変化などによってデータが入力される装置である。本発明の一態様は、タッチセンサとしてMEMS (Micro Electro Mechanical System) を用いる。

#### 【0019】

MEMSは、微小電気機械システムの略称であり、単にマイクロマシンと呼ばれることもある。マイクロマシンとは、一般的には、半導体微細加工技術を用いて作製した「立体構造を有し、可動する微小構造体」と「半導体素子を有する電子回路」とを集積した微細デバイスを指す。上記の微小構造体は半導体素子とは異なり、可動部を有することが一般的である。

#### 【0020】

上記の微小構造体は構造層と中空部とを有し、構造層は可動部を有する。構造層の可動部が動作するため、上記の微小構造体には十分な機械的な強度が必要とされる。従来の微小構造体は、可動部の動作領域を確保するために、中空部を有する。中空部の形成は、まず中空部となる箇所に犠牲層を形成し、構造層等を形成後にこの犠牲層をエッティング等により除去することで行う。例えば、構造層の可動部が基板表面と垂直な方向に動作する微小構造体では、微小構造体の下部を形成し、この微小構造体の下部上に犠牲層を形成し、この犠牲層上に微小構造体の上部を形成し、微小構造体の上部形成後に犠牲層をエッティング等により除去する。このようにして、中空部を有する微小構造体を形成している。

#### 【0021】

しかし、上記のように犠牲層を用いて中空部を形成すると、作製工程中に微小構造体の上部電極と微小構造体の下部電極とが強く接触すること等で破損し、又は破壊されやすくなるといった問題がある。また、上部電極と下部電極との間にスティッキングを生じることで、正常な動作ができなくなるといった問題があった。ここで、スティッキングとは、微小構造体の可動部の動作によって、上部電極と下部電極とが強く接触して離れることができない状態となる現象をいう。

#### 【0022】

更には、犠牲層を用いて中空部を形成する場合には、犠牲層が完全にエッティングされず、エッティング残りが生じることも問題となっていた。または、作製された微小構造体の上部が動作することで、微小構造体が破損し、又は破壊されることがある。これは中空部の高さが高い場合又は構造層の韌性が十分でない場合に特に顕著である。更には、中空部を設けることで、その中空部を有する構造体が反り等により変形してしまい、所望の構造が得られないという問題がある。

#### 【0023】

そこで、本発明の一態様で用いる微小構造体(MEMS)は、相対する一対の電極が空間により隔離され、可動する構造体に少なくとも一方の電極が設けられている微小構造体において、該空間に絶縁材料が充填された構成を有する。該絶縁材料は、可動部が動作する際に該絶縁材料により形成された充填材料層が変形できるよう空孔を有する材料を用いる。好ましくは、形成後に所定の処理(熱、薬液処理等)を行うことにより、軟化又は硬化する材料を用いる。

#### 【0024】

図1(A)及び図1(B)は本発明の一態様のタッチパネルを模式的に示した断面図である。

#### 【0025】

基板100上に下地膜101及び薄膜トランジスタ102が形成されている。薄膜トランジスタ102は、例えばゲート電極103、ゲート絶縁膜104、第1の半導体層105、第2の半導体層(半導体層106及び半導体層107)、導電層108、導電層10

10

20

30

40

50

9で構成される。図1(A)及び図1(B)では、導電層108及び導電層109と同材料でタッチセンサの下部電極110が形成されている。下部電極110は、薄膜トランジスタ102を構成する材料のうちいずれか一つを用いて形成すればよく、上記材料に限定されない。

【0026】

薄膜トランジスタ102を覆うように絶縁層111が形成されている。タッチセンサの下部電極110上には充填層112が形成されている。EL素子の第1の電極113と導電層108とを電気的に接続する配線114が形成されている。第1の電極113と同材料でタッチセンサの上部電極115が形成されている。なお、充填層112は変形可能な多孔質材料や弾性を有する絶縁性材料を用いることができる。また、第1の電極113と配線114とは同材料を用いて同時に形成することも可能である。

【0027】

図1(A)に示すように、充填層112は上部に膨らみを有していてもよい。また、図1(B)に示すように、充填層112の上部が平坦であってもよい。

【0028】

さらに、第1の電極113の端部及び上部電極115を覆い、且つ、上部電極115に達する開口を有する隔壁116が形成されている。前記開口にはスペーサ117が形成されている。スペーサ117は、上部電極115を介して下部電極110及び充填層112と重なる位置に設けられている。第1の電極113に接してEL層118が形成され、EL層118及び隔壁116上に第2の電極119が形成されている。

【0029】

ここで、充填層112、隔壁116、及びスペーサ117に用いる材料のうち、スペーサ117に用いる材料が最も硬い材料であり、充填層112に用いる材料が最も柔らかい材料である。硬さ及び柔らかさを示すものとして、弾性率などがあげられる。弾性率は変形しにくさを表す物性値である。弾性率で硬さ及び柔らかさを表す場合には、スペーサ117に用いる材料の弾性率は隔壁116に用いる材料の弾性率よりも高く、隔壁116に用いる材料の弾性率は充填層112に用いる材料の弾性率よりも高いといえる。

【0030】

続いて封止を行う。例えば、薄膜トランジスタ102等が形成された素子基板120の端部にシール材(図示しない)を設け、シール材によって素子基板120と封止基板121とを貼り合わせることによって封止する。図1(A)及び図1(B)に示すタッチパネルは、素子基板120、封止基板121、及びシール材で囲まれた空間122に面して発光素子が備えられた構造になっている。空間122には、不活性気体(例えば窒素やアルゴン等)が充填される。また、不活性気体の代わりにシール材を充填してもよい。

【0031】

次に、タッチパネルに指が接触した時の様子を図2に示す。

【0032】

図2のように、封止基板121の表面を指123で触ると、封止基板121が撓む。このとき、隔壁116の上部が押されて凹むが、隔壁116に用いる材料よりも硬い(弾性率が高い)スペーサ117が下に押し下げられる。スペーサ117の下層に設けられた充填層112は、スペーサ117よりも柔らかい(弾性率が低い)ため、スペーサ117は変形することなく下に押し下げられる。スペーサ117が下に押し下げられることによって、タッチセンサの上部電極115の位置が下に下がるので、タッチセンサの下部電極110と上部電極115とが接触する、もしくは下部電極110と上部電極115との距離に変化が生じる。これにより、データを入力することができる。

【0033】

本発明の一態様によれば、タッチセンサが発光素子と並置されているため、発光素子の上若しくは下にタッチセンサが設けられた場合と比べて、画質劣化の少ない、薄型のタッチパネルを提供することができる。

【0034】

10

20

30

40

50

本発明の一態様によれば、充填層、隔壁、及びスペーサに硬さの異なる材料を用いることによって、効率的にタッチセンサに入力ができる、且つ、発光素子に圧力が加わりにくい構造のタッチパネルを提供することができる。また、スペーサをタッチセンサの上部に設けることで、タッチセンサの耐久度及びセンサ感度を向上することができる。

【0035】

なお、本実施の形態は、本明細書の他の実施の形態で示した構成と適宜組み合わせて実施することができる。

【0036】

(実施の形態2)

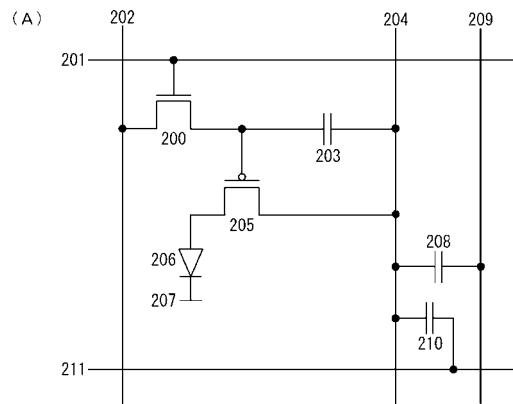

本実施の形態では、静電容量方式のタッチパネルの動作について説明する。

10

【0037】

静電容量方式のタッチセンサは、上部電極と下部電極との距離の変化によってデータが入力される。本発明の一態様は、タッチセンサとして微小構造体(MEMS)を用いる。

【0038】

タッチセンサの構造は、図1(A)、図1(B)、及び図2に示したとおりであるため、ここでは省略する。

【0039】

静電容量方式のタッチパネルは、上部電極と下部電極との間に誘電体となる絶縁性材料が設けられている。充填層112には、変形可能な多孔質材料や弾性を有する絶縁性材料を用いており、これが誘電体となる。

20

【0040】

図3(A)は、静電容量方式のタッチパネルの一画素の一態様を示したものである。図3(A)の上面図は、図12又は図22に一例として示している。

【0041】

スイッチング用トランジスタ200のゲートは、ゲート線201に電気的に接続している。スイッチング用トランジスタ200のソース及びドレインの一方は、ソース線202に電気的に接続している。第1の容量素子203の第1の端子は、スイッチング用トランジスタ200のソース及びドレインの他方に電気的に接続している。第1の容量素子203の第2の端子は、電源線204に電気的に接続している。駆動用トランジスタ205のゲートは、スイッチング用トランジスタ200のソース及びドレインの他方に電気的に接続している。駆動用トランジスタ205のソース及びドレインの一方は、発光素子206の一方の電極に電気的に接続している。発光素子206の他方の電極は、電源線207に電気的に接続している。駆動用トランジスタ205のソース及びドレインの他方は、電源線204に電気的に接続している。第2の容量素子208の第1の端子は、電源線204に電気的に接続している。第2の容量素子208の第2の端子は、カラム線209に電気的に接続している。第3の容量素子210の第1の端子は、電源線204に電気的に接続している。第3の容量素子210の第2の端子は、ロー線211に電気的に接続している。なお、第2の容量素子208及び第3の容量素子210は、タッチパネルに指等が接触することにより、容量値が変化する容量素子である。ここでは、駆動用トランジスタ205としてp型トランジスタを図示したが、n型トランジスタを用いてもよい。

30

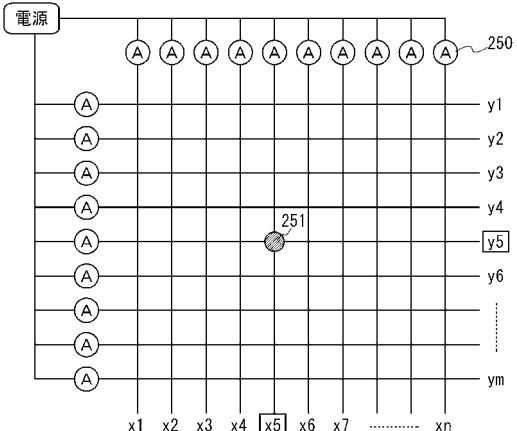

【0042】

図4は、タッチパネルに指等が接触した位置を検出するためのカラム線(×座標検出線)及びロー線(y座標検出線)を示したものである。カラム線209は、図4に示すx1～x n(nは1以上の整数)のいずれか一であり、ロー線211は、図4に示すy1～ym(mは1以上の整数)のいずれか一である。

40

【0043】

タッチセンサは上部電極、誘電体(本発明の一態様においては充填層)、及び下部電極からなる。タッチセンサの容量値は、充填層に用いた材料の誘電率と、上部電極あるいは下部電極の面積と、上部電極と下部電極との距離とによって決まる。上部電極と下部電極との距離が縮まると、容量値は大きくなる。上部電極と下部電極との距離が広がると、容

50

量値は小さくなる。

【0044】

また、タッチセンサにたまる電荷量は、容量値と、上部電極と下部電極との間の電圧とを掛け合わせたものである。上部電極と下部電極との間の電圧は変化しないので、上部電極と下部電極との距離が変化したことによって容量値に変化があったとき、タッチセンサにたまる電荷量が変化する。電荷量の変化によってカラム線209及びロー線211に電流が流れるので、電流が流れる先に検出器（検出回路）250を配置しておくことでタッチ位置251を検出することができる。

【0045】

静電容量方式のタッチパネルは、上部電極と下部電極との距離の変化によってデータが10

入力される方式であるため、軽くタッチするだけでデータ入力を行うことができる。

【0046】

なお、本実施の形態は、本明細書の他の実施の形態で示した構成と適宜組み合わせて実施することができる。

【0047】

（実施の形態3）

本実施の形態では、実施の形態2と異なる静電容量方式のタッチパネルの動作について説明する。

【0048】

図3（B）は、静電容量方式のタッチパネルの一画素の一態様を示したものである。図20

3（B）の上面図は、図13又は図23に一例として示している。

【0049】

スイッチング用トランジスタ200、ゲート線201、ソース線202、第1の容量素子203、電源線204、駆動用トランジスタ205、発光素子206、及び電源線207については、図3（A）と同様である。第2の容量素子212の第1の端子は、電源線204に電気的に接続している。第2の容量素子212の第2の端子は、カラム線213に電気的に接続している。カラム線213は、ロー線214と電気的に接続している。

【0050】

図3（A）では容量値が変化する容量素子（タッチセンサ）が2つ存在したが、図3（B）では、容量値が変化する容量素子（タッチセンサ）は1つであり、タッチパネルに指等が接触した位置を検出するためのカラム線（x座標検出線）とロー線（y座標検出線）とが電気的に接続している。したがって、図3（A）の構成では、タッチ位置をx座標、y座標それぞれで検出するが、図3（B）の構成では、x座標及びy座標を1つのタッチセンサで検出する。

【0051】

静電容量方式のタッチパネルは、上部電極と下部電極との距離の変化によってデータが入力される方式であるため、軽くタッチするだけでデータ入力を行うことができる。

【0052】

なお、本実施の形態は、本明細書の他の実施の形態で示した構成と適宜組み合わせて実施することができる。

40

【0053】

（実施の形態4）

本実施の形態では、抵抗膜方式のタッチパネルの動作について説明する。

【0054】

抵抗膜方式のタッチセンサは、上部電極と下部電極との接触によりデータが入力される。本発明の一態様は、タッチセンサとして微小構造体（MEMS）を用いる。

【0055】

タッチセンサの構造は、図1（A）及び図1（B）、図2に示したとおりであるため、ここでは省略する。

【0056】

50

抵抗膜方式のタッチパネルは、上部電極と下部電極との間に絶縁性材料が設けられている。充填層 112 には、変形可能な多孔質材料や弾性を有する絶縁性材料を用いるとよい。

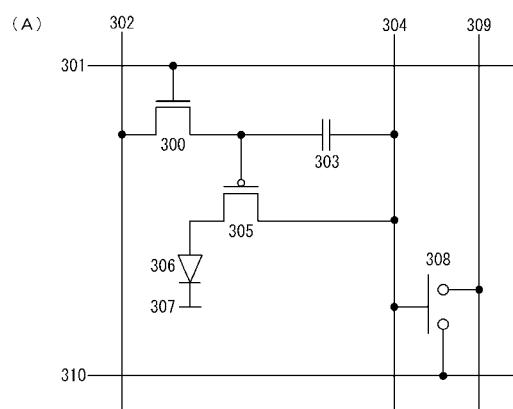

#### 【0057】

図 5 (A) は抵抗膜方式のタッチパネルの一画素の一態様を示したものである。図 5 (A) の上面図は、図 12 又は図 22 に一例として示している。

#### 【0058】

スイッチング用トランジスタ 300 のゲートは、ゲート線 301 に電気的に接続している。スイッチング用トランジスタ 300 のソース及びドレインの一方は、ソース線 302 に電気的に接続している。容量素子 303 の第 1 の端子は、スイッチング用トランジスタ 300 のソース及びドレインの他方に電気的に接続している。容量素子 303 の第 2 の端子は、電源線 304 に電気的に接続している。駆動用トランジスタ 305 のゲートは、スイッチング用トランジスタ 300 のソース及びドレインの他方に電気的に接続している。駆動用トランジスタ 305 のソース及びドレインの一方は、発光素子 306 の一方の電極に電気的に接続している。発光素子 306 の他方の電極は、電源線 307 に電気的に接続している。駆動用トランジスタ 305 のソース及びドレインの他方は、電源線 304 に電気的に接続している。スイッチ 308 の第 1 の端子は、電源線 304 に電気的に接続している。スイッチ 308 の第 2 の端子は、カラム線 309 に電気的に接続している。スイッチ 308 の第 3 の端子は、ロー線 310 に電気的に接続している。ここでは、駆動用トランジスタ 305 として p 型トランジスタを図示したが、n 型トランジスタを用いてよい。

10

20

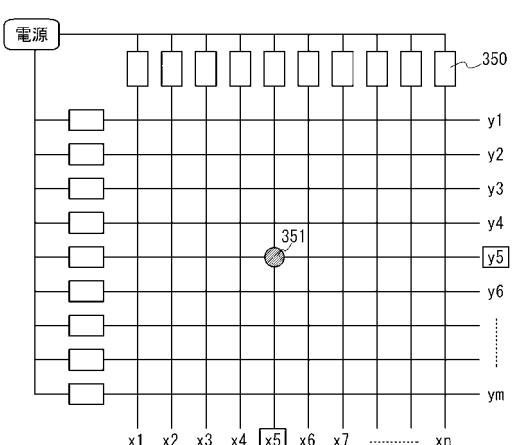

#### 【0059】

図 6 は、タッチパネルに指等が接触した位置 (タッチ位置 351) を検出するためのカラム線 (x 座標検出線) 及びロー線 (y 座標検出線) を示したものである。

#### 【0060】

指等でタッチパネルに触れると、上部電極と下部電極とが接触して、カラム線 309 及びロー線 310 にそれぞれ接続された検出器 350 に信号が入力される。検出器が電流計の場合、検出器には電流が流れ。検出器が電圧計の場合、検出器には電圧が印加される。図 5 (A) においては、x 座標をカラム線で、y 座標をロー線で検出する。

30

#### 【0061】

本実施の形態は、本明細書の他の実施の形態で示した構成と適宜組み合わせて実施することができる。

#### 【0062】

##### (実施の形態 5)

本実施の形態では、実施の形態 4 と異なる抵抗膜方式のタッチパネルの動作について説明する。

#### 【0063】

図 5 (B) は、抵抗膜方式のタッチパネルの一画素の一態様を示したものである。図 5 (B) の上面図は、図 14 又は図 24 に一例として示している。

#### 【0064】

40

スイッチング用トランジスタ 300、ゲート線 301、ソース線 302、容量素子 303、電源線 304、駆動用トランジスタ 305、発光素子 306、及び電源線 307 については、図 5 (A) と同様である。スイッチ 311 の第 1 の端子は、カラム線 312 に電気的に接続している。スイッチ 311 の第 2 の端子は、電源線 313 に電気的に接続している。図 5 (A) ではタッチセンサの上部電極が電源線 304 に電気的に接続しているが、図 5 (B) では接続していない。

#### 【0065】

指等でタッチパネルに触れると、上部電極が下部電極に接触して、カラム線 312 に接続された検出器に電源線 313 から信号が入力される。電源線 313 の電位や検出器の構成は x 座標及び y 座標を検出できるよう工夫が必要である。これにより、タッチ位置を知

50

ることができる。

【0066】

本実施の形態は、本明細書の他の実施の形態で示した構成と適宜組み合わせて実施することができる。

【0067】

(実施の形態6)

本実施の形態では、図1(A)及び図1(B)に示した充填層112に用いる材料について説明する。実施の形態1に記載したように、充填層112には、変形可能な多孔質材料や弾性を有する絶縁性材料を用いることができる。

【0068】

変形可能な多孔質材料としては、形成後に所定の処理(例えば熱処理や薬液処理等)を行うことにより、軟化又は硬化する材料が好ましい。このような材料として、例えばミクロ相分離構造を形成する、ブロックコポリマー又はグラフトコポリマーを用いることができる。

10

【0069】

ブロックコポリマーとは、複数のホモポリマー鎖がブロックとして結合した直鎖コポリマーをいう。例えば、ジブロックコポリマーが挙げられる。また、トリブロックコポリマーに代表される、3種以上のポリマー鎖が結合したブロックコポリマーを用いてもよい。

【0070】

グラフトコポリマーとは、ポリマーの主鎖に、他のポリマー鎖が側鎖として結合した構造のコポリマーをいう。側鎖として結合するポリマー鎖は、異なる種類のものであってもよい。

20

【0071】

充填層112を形成する材料としては、ブロックコポリマーを用いることが好ましい。ブロックコポリマーは、分子量分布の狭いポリマーを得やすく、組成比の制御も比較的容易だからである。充填層112を形成する材料の組成比を制御することで、充填層112の単位体積あたりに空孔が占める体積を制御することができる。そのため、単位荷重あたりの充填層112の変形量を異ならせることができる。以下に、本発明の一態様に適用することのできるブロックコポリマーについて説明する。

【0072】

30

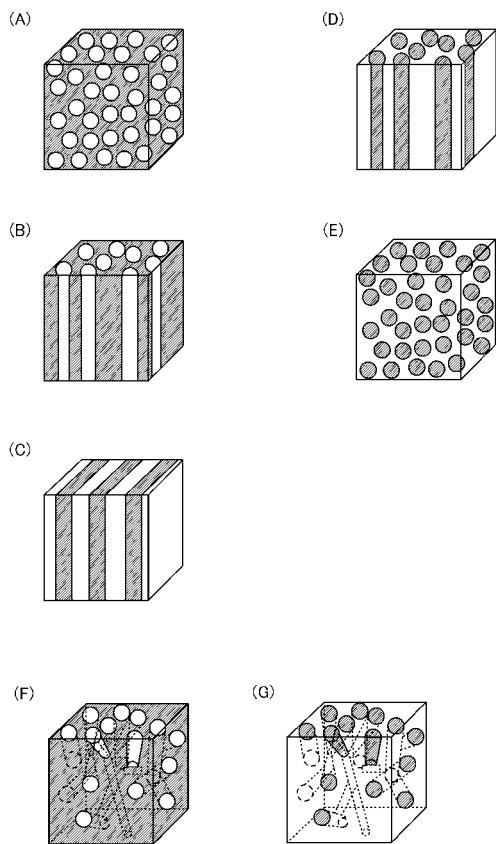

ブロックコポリマーは、ナノメートルスケールのミクロ相分離構造を自発的に形成することが知られている。例えば、A B型ブロックコポリマーではミクロ相分離により、ブロックコポリマーを構成する高分子の組成比に応じて、球構造、シリンドラー構造、ジャイロイド構造又はラメラ構造といった周期構造を形成する。なお、一方の成分の比率が概ね20%以下で球構造(図7(A)又は図7(E))となり、概ね20%以上35%以下でシリンドラー構造(図7(B)又は図7(D))となり、概ね35%以上40%以下でジャイロイド構造(図7(F)又は図7(G))となり、概ね40%以上でラメラ構造(図7(C))となる。なお、球構造では、ウエットエッティングにおいて薬液が達し難く、除去すべき一方の材料の除去が困難なため、シリンドラー構造、ジャイロイド構造又はラメラ構造とすることが好ましい。

40

【0073】

ブロックコポリマーの作製には、例えばリビング重合法を用いることができる。リビング重合法は、アニオン又はカチオンを生成する重合開始剤により一種のモノマーの重合を開始させ、他のモノマーを逐次的に添加することによって合成し、ブロックコポリマーを作製する方法である。その作製方法について以下に説明する。

【0074】

まず、ブロックコポリマーを構成する材料を溶媒に溶解させる。この溶媒は、ブロックコポリマーを構成する複数種のポリマーのすべてに対して良溶媒であることが好ましい。ここで、良溶媒とは、ブロックコポリマーを構成するポリマーの均一溶液を作製することができる溶媒をいう。ここでは、2種類のポリマーを用いるため、2種類のポリマーの均

50

一溶液を作製できればよい。例えば、ブロックコポリマーの約5重量%のトルエン溶液を、スピニコート法等により充填層112が形成される領域に塗布する。なお、スピニコート法では溶液が基板全面に塗布されるが、例えば液滴吐出法を用いることで所望の領域にのみ溶液が塗布されるため、後の工程が簡素化し、更には材料の利用効率が向上する。

【0075】

次に、該溶液が塗布された基板に対して加熱処理を行い、ミクロ相分離を誘起する。加熱処理の温度は、ブロックコポリマーを構成する成分のガラス転移点以上であり、且つ相転移温度以下に設定する。

【0076】

なお、ブロックコポリマーには様々な種類があるが、代表的にはスチレン-ブタジエン系AB型又はスチレン-イソブレン系AB型が挙げられる。その他には、PMMA (Poly methyl methacrylate) のブロックコポリマー等の、異なる材料により構成されたブロックコポリマーや、スチレン-イソブレン系のブロックコポリマーの末端に修飾基をつけたもの等がある。ブロックコポリマーの高分子セグメントとしては、例えば、ポリスチレン若しくはポリフルオレン等の疎水性芳香族炭化水素鎖、ポリブタジエン若しくはポリイソブレン等の疎水性脂肪族不飽和炭化水素鎖、ポリビニルアルコール若しくはポリエチレングリコール等の親水性脂肪族炭化水素鎖、若しくはポリスチレンスルホン酸等の親水性芳香族炭化水素鎖、ポリジメチルシロキサン等の疎水性シロキサン類又はポリフェロセン等の金属錯体等が挙げられる。そして、ブロックコポリマーは、これら高分子セグメントの二種以上が一点以上の結合点において共有結合することによって、線状、分岐状又は環状となっている。

【0077】

上記の材料には、更に溶媒を含んでいても良い。溶媒としては、例えば、ヘキサン、ヘプタン若しくはオクタン等の脂肪族炭化水素、四塩化炭素、クロロホルム若しくはジクロロメタン等のハロゲン化炭化水素、ベンゼン、トルエン若しくはキシレン等の芳香族炭化水素、アセトン若しくはメチルエチルケトン等のケトン類、ジメチルエーテル若しくはジエチルエーテル等のエーテル類、メタノール若しくはエタノール等のアルコール類又は水等が挙げられる。これらの溶媒は、形成する材料の性質又は状態に合わせて選択することができる。

【0078】

本実施の形態においては、充填層112を形成することができ、ブロックコポリマーを構成する成分の一方をエッティングで選択的に除去することができればよい。また、ABA型やBAB型でも、ブロックコポリマーの組成に応じて、球構造からラメラ構造までの様々な構造を採りうる。なお、上記したように本発明においてはシリンダー構造、ジャイロイド構造又はラメラ構造をとることが好ましい。

【0079】

なお、本実施の形態において、充填層112に適用することのできる材料は、上記材料に限定されず、複数種の物質からなり、いずれかの物質を後の工程でエッティング等により除去することができる材料であればよい。また、エッティング等で除去される物質は必ずしも一の物質でなくともよいが、エッティング等によりいずれかの物質を除去した後に、充填層112の少なくとも一の物質が除去されずに残存できることが最低限必要である。また、充填層112形成後の工程に耐えうる程度の耐熱性及び耐薬品性を要する。ここで、充填層112に除去されずに残存する物質は、弾性変形が可能な物質であることが好ましい。

【0080】

なお、本実施の形態において、上記したように充填層112はブロックコポリマーにより形成することができる。ブロックコポリマーにより充填層112を形成する場合には、充填層112を構成する一方の材料が占める体積を20%以上80%以下にすることで空隙率を概ね20%以上80%以下にすことができ、充填層112自体の形成又は充填層112が有する空孔の形成を良好に行うことができる。好ましくは空隙率を20%以上6

10

20

30

40

50

0 % 以下とする。空隙率を 20 % 以上 60 % 以下とすることで、充填層 112 はシリンダー構造、ジャイロイド構造又はラメラ構造となる。空隙率を 20 % 以上 60 % 以下とすると、シリンダー構造又はジャイロイド構造の場合であっても空孔の占める体積が充填層 112 の材料の占める体積よりも小さく、充填層 112 が密になるため、十分な機械的強度を確保することができる。更に好ましくは、空隙率を 20 % 以上 35 % 以下とする。空隙率を 20 % 以上 35 % 以下とすると、充填層 112 においてこれを構成する材料の占める体積が大きくなり、十分な機械的強度を有するシリンダー構造となるためである。

#### 【0081】

上記説明したように、充填層 112 は変形可能な多孔質材料により形成することができる。ただし、これに限定されない。例えば、充填層 112 を弾性を有する絶縁性材料により形成してもよい。弾性を有する絶縁性材料により充填層 112 を形成する場合について以下に説明する。

10

#### 【0082】

弾性を有する絶縁性材料としては、形成後に所定の処理（熱、薬液処理等）を行うことにより、軟化し、又は硬化する材料を用いることが好ましい。このような材料として、例えば、エラストマー又は熱可塑性エラストマーが挙げられる。エラストマー又は熱可塑性エラストマーを用いると、形成が行いやすいため好ましい。

#### 【0083】

なお、エラストマーとは、柔軟性及び反発弾性を有する有機系樹脂材料をいい、そのヤング率が約  $1.0 \times 10^6$  Pa 以上  $1.0 \times 10^7$  Pa 以下のものをいう。エラストマーの対義語としてプラスチマーがある。

20

#### 【0084】

充填層 112 を形成する材料としては、高分子エラストマーを用いることが好ましい。高分子エラストマーとしては、ポリウレタン樹脂、エチレン-酢酸ビニル樹脂、エチレン-エチルアクリレート樹脂、ポリエステル系樹脂、ポリアミド系樹脂、ブタジエンゴム、ブチルゴム、スチレンブタジエンゴム、ニトリルゴム、イソブレンゴム、クロロブレンゴム若しくはシリコーンゴム等の合成ゴム類、又はそれらの変形体が挙げられるが、これに限定されない。また、これらの材料の一つ又は複数種を組み合わせてもよいし、可塑剤等を添加して弾性率を調整してもよい。

#### 【0085】

30

高分子エラストマーの形成方法としては、例えば、含漬法、コーティング法、スクリーン法、グラビア法、スプレー法又は液滴吐出法等を用いればよい。これらの方法により形成する場合には、高分子エラストマーの材料を溶質として含む溶液を形成した後に、エラストマーを固化する必要がある。従って、充填層 112 として用いる高分子エラストマーは、常温乾燥型エラストマー又は常温架橋型エラストマーであることが好ましい。常温乾燥型エラストマー又は常温架橋型エラストマーを用いると、エラストマーの固化を目的とした処理（加熱処理又は乾燥処理等）が不要であり、作製工程が簡略化するからである。

#### 【0086】

なお、常温乾燥型エラストマー又は常温架橋型エラストマーとしては、常温で乾燥するもの又は常温で架橋を形成するもののみならず、常温よりやや高い温度で乾燥するもの又は常温よりやや高い温度で架橋を形成するものも含まれる。また、常温乾燥型エラストマーにおける溶媒は、沸点が常温と同程度のものよりも常温よりやや高い程度の温度のものを用いることが好ましい。沸点が常温に近いものでは形成時に沸騰が起こる可能性があるからである。例えば、塩化メチレン（沸点：40）又はアセトン（沸点：56）等よりもベンゼン（沸点：80）又はクロロホルム（沸点：61）を用いることが好ましい。更には、一定時間以上放置することで蒸発しうる溶媒すべてを用いることができる。

40

#### 【0087】

なお、常温とは、一般には概ね 15 以上 25 以下の温度範囲をいうが、本発明はこれに限定されない。常温乾燥型エラストマー又は常温架橋型エラストマーとしては、約 0 以上約 100 以下で乾燥するもの又は約 0 以上約 100 以下で架橋を形成するも

50

のを用いればよい。勿論、乾燥又は架橋の形成が上記温度範囲内で低温であることが好ましい。

【0088】

充填層112として用いるエラストマー又は熱可塑性エラストマーの形成方法として、最も好ましくはスピンドルコーティング法を用いる。スピンドルコーティング法を用いることで、充填層112の厚さ及び膜質にむらを生じることなく形成できるからである。充填層112の厚さ及び膜質の均一性を高くすることで、充填層112の強度分布におけるむらの発生を防止することができるため、歩留まり及び信頼性が向上し、好ましい。

【0089】

常温乾燥型エラストマーは、常温で揮発する有機溶剤に高分子エラストマーの固形物を溶解させることで作製することができる。例えば、溶剤希釈型ウレタン又は溶剤希釈型アクリル等を用いればよい。

10

【0090】

常温架橋型エラストマーは、空気中の水分を吸収して硬化する湿気硬化型又は紫外光(UV)、電子ビーム(EB)若しくは可視光等のエネルギーによって硬化するもの(UV硬化型、EB硬化型若しくは可視光硬化型)を用いればよい。可視光硬化型を用いる場合には、可視光を遮断した空間にて所定の処理を行い、エラストマーの硬化時にのみ可視光に暴露すればよい。可視光硬化型を用いることで、既に形成している層に紫外光又は電子ビーム等を照射することなく充填層112を形成することができるため、紫外光又は電子ビーム等を照射するための設備が不要であり、好ましい。これらは、エラストマーを有機溶剤等に溶解させ、またはエラストマーを水に分散させ、または溶剤等の媒体を用いることなく作製することができる。

20

【0091】

高分子エラストマーの固形物を水に分散させて塗布する場合には、均一に形成することが困難である。ソリッドインクは疎水性の成分が多いためである。従って、エラストマーを水に分散させることなく形成することができる。常温架橋型としては、例えば湿気硬化ウレタン樹脂又は紫外線硬化アクリル樹脂等を用いることができる。常温乾燥型エラストマー及び常温架橋型エラストマーでは特に高温にすることなく形成することができ、既に形成している層を変質等させることなく充填層112を形成することができる。

30

【0092】

また、エラストマーは所望の形状に加工することが困難であるため熱可塑性エラストマーを用いてもよい。熱可塑性エラストマーを用いることで、成形が容易になるため好ましい。すなわち、様々な形状に加工することや、精度よく加工することができるため好ましい。

【0093】

なお、熱可塑性エラストマーとは、常温では柔軟性及び反発弹性等を有し、加熱により塑性を発現するエラストマーをいう。熱可塑性エラストマーには、ウレタン系、スチレン系、ビニル系又はエステル系等があるが、特定の材料に限定されない。または、所定の処理を行うことにより可塑性を発現する材料を用いてもよい。

【0094】

なお、充填層112として多孔質材料を用いる場合には、ブロックコポリマーに含まれる材料のいずれかをエッティング除去する必要がある。以下に、ブロックコポリマーに含まれる材料のいずれかをエッティング除去する工程について説明する。

40

【0095】

ブロックコポリマーの一方の成分の除去には、ドライエッティング又はウエットエッティングを用いることができる。例えば、酸素ガス雰囲気におけるRIE(Reactive Ion Etching)法を用いることができる。ブロックコポリマー中における、除去すべき成分と残存させるべき成分との間のエッティングレートが大きく異なる条件を採用することができる。一般に、ポリマーの分子鎖に含まれる単位分子あたりの炭素分子の含有率が高いほどエッティング耐性が高く、セグメントあたりの酸素分子の含有率が高いほ

50

ドエッティング耐性が低い。例えば、P S - P M M A ( P o l y s t y r e n e - P o l y m e t h y l m e t h a c r y l a t e ) のブロックコポリマーでは、P S ( ポリスチレン ) が芳香環を含んでいるため炭素分子の含有率が高い。そのためエッティング耐性が高く、P A A M ( P o l y a c r y l a m i d e ) は酸素分子の含有率が高いためエッティング耐性が低い。R I E 法を用いた場合には、一般には、この 2 種類の間に 4 倍近いエッティングレートの差がある。

【 0 0 9 6 】

なお、上記のエッティングに用いるガスは酸素ガスに限定されず、C F <sub>4</sub>、H <sub>2</sub>、C <sub>2</sub> F <sub>6</sub>、C H F <sub>3</sub>、C H <sub>2</sub> F <sub>2</sub>、C F <sub>3</sub> B r、N F <sub>3</sub>、C l <sub>2</sub>、C C l <sub>4</sub>、H B r、S F <sub>6</sub> 等を用いてもよい。

10

【 0 0 9 7 】

なお、エッティングレートは、ブロックコポリマーのモノマー単位により決定される。モノマー単位の総原子数をN、モノマー単位の炭素原子数をN c、モノマー単位の酸素原子数をN oと表すと、エッティングレートはN / ( N c - N o ) に比例することが知られている。

【 0 0 9 8 】

しかし、上記のドライエッティング法では、シリンドラー構造等の場合には問題ないが、球構造ではエッティングされない部分が多く存在するおそれがある。そこで、球構造の場合には、ウエットエッティング法を用いるとよい。ウエットエッティング法では、形成したブロックコポリマーの材料に応じて一方の成分をエッティングすることが可能であり、且つ他方の成分に対しては、エッティング耐性の高い条件によりエッティングを行えばよい。しかし、上記の事情を勘案して、より好ましくは、充填層 1 1 2 にシリンドラー構造、ジャイロイド構造又はラメラ構造を用いる。

20

【 0 0 9 9 】

また、除去すべき成分の除去方法は、必ずしもエッティングに限定されない。可能であれば、除去すべき一方の成分を加熱処理等により蒸発又は昇華させる等により除去しても良い。

【 0 1 0 0 】

ブロックコポリマーを用いた場合には、上記工程により充填層 1 1 2 の作製が完了する。

30

【 0 1 0 1 】

なお、図 1 ( A ) 及び ( B ) において、充填層 1 1 2 は、充填層 1 1 2 に用いる材料を絶縁層 1 1 1 の開口部に充填して形成される。または、充填層 1 1 2 に用いる材料を絶縁層 1 1 1 上に形成した後、所望の形状に加工することによって形成される。

【 0 1 0 2 】

本発明の一態様の微小構造体は、従来の微小構造体とは異なり、上部電極と下部電極との間に変形が可能な材料が充填されている。そのため、中空部を有する従来の微小構造体よりも機械的強度の高い微小構造体を作製することができる。機械的強度が向上することで、作製工程中又は動作中の不良の発生を防ぐことができるため、歩留まりが向上し、信頼性が向上する。

40

【 0 1 0 3 】

なお、本実施の形態は、本明細書の他の実施の形態で示した構成と適宜組み合わせて実施することができる。

【 0 1 0 4 】

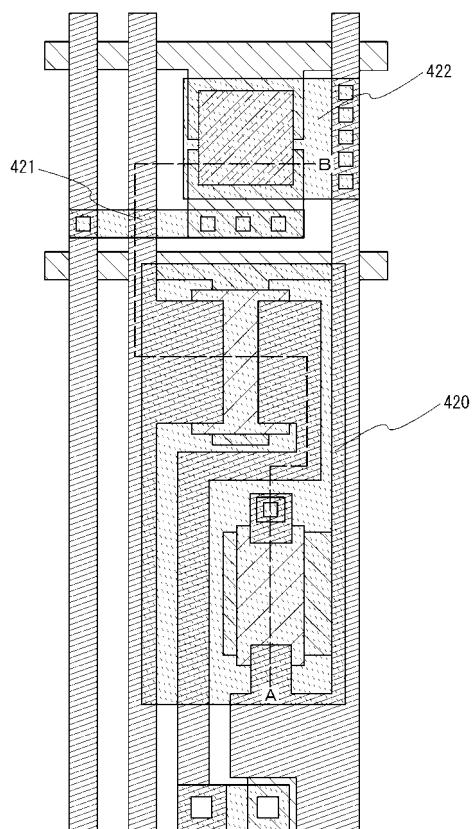

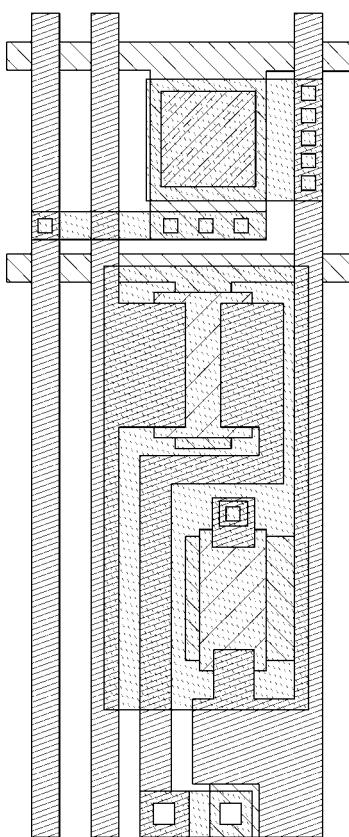

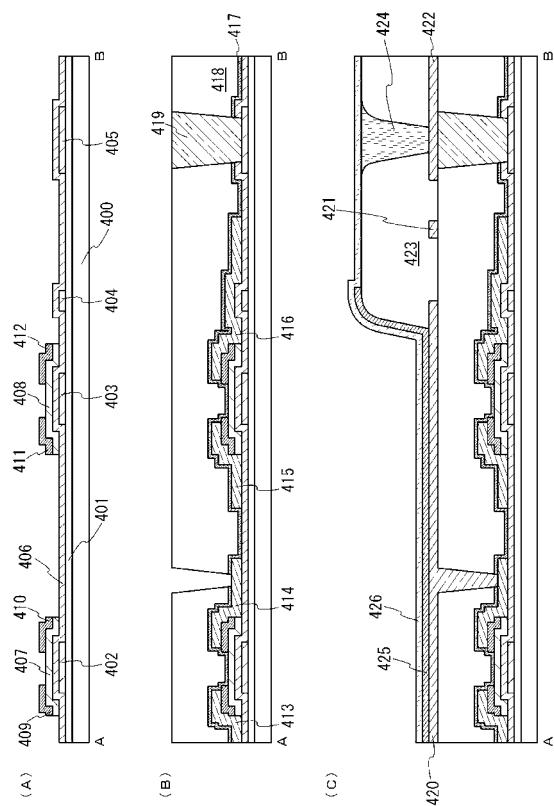

( 実施の形態 7 )

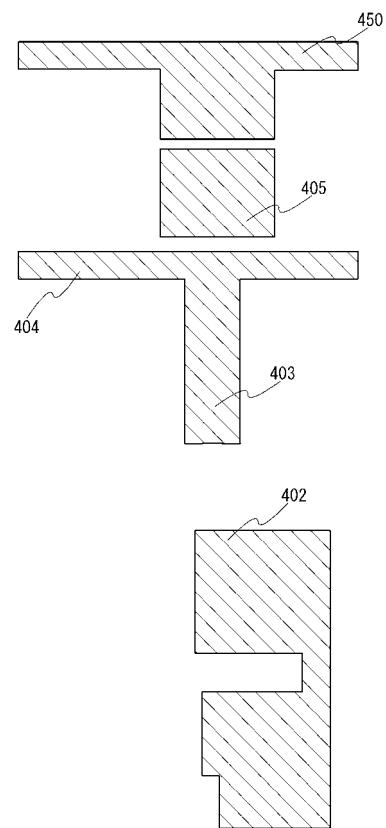

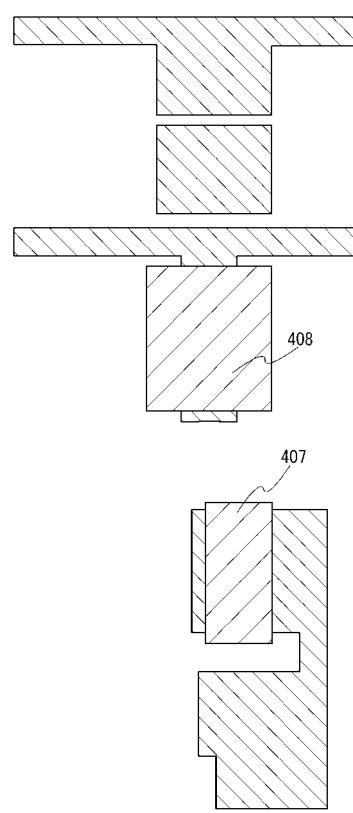

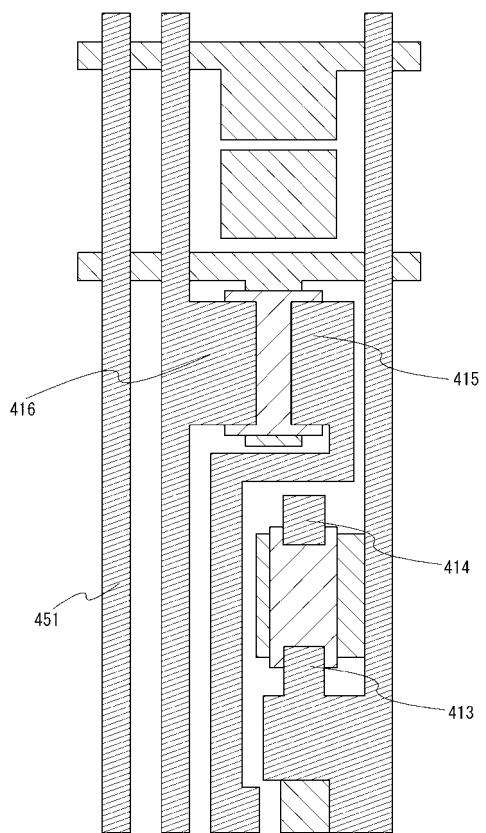

本実施の形態では、本発明の一態様であるタッチパネルの構造について、図 8 ~ 図 1 2 、図 1 5 ~ 図 1 7 を用いて説明する。図 8 ~ 図 1 2 は本発明の一態様であるタッチパネルの一画素分の上面図であり、図 1 5 ~ 図 1 7 は図 1 2 の A - B 断面図である。なお、図の簡略化のため、図 8 ~ 1 2 には、ゲート電極 4 0 2 、4 0 3 、配線 4 0 4 、下部電極 4 0 5 、ロー線 ( y 座標検出線 ) 4 5 0 、第 1 の半導体層 4 0 7 及び 4 0 8 、導電層 4 1 3 ~

50

416、カラム線（×座標検出線）451、充填層419、第1の電極420、配線421、及び上部電極422を図示する。また、本実施の形態で説明するタッチパネルは、実施の形態2で説明した静電容量方式のタッチセンサ、又は実施の形態4で説明した抵抗膜方式のタッチセンサを用いたタッチパネルである。

【0105】

基板400上に下地膜401を形成する（図15（A））。基板400は、バリウムホウケイ酸ガラス、アルミニノホウケイ酸ガラス、もしくはアルミニシリケートガラスなど、ヒュージョン法やフロート法で作製されるガラス基板、セラミック基板の他、トランジスタの処理温度に耐えうる耐熱性を有するプラスチック基板等を用いることができる。また、ステンレス合金などの金属基板の表面に絶縁膜を設けた基板を適用しても良い。

10

【0106】

下地膜401は、酸化シリコン系材料膜又は窒化シリコン系材料膜等により絶縁膜を単層で、又は積層して形成する。なお、酸化シリコン系材料とは、酸素とシリコンとを主成分とする酸化シリコン、又は酸化シリコンが窒素を含有し、且つ、酸素の含有量が窒素の含有量よりも多い酸化窒化シリコンをいう。窒化シリコン系材料とは、窒素とシリコンとを主成分とする窒化シリコン、又は窒化シリコンが酸素を含有し、窒素の含有量が酸素の含有量よりも多い窒化酸化シリコンをいう。

【0107】

下地膜401上にトランジスタを形成する。トランジスタはどのような形状であってもよく、また、どのような方法で作製されていてもよい。本実施の形態ではボトムゲート型（逆スタガ型）構造であり、特にチャネルエッチ型と呼ばれる構造のトランジスタについて説明する。

20

【0108】

下地膜401上にゲート電極402及び403、配線404、及び微小構造体（MEMS）の下部電極405を形成する（図8及び図15（A））。下地膜401上に導電膜を形成した後、図8のようにエッチングする。したがって、ゲート電極402及び403、配線404、及び下部電極405は同材料で形成されている。ゲート電極402及び403、配線404、及び下部電極405はチタン、モリブデン、タンタル、クロム、タンガステン、アルミニウム、ネオジム、銅、銀、金、白金、ニオブ、シリコン、亜鉛、鉄、バリウム、ゲルマニウムなどの導電性を有する金属もしくは半導体材料、又はこれらの合金材料を用いて、スパッタリング法又はCVD法等により形成することができる。また、2種以上の導電性を有する材料を積層することで形成してもよい。また、ゲート電極402及び403の側面をテーパ形状にエッチングしてもよい。なお、図8において、450はロー線（y座標検出線）である。ロー線450はゲート電極402及び403、配線404、及び下部電極405と同材料で形成される。

30

【0109】

ゲート電極402及び403、配線404、及び下部電極405上に絶縁膜406を形成する（図15（A））。絶縁膜406は酸化シリコン系材料又は窒化シリコン系材料等を用いて、プラズマCVD法又はスパッタリング法等により形成することができる。また、絶縁膜406は高密度プラズマ処理によって形成することもできる。ここで、高密度プラズマ処理とは、プラズマ密度が $1 \times 10^{11} \text{ cm}^{-3}$ 以上、好ましくは $1 \times 10^{11} \text{ cm}^{-3}$ 以上 $9 \times 10^{15} \text{ cm}^{-3}$ 以下で、マイクロ波（例えば周波数2.45GHz）等の高周波を用いたプラズマ処理をいう。このような条件でプラズマを発生させると、低電子温度が0.2eV以上2.0eV以下となる。このように低電子温度の高密度プラズマは、活性種の運動エネルギーが低いためプラズマダメージが少なく、欠陥の少ない膜を形成することを可能とする。このように、高密度プラズマ処理により形成された絶縁膜は、当該絶縁膜と絶縁膜に接触する層との間の界面状態が良好になる。そのため、高密度プラズマ処理を用いて絶縁膜406を形成すると、半導体層との界面状態を良好にすることができる。その結果、半導体素子の電気的特性を向上させることができる。

40

【0110】

50

絶縁膜406上に第1の半導体層407及び408を形成する(図9及び図15(A))。第1の半導体層407は、絶縁膜406を介してゲート電極402と重なる位置に形成する。第1の半導体層408は、絶縁膜406を介してゲート電極403と重なる位置に形成する。第1の半導体層407及び408は、アモルファスシリコン(a-Si:H)等の非結晶性を有する半導体層、微結晶シリコン( $\mu$ -Si:H)、多結晶シリコン、単結晶シリコン、ヒ化ガリウム(GaAs)等の化合物半導体又は酸化亜鉛(ZnO)、In-Ga-Zn-O系等の酸化物半導体等を用いて、フォトリソグラフィ法、インクジェット法又は印刷法等により形成することができる。なお、第1の半導体層407及び408は、トランジスタのチャネル領域として機能する部分を含む。

## 【0111】

10

アモルファスシリコン(a-Si:H)または微結晶シリコンを第1の半導体層407及び408として用いる場合は、トランジスタの特性の均一性が高く、かつ、製造コストが小さいという利点がある。特に、対角の長さが500mmを超えるような大型の基板にトランジスタを作製する場合に有効である。

## 【0112】

第1の半導体層407及び408として、多結晶シリコンを用いる場合は、トランジスタの移動度が高く、かつ、製造コストが小さいという利点がある。さらに、特性の経年劣化が小さいため、信頼性の高い装置を得ることができる。

## 【0113】

20

第1の半導体層407及び408として、酸化物半導体を用いる場合は、アモルファスシリコンを用いた薄膜トランジスタよりも高い電界効果移動度を得ることができる。酸化物半導体膜はスパッタ法などによって300以下の温度で膜形成が可能であり、多結晶シリコンを用いた薄膜トランジスタよりも製造工程が簡単である。

## 【0114】

なお、本明細書中で用いることができる酸化物半導体の一例としては、 $InMO_3$ ( $ZnO$ )<sub>m</sub>( $m > 0$ )で表記されるものがある。ここで、Mは、ガリウム(Ga)、鉄(Fe)、ニッケル(Ni)、マンガン(Mn)及びコバルト(Co)から選ばれた一の金属元素又は複数の金属元素を示す。例えばMとしてGaが選択される場合には、Gaのみの場合の他に、GaとNiや、GaとFeなど、Ga以外の上記金属元素が選択される場合を含む。また、上記酸化物半導体において、Mとして含まれる金属元素の他に、不純物元素としてFe、Niその他の遷移金属元素、又は該遷移金属の酸化物が含まれているものがある。本明細書においては、上記酸化物半導体のうち、Mとして少なくともガリウムを含むものをIn-Ga-Zn-O系酸化物半導体と呼び、当該材料を用いた薄膜をIn-Ga-Zn-O系非単結晶膜と呼ぶことがある。

30

## 【0115】

第1の半導体層407上に第2の半導体層409及び410を形成し、第1の半導体層408上に第2の半導体層411及び412を形成する(図15(A))。第2の半導体層409はソース及びドレインの一方として機能する部分を含む。第2の半導体層410はソース及びドレインの他方として機能する部分を含む。第2の半導体層411はソース及びドレインの一方として機能する部分を含む。第2の半導体層412はソース及びドレインの他方として機能する部分を含む。なお、第2の半導体層としては、リン等を含んだシリコン、第1の半導体層よりも導電率の高い半導体材料、第1の半導体層よりもキャリア濃度の高い酸化物半導体等を用いることができる。第2の半導体層は、その機能により、バッファ層又はn<sup>+</sup>層と表すこともできる。

40

## 【0116】

第2の半導体層409、410、411及び412上に導電層413、414、415及び416を形成する(図10及び図15(B))。導電層413はソース及びドレインの一方として機能する部分を含む。導電層414はソース及びドレインの他方として機能する部分を含む。導電層415はソース及びドレインの一方として機能する部分を含む。導電層416はソース及びドレインの他方として機能する部分を含む。導電層413、4

50

14、415及び416は、チタン、モリブデン、タンタル、クロム、タングステン、アルミニウム、ネオジム、銅、銀、金、白金、ニオブ、シリコン、亜鉛、鉄、バリウム、ゲルマニウムなどの導電性を有する金属もしくは半導体材料、又はこれらの合金材料を用いて、スパッタリング法又はCVD法等により形成することができる。なお、図10において、451はカラム線(×座標検出線)である。カラム線451は導電層413、414、415及び416と同材料で形成される。

【0117】

導電層413、414、415及び416上にパッシベーション膜417を形成する(図15(B))。パッシベーション膜417としては窒化シリコン等の絶縁膜を用いることができる。

10

【0118】

パッシベーション膜417上に絶縁層418を形成する(図15(B))。絶縁層418は、酸化シリコン系材料膜又は窒化シリコン系材料膜により形成する。また、絶縁層418としては、ポリイミド、ポリアミド、アクリル(感光性アクリルを含む)、BCB(ベンゾシクロブテン)といった有機樹脂を用いることもできる。また、絶縁層418は単層構造でも積層構造でもよい。

【0119】

絶縁層418をエッティングすることによって、導電層414の一部及び下部電極405の一部を露出させ、コンタクトホールを形成する。次に、形成したコンタクトホールを埋めるように、充填層419を形成する(図11及び図15(B))。充填層419としては、変形可能な多孔質材料や弾性を有する絶縁性材料が挙げられ、実施の形態6に記載した材料を用いることができる。

20

【0120】

なお、充填層419は、充填層419に用いる材料を絶縁層418のコンタクトホールに充填して形成される。または、充填層419に用いる材料を絶縁層418上に形成した後、所望の形状に加工することによって形成される。

【0121】

絶縁層418及び充填層419上に導電層を形成し、所望の形状にエッティングすることで第1の電極420、配線421、及び微小構造体(MEMS)の上部電極422となる(図12及び図15(C))。上部電極422は充填層419を介して下部電極405と重なる位置に形成される。第1の電極420、配線421、及び上部電極422はチタン、モリブデン、タンタル、クロム、タングステン、アルミニウム、ネオジム、銅、銀、金、白金、ニオブ、シリコン、亜鉛、鉄、バリウム、ゲルマニウムなどの導電性を有する金属もしくは半導体材料、又はこれらの合金材料を用いて、スパッタリング法又はCVD法等により形成することができる。

30

【0122】

第1の電極420の端部を覆い、且つ、上部電極422に達する開口を有する隔壁423を形成する(図15(C))。隔壁423としては、有機樹脂膜、無機絶縁膜、又は有機ポリシロキサンを用いることができる。具体的には、ポリイミド、ポリアミド、ポリイミドアミド、アクリル、ベンゾシクロブテン系樹脂を用いて形成すると良い。特に、感光性の材料を用いて、第1の電極420及び上部電極422上に開口を形成し、その開口の側壁が連続した曲率を持って形成される傾斜面となるように形成することが好ましい。

40

【0123】

上部電極422に達する隔壁423の開口を埋めるようにスペーサ424を形成する(図15(C))。スペーサ424としては紫外線硬化型樹脂等を用いることができる。具体的には、紫外線硬化型アクリル樹脂等を用いて形成するとよい。なお、スペーサ424は下部電極405と重なる位置に形成する。

【0124】

ここで、充填層419、隔壁423、及びスペーサ424に用いる材料のうち、スペーサ424に用いる材料が最も硬い材料であり、充填層419に用いる材料が最も柔らかい

50

材料である。硬さ及び柔らかさを示すものとして、弾性率などがあげられる。弾性率は変形しにくさを表す物性値である。弾性率で硬さ及び柔らかさを表すならば、スペーサ 424 に用いる材料の弾性率は隔壁 423 に用いる材料の弾性率よりも高く、隔壁 423 に用いる材料の弾性率は充填層 419 に用いる材料の弾性率よりも高いといえる。

【0125】

第 1 の電極 420 上に E L 層 425 を形成する(図 15 (C))。E L 層 425 には、正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層、正孔阻止層等が含まれる。E L 層 425 に用いる材料は適宜選択すればよい。

【0126】

E L 層 425 及び隔壁 423 上に第 2 の電極 426 を形成する(図 15 (C))。第 1 の電極 420、E L 層 425、及び第 2 の電極 426 で発光素子を構成している。第 2 の電極 426 は透光性を有する導電性材料により形成することができる。透光性を有する導電性材料としては、インジウム錫酸化物(以下、ITO という)、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、又は酸化シリコンを添加したインジウム錫酸化物等が挙げられる。透光性を有する導電性材料の膜の形成はスパッタリング法又は CVD 法等により行えばよいが、特定の方法に限定されるものではない。また、第 2 の電極 426 は単層構造でもよいし、積層構造としてもよい。

【0127】

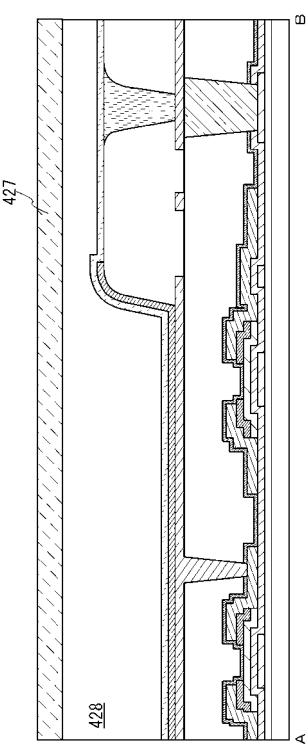

以上の工程により、素子基板が作製できる。続いて、素子基板の端部にシール材(図示せず)を設け、シール材によって素子基板と封止基板 427 とを貼り合わせることによって封止する(図 16)。本発明の一態様であるタッチパネルは、素子基板、封止基板 427、及びシール材で囲まれた空間 428 に発光素子が備えられた構造になっている。空間 428 には、不活性気体(例えば窒素やアルゴン等)が充填される。また、不活性気体の代わりにシール材を充填してもよい。

【0128】

なお、シール材にはエポキシ系樹脂を用いるのが好ましい。また、これらの材料はできるだけ水分や酸素を透過しない材料であることが望ましい。また、封止基板 427 にはガラス基板、FRP (Fiberglass-Reinforced Plastics)、PVF(ポリビニルフロライド)、ポリエステル又はアクリル等からなるプラスチック基板を用いることができる。

【0129】

次に、タッチパネルに指が接触した時の様子を図 17 に示す。

【0130】

図 17 のように、封止基板 427 を指 429 で押すと、封止基板 427 が撓む。このとき、隔壁 423 の上部が押されて凹むが、隔壁 423 に用いる材料よりも硬い(弾性率が高い)スペーサ 424 が下に押し下げられる。スペーサ 424 の下層に設けられた充填層 419 は、スペーサ 424 よりも柔らかい(弾性率が低い)ため、スペーサ 424 は変形することなく下に押し下げられる。スペーサ 424 が下に押し下げられることによって、微小構造体(MEMS)の上部電極 422 の位置が下に下がる。静電容量方式の場合、微小構造体(MEMS)の下部電極 405 と上部電極 422 との間の距離が変化することにより、データを入力することができる。抵抗膜方式の場合、微小構造体(MEMS)の下部電極 405 と上部電極 422 とが接触することにより、データを入力することができる。

【0131】

本発明の一態様によれば、薄膜トランジスタ及び発光素子を作製する工程において、タッチセンサを作製することができる。

【0132】

本発明の一態様によれば、タッチセンサが発光素子と並置されているため、発光素子の

10

20

30

40

50

上下にタッチセンサが設けられた場合と比べて、画質劣化の少ない、薄型のタッチパネルを提供することができる。

【0133】

本発明の一態様によれば、充填層、隔壁、及びスペーサに硬さの異なる材料を用いることによって、効率的にタッチセンサに入力ができる、且つ、発光素子に圧力が加わりにくい構造のタッチパネルを提供することができる。また、スペーサをタッチセンサの上部に設けることで、タッチセンサの耐久度及びセンサ感度を向上することができる。

【0134】

なお、本実施の形態は、本明細書の他の実施の形態で示した構成と適宜組み合わせて実施することができる。

10

【0135】

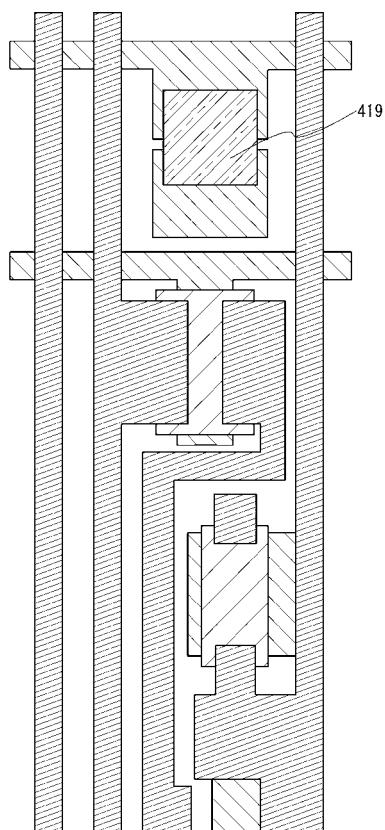

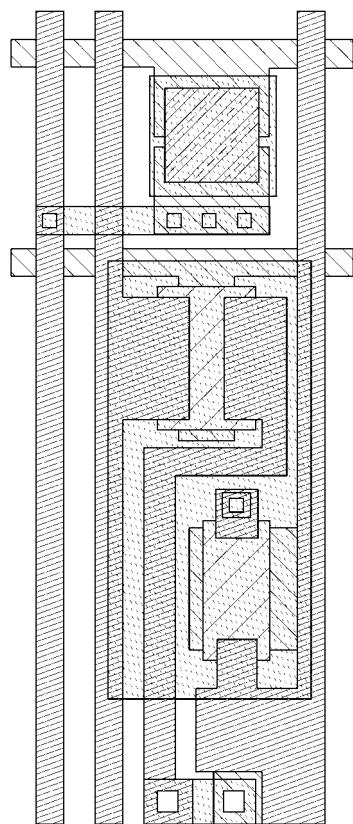

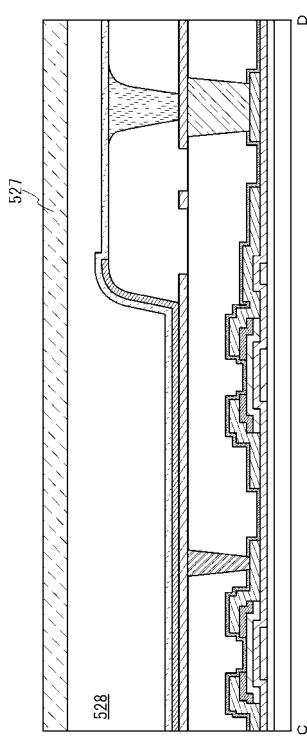

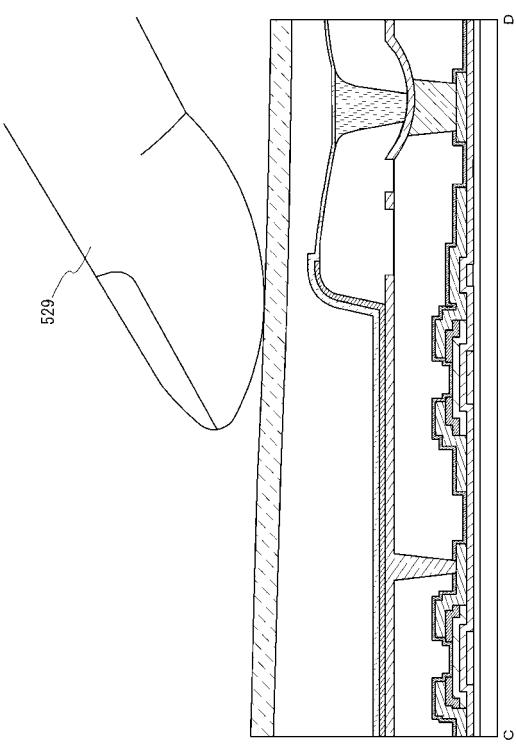

(実施の形態8)

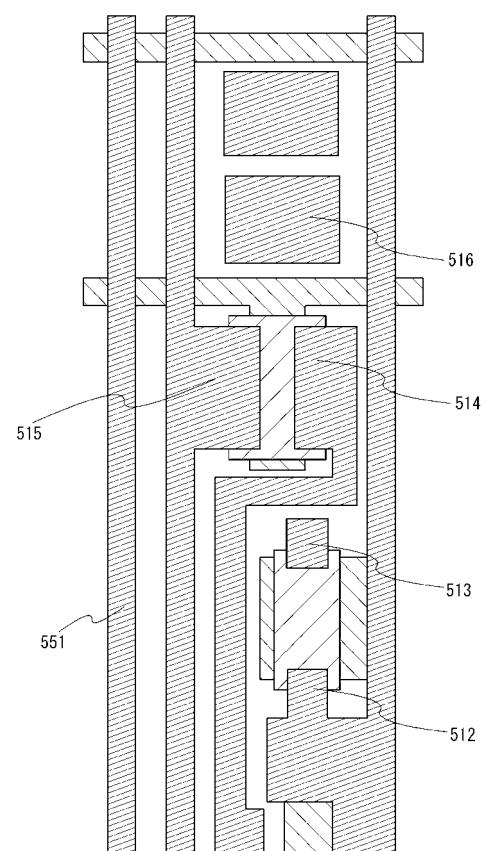

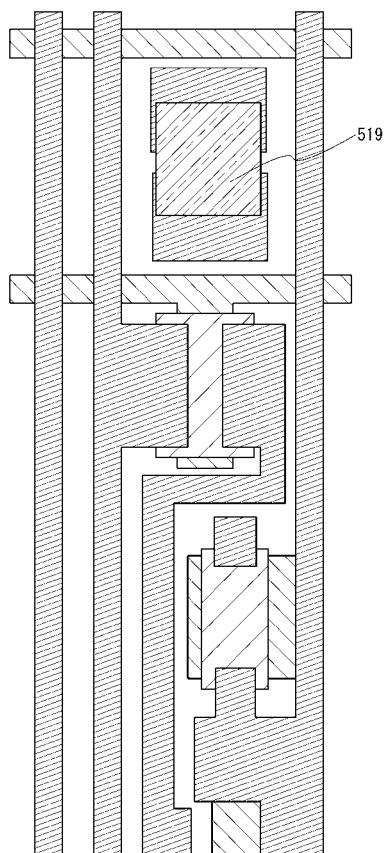

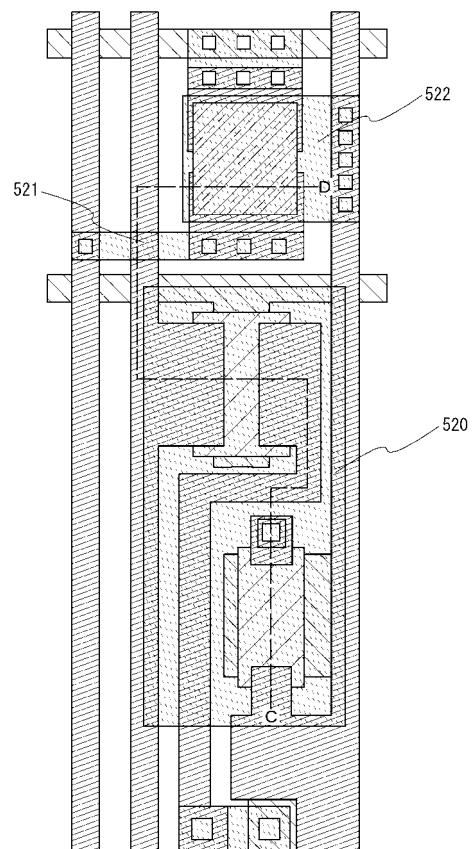

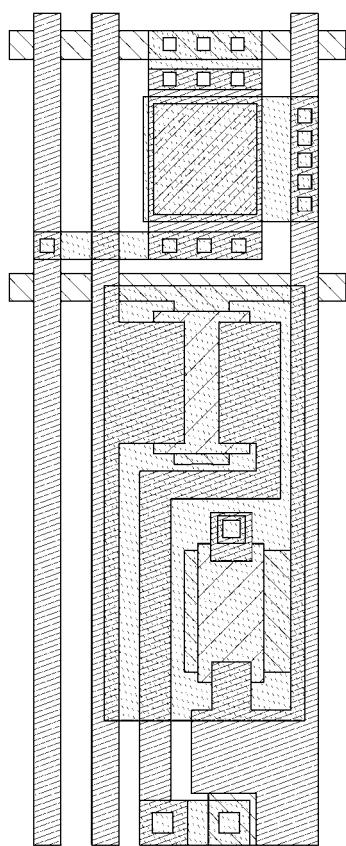

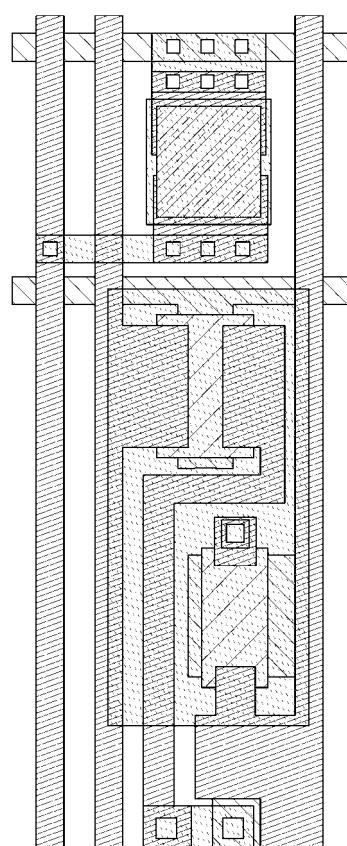

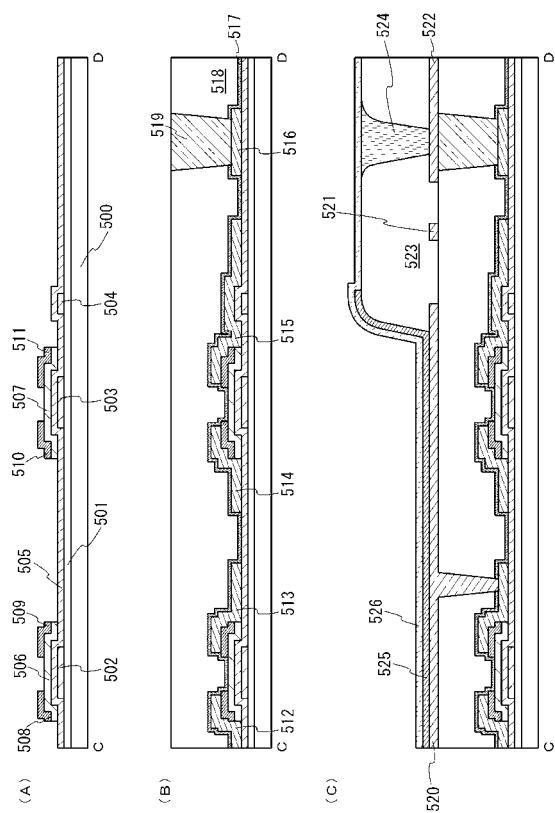

本実施の形態では、実施の形態7と異なるタッチパネルの構造について、図18～図22、図25～図27を用いて説明する。図18～図22は本発明の一態様であるタッチパネルの一画素分の上面図であり、図25～図27は図22のC-D断面図である。なお、図の簡略化のため、図18～図22では、ゲート電極502及び503、配線504、ロー線(y座標検出線)550、第1の半導体層506及び507、導電層512～515、下部電極516、カラム線(x座標検出線)551、充填層519、第1の電極520、配線521、及び上部電極522を図示する。また、本実施の形態で説明するタッチパネルは、実施の形態2で説明した静電容量方式のタッチセンサ、又は実施の形態4で説明した抵抗膜方式のタッチセンサを用いたタッチパネルである。

20

【0136】

基板500上に下地膜501を形成する(図25(A))。基板500は、バリウムホウケイ酸ガラス、アルミニノホウケイ酸ガラス、もしくはアルミニシリケートガラスなど、ヒュージョン法やフロート法で作製されるガラス基板、セラミック基板の他、トランジスタの処理温度に耐えうる耐熱性を有するプラスチック基板等を用いることができる。また、ステンレス合金などの金属基板の表面に絶縁膜を設けた基板を適用しても良い。

【0137】

下地膜501は、酸化シリコン系材料膜又は窒化シリコン系材料膜等により絶縁膜を単層で、又は積層して形成する。なお、酸化シリコン系材料とは、酸素とシリコンとを主成分とする酸化シリコン、又は酸化シリコンが窒素を含有し、且つ、酸素の含有量が窒素の含有量よりも多い酸化窒化シリコンをいう。窒化シリコン系材料とは、窒素とシリコンとを主成分とする窒化シリコン、又は窒化シリコンが酸素を含有し、窒素の含有量が酸素の含有量よりも多い窒化酸化シリコンをいう。

30

【0138】

下地膜501上にトランジスタを形成する。トランジスタはどのような形状であってもよく、また、どのような方法で作製されていてもよい。本実施の形態ではボトムゲート型(逆スタガ型)構造であり、特にチャネルエッチ型と呼ばれる構造のトランジスタについて説明する。

【0139】

下地膜501上にゲート電極502及び503と、配線504とを形成する(図25(A))。下地膜501上に導電膜を形成した後、図18のようにエッチングする。ゲート電極502及び503と、配線504とはチタン、モリブデン、タンタル、クロム、タンゲステン、アルミニウム、ネオジム、銅、銀、金、白金、ニオブ、シリコン、亜鉛、鉄、バリウム、ゲルマニウムなどの導電性を有する金属もしくは半導体材料、又はこれらの合金材料を用いて、スパッタリング法又はCVD法等により形成することができる。また、2種以上の導電性を有する材料を積層することで形成してもよい。また、ゲート電極502及び503の側面をテーパ形状にエッチングしてもよい。なお、図18において、550はロー線(y座標検出線)である。ロー線550はゲート電極502及び503と、配線504と同材料で形成される。

40

50

## 【0140】

ゲート電極502及び503、及び配線504上に絶縁膜505を形成する(図25(A))。絶縁膜505は酸化シリコン系材料又は窒化シリコン系材料等を用いて、プラズマCVD法又はスパッタリング法等により形成することができる。また、絶縁膜505は高密度プラズマ処理によって形成することもできる。ここで、高密度プラズマ処理とは、

10

プラズマ密度が $1 \times 10^{11} \text{ cm}^{-3}$ 以上、好ましくは $1 \times 10^{11} \text{ cm}^{-3}$ 以上 $9 \times 10^{15} \text{ cm}^{-3}$ 以下で、マイクロ波(例えば周波数 $2.45 \text{ GHz}$ )等の高周波を用いた

プラズマ処理をいう。このような条件でプラズマを発生させると、低電子温度が $0.2 \text{ eV}$ 以上 $2.0 \text{ eV}$ 以下となる。このように低電子温度の高密度プラズマは、活性種の運動エネルギーが低いためプラズマダメージが少なく、欠陥の少ない膜を形成することを可能とする。このように、高密度プラズマ処理により形成された絶縁膜は、当該絶縁膜と絶縁膜に接触する層との間の界面状態が良好になる。そのため、高密度プラズマ処理を用いて絶縁膜505を形成すると、半導体層との界面状態を良好にすることができる。その結果、半導体素子の電気的特性を向上させることができる。

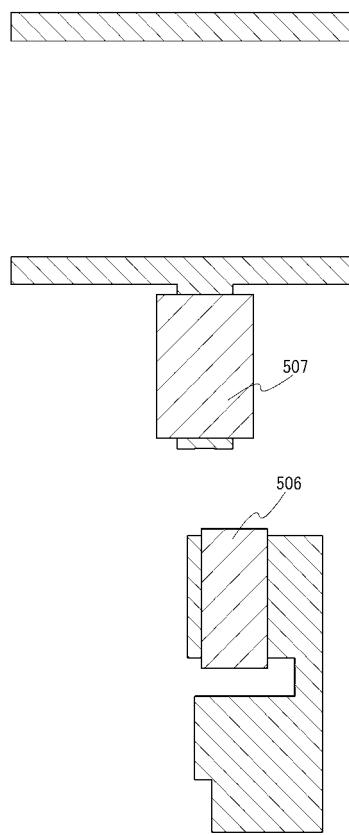

## 【0141】

絶縁膜505上に第1の半導体層506及び507を形成する(図19及び図25(A))。第1の半導体層506は、絶縁膜505を介してゲート電極502と重なる位置に形成する。第1の半導体層507は、絶縁膜505を介してゲート電極503と重なる位置に形成する。第1の半導体層506及び507は、アモルファスシリコン(a-Si:H)等の非結晶性を有する半導体層、微結晶シリコン( $\mu$ -Si:H)、多結晶シリコン、単結晶シリコン、ヒ化ガリウム(GaAs)等の化合物半導体又は酸化亜鉛(ZnO)、In-Ga-Zn-O系等の酸化物半導体等を用いて、フォトリソグラフィ法、インクジェット法又は印刷法等により形成することができる。なお、第1の半導体層506及び507は、トランジスタのチャネル領域として機能する部分を含む。

20

## 【0142】

第1の半導体層506及び507としてアモルファスシリコン(a-Si:H)または微結晶シリコンを用いる場合は、トランジスタの特性の均一性が高く、かつ、製造コストが小さいという利点がある。特に、対角の長さが $500 \text{ mm}$ を超えるような大型の基板にトランジスタを作製する場合に有効である。

## 【0143】

第1の半導体層506及び507として多結晶シリコンを用いる場合は、トランジスタの移動度が高く、かつ、製造コストが小さいという利点がある。さらに、特性の経年劣化が小さいため、信頼性の高い装置を得ることができる。

30

## 【0144】

第1の半導体層506及び507として、酸化物半導体を用いる場合は、アモルファスシリコンを用いた薄膜トランジスタよりも高い電界効果移動度を得ることができる。酸化物半導体膜はスパッタ法などによって $300$ 以下の温度で膜形成が可能であり、多結晶シリコンを用いた薄膜トランジスタよりも製造工程が簡単である。

## 【0145】

なお、本明細書中で用いることができる酸化物半導体の一例としては、 $\text{In}_n\text{MO}_3$ ( $\text{ZnO})_m$ ( $m > 0$ )で表記されるものがある。ここで、Mは、ガリウム(Ga)、鉄(Fe)、ニッケル(Ni)、マンガン(Mn)及びコバルト(Co)から選ばれた一の金属元素又は複数の金属元素を示す。例えばMとしてGaが選択される場合には、Gaのみの場合の他に、GaとNiや、GaとFeなど、Ga以外の上記金属元素が選択される場合を含む。また、上記酸化物半導体において、Mとして含まれる金属元素の他に、不純物元素としてFe、Niその他の遷移金属元素、又は該遷移金属の酸化物が含まれているものがある。本明細書においては、上記酸化物半導体のうち、Mとして少なくともガリウムを含むものをIn-Ga-Zn-O系酸化物半導体と呼び、当該材料を用いた薄膜をIn-Ga-Zn-O系非単結晶膜と呼ぶことがある。

40

## 【0146】

第1の半導体層506上に第2の半導体層508及び509を形成し、第1の半導体層507上に第2の半導体層510及び511を形成する(図25(A))。第2の半導体層508はソース及びドレインの一方として機能する部分を含む。第2の半導体層509はソース及びドレインの他方として機能する部分を含む。第2の半導体層510はソース及びドレインの一方として機能する部分を含む。第2の半導体層511はソース及びドレインの他方として機能する部分を含む。なお、第2の半導体層としては、リン等を含んだシリコン、第1の半導体層よりも導電率の高い半導体材料、第1の半導体層よりもキャリア濃度の高い酸化物半導体等を用いることができる。第2の半導体層は、その機能により、バッファ層又はn<sup>+</sup>層と表すこともできる。

## 【0147】

10

絶縁膜505及び第2の半導体層508、509、510、511上に導電層512、513、514、515、及び微小構造体(MEMS)の下部電極516を形成する(図20及び図25(B))。導電層512はソース及びドレインの一方として機能する部分を含む。導電層513はソース及びドレインの他方として機能する部分を含む。導電層514はソース及びドレインの一方として機能する部分を含む。導電層515はソース及びドレインの他方として機能する部分を含む。導電層512、513、514、515、及び下部電極516は、チタン、モリブデン、タンタル、クロム、タンゲステン、アルミニウム、ネオジム、銅、銀、金、白金、ニオブ、シリコン、亜鉛、鉄、バリウム、ゲルマニウムなどの導電性を有する金属もしくは半導体材料、又はこれらの合金材料を用いて、スパッタリング法又はCVD法等により形成することができる。なお、図20において、551はカラム線(×座標検出線)である。カラム線551は導電層512、513、514、515、及び下部電極516と同材料で形成される。

20

## 【0148】

導電層512、513、514、515、及び下部電極516上にパッシベーション膜517を形成する(図25(B))。パッシベーション膜517としては窒化シリコン等を用いることができる。

## 【0149】

30

パッシベーション膜517上に絶縁層518を形成する(図25(B))。絶縁層518は、酸化シリコン系材料膜又は窒化シリコン系材料膜により形成する。また、絶縁層518としては、ポリイミド、ポリアミド、アクリル(感光性アクリルを含む)、BCB(ベンゾシクロブテン)といった有機樹脂を用いることができる。また、絶縁層518は単層構造でも積層構造でもよい。

## 【0150】

絶縁層518をエッティングすることによって、導電層513及び下部電極516を露出させ、コンタクトホールを形成する。次に、形成したコンタクトホールを埋めるように、充填層519を形成する(図21及び図25(B))。充填層519としては変形可能な多孔質材料や弾性を有する絶縁性材料が挙げられ、実施の形態6に記載した材料を用いることができる。

## 【0151】

40

絶縁層518及び充填層519上に導電層を形成し、所望の形状にエッティングすることで第1の電極520、配線521及び微小構造体(MEMS)の上部電極522となる(図22及び図25(C))。上部電極522は充填層519を介して下部電極と重なる位置に形成される。第1の電極520、配線521及び上部電極522はチタン、モリブデン、タンタル、クロム、タンゲステン、アルミニウム、ネオジム、銅、銀、金、白金、ニオブ、シリコン、亜鉛、鉄、バリウム、ゲルマニウムなどの導電性を有する金属もしくは半導体材料、又はこれらの合金材料を用いて、スパッタリング法又はCVD法等により形成することができる。

## 【0152】

50

第1の電極520の端部を覆い、且つ、上部電極522に達する開口を有する隔壁523を形成する(図25(C))。隔壁523としては、有機樹脂膜、無機絶縁膜、又は有

機ポリシロキサンを用いることができる。具体的には、ポリイミド、ポリアミド、ポリイミドアミド、アクリル、ベンゾシクロブテン系樹脂を用いて形成すると良い。特に、感光性の材料を用いて、第1の電極520及び上部電極522上に開口を形成し、その開口の側壁が連続した曲率を持って形成される傾斜面となるように形成することが好ましい。

【0153】

上部電極522に達する隔壁523の開口を埋めるようにスペーサ524を形成する(図25(C))。スペーサ524としては紫外線硬化型樹脂等を用いることができる。具体的には、紫外線硬化型アクリル樹脂等を用いて形成するとよい。なお、スペーサ524は下部電極516と重なる位置に形成する。

【0154】

ここで、充填層519、隔壁523、及びスペーサ524に用いる材料のうち、スペーサ524に用いる材料が最も硬い材料であり、充填層519に用いる材料が最も柔らかい材料である。硬さ及び柔らかさを示すものとして、弾性率などがあげられる。弾性率は変形しにくさを表す物性値である。弾性率で硬さ及び柔らかさを表すならば、スペーサ524に用いる材料の弾性率は隔壁523に用いる材料の弾性率よりも高く、隔壁523に用いる材料の弾性率は充填層519に用いる材料の弾性率よりも高いといえる。

【0155】

第1の電極520上にEL層525を形成する(図25(C))。EL層525には、正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層、正孔阻止層等が含まれる。EL層525に用いる材料は適宜選択すればよい。

【0156】

EL層525及び隔壁523上に第2の電極526を形成する(図25(C))。第1の電極520、EL層525、及び第2の電極526で発光素子を構成している。第2の電極526は透光性を有する導電性材料により形成することができる。透光性を有する導電性材料としては、インジウム錫酸化物(以下、ITOという)、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、又は酸化シリコンを添加したインジウム錫酸化物等が挙げられる。透光性を有する導電性材料の膜の形成はスパッタリング法又はCVD法等により行えばよいが、特定の方法に限定されるものではない。また、第2の電極526は単層構造でもよいし、積層構造としてもよい。

【0157】

以上の工程により、素子基板が作製できる。続いて、素子基板の端部にシール材(図示せず)を設け、シール材によって素子基板と封止基板527とを貼り合わせることによって封止する(図26)。本発明の一態様であるタッチパネルは、素子基板、封止基板527、及びシール材で囲まれた空間528に発光素子が備えられた構造になっている。空間528には、不活性気体(例えば窒素やアルゴン等)が充填される。また、不活性気体の代わりにシール材を充填してもよい。

【0158】

なお、シール材にはエポキシ系樹脂を用いるのが好ましい。また、これらの材料はできるだけ水分や酸素を透過しない材料であることが望ましい。また、封止基板527にはガラス基板、FRP(Fiberglass-Reinforced Plastics)、PVF(ポリビニルフロライド)、ポリエステル又はアクリル等からなるプラスチック基板を用いることができる。

【0159】

次に、タッチパネルに指が接触した時の様子を図27に示す。

【0160】

図27のように、封止基板527を指529で押すと、封止基板527が撓む。このとき、隔壁523の上部が押されて凹むが、隔壁523に用いる材料よりも硬い(弾性率が高い)スペーサ524が下に押し下げられる。スペーサ524の下層に設けられた充填層

10

20

30

40

50

519は、スペーサ524よりも柔らかい（弾性率が低い）ため、スペーサ524は変形することなく下に押し下げられる。スペーサ524が下に押し下げられることによって、微小構造体（MEMS）の上部電極422の位置が下に下がる。静電容量方式の場合、微小構造体（MEMS）の下部電極516と上部電極522との間の距離が変化することにより、データを入力することができる。抵抗膜方式の場合、微小構造体（MEMS）の下部電極516と上部電極522とが接触することにより、データを入力することができる。

#### 【0161】

本発明の一態様によれば、薄膜トランジスタ及び発光素子を作製する工程において、タッチセンサを作製することができる。

10

#### 【0162】

本発明の一態様によれば、タッチセンサが発光素子と並置されているため、発光素子の上下にタッチセンサが設けられた場合と比べて、画質劣化の少ない、薄型のタッチパネルを提供することができる。

#### 【0163】

本発明の一態様によれば、充填層、隔壁、及びスペーサに硬さの異なる材料を用いることによって、効率的にタッチセンサに入力ができ、且つ、発光素子に圧力が加わりにくく構造のタッチパネルを提供することができる。また、スペーサをタッチセンサの上部に設けることで、タッチセンサの耐久度及びセンサ感度を向上することができる。

#### 【0164】

なお、本実施の形態は、本明細書の他の実施の形態で示した構成と適宜組み合わせて実施することができる。

20

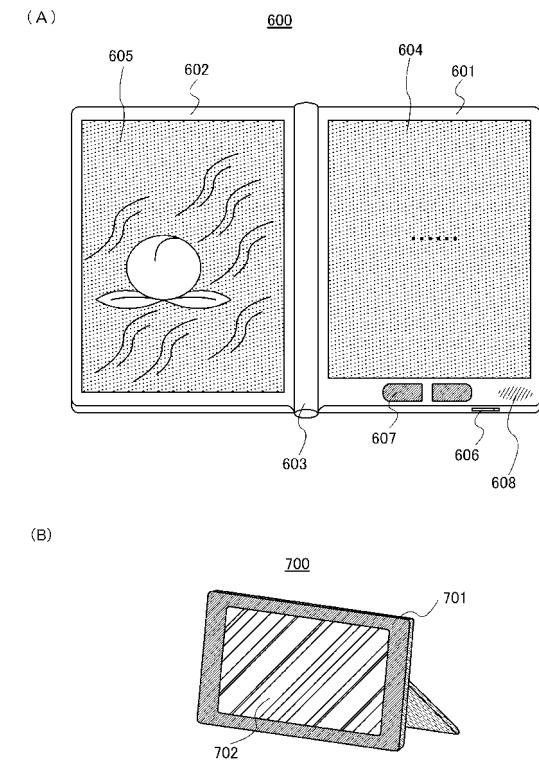

#### 【0165】

##### （実施の形態9）

本発明の一態様に係るタッチパネルはさまざまな電子機器に適用することができる。電子機器としては、例えば、テレビジョン装置（テレビ、またはテレビジョン受信機ともいう）、コンピュータ用などのモニタ、デジタルカメラ、デジタルビデオカメラなどのカメラ、デジタルフォトフレーム、携帯電話機（携帯電話、携帯電話装置ともいう）、携帯型ゲーム機、携帯情報端末、電子ペーパー、音響再生装置、パチンコ機などの大型ゲーム機などが挙げられる。電子機器の一例を図28に示す。

30

#### 【0166】

図28（A）は電子書籍600の一例を示している。例えば、電子書籍600は、筐体601及び筐体602の2つの筐体で構成されている。筐体601及び筐体602は、軸部603により一体とされており、該軸部603を軸として開閉動作を行うことができる。このような構成により、紙の書籍のような動作を行うことが可能となる。

#### 【0167】

筐体601には表示部604が組み込まれ、筐体602には表示部605が組み込まれている。表示部604および表示部605は本発明の一態様であるタッチセンサを有している。表示部604および表示部605は、継ぎ画面を表示する構成としてもよいし、異なる画面を表示する構成としてもよい。異なる画面を表示する構成として、例えば右側の表示部（図28（A）では表示部604）に文章を表示し、左側の表示部（図28（A）では表示部605）に画像を表示することができる。

40

#### 【0168】

また、図28（A）では、筐体601に操作部などを備えた例を示している。例えば、筐体601において、電源606、操作キー607、スピーカ608などを備えている。なお、筐体の表示部と同一面にキーボードやポインティングデバイスなどを備える構成としてもよい。また、筐体の裏面や側面に、外部接続用端子（イヤホン端子、USB端子、またはACアダプタおよびUSBケーブルなどの各種ケーブルと接続可能な端子など）、記録媒体挿入部などを備える構成としてもよい。さらに、電子書籍600は、電子辞書としての機能を持たせた構成としてもよい。

50

## 【0169】

また、電子書籍600は、無線で情報を送受信できる構成としてもよい。無線により、電子書籍サーバから、所望の書籍データなどを購入し、ダウンロードする構成とすることも可能である。

## 【0170】

本発明の一態様によれば、発光素子の上又は下にタッチセンサが設けられたものと比べて、画質劣化が少なく、薄型の電子書籍を提供することができる。

## 【0171】

また、本発明の一態様によれば、充填層、隔壁、及びスペーサに硬さの異なる材料を用いることによって、効率的にタッチセンサに入力することができ、且つ、発光素子に圧力が加わりにくい構造のタッチパネルを提供することができる。また、スペーサをタッチセンサの上部に設けることによって、タッチセンサの耐久度が高く、センサ感度の良い電子書籍を提供することができる。

10

## 【0172】

図28(B)は、デジタルフォトフレーム700の一例を示している。例えば、デジタルフォトフレーム700は、筐体701に表示部702が組み込まれている。表示部702は、各種画像を表示することができる。例えばデジタルカメラなどで撮影した画像データを表示させることで、通常の写真立てと同様に機能させることができる。

20

## 【0173】

本発明の一態様であるタッチセンサを適用すると、発光素子の上又は下にタッチセンサが設けられたものと比べて、画質劣化が少なく、薄型のデジタルフォトフレームを提供することができる。

## 【0174】

また、本発明の一態様によれば、充填層、隔壁、及びスペーサに硬さの異なる材料を用いることによって、効率的にタッチセンサに入力することができ、且つ、発光素子に圧力が加わりにくい構造のタッチパネルを提供することができる。また、スペーサをタッチセンサの上部に設けることによって、タッチセンサの耐久度が高く、センサ感度の良いデジタルフォトフレームを提供することができる。

## 【符号の説明】

## 【0175】

30

|     |          |

|-----|----------|

| 100 | 基板       |

| 101 | 下地膜      |

| 102 | 薄膜トランジスタ |

| 103 | ゲート電極    |

| 104 | ゲート絶縁膜   |

| 105 | 第1の半導体層  |

| 106 | 半導体層     |

| 107 | 半導体層     |

| 108 | 導電層      |

| 109 | 導電層      |

| 110 | 下部電極     |

| 111 | 絶縁層      |

| 112 | 充填層      |

| 113 | 第1の電極    |

| 114 | 配線       |

| 115 | 上部電極     |

| 116 | 隔壁       |

| 117 | スペーサ     |

| 118 | E L層     |

| 119 | 第2の電極    |

40

50

|       |               |    |

|-------|---------------|----|

| 1 2 0 | 素子基板          |    |

| 1 2 1 | 封止基板          |    |

| 1 2 2 | 空間            |    |

| 1 2 3 | 指             |    |

| 2 0 0 | スイッチング用トランジスタ |    |

| 2 0 1 | ゲート線          |    |

| 2 0 2 | ソース線          |    |

| 2 0 3 | 第1の容量素子       |    |

| 2 0 4 | 電源線           |    |

| 2 0 5 | 駆動用トランジスタ     | 10 |

| 2 0 6 | 発光素子          |    |

| 2 0 7 | 電源線           |    |

| 2 0 8 | 第2の容量素子       |    |

| 2 0 9 | カラム線          |    |

| 2 1 0 | 第3の容量素子       |    |

| 2 1 1 | ロー線           |    |

| 2 1 2 | 第2の容量素子       |    |

| 2 1 3 | カラム線          |    |

| 2 1 4 | ロー線           |    |

| 2 5 0 | 検出器(検出回路)     | 20 |

| 2 5 1 | タッチ位置         |    |

| 3 0 0 | スイッチング用トランジスタ |    |

| 3 0 1 | ゲート線          |    |

| 3 0 2 | ソース線          |    |

| 3 0 3 | 容量素子          |    |

| 3 0 4 | 電源線           |    |

| 3 0 5 | 駆動用トランジスタ     |    |

| 3 0 6 | 発光素子          |    |

| 3 0 7 | 電源線           |    |

| 3 0 8 | スイッチ          | 30 |

| 3 0 9 | カラム線          |    |

| 3 1 0 | ロー線           |    |

| 3 1 1 | スイッチ          |    |

| 3 1 2 | カラム線          |    |

| 3 1 3 | 電源線           |    |

| 3 5 0 | 検出器           |    |

| 3 5 1 | タッチ位置         |    |

| 4 0 0 | 基板            |    |

| 4 0 1 | 下地膜           |    |

| 4 0 2 | ゲート電極         | 40 |

| 4 0 3 | ゲート電極         |    |

| 4 0 4 | 配線            |    |

| 4 0 5 | 下部電極          |    |

| 4 0 6 | 絶縁膜           |    |

| 4 0 7 | 第1の半導体層       |    |

| 4 0 8 | 第1の半導体層       |    |

| 4 0 9 | 第2の半導体層       |    |

| 4 1 0 | 第2の半導体層       |    |

| 4 1 1 | 第2の半導体層       |    |

| 4 1 2 | 第2の半導体層       | 50 |

|       |               |    |

|-------|---------------|----|

| 4 1 3 | 導電層           |    |

| 4 1 4 | 導電層           |    |

| 4 1 5 | 導電層           |    |

| 4 1 6 | 導電層           |    |

| 4 1 7 | パッシベーション膜     |    |

| 4 1 8 | 絶縁層           |    |

| 4 1 9 | 充填層           |    |

| 4 2 0 | 第1の電極         |    |

| 4 2 1 | 配線            |    |

| 4 2 2 | 上部電極          | 10 |

| 4 2 3 | 隔壁            |    |

| 4 2 4 | スペーサ          |    |

| 4 2 5 | EL層           |    |

| 4 2 6 | 第2の電極         |    |

| 4 2 7 | 封止基板          |    |

| 4 2 8 | 空間            |    |

| 4 2 9 | 指             |    |

| 4 5 0 | 口一線 (y座標検出線)  |    |

| 4 5 1 | カラム線 (x座標検出線) |    |

| 5 0 0 | 基板            | 20 |

| 5 0 1 | 下地膜           |    |

| 5 0 2 | ゲート電極         |    |

| 5 0 3 | ゲート電極         |    |

| 5 0 4 | 配線            |    |

| 5 0 5 | 絶縁膜           |    |

| 5 0 6 | 第1の半導体層       |    |

| 5 0 7 | 第1の半導体層       |    |

| 5 0 8 | 第2の半導体層       |    |

| 5 0 9 | 第2の半導体層       |    |

| 5 1 0 | 第2の半導体層       | 30 |

| 5 1 1 | 第2の半導体層       |    |

| 5 1 2 | 導電層           |    |

| 5 1 3 | 導電層           |    |

| 5 1 4 | 導電層           |    |

| 5 1 5 | 導電層           |    |

| 5 1 6 | 下部電極          |    |

| 5 1 7 | パッシベーション膜     |    |

| 5 1 8 | 絶縁層           |    |

| 5 1 9 | 充填層           |    |

| 5 2 0 | 第1の電極         | 40 |

| 5 2 1 | 配線            |    |

| 5 2 2 | 上部電極          |    |

| 5 2 3 | 隔壁            |    |

| 5 2 4 | スペーサ          |    |

| 5 2 5 | EL層           |    |

| 5 2 6 | 第2の電極         |    |

| 5 2 7 | 封止基板          |    |

| 5 2 8 | 空間            |    |

| 5 2 9 | 指             |    |

| 5 5 0 | 口一線 (y座標検出線)  | 50 |

|       |                  |

|-------|------------------|

| 5 5 1 | カラム線 ( × 座標検出線 ) |

| 6 0 0 | 電子書籍             |

| 6 0 1 | 筐体               |

| 6 0 2 | 筐体               |

| 6 0 3 | 軸部               |

| 6 0 4 | 表示部              |

| 6 0 5 | 表示部              |

| 6 0 6 | 電源               |

| 6 0 7 | 操作キー             |

| 6 0 8 | スピーカ             |

| 7 0 0 | デジタルフォトフレーム      |

| 7 0 1 | 筐体               |

| 7 0 2 | 表示部              |

【 义 1 】

(B)

【 図 2 】

【図3】

Diagram (B) illustrates a logic circuit with the following components and connections:

- Resistors: 200, 203, 205, 212.

- Capacitors: 201, 204, 206, 207, 213.

- Logic gates: 202, 205, 206, 207, 214.

- Wires: 200, 203, 205, 212.

【図4】

【 図 5 】

【 図 6 】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

---

フロントページの続き

(56)参考文献 特開2007-58071(JP, A)

国際公開第2010/055596(WO, A1)

特開2007-264852(JP, A)

特開2005-332589(JP, A)

特表2008-520083(JP, A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 3 / 041