## (19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第4606502号 (P4606502)

(45) 発行日 平成23年1月5日(2011.1.5)

(24) 登録日 平成22年10月15日(2010.10.15)

| (51) Int.Cl. |                |                 | FI             |          |                         |

|--------------|----------------|-----------------|----------------|----------|-------------------------|

| HO4N 1       | 3/04           | (2006.01)       | HO4N           | 13/04    |                         |

| HO4N         | 7/01           | (2006.01)       | HO4N           | 7/01     | Z                       |

| G02F         | 1/13           | (2006.01)       | GO2F           | 1/13     | 505                     |

| G09G 8       | 5/ <b>3</b> 6  | (2006.01)       | G09G           | 5/36     | 5 1 O V                 |

| G09G 8       | 5/ <i>37</i> 7 | (2006.01)       | G09G           | 5/36     | 520C                    |

| -            |                |                 |                |          | 請求項の数 20 (全 25 頁) 最終頁に続 |

| (21) 出願番号    |                | 特願2009-135861   | (P2009-135861) | (73) 特許  | 権者 000006013            |

| (22) 出願日     |                | 平成21年6月5日(2     | 2009.6.5)      |          | 三菱電機株式会社                |

| (65) 公開番号    |                | 特開2010-61105 (F | 2010-61105A)   |          | 東京都千代田区丸の内二丁目7番3号       |

| (43) 公開日     |                | 平成22年3月18日      | (2010. 3. 18)  | (74) 代理。 | 人 100083840             |

| 審査請求日        |                | 平成21年6月22日      | (2009. 6. 22)  |          | 弁理士 前田 実                |

| (31) 優先権主張番号 |                | 特願2008-204110   | (P2008-204110) | (74) 代理。 | 人 100116964             |

| (32) 優先日     |                | 平成20年8月7日(2     | 2008.8.7)      |          | 弁理士 山形 洋一               |

| (33) 優先権主張   | 玉              | 日本国(JP)         |                | (74) 代理。 | 人 100135921             |

|              |                |                 |                |          | 弁理士 篠原 昌彦               |

|              |                |                 |                | (72) 発明  | 者 長瀬 章裕                 |

|              |                |                 |                |          | 東京都千代田区丸の内二丁目7番3号 三     |

|              |                |                 |                |          | 菱電機株式会社内                |

|              |                |                 |                | (72) 発明  | 者 山室 孝彦                 |

|              |                |                 |                |          | 東京都千代田区丸の内二丁目7番3号 三     |

|              |                |                 |                |          | 菱電機株式会社内                |

|              |                |                 |                |          | 最終頁に続く                  |

|              |                |                 |                | •        |                         |

(54) 【発明の名称】画像表示装置および方法

## (57)【特許請求の範囲】

# 【請求項1】

入力され映像信号をレート変換用フレームメモリに蓄積した後に読み出して、前記入力 される映像信号の倍のクロックで出力するフレームレート変換手段と、

前記フレームレート変換手段から出力された映像信号の、画素並びを変換し、出力する信号フォーマット変換手段と、

前記信号フォーマット変換手段から出力された映像信号に基づき、画像表示に用いる光源の点灯、消灯を制御する光源制御信号及び3Dメガネを制御するタイミング信号を出力する光源制御手段と、

前記信号フォーマット変換手段から出力された映像信号、および前記光源制御手段から出力されたタイミング信号に基づき、右目と左目に交互に光を透過させる3 Dメガネの、右目と左目への光の透過を切り替えるメガネ制御信号を生成する3 Dメガネ制御手段と、

前記光源から出射された光を、前記信号フォーマット変換手段から出力された映像信号に基づき空間変調する空間変調手段を有し、

前記入力される映像信号が3D表示用映像信号である場合に、前記空間変調手段で変調された光を、前記3Dメガネを用いて観察することで立体視を可能にすることを特徴とする画像表示装置。

### 【請求項2】

入力される映像信号にフィルタリング処理を行う高画質化手段をさらに有し、 前記高画質化手段は、前記入力される映像信号が同一フレーム内に右目用画像と左目用

画像が混在する3D表示用映像信号である場合に、前記右目用画像のデータと前記左目用画像のデータをそれぞれ独立にフィルタリング処理を施し、

前記フレームレート変換手段は、前記高画質化手段においてフィルタリングされた映像信号を前記レート変換用フレームメモリに蓄積した後に読出し、前記高画質化手段でフィルタリング処理を施した映像信号の倍のクロックで出力することを特徴とする請求項1に記載の画像表示装置。

#### 【請求項3】

前記フレームレート変換手段は、前記入力される映像信号が前記同一フレーム内に右目 用画像と左目用画像が混在する 3 D表示用映像信号である場合に、連続する 2 フレームに わたり同じ映像を繰り返し出力することを特徴とする請求項 1 または請求項 2 に記載の画 像表示装置。

### 【請求項4】

前記信号フォーマット変換手段は、前記入力される映像信号が同一フレーム内に右目用画像と左目用画像が混在する3D表示用映像信号である場合に、前記右目用画像のみで構成される映像信号と、前記左目用画像のみで構成される映像信号をフレームごとに交互に出力することを特徴とする請求項3に記載の画像表示装置。

### 【請求項5】

前記信号フォーマット変換手段は、前記入力される映像信号を記憶するフォーマット変換用フレームメモリを有し、前記入力される映像信号が同一フレーム内に右目用画像と左目用画像が混在する3D表示用映像信号である場合に、前記右目用画像のみで構成される映像信号と、前記左目用画像のみで構成される映像信号をフレームごとに交互に前記フォーマット変換用フレームメモリに蓄積することを特徴とする請求項4に記載の画像表示装置。

#### 【請求項6】

前記信号フォーマット変換手段は、前記入力される映像信号が同一フレーム内に右目用画像と左目用画像が混在する 3 D表示用映像信号である場合に、前記フォーマット変換用フレームメモリから前記蓄積された映像信号を読み出すとき、水平方向に 2 画素連続して同じ画像を配置して出力することを特徴とする請求項 5 に記載の画像表示装置。

## 【請求項7】

前記信号フォーマット変換手段は、前記入力される映像信号が同一フレーム内に右目用画像と左目用画像が混在する 3 D表示用映像信号である場合に、1ラインおきに前記フォーマット変換用フレームメモリに画像を蓄積し、前記フォーマット変換用フレームメモリから前記蓄積された映像信号を読み出すとき、垂直方向に2ライン連続して同じ画像を配置して出力することを特徴とする請求項5又は6に記載の画像表示装置。

## 【請求項8】

前記光源制御手段は、前記入力される映像信号が同一フレーム内に右目用画像と左目用画像が混在する3D表示用映像信号である場合に、前記フォーマット変換手段から出力される映像信号に同期し、前記フォーマット変換手段から出力される映像信号の各フレームの映像信号期間が終了してから所定の遅延時間が経過したときに前記光源が点灯し、前記フォーマット変換手段から出力される映像信号の各フレームの映像信号期間が始まると同時に光源が消灯するように光源を制御することを特徴とする請求項1から請求項7のいずれか1項に記載の画像表示装置。

## 【請求項9】

前記所定の時間が表示デバイスの応答時間よりも長く設定されていることを特徴とする請求項8に記載の画像表示装置。

# 【請求項10】

連続する2フレーム分の映像信号データを基に液晶パネルの液晶に印加される電圧に対応する画像の各画素の階調値を表す映像信号を生成するオーバードライブ手段を有し、

前記信号フォーマット変換手段は、前記入力される映像信号が同一フレーム内に右目用画像と左目用画像が混在する3D表示用映像信号である場合に、現フレーム映像信号とし

10

20

30

40

て、前記右目用画像のみで構成される映像信号と、前記左目用画像のみで構成される映像信号をフレームごとに交互に出力するとともに、前記現フレーム映像信号の 1 フレーム前の映像信号を出力し、

前記オーバードライブ手段は、前記信号フォーマット変換手段が出力する前記現フレーム映像信号と、前記1フレーム前の映像信号を基に液晶パネルの液晶に印加される電圧に対応する画像の各画素の階調値を表す映像信号を生成する

ことを特徴とする請求項1から請求項9までのいずれか1項に記載の画像表示装置。

## 【請求項11】

前記入力される映像信号が通常の映像信号である場合に、前記信号フォーマット変換手段は、前記フレームレート変換手段から出力された映像信号のフレーム遅延を行い、

前記オーバードライブ手段は、前記信号フォーマット変換手段によってフレーム遅延された映像信号と、前記フレームレート変換手段から出力された映像信号とを基に、液晶パネルの液晶に印加される電圧に対応する画像の各画素の階調値を表す映像信号を生成することを特徴とする請求項10に記載の画像表示装置。

## 【請求項12】

入力され映像信号をレート変換用フレームメモリに蓄積した後に読み出して、前記入力 される映像信号の倍のクロックで出力するフレームレート変換ステップと、

前記フレームレート変換ステップから出力された映像信号の、画素並びを変換し、出力 する信号フォーマット変換ステップと、

前記信号フォーマット変換ステップから出力された映像信号に基づき、画像表示に用いる光源の点灯、消灯を制御する光源制御信号及び3Dメガネを制御するタイミング信号を出力する光源制御ステップと、

前記信号フォーマット変換ステップから出力された映像信号、および前記光源制御ステップから出力されたタイミング信号に基づき、右目と左目に交互に光を透過させる3Dメガネの、右目と左目への光の透過を切り替えるメガネ制御信号を生成する3Dメガネ制御ステップと、

前記光源から出射された光を、前記信号フォーマット変換ステップから出力された映像信号に基づき空間変調する空間変調ステップを有し、

前記入力される映像信号が3D表示用映像信号である場合に、前記空間変調ステップで変調された光を、前記3Dメガネを用いて観察することで立体視を可能にすることを特徴とする画像表示方法。

# 【請求項13】

入力される映像信号にフィルタリング処理を行う高画質化ステップをさらに有し、

前記高画質化ステップは、前記入力される映像信号が同一フレーム内に右目用画像と左目用画像が混在する 3 D表示用映像信号である場合に、前記右目用画像のデータと前記左目用画像のデータをそれぞれ独立にフィルタリング処理を施し、

前記フレームレート変換ステップは、前記高画質化ステップにおいてフィルタリングされた映像信号を前記レート変換用フレームメモリに蓄積した後に読出し、前記高画質化ステップでフィルタリング処理を施した映像信号の倍のクロックで出力することを特徴とする請求項12に記載の画像表示方法。

# 【請求項14】

前記フレームレート変換ステップは、前記入力される映像信号が前記同一フレーム内に右目用画像と左目用画像が混在する 3 D表示用映像信号である場合に、連続する 2 フレームにわたり同じ映像を繰り返し出力することを特徴とする請求項 1 2 又は 1 3 に記載の画像表示方法。

# 【請求項15】

前記信号フォーマット変換ステップは、前記入力される映像信号が同一フレーム内に右目用画像と左目用画像が混在する 3 D表示用映像信号である場合に、前記右目用画像のみで構成される映像信号と、前記左目用画像のみで構成される映像信号をフレームごとに交互に出力することを特徴とする請求項 1 4 に記載の画像表示方法。

10

20

30

40

## 【請求項16】

前記信号フォーマット変換ステップは、前記入力される映像信号を記憶するフォーマット変換用フレームメモリを有し、前記入力される映像信号が同一フレーム内に右目用画像と左目用画像が混在する 3 D表示用映像信号である場合に、前記右目用画像のみで構成される映像信号と、前記左目用画像のみで構成される映像信号をフレームごとに交互に前記フォーマット変換用フレームメモリに蓄積することを特徴とする請求項 1 5 に記載の画像表示方法。

## 【請求項17】

前記信号フォーマット変換ステップは、前記入力される映像信号が同一フレーム内に右目用画像と左目用画像が混在する 3 D表示用映像信号である場合に、前記フォーマット変換用フレームメモリから前記蓄積された映像信号を読み出すとき、水平方向に 2 画素連続して同じ画像を配置して出力することを特徴とする請求項 1 6 に記載の画像表示方法。

#### 【請求項18】

前記信号フォーマット変換ステップは、前記入力される映像信号が同一フレーム内に右目用画像と左目用画像が混在する 3 D表示用映像信号である場合に、1ラインおきに前記フォーマット変換用フレームメモリに画像を蓄積し、前記フォーマット変換用フレームメモリから前記蓄積された映像信号を読み出すとき、垂直方向に2ライン連続して同じ画像を配置して出力することを特徴とする請求項16又は17に記載の画像表示方法。

#### 【請求項19】

連続する2フレーム分の映像信号データを基に液晶パネルの液晶に印加される電圧に対応する画像の各画素の階調値を表す映像信号を生成するオーバードライブステップを有し

前記信号フォーマット変換ステップは、前記入力される映像信号が同一フレーム内に右目用画像と左目用画像が混在する 3 D表示用映像信号である場合に、現フレーム映像信号として、前記右目用画像のみで構成される映像信号と、前記左目用画像のみで構成される映像信号をフレームごとに交互に出力するとともに、前記現フレーム映像信号の 1 フレーム前の映像信号を出力し、

前記オーバードライブステップは、前記信号フォーマット変換ステップが出力する前記 現フレーム映像信号と、前記1フレーム前の映像信号を基に液晶パネルの液晶に印加され る電圧に対応する画像の各画素の階調値を表す映像信号を生成する

ことを特徴とする請求項12から18までのいずれか1項に記載の画像表示方法。

# 【請求項20】

前記入力される映像信号が通常の映像信号である場合に、前記信号フォーマット変換ステップは、前記フレームレート変換ステップから出力された映像信号のフレーム遅延を行い、

前記オーバードライブステップは、前記信号フォーマット変換ステップによってフレーム遅延された映像信号と、前記フレームレート変換ステップから出力された映像信号とを基に、液晶パネルの液晶に印加される電圧に対応する画像の各画素の階調値を表す映像信号を生成する

ことを特徴とする請求項19に記載の画像表示方法。

【発明の詳細な説明】

## 【技術分野】

### [0001]

本発明は、光源から出射された光を空間変調しスクリーンに表示する画像表示装置において、3次元(3D)表示用映像信号を表示可能にする画像表示装置および方法に関する

## 【背景技術】

## [0002]

近年、ディスプレイの大画面化が進んでいる。例えばマイクロ・デバイス・ディスプレイは、光源から出射された光を空間変調し、投射レンズでスクリーンに投影するという大

10

20

30

- -

40

画面化が容易な構造であることに加え、空間変調に用いるDMD(Digital Mirror Device)やHTPS(High Temperature Poly-Silicon)、LCOS(Liquid Crystal on Silicon)といったマイクロ・ディスプレイ・デバイスの優れた画像表示性能を生かし、大画面ディスプレイ市場で確固たる地位を得ている。

### [0003]

大画面ディスプレイに表示するコンテンツとしては、古くから映画やスポーツが好まれてきた。しかし最近では3次元映画や3次元ビデオゲームなどの3次元映像(3D映像)を表示したいという要求も高まっている。

マイクロ・デバイス・ディスプレイで 3 次元映像を表示させる方法としては、例えば特許文献 1 に開示されているような方法が知られている。

10

【先行技術文献】

【特許文献】

[0004]

【特許文献1】特表2007-531473号公報

【発明の概要】

【発明が解決しようとする課題】

[0005]

しかし、特許文献 1 に示される方法は、光源の光をカラーフィルタホイールを用いて順次特定の色に濾波するものであり、右目と左目で異なる波長の光が透過するレンズを装着した 3 D メガネを使用し、空間変調した光を観察するものであるため、光源が出射する光量に対して、目に入射する光量が半減し、結果として画像が暗くなってしまうという問題があった。

20

[0006]

また、入力される映像信号を、右目用画像と左目用画像にサブフレーム分解し、これらサブフレームをシーケンシャル方式で表示するものであるが、この方式では、入力される映像信号が一般的な60Hzである場合、マイクロ・ディスプレイ・デバイス上では120Hz以上の速さで右目用画像と左目用画像を切り替え表示させる必要がある。また、HTPSやLCOSといった液晶デバイスは、応答速度が遅いため、3D表示向けに右目用画像と左目用画像を高速で切り替えた場合、前に表示したフレームの残像が見えてしまう、言い換えればクロストークが発生する恐れがあった。

30

[0007]

また、ディスプレイに表示する映像信号は、信号の伝送系で生じるノイズや、帯域制限によって生まれる解像度の低下を補うため、通常ノイズ処理や輪郭強調といった高画質化処理を行うが、入力信号の1フレーム内に右目用画像と左目用画像が混在している3D表示用映像信号の場合、2次元映像信号の場合と同様に画素間で均一的にフィルタリング処理を施すと、右目用画像と左目用画像のデータ間で不必要なフィルタリングが行われてしまい、3D映像として表示した際に画質が劣化してしまう問題があった。

[0008]

さらに、HTPSやLCOSといった液晶デバイスを使用する場合、動画応答性を改善するためにオーバードライブ処理を用いることが強く求められるが、3D表示向けにサブフレーム分解し、2倍のフレームレートになった映像信号に対してオーバードライブ処理を施す場合、フレームメモリにアクセスする多くのバス帯域が必要になり、コストがかかるという問題があった。

40

【課題を解決するための手段】

[0009]

本発明に係る画像表示装置は、

入力され映像信号をレート変換用フレームメモリに蓄積した後に読み出して、前記入力 される映像信号の倍のクロックで出力するフレームレート変換手段と、

前記フレームレート変換手段から出力された映像信号の、画素並びを変換し、出力する

10

20

30

40

50

信号フォーマット変換手段と、

前記信号フォーマット変換手段から出力された映像信号に基づき、画像表示に用いる光源の点灯、消灯を制御する光源制御信号及び3Dメガネを制御するタイミング信号を出力する光源制御手段と、

前記信号フォーマット変換手段から出力された映像信号、および前記光源制御手段から出力されたタイミング信号に基づき、右目と左目に交互に光を透過させる3Dメガネの、右目と左目への光の透過を切り替えるメガネ制御信号を生成する3Dメガネ制御手段と、

前記光源から出射された光を、前記信号フォーマット変換手段から出力された映像信号に基づき空間変調する空間変調手段を有し、

前記入力される映像信号が3D表示用映像信号である場合に、前記空間変調手段で変調された光を、前記3Dメガネを用いて観察することで立体視を可能にすることを特徴とする。

【発明の効果】

[0010]

本発明によれば、従来の3D映像のようにデバイスの応答速度に起因するクロストークが視認されたり、映像が暗くなってしまうことがないという効果が得られる。

【図面の簡単な説明】

[0011]

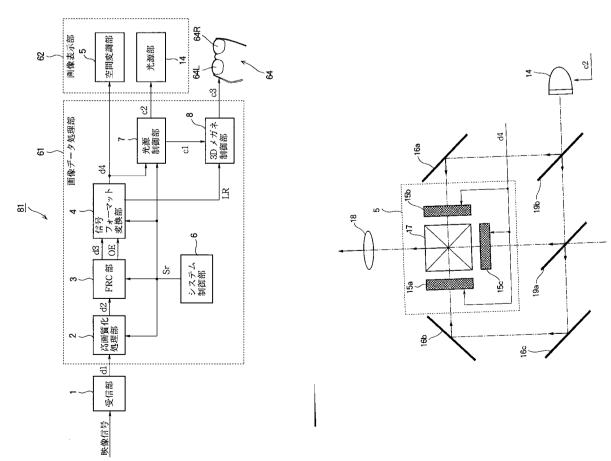

- 【図1】本発明の実施の形態1に係る画像表示装置を示すブロック図である。

- 【図2】図1の画像表示部62の一例を示す図である。

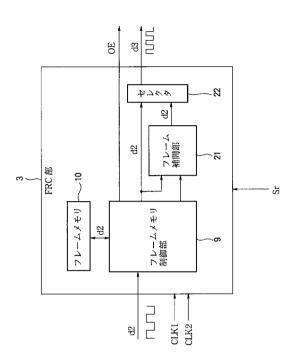

- 【図3】図1のFRC部3の一例を示すブロック図である。

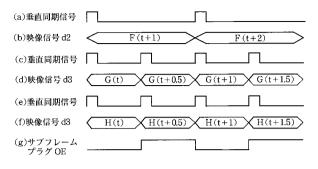

- 【図4】(a)~(g)は、図1のFRC部3の各部に表される信号を示す図である。

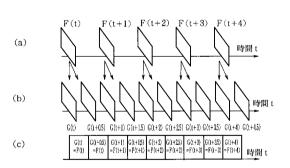

- 【図5】(a)~(c)は、3Dモード処理時における、図1のFRC部3の動作を示す図である。

- 【図6】(a)~(c)は、通常処理時における、図1のFRC部3の動作を示す図である。

- 【図7】図1の信号フォーマット変換部4の一例を示すブロック図である。

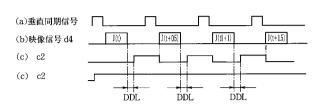

- 【図8】(a)~(d)は、3Dモード処理の場合に、図7のフレームメモリ制御部24に入力される信号及び出力される信号を示す図である。

- 【図9】(a)~(g)は、実施の形態3において、図7のフレームメモリ制御部24に 入力される信号及び出力される信号を示す図である。

- 【図10】(a)~(d)は、図1の光源制御部7の動作を示す図である。

- 【図11】(a)~(e)は、図1の3Dメガネ制御部8の動作を示す図である。

- 【図12】本発明の実施の形態2で用いられる信号フォーマット変換部4の一例を示すブロック図である。

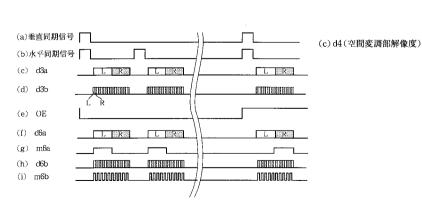

- 【図13】(a)~(i)は、図12のマスク部26の動作を示す図である。

- 【図14】(a)~(c)は、実施の形態2の動作中の各段階での画像サイズの変化を説明する図である。

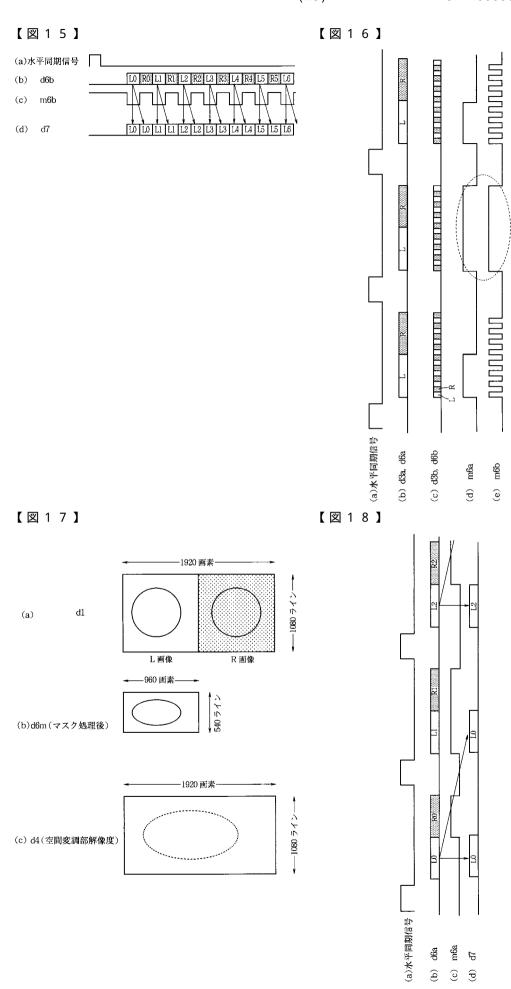

- 【図15】(a)~(d)は、本発明の実施の形態3における、フレームメモリ制御部の動作を説明するための図である。

- 【図16】(a)~(e)は、本発明の実施の形態4における、マスク部の動作を示す図である

- 【図17】(a)~(c)は、実施の形態4の動作中の各段階での画像サイズの変化を説明する図である。

- 【図18】(a)~(d)は、実施の形態4のフレームメモリ制御部の動作を示す図である。

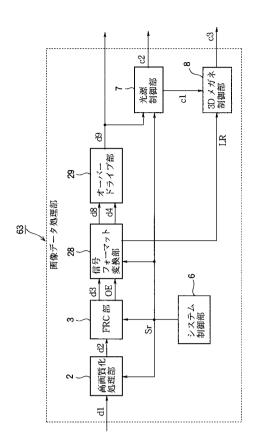

- 【図19】本発明の実施の形態5に係る、画像データ処理部の一例を示すブロック図である。

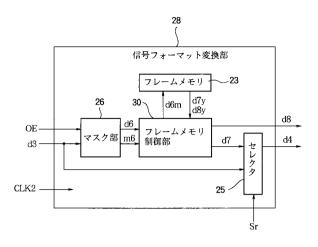

- 【図20】図19の信号フォーマット変換部28の一例を示すブロック図である。

- 【図21】(a)~(o)は、図20の信号フォーマット変換部28の動作を示す図であ

る。

【図22】図19のオーバードライブ部29の一例を示すブロック図である。

【図23】図22のルックアップテーブルの構成例を示す図である。

【発明を実施するための形態】

[0012]

実施の形態1.

図1は、本発明の実施の形態1の画像表示装置の構成を示すブロック図である。画像表示装置81は、受信部1、画像データ処理部61、及び画像表示部62を備える。

画像表示装置 8 1 に入力された映像信号は、受信部 1 に入力される。たとえばコンポジットビデオ信号が画像表示装置 8 1 に入力された場合、受信部 1 では、入力された映像信号を規定周波数のクロックでサンプリングし、輝度信号成分と色信号成分を分離した後、同期信号、画像有効期間信号、画像データ信号などで構成される映像信号 d 1 を画像データ処理部 6 1 に出力する。

[0013]

画像データ処理部61は、高画質化処理部2、フレームレート変換部(FRC部)3、信号フォーマット変換部4、システム制御部6、光源制御部7、及び3Dメガネ制御部8を備える。システム制御部6は例えばマイコンで構成される。

[0014]

高画質化処理部2では、受信部1から出力された映像信号 d1に対して、システム制御部6から送られてくる制御情報Srを基に、輪郭強調や色補正といった、いわゆる高画質化処理を施し、映像信号 d2を出力する。

[0015]

高画質化処理部2から出力された映像信号d2はFRC部3に入力される。FRC部3は、システム制御部6から送られてくる制御情報Srを基に、映像信号d2のフレームレートを変換し、映像信号d3を信号フォーマット変換部4に出力する。

FRC部3はまた、サブフレームフラグOEを生成し、信号フォーマット変換部4に出力する。

[0016]

信号フォーマット変換部4は、システム制御部6から送られてくる制御情報Sr、並びにFRC部3から入力される映像信号d3及びサブフレームフラグOEを基に、入力された映像信号d3の画素並び変換を行い、その結果生成された映像信号d4を画像表示部62および光源制御部7に出力するとともに、FRC部3から入力されるサブフレームフラグOEを基に選択制御信号LRを生成し、3Dメガネ制御部8に出力する。

[0017]

光源制御部7は、信号フォーマット変換部4から出力される映像信号 d 4、およびシステム制御部6から送られてくる制御情報Srに基づき、画像表示に用いる光源の点灯、消灯を制御する光源制御信号 c 2を生成し、画像表示部62に出力する。光源制御部7はまた、光源の点灯、消灯のタイミングよりタイミング信号 c 1を生成し、3Dメガネ制御部8に出力する。

[0018]

3 D メガネ制御部 8 は、信号フォーマット変換部 4 から出力された選択制御信号 L R と、光源制御部 7 から出力されたタイミング信号 c 1 を基に、 3 D メガネ制御信号 c 3 を生成し、 3 D メガネ 6 4 のシャッタを制御する。具体的には 3 D メガネ 6 4 に右目用、左目用それぞれ独立に組み込まれている、透過型の液晶シャッタ 6 4 R 、 6 4 L を、右目にのみ光を透過させる、または左目にのみ光を透過させるように切り替え制御する。

画像表示部62は、空間変調部5および光源部14を備える。

[0019]

図2は、画像表示部62の一例を示す。光源部14から出力された光は、ミラー16a、16b、及びダイクロイックミラー19a、19b、19cを介して空間変調部5に導 光され、空間変調部5において空間変調されて光は、投射レンズ18によりスクリーン( 10

20

30

40

図示しない)に投射される。

## [0020]

光源部14は、画像データ処理部61から出力された光源制御信号 c 2 に基づき光を発する。具体的には、光源部14としては、白色光を出力するものが用いられる。

空間変調部5は、3枚の液晶パネル15a、15b、15cとダイクロイックプリズム17を備える。光源部14から出力された白色光は、ダイクロックミラー19a、19b、19cを介することで分波される。分波された光は、それぞれミラー16a、16b等を介して、たとえば、液晶パネル15aへは赤色の光、液晶パネル15cへは青色の光が導光される。

## [0021]

液晶パネル15a、15b、15cでは画像データ処理部61から出力された映像信号 d 4 に基づき、光源部14から発せられた光を分波して得られた、赤色の光、緑色の光、青色の光をそれぞれ空間変調する。

液晶パネル 1 5 a 、 1 5 b 、 1 5 c により空間変調された光は、ダイクロイックプリズム 1 7 により一つにされ、投射レンズ 1 8 によってスクリーン(図示しない)に投影される。

### [0022]

ここで、光源の光をダイクロイックミラーを用いて3色に分波する例を示したが、分波 するのは3色に限らない。

また、光源部14において、光源の点灯、消灯の制御にシャッタを用いても良い。この場合、光源は常に点灯させておき、光源制御信号 c 2 に基づき光源の前に設置したシャッタを開閉させることで、ダイクロイックミラー19a、19b、19cへ出射する光量を制御する。

#### [0023]

また、ダイクロックミラー19a、19b、19cを用いることなく、光源部14を、それぞれの液晶パネル分用意する構成も考えられる。具体的には、例えば赤、青、緑の光を出力する半導体レーザや、LEDを光源として用い、それぞれの光を液晶パネルに照射させても良い。

さらに、空間変調部5のデバイスとして、HTPSを例に説明を行なったが、LCOSや、DMDを用いても同様の効果が得られる。

### [0024]

さらに、本実施の形態では空間変調された光を投射レンズを用いてスクリーンに投射するマイクロ・デバイス・ディスプレイを例に説明を行ったが、たとえば直視型液晶ディスプレイにも容易に適用できる。

## [0025]

次に、画像データ処理部61の動作を詳しく説明する。

受信部1から出力された映像信号 d 1 は、高画質化処理部2に入力される。高画質化処理部2では、映像信号 d 1 に対して、システム制御部6から送られてくる制御情報Srを基に、輪郭強調や色補正といった、高画質化のためのフィルタリング処理を施し、映像信号 d 2を出力する。

# [0026]

受信部1から出力される映像信号 d 1 が 3 D 表示用映像信号の場合、通常1つのフレーム内に右目用画像と左目用画像が混在したもの(両画像を含むもの)となる。

3 D表示用映像信号における、右目用画像と左目用画像はそれぞれ独立した画像であり、それぞれの画像をオーバーラップして(一連のデータとして扱って)フィルタリングを行うことは画質劣化につながる。具体的には、例えばラプラシアンフィルタ等を用いて輪郭部の強調を行なう場合、右目用画像と左目用画像が混在していると、輪郭部以外の画素にも擬似的に強調成分が付加され、結果的にノイズとして視認されてしまう。よって、高画質化処理部2では、システム制御部6から送られてくる制御情報Srを基に、3D表示用映像信号のフォーマットを判断し、同一フレーム内に混在する右目用画像を構成する画

10

20

30

40

素と左目用画像を構成する画素を分離し、独立にフィルタリングを施す。

#### [0027]

高画質化処理部2から出力された映像信号d2はFRC部3に入力される。

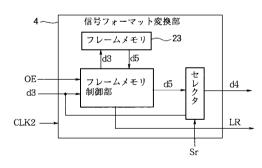

図3は、FRC部3の詳細を示すブロック図である。

FRC部3はフレームメモリ制御部9と、フレームメモリ(レート変換用フレームメモリ)10と、フレーム補間部21と、セレクタ22を備える。

#### [0028]

フレームメモリ制御部9は、入力された映像信号d2に含まれる同期信号を基に生成したメモリアドレスに従い、フレームメモリ10に映像信号d2を書き込む。

また、フレームメモリ制御部9は、フレームメモリ10に蓄積された映像信号の読み出しをも行う。映像信号の読み出し用アドレス生成は、映像信号d2に含まれる同期信号に必ずしも同期する必要はないが、書き込み用クロックCLK1の2倍の周波数の読み出しクロックCLK2でアドレスを生成する。

## [0029]

フレーム補間部 2 1 は、フレームメモリ制御部 9 から出力される複数フレームの映像信号を基に、補間フレーム映像信号 d i 2 を生成し出力する。セレクタ 2 2 はシステム制御部 6 から送られる制御信号 S r に基づきフレームメモリ制御部 9 から出力される映像信号 d 2 と、フレーム補間部 2 1 から出力される映像信号 d i 2 を交互に選択し、映像信号 d 3 として出力する。

また、フレームメモリ制御部9は、出力映像がサブフレームであるかを判定し、サブフレームフラグOEを出力する。ここで「サブフレーム」とは、フレームレートを2倍にしたときに、元々の垂直同期信号相互間に挿入される垂直同期信号で始まるフレームを意味する。

## [0030]

図4(a)~(g)はFRC部3に入力される映像信号d2と、FRC部3から出力される映像信号d3と、サブフレームフラグOEの関係を示した図である。図4(b)は、FRC部3に入力される映像信号d2を示し、図4(a)は、映像信号d2の垂直同期信号を示す。(なお、同期信号は、映像信号と複合したものであるが、便宜上分離して図示している。本願における他の同期信号についても同様である。)図4(d)は、3Dモード時にFRC部3から出力される映像信号d3を示し、図4(c)は、映像信号d3の垂直同期信号を示し、図4(f)は、通常表示時(2D表示時)にFRC部3から出力される映像信号d3を示し、図4(e)は、映像信号d3の垂直同期信号を示し、図4(g)は、サブフレームフラグOEを示す。

# [0031]

FRC部3より出力される映像信号d3(図4(d)、(f))は、入力される映像信号d2(図4(b))の2倍のフレームレートをもつ。具体的には、たとえば入力された映像信号d2が60Hzであるとすると、FRC部3から出力される映像信号d3として、図4(d)、(f)に示すように、2倍の120Hzの周波数を持つものに変換されて出力される。

図4(g)に示されるサブフレームフラグOEは、出力画像のフレームごとにトグルする信号であり、ここでは例として、出力画像がサブフレームであるときにHiとなるものとして示されている。

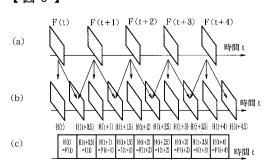

## [0032]

図 5 ( a ) ~ ( c ) は、システム制御部 6 から送られる制御情報 S r により、 3 D モード処理が指示された場合の、 F R C 部 3 へ入力される映像信号 d 2 (図 5 ( a ) ) と、フレームレート変換後に出力される映像信号 d 3 (図 5 ( b )、 ( c ) )の関係を示した図である。

## [0033]

3 Dモード処理の場合、フレームメモリ制御部 9 は、フレームレート変換後の出力映像信号 d 3 (図 4 ( d ) )の、G ( t )フレーム目の映像として、フレームメモリ 1 0 より

10

20

30

40

入力映像信号 d 2 の F ( t ) フレーム目の映像を読み出し、セレクタ部 2 2 に出力する。 さらにフレームメモリ制御部 9 は、フレームレート変換後の出力映像信号 d 3 の、 G ( t ) フレームの次フレームである G ( t + 0 . 5 ) フレーム目の映像としても、 F ( t ) フレーム目の映像をフレームメモリ 1 0 から読み出し、セレクタ部 2 2 に出力する。

## [0034]

3 Dモード処理の場合、セレクタ部 2 2 では、フレームメモリ制御部 9 から出力される映像信号 d 2 を選択する。これより出力画像信号 d 3 としては、 2 フレームにわたり同じ映像信号が繰り返し出力され、 2 フレームごとに映像の内容が切り替えられる。

## [0035]

システム制御部6から送られる制御情報Srにより、通常の2Dモード処理(非3Dモード)が指示された場合、フレームメモリ制御部9を介してフレームメモリ10から読み出された複数フレームの映像信号は、フレーム補間部21に入力される。

フレーム補間部 2 1 では、入力される複数フレームの映像信号に含まれる情報を基に、中間フレームの映像信号 d i 2 を生成する。

## [0036]

図6(a)~(c)は、通常処理(非3Dモード)が指示された場合における、FRC部3へ入力される映像信号d2(図6(a))と、フレームレート変換後に出力される映像信号d3(図6(b)、(c))の関係を示した図である。

入力映像信号d2のF(t)フレーム目の映像は、フレームレート変換後の出力映像信号d3では、H(t)フレーム目に出力される。

## [0037]

一方、図 5 ( b )、( c )に示す、 3 D モード処理が指示された場合とは異なり、 H ( t )フレームの次フレーム(中間フレーム)である H ( t + 0 . 5 )フレーム目では、 F ( t )と F ( t + 1 )を用いてフレーム間補間を行ったもの I ( t )が出力される。

フレーム間補間は、例えば以下の式により行われる。

I(t) = H(t) + (1 - ) H(t + 1)

上式において、は、

#### 0 1

を満足する値であり、H(t)とH(t+1)に対する重みづけ係数であり、 を 0 . 5 とした場合には、H(t)とH(t+1)との単純平均による補間(線形補間)が行われる。

# [0038]

なお、通常処理(非3Dモード)の場合にも、図5(b)、(c)に示すのと同様に、 2フレームにわたり同じ映像信号を出力することも可能であるが、動画画質向上の点では 、図6(b)、(c)に示すフレーム補間処理により得られた信号を用いる方が好ましい

# [0039]

FRC部3から出力された映像信号d3は、信号フォーマット変換部4に入力される。 図7は信号フォーマット変換部4の詳細を示すブロック図である。

信号フォーマット変換部4は、フレームメモリ制御部24と、フレームメモリ(フォーマット変換用フレームメモリ)23と、セレクタ25を備える。

#### [0040]

FRC部3より出力された映像信号d3、およびサブフレームフラグOEはフレームメモリ制御部24に入力される。フレームメモリ制御部24は、入力された映像信号d3に含まれる同期信号を基に生成したメモリアドレスに従い、フレームメモリ23に映像信号d3を書き込む。

#### [0041]

また、フレームメモリ制御部24は、フレームメモリ23に蓄積された映像信号の読み出しをも行う。この読み出しに際して、フレームメモリ制御部24は、サブフレームフラグOEを基に、右目用画像、または左目用画像のみをフレームメモリ23から読み出すよ

20

10

30

40

うに読み出し用アドレスを生成する。 FRC部 3 とは異なり、出力映像信号 d 4 の周波数は、入力映像信号 d 3 と同じであるため、読み出し時に必要となる 1 フレームあたりのフレームメモリアクセス量は、書き込み時の半分となる。

#### [0042]

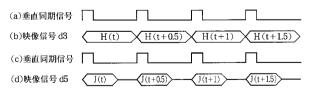

図8(a)~(d)は、3Dモード処理の場合のフレームメモリ制御部24に入力され、フレームメモリ23に書き込まれる映像信号d3と、フレームメモリ23から読み出され、フレームメモリ制御部24から出力される映像信号d5の関係を示したものである。図8(b)は、映像信号d3を示し、図8(a)は映像信号d3の垂直同期信号を示し、図8(d)は、映像信号d5を示し、図8(c)は映像信号d5の垂直同期信号を示す。

#### [0043]

システム制御部6から送られる制御情報Srにより、3Dモード処理が指示された場合、入力される映像信号d3に対して、出力映像信号d5は右目用画像、または左目用画像のみで構成されるため、出力映像信号のデータ量は、入力映像信号の半分になる。

## [0044]

図9(a)~(g)は、フレームメモリ制御部24に入力される3D表示用映像信号のパターンと、出力映像信号d5の関係、および選択制御信号LRの関係を示したものである。即ち、図9(c)、(d)は、フレームメモリ制御部24に入力される映像信号d3の具体例d3a、d3bを示し、図9(a)、(b)は映像信号d3a、d3bの垂直同期信号及び水平同期信号を示し、図9(f)は、フレームメモリ制御部24から出力される映像信号d5を示し、図9(e)は、映像信号d5の水平同期信号を示し、図9(g)は、選択制御信号LRを示す。

## [0045]

3 D表示用映像信号は、右目用画像と左目用画像が組み合わされた映像信号になっているが、たとえば図9(c)に示す映像信号d3aのように、各水平期間の前半に左目用画像データが、後半に右目用画像データが伝送され、従って画像の左半分に左目用画像、画像の右半分が右目用画像になっている場合がある。また、図9(d)に示す映像信号d3bのように、1画素ごとに右目用画像のデータと左目用画像のデータが交互に配置されており、かつ各水平ライン内における右目用画像のデータと左目用画像のデータの順序(各ラインの最初にどちらが現れるかが)1水平ラインごとに切り替わる場合もある。

#### [0046]

フレームメモリ制御部 2 4 は、入力された 3 D表示用映像信号 d 3 のフォーマットに応じてフレームメモリ 2 3 に蓄積された映像信号の読み出しを行うので、仕様の異なる 3 D表示用映像信号が入力されても、出力される 3 D表示用映像信号は、図 9 (f)に示すように、フレームごとに右目用画像、左目用画像が交互に現れる信号フォーマットになる。

また、フレームメモリ制御部24は、選択制御信号LRを生成し、3Dメガネ制御部8へ出力する。選択制御信号LRは、フレームメモリ制御部24がフレームメモリ23より、右目用画像を読み出している期間と、左目用画像を読み出している期間で異なる値を持つ。

## [0047]

フレームメモリ制御部 2 4 から出力された映像信号 d 5 は、セレクタ 2 5 に入力される。セレクタ 2 5 は、システム制御部 6 から送られる制御情報 S r により、 3 D モード処理が指示されている場合、フレームメモリ制御部 2 4 から出力された映像信号 d 5 を出力する。一方、通常処理(非 3 D モード)の時には、セレクタ 2 5 は入力された映像信号 d 3 を選択する。つまり、映像信号 d 3 がそのまま映像信号 d 4 として出力される。

#### [0048]

フォーマット変換部4から出力された映像信号 d4は、画像表示部62に出力されるの みならず、光源制御部7へも出力される。

光源制御部7は、信号フォーマット変換部4から出力される映像信号 d 4、およびシステム制御部6から送られてくる制御情報 S r に基づき、画像表示に用いる光源の点灯、消灯を制御する光源制御信号 c 2を画像表示部62に出力する。

10

20

30

40

### [0049]

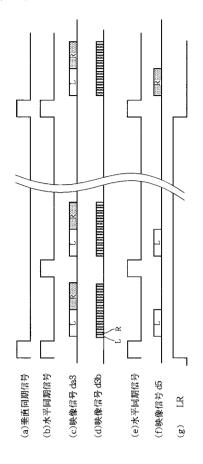

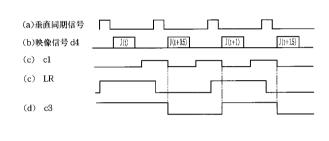

図10(a)~(d)は、光源制御部7の動作を説明する図である。光源制御部7に入力される映像信号 d4(図10(b))及びその垂直同期信号(図10(a))と、光源制御信号 c2(図10(c)、(d))の関係を示している。

## [0050]

システム制御部6から送られる制御情報Srにより、通常処理(非3Dモード)が指示された場合、光源制御信号 c 2 は、入力される映像信号 d 4 に関係なく動作し、例えば図10(d)に示すように常にHiを画像表示部62に出力する。

画像表示部62では光源制御信号c2がHiの期間光源が点灯する。

#### [0051]

一方、システム制御部6から送られる制御情報Srにより3Dモードが指示された場合、制御信号c2は、図10(c)に示すように、映像信号d4に同期して切り替わる。

具体的には、各フレームの映像信号 J ( t ) が終了し、所定の遅延時間 D D L が経過したときに光源制御信号 c 2 が H i になる。また光源制御信号 c 2 は少なくとも次フレームの映像信号 d 4 が H i となるまでに L o になる。

#### [0052]

遅延時間 D D L は、画像表示部 6 2 に用いる液晶パネルの応答時間より長いことが求められ、例えば数m秒程度である。

これにより、3D映像表示時に発生する液晶の応答速度に起因するフレーム間での表示映像のクロストークをなくすことが可能となる。

#### [0053]

光源制御部7は光源制御信号c2を画像表示部62に出力する他に、タイミング信号c1を3Dメガネ制御部8へも出力する。

タイミング信号 c 1 は光源制御信号 c 2 と同等の信号である。

#### [0054]

図11(a)~(e)は3Dメガネ制御部8の動作を説明する図である。

3 D メガネ制御部 8 は、タイミング信号 c 1 (図 1 1 ( c ) ) と選択制御信号 L R (図 1 1 ( d ) )を基に 3 D メガネ制御信号 c 3 (図 1 1 ( e ) )を生成する。 3 D メガネ制御信号 c 3 の値(レベル)変化するとき、すなわち画像表示部 6 2 の光源が消える時(点灯状態から消灯状態に切り替わる時)の、選択制御信号 L R の値(レベル)に従って切り替わる。

# [0055]

3 D メガネ制御信号 c 3 の値が光源の消えるタイミングで切り替わることで、 3 D メガネ制御信号 c 3 により制御される 3 D メガネ 6 4 の液晶シャッタも、光源が消えるタイミングで左右が入れ替わる。

光源が消えた後、すくなくとも映像信号 d 4 が画像表示部 6 2 に送られている期間は光源が点灯することはないので、たとえ 3 D メガネ 6 4 の液晶シャッタの応答速度が遅くても、次に光源が点灯するまでにシャッタの切り替えが完了する。

## [0056]

以上説明したように、3D表示用映像信号が入力された場合、2フレーム同じ画像を繰り返すことで2倍のフレームレートに変換し、フォーマット変換により右目用画像と左目用画像をフレームごとに交互に生成し、画像表示部62で表示するタイミングに合わせて、光源および3Dメガネ64を制御することで、クロストークのない3D映像を表示することが可能となる。

# [0057]

また、3 D表示用映像信号が入力された場合、高画質化処理部2では、右目用画像、左目用画像それぞれ独立に処理を行うため、右目用画像、左目用画像の情報が混じることなく、入力した3 D表示用映像信号に対して、不要なノイズを重畳させない。結果として、3 D表示画像の劣化を防ぐことができる。

## [0058]

50

10

20

30

また、信号フォーマット変換部4において、入力される3D表示用映像信号のフォーマットに応じてフレームメモリ23から読み出すアドレスを制御するので、複数の異なる3D表示用映像信号のフォーマットのいずれであっても同様に表示させることができる。

## [0059]

なお、本実施の形態では高画質化処理部 2 を用いて、入力された映像の輪郭強調や色補正を行う構成を説明したが、入力される映像信号がコンピュータグラフィックス等の場合、必ずしも高画質化処理を行う必要はなく、受信部 1 から出力された映像信号 d 1 が直接 FRC部 3 に入力される構成としても良い。

#### [0060]

実施の形態2.

実施の形態 2 の画像表示装置の全体的構成は、実施の形態 1 に関し図 1 を参照して説明 したのと同じである。実施の形態 2 の画像表示装置は、信号フォーマット変換部 4 の構成 が異なる。

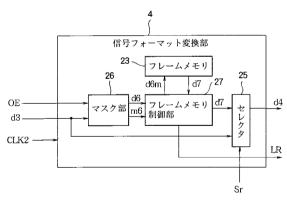

## [0061]

図12は実施の形態2における信号フォーマット変換部4の詳細を示すブロック図である。図7に示す信号フォーマット変換部4との違いは、図7のフレームメモリ制御部24の代わりに、フレームメモリ制御部27が設けられ、該フレームメモリ制御部27の前にマスク部26が追加されている点である。

#### [0062]

FRC部3により倍速に変換された映像信号d3はフォーマット変換部4で、フレームメモリ23に蓄えられる。例えばフルHD(full high definition)と言われている1フレームあたり1920dot×1080lineの映像が120Hzで入力されてきた場合、信号のビット数にも依存するが13Gbps程度の転送レートが必要になる。

高速アクセス可能なDRAMが普及してきたとはいえ、コストの面からフレームメモリのバス帯域が大きいことは問題となる。

#### [0063]

本実施の形態は、この問題を解決するためのものであり、マスク部26を用いてフレームメモリ23に書き込まれるデータの量を削減する。

そのために、マスク部 2 6 は入力される映像信号 d 3 が 3 D 表示用映像信号である場合、サブフレームフラグ O E を基にマスク信号 m 6 を生成し、映像信号 d 6 と共にフレームメモリ制御部 2 7 は、このマスク信号を基にして、フレームメモリ 2 3 に書き込まれるデータの量を削減する。

## [0064]

図 1 3 (a) ~ (i) にマスク部 2 6 の動作を示す。

図13(c)、(d)は、フレームフォーマット変換部4に入力される映像信号d3の具体例としてのd3a、d3bを示し、図13(a)、(b)は、映像信号d3a、d3bの垂直同期信号、水平同期信号を示す。図13(e)はサブフレームフラグOEを示し、図13(f)、(h)は、マスク部26から出力される映像信号d6の具体例としてのd6a、d6bを示し、図13(g)、(i)はマスク部26で生成されるマスク信号m6の具体例としての、m6a、m6bを示す。

## [0065]

マスク部 2 6 に、たとえば図 1 3 ( c )に示す映像信号 d 3 a のように、画像の左半分に左目用画像、画像の右半分に右目用画像を含む映像信号が入力された場合、マスク部 2 6 は図 1 3 ( f )に示す映像信号 d 6 a と、図 1 3 ( g )に示すマスク信号 m 6 a を出力する。

#### [0066]

ここで、マスク信号 m 6 a はサプフレームフラグ O E (図 1 3 ( e ) )を基に生成されるものであり、一つおきのフレームでは、映像信号 d 3 a に含まれる右目用画像の期間にHiとなり、上記一つおきのフレームの間のフレームでは映像信号 d 3 a に含まれる左目

10

20

30

40

用画像の期間にHiになる。即ち、Hiとなる期間が、フレームごとに交互に切り替わる

### [0067]

マスク部26に、図13(d)に示すように、1画素ごとに右目用画像のデータと左目用画像のデータが交互に配置されている映像信号d3bが入力された場合には、図13(i)に示されるマスク信号m6bが生成される。図示のマスク信号m6bは、映像信号d3(図13(f))が入力された場合と同様に、一つおきのフレームでは、映像信号d3bに含まれる右目用画像のデータの期間にマスク信号Hiとなり、上記一つおきのフレームの間のフレームでは、映像信号d3bに含まれる左目用画像のデータの期間にHiとなる。即5、Hiとなる期間が、フレームごとに交互に切り替わる。

[0068]

マスク部26で生成されたマスク信号m6は、映像信号d6と共にフレームメモリ制御部27に出力される。

フレームメモリ制御部 2 7 は、入力された映像信号 d 6 に含まれる同期信号(図 1 3 (a)、(b))を基にメモリアドレスを生成する。ただしメモリアドレスはマスク信号m 6 が L o の期間のみ生成される。これにより、フレームメモリ制御部 2 7 に入力される映像信号 d 6 のうち、フレームごとに右目用画像のデータのみ、または左目用画像のデータのみが選択され、フレームメモリ 2 3 に書き込まれる。選択されて書き込まれるデータが符号 d 6 m で表わされる。

これによりフレームメモリ23の書き込みに要するバス帯域は半分で済む。

[0069]

フレームメモリ制御部 2 7 はまた、フレームメモリ 2 3 に蓄積された映像信号の読み出しをも行う。フレームメモリ制御部 2 7 は、フレームメモリ 2 3 に記憶された映像信号 d 6 mを順に読み出していく。

書き込み段階で、フレームごとに右目用画像のみ、又は左目用画像のみがフレームメモリ23に書き込まれているので、フレームメモリ23から読み出され、フレームメモリ制御部27から出力される映像信号d7(=d6m)のデータ量は、図9(f)に示す映像信号d5と同様に、入力される映像信号d3の半分になる。

なお、他の構成は実施の形態1で説明した内容と同じであるため、説明は省略する。

[0070]

以上説明したように、信号フォーマット変換部4において、3D表示用映像信号が入力された場合、フレームごとに交互に右目用画素、または左目用画素に対してマスク信号を生成し、前記マスク信号を基にフレームメモリ書き込みアドレスを生成することで、フレームメモリ23のアクセスに必要なバス帯域を減らすことが可能になる。

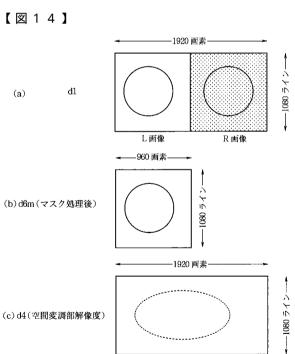

[0071]

実施の形態3.

実施の形態3の画像表示装置の全体的構成は、実施の形態1に関し図1を参照して説明したのと同じである。実施の形態3の信号フォーマット変換部4は、実施の形態2に関し図12を参照して説明したのと同様である。但し、以下のような違いがある。

[0072]

実施の形態 2 では、 3 D表示用映像信号が入力された場合、フレームごとに交互に右目用画素、または左目用画素に対してマスク信号を生成し、前記マスク信号を基にフレームメモリ 2 3 の書き込みアドレスを生成するため、受信部 1 から出力される映像信号 d 1 に対して、空間変調部 5 へ出力される映像信号 d 4 のサイズは半分になっている。実施の形態 3 は、実施の形態 2 で説明した方法でフレームメモリ 2 3 に書き込まれたデータを読み出して出力する場合に適用可能な方法である。但し、実施の形態 3 の読み出し方法は、実施の形態 2 で説明した書き込み方法以外の方法で書き込まれたデータの読み出しにも適用可能である。

[0073]

図14(a)~(c)は本システム(実施の形態3の装置)における各工程での画像サ

10

20

40

30

イズの変化を示す図である。図14(a)は、映像信号d1の画像サイズ、図14(b)は、マスク処理後映像信号d6mの画像サイズ、図14(c)は、画像表示部62に供給される映像信号d4の画像サイズ、従って、空間変調部5のサイズ(画素数)を示す。

## [0074]

例えば受信部1から出力される映像信号 d 1の右目用画像と左目用画像が図14(a)に示すように、フルHD(1920 d o t x 1080line)のそれぞれ半分を占めるとする。このとき信号フォーマット変換部4のフレームメモリ23から読み出される映像信号 d 6 m は図14(b)に示すように、960 d o t x 1080lineと受信部1から出力される映像信号 d 1のサイズの半分になる。

#### [0075]

空間変調部5のサイズ(画素数)が図14(c)に示すように、受信部1から出力される映像信号 d 1 サイズと同じ場合、フレームメモリ23から映像信号 d 6 を読出した後、空間変調部5に供給する前に、映像信号のサイズを増やす必要がある。

### [0076]

図15(a)~(d)は、実施の形態3における信号フォーマット変換部4内のフレームメモリ制御部27の動作を説明するための図である。図15(b)、(c)は、フレームメモリ23に書き込まれた映像信号d6の具体例としてのd6b及び書き込みの際に用いられたマスク信号m6の具体例としてのm6bを示し、図15(a)は、映像信号d6bの水平同期信号を示し、図15(d)は、フレームメモリ23から読み出される映像信号d7を示す。

#### [0077]

図 9 ( a ) ~ ( g ) に示すフレームメモリ制御部 2 4 の動作と異なる点は、フレームメモリ 2 3 から映像信号を読み出すとき、読み出した画素を(ホールド処理により) 2 画素連続で使用する(フレームメモリ制御部 2 7 から出力する)点である。フレームメモリ制御部 2 7 から出力されるデータ d 7 は、図 1 5 ( d ) に示すようになる。

### [0078]

このときフレームメモリ23から映像信号を読み出す際、フレームメモリ23へのアクセスは2画素(クロック)に1回でよく、バス帯域を増やすことはない。また、別途ラインメモリを増設し水平拡大回路を組み込む必要もない。

# [0079]

以上説明したように、信号フォーマット変換部4において、フレームメモリ23に蓄積された映像信号をフレームメモリ23から読み出すとき、読み出された画素を2画素連続で並べる(ホールド処理を行う)ことで、入力映像信号のサイズを落とすことなく、フレームメモリアクセスに必要なバス帯域を抑制することが可能になる。

## [0800]

#### 実施の形態4.

実施の形態 4 の画像表示装置は、実施の形態 3 と概して同じである。但し、信号フォーマット変換部 4 のマスク部の動作が異なる。

## [0081]

図16(a)~(e)は実施の形態4におけるマスク部26の動作を説明する図である。図16(b)、(c)は、フレームフォーマット変換部4に入力される映像信号d3の具体例としてのd3a、d3b及びマスク部26から出力される映像信号d6の具体例としてのd6a、d6b、図16(a)は、映像信号d3a、d3bの水平同期信号、図16(d)、(e)はマスク部26から出力されるマスク信号m6の具体例としてのm6a、m6bを示す。

# [0082]

図16(d)、(e)に示すマスク信号m6a、m6bが、図13(g)、(i)に示すマスク信号と異なる点は、マスク信号が1ラインおきに当該ラインの全データをマスクする(1ラインおきのラインを選択し、当該ラインの全データをマスクする)点である。また1ラインおきのラインの間に位置するライン(選択しないライン)においても、図13

10

20

30

40

(g)、(i)と同様に、当該ラインのうちの左目用画像のデータ及び右目用画像のデータのうちの一方を、交互にマスクする。

#### [0083]

図17(a)~(c)は、本実施の形態における各工程での画像サイズの変化を説明する図である。図17(a)は、映像信号d1の画像サイズ、図17(b)は、マスク処理後映像信号d6mの画像サイズ、図17(c)は、画像表示部62に供給される映像信号d4の画像サイズ、従って空間変調部5のサイズ(画素数)を示す。

### [0084]

例えば受信部 1 から出力される映像信号 d 1 の右目用画像と左目用画像が図 1 7 (a) に示すように、フルHD(1920 d o t x 1 0 8 0 l i n e) のそれぞれ半分を占めるとする。このとき信号フォーマット変換部 4 のフレームメモリから読み出される映像信号 d 6 m は図 1 7 (b) に示すように、960 d o t x 5 4 0 l i n e と受信部 1 から出力される映像信号 d 1 (図 1 7 (a)) のサイズの 4 分の 1 になる。

このとき、フォーマット変換時にフレームメモリへアクセスするのに必要となるバス帯 域も4分の1となる。

#### [0085]

空間変調部 5 のサイズ(画素数)が図 1 7 ( c )に示すように、受信部 1 から出力される映像信号 d 1 のサイズと同じ場合、サイズを増やす必要があるのは前記のとおりである

## [0086]

図18(a)~(d)は本実施の形態におけるフレームメモリ制御部27の動作を説明した図である。図18(b)、(c)は、マスク部26から出力される映像信号d6の具体例としてのd6a及びマスク信号m6の具体例としてのm6a、図18(a)は、映像信号d6aの水平同期信号、図18(d)は、フレームメモリ制御部24から出力される映像信号d7を示す。

図8(a)~(d)、図9(a)~(g)に示すフレームメモリ制御部24の動作と異なる点は、フレームメモリ23より、2ライン連続して同じデータを読み出す点である。

#### [0087]

以上説明したように、フレームメモリ制御部27において2ライン連続して同じデータを読み出すことで、空間変調部5に必要なサイズの映像信号を得られるうえ、フレームメモリアクセスに必要なバス帯域を低く抑えることが可能になる。

# [0088]

なお、フレームメモリ制御部 2 7 では 1 ラインおきにフレームメモリに書き込まれている映像データ d 6 を読み出し、空間変調部 5 において 2 ライン連続して同じデータを書き込んでも同じ効果が得られる。

また、ここでは1ラインおきに全データをマスクする例を説明したが、複数ライン連続 してマスク処理を行うことで、さらにフレームメモリのアクセスバス帯域を低くできる。

### [0089]

## 実施の形態5.

実施の形態5の画像表示装置の全体的構成は、実施の形態1に関し図1を参照して説明したのと同じであるが、実施の形態5の画像表示装置は、図1の画像データ処理部61の代わりに、図19に示される画像データ処理部63を備えている。

図19に示される画像データ処理部63は、図1に示す画像データ処理部61と概して同じであるが、図1の信号フォーマット変換部4の代わりに信号フォーマット変換部28が設けられ、さらにオーバードライブ部29が付加されている点で異なる。

# [0090]

受信部1から出力された映像信号 d 1 は高画質化処理部2に入力される。高画質化処理部2では、映像信号 d 1 に対して、システム制御部6から送られてくる制御情報Srを基に、輪郭強調や色補正といった、いわゆる高画質化処理を施し、映像信号 d 2 を出力する

20

10

30

50

#### [0091]

高画質化処理部2から出力された映像信号d2はFRC部3に入力される。FRC部3は、システム制御部6から送られてくる制御情報Srを基に、映像信号d2のフレームレートを変換し、映像信号d3を信号フォーマット変換部28に出力する。

FRC部3はまた、サブフレームフラグOEを生成し、信号フォーマット変換部28に出力する。

#### [0092]

信号フォーマット変換部28は、システム制御部6から送られてくる制御情報Sr、並びに、FRC部3から入力される映像信号d3及びサブフレームフラグOEを基に、入力された映像信号d3の画素並び変換を行い、その結果生成された映像信号d4及びd8をオーバードライブ部29に出力する。

信号フォーマット変換部28はまた、FRC部3から入力されるサブフレームフラグOEを基に選択制御信号LRを生成し、3Dメガネ制御部8に出力する。

## [0093]

オーバードライブ部 2 9 は、信号フォーマット部 2 8 から出力される映像信号 d 4 、および d 8 に基づいて、液晶パネル 1 5 の液晶に印加される電圧に対応する画像の各画素の階調値を表す映像信号 d 9 を生成し、画像表示部 6 2 及び光源制御部 7 に出力する。

## [0094]

光源制御部7は、オーバードライブ部29から出力される映像信号d9、およびシステム制御部6から送られてくる制御情報Srに基づき、画像表示に用いる光源の点灯、消灯を制御する光源制御信号c2を生成し、画像表示部62に出力する。光源制御部7はまた、光源の点灯、消灯のタイミングよりタイミング信号c1を生成し、3Dメガネ制御部8に出力する。

#### [0095]

3 D メガネ制御部 8 は、信号フォーマット変換部 2 8 から出力された選択制御信号 L R と、光源制御部 7 から出力されたタイミング信号 c 1 を基に、 3 D メガネ制御信号 c 3 を生成し、 3 D メガネ 6 4 のシャッタを制御する。具体的には 3 D メガネ 6 4 に右目用、左目用それぞれ独立に組み込まれている、透過型の液晶シャッタ 6 4 R、 6 4 L を、右目にのみ光を透過させる、または左目にのみ光を透過させるように切り替え制御する。

## [0096]

図20は本実施の形態における信号フォーマット変換部28の詳細ブロック構成を示した図である。図12に示す信号フォーマット変換部4と構成の異なる点は、図12のフレームメモリ制御部27の代わりに、フレームメモリ制御部30が用いられている点である。フレームメモリ制御部30は、フレームメモリ制御部27と概して同じであるが、その動作、特に映像信号d4に加えて、別個の映像信号d8を出力する点で異なる。

#### [0097]

FRC部3より出力された映像信号d3、およびサブフレームフラグOEはマスク部26に入力される。

マスク部 2 6 では入力される映像信号 d 3 が 3 D 表示用映像信号である場合、サブフレームフラグ O E を基にマスク信号 m 6 を生成し、映像信号 d 6 と共にフレームメモリ制御部 3 0 に出力する。

#### [0098]

フレームメモリ制御部 3 0 は、入力された映像信号 d 6 に含まれる同期信号を基にメモリアドレスを生成する。ただしメモリアドレスはマスク信号 m 6 が L o の期間のみ生成される。これにより、入力される映像信号 d 6 が 3 D表示用映像信号である場合、フレームメモリ制御部 3 0 に入力される映像信号 d 6 は、フレームごとに右目用画像のデータのみ、または左目用画像のデータのみが交互に選択され、フレームメモリ 2 3 に書き込まれる

## [0099]

これにより、フレームメモリへの書込みに必要となるメモリアクセスのバス帯域は、入

20

10

30

50

10

20

30

40

50

力される映像信号 d 6 が通常の映像信号である場合 (3 D表示用信号ではない場合)の半分となる。

## [0100]

フレームメモリ制御部30は、フレームメモリ23に蓄積された映像信号の読み出しを も行う。

ここで、フレームメモリ制御部30は、入力される映像信号 d 6 が、3D表示用映像信号であるか否かで異なる動きをする。

## [0101]

フレームメモリ制御部 3 0 に入力される映像信号 d 6 が 3 D 表示用映像信号である場合、フレームメモリ制御部 3 0 は、フレームメモリ 2 3 に記憶された連続する 2 フレームの映像信号 d 7 、 d 8 を同時に読み出す。

### [0102]

フレームメモリ制御部30から出力された映像信号 d 8 は、オーバードライブ部29に出力される。

また、フレームメモリ制御部30から出力された映像信号d7は、セレクタ25に入力される。セレクタ25は、システム制御部6から送られる制御情報Srにより、3Dモード処理が指示された場合、フレームメモリ制御部24から出力された映像信号d7を映像信号d4として出力する。

#### [0103]

一方、フレームメモリ制御部30に入力される映像信号 d 6 が通常の映像信号である場合(3D表示用映像信号ではない場合)、フレームメモリ制御部30は、フレームメモリ23に記憶された1フレーム前の映像データd 8 のみを読み出す。この場合、フレームメモリ23に蓄えられている映像信号はマスク部26でマスキングが行われない(従って、サブサンプリングが行なわれない)ため、3D表示用映像信号の2倍のデータ量を有する

しかしながら、フレームメモリ23から1フレーム分のデータのみを読み出すので、読み出しに必要となるバス帯域の量は、3D表示用映像信号が入力されてきた場合に2フレーム分のデータを読み出すのと変わらない。

# [0104]

通常処理(非 3 D モード)の時には、セレクタ 2 5 は入力された映像信号 d 3 を映像信号 d 4 として出力する。

# [0105]

図21(a)~(o)は信号フォーマット変換部28の動作を説明する図である。図21(c)は、信号フォーマット変換部28に入力される映像信号d3の具体例としてのd3bを示し、図21(a)、(b)は、信号d3bの垂直同期信号、水平同期信号を示し、図21(e)、(f)は、マスク部26から出力される映像信号d6の具体例としてのm6bを示し、図21(h)、(i)は、図21(e)、(f)の映像信号d6b及びマスク信号m6bの時間軸方向に拡大して示し、図21(d)は、図21(e)の映像信号d6bの垂直同期信号を示し、図21(g)は、図21(h)の映像信号d6bの水平同期信号を示し、図21(k)、(1)は、フレームメモリ制御部30から出力される映像信号d8、d7を示し、図21(j)は、映像信号d8、d7の垂直同期信号VSを示し、図21(o)は、図21(1)の映像信号d7を時間軸方向に拡大して示し、図21(n)は、図21(o)と同じ時間軸スケール上に描かれた、フレームメモリ23から読み出される映像信号d7yを示し、図21(m)は、図21(n)の映像信号d7yの水平同期信号を示す。

# [0106]

信号フォーマット変換部28に入力された映像信号d3は、マスク部26に入力される

マスク部26では、例えば映像信号d3が図21(c)に示すd3bのように、1画素 ごとに右目用画像のデータと左目用画像のデータが交互に配置されており、かつ各水平ラ イン内における右目用画像のデータと左目用画像のデータの順序(各ラインの最初にどちらが現れるかが)1水平ラインごとに切り替わるものである場合、マスク信号m6としてはフレームごとに映像信号d3bに含まれる右目用画像のデータと左目用画像データの期間が交互に選択されるマスク信号m6b(図21(f)、(i))が生成され、画像データd6b(図21(e)、(h))と共にフレームメモリ制御部30に出力される。

## [0107]

フレームメモリ制御部 3 0 は、入力された映像信号 d 6 b に含まれる同期信号を基にメモリアドレスを生成する。ただしメモリアドレスはマスク信号 m 6 b が L o の期間のみ生成される。これにより、フレームメモリ制御部 3 0 に入力される映像信号 d 6 b は、フレームごとに交互に右目用画像のデータのみ、または左目用画像のデータのみが選択され、フレームメモリ 2 3 に書き込まれる。

#### [0108]

フレームメモリ制御部 3 0 は、フレームメモリ 2 3 に蓄積された映像信号の読み出しを も行う。

フレームメモリ制御部30は、フレームメモリ23に記憶された少なくとも連続する2フレーム分の映像信号d6bを、2フレーム同時に読み出していく。

具体的には、画像表示部62で表示する現フレーム映像信号d7y(図21(n))とともに、1フレーム前の映像信号d8yを、フレームメモリ23から同時に読み出す。

ここで、映像信号 d 7 y および映像信号 d 8 y は、それぞれ入力される映像信号 d 3 b の半分のデータ量になっている。

## [0109]

フレームメモリ制御部30では、フレームメモリ23から読み出された映像信号d7yを、0次ホールドにより、2画素にわたり繰り返し出力することで、入力された映像信号d3bと同じデータ量の映像信号d7(図21(1)、(o))を生成するとともに、フレームメモリ23から読み出された映像信号d8yを、0次ホールドにより、2画素にわたり繰り返し出力することで、入力された映像信号d3bと同じデータ量の映像信号d8(図21(k))を生成する。

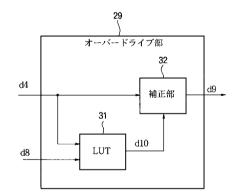

#### [0110]

図22はオーバードライブ部29の内部構成の一例を示すブロック図である。 オーバードライブ部29は、ルックアップテーブル31と補正部32とを備える。 フレームメモリ制御部30より出力された映像信号 d4、および映像信号 d8はルックアップテーブル31に入力される。また映像信号 d4は補正部32にも入力される。 ルックアップテーブル31は、1フレーム前の映像信号 d8と現フレーム映像信号 d4

## [0111]

の両者の値に基づいて補正量 d 1 0 を出力する。

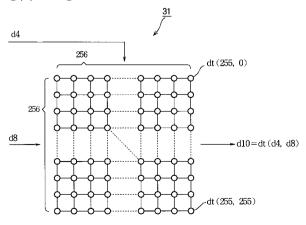

図23は、ルックアップテーブル31の構成の一例を示す模式図である。ルックアップテーブル31には、現フレーム映像信号d4、および1フレーム前の映像信号d8の値が読み出しアドレスとして入力される。現フレーム映像信号d4、および1フレーム前の映像信号d8がそれぞれ8ビットの画像データの場合、ルックアップテーブル31には256×256個のデータが補正量d10として格納されている。ルックアップテーブル31は、現フレーム映像信号d4、および1フレーム前の映像信号d8の各値に対応する補正量d10=dt(d4,d8)を読み出して出力する。

## [0112]

補正部32は、ルックアップテーブル31により出力された補正量d10を現フレーム映像信号d4に加算し、補正画像データd9を出力する。

# [0113]

以上説明したように、信号フォーマット変換時に、現フレーム映像信号に加え、1フレーム前の映像信号を同時に読み出し、1フレーム前の映像信号と現フレーム映像信号の両者の値に基づいて、液晶パネルの液晶に印加される電圧に対応する画像の各画素の階調値を表す映像信号を生成し、液晶パネルを駆動させることで、3D表示用映像信号が入力さ

10

20

30

40

れた場合にも、液晶パネルの応答速度を改善させることが可能になる。

## [0114]

また、3D表示用映像信号が入力された場合に、信号フォーマット変換前に、予めマスク信号を生成し、マスク信号に基づきフレームメモリに映像信号を書き込むことで、フレームメモリのバス帯域を抑えることが可能になる。

## [0115]

さらに、通常の映像信号が入力された場合(3D表示用映像信号が入力されなかった場合)には、現フレーム映像信号として、信号フォーマット変換部に入力される映像信号を選択することを可能にし、これにより、フレームメモリのバス帯域を抑えることが可能になる。

フレームメモリのバス帯域を抑制する結果、電力消費を節約することもできる。

### 【符号の説明】

## [0116]

1 受信部、 2 高画質化処理部、 3 FRC部、 4 信号フォーマット変換部 3 Dメガネ制御部、 9 フレームメモリ制御部、 10 フレームメモリ、 11 フレームメモリ、 11 フレームメモリ、 12 フレームメモリ制御部、 13 セレクタ、 14 光源部、 15 液晶パネル、 16 全反射ミラー、 17 ダイクロイックプリズム、 18 投射レンズ、 19 ダイクロイックミラー、 20 セレクタ、 21 フレーム補間部、 22 セレクタ、 23 フレームメモリ、 24 フレームメモリ制御部、 25 セレクタ、 26 マスク部、 27 フレームメモリ制御部、 28 信号フォーマット変換部、 29 オーバードライブ部、 30 フレームメモリ制御部、 31 ルックアップテーブル、 32 補正部、 61 画像データ処理部、 62 画像表示部、 63 画像データ処理部、 81 画像表示装置。

【図1】 【図2】

20

## 【図3】

# 【図4】

# 【図5】

# 【図7】

# 【図6】

【図8】

# 【図9】

# 【図10】

# 【図11】

# 【図12】

# 【図14】

(a)

d1

【図13】

【図19】

【図21】

(a)垂直同期 [L

(b)水平同期口

□解回直垂(p)

(e) d6b (f) m6b

【図20】

(g)水平同期门 (h) d6b

qgm

Э

(j) VS (k) d8 (l) d7 (m)水平同期

ď7y

47

【図22】

【図23】

## フロントページの続き

| (51) Int.CL. | Г |   | т |

|--------------|---|---|---|

| (SI) Int G   |   | _ |   |

|              |   |   |   |

| G 0 9 G | 5/38  | (2006.01) | G 0 9 G | 5/36  | 5 2 0 M |

|---------|-------|-----------|---------|-------|---------|

| G 0 2 F | 1/133 | (2006.01) | G 0 9 G | 5/38  | Α       |

|         |       |           | G 0 2 F | 1/133 | 5 3 5   |

|         |       |           | G 0 2 F | 1/133 | 5 7 5   |

# (72)発明者 岡崎 幸治

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

## 審査官 鈴木 明

# (56)参考文献 特表2007-531473(JP,A)

特開2000-050312(JP,A) 特開平09-331549(JP,A) 特開平06-169475(JP,A)

# (58)調査した分野(Int.CI., DB名)