(12)发明专利

(10)授权公告号 CN 105432018 B

(45)授权公告日 2019.01.08

(21)申请号 201480042802.7

专利权人 巴法络股份有限公司

(22)申请日 2014.06.09

(72)发明人 大塚寛治 佐藤阳一 冲永隆幸

(65)同一申请的已公布的文献号

东修一郎

申请公布号 CN 105432018 A

(74)专利代理机构 北京林达刘知识产权代理事

务所(普通合伙) 11277

(43)申请公布日 2016.03.23

代理人 刘新宇

(30)优先权数据

2013-157090 2013.07.29 JP

(51)Int.CI.

H03K 19/21(2006.01)

G06F 1/02(2006.01)

(85)PCT国际申请进入国家阶段日

2016.01.28

(56)对比文件

US 6487190 B1,2002.11.26,

US 6181164 B1,2001.01.30,

CN 101142747 A,2008.03.12,

CN 101147325 A,2008.03.19,

(86)PCT国际申请的申请数据

PCT/JP2014/065245 2014.06.09

审查员 李劲涛

(87)PCT国际申请的公布数据

W02015/015905 JA 2015.02.05

权利要求书1页 说明书10页 附图9页

(73)专利权人 学校法人明星学苑

地址 日本东京都

(54)发明名称

逻辑运算装置

(57)摘要

提供一种逻辑运算装置,该逻辑运算装置能够以较小规模的电路结构在较短时间内进行运算处理。一种逻辑运算装置,包括存储器设备(12),该存储器设备(12)接收N(N为大于等于2的整数)比特长度的位串的输入,在所输入的该位串所表示的地址中存储查找表,其中,该查找表是保存多比特长度的数据而成,该多比特长度的数据的一部分包含表示所输入的该位串所包含的各比特间的逻辑运算结果的比特,该逻辑运算装置访问存储器设备(12),输出在所接收的位串所表示的地址中保存的数据所包含的比特。

1. 一种逻辑运算装置,包括:

存储器设备,其接收N比特长度的位串的输入,在所输入的所述位串所表示的地址中存储查找表,其中,该查找表是保存多比特长度的数据而成的,针对各地址中存储的查找表,所保存的多比特长度的数据的固定位为表示在与该地址相应的所输入的位串所包含的各比特间进行同一逻辑运算的结果的比特,N为大于等于2的整数;以及

输出单元,其访问所述存储器设备,输出在所接收的所述位串所表示的地址中保存的数据所包含的表示该位串所包含的各比特间进行同一逻辑运算的结果的比特。

2. 根据权利要求1所述的逻辑运算装置,其特征在于,

在保存于所述存储器设备中的数据中包含所输入的所述位串所包含的各比特间的逻辑运算结果及其反转比特,

所述输出单元选择性地输出该比特间的逻辑运算结果及其反转比特中的一方。

3. 根据权利要求2所述的逻辑运算装置,其特征在于,

还包括分割单元,该分割单元接收M比特长度的位串的输入,从该M比特长度的位串提取N比特的位串,并将所提取的该N比特的位串分时地输出到所述存储器设备,其中,M为大于N的整数,

在分时地输出所述N比特的位串时,所述输出单元使用前次输出的比特来选择性地输出访问存储器设备而取出的比特间的逻辑运算结果及其反转比特中的一方。

4. 根据权利要求1~3中的任一项所述的逻辑运算装置,其特征在于,

保存于所述存储器设备中的逻辑运算结果是输入位串所包含的各比特间的异或的运算结果。

## 逻辑运算装置

### 技术领域

[0001] 本发明涉及一种进行包含在所输入的位串中的比特间的逻辑运算的逻辑运算装置。

### 背景技术

[0002] 伴随着信息处理技术、信息通信技术的发展和普及,要求更高速且更大容量的信息处理技术。例如近年来,在信息处理时的纠错处理中要求能够进行更多比特长度的数据的纠错。

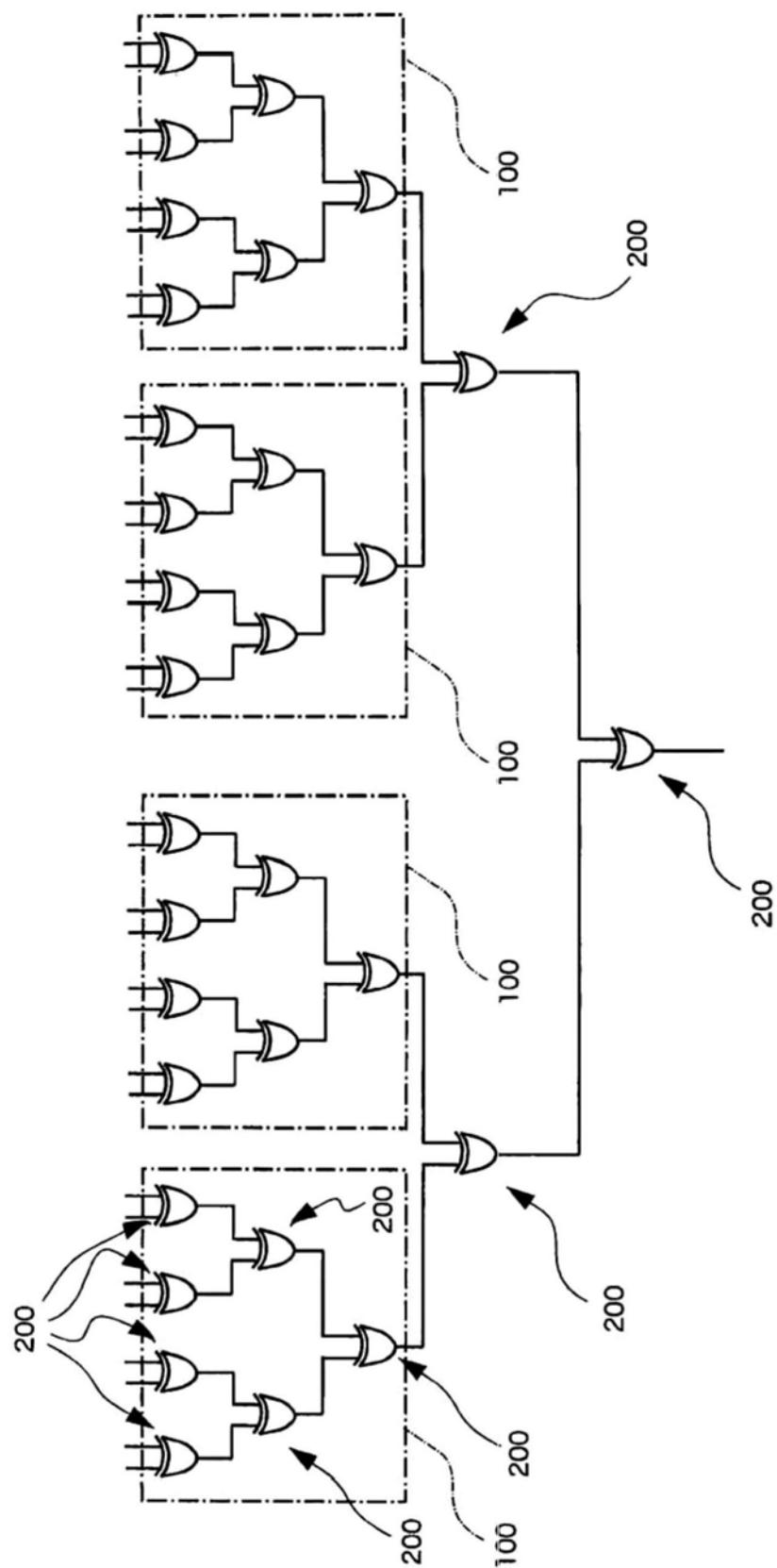

[0003] 在进行该纠错时,由于进行输入比特的奇偶校验等,需要求出所输入的比特间的异或(XOR或者EOR)。以往,与多比特长度的数据有关的异或的运算装置是将2输入异或电路进行组合而构成。例如,图11示出计算32比特长度的异或的逻辑运算装置的例子。

[0004] 如图11所例示,计算该32比特长度的异或的逻辑运算装置包括四个8输入异或电路100以及三个2输入异或电路200。另外,8输入异或电路100的内部包括七个2输入异或电路200。

[0005] 此外,非专利文献1中公开了多输入(3输入)的异或门的例子。

[0006] 非专利文献1:inet:“74LVC1G3863-input EXCLUSIVE-OR gate”、[online]、2007年9月3日、[日本平成25年7月16日检索]、因特网<URL:[http://www.jp.nxp.com/documents/data\\_sheet/74LVC1G386.pdf](http://www.jp.nxp.com/documents/data_sheet/74LVC1G386.pdf)>

### 发明内容

[0007] 发明要解决的问题

[0008] 然而,近年来越来越要求进行多比特长度的数据处理,存在如下问题:由于2输入异或电路的组合而电路规模变大,另外由于构成多级门导致运算处理时间也变长。

[0009] 本发明是鉴于上述实际情况而完成的,其目的之一在于提供一种即使是多比特长度的数据也能够以较小规模的电路结构在较短时间内进行运算处理的逻辑运算装置。

[0010] 用于解决问题的方案

[0011] 用于解决上述以往例的问题的本发明是一种逻辑运算装置,包括:存储器设备,其接收N(N为大于等于2的整数)比特长度的位串的输入,在所输入的所述位串所表示的地址中存储查找表,其中,该查找表是保存多比特长度的数据而成的,该多比特长度的数据的一部分包含表示所输入的该位串所包含的各比特间的逻辑运算结果的比特;以及输出单元,其访问所述存储器设备,输出在所接收的所述位串所表示的地址中保存的数据所包含的比特。

[0012] 发明的效果

[0013] 根据本发明,能够以较小的电路结构在较短时间内进行运算处理。

### 附图说明

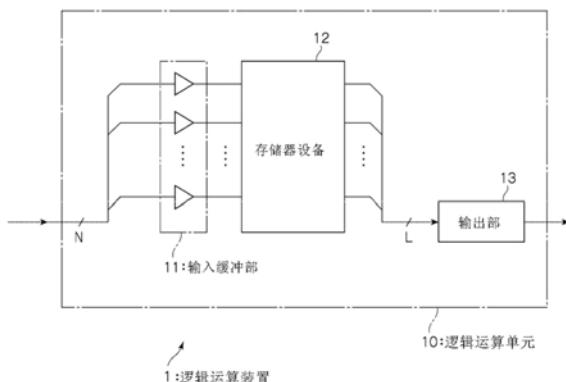

[0014] 图1是表示本发明的实施方式所涉及的逻辑运算装置的结构例的框图。

[0015] 图2是表示本发明的实施方式所涉及的逻辑运算装置所具备的查找表的内容例的说明图。

[0016] 图3是表示本发明的实施方式所涉及的逻辑运算装置所具备的查找表的另一个内容例的说明图。

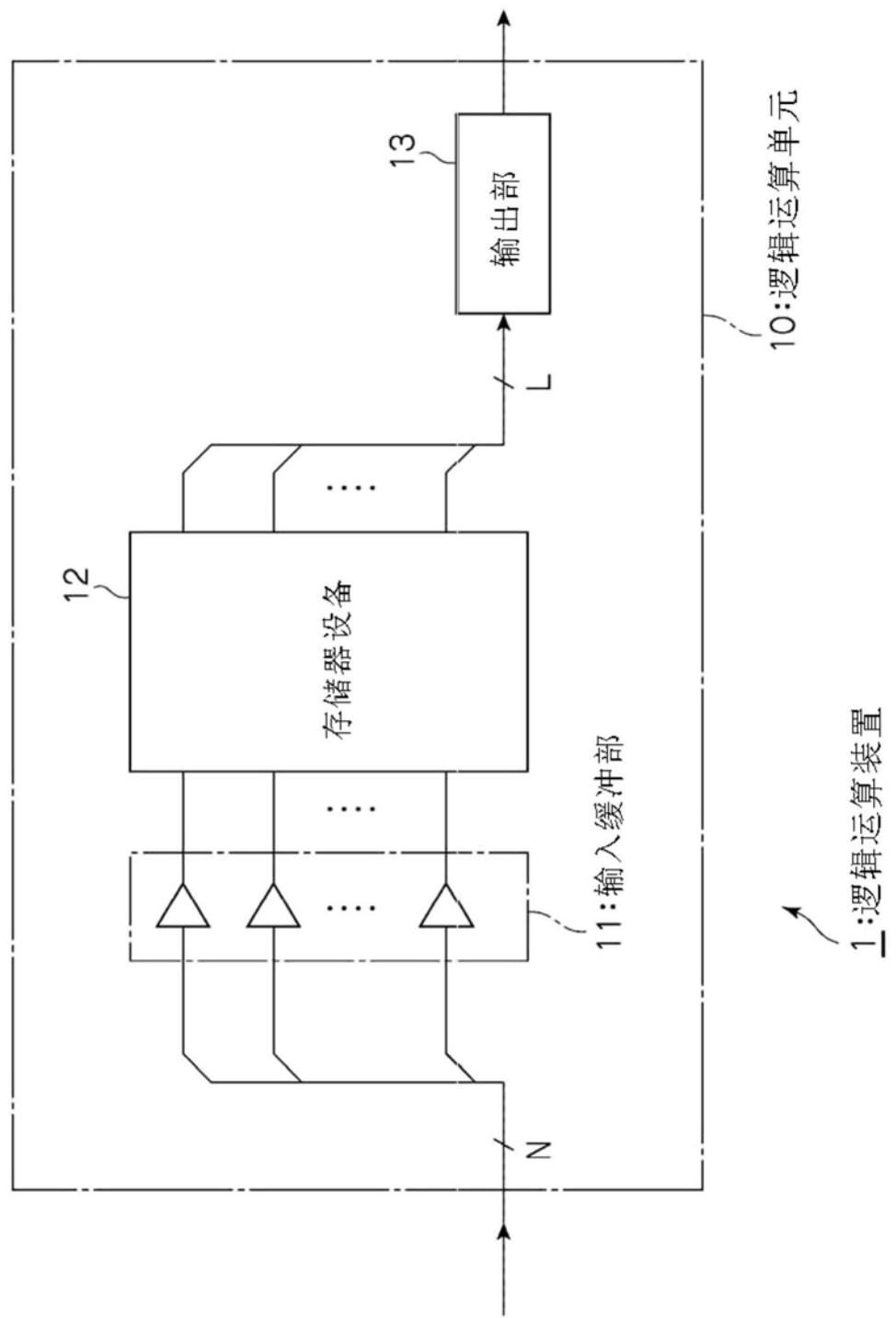

[0017] 图4是表示本发明的实施方式的另一个例子所涉及的逻辑运算装置的结构例的框图。

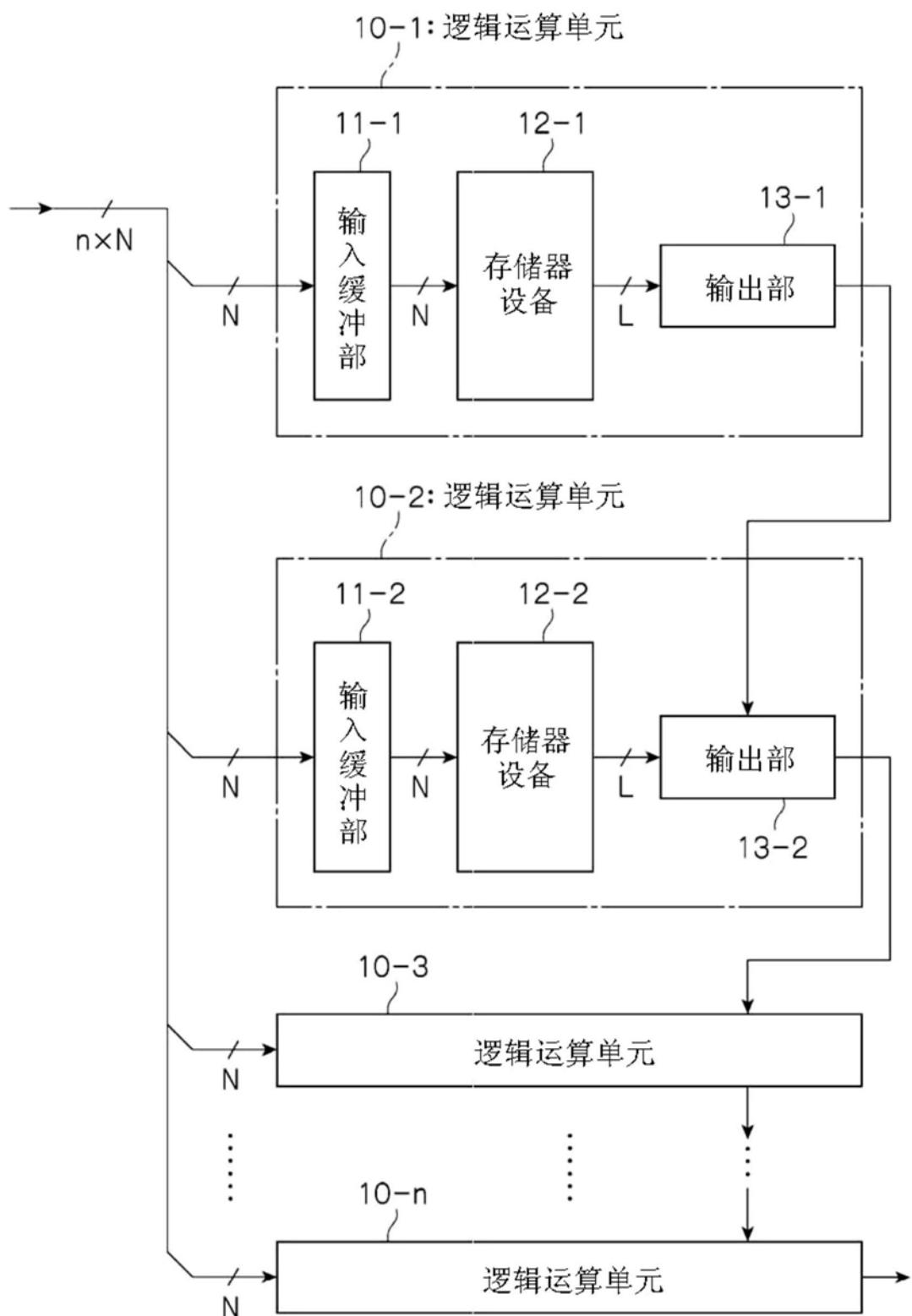

[0018] 图5是表示本发明的实施方式的再一个例子所涉及的逻辑运算装置的结构例的框图。

[0019] 图6是表示本发明的实施方式所涉及的逻辑运算装置的时钟供给部所输出的信号的例子的时序图。

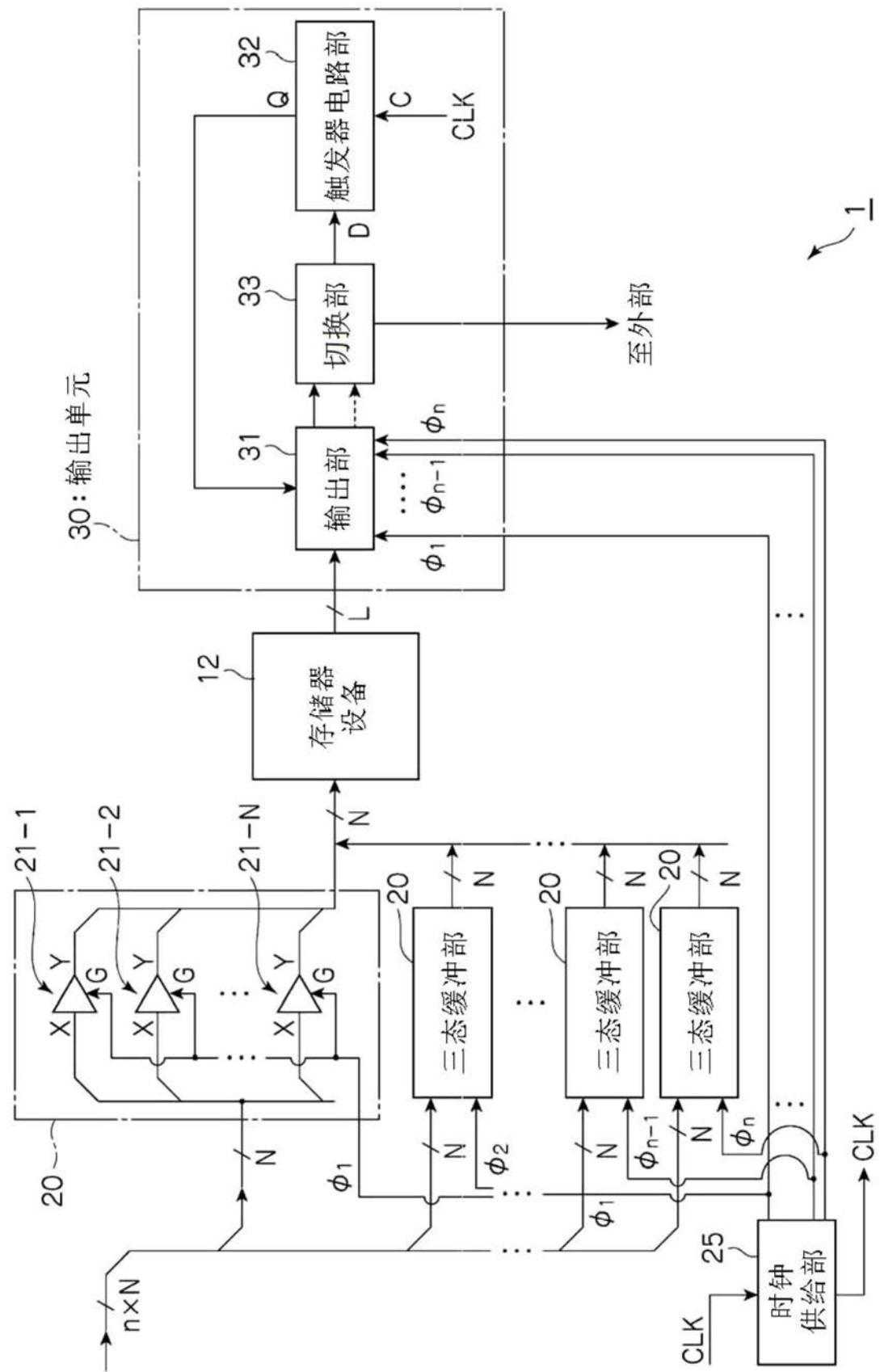

[0020] 图7是表示本发明的实施方式的又一个例子所涉及的逻辑运算装置的结构例的框图。

[0021] 图8是表示本发明的实施方式所涉及的逻辑运算装置所具备的又一个查找表的内容例的说明图。

[0022] 图9是表示本发明的实施方式所涉及的逻辑运算装置的输出级的其它电路例的说明图。

[0023] 图10是表示使用了本发明的实施方式所涉及的逻辑运算装置的进行与更多比特长度的位串有关的逻辑运算的装置的例子的说明图。

[0024] 图11是表示以往的计算32比特长度的异或的逻辑运算装置的例子的说明图。

[0025] 附图标记说明

[0026] 1:逻辑运算装置;10:逻辑运算单元;11:输入缓冲部;12:存储器设备;13、31:输出部;20:三态缓冲部;21:三态缓冲器;25:时钟供给部;30、40:输出单元;32:触发器电路部;33:切换部;41:选择部;51:逻辑反转电路;100:8输入异或电路;200:2输入异或电路。

## 具体实施方式

[0027] 参照附图说明本发明的实施方式。本发明的实施方式所涉及的逻辑运算装置1如图1所例示那样包括至少一个逻辑运算单元10。另外,该逻辑运算单元10基本上构成为包括输入缓冲部11、存储器设备12以及输出部13。

[0028] 输入缓冲部11接收N(N为大于等于2的整数)比特长度的位串的输入,并将该位串所表示的信号提供给存储器设备12的地址总线。即,在这里的例子中,N还与存储器设备12的地址总线宽度相当。

[0029] 具体地说,存储器设备12是非易失性存储器、SRAM(Static Random Access Memory:静态随机存取存储器)等半导体存储器,具备 $2^N$ 比特×L比特(L为大于等于2的整数)的存储单元。该存储器设备12在从该输入缓冲部11输入的位串所表示的地址中保存了查找表,该查找表是保存多比特长度的数据而成的,该多比特长度的数据的一部分包含表示所输入的该位串所包含的各比特间的逻辑运算结果的比特。在以下的例子中,以在由一个地址所确定的位置处保存L=8比特的数据的情形来进行说明。

[0030] 具体地说,该查找表如图2所例示,在N=8比特长度的位串“00000000”所表示的地

址中保存数据“0XXXXXXX”(在此,X可以是不定值),该数据“0XXXXXXX”的MSB(最高位比特)包含了该位串“00000000”的异或的运算结果、即“0”。另外,在位串“00000001”所表示的地址中保存数据“1XXXXXXX”(X可以是不定值),该数据“1XXXXXXX”的MSB(最高位比特)包含了该位串“00000001”的异或的运算结果、即“1”。

[0031] 输出部13读出存储器设备12所保存的数据中的在输入缓冲部11所输出的位串所表示的地址中保存的数据。该输出部13选择性地输出该读出的数据中的包含上述逻辑运算结果的比特。在本实施方式的上述例子中,MSB包含逻辑运算结果,因此该输出部13读出存储器设备所保存的数据中的在输入缓冲部11所输出的位串所表示的地址中保存的数据,并输出该数据中的MSB的比特。

[0032] 另外,在本实施方式的另一例子中,存储器设备12在从该输入缓冲部11输入的位串所表示的地址中保存了查找表,该查找表是保存多比特长度的数据而成的,该多比特长度的数据的一部分包含表示该输入的位串所包含的各比特间的逻辑运算结果的比特及其反转比特。

[0033] 具体地说,该查找表如图3所例示,在N=8比特长度的位串“00000000”所表示的地址中保存数据“01XXXXXX”(在此,X可以是不定值),该数据“01XXXXXX”的MSB(最高位比特)包含该位串“00000000”的异或的运算结果、即“0”,该数据“01XXXXXX”的次高位比特包含该运算结果的反转比特、即“1”。另外,在位串“00000001”所表示的地址中保存数据“10XXXXXX”(X可以是不定值),该数据“10XXXXXX”的MSB(最高位比特)包含该位串“00000001”的异或的运算结果、即“1”,该数据“10XXXXXX”的次高位比特包含其反转比特、即“0”。

[0034] 在该例子中,输出部13从外部接收1比特的信号的输入。而且,输出部13读出存储器设备12所保存的数据中的在输入缓冲部11所输出的位串所表示的地址中保存的数据,根据从外部输入的1比特的信号是“0”还是“1”来选择性地输出该数据中的上述逻辑运算结果及其反转比特中的某一个。在本实施方式的一个例子中,该输出部13在从外部输入的1比特的信号为“0”时,读出存储器设备所保存的数据中的在输入缓冲部11所输出的位串所表示的地址中保存的数据,输出该数据中的MSB的比特。另外,输出部13在从外部输入的1比特的信号为“1”时,读出存储器设备所保存的数据中的在输入缓冲部11所输出的位串所表示的地址中保存的数据,输出该数据中的MSB的下一比特(保存了逻辑运算结果的反转比特的比特)。

[0035] 本实施方式基本上具备有以上的结构,如下面的例子那样进行动作。在本实施方式的以下的例子中,设为如图4所例示的那样具备多个逻辑运算单元10\_1、10\_2、……、10\_n。另外,第i个逻辑运算单元10\_i的输出部13\_i接收第i-1个逻辑运算单元10\_i-1的输出比特作为来自外部的输入。此外,先头的逻辑运算单元10\_1的输出部13\_1设为不接收来自外部的输入(或者将来自外部的输入固定为“0”等),输出存储器设备12所保存的数据中的表示逻辑运算结果的比特(在上述例子中为MSB)。

[0036] 另外,在本实施方式的该例子中,接收8×n(存储器设备12的地址总线宽度的整数n倍)比特长度的数据D(将其第i个比特设为bi(i=1,2,……,8n))的输入作为异或的计算的对象。然后,从MSB侧(或者LSB侧)依次每8个比特(存储器设备12的地址总线宽度)分别输出到逻辑运算单元10\_1、10\_2、……、10\_n的缓冲部11\_1、11\_2、……、11\_n。

[0037] 逻辑运算单元10\_1的输出部13\_1读出存储器设备12\_1所保存的数据中的在输入到输入缓冲器11\_1的8比特长度的位串(b1、b2、……、b8)所表示的地址中保存的数据。然后,输出该读出的数据所包含的逻辑运算结果(在此,设为所输入的8比特长度的位串的异或的运算结果)的比特。

[0038] 下一逻辑运算单元10\_2的输出部13\_2读出存储器设备12\_2所保存的数据中的在输入到输入缓冲器11\_2的8比特长度的位串(b9、b10、……、b16)所表示的地址中保存的数据。另外,该输出部13\_2根据前级的逻辑运算单元10\_1的输出部13\_1所输出的比特选择该读出的数据所包含的逻辑运算结果的比特及其反转比特中的某一方来进行输出。具体地说,输出部13\_2在输出部13\_1所输出的比特为“0”时,输出所读出的数据所包含的逻辑运算结果。另外,输出部13\_2在输出部13\_1所输出的比特为“1”时,输出逻辑运算结果的反转比特。

[0039] 以下,第i个逻辑运算单元10\_i的输出部13\_i读出存储器设备12\_i所保存的数据中的在输入到输入缓冲器11\_i的8比特长度的位串(b8(i-1)+1、b8(i-1)+2、……、b8i)所表示的地址中保存的数据。另外,该输出部13\_i根据前级的逻辑运算单元10\_{i-1}的输出部13\_{i-1}所输出的比特选择该读出的数据所包含的逻辑运算结果的比特及其反转比特中的某一方来进行输出。具体地说,输出部13\_i在输出部13\_{i-1}所输出的比特为“0”时,输出所读出的数据所包含的逻辑运算结果。另外,输出部13\_i在输出部13\_{i-1}所输出的比特为“1”时,输出逻辑运算结果的反转比特。

[0040] 而且,第n个逻辑运算单元10\_n的输出部13\_n读出存储器设备12\_n所保存的数据中的在输入到输入缓冲器11\_n的8比特长度的位串(b8(n-1)+1、b8(n-1)+2、……、b8n)所表示的地址中保存的数据。另外,该输出部13\_n根据前级的逻辑运算单元10\_{n-1}的输出部13\_{n-1}所输出的比特选择该读出的数据所包含的逻辑运算结果的比特及其反转比特中的某一方来进行输出。具体地说,输出部13\_n在输出部13\_{n-1}所输出的比特为“0”时,输出所读出的数据所包含的逻辑运算结果。另外,输出部13\_n在输出部13\_{n-1}所输出的比特为“1”时,输出逻辑运算结果的反转比特。

[0041] 这样,使得第n个逻辑运算单元10\_n的输出部13\_n输出8×n比特长度的数据D所包含的各比特的逻辑运算结果(在这里的例子中为异或)。

[0042] 并且,在此叙述了并联使用多个逻辑运算单元10、总之存储器设备12的例子,但是本实施方式并不限于此。在本实施方式的另一例子中,也可以分时地利用存储器设备12。该例子所涉及的本发明的实施方式所涉及的逻辑运算装置1如图5所例示,构成为包括n个三态缓冲部20、存储器设备12、时钟供给部25以及输出单元30。另外,三态缓冲部20各自包括N(在这里的例子中为N=8)个三态缓冲器21,输出单元30包括输出部31、触发器电路部32以及切换部33。在此,对于与已经说明的部分结构上相同的部分附加相同的附图标记并省略说明。此外,在该例子中设为在存储器设备12中保存了图3所例示的数据。

[0043] 三态缓冲器21各自具备输入端子X、输出端子Y以及门端子G。该三态缓冲器21在门端子G的输入为“0”的期间,无论对输入端子X有何种输入都将输出端子Y的状态设为高阻抗状态“Z”。关于输出端子Y成为高阻抗的三态缓冲器21,从该输出端子Y的连接目的地来看,等同于绝缘的状态(连接被切断的状态)。

[0044] 在本实施方式的该例子中,8n个三态缓冲器21以第1个三态缓冲器21\_1~第8个三

态缓冲器21\_8的组、第9个三态缓冲器21\_9～第16个三态缓冲器21\_16的组……的方式被分为每8个一组。而且,从时钟供给部25向属于同一组的三态缓冲器21的门端子G输入相同的信号。关于该信号将在后面叙述。另外,从成为逻辑运算的对象的 $8 \times n$ 比特长度的数据D的MSB侧(或者LSB侧)依次将各比特的值输入到第*i*个三态缓冲器21\_*i*的输入端子X\_*i*。

[0045] 另外,第*i*个三态缓冲器21\_*i*的输出端子Y\_*i*连接于存储器设备12的地址总线中的第(*i* mod 8)个引脚。在此(*i* mod k)意味着*i*除以k时的余数。

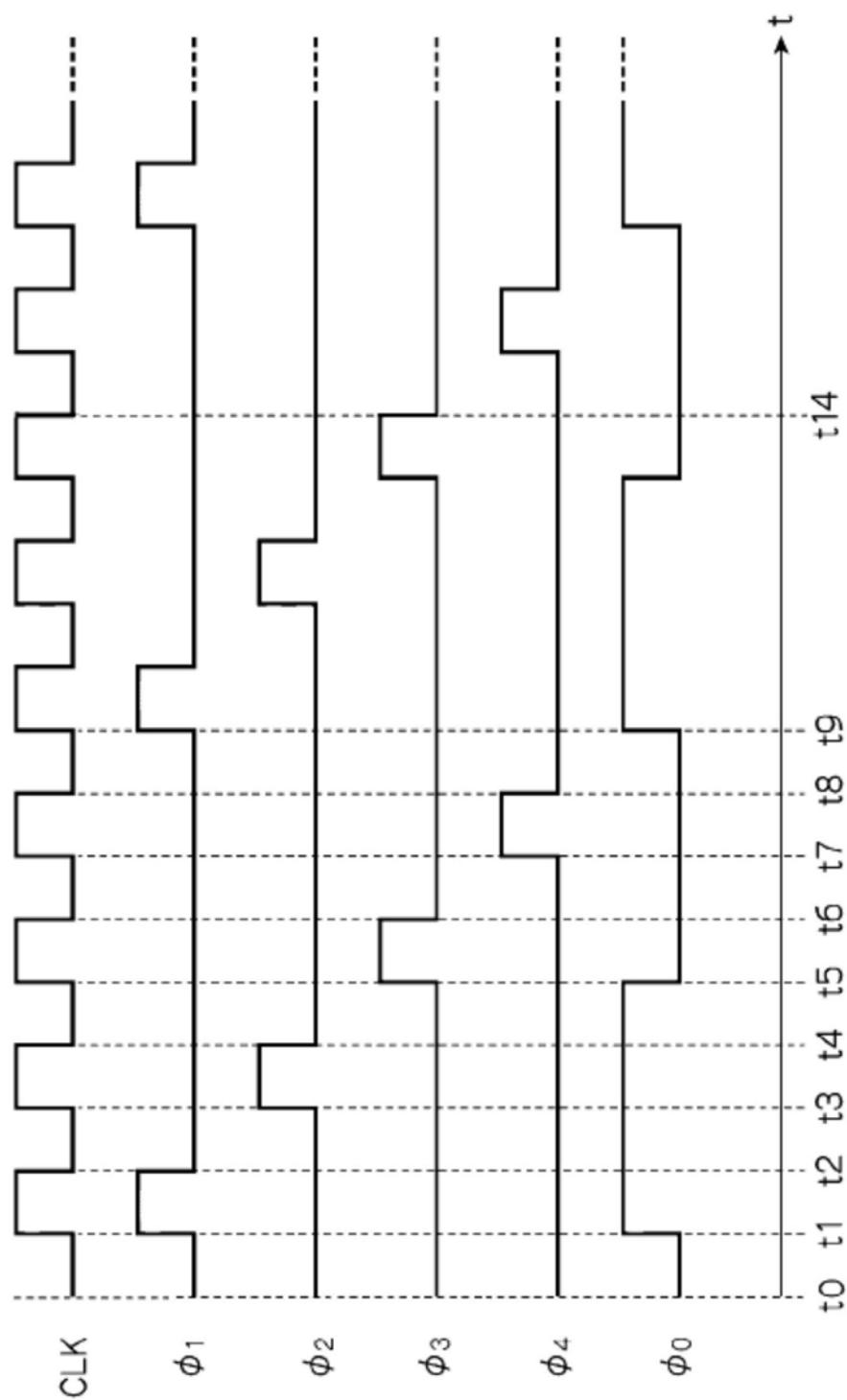

[0046] 时钟供给部25如图6所示,生成定期地反复进行上升和下降的时钟信号CLK并将其输出。另外,该时钟供给部25生成n个(n是将成为逻辑运算的对象的比特数8n除以作为存储器设备12的地址总线宽度的8所得到的值)的副时钟信号 $\varphi_i$ (*i*=1、2、……、n)。图6中例示了在n=4的情况下副时钟信号 $\varphi_1$ 、 $\varphi_2$ 、 $\varphi_3$ 、 $\varphi_4$ 以及 $\varphi_0$ 。

[0047] 该副时钟信号 $\varphi_i$ 的上升沿或者下降沿时刻如下那样。即,事先设为在时钟信号CLK从规定的时刻(例如t2)起第j次上升时*i*=(*j* mod n)+1的副时钟信号 $\varphi_i$ 上升,在时钟信号CLK第j次下降时*i*=(*j* mod n)+1的副时钟信号 $\varphi_i$ 下降。此时,成为*i*≠(*j* mod n)+1的副时钟信号 $\varphi_i$ 维持L的状态。

[0048] 例如,图6(表示n=4的例子)中,在时钟信号CLK在规定的时刻t2之后第一次上升时(时刻t3),*i*=(1 mod 4)+1=2的副时钟信号 $\varphi_2$ 上升,在时钟信号CLK在规定的时刻t2之后第一次下降时(时刻t4),*i*=(1 mod 4)+1=2的副时钟信号 $\varphi_2$ 下降。

[0049] 另外,时钟供给部25生成如下的副时钟信号 $\varphi_0$ 。即,该 $\varphi_0$ 在时钟信号CLK从规定时刻起第j次上升时如果(*j* mod n)=0则上升,在之后的时钟信号CLK的第n/2+1次或者第(n-1)/2+1次下降时等时钟信号CLK之后第n次下降之前下降。

[0050] 具体地说,在图6的例子中,在时钟信号CLK在规定的时刻t2之后第4次上升时(时刻t9),为(4 mod 4)=0,因此,时钟供给部25在该时刻进行控制使得副时钟信号 $\varphi_0$ 上升。另外,时钟供给部25在之后(时刻t9之后),进行控制使得副时钟信号 $\varphi_0$ 在时钟信号CLK的第n/2+1次或者第(n-1)/2+1次下降时(在此设为第n/2+1=3次)的下降时(时刻t14)之前下降。在图6的例子中,示出以下例子:进行控制,使得在从时刻t9起第n/2+1次、即第3次下降时的前一次时钟信号CLK上升的上升时刻,副时钟信号 $\varphi_0$ 下降。

[0051] 在此,时钟供给部25以将副时钟信号 $\varphi_1$ 提供给第1个三态缓冲器21\_1～第8个三态缓冲器21\_8、将副时钟信号 $\varphi_2$ 提供给第9个三态缓冲器21\_9～第16个三态缓冲器21\_16这样的方式将副时钟信号 $\varphi_i$ 分别提供给8个三态缓冲器21\_([i/8]+1)。在此,[\*]意味着不超过\*的最大的整数。

[0052] 通过这些三态缓冲器21和时钟供给部25的动作来实现接收分割单元,该分割单元接收M(M为大于N的整数)比特长度的位串的输入,从该位串提取N比特的位串,并将所提取的该N比特的位串分时地向存储器设备12输出。

[0053] 输出单元30的输出部31在从时钟供给部25输入的时钟信号CLK下降且副时钟信号

$\phi n$  (n是将成为逻辑运算的对象的比特数8n除以作为存储器设备12的地址总线宽度的8所得到的值) 未下降的定时, 接收触发器电路部32所输出的1比特的信号的输入并保持在缓冲器(未图示)中。而且, 输出部31接着在时钟信号CLK上升的定时, 读出存储器设备12所保存的数据中的在三态缓冲器21所输出的位串所表示的地址中保存的数据。输出部31根据保持在缓冲器中的1比特的信号是“0”还是“1”来选择性地输出该读出的数据中的上述逻辑运算结果及其反转比特中的某一个。

[0054] 在本实施方式的一个例子中, 该输出部31在保持于缓冲器中的比特为“0”时, 将从存储器设备12读出的数据中的MSB的比特(逻辑运算结果)输出到切换部33。另外, 该输出部31在保持于缓冲器中的比特为“1”时, 将从存储器设备12读出的数据中的MSB的下一比特(保存了逻辑运算结果的反转比特的比特)输出到切换部33。输出部31继续进行该输出直到接下来时钟信号CLK下降为止。

[0055] 另外, 该输出部31控制后面说明的切换部33。具体地说, 在时钟供给部25所输出的副时钟信号 $\phi n$  (n是将成为逻辑运算的对象的比特数8n除以作为存储器设备12的地址总线宽度的8所得到的值)上升的定时, 输出部31将后面说明的切换部33的输出目的地设定为输出至外部。而且, 接着在时钟供给部25所输出的时钟信号CLK上升的定时, 将切换部33的输出目的地设定为触发器电路部32。

[0056] 并且, 在时钟供给部25所输出的副时钟信号 $\phi n$ 下降的定时, 输出部31无论触发器电路部32的输出为何都在缓冲器中保持“0”的比特。以下将该动作称为输出部的复位动作。

[0057] 触发器电路部32例如构成为包括D型的触发器电路。具体地说, 在该触发器电路24中D端子(输入端子)接收输出部31的输出。另外, C端子(时钟端子)从时钟供给部25接收时钟信号CLK的输入。而且, 该触发器电路部32在时钟信号CLK上升的定时保持输入到作为输入端子的D端子的比特并在输出端子Q输出该比特的信号。在时钟信号CLK下降的定时也继续该输出。另外, 从该输出端子Q输出的比特作为来自触发器电路部32的输出而被输入到输出部31。

[0058] 切换部33接受来自输出部31的控制, 从而将从输出部31输入的1比特的信息选择性地输出到触发器电路部32以及外部中的某一个。

[0059] 接着说明本实施方式的该例子所涉及的逻辑运算装置1的动作。在此, 例如接收 $M = N \times n$  (存储器设备12的地址总线宽度N的整数n倍)比特长度的数据D(将其第i个比特设为 $b_i$  ( $i = 1, 2, \dots, N \times n$ ))的输入作为逻辑运算、即异或的计算的对象。而且, 从MSB侧(或者LSB侧)依次将第i个比特分别输入到第i个三态缓冲器 $21_i$ 。

[0060] 而且, 逻辑运算装置1如下那样进行动作。即, 当进行了输出部的复位动作时(图6的时刻 $t_0$ ), 输出部31将“0”的比特保持在缓冲器中。接着在时钟供给部25所输出的时钟信号CLK上升的定时(图6的时刻 $t_1$ ), 三态缓冲器 $21_1 \sim 21_8$ 将被输入的比特 $b_1, b_2, \dots, b_8$ 提供给存储器设备12的地址总线。

[0061] 输出部31读出存储器设备12所保存的数据中的在三态缓冲器 $21_1 \sim 21_8$ 所输出的位串所表示的地址中保存的数据。此时, 输出部31的缓冲器保持了“0”的比特, 因此该输出部31将从存储器设备12读出的数据中的MSB的比特(逻辑运算结果)作为第一次的运算结果R1进行输出。该输出R1经由切换部33输出到触发器电路部32并保持在触发器电路部32

中。

[0062] 接着当到时钟供给部25所输出的时钟信号CLK下降的定时(图6的时刻t2)时,三态缓冲器21\_1~21\_8的输出成为高阻抗。而且,输出部31从触发器电路部32接收前次的运算结果R1并保持到缓冲器中。

[0063] 接着在时钟供给部25所输出的时钟信号CLK上升的定时(图6的时刻t3),三态缓冲器21\_9~21\_16将被输入的比特b9、b10、……、b16提供给存储器设备12的地址总线。

[0064] 输出部31读出存储器设备12所保存的数据中的在三态缓冲器21\_9~21\_16所输出的位串所表示的地址中保存的数据。而且,输出部31在该缓冲器保持了“0”的比特时(运算结果R1为“0”时),将从存储器设备12读出的数据中的MSB的比特(逻辑运算结果)作为第二次的运算结果R2进行输出。另外,输出部31在该缓冲器保持了“1”的比特时(运算结果R1为“1”时),将从存储器设备12读出的数据中的MSB的下一比特(逻辑运算结果的反转比特)作为第二次的运算结果R2进行输出。该输出R2经由切换部33输出到触发器电路部32并保持在触发器电路部32中。

[0065] 以下同样地进行动作,在时钟供给部25所输出的副时钟信号 $\varphi n$ 上升的定时,输出部31将切换部33的输出目的地设定为输出至外部。另外,此时输出部31读出存储器设备12所保存的数据中的在三态缓冲器 $21_{(8 \times (n-1)+1)} \sim 21_{(8n)}$ 所输出的位串所表示的地址中保存的数据。而且,输出部31在该缓冲器保持了“0”的比特时(运算结果Rn-1为“0”时),将从存储器设备12读出的数据中的MSB的比特(逻辑运算结果)作为运算结果R进行输出。另外,输出部31在该缓冲器保持了“1”的比特时(运算结果Rn-1为“1”时),将从存储器设备12读出的数据中的MSB的下一比特(逻辑运算结果的反转比特)作为运算结果R进行输出。该输出经由切换部33提供给外部。

[0066] 接着在时钟信号CLK下降的定时,输出部31进行输出部的复位动作,接着在时钟信号CLK再次上升的定时,将切换部33的输出目的地设定为触发器电路部32。

[0067] 这样,在本实施方式的该例子中,输出部31作为如下单元而发挥功能:在分时地输出N比特的位串的定时,使用前次输出的比特来选择性地输出访问存储器设备而取出的比特间的逻辑运算结果及其反转比特中的一方进行输出。

[0068] 这样,在第n次中输出部31将 $8 \times n$ 比特长度的数据D所包含的各比特的逻辑运算结果(在此的例子中为异或)作为运算结果R进行输出。

[0069] 并且,这样分时地进行运算的情况下输出单元的例子并不限于该例子。即,存储器设备12的各地址所能保存的数据是8比特,因此还能够灵活利用该位宽来如下地构成。

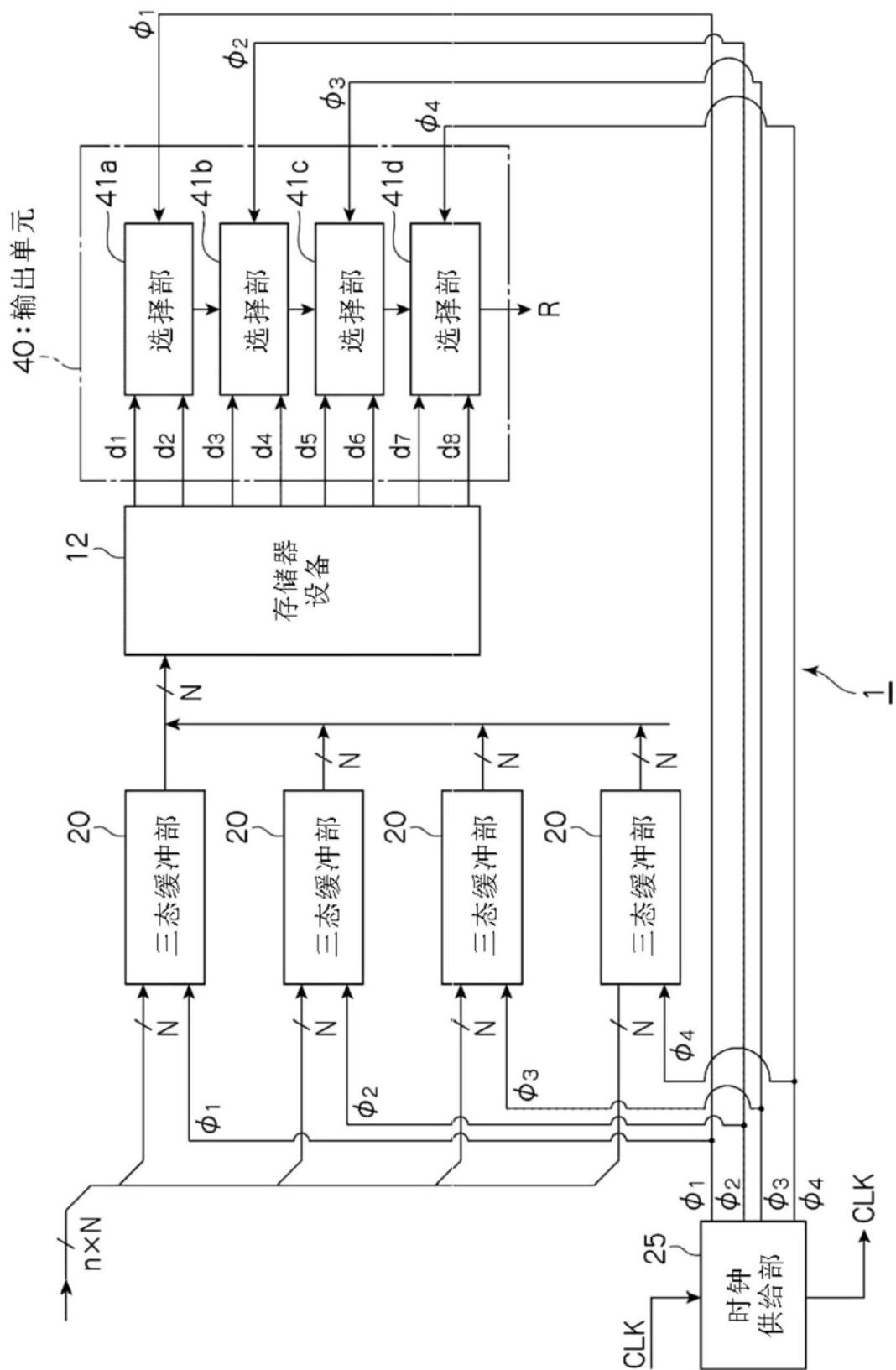

[0070] 本实施方式的再一例子所涉及的逻辑运算装置1如图7所例示那样构成为包括 $8 \times n$ 个(在此设为存储器设备12的地址总线宽度N=8)三态缓冲器21(与图5所例示的同样地每8个构成一个三态缓冲部20)、存储器设备12、时钟供给部25以及输出单元40。另外,输出单元40构成为包括四个(存储器设备12的数据总线宽度L的1/2)选择部41a、b、c、d。在此,对于与已经说明的部分结构上相同的部分附加相同的附图标记并省略说明。

[0071] 另外,在该例子中的存储器设备12中,如图8所例示,在8比特长度的地址A(以位串a1、a2、……、a8来表示)所示的位置处从MSB侧重复配置了基于位串a1、a2、……、a8的逻辑运算结果与其反转比特的组。即,在该例子中,在各地址的位置所保存的数据的第奇数个比特中分别保存逻辑运算结果,在第偶数个比特中保存第奇数个比特的反转比特。

[0072] 输出单元40的选择部41a连接有存储器设备12的数据总线中的作为MSB的d1和作为MSB的下一比特的d2的各信号线。另外,该选择部41a接收从外部输入的1比特的信号。

[0073] 而且,在从时钟供给部25输入的副时钟信号 $\varphi 1$ 上升的定时,选择部41a读出存储器设备12所保存的数据中的在三态缓冲器21所输出的位串所表示的地址中保存的数据并进行锁存。该选择部41a根据从外部接收的1比特的信号是“0”还是“1”来选择性地锁存并输出该读出的数据中的表示上述逻辑运算结果的MSB的1个比特以及表示其反转比特的MSB的下一比特中的某一个。

[0074] 在这里的例子中,选择部41a在从外部接收的比特为“0”时,选择从存储器设备12读出的数据中的MSB的比特(信号线d1所输出的逻辑运算结果)进行锁存、输出。另外,该选择部41a在从外部接收的比特为“1”时,选择从存储器设备12读出的数据中的MSB的下一比特(表示逻辑运算结果的反转比特的信号线d2的输出)进行锁存、输出。

[0075] 另外,选择部41b连接有存储器设备12的数据总线中的MSB侧的d3与作为其下一比特的d4的各信号线。另外,该选择部41b接收选择部41a所输出的1比特的信号。

[0076] 而且,在从时钟供给部25输入的副时钟信号 $\varphi 2$ 上升的定时,选择部41b读出存储器设备12所保存的数据中的在三态缓冲器21所输出的位串所表示的地址中保存的数据并进行锁存。该选择部41b根据从选择部41a接收的1比特的信号是“0”还是“1”来选择性地锁存并输出该读出的数据中的表示上述逻辑运算结果的MSB侧的1个比特以及表示其反转比特的其下一比特中的某一个。

[0077] 在这里的例子中,选择部41b在从选择部41a接收的比特为“0”时,选择从存储器设备12读出的数据中的MSB侧的比特(信号线d3所输出的逻辑运算结果)进行锁存、输出。另外,该选择部41b在从选择部41a接收的比特为“1”时,选择从存储器设备12读出的数据中的上述信号线d3的下一信号线d4所表示的比特(表示逻辑运算结果的反转比特)进行锁存、输出。

[0078] 选择部41c连接有存储器设备12的数据总线中的MSB侧的d5和作为其下一比特的d6的各信号线。另外,该选择部41c接收选择部41b所输出的1比特的信号。

[0079] 而且,在从时钟供给部25输入的副时钟信号 $\varphi 3$ 上升的定时,选择部41c读出存储器设备12所保存的数据中的在三态缓冲器21所输出的位串所表示的地址中保存的数据并进行锁存。在这里的例子中的选择部41c在从选择部41b接收的比特为“0”时,选择从存储器设备12读出的数据中的MSB侧的比特(信号线d5所输出的逻辑运算结果)进行锁存、输出。另外,该选择部41c在从选择部41b接收的比特为“1”时,选择从存储器设备12读出的数据中的上述信号线d5的下一信号线d6所表示的比特(表示逻辑运算结果的反转比特)进行锁存、输出。

[0080] 并且,选择部41d连接有存储器设备12的数据总线中的MSB侧的d7和作为其下一比特的d8的各信号线。另外,该选择部41d接收选择部41c所输出的1比特的信号。

[0081] 而且,在从时钟供给部25输入的副时钟信号 $\varphi 4$ 上升的定时,选择部41d读出存储器设备12所保存的数据中的在三态缓冲器21所输出的位串所表示的地址中保存的数据并进行锁存。在这里的例子中的选择部41d在从选择部41c接收的比特为“0”时,选择从存储器设备12读出的数据中的MSB侧的比特(信号线d7所输出的逻辑运算结果)进行锁存、输出。另

外,该选择部41c在从选择部41b接收的比特为“1”时,选择从存储器设备12读出的数据中的上述信号线d7的下一信号线d8所表示的比特(表示逻辑运算结果的反转比特)进行锁存、输出。该选择部41d的输出被输出到外部。

[0082] 接着说明本实施方式的该例子所涉及的逻辑运算装置1的动作。在此,例如接收 $M = N \times n$ (存储器设备12的地址总线宽度N的整数n倍)比特长度的数据D(将其第i个比特设为 $b_i$ ( $i = 1, 2, \dots, N \times n$ ))的输入作为逻辑运算、即异或的计算的对象。而且,从MSB侧(或者LSB侧)依次将第i个比特分别输入到第i个三态缓冲器21\_i。

[0083] 而且,逻辑运算装置1如下那样进行动作。在存在选择部41d的输出之后(图6的时刻t0),接着在时钟供给部25所输出的时钟信号CLK以及副时钟信号 $\varphi 1$ 上升的定时(图6的时刻t1),三态缓冲器21\_1~21\_8将被输入的比特b1、b2、……、b8提供给存储器设备12的地址总线。

[0084] 此时,输出单元40的选择部41a读出存储器设备12所保存的数据中的在三态缓冲器21\_1~21\_8所输出的位串所表示的地址中保存的数据。此外,在此,设为从外部向选择部41a输入“0”的信号。选择部41a具备锁存器,该锁存器在副时钟信号 $\varphi 1$ 上升的定时(图6的时刻t1),将从存储器设备12读出的数据中的MSB的比特(经由数据总线的信号线d1输出的数据、即逻辑运算结果)作为运算结果R1进行锁存、输出。该输出R1输出到选择部41b。

[0085] 选择部41b事先接收该输出R1。接着在时钟供给部25所输出的时钟信号CLK和副时钟信号 $\varphi 2$ 上升的定时(图6的时刻t3),三态缓冲器21\_9~21\_16将被输入的比特b9、b10、……、b16提供给存储器设备12的地址总线。

[0086] 而且,选择部41b读出存储器设备12所保存的数据中的在三态缓冲器21\_9~21\_16所输出的位串所表示的地址中保存的数据。而且,选择部41b在从选择部41a输入的比特为“0”时(运算结果R1为“0”时),将从存储器设备12读出的数据中的MSB侧的比特(数据总线上的信号线d3的输出、即逻辑运算结果)作为运算结果R2,而在副时钟信号 $\varphi 2$ 上升的定时(图6的时刻t3)进行锁存、输出。另外,该选择部41b在从选择部41a输入的比特为“1”时(运算结果R1为“1”时),将从存储器设备12读出的数据中的信号线d4的输出(逻辑运算结果的反转比特)作为运算结果R2,而在副时钟信号 $\varphi 2$ 上升的定时(图6的时刻t3)进行锁存、输出。该输出R2被选择部41c接收。

[0087] 以下选择部41c……也同样地进行动作。而且,如果在时钟供给部25所输出的副时钟信号 $\varphi 4$ 上升的定时三态缓冲器21\_25~21\_32将被输入的比特b25、b26、……、b32提供给存储器设备12的地址总线,则选择部41d读出存储器设备12所保存的数据中的在三态缓冲器21\_25~21\_32所输出的位串所表示的地址中保存的数据。

[0088] 而且,选择部41d在从选择部41c输入的比特为“0”时(运算结果R3为“0”时),将从存储器设备12读出的数据中的MSB侧的比特(数据总线上的信号线d7的输出、即逻辑运算结果)作为运算结果R,而在副时钟信号 $\varphi 4$ 上升的定时进行锁存、输出。另外,该选择部41d在从选择部41c输入的比特为“1”时(运算结果R3为“1”时),将从存储器设备12读出的数据中的信号线d8的输出(逻辑运算结果的反转比特)作为运算结果R,而在副时钟信号 $\varphi 4$ 上升的定时进行锁存、输出。

[0089] 这样,在本实施方式的该例子中,输出单元40所包括的各选择部41作为如下单元而发挥功能:在分时地输出均为N比特的位串的定时,使用前次输出的比特来选择性地输出访问存储器设备而取出的比特间的逻辑运算结果及其反转比特中的一方。而且,在第四次中输出单元40将 $8 \times 4 = 32$ 比特长度的数据D所包含的各比特的逻辑运算结果(在这里的例子中为异或)作为运算结果R并进行输出。

[0090] 这样,在本实施方式的该例子中,输出单元40作为如下单元而发挥功能:在分时地输出N比特的位串的定时使用前次输出的比特来选择性地输出访问存储器设备而取出的比特间的逻辑运算结果及其反转比特中的一方。

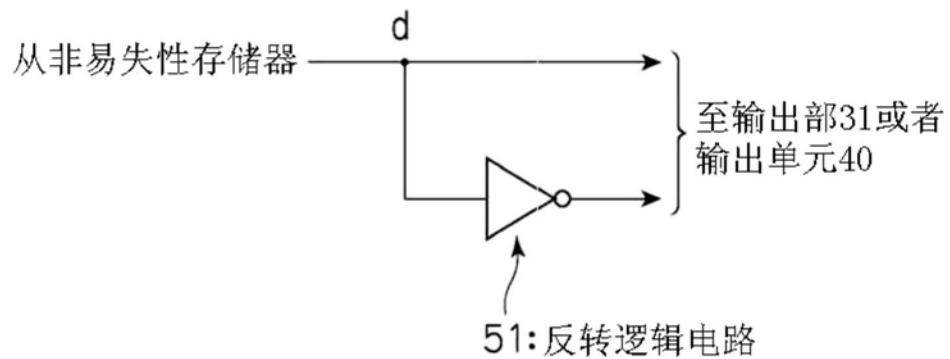

[0091] 并且,在本实施方式的目前为止的说明中,在利用图3所示的查找表的情况下,输出部31或者输出单元40利用前级的输出来对是输出从存储器设备12读出的数据的第奇数个比特还是输出第偶数个比特进行切换。然而,本实施方式并不限于此,例如图9所例示的那样,也可以将反转逻辑(NOT)电路51与从存储器设备12输出的信号线d(输出使用了以输入到存储器设备12的地址表示的位串的逻辑运算结果的信号线),从而获得使用了以输入到存储器设备12的地址表示的位串的逻辑运算结果的反转比特。在这种情况下,输出部31或者输出单元40利用前级的输出选择上述信号线d以及反转逻辑电路51的输出中的某一个(在输出单元40中对其进行锁存)并进行输出。

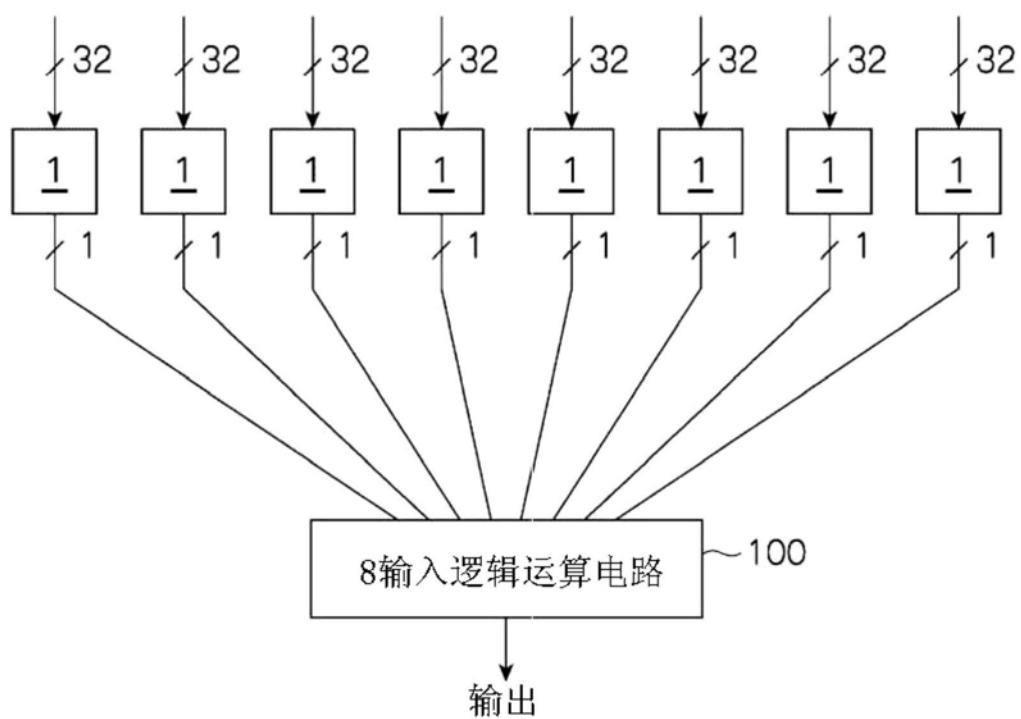

[0092] 并且,如本实施方式的图4、图5或者图7所例示的逻辑运算装置1那样,也可以接收存储器设备的地址总线宽度N的n倍长度(例如如果地址总线宽度为8比特、n=4,则为32比特长度)的位串的输入,当输出其逻辑运算结果1比特时,将这些逻辑运算装置1例如并联地配置8个,将其输出进一步输入到8输入逻辑运算电路,来进行 $N \times n \times 8$ 比特长度的逻辑运算。

[0093] 具体地说,图10示出并联地配置8个图4、图5或者图7所例示的逻辑运算装置1,该逻辑运算装置1接收地址总线宽度为8比特、n=4的32比特长度的位串的输入,并且为了计算作为其逻辑运算结果的异或而设置了存储器设备12内的查找表。

[0094] 在该图10的例子中,将各逻辑运算装置1所输出的1比特的输出分别输入到与图11所例示的电路相同的8输入异或电路100,从而获得该异或的运算结果1比特。根据该电路结构,能够通过较小规模的电路结构来获得 $8 \times 4 \times 8 = 256$ 比特长度的位串所包含的各比特间的异或。

图1

| 地址       | 数据      |

|----------|---------|

| 00000000 | 0xxxxxx |

| 00000001 | 1xxxxxx |

| :        | :       |

| 11111111 | 0xxxxxx |

图2

| 地址       | 数据       |

|----------|----------|

| 00000000 | 01xxxxxx |

| 00000001 | 10xxxxxx |

| :        | :        |

| 11111111 | 01xxxxxx |

图3

图5

图6

图7

| 地址       | 数据       |

|----------|----------|

| 00000000 | 01010101 |

| 00000001 | 10101010 |

| ⋮        | ⋮        |

| 11111111 | 01010101 |

图8

图9

图10

图11