**(19) 대한민국특허청(KR)**

**(12) 특허공보(B1)**

(51) Int. Cl.<sup>4</sup>

G06F 12/08

(45) 공고일자 1989년 12월 04일

(11) 공고번호 특 1989-0004994

---

|           |                |           |                |

|-----------|----------------|-----------|----------------|

| (21) 출원번호 | 특 1984-0008615 | (65) 공개번호 | 특 1985-0004677 |

| (22) 출원일자 | 1984년 12월 28일  | (43) 공개일자 | 1985년 07월 25일  |

---

|            |                                                              |

|------------|--------------------------------------------------------------|

| (30) 우선권주장 | 58-246112 1983년 12월 29일 일본(JP)                               |

| (71) 출원인   | 후지쓰 가부시끼가이샤 야마모토 다꾸마<br>일본국 가나가와쿄 가와자끼시 나가하라구 가미고 다나까 1015반찌 |

|          |                                                                                                                              |

|----------|------------------------------------------------------------------------------------------------------------------------------|

| (72) 발명자 | 도네 히로사다<br>일본국 가나가와쿄 가와자끼시 나가하라구 가미고 다나까 1015반찌 후지쓰 가부시끼가이샤내<br>다나까 쓰또무<br>일본국 가나가와쿄 가와자끼시 나가하라구 가미고 다나까 1015반찌 후지쓰 가부시끼가이샤내 |

| (74) 대리인 | 문기상, 조기호                                                                                                                     |

**심사관 : 고금영 (책자공보 제1705호)**

---

**(54) 어드레스 변환 제어장치**

---

**요약**

내용 없음.

**대표도**

**도1**

**명세서**

[발명의 명칭]

어드레스 변환 제어장치

[도면의 간단한 설명]

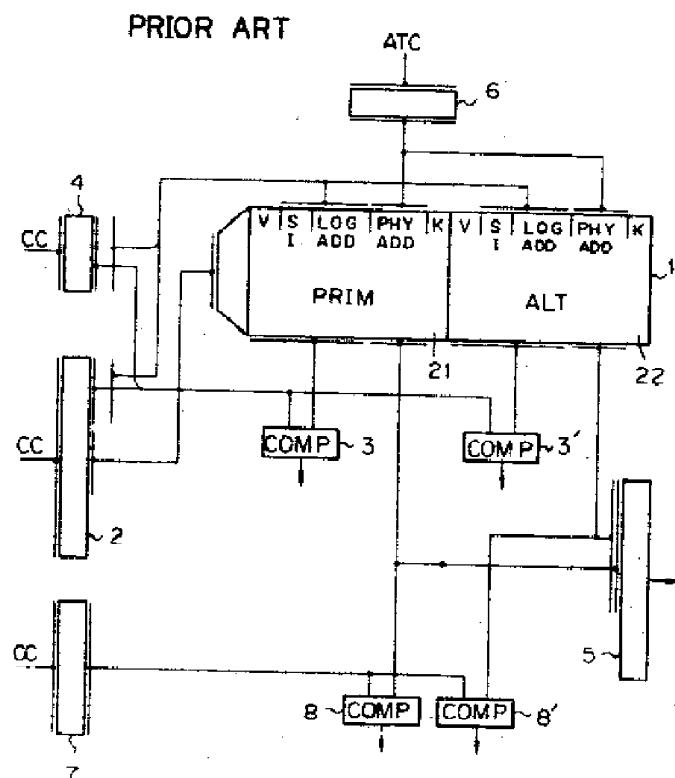

제 1 도는 종래의 어드레스 변환 제어장치를 보이는 계통회로도.

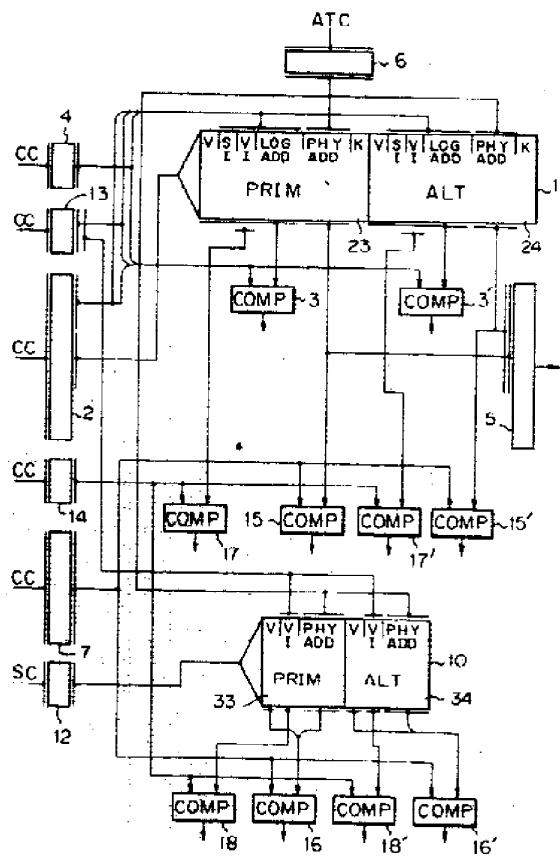

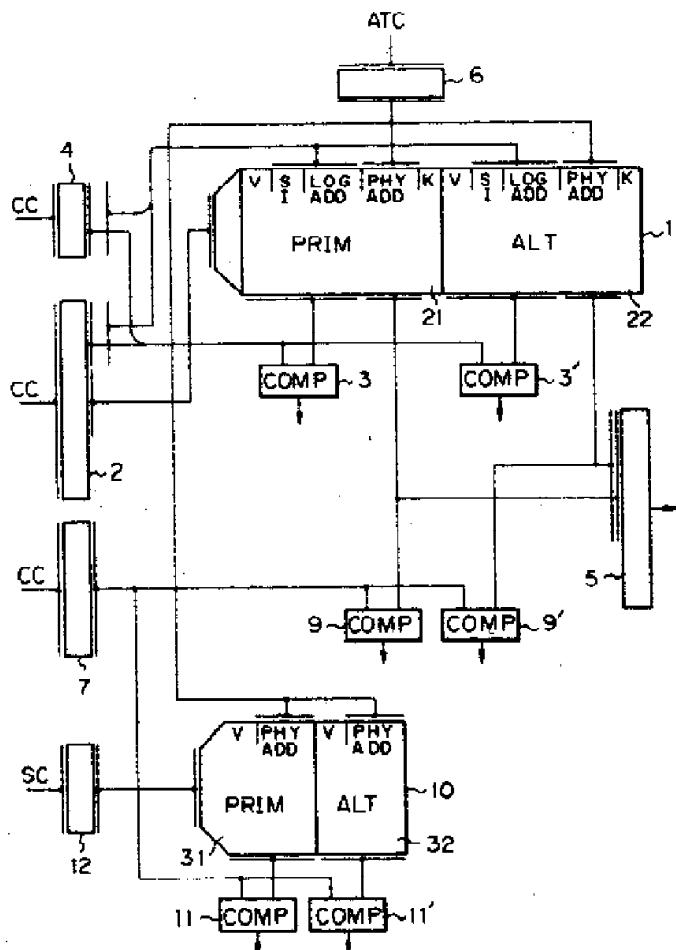

제 2 도는 본 발명의 제 1 실시예에 의한 어드레스 변환 제어장치를 보이는 개통회로도.

제 3 도는 본 발명의 제 2 실시예에 의한 어드레스 변환 제어장치를 보이는 개통회로도.

[발명의 상세한 설명]

본 발명은 어드레스 변환 제어장치(address translation control system)에 관한 것으로, 특히 논리 어드레스(logic address)를 물리 어드레스(physical address)로 고속 변환시켜주는 어드레스 변환 버퍼(buffer)이외에 어드레스 변환 버퍼의 내용의 일부분을 카피(copy)한 메모리 어레이(array)를 구비하여 메모리 어레이를 탐색하여 어드레스 변환 버퍼내에서 일부분을 퍼지(purge)시켜 주는 어드레스 변환 제어장치에 관한 것이다.

가상 기억방식을 채용하고 있는 데이터처리 장치에서는 고속으로 논리 어드레스를 물리 어드레스로 변환시키기 위해 한번 어드레스의 변환된 논리 어드레스와 물리 어드레스의 쌍을 TLB(Translation Lookaside Buffer)이른바, 어드레스 변환 버퍼내에 등록해 놓고, 이 어드레스 변환 버퍼를 억세스하는 것에 의해 고속변환을 행하는 어드레스 변환 제어방식을 쓰고 있다.

어드레스 변환 버퍼는 프라이머리블록(primary block)과 일터네이트블록(alternate block)으로 구성되는데 각 블록은 다수의 엔트리(Entry)들을 갖고 있다.

각 엔트리는 그 엔트리가 유효하다는 것을 나타내는 유효 플래그(flag)와, 다중 가상 기억 공간을 식별하는 다중 가상기억식별 필드(identificatuation field)와, 논리 어드레스 필드와, 물리 어드레스 필드와, 그리고, 기억보호키이(key)필드로 구성된다.

통상의 명령인출(command fetch) 또는 오퍼랜드 억세스(operend access)용 어드레스 변환 버퍼를 갖는 종래의 어드레스 변환 제어장치에서, 상술한 어드레스 변환 버퍼는 변환해야 할 논리 어드레스의 일부 즉, 실행어드레스 레지스터로부터의 억세스 어드레스를 입력시킴으로써 억세스된다.

억세스에 의해 어드레스 변환 버퍼 내의 프라이머리블록과 알터네이트블록내에 기억되어 있는 억세스된 모든 엔트리의 내용이 판독된다.

어드레스 변환 버퍼로부터 판독되는 다중 가상 기억식별과 논리 어드레스의 일부는 다중 가상 기억식별 레지스터로부터의 다중 기억식별과 실행 어드레스 레지스터로부터의 대응하는 논리 어드레스의 다른 부분과 각각 비교된다.

만일, 비교 내용이 일치하면 엔트리의 물리 어드레스는 실행 어드레스 레지스터에, 입력된 논리 어드레스에 대한 물리 어드레스로서 실어드레스 레지스터(real address register)로 보내진다.

가상 기억장치에서는 사용가능 물리 어드레스 보다 더 큰 논리 어드레스가 사용되기 위해 하나의 물리 어드레스가 사용되지 않을 때 물리 어드레스는 차례 차례로 다른 논리 어드레스로 할당된다. 그때에, 만일 주기억장치상의 변환 테이블(translation table)이 갱신될 경우, 갱신이전에 변환된 논리 어드레스와 물리 어드레스의 쌍들이 어드레스 변환 버퍼내에 여전히 남아있을 수 있기 때문에 그 쌍들을 탐색하여 퍼지시켜야만 한다.

이러한 이유 때문에, 종래의 어드레스 변환 제어장치에서는 어드레스 변환 버퍼내의 각 엔트리를 물리 어드레스에 대해 탐색하는 부분 퍼지방법이 자주 사용된다.

이 방법에 의하면 퍼지 해야 할 물리 어드레스가 퍼지 레지스터로 입력되면 실행 어드레스 레지스터 내의 억세스 어드레스를 순차적으로 인크리먼트(increment)해서, 어드레스 변환 버퍼내의 엔트리를 순차적으로 판독하여 퍼지 레지스터내의 물리 어드레스를 어드레스 변환 버퍼내의 물리 어드레스와 비교하고, 만일 비교에 의해 그 어드레스들이 일치할 경우 그 엔트리의 유효 플래그를 무효 즉, 오프로하고 있다.

그러한 종래의 어드레스 변환 제어장치에서는 부분 퍼지를 행할 때 어드레스 변환 버퍼의 모든 내용들을 판독해야 되기 때문에 어드레스 변환 버퍼를 통상의 명령 인출이나 오퍼랜드 억세스시에 사용할 수 없는 결점이 있다.

종래의 어드레스 변환 제어장치에서의 상술한 결점은 어드레스 변환 버퍼의 사용 효율을 저하시키며 특히 파이프라인(pipeline)방법을 사용할 때 성능이 현저히 떨어지는 문제가 있다.

본 발명의 목적은 어드레스 변환 버퍼의 부분 퍼지를 통상의 명령 인출 또는 오퍼랜드 억세스와 별도로 처리할 수 있으며 결국 어드레스 변환 버퍼의 사용 효율을 저하시키지 않고 파이프라인 방법을 사용할 시에 성능을 향상 시킬 수 있는 어드레스 변환 제어장치를 제공하는데 있다.

본 발명의 한 특징에 의하면, 적어도 유효 플래그, 논리 어드레스 필드 및 물리 어드레스 필드를 각각 포함하는 다수의 엔트리들을 갖는 어드레스 변환 버퍼와, 어드레스 변환 버퍼의 내용들 내에 적어도 유효 플래그와 물리 어드레스 필드의 카피들을 갖는 메모리 어레이와, 어드레스 변환 버퍼를 부분적으로 퍼지시키도록 어드레스 변환 버퍼의 내용들의 일부분을 나타내는 정보를 기억시키기 위한 퍼지 레지스터와, 어드레스 변환 버퍼의 내용부분과 퍼지 레지스터의 내용을 비교하기 위한 제 1 비교기 수단과, 퍼지 레지스터의 내용과 메모리 어레이의 내용부분을 비교하기 위한 제 2 비교기를 구비하며, 두 개의 입력된 내용들이 제 1 비교기 수단에서 일치하지 않을 때 상기 어드레스 변환 버퍼에 로의 통상의 억세스를 처리하고, 또한 메모리 어레이의 엔트리가 차례로 억세스되어 두입력된 내용들이 제 2 비교기 수단에서 일치할 때 어드레스 변환 버퍼와 메모리 어레이의 대응하는 엔트리들의 유효 플래그들을 오프시킴에 의해 부분퍼지를 수행하는 것을 특징으로 하는 어드레스 변환 장치를 제공하는데 있다.

본 발명의 다른 특징에 의하면 적어도 유효 플래그, 논리 어드레스 필드, 물리 어드레스 필드 및 가상 계산기 식별 필드를 각각 포함하는 다수의 엔트리들을 갖고 있는 어드레스 변환 버퍼와, 어드레스 변환 버퍼의 내용들 내에 적어도 유효 플래그, 물리 어드레스 필드, 및 가상 계산기 식별 필드를 갖는 메모리 어레이와, 어드레스 변환 버퍼를 부분 퍼지를 행하기 위해 어드레스 변환 버퍼의 내용의 일부를 나타내는 정보를 기억시키기 위한 퍼지 레지스터와, 퍼지 레지스터의 내용과 어드레스 변환 버퍼내의 상기 일부의 내용들을 비교하기 위한 제 1 비교기 수단과, 퍼지 레지스터의 내용과 메모리 어레이내의 상기 일부의 내용을 비교하기 위한 제 2 비교기 수단과, 퍼지해야될 가상 계산기 식별을 측정시키기 위한 퍼지 가상 계산기 식별 레지스터와, 퍼지 가상 계산기 식별 레지스터의 내용들과 어드레스 변환 버퍼내의 가상 계산기 식별 필드의 내용들을 비교하기 위한 제 3 비교기 수단과, 그리고, 퍼지 가상 계산기 식별 레지스터의 내용들과 메모리 어레이 내의 가상 계산기 식별 필드의 내용들을 비교하기 위한 제 4 비교기 수단을 구비하며, 제 1 비교기 수단에서의 일치와 제 3 비교기 수단에서의 일치가 발생하지 않을 때 어드레스 변환 버퍼에로의 통상의 억세스를 처리하고, 또한 메모리 어레이의 엔트리가 차례로 억세스되어 제 2 비교기 수단에서의 일치와 제 4 비교기 수단에서의 일치가 발생할 때 어드레스 변환 버퍼와 메모리 어레이의 대응하는 엔트리의 유효 플래그를 오프시킴에 의해 부분 퍼지를 수행하는 것을 특징으로 하는 어드레스 변환 제어장치가 제공된다.

본 발명의 실시예들을 설명하기 전에, 종래의 어드레스 변환 제어장치를 제 1 도를 참조하여 보충 설명하고 또한 본 발명의 실시예들과 비교 설명한다.

제 1 도의 장치에서, 통상의 명령 인출 또는 오퍼랜드 억세스용 어드레스 변환 버퍼 1은 변환해야 할 논리 어드레스 즉, 실행 어드레스 레지스터 2로부터의 억세스 어드레스의 일부를 입력시킴으로써 억세스된다.

이러한 억세스에 의해 어드레스 변환 버퍼 1내의 프라이머리블록(PRIM) 21과 알터네이트블록(ALT) 22내에 기억되어 있는 억세스된 모든 엔트리의 내용들이 판독된다.

어드레스 변환 버퍼 1로부터 판독된 각 엔트리내의 다중 가상 기억식별과 부분 논리 어드레스는 다중 가상 기억식별 레지스터 4로부터의 다중 가상 기억식별과 그리고 실행 어드레스 레지스터 2로부터의 대응하는 부분 논리 어드레스와를 프라이머리 블록 21에 대해서는 비교기 3에서 그리고 알터네이

트블록 22에 대해서는 비교기 3'에서 각각 비교된다. 만일, 비교 내용들이 일치할 경우, 엔트리의 물리 어드레스는 실 어드레스 레지스터 5로 보내진다.

실행 어드레스 레지스터 2로부터의 논리 어드레스가 어드레스 변환 버퍼 1내에 기억되지 않을 때 물리 어드레스는 주기억장치내의 변환 테이블을 사용하여 어드레스 변환 수단에 의해 얻어진다.

그 얻어진 물리 어드레스는 등록 레지스터 6으로 보내져 논리 어드레스등의 일부로서 어드레스 변환 버퍼 1내에 등록된다.

가상 기억장치에서는 논리 어드레스가 물리 어드레스보다 더 넓은 사용 범위를 확보하기 위해 물리 어드레스가 사용되지 않을 때 물리 어드레스를 차례 차례로 다른 논리 어드레스에 할당한다. 그때에, 만일, 주기억장치내의 변환 테이블의 갱신될 경우, 갱신되기 이전에 변환해야 할 논리 어드레스와 물리 어드레스의 쌍들은 탐색된 다음 퍼지되어야만 한다.

이러한 이유 때문에 제 1 도에 보인 바와같은 종래의 어드레스 변환 제어장치에서는 어드레스 변환 버퍼 1 내의 각 엔트리를 물리 어드레스에 대해 탐색하는 부분 퍼지 방법이 자주 사용된다.

이 방법에 의하면 퍼지해야 할 물리 어드레스가 퍼지 레지스터 7에 입력될 때 실행 어드레스 레지스터 2내의 억세스 어드레스를 순차적으로 인크리 멘트해서 어드레스 변환 버퍼 1내의 엔트리를 순차적으로 판독하여 퍼지 레지스터 7내의 물리 어드레스를 어드레스 변환 버퍼 1내의 물리 어드레스와 프라이머리 블록 21에 대해 비교기 8에서 그리고 알터네이트블록 22에 대해 비교기 8'에서 각각 비교한다.

만일, 비교기들에서 일치가 얻어지면, 대응하는 엔트리의 유효 플래그를 무효 즉 오프한다. 부분 퍼지가 수행될 때 그러한 종래의 어드레스 변환 제어장치에서는 어드레스 변환 버퍼 1의 모든 내용을 판독해야 되기 때문에 부분퍼지 기간동안 어드레스 변환 버퍼 1을 사용하여 통상의 명령 인출 오퍼랜드 억세스를 수행할 수 없는 결점이 있다.

한편, 비교기 3 또는 3'에서 일치가 얻어질 때 조차 기억된 물리 어드레스를 사용할 수 없다. 즉, 물리 어드레스가 퍼지 레지스터 7내에 세트된 물리 어드레스와 일치할 때 그 결과는 상술한 바와같다. 왜냐하면, 이 경우에, 나머지 물리 어드레스들은 어드레스 변환 버퍼 1내에 여전히 퍼지되지 않고 남아 있기 때문이다. 이제 제 2 도를 참조하여 본 발명의 제 1 실시예를 설명한다. 제 2 도에서 어드레스 변환 버퍼 1, 실행 어드레스 레지스터 2, 비교기 3과 3', 다중 가상 기억식별 레지스터 4, 실어드레스 레지스터 5, 등록 레지스터 6, 그리고 퍼지 레지스터 7은 제 1 도의 종래 장치에서와 동일한 것 들이다. 그러므로, 동일 소자에 대해서는 이후 동일 표시번호를 붙인다.

제 1 실시예의 어드레스 변환 제어장치는 상술한 소자들 이외에도, 어드레스 변환 버퍼 1내에 기억된 물리 어드레스와 퍼지 레지스터 7내에 세트된 물리 어드레스를 비교하기 위해 어드레스 변환 버퍼 1내의 프라이머리 블록 21에 대한 비교기 9와 알터네이트블록 22에 대한 비교기 9'로 구성되는 제 1 비교기 수단과, 어드레스 변환 버퍼 1내에 유효 플래그(V)와 물리 어드레스(PHY ADD)의 카피들을 기억하기 위한 메모리 어레이 10과, 퍼지 레지스터 7내에 세트된 물리 어드레스와 메모리 어레이 10내에 기억된 물리 어드레스를 비교하기 위해 프라이머리블록 31에 대한 비교기 11과 알터네이트블록 32에 대한 비교기 11'로 구성되는 제 2 비교기 수단과, 그리고 메모리 어레이 10을 억세스시키기 위한 억세스 어드레스 레지스터 12를 포함한다. 메모리 어레이 10은 등록레지스터 6에 연결된다.

제 1 실시예의 장치의 동작을 설명하면 다음과 같다. 통상의 명령 인출 또는 오퍼랜드 액세스를 위해 어드레스 변환 버퍼 1은 변화해야 할 논리 어드레스 즉, 실행 어드레스 레지스터 2로부터의 억세스 어드레스의 일부분을 입력하는 것에 의해 수행된다.

이 억세스에 의해 프라이머리블록 21과 알터네이트블록 22내에 내포된 모든 엔트리의 내용들이 판독된 바, 판독된 엔트리로부터의 논리 어드레스들의 부분들 및 다중 가상 기억식별들은 다중 가상 기억식별 레지스터 4로부터의 다중 가상 기억식별 및 실행 어드레스 레지스터 2로부터의 논리 어드레스의 일부분과 비교기들 3과 3'에 의해 각각 비교된다. 또한, 판독된 엔트리의 물리 어드레스들은 비교기들 9와 9'를 사용하여 퍼지 레지스터 7에 세트된 물리 어드레스와 비교된다.

프라이머리블록 21과 비교기 30이나 또는 알터네이트블록 22과 비교기 3' 중 어느 하나에서 일치가 얻어지지 않을 때 어드레스 변환은 주기억장치내에 기억된 어드레스 변환테이블을 사용하여 어드레스 변환수단(도시 않됨)에 의해 수행된다. 그 결과로 얻어진 물리 어드레스는 등록 레지스터 6에 세트되며, 그 다음 유효 플래그(V), 다중 가상 기억식별(SI), 논리 어드레스(LOG ADD), 물리 어드레스(PHY ADD), 그리고 기억 보호키(K)가 어드레스 변환 버퍼 1내에 등록된다.

상술한 유효 플래그 등이 기억되는 어드레스 변환 버퍼 1내의 어드레스는 억세스 어드레스 레지스터 12내에 역시 세트된다.

어드레스 변환 버퍼 1내에 등록된 유효 플래그(V)와 물리 어드레스(PHY ADD)의 카피들은 억세스 어드레스 레지스터 12로부터 억세스된 메모리 어레이 10의 어드레스에 기억된다. 그 다음, 다음의 명령 인출 또는 오퍼랜드 억세스의 어드레스가 다시 실행 어드레스 레지스터 2내에 세트되어 어드레스 변환 버퍼 1을 억세스 한다.

비교 입력들의 일치가 비교기 3 또는 3' 중 어느 하나에서 얻어질 때, 만일 판독된 엔트리로부터의 물리적인 어드레스들 중 적어도 하나가 비교기들 9와 9'를 사용하여 퍼지 레지스터 7에 세트된 물리 어드레스와 일치하면, 부분퍼지 동작이 완료되지 않아 퍼지 해야 할 물리 어드레스가 어드레스 변환 버퍼 1내에 그대로 남아있다.

그러므로, 물리 어드레스는 사용될 수 없다. 이 경우에, 명령인출 또는 오퍼랜드 억세스는 그의 변환을 금지하도록 제어된다. 따라서, 만일 비교기 9 또는 9'에서 일치가 아닐 경우, 통상 억세스가 허용되어 부분 퍼지의 완료를 기다리지 않고 어드레스 변환 버퍼 1을 사용할 수 있다.

만일, 비교기 3 또는 3'에서 일치일 경우, 판독된 엔트리의 물리 어드레스가 비교기 9와 9'를 사용하여 퍼지 레지스터 7내에 세트된 물리 어드레스와 일치하지 않으면 판독된 엔트리의 물리 어드레스는 실어드레스 레지스터 5로 보내진다. 그러면, 물리 어드레스는 예를 들어 버퍼 기억장치 또는 버퍼 주기억장치용 억세스 어드레스로 사용된다.

부분 퍼지가 수행되는 동작에 대해 아래에 설명하면 다음과 같다. 퍼지해야 할 물리 어드레스가 퍼지 레지스터 7내에 세트될 때 억세스 어드레스 레지스터 12내의 억세스 어드레스는 순차적으로 인크리먼트되어 메모리 어레이 10의 엔트리를 차례로 억세스된다.

각 엔트리의 억세스시에 물리 어드레스는 비교기 11과 11'를 사용하여 퍼지 레지스터 7내의 물리 어드레스와 비교된다. 만일, 비교기들에서 일치일 경우 억세스된 어드레스는 입력으로서 억세스 어드레스 레지스터 12로 다시 입력된다. 그와 동시에, 억세스된 어드레스는 실행 어드레스 레지스터 2에 역시 세트된다. 그러면, 어드레스 변환 버퍼 1 및 메모리 어레이 10의 해당 엔트리를 억세스하여 유효 플래그들은 오프한다. 메모리 어레이 10의 모든 엔티리들이 억세스 어드레스 레지스터 12에 의해 탐색된 후 부분 퍼지 동작은 끝나고 퍼레지스터 7은 텅빈 상태가 된다.

상술한 바와 같이, 부분 퍼지는 메모리 어레이 10을 사용하여 수행되므로 어드레스 변환 버퍼 1에 대한 통상의 명령인출이나 오퍼랜드액세스 동작은 부분 퍼지 동작과 별개로 동작할 수 있다. 따라서 부분 퍼지 동작에 의해 어드레스 변환 버퍼 1을 사용하는 통상의 억세스가 제한되지 않는다.

비교기 9 또는 9'에서 일치가 검출되지 않는 한 어드레스 변환 버퍼 1로부터의 물리 어드레스는 유효하게 사용될 수 있다.

제 3 도는 본 발명의 제 2 실시예에 의한 가상 계산기에 사용된 어드레스 변환 제어장치의 개통 회로도이다. 가상 계산기는 다수의 동작시스템들과 이 동작시스템들을 하나의 실계산기 상에서 동시에 동작시키기 위한 관리 프로그램에 의해 구성되어 있다. 관리 프로그램은 다수의 동작시스템들에 가상 계산기 식별(VI)을 추가시켜 주기억장치상에 할당시키고 있다.

가상 계산기 식별은 어드레스 변환 버퍼 1의 엔트리내에 등록되어 있기 때문에, 한번 등록된 가상 계산기 식별은 만일 어떤 가상 계산기를 더 이상 동작시킬 필요가 없어졌거나 혹은 주기억장치의 용량으로 인해 가상계산기 식별을 다른 가상 계산기로 할당할 경우 부분적으로 퍼지되어야만 한다.

이러한 경우에, 제 1 실시예에서와 같이 그 장치는 메모리 어레이를 포함하며, 메모리 어레이를 사용하여 부분퍼지를 수행한다.

제 3 도에서, 제 2 도의 소자와 동일한 소자에 대해서는 동일 표시번호를 붙인다. 또한, 가상 계산기 식별은 프라이머리블록(PRIM)23과 알터네이트블록(ALT)24를 포함하는 어드레스변환 버퍼 1내에 등록된다.

프라이머리블록(PRIM)33과 알터네이트블록(ALT)34를 포함하는 메모리 어레이 10내에는 어드레스 변환버퍼 1의 내용들의 유효 플래그(V), 가상 계산기 식별(VI), 그리고, 물리 어드레스(PHYADD)의 카피들이 기억된다.

본 실시예의 장치는 가상 계산기 식별 레지스터 13, 부분적으로 퍼지해야 할 가상 계산기 식별을 세트시키기 위한 퍼지 가상 계산기 식별 레지스터 14, 비교기 15와 15'를 포함하는 제 1 비교기 수단, 비교기를 16과 16'를 포함하는 제 2 비교기수단, 그리고 비교기 17과 17'를 포함하는 제 3 비교기수단, 비교기 18과 18'를 포함하는 제 4 비교기수단을 더 구비한다. 가상 계산기 식별 레지스터 13은 메모리 어레이 10에 연결된다.

비교기 3과 3'에서는 어드레스 변환 버퍼 1의 각 엔트리의 다중 가상기억식별(SI)과 가상 계산기 식별(VI)과, 그리고 논리 어드레스(LOG ADD)가 다중 가상기억식별 레지스터 4로 부터의 다중 가상기억식별과, 가상 계산기 식별 레지스터 13으로부터의 가상 계산기 식별과 그리고, 실행 어드레스 레지스터 2로부터의 놀리 어드레스와 제각기 비교된다.

비교기 15와 15'에서는 어드레스 변환 버퍼 1내의 엔트리의 물리 어드레스는 퍼지 레지스터 7로부터의 물리 어드레스와 비교된다. 비교기 17과 17'에서는 어드레스 변환 버퍼 1로부터의 가상 계산기 식별들이 퍼지 가상 계산기 식별 레지스터 14의 내용과 비교된다. 비교기 16과 16'에서는 메모리 어레이 10으로부터의 물리 어드레스들이 퍼지 레지스터 7로부터의 물리 어드레스와 비교된다.

퍼지 레지스터 7로부터의 물리 어드레스와 비교된다.

비교기 18과 18'에서는 메모리 어레이 10으로부터의 가상 계산기 식별이 퍼지 가상 계산기 식별 레지스터 14의 내용들과 비교된다.

본 실시예의 동작은 제 2 도의 실시예와 근본적으로 동일하다. 부분 퍼지는 가상 계산기 식별을 사용해서 수행될 수 있다.

그 밖에, 입력장치들을 나타내는 표시문자 들은 다음과 같다.

ATC(어드레스 변환회로 : address translation circuit), CC(명령제어장치 : command control unit) 그리고, SC(기억 제어장치 : storage control unit)이다.

실어드레스 레지스터 5의 출력은 억세스 어드레스로서 주기억장치에 입력된다. 비교기들의 출력은 상술한 바와같은 장치를 제어하기 위한 제어신호로서 사용된다.

### (57) 청구의 범위

청구항 1

적어도 유효 플래그(V), 논리 어드레스 필드(LOG ADD) 및 물리 어드레스 필드(PHY ADD)를 각각 포함하는 다수의 엔트리들을 갖는 어드레스 변환 버퍼(1)와, 상기 어드레스변환 버퍼를 부분적으로 퍼지시키도록 상기 어드레스 변환 버퍼(1)의 내용들의 일부분을 나타내는 정보를 기억시키기 위한 퍼지레지스터(7)와, 그리고 상기 퍼지 레지스터의 내용과 상기 어드레스 변환 버퍼의 내용부분을 비교하기 위한 제 1 비교기수단(9, 9')을 포함하는 어드레스 변환 제어장치에서, 상기 어드레스 변환 버퍼(1)의 내용들의 적어도 상기 유효 플래그와 상기 물리 어드레스 필드의 카피들을 갖는 메모리 어레이(10)와 상기 퍼지 레지스터의 내용과 상기 메모리 어레이(10)의 내용부분을 비교하기 위한 제 2 비교기 수단(11, 11')을 구비하며, 두 입력된 내용들이 상기 제 1 비교기수단(9, 9')에서 일치하지 않을때 상기 어드레스 변환 버퍼(1)로부터 판독되는 해당 물리 어드레스를 사용하여, 상기 메모리 어레이(10)의 엔트리가 차례로 억세스되어 두 입력된 내용들이 상기 제 2 비교기수단(11, 11')에서 일치할때 부분 퍼지는 상기 어드레스 변환 버퍼(1)와 상기 메모리 어레이(10)의 해당 엔트리들의 상기 유효 플래그들을 오프시킹에 의해 수행되는 것이 특징인 어드레스 변환 제어장치.

## 청구항 2

적어도 유효 플래그(V), 논리 어드레스 필드(LOG ADD) 및 가상 계산기 식별 필드(VI)를 각각 포함하는 다수의 엔트리를 갖는 어드레스 변환 버퍼(1)와 상기 어드레스 변환 버퍼를 부분적으로 퍼지시키도록 상기 어드레스 변환 버퍼의 내용의 일부를 나타내는 정보를 기억시키기 위한 퍼지 레지스터(7)와, 그리고 상기 퍼지 레지스터의 내용과 상기 어드레스 변환 버퍼상의 상기 일부의 내용과 비교하기 위한 제 1 비교기 수단(15, 15')을 포함하는 어드레스 변환 제어장치에서 상기 어드레스 변환 버퍼의 내용들의 적어도 상기 유효 플래그, 상기 물리 어드레스 및 상기 가상 계산기 식별 필드의 카피들을 갖는 메모리 어레이(10)와 상기 퍼지 레지스터의 내용과 상기 메모리 어레이상의 상기 일부의 내용을 비교하기 위한 제 2 비교기수단(16, 16')과, 퍼지해야 할 가상 계산기 식별을 기억시키기 위한 퍼지 가상 계산기 식별 레지스터(14)와, 상기 퍼지 가상 계산기 식별 레지스터의 내용과 상기 어드레스 변환 버퍼(1)상의 가상 계산기 식별 필드(VI)의 내용들을 비교하기 위한 제 3 비교기수단(17, 17')과, 그리고, 상기 퍼지 가상 계산기 식별 레지스터의 내용과 상기 메모리 어레이 상의 상기 가상 계산기 식별 필드의 내용을 비교하기 위한 제 4 비교기 수단(18, 18')을 구비하며, 상기 제 1 비교기 수단(15, 15') 또는 제 3 비교기수단(17, 17')에서 일치가 발생하지 않을때, 상기 어드레스 변환 버퍼(1)로부터 판독된 해당 물리 어드레스를 사용하여, 그리고 상기 메모리 어레이(10)의 엔트리가 차례로 억세스되어 상기 제 2 비교기 수단(16, 16') 또는 제 4 비교기 수단(18, 18')에서 일치가 발생할때 상기 어드레스 변환 버퍼(1)와 상기 메모리 어레이(10)의 해당 엔트리의 상기 유효 플래그들을 오프시킹에 의해 부분페이지가 수행되는 것이 특징인 어드레스 변환 제어장치.

## 도면

### 도면1

도면2

도면3