(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5466818号

(P5466818)

(45) 発行日 平成26年4月9日(2014.4.9)

(24) 登録日 平成26年1月31日(2014.1.31)

(51) Int.Cl.

F 1

|              |           |            |      |

|--------------|-----------|------------|------|

| HO1L 21/336  | (2006.01) | HO1L 29/78 | 301X |

| HO1L 29/78   | (2006.01) | HO1L 29/78 | 653B |

| HO1L 21/8242 | (2006.01) | HO1L 29/78 | 652S |

| HO1L 27/108  | (2006.01) | HO1L 29/78 | 652Q |

| HO1L 29/423  | (2006.01) | HO1L 27/10 | 671A |

請求項の数 5 (全 14 頁) 最終頁に続く

(21) 出願番号

特願2007-251130 (P2007-251130)

(22) 出願日

平成19年9月27日 (2007.9.27)

(65) 公開番号

特開2009-81377 (P2009-81377A)

(43) 公開日

平成21年4月16日 (2009.4.16)

審査請求日

平成22年8月10日 (2010.8.10)

(73) 特許権者 513192281

ピースフォー ルクスコ エスエイアールエル

P S 4 L u x c o S. a. r. l.

ルクセントルク大公国エル-2121、ル

クセントルク、ヴァル デ ポン マラテ

ス208

(74) 代理人 100123788

弁理士 宮崎 昭夫

(74) 代理人 100106138

弁理士 石橋 政幸

(74) 代理人 100127454

弁理士 緒方 雅昭

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の導電型のゲート電極を共有した複数の縦型MOSトランジスタを有する半導体装置であって、

該複数の縦型MOSトランジスタが、側面周囲に形成された第1のゲート絶縁膜を介して前記ゲート電極と側面周囲で対峙して成る第1の半導体柱を有し、

前記半導体装置は、第1の導電型であり、側面周囲に形成された第2のゲート絶縁膜を介して前記ゲート電極と側面周囲で対峙して成り、少なくとも一部分の前記第2のゲート絶縁膜を除去した部分で前記ゲート電極と接している第2の半導体柱を有し、

前記複数の縦型MOSトランジスタの共有されるゲート電極への電位供給が、前記第2の半導体柱を介して行われることを特徴とする半導体装置。

## 【請求項 2】

請求項1に記載の半導体装置において、前記複数の縦型MOSトランジスタの共有されるゲート電極への電位供給が、前記第2の半導体柱上にコンタクトされた電極・配線により行われていることを特徴とする半導体装置。

## 【請求項 3】

請求項1に記載の半導体装置において、前記複数の縦型MOSトランジスタの共有されるゲート電極への電位供給が、前記第2の半導体柱下に形成された第1の導電型の拡散層にコンタクトされた電極・配線により行われていることを特徴とする半導体装置。

## 【請求項 4】

10

20

請求項 1 に記載の半導体装置において、前記複数の縦型MOSトランジスタの共有されるゲート電極への電位供給が、前記第2の半導体柱下に形成された第1の導電型の拡散層を共有した縦型MOSトランジスタを動作させることにより行われていることを特徴とする半導体装置。

**【請求項 5】**

前記半導体装置は、第1の導電型のゲート電極を共有した複数の縦型MOSトランジスタからなるトランジスタ列が複数配置され、アレイ状に形成された半導体装置であって、各トランジスタ列と交差する行方向に、各トランジスタ列の一つのトランジスタ同士が、前記第1の半導体柱下に形成された第1の導電型の拡散層で接続され、各行方向でトランジスタ下にビットラインを構成していることを特徴する請求項 1 乃至 4 のいずれか 1 項に記載の半導体装置。

10

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、縦型MOSトランジスタのゲート電極への電源供給に関し、特に、ゲート電極を共有した複数の縦型MOSトランジスタのゲート電極への電源供給に適した構造を有する半導体装置に関する。

**【背景技術】**

**【0002】**

従来の3次元トランジスタ、即ち縦型MOSトランジスタは、特許文献1記載のFig. 2に示すように、ソース・ドレイン拡散層とチャネルを形成するSi柱において、チャネル部はゲート絶縁膜およびゲート電極に囲まれた構造であり、また、ソース・ドレイン拡散層はシリコン柱全体に形成してチャネル部を完全に覆う構造である。

20

**【0003】**

又、特許文献2には、シリコン基板の表面に格子状に形成された溝により規定された複数のシリコン柱を有し、このシリコン柱の側面に選択トランジスタが形成され、溝底にトランジスタのソース又はドレイン拡散層を有し、このトランジスタを1トランジスタ-1キャパシタ型のDRAMメモリセルの選択トランジスタとした半導体記憶装置であって、溝底拡散層は、多数のメモリセルに共通の一定電圧に接続されている。又、シリコン柱の一側面にゲート絶縁膜を介して接するように形成されたゲート電極を連続して接続し、ワード線とすることが開示されている。

30

**【特許文献1】米国特許U.S.2004/262681A1**

**【特許文献2】特開2002-94027号公報**

**【発明の開示】**

**【発明が解決しようとする課題】**

**【0004】**

上記特許文献1の縦型MOSトランジスタにおいて、ゲート電極への電位供給の構造については明確な記載がない。また、ゲート電極を共有した複数の縦型MOSトランジスタのゲート電極への電源供給の構造についても開示されていない。

**【0005】**

40

通常は、ゲート電極材のいずれかの位置において、コンタクトを形成して電位供給を行うものと考えられる。しかしながら、微細な縦型MOSトランジスタが密集するアレイ部分において、ゲート電極材へ直接コンタクトを形成することは容易ではない。又、コンタクトが形成できたとしても、コンタクト位置が制限され、設計の自由度が制限されるという問題もある。

**【0006】**

特許文献2では、シリコン柱の一側面にしかチャネルが形成されないため、チャネル周囲をゲート電極で覆って完全空乏化した特許文献1に記載の縦型MOSトランジスタと比較して、サブスレッショルド特性に劣るという問題がある。

**【0007】**

50

そこで、本発明の目的は、縦型MOSトランジスタが密集するアレイ部において、設計自由度の高いゲート電極への電位供給手段を有した半導体装置を提供することにある。

**【課題を解決するための手段】**

**【0008】**

上記従来の問題点を解決するために、本発明では、以下の特徴を持つ半導体装置を提供する。

**【0009】**

第1の導電型のゲート電極を共有した複数の角柱縦型MOSトランジスタを有する半導体装置であって、角柱縦型MOSトランジスタが第1の角柱の周りに形成されたゲート絶縁膜を介して前記ゲート電極と対峙して成り、該ゲート電極への電位供給が、前記第1の角柱と同時に形成され、かつ、ゲート電極の導電型と同じ第1の導電型であり、少なくとも一部分のゲート絶縁膜を除去した部分で前記ゲート電極に接している第2の柱を介して行われることを特徴とする半導体装置とする。10

**【0010】**

また、上記の半導体装置において、ゲート電極への電位供給が、第2の柱上にコンタクトされた電極・配線により行われている半導体装置とする。

**【0011】**

さらに、上記の半導体装置において、ゲート電極への電位供給が、第2の柱下に形成された第1の導電型の拡散層にコンタクトされた電極・配線により行われている半導体装置とする。20

**【0012】**

さらに、上記の半導体装置において、ゲート電極への電位供給が、第2の柱下に形成された第1の導電型の拡散層を共有した縦型MOSトランジスタを動作させることにより行われている半導体装置とする。

**【0013】**

加えて、前記半導体装置は、第1の導電型のゲート電極を共有した複数の角柱縦型MOSトランジスタからなるトランジスタ列が複数配置され、アレイ状に形成された半導体装置であって、各トランジスタ列と交差する行方向に、各トランジスタ列の一つのトランジスタ同士が、第1の角柱下に形成された第1の導電型の拡散層で接続され、各行方向でトランジスタ下にピットラインを構成していることを特徴する。30

**【発明の効果】**

**【0014】**

ゲート電極を共有した複数の角柱縦型MOSトランジスタによりアレイ部を構成する場合、角柱縦型MOSトランジスタのゲート電極への電位供給をアレイ部周辺において自由に構成できるので、設計の自由度が増える。

**【発明を実施するための最良の形態】**

**【0015】**

**〔第1の実施例の構成〕**

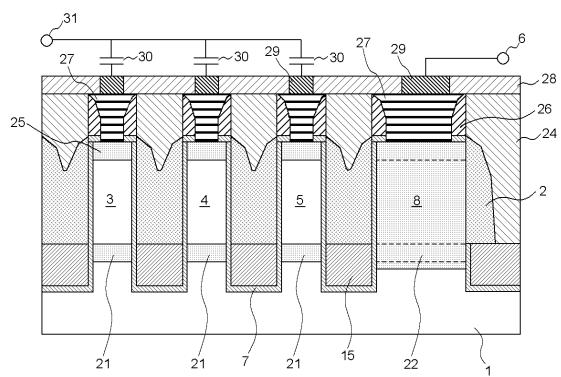

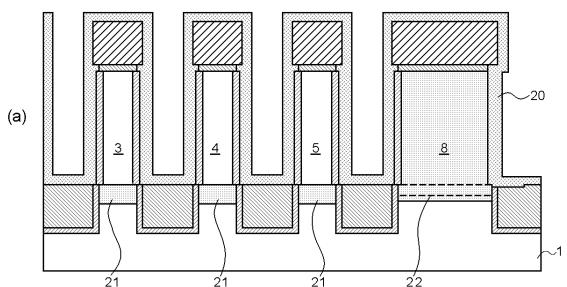

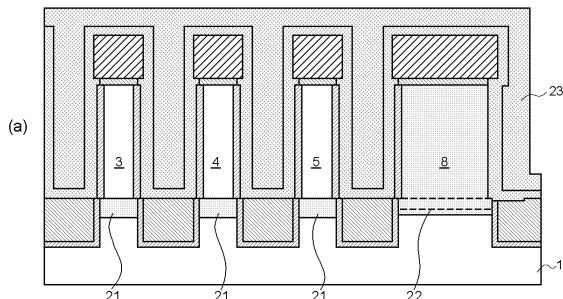

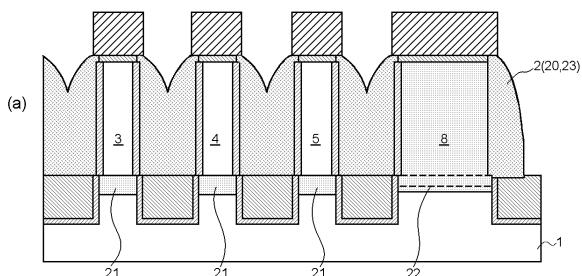

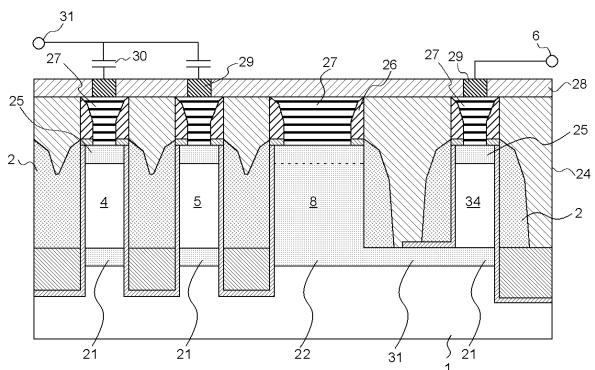

図1に示すように、シリコン基板1の主表面に形成された第1の導電型のゲート電極2を共有した複数の角柱縦型MOSトランジスタ3, 4, 5のゲート電極2の電位供給6が、角柱縦型MOSトランジスタの第1の角柱3, 4, 5と同時に形成され、かつ、一部分にゲート絶縁膜7を有しない、かつ、ゲート電極2の導電型と同じ第1の導電型である第2の柱8の拡散層22を介して行われていて、ゲート電極2への電位供給が、第2の柱8上にコンタクトされた電極・配線6により行なう構造とする。40

**【0016】**

**〔第1の実施例の製法〕**

第1の実施例の製法は、以下の通りである。

**【0017】**

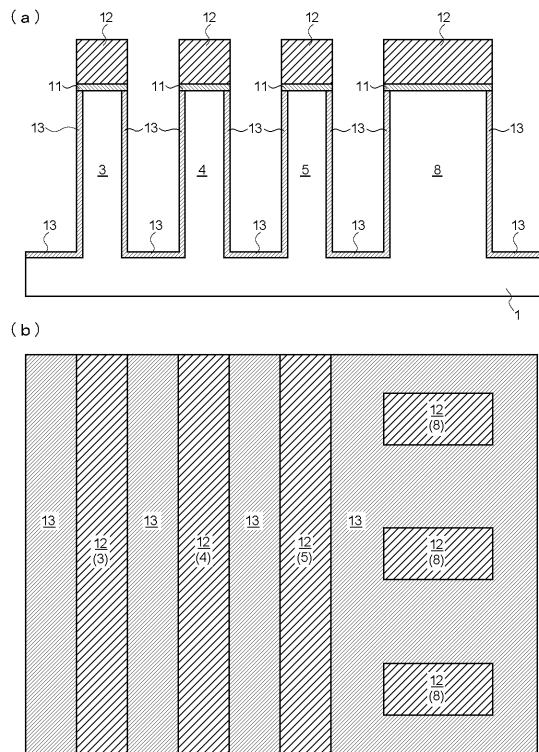

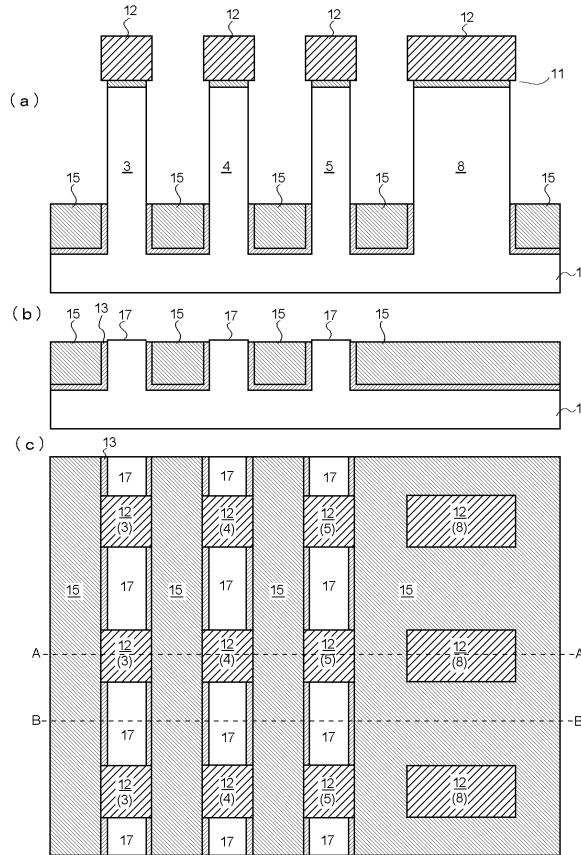

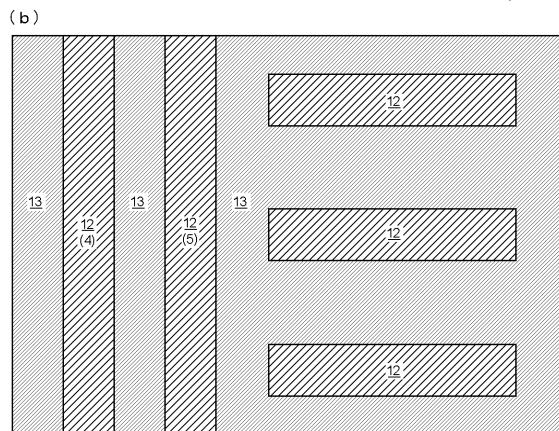

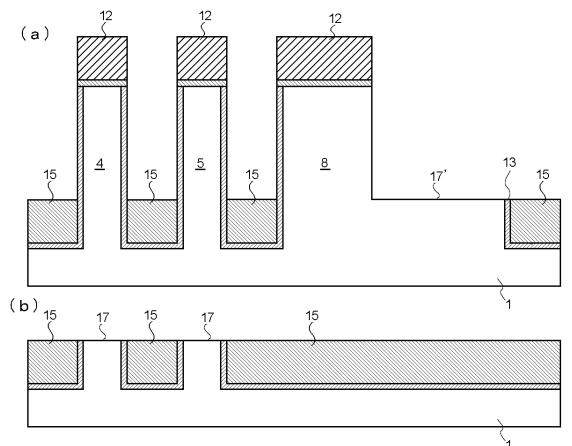

図2(a)の断面図に示したように、シリコン基板1の表面から深さ500nmの部分までボロンを $3 \times 10^{17} / \text{cm}^3$ の濃度となるようにドーピングした後、シリコン基板1表50

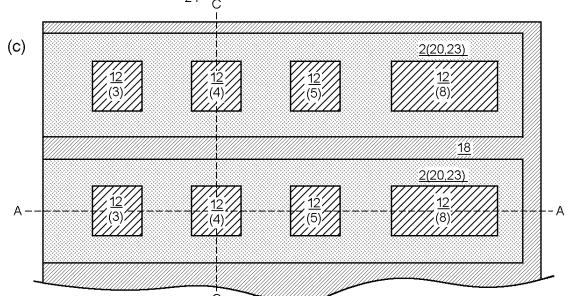

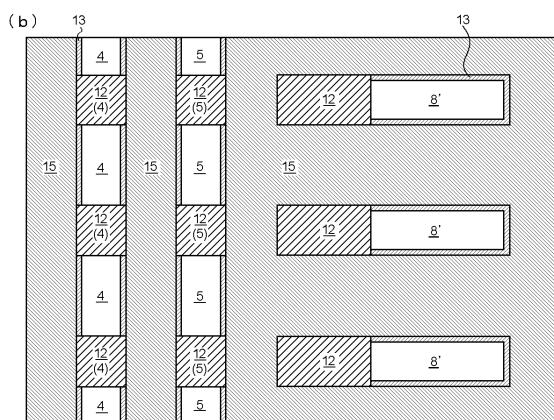

面に 5 nm のシリコン酸化膜 11 と 100 nm のシリコン窒化膜 12 から成るエッチングマスクを形成し、ドライエッティングによりシリコン基板 1 を加工してシリコン柱 3, 4, 5, 8 を形成した。柱の高さは、150 nm とした。なお、ここで、図 2 (b) の平面図に示したように、シリコン柱 3, 4, 5 はライン状に形成され、シリコン柱 8 は矩形状に形成される。その後、シリコン露出面を熱酸化して 5 nm のシリコン酸化膜 13 を形成した。

#### 【0018】

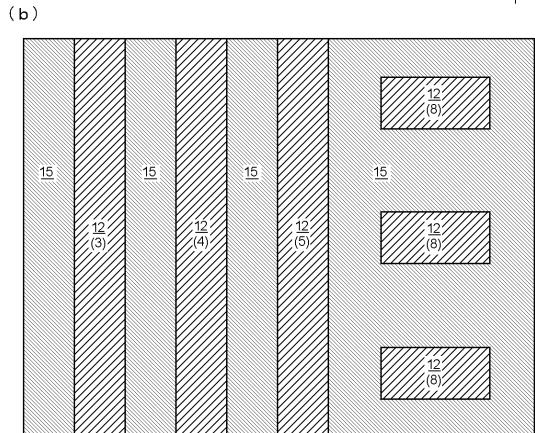

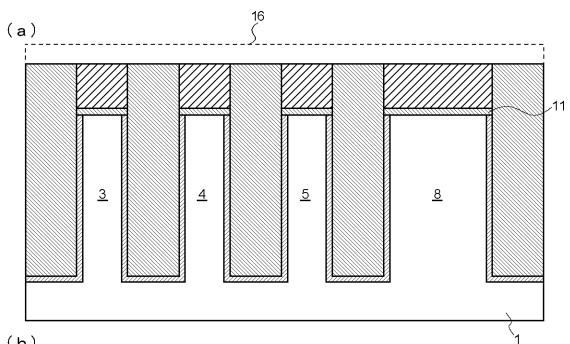

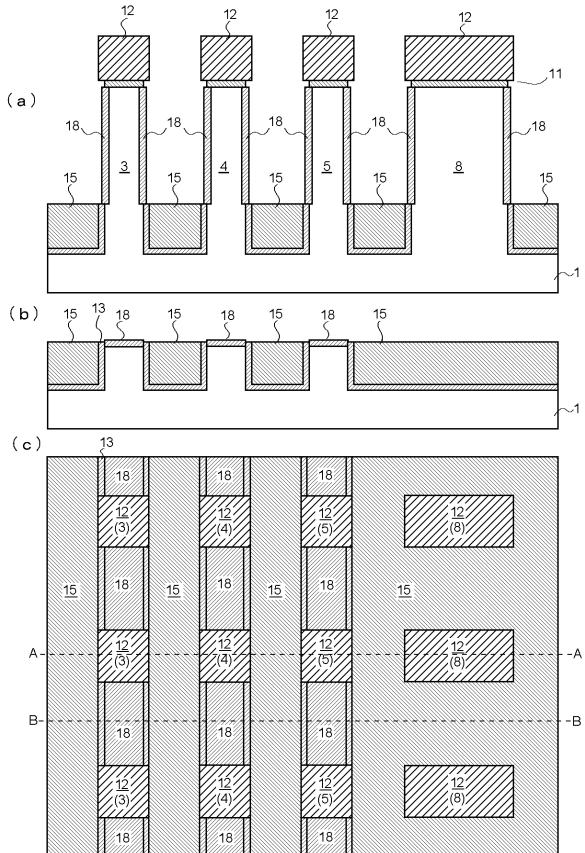

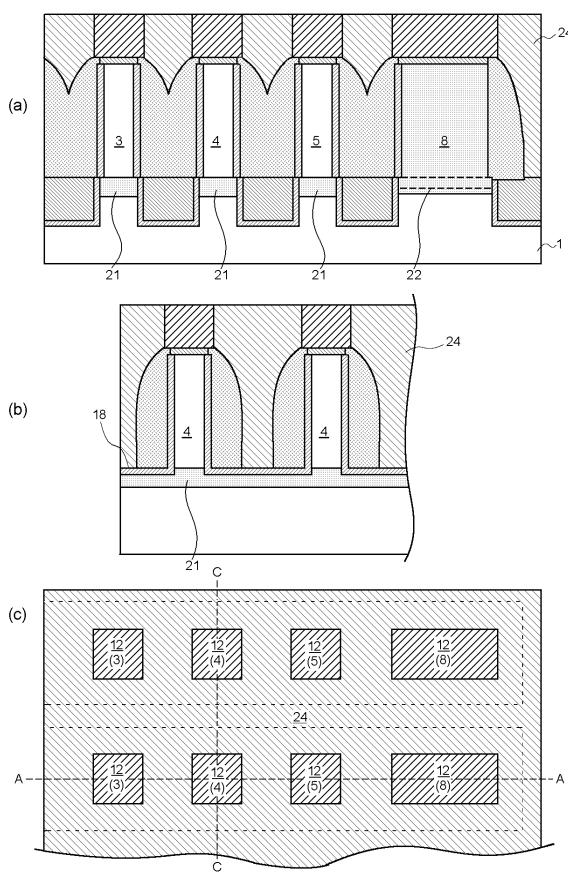

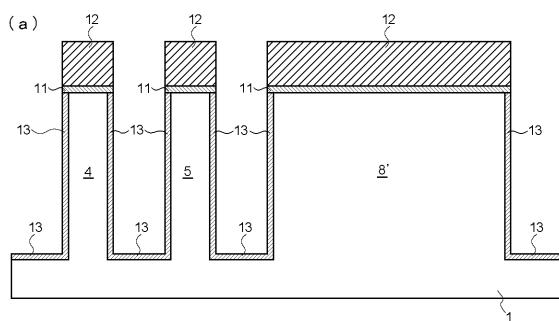

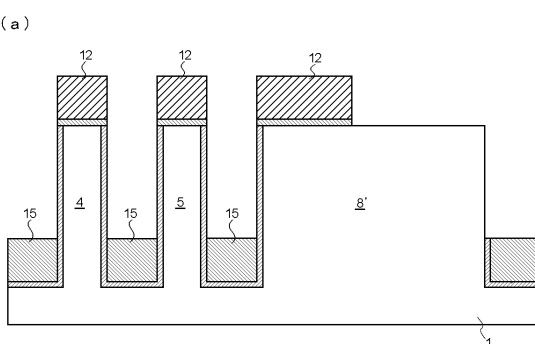

つぎに、図 3 (a) の断面図に示したように、シリコン酸化膜 15 を堆積し、CMP により平坦化して、シリコン柱 3, 4, 5, 8 の周辺にシリコン酸化膜 15 を埋め込んだ。

#### 【0019】

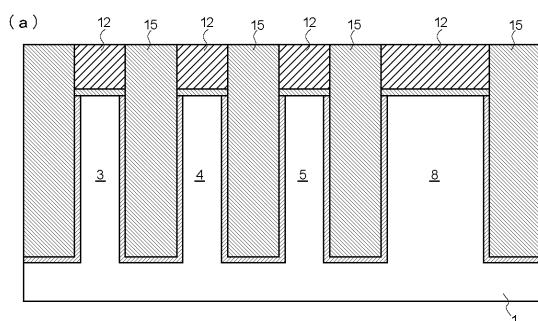

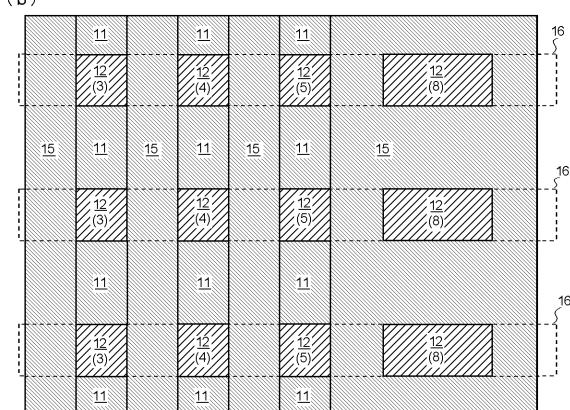

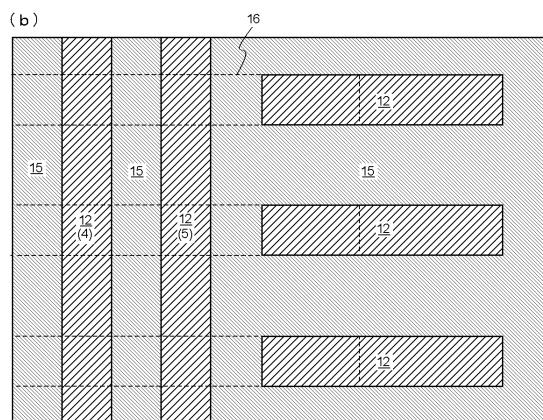

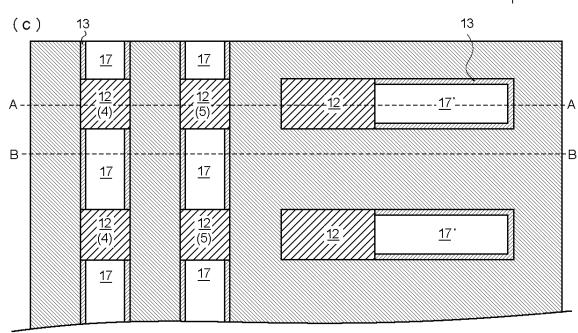

つぎに、図 4 (b) の平面図に示したように、レジストマスク 16 を形成してシリコン窒化膜 12 を加工し、平面的に図のようにシリコン窒化膜 12 が残るようにした。シリコン窒化膜 12 を除去した部分ではシリコン柱 3, 4, 5 上のシリコン酸化膜 11 が露出する。

#### 【0020】

つぎに、図 5 (a) の断面図に示したように、シリコン酸化膜 15 をエッチングして後退させた。ここで、エッチング量は 100 nm であり、残存シリコン酸化膜 15 は 50 nm である。この時、シリコン窒化膜 12 の無い部分のシリコン柱 3, 4, 5 の側壁のシリコン酸化膜 11, 13 も同時にエッチングされ、シリコン柱 3, 4, 5 が露出する。

#### 【0021】

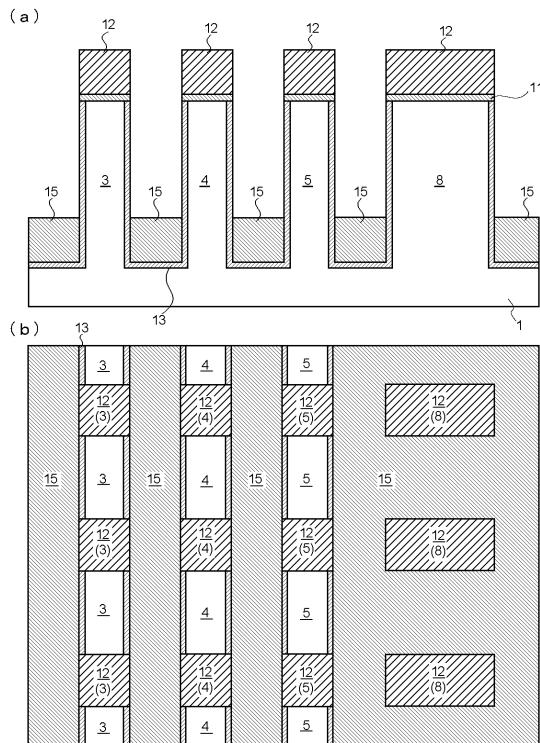

つぎに、図 6 に示したように、シリコン窒化膜 12 をマスクとして、シリコン窒化膜 12 の無い部分に露出したシリコン柱 3, 4, 5 をエッチングした。ここで、シリコンのエッチング量は 100 nm とした。図 6 (a) は図 6 (c) の A-A 線での断面図であり、図 5 (a) の断面図と変わらないが、図 6 (c) の B-B 線での断面 (図 6 (b)) では、シリコン酸化膜 15 とほぼ同じ高さになりシリコン面 17 が露出する。

#### 【0022】

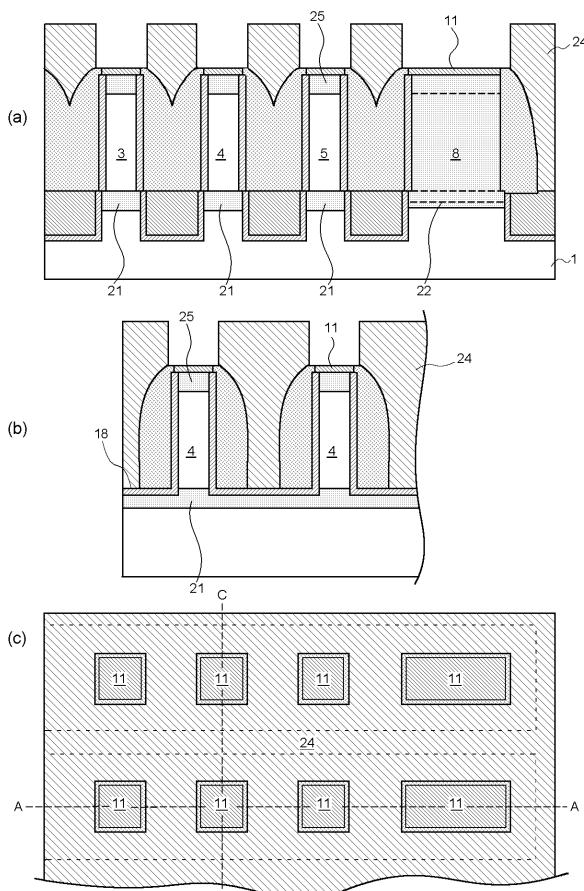

つぎに、図 7 (a) の断面図に示すように、シリコン酸化膜 13 をエッチングして、シリコン柱 3, 4, 5, 8 の側面のシリコンを露出させた。

#### 【0023】

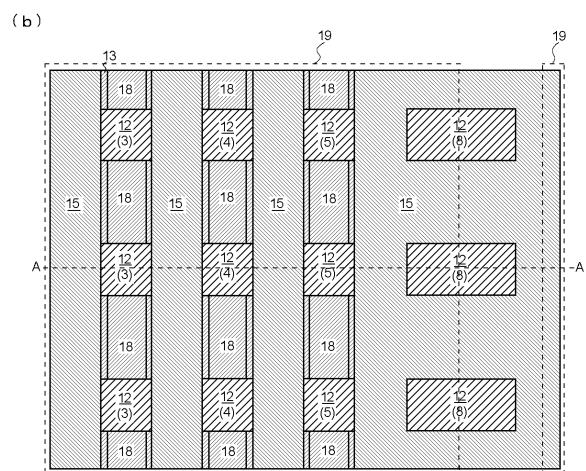

つぎに、図 8 (a) の断面図に示すように、熱酸化により 7 nm のゲート酸化膜 18 を形成した。

#### 【0024】

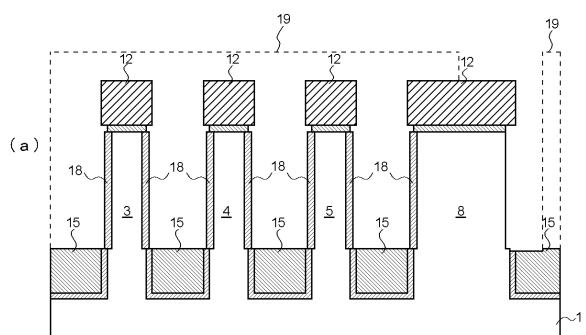

つぎに、図 9 (b) の平面図に示すように、レジストマスク 19 を開口した。この際、断面図は図 9 (a) に示すようになり、この状態でゲート酸化膜 18 をエッチングして、シリコン柱 8 の一部のシリコンを露出させた。

#### 【0025】

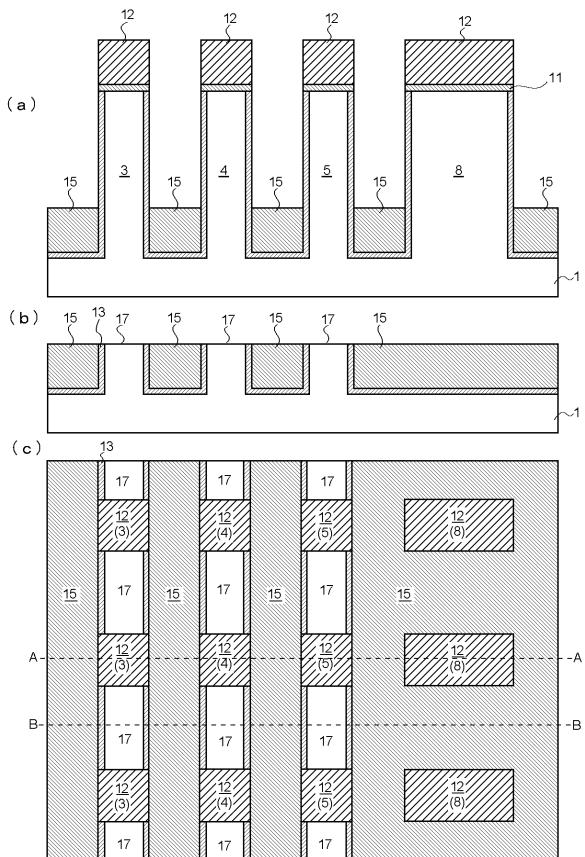

つぎに、図 10 (a) の断面図に示すように、リンを  $4 \times 10^{20} / \text{cm}^3$  ドーピングした多結晶シリコン膜を 10 nm 堆積した。ここで、砒素を  $5 \times 10^{14} / \text{cm}^2$  だけ注入し 1000 秒、10 秒の熱処理を行い、図 10 (c) の平面図に示したように、シリコン柱以外のシリコン部分 17 にドーピングした。この時、シリコン部分 17 からの横方向広がりにより、図 10 (b) の断面図に示すように、n 型の下部拡散層 21 が形成される。なお、上記熱処理により、多結晶シリコンにドーピングされたリンがシリコン柱 8 に拡散し、シリコン柱 8 は n 型層 22 になる。ここで、図 10 (a) は図 10 (c) における A-A 線での断面図、図 10 (b) は C-C 線での断面図を示す。

#### 【0026】

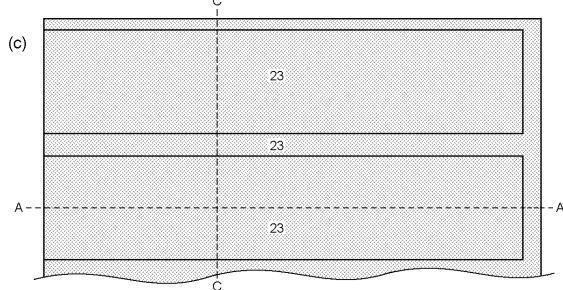

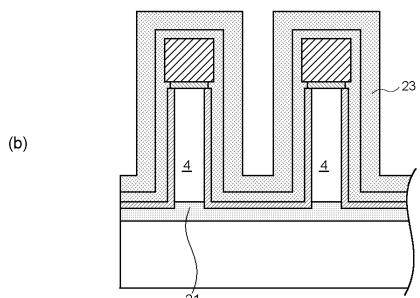

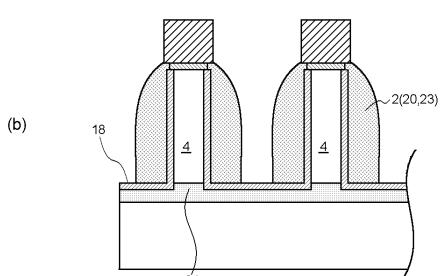

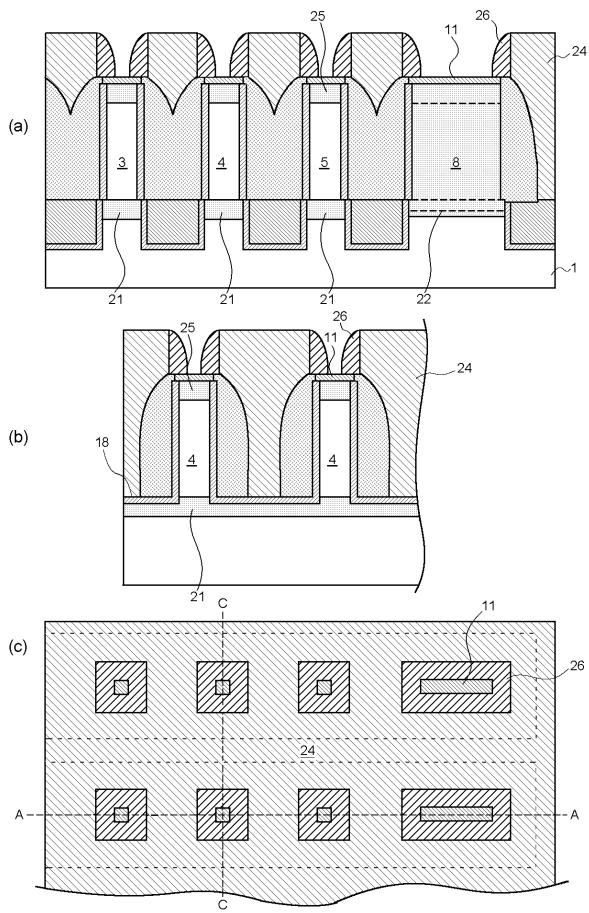

つぎに、図 11 (a) の断面図に示すように、リンを  $4 \times 10^{20} / \text{cm}^3$  ドーピングした多結晶シリコン膜 23 を 20 nm 堆積した。この時、シリコン柱 3, 4, 5, 8 の間には上記多結晶シリコン膜 20, 23 で埋め込まれる。

#### 【0027】

つぎに、図 12 (a) の断面図に示すように、多結晶シリコン 20, 23 を 150 nm

10

20

30

40

50

分だけエッチバックする。その結果、図12(b)の平面図に示すように、シリコン柱3, 4, 5, 8の側壁部分がゲート電極2(多結晶シリコン20, 23)で覆われた構造となり、各シリコン柱3, 4, 5, 8の周りのゲート電極2(多結晶シリコン20, 23)は図面横方向に電気的に接続された構造となる。

#### 【0028】

また、図面縦方向ではシリコン柱同士が離れているため、ゲート電極2(多結晶シリコン20, 23)は分離されている。

#### 【0029】

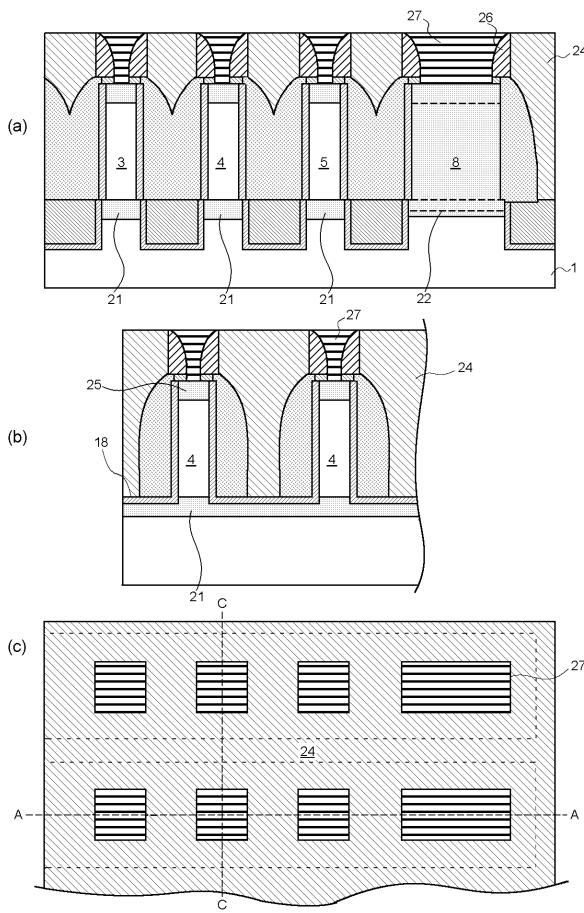

つぎに、図13(a)の断面図に示すように、シリコン酸化膜24を堆積し、CMPにより平坦化した。

10

#### 【0030】

つぎに、図14(a)の断面図に示すように、これまでシリコン柱3, 4, 5, 8の上部にあったシリコン窒化膜12を除去した。その後、砒素を20keVで $5e13/cm^2$ だけ注入し1000、10秒の熱処理を施して上部拡散層25を形成した。この時、シリコン柱8の上部にも砒素が注入され、n型層22の上部では不純物濃度が高くなる。

#### 【0031】

つぎに、図15(a)の断面図に示すように、10nmのシリコン窒化膜を堆積しエッチバックしてシリコン窒化膜サイドウォール26を形成した。

#### 【0032】

つぎに、図16(a)の断面図に示すように、これまでシリコン柱3, 4, 5, 8の上部にあったシリコン酸化膜11を除去したのち、エピタキシャル成長層27を形成した。なお、このエピタキシャル成長層27は、50nm成長させた。この後、エピタキシャル成長層27の低抵抗化のために、砒素を30keVで $1e15/cm^2$ だけ注入し1000、10秒の熱処理を行った。

20

#### 【0033】

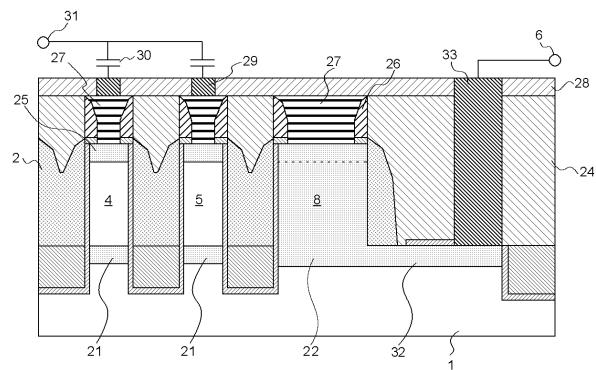

最後に、図1に示すように、100nmのシリコン酸化膜28を堆積し、コンタクト穴を開け電極29を形成した。なお、本実施例をDRAMに適用する場合には、縦型MOSトランジスタ3, 4, 5の上部拡散層25はキャパシタ30下部電極に接続され、キャパシタ30の一方の電極はプレート電位31が供給できるようになる。また、シリコン柱8上部のエピタキシャル成長層27はワード線電位6が供給できるようになる。

30

#### 【0034】

##### 〔第1の実施例の効果〕

第1の実施例によれば、DRAMのセルトランジスタを縦型MOSトランジスタ3, 4, 5で構成し、シリコン柱8をワード線電位供給に利用できるので、以下のような効果がある。

#### 【0035】

各縦型MOSトランジスタでゲート電極を共有する場合、ゲート電極2である多結晶シリコン20, 23を厚くできないため、ワード線抵抗が高くなってしまう。この場合、メモリマット端までの抵抗が非常に大きくなるため、正常な動作が期待できない。本発明のワード線電位供給方法によれば、必要な場所にワード電位供給部6を設けることで、その上部に形成した低抵抗のワード線にワード電位供給部6を接続できる。その結果、実質的にメモリマット端まで低抵抗ワード線とすることができるため、正常な動作が行える。このようなワード電位供給部6を任意に設けることで設計の自由度が大幅に増すようになる。

40

#### 【0036】

##### 〔第2の実施例の構成〕

図17に示すように、シリコン基板1の主表面に形成された第1の導電型のゲート電極2を共有した複数の角柱縦型MOSトランジスタ4, 5のゲート電極2への電位供給6が、角柱縦型MOSトランジスタの第1の角柱4, 5と同時に形成され、かつ、一部分にゲート絶縁膜7を有しない、かつ、ゲート電極2の導電型と同じ第1の導電型である第2の

50

柱8の拡散層22を介して行われていて、ゲート電極の電位供給6が、第2の柱8下に形成された第1の導電型の拡散層32より行なわれ、ゲート電極の電位供給6用のコンタクト33が上記拡散層32に形成されている構造とする。なお、図17では、シリコン柱8上にサイドウォール26、エピタキシャル成長層27を同様に形成しているが、シリコン柱8上のマスク層12を除去せずに上部への不純物注入を行わず、サイドウォール26、エピタキシャル成長層27を形成しない構成や、上部への不純物注入を行った後、開口部を絶縁膜で埋め込み、サイドウォール26、エピタキシャル成長層27を形成しない構成としても問題はない。

#### 【0037】

##### 〔第2の実施例の製法〕

10

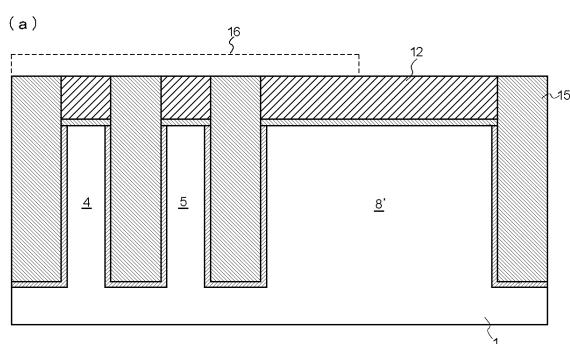

第2の実施例の製法は、第1の実施例と同じであるが、上記図2で示した構造を図18に示した構造に置き換えることと、上記図4で示した構造を図19に示した構造に置き換えることと、上記図5で示した構造を図20に示した構造に置き換えることと、上記図6で示した構造を図21に示した構造に置き換えることにより実現できる。

#### 【0038】

すなわち、図18に示すように、シリコン柱8を第1の実施例よりも横長（シリコン柱8'）に形成し、次に、図19に示すように、レジストマスク16をシリコン柱8'上のシリコン窒化膜12が一部露出するように形成する。つぎに、図20に示したように、シリコン窒化膜12をマスクとして、シリコン窒化膜12の無い部分に露出したシリコン柱4, 5, 8'をエッチングした。ここで、シリコンのエッティング量は100nmとした。図20(a)は図20(c)のA-A線での断面図であり、図20(a)は図20(c)のB-B線での断面である。シリコン酸化膜15とほぼ同じ高さに、シリコン面17、17'が露出する。以後、第1の実施例と同様にしてシリコン酸化膜28の形成まで行った後、コンタクト穴を開け電極29、コンタクト33を形成した。

20

#### 【0039】

##### 〔第2の実施例の効果〕

第2の実施例によれば、第1の実施例と同様の効果を有する。なお、ゲート電極の電位供給6に必要な面積が増加するものの、コンタクト33の配置に自由度が増す。

#### 【0040】

##### 〔第3の実施例の構成〕

30

次に第3の実施例は、図22に示すように、第1の導電型のゲート電極を共有した複数の角柱縦型MOSトランジスタ4, 5のゲート電極2への電位供給が、角柱縦型MOSトランジスタ4, 5の第1の角柱と同時に形成され、かつ、少なくとも一部分にゲート絶縁膜を有しない、かつ、ゲート電極の導電型と同じ第1の導電型である第2の柱8の拡散層22を介して行われていて、ゲート電極の電位供給が、第2の柱下に形成された第1の導電型の拡散層を共有した縦型MOSトランジスタ34を動作させることにより行なう構造とする。

#### 【0041】

##### 〔第3の実施例の製法〕

第3の実施例の製法は、第1の実施例及び第2の実施例の製法を組み合わせたものであり、詳細は省略する。

40

#### 【0042】

##### 〔第3の実施例の効果〕

第3の実施例によれば、第1の実施例と同様の効果を有する。なお、ゲート電極の電位供給6に必要な縦型MOSトランジスタ34分の面積が増加するものの、縦型MOSトランジスタ34の上部拡散層25からの電位供給が可能になるので配置に自由度が増す。

#### 【図面の簡単な説明】

#### 【0043】

##### 【図1】本発明の第1の実施例を説明する断面構造図

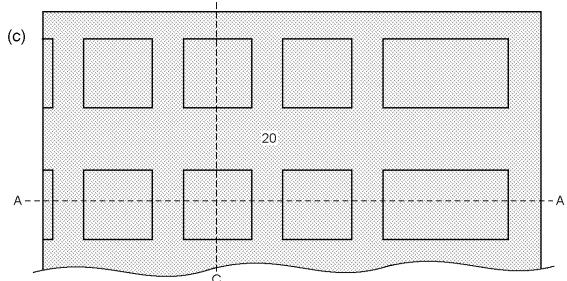

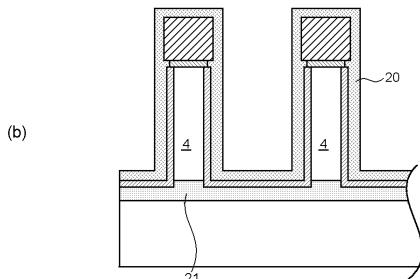

##### 【図2】本発明の第1の実施例の製法を説明する断面図および平面図

50

【図 3】本発明の第 1 の実施例の製法を説明する断面図および平面図

【図 4】本発明の第 1 の実施例の製法を説明する断面図および平面図

【図 5】本発明の第 1 の実施例の製法を説明する断面図および平面図

【図 6】本発明の第 1 の実施例の製法を説明する断面図および平面図

【図 7】本発明の第 1 の実施例の製法を説明する断面図および平面図

【図 8】本発明の第 1 の実施例の製法を説明する断面図および平面図

【図 9】本発明の第 1 の実施例の製法を説明する断面図および平面図

【図 10】本発明の第 1 の実施例の製法を説明する断面図および平面図

【図 11】本発明の第 1 の実施例の製法を説明する断面図および平面図

【図 12】本発明の第 1 の実施例の製法を説明する断面図および平面図

【図 13】本発明の第 1 の実施例の製法を説明する断面図および平面図

【図 14】本発明の第 1 の実施例の製法を説明する断面図および平面図

【図 15】本発明の第 1 の実施例の製法を説明する断面図および平面図

【図 16】本発明の第 1 の実施例の製法を説明する断面図および平面図

【図 17】本発明の第 2 の実施例を説明する断面構造図

【図 18】本発明の第 2 の実施例の製法を説明する断面図および平面図

【図 19】本発明の第 2 の実施例の製法を説明する断面図および平面図

【図 20】本発明の第 2 の実施例の製法を説明する断面図および平面図

【図 21】本発明の第 2 の実施例の製法を説明する断面図および平面図

【図 22】本発明の第 3 の実施例を説明する断面構造図

10

20

## 【符号の説明】

## 【0044】

- 1 . . . シリコン基板

- 2 . . . ゲート電極

- 3、4、5、34 . . . 縦型MOSトランジスタ

- 6 . . . ワード線電位供給

- 7 . . . ゲート酸化膜

- 8 . . . 第2の柱

- 11、13、15、24、28 . . . シリコン酸化膜

- 12 . . . シリコン窒化膜

- 16、19 . . . レジスト膜

- 17 . . . シリコン露出面

- 18 . . . ゲート酸化膜

- 20、23 . . . 多結晶シリコン膜

- 21 . . . 下部拡散層

- 22 . . . n型層

- 25 . . . 上部拡散層

- 26 . . . サイドウォール

- 27 . . . エピタキシャル成長層

- 29、33 . . . 電極

- 30 . . . キャパシタ

- 31 . . . プレート電位供給

- 32 . . . 下部拡散層と同じ導電型層

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 29/49 (2006.01) H 01 L 27/10 621Z

H 01 L 29/58 G

(72)発明者 大湯 静憲

東京都中央区八重洲2-2-1 エルピーダメモリ株式会社内

審査官 井上 弘亘

(56)参考文献 特開平5-136374 (JP, A)

特開2003-218242 (JP, A)

特開平04-079369 (JP, A)

特開平02-188966 (JP, A)

特表2005-538537 (JP, A)

特開平03-231460 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/336

H 01 L 21/8242

H 01 L 27/108

H 01 L 29/423

H 01 L 29/49

H 01 L 29/78