(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2014-6518

(P2014-6518A)

(43) 公開日 平成26年1月16日(2014.1.16)

| (51) Int.Cl.                 | F 1             | テーマコード (参考) |

|------------------------------|-----------------|-------------|

| <b>G02F 1/1368 (2006.01)</b> | GO2F 1/1368     | 2H192       |

| <b>H04N 5/3745 (2011.01)</b> | HO4N 5/335 745  | 4M118       |

| <b>H01L 27/146 (2006.01)</b> | HO1L 27/14 C    | 5B068       |

| <b>H01L 29/786 (2006.01)</b> | HO1L 29/78 612C | 5B087       |

| <b>G09F 9/30 (2006.01)</b>   | HO1L 29/78 618B | 5CO24       |

審査請求 未請求 請求項の数 7 O L (全 23 頁) 最終頁に続く

(21) 出願番号 特願2013-112886 (P2013-112886)

(22) 出願日 平成25年5月29日 (2013.5.29)

(31) 優先権主張番号 特願2012-122521 (P2012-122521)

(32) 優先日 平成24年5月29日 (2012.5.29)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 小山 潤

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

F ターム (参考) 2H192 AA24 CB05 CB22 CB26 CB37

DA12 FB02 GB04 GB14

4M118 AB01 AB10 BA05 CA14 CA22

CB05 CB14 DD04 DD12 EA01

EA14 FB03 FB13 FB24

5B068 AA03 AA22 BB18 BC07 BE06

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【要約】

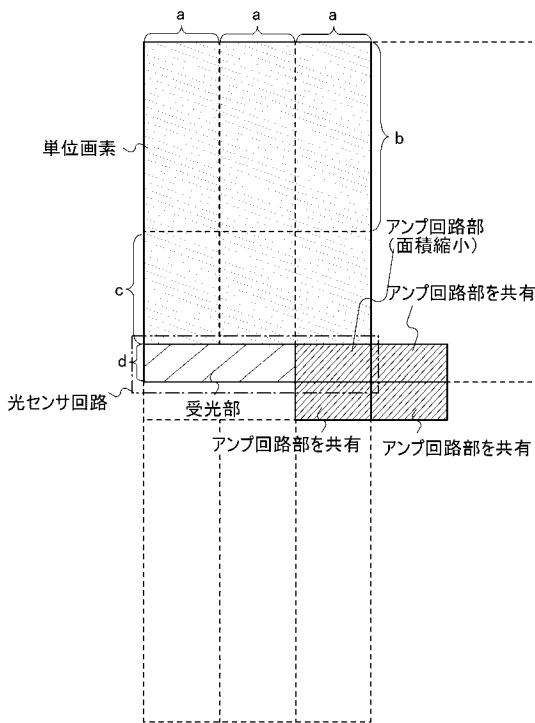

【課題】液晶表示装置の表示部において、単位画素の開口率を向上させつつ、単位画素に対応するデッドスペースを低減させる。

【解決手段】複数の単位画素で、アンプ回路部を共有することにより、単位画素に対応するアンプ回路部の面積を低減させ、単位画素の開口率を高める。また、より多くの単位画素で同一のアンプ回路部を共有することで、受光感度を高めても、単位画素に対応する光センサ回路の面積の増大を防ぐ。更に、単位画素の開口率を高めることで、液晶表示装置におけるバックライトの消費電力を下げる。

【選択図】図 1

**【特許請求の範囲】****【請求項 1】**

液晶素子を含む複数の画素と、

第1のトランジスタ及び第2のトランジスタを含むアンプ回路と、

非単結晶半導体層を含む複数の受光素子と、

各前記受光素子に対して設ける第3のトランジスタと、を有し、

前記第1のトランジスタの一方の端子と、前記第2のトランジスタのゲート端子と、ノードとは、電気的に接続され、

各前記第3のトランジスタの一方の端子と、前記ノードとは、電気的に接続され、

前記アンプ回路は、4個以上20個以下の前記画素に対して1個設ける

ことを特徴とする半導体装置。

10

**【請求項 2】**

請求項1において、

前記非単結晶半導体層は、アモルファスシリコン層である

ことを特徴とする半導体装置。

**【請求項 3】**

請求項1又は請求項2において、

前記トランジスタの半導体層として、酸化物半導体材料を用いる

ことを特徴とする半導体装置。

20

**【請求項 4】**

請求項1乃至請求項3のいずれか一項において、

前記アンプ回路は、一方の端子が前記第2のトランジスタの一方の端子と電気的に接続され、他方の端子が出力信号線と電気的に接続される第4のトランジスタを含む

ことを特徴とする半導体装置。

**【請求項 5】**

請求項1乃至請求項4のいずれか一項において、

前記画素は、前記第1乃至第4のトランジスタと同一基板上に形成される第5のトランジスタと、保持容量とを有する

ことを特徴とする半導体装置。

30

**【請求項 6】**

請求項1乃至請求項5のいずれか一項において、

前記半導体装置は、透過型液晶表示領域を有する

ことを特徴とする半導体装置。

**【請求項 7】**

請求項1乃至請求項6のいずれか一項において、

前記半導体装置は、反射型液晶表示領域を有する

ことを特徴とする半導体装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

半導体装置に関する。特に、受光素子の半導体層として非単結晶半導体層を用いる半導体装置に関する。

40

**【0002】**

なお、本明細書中において半導体装置とは、半導体特性を利用して機能しうる装置全般を指し、電気光学装置、半導体回路および電子機器は全て半導体装置である。

**【背景技術】****【0003】**

近年、光センサ回路を表示装置の表示部内に組み込むことによって構成される光検出方式のタッチセンサについての提案が各種なされている。一般的に、光センサ回路は、単位画素又は3個のサブ画素(RGB)に対応して、1個配置される。光センサ回路は、受光素

50

子等で構成される受光部と、受光部からの受光信号を増幅して検出信号を出力するアンプ回路部とにより構成される。

#### 【0004】

限られたマスク数で光センサ回路11を形成する場合、即ち同一平面上に光センサ回路11を形成する場合、光センサ回路11内に占めるアンプ回路部12の面積は、受光部13の面積に比べて小さくなる。従って、図8(A)に示すように、面積の差により、表示部内にはデッドスペース14が生じる。

#### 【0005】

また、光センサ回路11の受光感度を高めるために、受光部13の面積を広げると、表示部内における光センサ回路11の面積は更に広がる。

10

#### 【0006】

特許文献1では、光センサ回路11内に占めるアンプ回路部12と受光部13との面積の差により生じるデッドスペース14をなくすために、デッドスペース14の面積の半分だけ、単位画素15の面積を狭くしている。(図8(B)参照。)

#### 【0007】

また、特許文献2では、受光素子に用いられる半導体層として、フォトダイオードを用いている。当該フォトダイオードは、微結晶シリコンのp層、アモルファスシリコンのi層、微結晶シリコンのn層の3層を積層した構造を有している。

20

#### 【先行技術文献】

#### 【特許文献】

#### 【0008】

【特許文献1】特開2009-271308号公報

【特許文献2】特開2011-210241号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0009】

できるだけマスク数を低減させ、工程の簡略化を図りながら光センサ回路を表示部内に組み込む場合、アンプ回路部と受光部とを積層することが難しいため、アンプ回路部と受光部との面積の差による影響は無視できない。光センサ回路内においてアンプ回路部と受光部との面積の差が大きい程、表示部内におけるデッドスペースが広くなり、単位画素に対応する光センサ回路の面積が増大する。

30

#### 【0010】

特許文献1に示すように、デッドスペースを埋めるために単位画素の面積を狭くすれば、開口率が低下する。

#### 【0011】

開口率を高め、且つ単位画素に対応する光センサ回路の面積を低減させることは非常に困難である。

#### 【0012】

また、受光素子としてフォトダイオードを使用する場合、I層、P層、N層の3層を作製する必要があり、工程数が増大する。その結果、製造コストが増大するという問題がある。

40

#### 【0013】

上述の問題を鑑みて、単位画素の開口率を向上させつつ、単位画素に対応するデッドスペースを低減させることを課題の一つとする。

#### 【0014】

また、消費電力を低減させることを課題の一つとする。

#### 【0015】

また、製造コストの増大を防止することを課題の一つとする。

#### 【課題を解決するための手段】

#### 【0016】

50

1個のアンプ回路部を複数の単位画素で共有することにより、工程の簡略化を図りつつ単位画素に対応するアンプ回路部の面積を低減させる。また、受光感度を高めるために受光部の面積を増大させる場合、より多くの単位画素でアンプ回路部を共有することで、単位画素に対応する光センサ回路の面積の増大を防ぐ。

#### 【0017】

本明細書で開示する本発明の一態様は、液晶素子を含む複数の画素と、第1のトランジスタ及び第2のトランジスタを含むアンプ回路と、非単結晶半導体層を含む複数の受光素子と、各受光素子に対して設ける第3のトランジスタと、を有し、第1のトランジスタの一方の端子と、第2のトランジスタのゲート端子と、ノードとは、電気的に接続され、各第3のトランジスタの一方の端子と、ノードとは、電気的に接続され、アンプ回路は、4個以上20個以下の画素に対して1個設けることを特徴とする半導体装置である。10

#### 【0018】

上記において、非単結晶半導体層は、アモルファスシリコン層であることが好ましい。特に、受光することで生成される光電流の値が暗電流の値の100倍以上を有するアモルファスシリコン層であることが好ましい。

#### 【0019】

上記において、トランジスタの半導体層として、酸化物半導体材料を用いてもよい。

#### 【0020】

上記において、アンプ回路は、一方の端子が第2のトランジスタの一方の端子と電気的に接続され、他方の端子が出力信号線と電気的に接続される第4のトランジスタを含んでいてもよい。20

#### 【0021】

上記において、画素は、液晶素子の他に、第1乃至第4のトランジスタと同一基板上に形成される第5のトランジスタと、保持容量とを含んでいても良い。

#### 【0022】

上記において、半導体装置は、透過型液晶表示領域を有していてもよい。

#### 【0023】

上記において、半導体装置は、反射型液晶表示領域を有していてもよい。

#### 【0024】

なお、図面等において示す各構成の、位置、大きさ、範囲などは、説明を分かりやすくするために、実際の位置、大きさ、範囲などを表していない場合がある。このため、開示する発明は、必ずしも、図面等に開示された位置、大きさ、範囲などに限定されない。30

#### 【0025】

なお、本明細書等における「第1」、「第2」、「第3」などの序数は、構成要素の混同を避けるために付したものであり、数的に限定するものではないことを付記する。

#### 【発明の効果】

#### 【0026】

1個のアンプ回路部を複数の単位画素で共有することにより、単位画素に対応するアンプ回路部の面積を低減させ、単位画素の開口率を高めることができる。また、より多くの単位画素で同一のアンプ回路部を共有することで、受光感度を高めても、単位画素に対応する光センサ回路の面積の増大を防ぐことができる。更に、単位画素の開口率を高めることで、液晶表示装置におけるバックライトの消費電力を下げることができる。40

#### 【図面の簡単な説明】

#### 【0027】

【図1】実施の形態1に係わる半導体装置を説明する図。

【図2】実施の形態1に係わる光センサ回路の駆動を示すタイミングチャート。

【図3】本発明の一態様を示す半導体装置を説明する図。

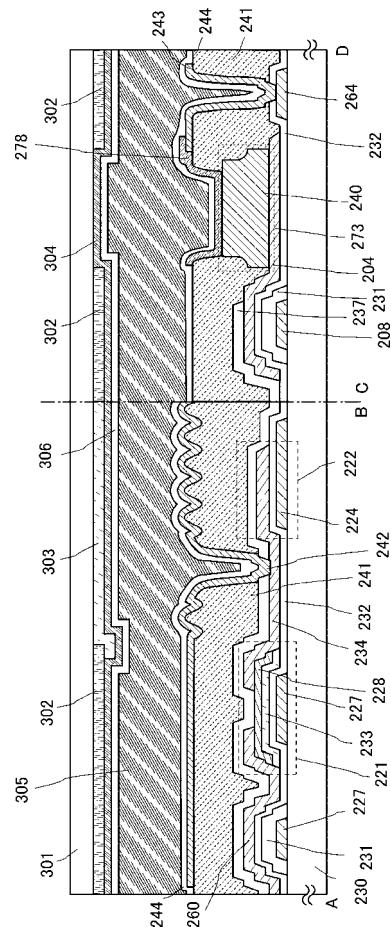

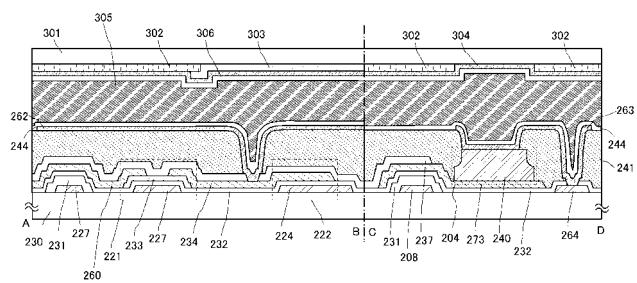

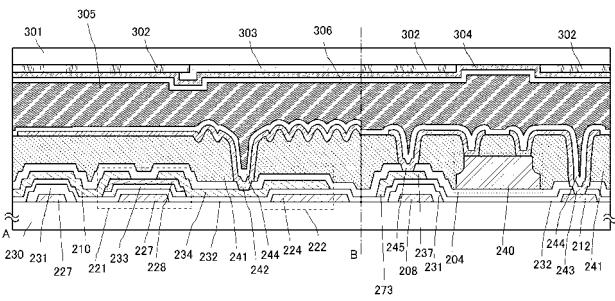

【図4】本発明の一態様を示す半導体装置の断面図。

【図5】本発明の一態様を示す半導体装置の断面図。

【図6】本発明の一態様を示す電気機器の一例を説明する図。50

【図7】本発明の一態様を示す半導体装置の断面図。

【図8】従来例の半導体装置を説明する図。

【発明を実施するための形態】

【0028】

実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更しえることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

10

【0029】

(実施の形態1)

本実施の形態では、1個のアンプ回路部を複数の単位画素で共有することにより、単位画素に対応する光センサ回路の面積を低減させた半導体装置について説明する。表示部内におけるデッドスペースを低減させることで、結果的に単位画素の開口率を高められる。

【0030】

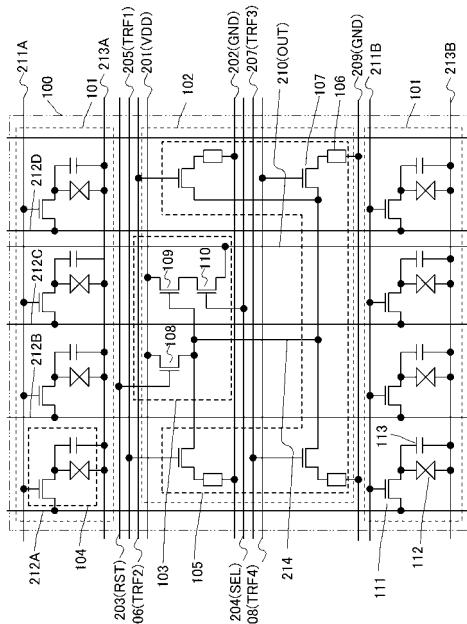

図1は、本発明の一態様に係る半導体装置における表示部の一部を示している。なお、図1に示す回路構成は、一例であり、該構成に限定されない。

【0031】

表示部100は、画素回路101と、光センサ回路102と、を有する。画素回路101には、8個の単位画素104が含まれている。光センサ回路102には、アンプ回路部103と、受光部105が含まれている。

20

【0032】

なお、本実施の形態では、1個のアンプ回路部103を、8個の単位画素104で共有する例を示しているが該構成に限定されない。本発明の一態様によれば、1個のアンプ回路部103で、4個以上20個以下の単位画素104を共有することができる。

【0033】

また、本実施の形態では、1個のアンプ回路部103を、4個の受光素子106で共有する例を示しているが該構成に限定されない。但し、1個のアンプ回路部103を共有する受光素子106の個数は、単位画素104の個数よりも少ないことが好ましい。

30

【0034】

また、表示部100は、電源線(VDD)201、グランド線(GND)202、リセット信号線(RST)203、選択信号線(SEL)204、信号線(TRF1)205、信号線(TRF2)206、信号線(TRF3)207、信号線(TRF4)208、グランド線(GND)209、フォトセンサ出力信号線(OUT)210、走査線211(211A及び211B)、信号線212(212A、212B、212C、及び212D)、グランド線213(213A及び213B)を有する。

【0035】

ノード214は、フローティングディフュージョン(FD)ノードである。ノード214を介して、4個の受光素子106及び4個の転送トランジスタ107が、1個のアンプ回路部103を共有している。

40

【0036】

受光部105には、4個の受光素子106と、4個の転送トランジスタ107とが含まれている。なお、本実施の形態では、転送トランジスタ1個に対して、受光素子1個が設けられている例を示しているが、該構成に限定されない。

【0037】

受光素子106は、一対の電極と、一対の電極に挟持される半導体層とから構成される。半導体層としては、非単結晶半導体層が用いられる。非単結晶半導体層は、受光することで抵抗を変化させる抵抗層として機能する。従って、非単結晶半導体層に一定期間内に照射された光の量を検知することが可能となる。非単結晶半導体層として、非単結晶シリコ

50

ン層を用いる事が好ましく、さらに好ましくはアモルファスシリコン層を用いる事が好ましい。受光することで生成される光電流の値が暗電流の値の100倍以上を有するアモルファスシリコン層であることが好ましい。*i*型アモルファスシリコン層を用いる事が特に好ましい。

#### 【0038】

転送トランジスタ107は、ノード214に蓄積される電荷量を変化させるトランジスタとして機能する。本実施の形態においては、信号線（TRF1）205、信号線（TRF2）206、信号線（TRF3）207、信号線（TRF4）208のそれぞれの電位、即ち転送トランジスタ107のゲートの電位を、“L”から“H”に切り替えると、ノード214に、各受光素子106に一定期間内に照射された光の量に応じて負の電荷が蓄積されていく。

10

#### 【0039】

アンプ回路部103には、リセットトランジスタ108と、増幅トランジスタ109と、選択トランジスタ110とが含まれている。

#### 【0040】

リセットトランジスタ108は、ノード214の電位を、一定期間毎にリセットする（一定電位に戻す）トランジスタとして機能する。リセットトランジスタ108のゲートの電位を、“L”から“H”に切り替えると、ノード214の電位は、“L”から“H”に切り替わる。

20

#### 【0041】

増幅トランジスタ109は、ノード214に蓄積された電荷に応じた電位を増幅するトランジスタとして機能する。

#### 【0042】

選択トランジスタ110は、光センサ回路102の出力を制御するトランジスタとして機能する。増幅トランジスタ109によって増幅された電位を、出力信号に変換し、フォトセンサ出力信号線（OUT）210へと出力する。フォトセンサ出力信号線（OUT）210が“L”から“H”に切り替わる時、出力信号が読み出される。

30

#### 【0043】

単位画素104には、トランジスタ111と、液晶素子112と、保持容量113とが含まれている。

#### 【0044】

トランジスタ111は、保持容量113への電荷の注入もしくは保持容量113からの電荷の排出を制御する機能を有する。

#### 【0045】

保持容量113は、液晶素子112に印加する電圧に相当する電荷を保持する機能を有する。液晶素子112に電圧を印加することで偏光方向が変化する。偏光方向の変化を利用して、液晶素子112を透過する光の明暗（階調）を作ることで、液晶素子112は表示素子として機能しうる。液晶素子112を透過する光には、外光（太陽光または照明光）を利用して半導体装置の表面から照射される光を用いる。

40

#### 【0046】

液晶素子112は、一対の端子と、該一対の端子の間の液晶層を含む素子である。液晶素子112の液晶層としては、特に限定されず、公知の液晶材料（代表的には、ネマチック液晶材料やコレステリック液晶材料）を用いれば良い。例えば、高分子分散型液晶（PDL C（Polymer Dispersed Liquid Crystal）、高分子分散液晶、ポリマー分散型液晶ともいう）又は高分子ネットワーク型液晶（PNL C（Polymer Network Liquid Crystal））を液晶層に用いて、液晶による光の散乱光を利用して白表示（明表示）を行ってもよい。PDL CやPNL Cを液晶層に用いると、偏光板を必要とせず、紙面に近い表示が実現でき、使用者の目に優しく、疲労感を低減させることができる。

50

#### 【0047】

なお、上述したトランジスタに用いる半導体層として、酸化物半導体層を用いることもできる。受光素子 106 に光が照射されることにより生成された電荷を、長時間保持するためには、受光素子 106 と電気的に接続される転送トランジスタ 107 を、オフ電流が極めて低いトランジスタで構成することが好ましい。半導体層として酸化物半導体材料を用いることで光センサ回路 102 の性能を高めることができる。

#### 【0048】

リセットトランジスタ 108 のソース又はドレインの一方と、増幅トランジスタ 109 のゲートと、ノード 214 とは電気的に接続されている。また、選択トランジスタ 110 のソース又はドレインの一方と、増幅トランジスタ 109 のソース又はドレインの一方とは電気的に接続されている。増幅トランジスタ 109 のソース又はドレインの他方は電源線 201 (VDD) と電気的に接続されている。選択トランジスタ 110 のソース又はドレインの他方はフォトセンサ出力信号線 (OUT) 210 と電気的に接続されている。10

#### 【0049】

リセットトランジスタ 108 のソース又はドレインの他方は電源線 (VDD) 201 と電気的に接続されている。リセットトランジスタ 108 のゲートは、リセット信号線 (RST) 203 と電気的に接続されている。選択トランジスタ 110 のゲートは、選択信号線 (SEL) 204 と電気的に接続されている。

#### 【0050】

4 個の各転送トランジスタ 107 のソース又はドレインの一方と、ノード 214 とは電気的に接続されている。また、4 個の各転送トランジスタ 107 のソース又はドレインの他方と、4 個の各受光素子 106 の一方の電極とは電気的に接続されている。4 個の各受光素子 106 の他方の電極は、グランド線 (GND) 202 又は 209 と電気的に接続されている。20

#### 【0051】

4 個の各転送トランジスタ 107 のゲートは、それぞれ信号線 (TRF1) 205、信号線 (TRF2) 206、信号線 (TRF3) 207、信号線 (TRF4) 208 と電気的に接続されている。

#### 【0052】

トランジスタ 111 のゲートは、走査線 211 を介して表示素子駆動回路 (図示せず) に電気的に接続されている。トランジスタ 111 のソース又はドレインの一方は、信号線 212 を介して、表示素子駆動回路 (図示せず) に電気的に接続されている。トランジスタ 111 のソース又はドレインの他方は、保持容量 113 の一方の端子及び液晶素子 112 の一方の端子に電気的に接続されている。保持容量 113 の他方の端子、及び液晶素子 112 の他方の端子は、グランド線 213 に電気的に接続され、一定の電位に保たれている。30

#### 【0053】

なお電源線 (VDD) 201 に入力される電位 "H" を高レベル電源電位 VDD として表すものとする。また、グランド線 (GND) 202、209 に入力される電位 "L" を低レベル電源電位 VSS として表すものとする。なお本明細書では、低レベル電源電位 VS として接地電位 GND (0V) が用いられるが、これに限定されない。高レベル電源電位 VDD より低い電位であれば、低レベル電源電位 VSS として用いることができる。40

#### 【0054】

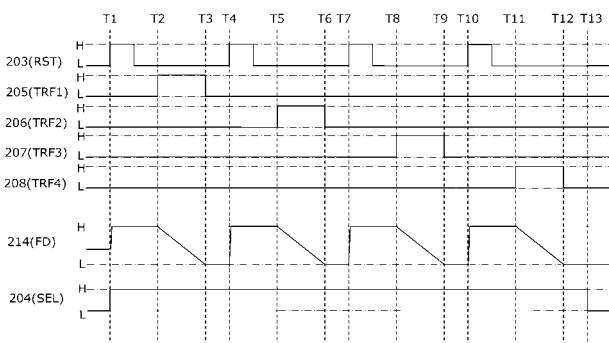

図 3 は、単位画素 315、光センサ回路 311、受光部 313、アンプ回路部 312 を、模式的に示した図である。図 3、図 8 (A)、図 8 (B) は、全て同一面積における比較である。長辺方向が、(b + c + d)、短辺方向が 3a としている。

#### 【0055】

図 8 (A) では、 $2a \times c$  のデッドスペース 14 が生じている。図 8 (B) では、デッドスペースを無くしたため、 $a \times c$  だけ、単位画素 15 の面積が縮小している。図 3 における単位画素 315 の面積は、 $3a \times (b + c)$ 、図 8 (A) における単位画素 15 の面積は、 $3a \times b$ 、図 8 (B) における単位画素 15 の面積は、 $2a \times b + \{a \times (b - c)\}$ 50

} となり、図 3 は、図 8 (B) よりも単位画素の面積を広げられていることがわかる。

【0056】

図 8 (B) では、1 個の画素に対応するアンプ回路部 12 の面積は、 $a \times (b + c)$  である。一方、図 3 では、ある 1 個の画素とその 1 個の画素に隣接する 3 個の画素、即ち合計 4 個の画素が 1 個のアンプ回路部 312 を共有することによって、1 個の画素に対応するアンプ回路部 312 の面積は、 $1/4 \{ a \times (b + c) \}$  となっていることがわかる。

【0057】

本発明の一態様によれば、1 個のアンプ回路部を複数の単位画素で共有することにより、図 8 (A) のように表示部内におけるデッドスペース 14 の面積を増大させず、図 8 (B) のように単位画素 15 の面積を低減させることなく、単位画素に対応するアンプ回路部の面積を低減させ、単位画素の開口率を高めることができる。また、受光部の面積が増えても、より多くの単位画素で、アンプ回路部を共有することにより、単位画素に対応する光センサ回路の面積の増大を防ぐことができる。従って、受光素子の半導体層として受光感度を稼ぐためには、p 層、i 層、n 層の 3 層を積層した構造の受光素子よりも光センサ回路内に占める面積が大きくなる可能性の大きい、非単結晶半導体層を抵抗層として用いた受光素子を用いた場合であっても、特に問題が生じない。つまり工程の簡略化を図りつつ単位画素に対応するデッドスペースを低減させることが可能になる。

【0058】

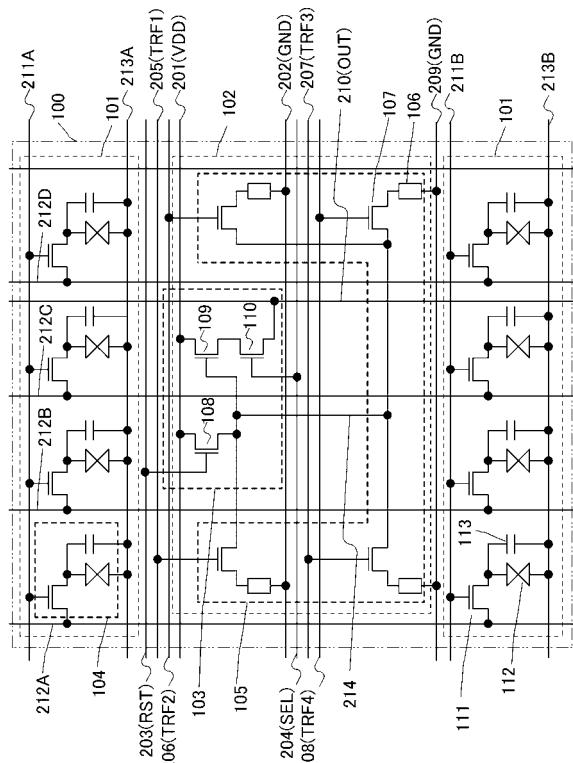

次に、図 1 で示した光センサ回路 102 の駆動について説明する。図 2 に光センサ回路 102 のタイミングチャートを示す。

【0059】

なお、図 2 に示すタイミングチャートにおいて、高レベル電源電位 VDD を、"H" で、低レベル電源電位 VSS を、"L" で表すものとする。

【0060】

時刻 T1 において、リセット信号線 (RST) 203 の電位を、"H" とする。(第 1 のリセット)。リセットトランジスタ 108 のゲートは、"H" となるため、リセットトランジスタ 108 がオン状態となる。この時、ノード 214 の電位が、"L" から "H" に切り替わる。一定期間の後、リセット信号線 (RST) 203 の電位を、"H" から "L" とする。

【0061】

時刻 T2 において、信号線 (TRF1) 205 の電位を、"H" とする。この時、信号線 (TRF1) 205 と電気的に接続された転送トランジスタ 107 のゲートが "H" になるため、転送トランジスタ 107 がオン状態となる。該トランジスタと電気的に接続された受光素子 106 と、ノード 214 とが導通し、ノード 214 の電位が "H" より低下し始める。

【0062】

時刻 T3 において、信号線 (TRF1) 205 の電位を、"H" から "L" とする。この時、転送トランジスタ 107 がオフ状態となる。ノード 214 の電位は、時刻 T3 以後は、再びリセットトランジスタ 108 のゲートが "H" となるまで一定となる。本実施の形態では、この時のノード 214 の電位は低レベル電源電位 VSS となっている。

【0063】

時刻 T2 ~ 時刻 T3 の間、受光素子 106 に照射される光の量に応じて、受光素子 106 の抵抗は変化し、受光素子 106 と、ノード 214 との間に電流が流れ。流れた電流に応じた電荷がトランジスタ 107 を介してノード 214 に蓄積される。

【0064】

時刻 T4 において、再びリセット信号線 (RST) 203 の電位を、"H" とする。(第 2 のリセット)。リセットトランジスタ 108 のゲートは、"H" となるため、リセットトランジスタ 108 がオン状態となる。この時、ノード 214 の電位が、"L" から "H" に切り替わる。一定期間の後、リセット信号線 (RST) 203 の電位を、"H" から "L" とする。

10

20

30

40

50

**【 0 0 6 5 】**

時刻 T 5において、信号線 (TRF2) 206の電位を、”H”とする。この時、信号線 (TRF2) 206と電気的に接続された転送トランジスタ107のゲートが”H”になるため、転送トランジスタ107がオン状態となる。該トランジスタと電気的に接続された受光素子106と、ノード214とが導通し、ノード214の電位が”H”より低下し始める。

**【 0 0 6 6 】**

時刻 T 6において、信号線 (TRF2) 206の電位を、”H”から”L”とする。この時、転送トランジスタ107がオフ状態となる。ノード214の電位は、時刻 T 6以後は、再びリセットトランジスタ108のゲートが”H”となるまで一定となる。本実施の形態では、この時のノード214の電位は低レベル電源電位 VSS となっている。10

**【 0 0 6 7 】**

時刻 T 5～時刻 T 6の間、受光素子106に照射される光の量に応じて、受光素子106の抵抗は変化し、受光素子106と、ノード214との間に電流が流れる。流れた電流に応じた電荷がトランジスタ107を介してノード214に蓄積される。

**【 0 0 6 8 】**

時刻 T 7において、再びリセット信号線 (RST) 203の電位を、”H”とする。(第3のリセット)。リセットトランジスタ108のゲートは、”H”となるため、リセットトランジスタ108がオン状態となる。この時、ノード214の電位が、”L”から”H”に切り替わる。一定期間の後、リセット信号線 (RST) 203の電位を、”H”から”L”とする。20

**【 0 0 6 9 】**

時刻 T 8において、信号線 (TRF3) 207の電位を、”H”とする。この時、信号線 (TRF3) 207と電気的に接続された転送トランジスタ107のゲートが”H”になるため、転送トランジスタ107がオン状態となる。該トランジスタと電気的に接続された受光素子106と、ノード214とが導通し、ノード214の電位が”H”より低下し始める。

**【 0 0 7 0 】**

時刻 T 9において、信号線 (TRF3) 207の電位を、”H”から”L”とする。この時、転送トランジスタ107がオフ状態となる。ノード214の電位は、時刻 T 9以後は、再びリセットトランジスタ108のゲートが”H”となるまで一定となる。本実施の形態では、この時のノード214の電位は低レベル電源電位 VSS となっている。30

**【 0 0 7 1 】**

時刻 T 8～時刻 T 9の間、受光素子106に照射される光の量に応じて、受光素子106の抵抗は変化し、受光素子106と、ノード214との間に電流が流れる。流れた電流に応じた電荷がトランジスタ107を介してノード214に蓄積される。

**【 0 0 7 2 】**

時刻 T 10において、再びリセット信号線 (RST) 203の電位を、”H”とする。(第4のリセット)。リセットトランジスタ108のゲートは、”H”となるため、リセットトランジスタ108がオン状態となる。この時、ノード214の電位が、”L”から”H”に切り替わる。一定期間の後、リセット信号線 (RST) 203の電位を、”H”から”L”とする。40

**【 0 0 7 3 】**

時刻 T 11において、信号線 (TRF4) 208の電位を、”H”とする。この時、信号線 (TRF4) 208と電気的に接続された転送トランジスタ107のゲートが”H”になるため、転送トランジスタ107がオン状態となる。該トランジスタと電気的に接続された受光素子106と、ノード214とが導通し、ノード214の電位が”H”より低下し始める。

**【 0 0 7 4 】**

時刻 T 12において、信号線 (TRF4) 208の電位を、”H”から”L”とする。こ50

の時、転送トランジスタ 107 がオフ状態となる。ノード 214 の電位は、時刻 T12 以後は、再びリセットトランジスタ 108 のゲートが "H" となるまで一定となる。本実施の形態では、この時のノード 214 の電位は低レベル電源電位 VSS となっている。

#### 【0075】

時刻 T11 ~ 時刻 T12 の間、受光素子 106 に照射される光の量に応じて、受光素子 106 の抵抗は変化し、受光素子 106 と、ノード 214 との間に電流が流れる。流れた電流に応じた電荷がトランジスタ 107 を介してノード 214 に蓄積される。

#### 【0076】

また、期間 T1 で選択信号線 (SEL) 204 の電位は、"L" から "H" となり、期間 T1 ~ 期間 T13までの間、"H" 電位を維持する。期間 T13 で選択信号線 (SEL) 204 の電位は、"H" から "L" となる。これにより、期間 T1 ~ 期間 T13までの間、選択トランジスタ 110 は、常にオン状態となっている。従って、増幅トランジスタ 109 のゲートの電位、即ちノード 214 の電位に応じて、フォトセンサ出力信号線 (OUT) 210 から、出力信号が隨時出力される。

10

#### 【0077】

上述の駆動方法によれば、4 個の受光素子に対して、リセットトランジスタ、増幅トランジスタ、選択トランジスタが、それぞれ 1 個ずつしかなくとも、これらを共有する 4 個の受光素子、それぞれに対応する出力信号を、フォトセンサ出力信号線 (OUT) 210 から順次取り出すことが可能になる。

20

#### 【0078】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

#### 【0079】

##### (実施の形態 2)

本実施の形態では、本発明の一態様に係る半導体装置が反射型液晶表示領域を有する場合について説明する。

30

#### 【0080】

受光素子の半導体層として非単結晶半導体層を、トランジスタの半導体層として酸化物半導体層を用いる反射型液晶表示装置の作製方法の一例について、図 4 を用いて説明する。図 4 における A - B までの領域は、単位画素の一部分を、C - D までの領域は、光センサ回路の一部分を示している。なお、単位画素及び光センサ回路は該構成に限定されない。

#### 【0081】

まず、基板 230 上に導電膜を形成した後、当該導電膜を用いて、走査線 227、容量配線 224、信号線 208、電源線 264 を形成する。また図示しない、選択線、電極層、リセット線、グランド線等を形成する。本実施の形態では基板 230 としてガラス基板を用いる。酸化物半導体層を用いるトランジスタのプロセス温度は 400 以下という低い温度にできるため、基板 230 として、ガラス基板の他に、プラスティック基板を用いてもよい。

30

#### 【0082】

下地膜となる絶縁膜を基板 230 と導電膜との間に設けてもよい。下地膜は、基板 230 からの不純物元素の拡散を防止する機能があり、窒化シリコン膜、酸化シリコン膜、窒化酸化シリコン膜、又は酸化窒化シリコン膜から選ばれた一又は複数の膜による積層構造により形成することができる。

40

#### 【0083】

また、導電膜は、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料又はこれらを主成分とする合金材料を用いて、単層で又は積層して形成することができる。

#### 【0084】

次いで、これらの配線を覆う絶縁層を形成し、後に形成される配線と交差する部分にのみ絶縁層 231 を残して選択的にエッチングを行う。本実施の形態では、絶縁層 231 は膜

50

厚600nmの酸化窒化珪素膜を用いる。

【0085】

次いで、ゲート絶縁層232及び酸化物半導体膜を形成する。

【0086】

ゲート絶縁層232は、窒素を含むシリコン膜を含んで構成されていてもよい。窒素を含むシリコン膜は、酸化シリコン膜と比較して比誘電率が高く、同等の静電容量を得るのに必要な膜厚が大きいため、ゲート絶縁層を物理的に厚膜化することができる。よって、トランジスタの絶縁耐圧の低下を抑制、さらには絶縁耐圧を向上させて、半導体装置の静電破壊を抑制することができる。

【0087】

ゲート絶縁層232の膜厚は、少なくとも後述する酸化物絶縁層よりも厚い膜厚で設けるものとし、325nm以上550nm以下とすることが好ましく、355nm以上550nm以下とすることがより好ましい。

【0088】

窒素を含むシリコン膜としては、例えば、窒化シリコン膜、窒化酸化シリコン膜、酸化窒化シリコン膜が挙げられるが、窒素の含有量が多い程高い比誘電率を有するため、窒化シリコン膜を適用することが好ましい。また、酸化シリコンのエネルギーギャップが8eVであるのに対して窒化シリコンのエネルギーギャップは5.5eVと小さく、それに応じて固有抵抗も小さいため、窒化シリコン膜を用いることでより高いESD耐性を付与することが可能となる。さらに、窒化シリコン膜をCVD法で成膜する場合、窒化酸化シリコン膜等の酸素と窒素を含むシリコン膜をCVD法で成膜する場合に適用される温室効果ガスであるN<sub>2</sub>Oガスを用いる必要がない。なお、本明細書中において、酸化窒化シリコン膜とは、その組成として、窒素よりも酸素の含有量が多い膜を指し、窒化酸化シリコン膜とは、その組成として、酸素よりも窒素の含有量が多い膜を指す。

【0089】

上記酸化物半導体膜は、化学式InMO<sub>3</sub>(ZnO)<sub>m</sub>(m>0)で表記される酸化物薄膜を用いることができる。ここで、Mは、Ga、Al、MnおよびCoから選ばれた一または複数の金属元素を示す。例えばMとして、Ga、Ga及びAl、Ga及びMn、またはGa及びCoなどがある。また、上記酸化物薄膜にSiO<sub>2</sub>を含んでもよい。

【0090】

また、酸化物薄膜をスパッタリング法で作製するためのターゲットとしては、例えば、組成として、In<sub>2</sub>O<sub>3</sub>:Ga<sub>2</sub>O<sub>3</sub>:ZnO=1:1:1[mol数比]の酸化物ターゲットを用い、In-Ga-Zn-O膜を成膜する。また、このターゲットの材料及び組成に限定されず、例えば、In<sub>2</sub>O<sub>3</sub>:Ga<sub>2</sub>O<sub>3</sub>:ZnO=1:1:2[mol数比]の酸化物ターゲットを用いてもよい。なお、ここで、例えば、In-Ga-Zn-O膜とは、インジウム(In)、ガリウム(Ga)、亜鉛(Zn)を有する酸化物膜、という意味であり、その化学量論比はとくに問わない。

【0091】

なおゲート絶縁層232及び上記酸化物半導体膜との間に、酸化物絶縁層を設けてよい。

【0092】

当該酸化物絶縁層は、上記酸化物半導体膜の構成元素から選択される一又は複数の金属元素を含んで構成される。このような材料を用いて当該酸化物絶縁層を構成することで、上記酸化物半導体膜との界面を安定化させることができ、該界面に電荷がトラップされることを抑制することができる。よって、トランジスタの劣化、特に光劣化を防止し、信頼性の高いトランジスタとすることができます。

【0093】

具体的には、当該酸化物絶縁層として、例えば、酸化ガリウム膜(GaO<sub>x</sub>とも表記する、なお、xは自然数とは限らず、非自然数を含む)、酸化ガリウム亜鉛膜(Ga<sub>2</sub>Zn<sub>x</sub>O<sub>y</sub>(x=1~5)とも表記する)、Ga<sub>2</sub>O<sub>3</sub>(Gd<sub>2</sub>O<sub>3</sub>)膜、ガリウムの含有量が

10

20

30

40

50

多く、且つ、インジウムの含有量の少ないIn-Ga-Zn系酸化物膜などを設けることが好ましい。

#### 【0094】

当該酸化物絶縁層と上記酸化物半導体膜の構成元素を同一とし、両者の組成を異ならせてよい。例えば、当該酸化物半導体膜として、In-Ga-Zn系酸化物半導体層を用いる場合、インジウム(In)とガリウム(Ga)の比率によって、エネルギーギャップを制御することが可能であるため、上記酸化物半導体膜の原子数比をIn:Ga:Zn=1:1:1、又は、In:Ga:Zn=3:1:2として、当該酸化物絶縁層の原子数比をIn:Ga:Zn=1:3:2とすればよい。なお、当該酸化物絶縁層及び上記酸化物半導体膜は、スパッタリング法によって形成することができ、スパッタリングターゲットにインジウムを含有すると成膜時のパーティクルの発生を低減することができる。よって、インジウムを含む酸化物絶縁層及びインジウムを含む酸化物半導体膜とすることが好ましい。

10

#### 【0095】

上記酸化物半導体膜(第1の酸化物半導体膜とする)上に、新たに第2の酸化物半導体膜を形成し、酸化物半導体膜を積層構造としてもよい。図4では、第1の酸化物半導体膜から酸化物半導体層233、第2の酸化物半導体膜から酸化物半導体層228を形成する例を示している。

20

#### 【0096】

第1の酸化物半導体膜と第2の酸化物半導体膜は、構成元素を同一とし、両者の組成を異ならせることが好ましい。第1の酸化物半導体膜と第2の酸化物半導体膜としてインジウム及びガリウムを含む酸化物半導体膜を形成する場合、ゲート電極に近い側(チャネル側)の第1の酸化物半導体膜のインジウムとガリウムの含有率をIn>Gaとするとい。またゲート電極から遠い側(バックチャネル側)の第2の酸化物半導体膜のインジウムとガリウムの含有率をIn<Gaとするとい。

20

#### 【0097】

酸化物半導体では主として重金属のs軌道がキャリア伝導に寄与しており、インジウムの含有率を多くすることによりs軌道のオーバーラップが多くなる傾向があるため、In>Gaの組成となる酸化物はIn-Gaの組成となる酸化物と比較して高い移動度を備える。また、GaはInと比較して酸素欠損の形成エネルギーが大きく酸素欠損が生じにくいため、In-Gaの組成となる酸化物はIn>Gaの組成となる酸化物と比較して安定した特性を備える。

30

#### 【0098】

チャネル側にIn>Gaの組成となる酸化物半導体を適用し、バックチャネル側にIn-Gaの組成となる酸化物半導体を適用することで、トランジスタの移動度および信頼性をさらに高めることができるとなる。例えば、第1の酸化物半導体膜の原子数比をIn:Ga:Zn=3:1:2とし、第2の酸化物半導体膜の原子数比をIn:Ga:Zn=1:1:1としてもよい。

30

#### 【0099】

なお、第1の酸化物半導体膜に接する酸化物絶縁層の構成元素を第1の酸化物半導体膜と同一とし、組成を異ならせることで酸化物絶縁層の導電性を低下させると、両者の界面をより安定化させることができると、好ましい。第2の酸化物半導体膜に酸化物絶縁層が接する場合も同様である。

40

#### 【0100】

また、第1の酸化物半導体膜と第2の酸化物半導体膜に、結晶性の異なる酸化物半導体を適用してもよい。すなわち、単結晶酸化物半導体、多結晶酸化物半導体、微結晶酸化物半導体、非晶質酸化物半導体、またはCAC-O<sub>5</sub>膜を適宜組み合わせた構成としてもよい。また、第1の酸化物半導体膜と第2の酸化物半導体膜の少なくともどちらか一方に非晶質酸化物半導体を適用すると、第1の酸化物半導体膜と第2の酸化物半導体膜の積層構造の内部応力や外部からの応力を緩和し、トランジスタの特性ばらつきが低減され、また

50

、トランジスタの信頼性をさらに高めることが可能となる。

【0101】

一方で、非晶質酸化物半導体は水素などのドナーとなる不純物を吸収しやすく、また、酸素欠損が生じやすいためn型化されやすい。このため、チャネル側の第1の酸化物半導体膜は、CAAC-OS膜などの結晶性を有する酸化物半導体を適用することが好ましい。

【0102】

酸化物半導体は、非単結晶であって、そのa-b面に垂直な方向から見て、三角形、六角形、正三角形、又は正六角形の原子配列を有し、且つ、c軸に垂直な方向から見て、金属原子が層状、又は金属原子と酸素原子が層状に配列した相を含む酸化物である。なお、本明細書等では、c軸配向結晶を含む酸化物半導体をCAAC-OS(C Axis Aligned Crystalline Oxide Semiconductor)と呼ぶ。

10

【0103】

CAAC-OSは単結晶ではないが、非晶質のみから形成されているものでもない。また、CAAC-OSは結晶部分を含むが、1つの結晶部分と他の結晶部分を明確に判別できないこともある。

【0104】

CAAC-OSに酸素が含まれる場合、酸素の一部は窒素で置換されてもよい。また、CAAC-OSを構成する個々の結晶部分のc軸は一定の方向(例えば、CAAC-OSが形成される基板面、CAAC-OSの表面などに垂直な方向)に揃っていてもよい。または、CAAC-OSを構成する個々の結晶部分のa-b面の法線は一定の方向(例えば、CAAC-OSが形成される基板面、CAAC-OSの表面などに垂直な方向)を向いていてもよい。

20

【0105】

このようなCAAC-OSの例として、層状に形成され、層表面、または支持する基板面に垂直な方向から観察すると、三角形または六角形の原子配列が認められ、且つその層の断面を観察すると金属原子または金属原子と酸素原子(または窒素原子)の層状配列が認められる材料を挙げることもできる。

【0106】

CAAC-OS膜は、例えば、多結晶である酸化物半導体スパッタリング用ターゲットを用い、スパッタリング法によって成膜する。当該スパッタリング用ターゲットにイオンが衝突すると、スパッタリング用ターゲットに含まれる結晶領域がa-b面から劈開し、a-b面に平行な面を有する平板状またはペレット状のスパッタリング粒子として剥離することがある。この場合、当該平板状のスパッタリング粒子が、結晶状態を維持したまま基板に到達することで、スパッタリング用ターゲットの結晶状態が基板に転写され、CAAC-OS膜を成膜することができる。

30

【0107】

また、CAAC-OS膜を成膜するために、以下の条件を適用することが好ましい。

【0108】

成膜時の不純物濃度を低減することで、不純物によって結晶状態が崩れることを抑制できる。例えば、成膜室内に存在する不純物(水素、水、二酸化炭素および窒素など)を低減すればよい。また、成膜ガス中の不純物を低減すればよい。具体的には、露点が-80以下、好ましくは-100以下である成膜ガスを用いる。

40

【0109】

また、成膜時の基板加熱温度を高めることで、基板付着後にスパッタリング粒子のマイグレーションが起こる。具体的には、基板加熱温度を100以上740以下、好ましくは200以上500以下として成膜する。成膜時の基板加熱温度を高めることで、平板状のスパッタリング粒子が基板に到達した場合、基板上でマイグレーションが起こり、平らな面が基板に付着する。

【0110】

50

また、成膜ガス中の酸素割合を高め、電力を最適化することで成膜時のプラズマダメージを軽減すると好ましい。成膜ガス中の酸素割合は、30体積%以上、好ましくは100体積%とする。

#### 【0111】

スパッタリング用ターゲットの一例として、In-Ga-Zn-O化合物ターゲットについて以下に示す。

#### 【0112】

InO<sub>x</sub>粉末、GaO<sub>y</sub>粉末およびZnO<sub>z</sub>粉末を所定の比率で混合し、加圧処理後、1000以上1500以下の温度で加熱処理することで多結晶であるIn-Ga-Zn-O化合物ターゲットとする。なお、X、YおよびZは任意の正数である。ここで、所定の比率は、例えば、InO<sub>x</sub>粉末、GaO<sub>y</sub>粉末およびZnO<sub>z</sub>粉末が、2:2:1、8:4:3、3:1:1、1:1:1、4:2:3または3:1:2のmol数比である。なお、粉末の種類、およびその混合する比率は、作製するスパッタリング用ターゲットによって適宜変更すればよい。

10

#### 【0113】

また、バックチャネル側の第2の酸化物半導体膜に非晶質酸化物半導体を用いると、後に形成されるソース電極層及びドレイン電極層形成時のエッチング処理により酸素欠損が生じ、n型化されやすい。第2の酸化物半導体膜には結晶性を有する酸化物半導体を適用することが好ましい。

20

#### 【0114】

本実施の形態では、ゲート絶縁層232として膜厚100nmの酸化窒化珪素膜を用い、酸化物半導体膜として膜厚30nmのIn-Ga-Zn-O膜を用いる。

#### 【0115】

上記酸化物半導体膜（第1の半導体膜）を用いて、ゲート絶縁層232を介して、走査線227と重なる酸化物半導体層233を形成する。

#### 【0116】

次いで、酸化物半導体層に第1の加熱処理を行う。この第1の加熱処理によって酸化物半導体層の脱水化または脱水素化を行うことができる。第1の加熱処理の温度は、350以上基板の歪み点未満とする。本実施の形態では、RTA（Rapid Thermal Anneal）装置を用い、窒素雰囲気下で650、6分の加熱処理を行った後、大気に触れることなく、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体層に対して窒素雰囲気下450において1時間の加熱処理を行った後、大気に触れないように酸化物半導体層の成膜室に移動させて酸化物半導体層への水や水素の再混入を防ぎ、酸化物半導体層を得る。

30

#### 【0117】

次いで、ゲート絶縁層232、及び酸化物半導体層上に、導電膜を形成する。導電膜としては、例えば、アルミニウム（Al）、クロム（Cr）、銅（Cu）、タンタル（Ta）、チタン（Ti）、モリブデン（Mo）、タングステン（W）から選ばれた元素を成分とする金属膜、または上述した元素の窒化物を成分とする合金膜か、上述した元素を組み合わせた合金膜等を用いることができる。本実施の形態において、導電膜は、膜厚100nmのチタン膜と、膜厚400nmのアルミニウム膜と、膜厚100nmのチタン膜との三層構造とする。

40

#### 【0118】

そして、導電膜上にレジストマスクを形成し、選択的にエッチングを行って、信号線260、電極層234、電極層273を形成する。

#### 【0119】

なお、トランジスタ221は、酸化物半導体層233を有し、走査線227をゲートとし、信号線260をソース電極層又はドレイン電極層の一方とし、電極層234をソース電極層又はドレイン電極層の他方とするトランジスタである。

#### 【0120】

50

また、電極層 234 及び容量配線 224 は、間に挟まれたゲート絶縁層 232 を誘電体とし、保持容量 222 を形成する。

#### 【0121】

次いで、不活性ガス雰囲気下、または酸素ガス雰囲気下で第2の加熱処理（好みしくは200以上400以下）を行う。本実施の形態では、窒素雰囲気下で220、1時間の第2の加熱処理を行う。第2の加熱処理を行うと、酸化物半導体層の一部（チャネル形成領域）が絶縁層と接した状態で加熱される。

#### 【0122】

次いで保護絶縁層となる絶縁層 237 を形成し、電極層 234 に達する開口、電極層 273 に達する開口、電源線 264 に達する開口を形成する。本実施の形態において、絶縁層 237 は、スパッタ法により得られる膜厚 300 nm の酸化シリコン膜を用いる。

10

#### 【0123】

次いで、電極層 273 上に非単結晶半導体層 240 を成膜する。本実施の形態では、非単結晶半導体層 240 として、プラズマ CVD 法により、膜厚 800 nm の i 型アモルファスシリコン層を成膜する。そして、非単結晶半導体層 240 を選択的にエッチングする。

#### 【0124】

次いで感光性有機樹脂層を形成し、露光マスクで開口となる領域を露光し、別の露光マスクで凹凸となる領域を露光し、現像して部分的に凹凸を有する絶縁層 241 を形成する。本実施の形態では、感光性有機樹脂層として、アクリル樹脂を用い、膜厚を 1.5 μm とする。

20

#### 【0125】

次いで、反射性を有する導電膜を成膜し、当該反射性を有する導電膜を用いて、反射電極層 242、接続電極層 243 を形成する。更に、接続電極層 243 に接し、非単結晶半導体層 240 に重畠するように、電極層 278 を形成する。電極層 278 は、ITO 等の透光性を有する導電性材料などで形成され、非単結晶半導体層 240 に照射される光が透過される材料を用いることが好みしい。なお、反射電極層 242、接続電極層 243、電極層 278 を図 4 に示す。反射性を有する導電膜としてはアルミニウム (Al)、銀 (Ag)、またはこれらの合金、例えばネオジム (Nd) を含むアルミニウム、Ag-Pd-Cu 合金等を用いる。本実施の形態において、反射性を有する導電膜は、膜厚 100 nm のチタン (Ti) 膜とその上に設けた膜厚 300 nm のアルミニウム (Al) 膜の積層を用いる。次いで第3の加熱処理、本実施の形態では、窒素雰囲気下 250、1 時間を行う。そして、反射電極層 242 を覆う配向膜 244 を形成する。

30

#### 【0126】

以上の工程により、同一基板上に反射電極層 242 を有する画素、及び、非単結晶半導体層 240 を有する受光素子 106 を作製することができる。受光素子 106 は、一対の電極である電極層 273 及び接続電極層 278 との間に非単結晶半導体層 240 が挟まれた構成となる。

#### 【0127】

そして、上述のようにして作製されたアクティブマトリクス基板と貼り合わせる対向基板を用意する。対向基板として、透光性を有する基板 301 を用い、基板 301 に、遮光層 302（ブラックマトリクスとも呼ぶ）、反射電極層 242 上にカラーフィルタ 303 を形成する。遮光層 302 としては、チタン、クロムなどの反射率の低い金属膜、または、黒色顔料や黒色染料が含浸された有機樹脂膜などを用いることができる。カラーフィルタ 303 は、特定の波長領域の光を透過する有色層である。例えば、赤色の波長帯域の光を透過する赤色 (R) の着色層、緑色の波長帯域の光を透過する緑色 (G) の着色層、青色の波長帯域の光を透過する青色 (B) の着色層などを用いることができる。

40

#### 【0128】

また、非単結晶半導体層 240 上には、遮光層もカラーフィルタも形成しない。さらに、基板 301、遮光層 302、カラーフィルタ 303 を覆って、透光性を有する導電膜 304 を形成する。透光性を有する導電膜 304 として、酸化タンゲステンを含むインジウム

50

酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物（以下、ITOと示す。）、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物、グラフェン等を用いればよい。さらに有機樹脂を用いた柱状スペーサを形成する。そして、最後に配向膜306で覆う。

#### 【0129】

この対向基板をシール材を用いてアクティブマトリクス基板と貼り合わせ、一対の基板間に液晶層305を挟持する。対向基板の遮光層302は、反射電極層242の表示領域及び受光素子106のセンシング領域に重ならないように設ける。また、一対の基板の間隔を一定に保持するために、位置合わせを正確に行って対向基板に柱状スペーサを設ける。

10

#### 【0130】

以上説明したように、図4のような反射性を有する導電膜を画素電極とする半導体装置を作製することができる。

#### 【0131】

なお図4では、受光素子106は、電極層273、非単結晶半導体層240、及び接続電極層278が順に積層された構成である。すなわち、受光素子の一対の電極が非単結晶半導体層の上下に接して設けられている。受光素子の構成は、これに限定されず、受光素子の一対の電極は、非単結晶半導体層の同じ面に接して形成されていてもよい。

20

#### 【0132】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

#### 【0133】

##### (実施の形態3)

本実施の形態では、本発明の一態様に係る半導体装置が透過型液晶表示領域を有する場合について説明する。なお本実施の形態において、実施の形態2と同じものは同じ符号で示し、その説明は省略する。

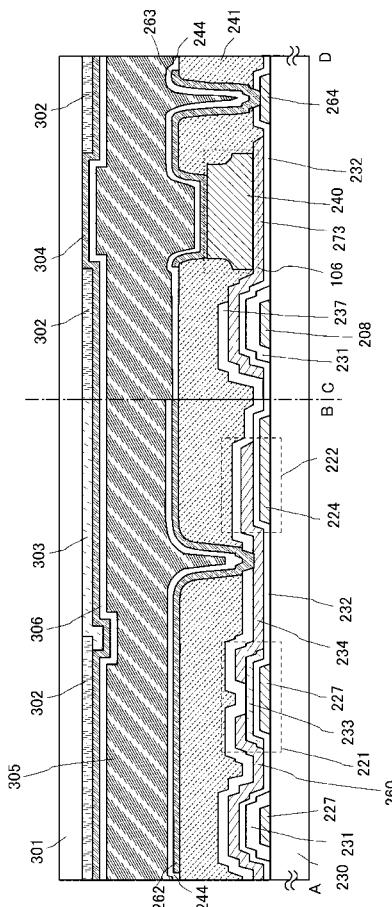

#### 【0134】

受光素子の半導体層として非単結晶半導体層を、トランジスタの半導体層として酸化物半導体層を用いる透過型液晶表示装置の一例について、図5を用いて説明する。図5におけるA-Bまでの領域は、単位画素の一部分を、C-Dまでの領域は、光センサ回路の一部分を示している。なお、単位画素及び光センサ回路は該構成に限定されない。

30

#### 【0135】

図5に示す半導体装置の絶縁層241は、凹凸を設げず、平坦な面を有するように形成する。

#### 【0136】

また図5に示す半導体装置では、図4の反射電極層242及び接続電極層243に代えて、透光性を有する導電膜にて、電極層262及び接続電極層263を形成する。アクティブマトリクス基板側に設けられたバックライトの光が受光素子106上の指などに反射し、反射した光が受光素子106に入射する。このようにして、光センサ回路によるセンシングを行うことができる。

40

#### 【0137】

以上説明したように、図5のような透光性を有する導電膜を画素電極とする半導体装置を得ることができる。

#### 【0138】

また、液晶層を挟む一対の電極を透光性を有する導電膜で形成し、当該一対の透光性を有する電極を、同一基板上に設けてもよい。これにより、IPSモード( In-Plane - Switching )などの横電界モードで液晶分子を駆動する半導体装置を得ることができる。

#### 【0139】

50

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

#### 【0140】

##### (実施の形態4)

本実施の形態では、画像表示を行う表示部を有する電気機器の一例を図6(A)及び図6(B)に示す。

#### 【0141】

図6に示す電気機器の構成例について説明する。電気機器1030の表示部1032はフォトセンサを用いるタッチ入力機能を有し、図6(A)に示すように表示部の領域1033にキーボードのボタン1031が複数表示される。表示部1032は表示領域全体を指しており、表示部の領域1033を含む。そして、使用者が所望のキーボードのボタンをタッチ入力し、表示部1032に入力結果の表示を行う。10

#### 【0142】

表示部の領域1033は静止画を表示しているため、書き込み時以外の期間では表示素子制御回路を非動作とすることで消費電力の節約ができる。

#### 【0143】

電気機器1030を使用している様子の一例を示す。例えば、表示部の領域1033に表示されているキーボードボタンを使用者の指を用いて順次触れる、または非接触で文字入力を行い、その結果表示される文章を表示部の領域1033以外の領域に表示する。使用者が画面のキーボードから指をはずし、フォトセンサの出力信号の検出されない期間が一定時間経つと自動的に表示部の領域1033に表示されていたキーボード表示が消され、表示部の領域1033にも入力された文章の表示が行われ、画面一杯に入力された文章を使用者は確認することができる。再度入力する場合には、表示部1032に使用者の指を用いて触れる、または非接触でフォトセンサの出力信号を検出させることで再び表示部の領域1033にキーボードボタンを表示し、文字入力を行うことができる。20

#### 【0144】

また、自動的ではなく、使用者が切り替えスイッチ1034を押すことによって、キーボード表示をなくし、図6(B)に示すように表示部1032の全体を静止画とすることもできる。また、電源スイッチ1035を押して電源を切っても、静止画を長時間維持することができる。また、キーボード表示スイッチ1036を押すことによってキーボードを表示し、タッチ入力可能な状態とすることができます。30

#### 【0145】

また、切り替えスイッチ1034、電源スイッチ1035、及びキーボード表示スイッチ1036は、表示部1032にそれぞれスイッチボタンとして表示し、表示されたスイッチボタンに触れることで、各操作を行ってもよい。

#### 【0146】

また、表示部の領域1033は静止画を表示することに限定されず、一時的、または部分的に動画表示してもよい。例えば、キーボードボタンの表示位置を使用者の好みに合わせて一時的に変更する、または非接触で入力した場合に入力されたかどうかが分かるように対応するキーボードボタンのみに部分的に表示の変化を与えてよい。40

#### 【0147】

また、電気機器1030は少なくともバッテリを有し、データ情報を保存するためのメモリ(Flash Memory回路、SRAM回路、DRAM回路など)、CPU(中央演算処理回路)やLogic回路を備えた構成とすることが好ましい。CPUやメモリを備えることにより、様々なソフトウェアのインストールが行え、パーソナルコンピュータの機能の一部または全部の機能を持たせることができる。

#### 【0148】

また、電気機器1030に対して、ジャイロスコープ、または3軸加速度センサなどの傾き検出部を設け、傾き検出部からの信号に応じて、電気機器1030で使用する機能、特に表示部での表示及び入力に係る機能を、演算回路により切り替えることができる。その50

ため、備え付けの操作キーのように入力キーの種類、大きさ、または配置が予め定まつたものとは異なり、使用者の利便性を向上させることができる。

#### 【0149】

上述した電気機器1030の表示部に、実施の形態1に示した回路構成を適用することにより、単位画素に対応するフォトセンサの面積を低減させ、単位画素の開口率を高めることができる。また、受光感度を高めても、単位画素に対応するフォトセンサの面積を低減させることができる。更に、電気機器1030におけるバックライトの消費電力を下げることができる。

#### 【0150】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

10

#### 【0151】

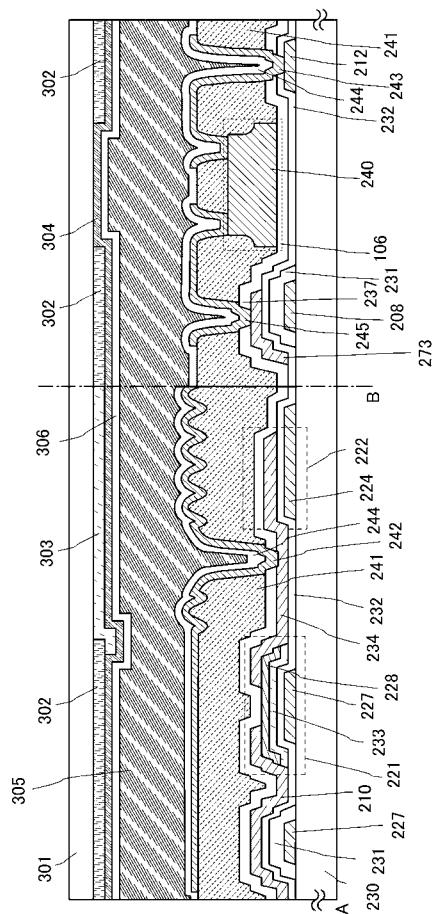

##### (実施の形態5)

本実施の形態では、実施の形態2で示した半導体装置とは異なる反射型液晶表示領域を有する半導体装置について、図7を用いて説明する。

#### 【0152】

受光素子の半導体層としては、非単結晶半導体層を用いている。なお、図4では、受光素子106は、電極層273、非単結晶半導体層240、及び接続電極層278が順に積層された構成である。すなわち、受光素子の一対の電極が非単結晶半導体層の上下に接して設けられている。本実施の形態の受光素子は、図4の構成と異なり、受光素子の一対の電極が、非単結晶半導体層の同じ面に接して形成されている例について示す。

20

#### 【0153】

図7は、図4と受光素子の周辺構造が異なるだけであるため、同一箇所の説明はここでは省略することとする。

#### 【0154】

実施の形態2では、非単結晶半導体層240の上下に一対の電極を配置する例を示したが、本実施の形態では、非単結晶半導体層240の上方に一対の電極を配置する例である。

#### 【0155】

図7の断面構造を得る手順の一部を以下に示す。

30

#### 【0156】

実施の形態2と同様の手順に従って、非単結晶半導体層240を形成する。そして、非単結晶半導体層240を覆う絶縁層241を形成した後、絶縁層241に非単結晶半導体層240に達する開口を複数形成する。そして、導電層を形成し、フォトリソグラフィ工程、及びエッティング工程を行うことで、非単結晶半導体層240上に接する接続電極層243と、非単結晶半導体層240上に接する接続電極層245とを形成する。また、接続電極層245は、絶縁層237に設けられた開口を介して、電極層273と電気的に接続されている。こうして、非単結晶半導体層240の上方に接続電極層243、及び接続電極層245を配置する受光素子を有する半導体装置が作製できる。

#### 【0157】

なお、図4に示す断面構造を得るために工程数と図7に示す断面構造を得るために工程数は同じであり、マスク数も同一である。ただし、図7に示す断面構造は、図4よりも開口の数は増加する。

40

#### 【0158】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

#### 【符号の説明】

#### 【0159】

11 光センサ回路

12 アンプ回路部

13 受光部

50

|       |            |    |

|-------|------------|----|

| 1 4   | デッドスペース    |    |

| 1 5   | 単位画素       |    |

| 1 0 0 | 表示部        |    |

| 1 0 1 | 画素回路       |    |

| 1 0 2 | 光センサ回路     |    |

| 1 0 3 | アンプ回路部     |    |

| 1 0 4 | 単位画素       |    |

| 1 0 5 | 受光部        |    |

| 1 0 6 | 受光素子       |    |

| 1 0 7 | 転送トランジスタ   | 10 |

| 1 0 8 | リセットトランジスタ |    |

| 1 0 9 | 増幅トランジスタ   |    |

| 1 1 0 | 選択トランジスタ   |    |

| 1 1 1 | トランジスタ     |    |

| 1 1 2 | 液晶素子       |    |

| 1 1 3 | 保持容量       |    |

| 2 0 1 | 電源線        |    |

| 2 0 4 | 選択信号線      |    |

| 2 0 7 | 信号線        |    |

| 2 0 8 | 信号線        | 20 |

| 2 0 9 | グランド線      |    |

| 2 1 1 | 走査線        |    |

| 2 1 2 | 信号線        |    |

| 2 1 3 | グランド線      |    |

| 2 1 4 | ノード        |    |

| 2 2 1 | トランジスタ     |    |

| 2 2 2 | 保持容量       |    |

| 2 2 3 | 液晶素子       |    |

| 2 2 4 | 容量配線       |    |

| 2 2 7 | 走査線        | 30 |

| 2 2 8 | 酸化物半導体層    |    |

| 2 3 0 | 基板         |    |

| 2 3 1 | 絶縁層        |    |

| 2 3 2 | ゲート絶縁層     |    |

| 2 3 3 | 酸化物半導体層    |    |

| 2 3 4 | 電極層        |    |

| 2 3 7 | 絶縁層        |    |

| 2 4 0 | 非単結晶半導体層   |    |

| 2 4 1 | 絶縁層        |    |

| 2 4 2 | 反射電極層      | 40 |

| 2 4 3 | 接続電極層      |    |

| 2 4 4 | 配向膜        |    |

| 2 4 5 | 接続電極層      |    |

| 2 6 0 | 信号線        |    |

| 2 6 2 | 電極層        |    |

| 2 6 3 | 接続電極層      |    |

| 2 6 4 | 電源線        |    |

| 2 7 3 | 電極層        |    |

| 2 7 8 | 電極層        |    |

| 3 0 1 | 基板         | 50 |

3 0 2 遮光層

3 0 3 カラーフィルタ

3 0 4 導電膜

3 0 5 液晶層

3 0 6 配向膜

3 1 1 光センサ回路

3 1 2 アンプ回路部

3 1 3 受光部

3 1 5 単位画素

1 0 3 0 電気機器

1 0 3 1 ボタン

1 0 3 2 表示部

1 0 3 3 領域

1 0 3 4 スイッチ

1 0 3 5 電源スイッチ

1 0 3 6 キーボード表示スイッチ

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

| (51) Int.CI.            | F I                   | テーマコード(参考) |

|-------------------------|-----------------------|------------|

| G 0 9 F 9/00 (2006.01)  | G 0 9 F 9/30 3 3 8    | 5 C 0 9 4  |

| G 0 6 F 3/042 (2006.01) | G 0 9 F 9/30 3 4 9 Z  | 5 F 1 1 0  |

| G 0 6 F 3/041 (2006.01) | G 0 9 F 9/00 3 6 6 A  | 5 G 4 3 5  |

|                         | G 0 6 F 3/042 4 7 2   |            |

|                         | G 0 6 F 3/041 3 2 0 A |            |

F ターム(参考) 5B087 AA03 AB04 CC02 CC24 CC33

5C024 CY42 CY47 CY50 EX32 GX14 GX16 GX18

5C094 AA10 AA15 AA22 AA44 BA03 BA43 DA09 EB05 FB02 FB14

5F110 AA09 AA30 BB01 BB10 CC07 DD01 DD02 DD13 DD14 DD15

DD17 EE02 EE03 EE04 EE06 EE14 FF03 FF04 FF05 GG01

GG07 GG12 GG13 GG14 GG15 GG19 GG58 HK01 HK02 HK03

HK04 HK06 HK21 HK22 HL02 HL03 HL04 HL06 HL11 NN03

NN04 NN23 NN34 NN71 NN73

5G435 AA03 AA16 AA17 BB12 HH13