(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5419103号

(P5419103)

(45) 発行日 平成26年2月19日(2014.2.19)

(24) 登録日 平成25年11月29日(2013.11.29)

(51) Int.Cl.

G06F 11/28 (2006.01)

G06F 9/38 (2006.01)

F 1

G06F 11/28 320E

G06F 9/38 380C

請求項の数 5 (全 29 頁)

(21) 出願番号 特願2010-526984 (P2010-526984)

(86) (22) 出願日 平成20年8月4日 (2008.8.4)

(65) 公表番号 特表2010-541067 (P2010-541067A)

(43) 公表日 平成22年12月24日 (2010.12.24)

(86) 國際出願番号 PCT/US2008/072109

(87) 國際公開番号 WO2009/045628

(87) 國際公開日 平成21年4月9日 (2009.4.9)

審査請求日 平成23年8月4日 (2011.8.4)

(31) 優先権主張番号 11/864,292

(32) 優先日 平成19年9月28日 (2007.9.28)

(33) 優先権主張国 米国(US)

(73) 特許権者 504199127

フリースケール セミコンダクター イン

コーポレイテッド

アメリカ合衆国 テキサス州 78735

オースティン ウィリアム キャノン

ドライブ ウエスト 6501

(74) 代理人 100142907

弁理士 本田 淳

(72) 発明者 モイヤー、ウィリアム シー。

アメリカ合衆国 78620 テキサス州

ドリッピング スプリングス メドウ

リッジ ドライブ 1111

審査官 大塚 俊範

最終頁に続く

(54) 【発明の名称】デバッグイベントを監視するためのシステム及び方法

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の命令について、フェッチ、デコード、および実行と、各命令の実行に関連した結果の書き込みとを連続的に行うことによって、複数の命令を実行するためのパイプライン・プロセッサと、

前記パイプライン・プロセッサに結合されており、前記複数の命令の実行を監視してデバッグイベントが発生する時を判定し、デバッグ例外を発生させて命令処理フローを中断するためのデバッグ回路と、を含むシステムであって、前記デバッグ回路は、前記デバッグイベントの発生から該デバッグイベントの発生に応じたデバッグ例外の発生までに書き戻しによって完了する命令の数のカウントを行うための制御回路をさらに含む、システム。

## 【請求項 2】

前記デバッグ回路の前記制御回路は、

前記デバッグイベントの発生から前記デバッグ例外の発生までに書き戻しによって完了する命令の数のカウントとしてカウント値を計数して与えるためのカウンタをさらに含む請求項 1 に記載のシステム。

## 【請求項 3】

前記デバッグ回路は、前記デバッグイベントの発生から前記デバッグ例外の発生までに書き戻しによって完了する命令の数のカウントを保持するためのフィールドを有するデバッグ状態レジスタをさらに含む、請求項 1 に記載のシステム。

**【請求項 4】**

前記デバッグ回路は、前記複数の命令のうちの1つのデコードを行うことと、前記パイプライン・プロセッサによって形成されたアドレスを1つ以上の所定のデバッグアドレスと比較してデータアドレース一致が発生したか否かを判定することと、前記パイプライン・プロセッサによってアクセスの行われたデータ値を1つ以上の所定のデータ値と比較してデータ値一致が発生したか否かを判定することとに応じて、デバッグイベントが発生したことを判定し、デバッグイベントは両比較演算について一致が発生することを必要とする、請求項1に記載のシステム。

**【請求項 5】**

複数の命令について、フェッチ、デコード、および実行と、各命令の実行に関連した結果の書き込みを連続的に行うことによって、複数の命令を実行するためのパイプライン処理回路と、

前記パイプライン処理回路に結合されており、1つ以上のデバッグアドレスを命令実行によって形成されるアドレスと選択的に比較することと、1つ以上のデバッグデータ値を命令実行によって形成されるデータと選択的に比較することによって、前記複数の命令の実行を監視するデバッグ回路と、を含むシステムであって、前記デバッグ回路は、両方の比較が一致を生じるときを判定し、該判定に応答してデバッグイベントの発生を示すことと、前記デバッグ回路は、前記デバッグイベントの発生から該デバッグイベントの発生に応じたデータ値ブレークポイントの発生までに実行される命令の数のカウントを行う、システム。

10

**【発明の詳細な説明】****【技術分野】****【0001】**

本開示は、一般的に、データ処理システムに関し、特に、デバッグイベントを監視するためのシステム及び方法に関する。

**【背景技術】****【0002】**

データ値ブレークポイントには、ブレークポイント例外を発生させるか否かを判定するために、データアクセスアドレスと、そのデータアクセスアドレスに関するデータとの両方の比較が含まれる。しかしながら、通常のパイプライン・プロセッサでは、データは、アクセスアドレスが利用可能になった後、何サイクルも経過するまで利用可能にならないことがある。従って、アクセスデータがまだ利用可能でないときにデータアクセスに続く1つ以上の命令が実行され得るので、命令ストリームのどこでブレークポイントが発生したか正確には不明である。現在利用可能なデータ処理システムには、アクセスデータがまだ利用可能でない間に命令が実行されないように、通常の実行に追加のストールを付加するものがある。しかしながら、このことは追加のオーバーヘッドを必要とし、また、通常の実行タイミングを乱すものであり、デバッグ時、望ましくないことがある。

20

**【図面の簡単な説明】****【0003】**

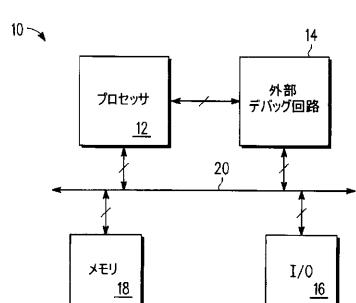

【図1】本発明の一実施形態に基づくデータ処理システムのブロック図。

40

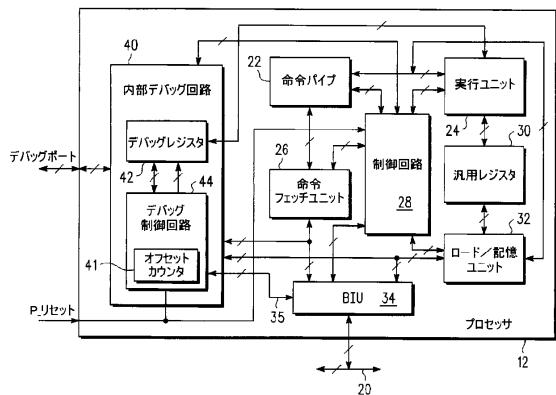

【図2】本発明の一実施形態に基づく、図1のデータ処理システムに関するプロセッサのブロック図。

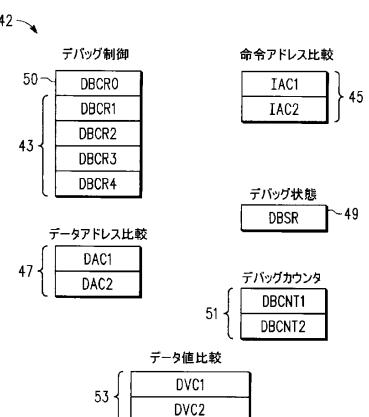

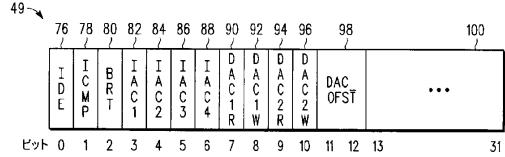

【図3】図1のデータ処理システムに関する代表的なデバッグレジスタを示す図。

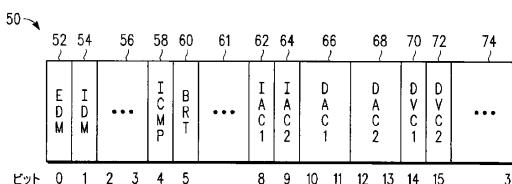

【図4】本発明の一実施形態に基づく、図3のデバッグレジスタに関するデバッグ制御レジスタの図。

【図5】本発明の一実施形態に基づく、図4のデバッグ制御レジスタの一部の機能を表形式で示す図。

【図6】本発明の一実施形態に基づく、図4のデバッグ制御レジスタの一部の機能を表形式で示す図。

【図7】本発明の一実施形態に基づく、図3のデバッグレジスタに関するデバッグ状態

50

レジスタの図。

【図 8】本発明の一実施形態に基づく、図 7 のデバッグ状態レジスタの一部の機能を表形式で示す図。

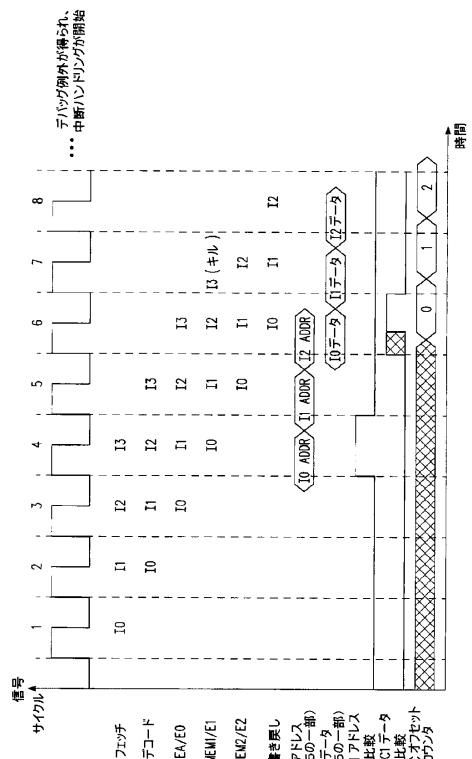

【図 9】図 2 のプロセッサの異なる動作例を示すタイミング図。

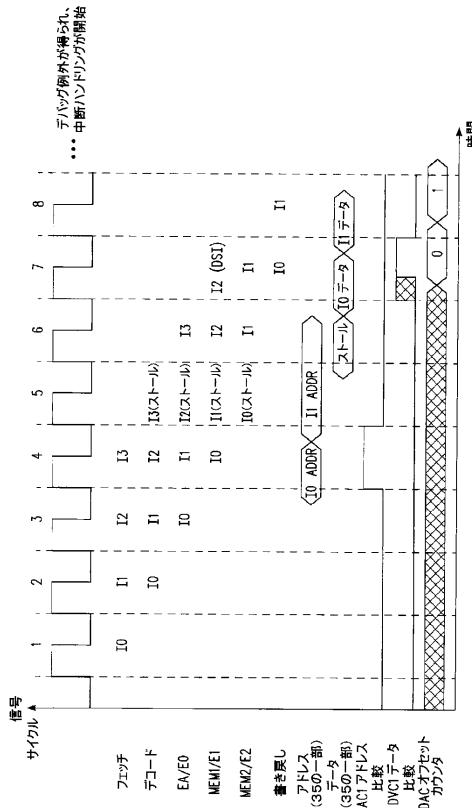

【図 10】図 2 のプロセッサの異なる動作例を示すタイミング図。

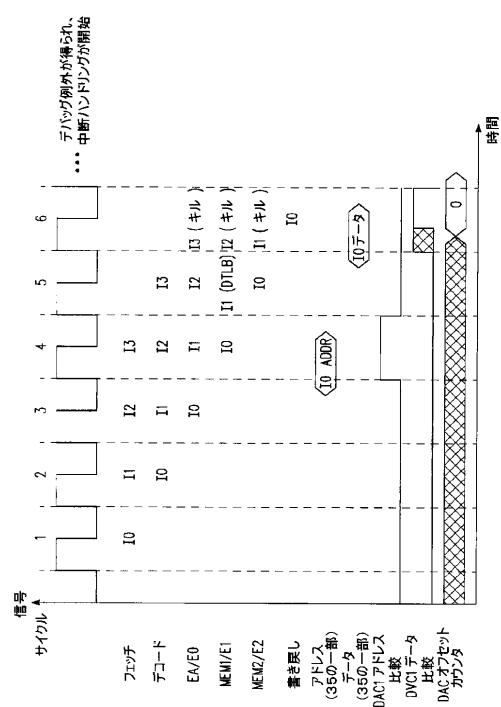

【図 11】図 2 のプロセッサの異なる動作例を示すタイミング図。

【図 12】様々な代表的なデータアドレス比較 (D A C) イベント及びそれらに対応する結果を表形式で示す図。

【図 13】様々な代表的なデータアドレス比較 (D A C) イベント及びそれらに対応する結果を表形式で示す図。 10

【図 14】様々な代表的なデータアドレス比較 (D A C) イベント及びそれらに対応する結果を表形式で示す図。

【図 15】様々な代表的なデータアドレス比較 (D A C) イベント及びそれらに対応する結果を表形式で示す図。

【図 16】様々な代表的なデータアドレス比較 (D A C) イベント及びそれらに対応する結果を表形式で示す図。

【図 17】本発明の一実施形態に基づく、図 3 のデバッグレジスタに関するデバッグ状態レジスタの図。

【図 18】図 2 のプロセッサの動作例を示すタイミング図。

【発明を実施するための形態】 20

【0004】

本発明は、一例として示すものであり、添付図によって限定されない。図では、同様な参照符号は、同様な要素を示す。図の要素は、簡単明瞭に示されており、必ずしも縮尺通りに描かれていない。

【0005】

コードのデバッグ時、実際にどの命令がデバッグ例外発生を引き起こしたか知ることは、困難であることが多い。例えば、データ値ブレークポイントの場合、データアクセスアドレスの比較及びアクセスしたデータとのデータ値の比較の双方が実施されるので、比較結果によって通常の命令ストリームの実行を中断するデバッグ例外を発生させことがある。アクセスに対するデータが、そのアクセスの開始から何サイクルも後に返されることがあるが、これは、データアクセス要求及びアクセスアドレスを供給することによって起こる。要求したアクセスに基づくデータアドレス比較と受信データに基づくデータ値比較との間の遅れにより、命令ストリーム中のどの命令が実際に命令ストリームを中断したか判定することは、格段に困難なことがある。一実施形態では、データ値ブレークポイントを引き起こした命令と命令ストリーム中におけるブレークポイント例外が実際に発生するポイントとの間で幾つの命令が実行されたかを示すために、オフセット値が用いられる。このようにして、デバッグ機能の改善が達成される。 30

【0006】

本明細書に用いる用語「バス」は、データ、アドレス、制御、又は状態等の、1つ又は複数の様々な種類の情報を伝達するのに用い得る複数の信号又はコンダクタ（導体）を参照するために用いる。本明細書で述べる導体は、単一の導体、複数の導体、单方向の導体、又は双方向の導体であることに関連して例示又は記述し得る。しかしながら、異なる実施形態では、導体の実装も異なり得る。例えば、双方向の導体よりもむしろ別個の单方向導体を用いたり、その逆の場合もあったりする。また、直列に又は時分割多重方式で複数の信号を伝達する单一の導体で複数の導体を置き換えることがある。同様に、複数の信号を搬送する单一の導体は、これらの信号の一部を搬送する様々な異なる導体に分離し得る。従って、信号を伝達するための多くのオプションが存在する。 40

【0007】

用語「アサート」又は「設定」と「ネゲート」（又は「ディアサート」又は「クリア」）は、信号、状態ビット、又は同様の装置をそれぞれその論理的に真又は論理的に偽の 50

状態にすることを参照する際に用いる。論理的に真の状態が論理レベル1である場合、論理的に偽の状態は、論理レベル0である。また、論理的に真の状態が論理レベル0である場合、論理的に偽の状態は、論理レベル1である。

#### 【0008】

本明細書に述べた各信号は、正又は負論理として構成し得る。この場合、負論理は、信号名称上のバー又は名称に続くアスタリスク記号(\*)によって示し得る。負論理信号の場合、信号は、アクティブ「ロー」であり、この場合、論理的に真の状態は、論理レベル0に対応する。正論理信号の場合、信号は、アクティブ「ハイ」であり、この場合、論理的に真の状態は、論理レベル1に対応する。本明細書で述べる信号は、いずれも負又は正のいずれかの論理信号として構成し得ることに留意されたい。従って、他の実施形態では、正論理信号として述べた信号は、負論理信号として実現してもよく、また、負論理信号として述べた信号は、正論理信号として実現してよい。10

#### 【0009】

角括弧は、本明細書では、バスの導体又は値のビット位置を示すために用いる。例えば、「バス60[7:0]」又は「バス60の導体[7:0]」は、バス60の8つの下位導体を示し、「アドレスビット[7:0]」又は「ADDRESS[7:0]」は、アドレス値の8つの下位ビットを示す。数に先行する記号「\$」は、その数が16進数、即ち、基數16の形式で表されることを示す。数に先行する記号「%」又は「0b」は、その数が2進数、即ち、基數2の形式で表されることを示す。

#### 【0010】

図1は、本発明の実施形態と整合性のあるデータ処理システム10を示す。データ処理システムは、システム・オン・チップであってよい。データ処理システム10は、単一の集積回路又は複数の集積回路上に実装し得る。データ処理システム10には、プロセッサ12、外部デバッグ回路14、I/Oモジュール16、及びメモリ18が含まれ、これらは、バス20を介して結合し得る。他の実施形態では、メモリ18は、任意の種類のメモリであってよく、また、プロセッサ12と同じ集積回路上に配置してもよく、又はプロセッサ12と異なる集積回路上に配置してもよい。メモリ18は、任意の種類のメモリであってよく、例えば、読み出し専用メモリ(ROM)、ランダムアクセスメモリ(RAM)、不揮発性メモリ(例えば、フラッシュメモリ)等であってよい。更に、メモリ18は、他の周辺装置もしくはスレーブ内又は異なる集積回路上に配置されたメモリ又は他のデータ記憶装置であってよい。2030

#### 【0011】

図2は、図1のデータ処理システム10に関係するプロセッサ12のブロック図である。プロセッサ12には、命令パイプ22、実行ユニット24、命令フェッチユニット26、制御回路28、汎用レジスタ30、ロード/記憶ユニット32、バス・インターフェイス・ユニット(BIU)34、及び内部デバッグ回路40を含み得る。プロセッサ12は、BIU(34)に結合したバス20を介して、データ処理システム10の他の構成要素と通信を行い得る。内部デバッグ回路40は、図2に示すデバッグポートを介して外部デバッグ処理ユニットに結合してよく、例えば、IEEE15001準拠のNexus(商標)デバッグ処理ユニットに結合してよい。Nexus(商標)は、テキサス州オースティン所在のフリースケール・セミコンダクタ(Freescale Semiconductor)社の商標である。デバッグポートは、JTAG等のシリアルインターフェイスであってよく、又はパラレルポート、シリアル及びパラレルポートの組合せ、又はイーサネット(登録商標)ポートとして実装してよい。内部デバッグ回路40には、デバッグレジスタ42及びデバッグ制御回路44を含み得る。デバッグ制御回路44には、1つ又は複数のオフセットカウンタ41を含んでもよく、これらは、デバッグイベントを引き起こした命令と、そのデバッグイベントが処理される時の命令実行中の一つのポイントとの間で命令実行を完了させる命令(存在する場合)の数を求めるために用い得る。デバッグレジスタ42には、命令ブレークポイント、データブレークポイント、ウォッチポイント、及びデバッグ処理に関連する他のメッセージ伝達を含む様々なデバッグ関連イ4050

メントを制御するためのフィールドにグループ分けされたビットを含み得る。これらのデバッガ処理資源は、プロセッサ 12 と外部デバッガ回路 14との間で共有し得る。更に、デバッガ制御回路 44 は、導体 35 を経由して B I U (34) とアドレス及びデータを通信し得る。

#### 【0012】

次に、図 3において、デバッガレジスタ 42 内のレジスタは、更に、命令及び / 又はデータアクセスブレークポイント及びウォッチポイントイベント、並びに他のデバッガ制御基準を実現するための 1つ又は複数のアドレス比較値、アドレス範囲、及びデータマッチ値を記憶するために提供し得る。これらのアドレス及びデータ値は、様々な制御基準値と共に用いられ、プロセッサ 12 が、ブレークポイント又はウォッチポイントイベントを発生させる目的で、1つ又は複数の所定の命令アドレス又はデータアドレスにいつアクセスするか判定される。これによって、内部デバッガモードが有効な場合、プロセッサ 12 は、デバッガ例外のための例外処理を開始することができるようになる。あるいは、外部デバッガモードが有効な場合、プロセッサ 12 は、デバッガ休止モードに入ることができるようになり、この場合、内部デバッガユニット 40 のデバッガポートを通して外部デバッガ回路 14 によって提供されたコマンドに応答する。一例として、デバッガレジスタ 42 には、様々なデバッガ制御レジスタを含んでよく、例えば、デバッガ制御レジスタ 50 (D B C R 0 ) 及び他のデバッガ制御レジスタ 43 (D B C R 1 、 D B C R 2 、 D B C R 3 、及び D B C R 4 ) を含んでよい。デバッガレジスタ 42 には、更に、命令アドレス比較レジスタ 45 (I A C 1 及び I A C 2 ) を含み得る。命令アドレス比較レジスタ 45 は、アドレス比較の目的のために命令アドレスを記憶し得る。デバッガレジスタ 42 には、更に、データアドレス比較レジスタ 47 (D A C 1 及び D A C 2 ) を含み得る。データアドレス比較レジスタ 47 は、アドレス比較の目的のためにデータアクセスアドレスを記憶し得る。デバッガレジスタ 42 には、更に、デバッガ状態レジスタ 49 、デバッガカウンタ 51 (D B C N T 1 及び D B C N T 2 ) 、及びデータ値比較レジスタ 53 (D V C 1 及び D V C 2 ) を含み得る。デバッガレジスタ 42 は、ユーザのソフトウェア・プログラミング・モデルの一部であってよい。デバッガカウンタ 51 は、1つ又は複数の計数割込可能なイベントが発生すると、カウントダウンするように構成し得る。カウント値が 0 に達すると、デバッガ計測イベントが通知され、割込可能ならば、デバッガ割込を生成し得る。データ値比較レジスタ 53 は、データ比較の目的のためにデータ値を記憶し得る。

#### 【0013】

内部デバッガモードにおいて、これらのレジスタ資源は、ソフトウェアによって管理され、外部デバッガ回路は、用いる必要が無い。ソフトウェアは、専用レジスタ命令への及び専用レジスタ命令からのムーブ (m o v e ) を用いたデータ移動によりレジスタを構成することができるが、これらの専用レジスタ命令は、ソフトウェアベースのデバッガ処理アクティビティを実施するために個々のデバッガレジスタを初期化するためのプログラマ・モデルのソフトウェア命令であり、この場合、割込可能なデバッガイベントによりソフトウェアデバッガ割込が発生する。すると、ソフトウェア割込ハンドラは、データ処理システム 10 のソフトウェア・プログラマによって判定される様々な所望のアクティビティを実施し得る。外部デバッガモードでは、外部デバッガ回路 14 は、これらの共有デバッガイベント設定レジスタの所有権を割り当てられ、また、設定されたデバッガイベントが発生すると、プロセッサ 12 は、休止状態に入り、コマンドが外部デバッガ回路 14 によって提供されるのを待つことができる。ソフトウェアは、外部デバッガモードが割込可能である場合、もはや共有デバッガ資源を制御しない。外部デバッガ回路 14 は、デバッガレジスタ 42 を含む共有デバッガ資源にデバッガポート (図 2 に示す) を介して直接アクセスすることができるが、デバッガポートは、例えば、J T A G T A P ポートとして実現し得る。一実施形態では、デバッガレジスタ 42 は、様々な J T A G 命令用の 1つ又は複数のフィールド内にレジスタ選択符号が含まれる J T A G データレジスタとしてマッピングし得るが、これら J T A G 命令は、J T A G I R 及び D R 動作を介したデバッガによるレジスタの読み込み及び書き出しが規定する。

10

20

30

40

50

## 【0014】

一組のレジスタを共有すると、実装すべきプロセッサ12の資源が低減され、これにより、データ処理システム10のユーザ向けのプログラミングモデルが簡素化される。内部デバッグユニット40は、プロセッサ12内のアクティビティを監視し、また、記憶したデバッグ設定情報に基づく1つ又は複数の所定条件の検出に応じて、1つ又は複数のデータブレークポイントイベント、命令ブレークポイントイベントを発生させることができ、更に、分岐又はトラップ発生イベント、命令完了イベント等の命令実行イベントを発生させることができる。このような動作では、プロセッサ12は、当業者が認識できるように機能する。

## 【0015】

図4は、図1のデータ処理システムに関するデバッグ制御レジスタ50の図である。デバッグ制御レジスタ50は、デバッグレジスタ42の一部として含むことができ、デバッグレジスタ42は、更に、内部デバッグユニット40の一部として含み得る。デバッグ制御レジスタ50は、デバッグ設定情報を記憶するために用い得る。図4は、特定のビットフィールドを用いる本発明の特定の実施形態を示すが、本発明の他の実施形態では、各フィールドに様々な数のビットを有する異なるビットフィールドを用い得る。図4に示す特定のビットフィールドは、例示のみの目的で示す。一例として、デバッグ制御レジスタ50には、32ビットを含み得る。デバッグ制御レジスタ50には、EDM(52)、IDM(54)、ICMP(58)、BRT(60)、IAC1(62)、IAC2(64)、DAC1(66)、DAC2(68)、DVC1(70)、及びDVC2(72)と表記したビットフィールドを含み得る。これらのビットフィールドは、単なる例であり、デバッグ制御レジスタ50には、これより少ない又は追加のビットフィールドを含み得る。更に、これらのビットフィールドは、様々に構成し得る。デバッグ制御レジスタ50には、更に、将来用い得る予約ビットフィールド56、61、及び74を含み得る。様々なビットフィールドの機能は、図5及び図6で後述する。一例として、デバッグ制御レジスタ50は、書き可能レジスタであってよく、更に読み込み可能であってもよいが、これは、ユーザのソフトウェア・プログラミング・モデルの一部であってよい。本発明の他の実施形態では、デバッグ制御レジスタ50は、ユーザのソフトウェア・プログラミング・モデル内の制御レジスタでなくてよいが、その代わり、ユーザのソフトウェア・プログラミング・モデル外に実装してよい。任意の種類の記憶回路をデバッグ制御レジスタ50の実現のために用い得る。

## 【0016】

図5は、図4のデバッグ制御レジスタ50の一部の機能を表形式で示す。EDMビット52は、外部デバッグモードが有効か無効かを示し得る。例えば、EDMビット52を1に設定すると、デバッグ制御レジスタ50等の制御レジスタは、外部デバッグ回路14の排他的制御下に置かれ、データ処理システム10のソフトウェアは、これらの制御レジスタに情報を書き込めない。他の選択肢として、EDMビット52を1に設定すると、ソフトウェアは、デバッグ制御レジスタの特定の部分に書き込めない。従って、EDMビット52は、デバッグ制御及びセットアップ情報を含み得るデバッグ制御レジスタ50及び他のデバッグ資源に記憶された情報が何らかのリセットイベントにより消去されるのを選択的に阻止するために用いられる。IDMビット54は、内部デバッグモードが有効か無効かを示し、従って、デバッグ例外が有効か無効かを示し得る。ICMPビット58は、命令完了デバッグイベントが有効か無効かを示すために用い得る。BRTビット60は、分岐発生デバッグイベントが有効か無効かを示すために用い得る。ビット6:7(61)は、将来の用途のために予約し得る。次に、図6を参照すると、図6は、図4のデバッグ制御レジスタ50の一部の機能を表形式で示す。IAC1ビット62は、命令アドレス比較1デバッグイベントが有効か無効かを示すために用い得る。IAC2ビット62は、命令アドレス比較2デバッグイベントが有効か無効かを示すために用い得る。DAC1ビット66は、データアドレス比較1デバッグイベントが有効か無効かを示すために用い得る。有効な場合、DAC1ビット66は、更に、どの種類の記憶アクセスに対してデータアド

10

20

30

40

50

レス比較 1 デバッグイベントが有効かを示す（例えば、記憶（ストア）型のデータ記憶アクセス、ロード型のデータ記憶アクセス、又はロード型もしくは記憶型両方のデータ記憶アクセス）。D A C 2 ビット 6 8 は、データアドレス比較 2 デバッグイベントが有効か無効かを示すために用い得る。有効な場合、D A C 2 ビット 6 8 は、更に、どの種類の記憶アクセスに対してデータアドレス比較 1 デバッグイベントが有効かを示す（例えば、記憶型のデータ記憶アクセス、ロード型のデータ記憶アクセス、又はロード型もしくは記憶型両方のデータ記憶アクセス）。D V C 1 ビット 7 0 は、データ値比較 1 修飾子が有効か否かを示すために用い得る。D V C 2 ビット 7 2 は、データ値比較 2 修飾子が有効か否かを示すために用い得る。ビット 1 6 : 3 1 は、将来の用途のために予約し得る。図 5 及び 6 は、デバッグイベントに関する異なる設定情報を提供するための特定の数のビットフィールドについて述べるが、これらの図に示したものと異なる数のビットフィールドも用いてよい。

10

#### 【 0 0 1 7 】

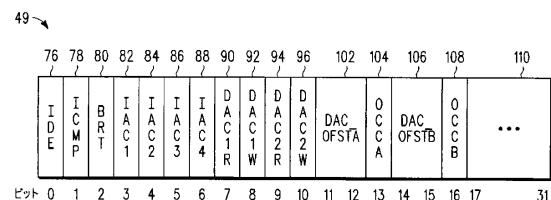

図 7 は、図 1 のデータ処理システムに関するデバッグ状態レジスタ 4 9 の図である。デバッグ状態レジスタ 4 9 は、デバッグレジスタ 4 2 の一部として含むことができ、デバッグレジスタ 4 2 は、更に、内部デバッグユニット 4 0 の一部として含み得る。デバッグ状態レジスタ 4 9 は、デバッグイベントに関する状態情報を記憶するために用い得る。図 7 は、特定のビットフィールドを用いる本発明の特定の実施形態を示すが、本発明の他の実施形態は、各フィールドに様々な数のビットを有する異なるビットフィールドを用い得る。図 7 に示す特定のビットフィールドは、例示だけの目的で示す。一例として、デバッグ状態レジスタ 4 9 には、3 2 ビットを含み得る。デバッグ状態レジスタ 4 9 には、I D E ( 7 6 )、I C M P ( 7 8 )、B R T ( 8 0 )、I A C 1 ( 8 2 )、I A C 2 ( 8 4 )、I A C 3 ( 8 6 )、I A C 4 ( 8 8 )、D A C 1 R ( 9 0 )、D A C 1 W ( 9 2 )、D A C 2 R ( 9 4 )、D A C 2 W ( 9 6 )、及び D A C \_ O F S T ( 9 8 ) と表記したビットフィールドを含み得る。これらのビットフィールドは、単なる例であり、デバッグ状態レジスタ 4 9 には、これより少ない又は追加のビットフィールドを含み得る。更に、これらのビットフィールドは、様々に構成し得る。デバッグ状態レジスタ 4 9 には、更に、将来用い得る予約ビットフィールド 1 0 0 を含み得る。様々なビットフィールドの機能は、図 8 で以下に述べる。更に、デバッグ状態レジスタ 4 9 において、ビットの設定は、論理レベル 1 の書きを意味し、ビットのクリアは、論理レベル 0 の書きを意味する。一例として、デバッグ状態レジスタ 4 9 は、そのビットがハードウェアを介して設定され、ソフトウェアを介して読み込みクリアされるレジスタであってよく、また、ユーザのソフトウェア・プログラミング・モデルの一部であってよい。本発明の他の実施形態では、デバッグ状態レジスタ 4 9 は、ユーザのソフトウェア・プログラミング・モデル内になくてもよく、その代わり、ユーザのソフトウェア・プログラミング・モデル外に実装してもよい。一実施形態では、デバッグ状態レジスタ 4 9 のデバッグ状態ビットは、内部デバッグモードが有効か又は外部デバッグモードが有効の間だけデバッグイベントによって設定される。また、一実施形態では、デバッグ割込が有効な場合、デバッグ状態レジスタ 4 9 の設定済みビットによって、デバッグ割込を生成し得るが、この場合、デバッグ割込ハンドラが、通常実行に戻る前に、デバッグ状態レジスタ 4 9 のビットをクリアする役割を担っている。更に、任意の種類の記憶回路を用いて、デバッグ状態レジスタ 4 9 を実現し得る。

20

30

40

#### 【 0 0 1 8 】

図 8 は、図 7 のデバッグ状態レジスタ 4 9 の機能を表形式で示す。I D E ビット 7 6 は、曖昧なデバッグイベントの発生を示すために用いられ、従って、デバッグ例外が無効であり、且つ、デバッグイベントによってそのそれぞれのデバッグ状態レジスタビットが 1 に設定される場合、1 に設定されることがある。即ち、デバッグイベントは、起こり得るが、デバッグ例外は、パイプラインの現在の状態により割込がまだ起こり得ないことから、無効のままであり得る。I C M P ビット 7 8 は、命令完了デバッグイベントが発生した場合、1 に設定し得る。B R T ビット 8 0 は、分岐発生デバッグイベントが発生した場合、1 に設定し得る。I A C 1 ビット 8 2 は、I A C 1 デバッグイベントが発生した場合、

50

1に設定し得る。IAC2ビット84は、IAC2デバッグイベントが発生した場合、1に設定し得る。IAC3ビット86は、IAC3デバッグイベントが発生した場合、1に設定し得る。IAC4ビット88は、IAC4デバッグイベントが発生した場合、1に設定し得る。DAC1Rビット90は、DAC1ビット66が%10又は%11に等しい(図6に示すように、DAC1デバッグイベントがロード型のデータ記憶アクセスに対して有効であることを示す)間に、読み込み型のDAC1デバッグイベントが発生した場合、1に設定し得る。DAC1Wビット92は、DAC1ビット66が%01又は%11に等しい(図6に示すように、DAC1デバッグイベントが記憶型のデータ記憶アクセスに対して有効であることを示す)間に、書き込み型のDAC1デバッグイベントが発生した場合、1に設定し得る。DAC2Rビット94は、DAC2ビット68が%10又は%11に等しい(図6に示すように、DAC2デバッグイベントがロード型のデータ記憶アクセスに対して有効であることを示す)間に、読み込み型のDAC2デバッグイベントが発生した場合、1に設定し得る。DAC2Wビット96は、DAC2ビット68が%01又は%11に等しい(図6に示すように、DAC2デバッグイベントが記憶型のデータ記憶アクセスに対して有効であることを示す)間に、書き込み型のDAC2デバッグイベントが発生した場合、1に設定し得る。DAC\_OFSTビット98は、データアドレス比較オフセットを示すために用い得る。一実施形態では、ビット13乃至31は、考えられる将来の用途のために予約される。

#### 【0019】

DAC1又はDAC2用にデータ値比較修飾子が、デバッグ制御レジスタ50に示されている場合、DVC1 DAC1又はDVC2 DAC2デバッグイベントを示すために、データアクセスアドレスの一一致並びにデータ値の一一致(そのデータアクセスアドレスに関係するデータ値に対する)が起こらなければならない。即ち、それぞれDAC1Rビット90、DAC1Wビット92、DAC2Rビット94、及びDAC2Wビット96は、データ値も一致するまで、DVC1 DAC1又はDVC2 DAC2デバッグイベントを示すようには設定されない。尚、一致すべき値は、データアドレス比較レジスタ47及びデータ値比較レジスタ53等のデバッグレジスタ42に記憶し得る。例えば、デバッグ制御レジスタ50のDVC1ビット70を設定する場合、DAC1デバッグイベントは、データ値比較によって限定される。これは、DVC1 DAC1デバッグイベントを示すには、アドレスがDAC1データアドレス比較レジスタに一致しなければならず、また、そのアドレスに対する関連データ値が、DVC1データ値比較レジスタに一致しなければならないことを意味する。しかしながら、プロセッサ12のパイプラインの性質により、データは、アクセスアドレスが利用可能になった後何サイクルも比較に利用できることがある。更に、データが利用可能になりDVC DACが示されても、その瞬間に命令ストリームが割込可能でないことがある(即ち、デバッグ例外が無効である可能性がある)。これは、実際のデータ値ブレークポイントが、DVC DACが示される瞬間に起こり得ないことを意味する。この場合、IDEビット76は、デバッグイベントが示された時、デバッグ例外が起こり得ないという曖昧なデバッグイベントを示ために1に設定し得る。即ち、実際のデータ値ブレークポイントは、デバッグ例外が有効になるまで起こり得ず、これは、図9乃至11を参照して説明するように、後続の命令ストリームにおける様々な(及び予測不可能な)ポイントで起こり得る。デバッグ例外が起こると、割込処理が始まり、デバッグイベントが処理される。

#### 【0020】

従って、DAC\_OFSTビット98を用いると、DVC DACを示させた命令と、データ値ブレークポイントが起こり且つデバッグ例外が発生するポイントと、の間に実行される命令の数を示し得る。DAC\_OFSTビット98は、データアドレス比較デバッグ例外を起こしたロード又は記憶(ストア)命令のアドレスからのセーブしたDSRR0値の「オフセット-1」を記憶するために用い得る。尚、DSRR0は、デバッグセーブ復旧レジスタ0に対応し、セーブしたDSRR0値は、ブレークポイント割込用の復帰ポインタに対応する。従って、データ値ブレークポイントが発生した場合、セーブしたDS

R R 0 アドレス値は、割込処理前に実行された最後の命令に続く命令のアドレス値に対応する。このようにして、D V C 1 D A C 1を引き起こしたアドレスと、命令ストリームが中断されデータ値ブレークポイントが生じるポイントとの間で幾つの命令が実行されたかを求めることができる。これによって、ユーザは、どの命令が実際にデータ値ブレークポイントを引き起こしたか判定し得る。一実施形態では、D A C \_ O F S T ビット9 8は、通常% 0 0に設定され、D V C D A Cは、このフィールドを、「オフセット - 1」を表す% 0 1、% 1 0、又は% 1 1に設定する。図9乃至1 1に関して、後で例を示す。しかしながら、アクセス許可エラー又は他のアクセス関連エラーにより、同時変換索引バッファミス(D T L B エラーとも称する)又はデータ記憶割込(例えば、D S I )エラーが起きた場合、D A C \_ O F S T ビット9 8は、% 0 0に設定され、I D E ビット7 6は、1に設定し得ることに留意されたい。これらの場合、これらのエラーの内の1つが起こることにより、そのアドレスに関するデータは、決して利用可能になり得ないことに留意されたい。

10

#### 【0 0 2 1】

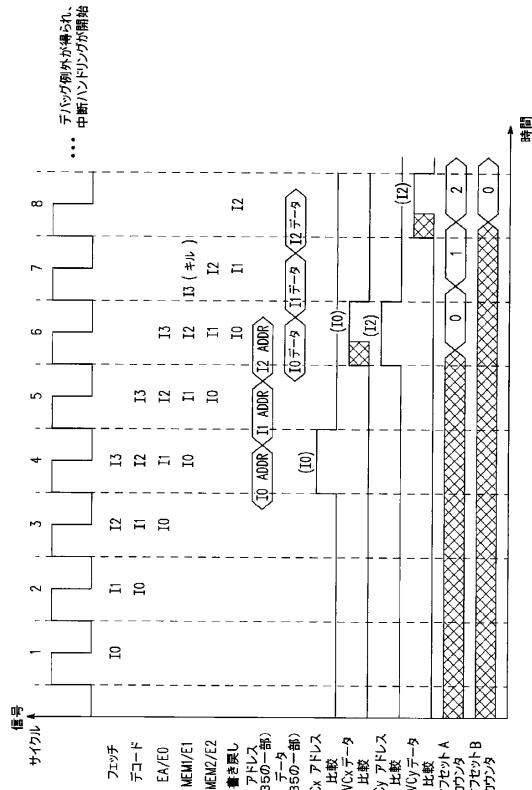

様々な状況及び条件が、データアドレス比較を実施する時とデータ値ブレークポイントが実際に発生する時との間に実行される命令の数に影響を及ぼし得る。図9乃至1 1が示すタイミング図は、どのように一連の4つのロード命令(I 0、I 1、I 2、及びI 3、によって表され、この場合、I 0がD V C D A C デバッグイベントを発生させる)が異なるD A C オフセット値をもたらすかを表す。これらのD A C オフセット値は、D A C オフセットカウンタ4 1によって追跡し得るが、I 0と、I 0のD V C D A C が示された後、データ値ブレークポイントのデバッグ例外が起こる時点と、の間で実行される命令の数を表す又は符号化する。図9乃至1 1の場合、I 0が、D V C 1 D A C 1 デバッグイベントを発生させると仮定する。従って、D A C 1 ビット6 6は、% 1 0又は% 1 1であり、D A C 1 デバッグイベントが読み型のデータ記憶アクセスに対して有効であり、D V C 1 ビット7 0は、D A C 1 デバッグイベントがデータ値比較によって限定されることを示すように設定される。I 0のD V C 1 D A C 1 デバッグイベントに対応する状態ビットは、D A C 1 R ビット9 0であり、これは、同じアクセスに関するアドレス値比較及びデータ値比較の各々が一致するまで設定されない。尚、本例では、データアドレス比較の場合、データアドレス比較レジスタ4 7のD A C 1 値は、I 0によって演算されたデータアドレスとの比較に用い得る。また、データ値比較の場合、データ値比較レジスタ5 3のD V C 1 値は、I 0に関する読み込み結果のデータとの比較に用い得ることに留意されたい。

20

30

30

他の実施形態では、I 0は、D A C 2 ビット6 8、D V C 2 ビット7 2、D A C 2 R ビット9 0等を用いて、D A C 2 D V C 2 に対応してもよい。

#### 【0 0 2 2】

図9乃至1 1の各々は、六段パイプラインについて例示しており、これらの段には、フェッチ、デコード、有効アドレス(E A) / E 0、メモリ1(m e m 1) / E 1、メモリ2(m e m 2) / E 2、及び書き戻しを含むことに留意されたい。これは、プロセッサ1 2の命令パイプ2 2のパイプライン例として提供されるが、他の実施形態には、例えば、異なる数の段を有する異なるパイプラインを含んでもよいことに留意されたい。図9乃至1 1で参照される六段パイプライン等の命令パイプラインの動作は、当分野で公知であり、従って、本明細書では詳述しない。更に、図9乃至1 1の各々には、プロセッサ1 2のプロセッサ・クロックに対応し得るクロック信号が含まれる。プロセッサ・クロックは、システムクロック又はプロセッサ1 2の一部だけに供給されるクロックであってよく、当分野で公知なように生成し得る。

40

#### 【0 0 2 3】

図9において、I 0は、クロックサイクル1においてフェッチ段に入り、クロックサイクル2においてデコード段に入り、クロックサイクル3においてE A / E 0段に入り、ここでI 0の有効アドレスが計算され、そして、クロックサイクル4においてm e m 1 / E 1段に入る。従って、有効アドレスは、クロックサイクル3の終わりに準備が整っており、導体3 5のアドレス部でデバッグ制御回路4 4に提供され、I 0の有効アドレスとデー

50

タアドレス比較レジスタ47に記憶されたD A C 1値との間でアドレス比較を実施できるようにする(尚、この時点で、B I U(34)によってバス20上にもアドレスを配置し得る)。このD A C 1アドレス比較は、D A C 1アドレス比較信号の正のパルスによって示されるように、クロックサイクル4において実施するが、D A C 1アドレス比較信号は、命令I0に対してD A C 1アドレス比較の一致が起こっていることを示すためにデバッグ制御回路44内でアサートされる制御信号であってよい。しかしながら、D A C 1は、D V C 1修飾子を必要とすることから(D V C 1ビット70の設定により)、D A C 1 Rデバッグイベントは、アドレス比較が一致してもまだ示されない。命令処理は、I0に関係する(I0ロード命令に応じて検索される)データがまだデータ値比較のために利用可能でないため、継続する。次に、I0は、m e m 2 / E 2段に進み、この間、データがメモリ(例えば、図1のメモリ18等)から読み込まれる。この読み込んだデータは、この段の終わりで利用可能となり得る(また、例えば、バス20を介してB I U(34)によって受信される)。そして、導体35のデータ部でデバッグ制御回路44に提供され、I0に関連する読み込んだデータ値とデータ値比較レジスタ53に記憶されたD V C 1値との間でデータ値比較を実施できるようにする。従って、データ値比較は、D V C 1データ比較信号の正のパルスによって示されるように、次のクロックサイクルであるクロックサイクル6において実施するが、D V C 1データ比較信号は、命令I0に関してD V C 1データ比較の一致が起こっていることを示すためにデバッグ制御回路44内でアサートされる制御信号であってよい。データ値比較レジスタ53に記憶したD V C 1値に一致するD V C 1 D A C 1デバッグイベントが示され、従って、ハードウェアが、D A C 1 Rビット90を設定する。

#### 【0024】

サイクル6内においてI0上でD V C 1 D A C 1を検出すると、D A Cオフセットカウンタが0にクリアされ、また、後続の各完了した命令の計数が開始できるようになることに留意されたい。しかしながら、パイプラインは、I1及びI2がメモリ段(m e m 1及びm e m 2)にあるため、クロックサイクル6ではまだ中断できない。従って、I1及びI2は、メモリアクセスが開始されると、中断できず、完了しなければならないことから、待ち状態のデバッグ例外を更に処理する前に完了しなければならない。後続のメモリアクセスは、しかしながら、D V C 1 D A C 1例外が現在待ち状態であることから、起動されない。I1及びI2の各メモリアクセスは、書き戻し段に入った後、完了と見なされる。I2(命令I1及びI2の後側)は、クロックサイクル8の書き戻し段にあり、その後、待ち状態のデバッグ例外を発生させることができ、割込処理を開始できることに留意されたい。即ち、D V C 1 D A C 1デバッグイベントの割込処理は、クロックサイクル8の後(例えば、クロックサイクル9)まで開始されない。D V C 1 D A C 1を検出する時点で、I3は、まだパイプラインのE A / E 0段にあり、従って、キルし得ることに留意されたい。即ち、命令ストリームは、I3において中断される(即ち、デバッグ例外は、I2の実行後、I3の実行前に起こる)。通常の実行は、従って、割込処理の完了後に、I3で再開し得る。従って、D S R R 0レジスタは、I3のアドレスを記憶し得るが、その理由は、これが、データブレークポイントデバッグ割込の復帰ポインタに対応するためである。デバッグ割込ハンドラのソフトウェア・ルーチンの完了に続いて、通常の実行は、割込命令からの復帰を実行することによって再開されるが、通常の(非割込)命令実行を継続するために、復帰すべき命令(この場合、I3)へのポインタとしてD S R R 0にセーブした値が用いられる。

#### 【0025】

D V C 1 D A C 1デバッグイベントを検出してD A Cオフセットカウンタをクリアした後、後続の各命令が完了した状態で、D A Cオフセットカウンタは、デバッグ例外が発生する(この時点で割込処理が起こる)まで、1ずつ増加することに留意されたい。従って、D A Cオフセットカウンタは、後続の命令I1及びI2が、それぞれクロックサイクル7及び8で完了することから、クロックサイクル8において2まで増加し、従って、デバッグ状態レジスタ49のD A C\_O F S Tビット98は、%10に設定される。即ち、

DVC1 DAC1を引き起こした命令（本例では、I0）の後で且つデバッグイベント割込処理に先立って実行される命令の数は、2であり、これは、DAC\_OFSTとして記憶される。この場合、ユーザは、データ値ブレークポイントが発生すると、そのデータ値ブレークポイントを実際に引き起こしたのは、前の命令（本例では、I2）ではなく、I2から更に2命令前であることを知ることができる（ここで、この値「2」は、DAC\_OFSTに対応する）。I2から更に2命令前の命令は、I0であり、本例においてデータ値ブレークポイントを引き起こしたのは、これである。DAC\_OFSTビット98に関して上述したように、DVC DACが起こると、これは、DACデバッグ例外を起こした命令（これは、I0である）のアドレスからのセーブしたDSRR0値の「オフセット-1」を示す。I0からのセーブしたDSRR0値（本例では、I3のアドレスに対応する）のオフセットは、3であり、従って、DAC\_OFSTビット98は、2を示すが、これは、「3-1」である。他の実施形態では、DAC\_OFSTを計算するために異なる境界を用いることが可能であり、あるいは、異なる計数方法を用いて、DAC\_OFSTが本例のI0を示すようにしてよいことに留意されたい。

10

#### 【0026】

図10において、I0は、クロックサイクル1においてフェッチ段に入り、クロックサイクル2においてデコード段に入り、クロックサイクル3においてEA/E0段に入り、ここでI0の有効アドレスを計算し、そして、クロックサイクル4においてmem1/E1段に入る。有効アドレスは、導体35のアドレス部でデバッグ制御回路44に提供され、I0の有効アドレスとデータアドレス比較レジスタ47に記憶されたDAC1値との間でアドレス比較を実施できるようにする。I0に対するこのDAC1アドレス比較は、クロックサイクル4において実施され、DAC1アドレス比較信号の正のパルスによって示されるように、アドレス比較の一致が起こる。しかしながら、DAC1は、DVC1修飾子を必要とすることから（DVC1ビット70の設定により）、DAC1Rデバッグイベントは、アドレス比較が一致してもまだ示されない。命令処理は、I0に関係する（I0ロード命令に応じて検索される）データが、まだデータ値比較に利用可能でないため、継続する。次に、I0は、mem2/E2段に進み、この間、データをメモリ（例えば、図1のメモリ18等）から読み込む。しかしながら、クロックサイクル5では、I0用の読み込みデータは、メモリ待ち状態によってストールされる（I0のストールは、パイプラインのストールになり、この場合、I1乃至I3は、各々、クロックサイクル5でストールすることに留意されたい）。従って、I0用の読み込みデータは、クロックサイクル5の終わりに提供される（図9のように）のではなく、クロックサイクル6の終わりまで、導体35のデータ部でデバッグ制御回路44に提供されない。次に、データ値比較は、次のクロックサイクルであるクロックサイクル7において実施され、DVC1データ比較信号の正のパルスによって示されるように、データの一致が起こる。データ値比較レジスタ53に記憶されたDVC1値に一致すると、DVC1 DAC1デバッグイベントが示され、従って、ハードウェアは、DAC1Rビット90を設定する。

20

30

#### 【0027】

サイクル7内においてI0上でDVC1 DAC1を検出すると、DACオフセットカウンタが0にクリアされ、また、後続の各完了した命令の計数が開始できるようになることに留意されたい。しかしながら、パイプラインは、I1がメモリ段(mem2)にあるため、クロックサイクル7ではまだ中断できない。従って、I1は、メモリアクセスが開始されると、中断することはできず、完了しなければならないことから、待ち状態のデバッグ例外の更なる処理に先立って、これを完了しなければならない。後続のメモリアクセスは、しかしながら、DVC1 DAC1例外が現在待ち状態であることから、起動されない。しかしながら、図10の例では、命令I2は、アクセス許可が破られ且つメモリがI2の読み込みデータを何も返さないことを示すDSIエラーを返す。従って、I2もメモリ段(mem1)にあるが、DSIエラーによりキルし得る。I3は、EA/E0段にあり、通常パイプライン段mem1で起こるメモリアクセスをまだ開始していないことから、同様にキルし得る。命令I1は、クロックサイクル8において書き戻し段にあり、この後

40

50

、待ち状態のデバッグ例外を更に処理することができ、これによりデバッグ例外を発生させて割込処理を開始し得る。即ち、DVC1 DAC1 デバッグイベントの割込処理は、クロックサイクル 8 の後（例えば、クロックサイクル 9）まで開始されない。従って、命令ストリームは、I2において中断される（即ち、デバッグ例外は、I1の実行後、I2の実行に先立って起こる）。そして、通常の実行は、デバッグ割込用の割込処理の完了後に、I2から再開し得る。従って、DSRR0 レジスタは、I2のアドレスを記憶し得るが、その理由は、これが、データブレークポイントデバッグ割込の復帰ポインタに対応するためである。デバッグ割込ハンドラのソフトウェア・ルーチンの完了に続いて、通常の実行は、割込命令からの復帰を実行することによって再開されるが、通常の（非割込）命令実行を継続するために、復帰すべき命令（この場合、I2）へのポインタとして DSRR0 にセーブした値が用いられる。10

#### 【0028】

DVC1 DAC1 を検出して DAC オフセットカウンタをクリアした後、後続の各命令が完了した状態で、DAC オフセットカウンタは、デバッグ例外が発生する（この時点で割込処理が起こる）まで、1ずつ増加することに留意されたい。従って、本例では、DAC オフセットカウンタは、1だけ増加し、従って、デバッグ状態レジスタ 49 の DAC\_OFST ビット 98 が %01 に設定される。即ち、DVC1 DAC1 を引き起こした命令（本例では、I0）の後で且つデバッグイベント割込処理前に実行される命令の数は、1であり、これは、DAC\_OFST として記憶される。この場合、ユーザは、データ値ブレークポイントが発生すると、そのデータ値ブレークポイントを実際に引き起こしたのは、前の命令（本例では、I1）ではなく、I2 から更に 1 命令前であることを知ることができる。I1 から更に 1 命令前の命令は、I0 であり、本例においてデータ値ブレークポイントを引き起こしたのは、これである。DAC\_OFST ビット 98 に関して上述したように、DVC DAC が起こると、これは、DAC デバッグ例外を起こした命令（これは、I0 である）のアドレスからのセーブした DSRR0 値の「オフセット - 1」を示す。I0 からのセーブした DSRR0 値（本例では、I2 のアドレスに対応する）のオフセットは、2 であり、従って、DAC\_OFST ビット 98 は、1を示すが、これは、「2 - 1」である。他の実施形態では、DAC\_OFST を計算するために異なる境界を用いることが可能であり、あるいは、異なる計数方法を用いて、DAC\_OFST が本例の I0 を示すようにしてもよいことに留意されたい。2030

#### 【0029】

図 11において、I0 は、クロックサイクル 1 においてフェッチ段に入り、クロックサイクル 2 においてデコード段に入り、クロックサイクル 3 において EA/E0 段に入り、ここで I0 の有効アドレスを計算し、また、クロックサイクル 4 において mem1/E1 段に入る。有効アドレスは、導体 35 のアドレス部でデバッグ制御回路 44 に提供され、I0 の有効アドレスとデータアドレス比較レジスタ 47 に記憶された DAC1 値との間でアドレス比較を実施できるようとする。この DAC1 アドレス比較は、クロックサイクル 4 において I0 に対して実施され、DAC1 アドレス比較信号の正のパルスによって示されるように、アドレスの一致が起こる。しかしながら、DAC1 が DVC1 修飾子を必要とすることから（DVC1 ビット 70 の設定により）、DAC1R デバッグイベントは、アドレス比較で一致してもまだ示されない。命令処理は、I0 に関する（I0 ロード命令に応じて検索される）データが、まだデータ値比較のために利用可能でないため、継続する。次に、I0 は、mem2/E2 段に進み、この間、データをメモリ（例えば、図 1 のメモリ 18 等）から読み込む。I0 用の読み込みデータは、クロックサイクル 5 の終わりに準備が整っており、導体 35 のデータ部でデバッグ制御回路 44 に提供される。そして、I0 のデータ値比較は、次のクロックサイクルであるクロックサイクル 6 において実施され、DVC1 データ比較信号の正のパルスによって示されるように、データの一致が起こる。データ値比較レジスタ 53 に記憶した DVC1 値に一致すると、DVC1 DAC1 デバッグイベントが示され、従って、ハードウェアは、DAC1R ビット 90 を設定する。4050

## 【0030】

サイクル6内においてI0上でDVC1 DAC1を検出すると、DACオフセットカウンタが0にクリアされ、また、後続の各完了した命令の計数が開始できるようになる。図11の例では、I1が、メモリ段mem1において、変換索引バッファ(TLB)のアドレス変換ミスによりエラーを引き起こし、従って、I1は、実行を継続しないことに留意されたい(尚、TLBは、図示しないが、当分野で公知なように、メモリ管理ユニット(MMU)と共にプロセッサ12に配置することができ、この場合、TLB及びMMUは、双方共、当分野で公知なように動作し得る)。従って、クロックサイクル6では、命令I1乃至I3の全てをキルし得る。従って、デバッグ例外は、クロックサイクル7の間に直ちに有効にすることができ、これにより、デバッグ例外を発生させることができ、割込処理を開始できる。即ち、命令I0に対するDVC1 DAC1デバッグイベントの割込処理は、クロックサイクル6の後(例えば、クロックサイクル7において)開始し得る。従って、命令ストリームは、I1において中断される(即ち、デバッグ例外は、I0の実行後、I1の実行の前に起る)。次に、実行は、割込処理の完了後、I1から再開し得る。従って、DSRR0レジスタは、I1のアドレスがデータブレークポイントデバッグ割込の復帰ポインタに対応することから、I1のアドレスを記憶し得る。本例では、DACオフセットカウンタは、0のままである。従って、デバッグ状態レジスタ49のDAC\_OFSTビット98は、%00のままである。即ち、DVC1 DAC1を引き起こした命令(本例では、I0)は、中断された命令(I1)の前の命令である。この時、通常の実行は、デバッグ割込用の割込処理が完了した後、I1から再開し得る。従って、DSRR0レジスタは、I1のアドレスがデータブレークポイントデバッグ割込の復帰ポインタに対応することから、I1のアドレスを記憶し得る。デバッグ割込ハンドラのソフトウェア・ルーチンの完了に続いて、通常の実行は、割込命令からの復帰を実行することによって再開されるが、通常の(非割込処理)命令実行を継続するために、復帰すべき命令(この場合、I1)へのポインタとしてDSRR0にセーブした値が用いられる。

## 【0031】

従って、DVC DACを基準にしたデータ値ブレークポイントのタイミングは、様々な要因に依存して変動することがあり、それらの多くは、予測不可能であり、事前には分からぬことに留意されたい。しかしながら、DAC\_OFSTを利用して、デバッグ例外が実際に発生すると、ユーザは、どの命令が実際にデータ値ブレークポイントを引き起こしたか(即ち、実際にデバッグ例外を発生させたか)判定し得る。

## 【0032】

状況によっては、例えば、ユーザが、割込マスク制御でデバッグ割込を明示的にマスクして無効にした場合、IDEビット76は、ユーザに対して、デバッグイベント(DVC DACデバッグイベント等)が起こったことを通知するが、デバッグ例外がユーザによって一括して無効にされたことから、それが曖昧であることも通知する。即ち、たとえデバッグイベントが起こっても、デバッグ例外は、ユーザによって現在マスクされている。従って、デバッグ割込のマスクが解除された後、そのデバッグ例外が実際に起こると、DAC\_OFST値を用いて、どの命令がデバッグ例外を発生させたか正確に判定できない。これは、ユーザがデバッグ割込のマスクを再び解除する前に、多くの命令を実行し得るためである。この場合、IDEビット76は、実行される命令の実際の数を反映しないことから、DAC\_OFSTの妥当性を限定するためにソフトウェアによって用いてよい。

## 【0033】

図12乃至16は、DAC及びDVC DACデバッグイベントの発生、並びに一実施形態における、例えば、DAC\_OFSTビット98に対するデバッグ状態レジスタ49の更新結果を示す様々な例を表形式で示す。図12乃至16の表では、一連の3つの命令I0、I1、及びI2を各例に用いる。第1命令I0は、ロード/記憶クラスの命令であり、第2命令I1は、他に規定されない限り、ロード/記憶クラス命令であり、また、第3命令I2は、他に規定されない限り、ロード/記憶命令である。図12には、行201乃至208が含まれ、図13には、行209乃至212が含まれ、図14には、行213

10

20

30

40

50

乃至 215 が含まれ、図 15 には、行 216 乃至 218 が含まれ、また、図 16 には、行 219 乃至 220 が含まれることに留意されたい。

#### 【0034】

例を示す表の行 201 では、I0 が DTLB エラーになり、DAC デバッグイベントが起こらないと仮定する。この場合、DTLB 例外が起こり、デバッグ状態レジスタは、更新されない。行 202 が表す例では、I0 が、データ記憶割込 (DSI) エラーになり、また、DAC デバッグイベントが起こらない。この場合、DSI 例外が生じ、デバッグ状態レジスタは、更新されない。行 203 が表す例では、I0 が、DTLB エラーになるが、DACx デバッグイベントが示される（例えば、DAC1 又は DAC2 デバッグイベント）。この場合、DACx デバッグイベントに起因するデバッグ例外が発生し、また、対応する DACx ビットフィールドが設定され（例えば、DAC1R、DAC1W、DAC2R、DAC2W）、IDE ビット 76 が設定され、また、DAC\_OFST ビット 98 が %00 に設定される。DSRR0 レジスタは、I0 を指す（即ち、I0 のアドレスを記憶する）。行 204 が表す例では、I0 が、DSI エラーになるが、DACx デバッグイベントが示される（例えば、DAC1 又は DAC2 デバッグイベント）。この場合、DACx デバッグイベントに起因するデバッグ例外が発生し、また、対応する DACx ビットフィールドが設定され（例えば、DAC1R、DAC1W、DAC2R、DAC2W）、IDE ビット 76 が設定され、また、DAC\_OFST ビット 98 が %00 に設定される。DSRR0 レジスタは、I0 を指す（即ち、I0 のアドレスを記憶する）。行 205 が表す例では、I0 が DACx デバッグイベント（例えば、DAC1 又は DAC2 デバッグイベント）を発生させる。この場合、DACx デバッグイベントに起因するデバッグ例外が発生し、また、対応する DACx ビットフィールドが設定され（例えば、DAC1R、DAC1W、DAC2R、DAC2W）、DAC\_OFST ビット 98 が %00 に設定される。DSRR0 レジスタは、I1 を指す（即ち、I1 のアドレスを記憶する）。行 203 及び 204 に示された条件の場合、IDE ビット 76 が設定されるが、行 205 の場合、IDE ビット 76 は設定されないことに留意されたい。このことを用いて、行 203 及び 204 の %00 の DAC\_OFST 設定値が、命令 I0 が割込を発生させたことを示していることが示され、また、DAC1 又は DAC2 イベントにより I0 上でデバッグ割込が起こる時、DSRR0 のセーブしたプログラムカウンタ値は、I0 を指しており、通常の位置 (I1) ではないことが示される。これが起こる理由は、I0 上には、同時に DTLB 又は DSI 例外もあり、従って、I0 は、実行が完了していないことから、デバッグ割込の後、再実行するべきためである。再実行時、DAC1、DAC2 イベントは、ユーザによって無効にされることがあり、その場合、通常の DTLB 又は DSI 例外が発生し、適切に処理される。しかしながら、行 205 の場合、命令 I0 は、実行を完了しており、従って、セーブした DSRR0 値が I1 を指し、DAC\_OFST 値が %00 であり、また、IDE がクリアされ、DAC\_OFST 値が %00 の場合の DSRR0 の通常の境界条件を示す。

10

20

30

30

#### 【0035】

行 206 乃至 220 が表す様々な例では、I0 が DVCx DACx デバッグイベント（例えば、DVC1 DAC1 又は DVC2 DAC2 デバッグイベントのいずれか）を発生させる。行 206 が表す例では、I1 は、例外を起こさず、任意の命令であってよく、また、I3 は、例外を起こさず、ロード / 記憶型の命令ではない。この場合、DVCx DACx デバッグイベントに起因するデバッグ例外が発生し、また、対応する DACx ビットフィールドが設定され（例えば、DAC1R、DAC1W、DAC2R、DAC2W）、DAC\_OFST ビット 98 が %01 に設定される。DSRR0 レジスタは、I2 の後の命令を指す。DAC\_OFST ビット 98 を調べることによって、I0 が DVCx DACx イベントを引き起こしたことを判定できる。

40

#### 【0036】

行 207 は、図 9 と同様な例を表し、この例では、I1 が例外を起こさず、また、I3 が例外を起こさないが、I3 は、ロード / 記憶クラス命令である。この場合、DVCx 50

D A C x デバッグイベントに起因するデバッグ例外が発生し、そして、対応する D A C x ビットフィールドが設定され（例えば、D A C 1 R、D A C 1 W、D A C 2 R、D A C 2 W）、D A C \_ O F S T ビット 9 8 が% 1 0 に設定される。D S R R 0 レジスタは、I 2 の後の命令を指す。本例では、命令 I 2 は、メモリアクセスを開始したことから、完了できるようにすべきである。行 2 0 8 は、図 1 1 と同様な例を表し、この例では、I 1 は、D T L B エラーを起こし、D A C を引き起こさない。この場合、D V C x D A C x デバッギングイベントに起因するデバッグ例外が発生し、そして、対応する D A C x ビットフィールドが設定され（例えば、D A C 1 R、D A C 1 W、D A C 2 R、D A C 2 W）、D A C \_ O F S T ビット 9 8 が% 0 0 に設定される。D S R R 0 レジスタは、I 1 が、D T L B エラーを引き起こし、実行を完了しなかったことから、I 1 を指す。D A C \_ O F S T ビット 9 8 を調べることによって、I 0 が D V C x D A C x イベントを引き起こしたこと 10 を判定できる。

#### 【 0 0 3 7 】

行 2 0 9 が表す例では、I 1 が D S I エラーを起こし、D A C を引き起こさない。この場合、D V C x D A C x デバッギングイベントに起因するデバッグ例外が発生し、そして、対応する D A C x ビットフィールドが設定され（例えば、D A C 1 R、D A C 1 W、D A C 2 R、D A C 2 W）、D A C \_ O F S T ビット 9 8 が% 0 0 に設定される。D S R R 0 レジスタは、I 1 が、D S I 例外を引き起こし、実行を完了しなかったことから、I 1 を指す。行 2 1 0 が表す例では、I 1 が D T L B エラー及び D A C y （例えば、D A C 1 又は D A C 2 デバッギングイベント）を発生させる。この場合、D V C x D A C x デバッギングイベントに起因するデバッグ例外が発生し、そして、対応する D A C x ビットフィールドが設定され（例えば、D A C 1 R、D A C 1 W、D A C 2 R、D A C 2 W）、D A C \_ O F S T ビット 9 8 が% 0 0 に設定される。D S R R 0 レジスタは、I 1 を指す。この場合、I 1 の D A C y イベントは、I 1 の D T L B エラーによりいずれにせよ再実行すべきであることから、報告されない。行 2 1 1 が表す例では、I 1 が D S I エラー及び D A C y （例えば、D A C 1 又は D A C 2 デバッギングイベント）を発生させる。この場合、D V C x D A C x デバッギングイベントに起因するデバッグ例外が発生し、そして、対応する D A C x ビットフィールドが設定され（例えば、D A C 1 R、D A C 1 W、D A C 2 R、D A C 2 W）、D A C \_ O F S T ビット 9 8 が% 0 0 に設定される。D S R R 0 レジスタは、I 1 を指す。この場合、I 1 の D A C y イベントは、I 1 の D T L B エラーによりいずれにせよ再実行すべきであることから、報告されない。行 2 0 8 乃至 2 1 1 の例の場合、I 1 例外は、マスクされるが、このことは、実施例に依存するものであり、他のプロセッサでは異なり得ることに留意されたい。 20 30

#### 【 0 0 3 8 】

行 2 1 2 が表す例では、I 1 が D A C y （例えば、D A C 1 又は D A C 2 デバッギングイベント）を発生させる。この場合、デバッグ例外が発生し、そして、対応する D A C x ビットフィールドが設定され（例えば、D A C 1 R、D A C 1 W、D A C 2 R、D A C 2 W）、対応する D A C y ビットフィールドが設定され（例えば、D A C 1 R、D A C 1 W、D A C 2 R、D A C 2 W）、また、D A C \_ O F S T ビット 9 8 が% 0 1 に設定される。D S R R 0 レジスタは、I 2 を指す。行 2 1 3 が表す例では、I 1 は、D V C y D A C y （例えば、D V C 1 D A C 1 又は D V C 2 D A C 2 デバッギングイベント）を引き起こし、また、通常のロード / 記憶命令であり、I 2 は、ロード / 記憶命令ではない。この場合、デバッグ例外が発生し、そして、対応する D A C x ビットフィールドが設定され（例えば、D A C 1 R、D A C 1 W、D A C 2 R、D A C 2 W）、対応する D A C y ビットフィールドが設定され（例えば、D A C 1 R、D A C 1 W、D A C 2 R、D A C 2 W）、また、D A C \_ O F S T ビット 9 8 が% 0 1 に設定される。D S R R 0 レジスタは、I 2 を指す。この場合、x が y に等しければ、デバッグ状態レジスタ及び D S R R 0 に結果的に生じる状態は、「D A C y なし」の場合（即ち、I 2 が D A C y を引き起こさない場合）と区別できなくなり得ることにも留意されたい。 40

#### 【 0 0 3 9 】

行 214 が表す例では、I 1 は、DVCy DACy (例えば、DVC1 DAC1 又は DVC2 DAC2 デバッグイベント) を引き起こし、また、通常のロード / 記憶命令であり、I 2 は、例外を引き起こさないロード / 記憶命令である。この場合、デバッグ例外は、I 2 がメモリアクセスを開始したことから、その完了後に発生し、そして、対応する DACx ビットフィールドが設定され (例えば、DAC1R, DAC1W, DAC2R, DAC2W)、対応する DACy ビットフィールドが設定され (例えば、DAC1R, DAC1W, DAC2R, DAC2W)、また、DAC\_OFST ビット 98 が %10 に設定される。DSRR0 レジスタは、I 2 の後の命令を指す。この場合、x が y に等しければ、デバッグ状態レジスタ及び DSRR0 に結果的に生じる状態は、「DACy なし」の場合 (即ち、I 2 が DACy を引き起こさない場合) と区別できなくなり得ることにも留意されたい。10

#### 【0040】

行 215 が表す例では、I 1 は、DVCy DACy (例えば、DVC1 DAC1 又は DVC2 DAC2 デバッグイベント) を引き起こし、また、通常のロード / 記憶命令であり、I 2 は、DSI エラーを発生させる。行 216 が表す例では、I 1 は、DVCy DACy (例えば、DVC1 DAC1 又は DVC2 DAC2 デバッグイベント) を引き起こし、また、通常のロード / 記憶命令であり、I 2 は、DTLB エラーを発生させる。これらの場合のいずれにおいても、デバッグ例外が発生し、そして、対応する DACx ビットフィールドが設定され (例えば、DAC1R, DAC1W, DAC2R, DAC2W)、対応する DACy ビットフィールドが設定され (例えば、DAC1R, DAC1W, DAC2R, DAC2W)、また、DAC\_OFST ビット 98 が %01 に設定される。DSRR0 レジスタは、I 2 を指す。この場合、x が y に等しければ、デバッグ状態レジスタ及び DSRR0 に結果として生じる状態は、「DACy なし」の場合 (即ち、I 2 が DACy を引き起こさない場合) と区別できなくなり得ることにも留意されたい。更に、これらの場合、命令 I 2 は、マスクされるが、この振舞いは、実施例に依存するものであり、他のプロセッサでは異なり得ることに留意されたい。20

#### 【0041】

行 217 が表す例では、I 1 は、DVCy DACy (例えば、DVC1 DAC1 又は DVC2 DAC2 デバッグイベント) を引き起こし、また、通常のロード / 記憶命令であり、I 2 は、DACy 又は DVCy DACy を発生させる通常のロード / 記憶命令又は複数ワードのロード / 記憶命令である。この場合、デバッグ例外が発生し、そして、対応する DACx ビットフィールドが設定され (例えば、DAC1R, DAC1W, DAC2R, DAC2W)、対応する DACy ビットフィールドが設定され (例えば、DAC1R, DAC1W, DAC2R, DAC2W)、また、DAC\_OFST ビット 98 が %10 に設定される。DSRR0 レジスタは、I 2 の後の命令を指す。この場合、x が y に等しければ、デバッグ状態レジスタ及び DSRR0 に結果として生じる状態は、「DACy なし」の場合 (即ち、I 1 又は I 2 が DACy を引き起こさない場合) と区別できなくなり得ることにも留意されたい。30

#### 【0042】

行 218 が表す例では、I 1 は、DVCy DACy (例えば、DVC1 DAC1 又は DVC2 DAC2 デバッグイベント) を引き起こし、また、複数ワードのロード / 記憶命令であり、I 2 は、任意の命令である。この場合、デバッグ例外が発生し、そして、対応する DACx ビットフィールドが設定され (例えば、DAC1R, DAC1W, DAC2R, DAC2W)、対応する DACy ビットフィールドが設定され (例えば、DAC1R, DAC1W, DAC2R, DAC2W)、また、DAC\_OFST ビット 98 が %01 に設定される。DSRR0 レジスタは、I 2 を指す。この場合、I 1 は、複数のレジスタに読込又は書込を行うことから、I 2 のメモリへのアクセスを防止するのに充分な時間があり、従って、I 0 に DVCx DACx の条件が現れると、それをキルし得る。この場合、x が y に等しければ、デバッグ状態レジスタ及び DSRR0 に結果として生じる状態は、「DACy なし」の場合 (即ち、I 2 が DACy を引き起こさない場合) と区別4050

できなくなり得ることにも留意されたい。

#### 【0043】

行219が表す例では、I1は、任意の命令であり、また、例外を起こさず、I2は、D S Iエラーを発生させる通常のロード／記憶又は複数ワードのロード／記憶命令であつて、D A Cを発生させる場合も発生させない場合もある命令である。この場合、デバッグ例外が発生し、そして、対応するD A C xビットフィールドが設定され（例えば、D A C 1 R、D A C 1 W、D A C 2 R、D A C 2 W）、対応するD A C yビットフィールドが設定され（例えば、D A C 1 R、D A C 1 W、D A C 2 R、D A C 2 W）、また、D A C \_O F S Tビット98が%01に設定される。D S R R 0レジスタは、I2を指す。この場合、命令I2は、マスクされるが、この振舞いは、実施例に依存するものであり、他のプロセッサでは異なり得ることに留意されたい。10

#### 【0044】

行220が表す例では、I1は、任意の命令であり、また、例外を起こさず、I2は、D A C y又はD V C y D A C yを発生させる通常のロード／記憶又は複数ワードのロード／記憶命令である。この場合、デバッグ例外が発生し、そして、対応するD A C xビットフィールドが設定され（例えば、D A C 1 R、D A C 1 W、D A C 2 R、D A C 2 W）、対応するD A C yビットフィールドが設定され（例えば、D A C 1 R、D A C 1 W、D A C 2 R、D A C 2 W）、また、D A C \_O F S Tビット98が%10に設定される。D S R R 0レジスタは、I2の後の命令を指す。この場合、xがyに等しければ、デバッグ状態レジスタ及びD S R R 0に結果として生じる状態は、「D A C yなし」の場合（即ち、I2がD A C yを引き起こさない場合）と区別できなくなり得ることに留意されたい。20

#### 【0045】

図17は、本発明の他の実施形態に基づく、図1のデータ処理システムに関するデバッグ状態レジスタ49の図である。図17の例では、デバッグ状態レジスタ49には、I D E (76)、I C M P (78)、B R T (80)、I A C 1 (82)、I A C 2 (84)、I A C 3 (86)、I A C 4 (88)、D A C 1 R (90)、D A C 1 W (92)、D A C 2 R (94)、D A C 2 W (96)、D A C \_O F S T A (102)、O C C A (104)、D A C \_O F S T B (106)、及びO C C B (108)と表記したビットフィールドが含まれる。図17の例には、更に、将来の用途のために予約し得る予約ビットフィールド110を含み得る。尚、デバッグ状態レジスタ49、並びにビットフィールドI D E (76)、I C M P (78)、B R T (80)、I A C 1 (82)、I A C 2 (84)、I A C 3 (86)、I A C 4 (88)、D A C 1 R (90)、D A C 1 W (92)、D A C 2 R (94)、及びD A C 2 W (96)に関する上記説明（例えば、図7及び8の説明等）は、図17に同様に当てはまり、従って、ここでは繰り返さない。しかしながら、図7の例と異なり、図17の例には、D A C \_O F S T (98)ではなく複数のD A Cオフセットフィールド（例えば、D A C \_O F S T A (102)及びD A C \_O F S T B (106)）が含まれる。複数のD A Cオフセットフィールドを用いると、複数のオフセットを追跡することができ、この場合、各D A Cオフセットフィールドは、D A C \_O F S T (98)に関して上述したように動作し得る。しかしながら、複数のD A Cオフセットフィールドが存在することにより、各D A Cオフセットフィールド（例えば、D A C \_O F S T A (102)及びD A C \_O F S T B (106)）は、対応する発生フィールドを有する（例えば、それぞれO C C A (104)及びO C C B (108)）。3040

#### 【0046】

従って、D A C \_O F S T Aビット102を用いると、第1D V C D A C (D V C 1 D A C 1又はD V C 2 D A C 2のいずれか)を示させた命令と、データ値ブレークポイントが起こり、D V C D A C用のデバッグ例外が発生するポイントとの間に実行した命令の数を示し得る。D A C \_O F S T Aビット102を用いると、D A C \_O F S T (98)と同様に、第1データアドレス比較デバッグ例外を起こしたロード又は記憶命令のアドレスからのセーブしたD S R R 0値の「オフセット-1」を記憶し得る。上述したよ50

うに、D S R R 0 は、デバッグセーブ復旧レジスタ 0 に対応し、セーブした D S R R 0 値は、デバッグ割込用の復帰ポインタに対応する。このようにして、第 1 D V C D A C を引き起こしたアドレスと、命令ストリームが中断されてデータ値ブレークポイントが発生したポイント（この場合、そのデータ値ブレークポイントが、第 1 D V C D A C 又は他の D V C D A C の結果として発生し得る）との間に期間内に幾つの命令が実行されたかを判定し得る。これによって、ユーザは、どの命令が第 1 D V C D A C を引き起こしたかを判定し得る。一実施形態では、D A C \_ O F S T A ビット 1 0 2 は、通常、% 0 0 に設定され、D V C D A C が、このフィールドを% 0 0、% 0 1、% 1 0、又は% 1 1 に設定するが、これは、「オフセット - 1」を表す。D A C \_ O F S T A ビット 1 0 2 は、既定値として通常% 0 0 に設定されることから、O C C A ( 1 0 4 ) は、第 1 D V C D A C の発生時に設定され、D A C \_ O F S T A が、D V C D A C オフセットを示す値を保持していることを示し得る。D A C \_ O F S T B ビット 1 0 6 を用いると、従って、第 2 D V C D A C を示させた命令と、データ値ブレークポイントが起こり、D V C D A C 用のデバッグ例外が発生するポイントとの間に実行される命令の数を示し得る。D A C \_ O F S T B ビット 1 0 6 を用いると、第 2 データアドレス比較デバッグ例外を起こしたロード又は記憶命令のアドレスからのセーブした D S R R 0 値の「オフセット - 1」を記憶し得る。このようにして、第 2 D V C D A C を引き起こしたアドレスと、命令ストリームが中断されてデータ値ブレークポイントが発生したポイント（ここでもまた、そのデータ値ブレークポイントが、第 1 D V C D A C 又は第 2 D V C D A C の結果として発生し得る）との間に期間内に幾つの命令が実行されたかを判定し得る。一実施形態では、D A C \_ O F S T B ビット 1 0 6 は、通常、% 0 0 に設定され、D V C D A C が、このフィールドを% 0 0、% 0 1、% 1 0、又は% 1 1 に設定するが、これは、「オフセット - 1」を表す。D A C \_ O F S T B ビット 1 0 6 は、通常、既定値として% 0 0 に設定されることから、O C C B ( 1 0 8 ) は、第 2 D V C D A C の発生時に設定し得る（更に、上述したように、D V C D A C に対して同時に D T L B エラー又は D S I エラーが起る場合、D A C \_ O F S T ビット 9 8 に関して上述したように、対応する D A C オフセットビットは、% 0 0 に設定され、I D E ビット 7 6 は、1 に設定され得ることに留意されたい）。 10 20

#### 【 0 0 4 7 】

従って、複数の命令が、D V C D A C をもたらすことがあり、また、命令ストリームが中断されてデータ値ブレークポイントが発生するポイントにおいて、オフセットフィールド D A C \_ O F S T A ( 1 0 2 ) 及び D A C \_ O F S T B ( 1 0 4 ) の各々は、対応する発生ビットが設定されていると仮定すると、命令ストリームのどの命令（1つ又は複数）が、データ値ブレークポイントをもたらし得る D V C D A C を引き起こしたかを示せることに留意されたい。O C C A ビット 1 0 4 及び O C C B ビット 1 0 8 の双方が設定され、2つのD V C D A C が発生したことを示す場合、ユーザは、どの命令が実際に各 D V C D A C を引き起こしたかを示すために、対応するオフセット値を用い得るが、これら2つの命令の内のどちらが（即ち、2つのD V C D A C の内のどちらが）命令ストリームを中断したデータ値ブレークポイントを実際にもたらしたかについてユーザが実際に判定することが必要なこともある。 30 40

#### 【 0 0 4 8 】

図 1 8 は、図 1 7 について述べたように、複数のオフセットフィールドの使用方法を示すタイミング図を表す。図 1 8 の例の場合、I 0 乃至 I 4 の各々は、ロード命令であり、I 0 は、第 1 D A C D V C デバッグイベント ( D V C x D A C x 、ここで、x は、1 又は 2 のいずれかであり得る) を発生させ、I 2 は、第 2 D A C D V C デバッグイベント ( D V C y D A C y 、ここで、y は、1 又は 2 のいずれかであり得る) を発生させるものと仮定する。図 1 8 は、更に、六段パイプラインについて描かれているが、他の実施形態には、例えば、異なる数の段を有する異なるパイプラインを含んでもよい。図 1 8 で参照する六段パイプライン等の命令パイプラインの動作は、当分野で公知であり、従って、本明細書では詳述しない。更に、図 1 8 には、プロセッサ 1 2 のプロセッサ・クロック 50

に対応し得るクロック信号が含まれる。プロセッサ・クロックは、システムクロック又はプロセッサ12の一部だけに供給されるクロックであってよく、当分野で公知なように生成し得る。

#### 【0049】

図18において、I0は、クロックサイクル1においてフェッチ段に入り、クロックサイクル2においてデコード段に入り、クロックサイクル3においてEA/E0段に入り、ここでI0の有効アドレスを計算し、そして、クロックサイクル4においてmem1/E1段に入る。従って、有効アドレスは、クロックサイクル3の終わりに準備が整っており、導体35のアドレス部でデバッグ制御回路44に提供され、I0の有効アドレスとデータアドレス比較レジスタ47に記憶したDAC値(DAC1及びDAC2)との間でアドレス比較を実施できるようにする(更に、この時点で、BIU(34)によってバス20上にもアドレスを配置し得ることに留意されたい)。このDACxアドレス比較は、DACアドレス比較信号の正のパルスによって示されるように、クロックサイクル4において命令I0に対して実施され、一致が起こるが、DACアドレス比較信号は、DACxアドレス比較が実施され、一致が起こっていることを示すためにデバッグ制御回路44内でアサートされる制御信号であってよい。しかしながら、DACxは、DVCx修飾子を必要とすることから(DVCxビットの設定、例えば、DVC1ビット70又はDVC2ビット72の設定により)、デバッギングイベントは、DACxアドレス比較で一致しても、まだ示されない。命令処理は、I0に関係する(I0ロード命令に応じて検索される)データが、まだデータ値比較のために利用可能でないため、継続する。次に、I0は、mem2/E2段に進み、この間、データをメモリ(例えば、図1のメモリ18等)から読み込む。この読み込んだデータは、この段の終わりで利用可能となり得る(また、例えば、バス20を介してBIU(34)によって受信される)。そして、導体35のデータ部でデバッグ制御回路44に提供され、I0に関連する読み込んだデータ値と、データ値比較レジスタ53に記憶したDVCx値との間でデータ値比較を実施できるようにする。従って、データ値比較は、DVCxデータ比較信号の正のパルスによって示されるように、次のクロックサイクルであるクロックサイクル6において実施され、一致が起こるが、DVCxデータ比較信号は、DVCデータ比較が起こっていることを示すためにデバッグ制御回路44内でアサートされる制御信号であってよい。データ値比較レジスタ53に記憶したDVCx値に一致すると、DVCx DACxデバッギングイベントが示され、従って、ハードウェアは、対応する状態ビットを設定する(例えば、DAC1Rビット90又はDAC2Rビット94。I0がDAC1 DVC1を引き起こしたか又はDAC2 DVC2を引き起こしたかに依存する)。

#### 【0050】

サイクル6内においてI0上でDVCx DACxを検出すると、DACオフセットAカウンタを0にクリアし、また、後続の各完了した命令の計数を開始できるようにすることに留意されたい(DACオフセットAカウンタは、カウンタ41に含み得る)。しかしながら、パイプラインは、I1及びI2がメモリ段(mem1及びmem2)にあるため、クロックサイクル6ではまだ中断できない。従って、I1及びI2は、メモリアクセスが開始すると、中断することはできず、完了しなければならないことから、待ち状態のデバッグ例外の更なる処理に先立って、完了しなければならない。後続のメモリアクセスは、しかしながら、DVCx DACx例外が現在待ち状態であることから、起動されない。I1及びI2の各メモリアクセスは、書き戻し段に入った後、完了と見なされる。I2(命令I1及びI2の後半)は、クロックサイクル8において書き戻し段にあり、その後、デバッグ例外が発生し、また、割込処理を開始できるように、待ち状態のデバッグ例外を処理し得ることに留意されたい。即ち、DVC1 DAC1デバッギングイベントの割込処理は、クロックサイクル8の後(例えば、クロックサイクル9)まで、開始できない。DVCx DACxが検出される時点で、I3は、まだパイプラインのEA/E0段にあり、従って、キルし得ることに留意されたい。即ち、命令ストリームは、I3において中斷される。実行は、従って、割込処理の完了後に、I3から再開し得る。従って、DSRR

10

20

30

40

50

0レジスタは、I 3のアドレスがデータブレークポイントデバッグ割込の復帰ポインタに対応することから、I 3のアドレスを記憶し得る。デバッグ割込ハンドラのソフトウェア・ルーチンの完了に続いて、通常の実行は、割込命令からの復帰を実行することによって再開されるが、通常の（非割込）命令実行を継続するために、復帰すべき命令（この場合、I 3）へのポインタとしてD S R R 0にセーブした値が用いられる。

#### 【0051】

D V C x D A C x デバッグイベントを検出して D A C オフセット A カウンタをクリアした後、後続の各命令が完了した状態で、D A C オフセット A カウンタは、デバッグ例外が発生する（この時点で割込処理が起こる）まで、1ずつ増加することに留意されたい。従って、D A C オフセット A カウンタは、クロックサイクル 8において 2 まで増加し、従って、デバッグ状態レジスタ 49 の D A C \_ O F S T A ビット 102 が %10 に設定され、更に、O C C A ビット 104 が設定される。即ち、D V C x D A C x を引き起こした命令（本例では、I 0）の後で且つ割込処理の前に実行される命令の数は、2 であり、これは、D A C \_ O F S T A として記憶される。

10

#### 【0052】

I 2 は、クロックサイクル 5において E A / E 0 段に入ることに留意されたい。従って、有効アドレスは、クロックサイクル 5 の終わりに準備が整っており、導体 35 のアドレス部でデバッグ制御回路 44 に提供され、I 2 の有効アドレスとデータアドレス比較レジスタ 47 に記憶した D A C 値（D A C 1 及び D A C 2）との間でアドレス比較を実施できるようにする（更に、この時点で、B I U (34) によってバス 20 上にもアドレスを配置し得ることに留意されたい）。この D A C y アドレス比較は、D A C y アドレス比較信号の正のパルスによって示されるように、クロックサイクル 6において実施され、一致が起こるが、D A C y アドレス比較信号は、D A C アドレス比較が実施されて一致が起こっていることを示すためにデバッグ制御回路 44 内でアサートされる制御信号であってよい。しかしながら、D A C y は、D V C y 修飾子を必要とすることから（D V C y ビット、例えば、D V C 1 ビット 70 又は D V C 2 ビット 72 の設定により）、デバッグイベントは、D A C y アドレス比較で一致しても、まだ示されない。命令処理は、I 2 に関する（I 2 ロード命令に応じて検索される）データが、まだデータ値比較のために利用可能でないため、継続する。次に、I 2 は、m e m 2 / E 2 段に進み、この間、データをメモリ（例えば、図 1 のメモリ 18 等）から読み込む。この読み込んだデータは、この段の終わりで利用可能となり得る（また、例えば、バス 20 を介して B I U (34) によって受信し得る）。そして、導体 35 のデータ部でデバッグ制御回路 44 に提供され、I 2 に関する読み込んだデータ値と、データ値比較レジスタ 53 に記憶した D V C y 値との間でデータ値比較を実施できるようにする。従って、データ値比較は、D V C y データ比較信号の正のパルスによって示されるように、次のクロックサイクルであるクロックサイクル 8において実施され、一致が起こるが、D V C y データ比較信号は、D V C データ比較が実施されて一致が起こっていることを示すためにデバッグ制御回路 44 内でアサートされる制御信号であってよい。データ値比較レジスタ 53 に記憶した D V C y 値に一致すると、D V C y D A C y デバッグイベントが示され、従って、ハードウェアは、対応する状態ビット（例えば、D A C 1 R ビット 90 又は D A C 2 R ビット 94。I 2 が D A C 1 D V C 1 を引き起こしたか又は D A C 2 D V C 2 を引き起こしたかに依存する）。

20

30

40

#### 【0053】

サイクル 8 内において I 2 上で D V C y D A C y を検出すると、D A C オフセット B カウンタを 0 にクリアし、また、後続の各完了した命令の計数を開始できるようにすることに留意されたい（D A C オフセット B カウンタは、カウンタ 41 に含み得る）。パイプラインは、クロックサイクル 8において、まだ中断されていない。その理由は、I 0 によって引き起こされた D V C x D A C x に応じてデータ値ブレークポイントが発生する前に、I 1 及び I 2 の双方が完了しなければならないためである。従って、I 2 に対応するデータも返され、D V C y D A C y がデバッグ例外の発生前に起こり得る。上述したように、命令ストリームは、サイクル 8 の後、I 3 において中断され、これは、D A C オフ

50

セットBカウンタが、増加せず、デバッグ例外発生時に0のままであることを意味する。従って、デバッグ状態レジスタ49のD A C \_ O F S T Bビット106が%00に設定され、更に、O C C Bビット108が設定される（これにより、ユーザは、%00が、実際のオフセット値を示すものであって、第2D V C D A Cが起らなかった場合に返される単なる既定値ではないことを知ることができる）。従って、D V C y D A C yを引き起こした命令（本例では、I2）の後で且つ割込処理前に実行される命令の数は、0である。このようにして、D A C \_ O F S T Bビット106及びO C C Bビット108は、第1デバッグイベント（例えば、D V C x D A C x）と、その第1デバッグイベントのデバッグ例外が起こるポイントとの間で起こるデバッグイベント（例えば、D V C y D A C y）に関する情報を提供し得ることに留意されたい。

10

#### 【0054】

従って、図18の例では、各々異なる命令によって引き起こされた2つのD V C D A Cが、サイクル8の後、デバッグ例外の発生の前に起こることに留意されたい。D A C \_ O F S T Aビット102及びD A C \_ O F S T Bビット104を、対応するO C C Aビット104及びO C C Bビット108と共に用いて、I0（命令ストリームが中断したポイントに対応する前の命令I2から更に2命令前）及びI2（命令ストリームが中断したポイントに対応する前の命令I2から更に0命令前）の各々がD V C D A Cを引き起こしたことが分かる。そして、ユーザは、どちらの命令が実際にデータ値ブレークポイントをもたらしたかをデコードし得る（本例では、I0であり、これが第1D V C D A C、D V C x D A C xを引き起こした）。更に、I0がD V C 1 D A C 1又はD V C 2 D A C 2の1つを引き起こし、I2がD V C 1 D A C 1及びD V C 2 D A C 2の他方を発生させるように、x及びyが異なってよいことに留意されたい。他の選択肢として、I0及びI2の双方が、D V C 1 D A C 1又はD V C 2 D A C 2のいずれかを発生させるように、xがyに等しくてもよい。更に、一実施形態では、D A C Aオフセットカウンタ及びD A C Bオフセットカウンタは、オフセットカウンタ（1つ又は複数）41内に配置し得ることに留意されたい。

20

#### 【0055】

従って、デバッグイベントの発生とデバッグ例外の発生との間（即ち、デバッグイベントの発生とそのデバッグイベントの割込処理の開始との間）で実行する命令の数の判定を支援するために、どのように1つ又は複数のオフセット値を用いるかについて認識することができる。これによって、デバッグ処理を改善でき、ユーザは、これらの1つ又は複数のオフセット値を用いて、実際にどの命令がデバッグ例外を発生させたか良く理解できるようになる。上記の説明は、データ値ブレークポイントに帰着するD V C D A Cデバッグイベントに関して行ったが、これらのオフセット値（D A C \_ O F S T、D A C \_ O F S T A、及びD A C \_ O F S T B等）は、他の種類のデバッグイベントに用いてよい。即ち、D A C \_ O F S T、D A C \_ O F S T A、及びD A C \_ O F S T B等のオフセットフィールドは、任意の種類のデバッグイベントの発生と、対応するデバッグ例外の発生との間（即ち、任意の種類のデバッグイベント発生と、特定のデバッグイベントの割込処理開始との間）に実行する命令の数を示すために用い得る。

30

#### 【0056】

更に、デバッグイベントを引き起こした命令の位置ではなく、そのイベントが起ころから実行される命令の数を知ることは、有用であり得ることに留意されたい。その理由は、待ち状態のデバッグイベントの場合、命令ストリームを中断できるパイプライン境界に達する前に、（同じ位置の）同じ命令を何回も実行可能であり、従って、位置情報が、それ自体では、実際の一連のイベントを判定するには不充分な場合があり得ることを理解できるためである。

40

#### 【0057】

一実施形態では、システムは、複数の命令について、フェッチ、デコード、および実行と、各命令の実行に関連した結果の書きとを連続的に行うことによって、複数の命令を実行するためのパイプライン・プロセッサと、パイプライン・プロセッサに結合されており

50

、複数の命令の実行を監視してデバッグイベントが発生する時を判定し、デバッグ例外を発生させて命令処理フローを中断するためのデバッグ回路と、を含む。デバッグ回路は、デバッグイベントを引き起こした命令と命令実行においてデバッグ例外が発生するポイントとの間で命令実行を完了させる命令（存在する場合）の数を表す値を示すための制御回路をさらに含む。

#### 【0058】

更なる一実施形態では、デバッグ回路の制御回路は、デバッグイベントを引き起こした命令に続き命令実行を完了させる命令の数を表す値としてカウント値を計数して与えるためのカウンタをさらに含む。更に他の実施形態では、カウント値が0より大きいことはデバッグイベントの処理が曖昧であることを示す。

10

#### 【0059】

更なる他の実施形態では、デバッグ回路は、デバッグイベントを引き起こした命令に続き命令実行を完了させる1つ以上の追加の命令もデバッグイベントの発生を引き起こしたことを見出す。

#### 【0060】

更なる他の実施形態では、パイプライン・プロセッサはデバッグイベントを各々引き起こす2つ以上の命令を実行し、制御回路は複数のカウンタをさらに含み、各カウンタは、デバッグイベントを引き起こす2つ以上の命令のそれぞれの命令に続き命令実行を完了させる追加の命令の数によって決定される、それぞれのカウント値を与える。

20

#### 【0061】

更なる他の実施形態では、デバッグ回路は、デバッグイベントを引き起こした命令に続き命令実行においてデバッグ例外が発生する所定のポイントまでに命令実行を完了させる追加の命令（存在する場合）の数を表す値を保持するためのフィールドを有するデバッグ状態レジスタをさらに含む。

#### 【0062】

更なる他の実施形態では、デバッグ回路は、複数の命令のうちの1つのデコードを行い、パイプライン・プロセッサによって形成されたアドレスを1つ以上の所定のデバッグアドレスと比較してデータアドレス一致が発生したか否かを判定し、パイプライン・プロセッサによってアクセスの行われたデータ値を1つ以上の所定のデータ値と比較してデータ値一致が発生したか否かを判定することとに応じて、デバッグイベントが発生したことを見出す。

30

#### 【0063】

他の実施形態では、システムは、複数の命令について、フェッチ、デコード、および実行と、各命令の実行に関連した結果の書き込みとを連続的に行うことによって、複数の命令を実行するためのパイプライン処理回路と、パイプライン処理回路に結合されており、1つ以上のデバッグアドレスを命令実行によって形成されるアドレスと選択的に比較することと、1つ以上のデバッグデータ値を命令実行によって形成されるデータと選択的に比較することによって、複数の命令の実行を監視するデバッグ回路と、を含む。デバッグ回路は、両方の比較が一致を生じるときを判定し、該判定に応答してデバッグイベントを示し、デバッグイベントを引き起こした命令の後に命令実行においてデータ値ブレークポイントが発生する所定のポイントまでに実行される命令の数を示す。

40

#### 【0064】

他の実施形態の更なる実施形態では、データ値ブレークポイントは曖昧であり、試験回路は、曖昧なデータ値ブレークポイントが発生したか否かを示すビットフィールドを有するレジスタをさらに含む。

#### 【0065】

他の実施形態の更なる他の実施形態では、試験回路は、デバッグイベントが発生する時とデータ値ブレークポイントが発生する時との間に発生するイベントに関する状態情報を示すための状態レジスタをさらに含む。更に他の実施形態では、デバッグイベントが発生する時とデータ値ブレークポイントが発生する時との間に発生するイベントのうちの1つ

50

は、第2のデバッグイベントをさらに含む。

**【0066】**

他の実施形態の更なる他の実施形態では、デバッグ回路は、デバッグイベントを引き起こした命令に続き命令実行を完了させる命令の数のカウント値を計数して与えるためのカウンタをさらに含む。

**【0067】**

他の実施形態の更なる他の実施形態では、デバッグ回路は、デバッグイベントを引き起こした命令に続き、命令実行においてデータ値ブレークポイントが発生する所定のポイントまでに命令実行を完了させる追加の命令（存在する場合）の数を示す値を保持するためのフィールドを有する状態デバッグルジスタをさらに含む。 10

**【0068】**

更に他の実施形態では、方法は、複数の命令について、フェッチ、デコード、および実行と、各命令の実行に関連した結果の書き込みとを連続的に行うことによって、複数の命令を実行する工程と、複数の命令の実行を監視してデバッグイベントが発生する時を判定する工程と、デバッグ例外を発生させて命令処理フローを中断する工程と、デバッグイベントを引き起こした命令と命令実行においてデバッグ例外が発生するポイントとの間で命令実行を完了させる命令（存在する場合）の数を示す工程と、を含む。

**【0069】**

更に他の実施形態の更なる実施形態では、方法は、デバッグイベントを引き起こした命令に続き命令実行を完了させる命令の数のカウント値を計数して与える工程をさらに含む。 20 更なる実施形態では、方法は、デバッグイベントの処理が曖昧であることを示す0より大きいカウント値を形成する工程をさらに含む。

**【0070】**

他の実施形態の更なる他の実施形態では、方法は、デバッグイベントを引き起こした命令に続き命令実行を完了させる1つ以上の追加の命令もデバッグイベントの発生を引き起こしたことを見定する工程をさらに含む。

**【0071】**

他の実施形態の更なる他の実施形態では、方法は、2つ以上の命令が各々デバッグイベントを引き起こすことを見定する工程と、2つ以上の命令の各々に続き命令実行を完了させる追加の命令の数のそれぞれのカウント値を異なるカウンタに記憶する工程と、をさらに含む。 30

**【0072】**

他の実施形態の更なる他の実施形態では、方法は、デバッグ回路にデバッグ状態レジスタを与える工程と、状態レジスタは、デバッグイベントを引き起こした命令に続き命令実行においてデバッグ例外が発生する所定のポイントまでに命令実行を完了させる追加の命令（存在する場合）の数を示すための値を保持するためのフィールドを有することと、をさらに含む。

**【0073】**

他の実施形態の更なる他の実施形態では、方法は、複数の命令のうちの1つのデコードを行うことに応答して、デバッグイベントが発生したと見定する工程と、パイプライン・プロセッサによって形成されるアドレスを1つ以上の所定のデバッガーアドレスと比較してデータアドレス一致が発生したか否かを判定する工程と、パイプライン・プロセッサによって形成されるデータ値を1つ以上の所定のデータ値と比較してデータ値一致が発生したか否かを判定する工程と、デバッグイベントは両比較演算について一致が発生することを必要とすることと、をさらに含む。 40

**【0074】**

本発明を実装する装置は、ほとんど当業者には既知の電子部品や回路から構成されるため、回路の詳細については、本発明の根底にある概念の理解や認識のために、また、本発明の教示内容が不明瞭になったり注意が逸れたりしないように、上述した如く必要と思われる以上の説明はしない。 50

## 【0075】

本明細書に用いる用語「プログラム」は、コンピュータシステム上の実行用に設計された一連の命令と定義する。プログラム、即ち、コンピュータプログラムには、サブルーチン、関数、手順、オブジェクト・メソッド、オブジェクト実装、実行可能なアプリケーション、アプレット、サーブレット、ソースコード、オブジェクトコード、共有ライブラリ／動的読み込みライブラリ、及び／又はコンピュータシステム上の実行用に設計された他の一連の命令を含み得る。

## 【0076】

上述した実施形態の一部は、適用可能であれば、様々な異なる情報処理システムを用いて実現し得る。例えば、図1及びそれについての説明では、代表的な情報処理構成について述べるが、この代表的な構成は、本発明の様々な態様の説明において有用な基準を提供するためだけに示している。勿論、構成の説明は、説明のために簡素化しており、また、この構成は、本発明に基づいて用い得る多くの異なる種類の適切な構成内の1つに過ぎない。当業者は、論理ブロック間の境界は、説明のためだけであり、他の実施形態では、論理ブロック又は回路素子を併合したり、様々な論理ブロック又は回路素子に機能を分解して代替させたりしてよいことを認識されるであろう。10

## 【0077】

従って、本明細書に示した構成は代表例に過ぎず、実際には、同じ機能を実現する任意の他の構成を実装し得ることを理解されたい。抽象的ではあるが明確に、同じ機能を達成する構成要素の任意の構成は、所望の機能を達成するように有効に「関連付けられる」。従って、本明細書において特定の機能を達成するために組み合わせた任意の2つの構成要素は、構成又は中間構成要素にかかわらず、所望の機能を達成するように互いに「関連付けられている」と理解し得る。同様に、そのように関連付けた任意の2つの構成要素は、所望の機能を達成するために互いに「動作可能に接続された」又は「動作可能に結合された」とも見なし得る。20

## 【0078】

更に、例えば、一実施形態では、システム10の図示した要素は、単一の集積回路上又は同一装置内に配置された回路である。他の選択肢として、システム10には、相互接続された任意の数の別個の集積回路又は別個の装置を含み得る。更に、例えば、システム10又はその一部は、物理的な回路又は物理的な回路に転換可能な論理表現のソフト又はコード表現であってよい。このように、システム10は、任意の適切な種類のハードウェア記述言語で具現化し得る。30

## 【0079】

更に、当業者は、上述した動作の機能間の境界は、单なる例示であることを認識されるであろう。複数動作の機能は、单一動作に集約してもよく、及び／又は单一動作の機能は、追加の動作に分散してもよい。更に、他の実施形態には、特定の動作の複数のインスタンスを含んでもよく、動作順序は、様々な他の実施形態では、変更してもよい。

## 【0080】

本明細書に述べたソフトウェアの全て又は一部は、データ処理システム10の受信される要素であってよく、例えば、メモリ18等のコンピュータ判読可能媒体又は他のコンピュータシステム上の他の媒体から受信し得る。そのようなコンピュータ判読可能媒体は、データ処理システム10等の情報処理システムに、恒久的に、着脱可能に、又は遠隔的に結合してよい。コンピュータ判読可能媒体には、例えば、これらに限定するものではないが、ほんの一例を挙げると、ディスク及びテープ記憶媒体を含む磁気記憶媒体と、コンパクトディスク媒体（例えば、CD-ROM、CD-R等）及びデジタル映像ディスク記憶媒体等の光学記憶媒体と、FLASHメモリ、EEPROM、EPROM、ROM等の半導体ベースのメモリユニットを含む不揮発性メモリ記憶媒体と、強磁性デジタルメモリと、MRAMと、レジスタ、バッファ又はキャッシュ、主記憶装置、RAM等を含む揮発性記憶媒体と、コンピュータネットワーク、二地点間電気通信設備、及び搬送波伝送媒体を含むデータ伝送媒体と、の内から任意の数のものを含んでよい。40

## 【0081】

本発明について、本明細書では特定の実施形態を参照して述べたが、様々な修正や変更は、以下の請求項に記載した本発明の範囲から逸脱することなく行い得る。従って、明細書及び図は、限定的であるというよりもむしろ例示であると解釈すべきであり、また、そのような全ての修正は、本発明の範囲内に含まれるものとする。本明細書において具体的な実施形態に関して述べたあらゆる恩恵、利点、又は問題に対する解決策も、全ての請求項の不可欠、必須、又は本質的な特徴もしくは要素であると解釈しようとするものではない。

## 【0082】

本明細書に用いた用語「結合された」は、直接結合又は機械的結合に限定するものではない。10

更に、本明細書に用いた用語「a又はan(不定冠詞)」は、1つ又は2つ以上と定義する。更に、請求項において「少なくとも1つの」と及び「1つ又は複数の」等の導入節を用いることは、不定冠詞「a」又は「an」による他の請求項要素の導入が、同じ請求項に導入節「1つ又は複数の」又は「少なくとも1つの」と及び「a」又は「an」等の不定冠詞が含まれる場合でも、そのように導入した請求項要素を含む任意の特定の請求項を、そのような要素を1つだけ含む発明に限定することを意味すると解釈すべきではない。同じことは、定冠詞の使用にも当てはまる。

## 【0083】

特に明記しない限り、「第1」と及び「第2」等の用語は、そのような用語が述べる要素間を任意に区別するために用いる。従って、これらの用語は、必ずしもそのような要素の時間的な又は他の優先順位付けを示そうとするものではない。20

【図1】

【図2】

【図3】

【図4】

【図5】

| ビット | 名前   | 説明                                                                                                                                                                                                                     |    |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 0   | EDM  | 外部デバッグモード。このビットはソフトウェアには読み取りのみ可能。<br>0:-外部デバッグコード無効。内部デバッグイベントは<br>外部デバッグイベントへマッピングされない。<br>1:-外部デバッグコード有効。イベントはCPUにコードの中断を媒介させない。<br>ソフトウェアにはデバッガレジスタに対する書き込み許可されない。<br>[DBCRx, DBSR, DBCNT, IAC1-2, DAC1-2, DVC1-2]; | 52 |

| 1   | IDM  | 内部デバッグモード。<br>0:-デバッグ例外は無効。EDMがセットされない限りデバッグイベントは<br>DBSRに影響を与えない。<br>1:-デバッグ例外は有効。有効化されたデバッグイベントはDBSRを更新する。<br>また、CPUにコードの中断を媒介させることもできる。ソフトウェアには<br>デバッガレジスタに対する書き込み許可される。                                           | 54 |

| 2:3 | -    | 予約済み                                                                                                                                                                                                                   | 56 |

| 4   | ICMP | 命令完了デバッグイベント有効。<br>0:-ICMPデバッグイベントは無効。<br>1:-ICMPデバッグイベントは有効。                                                                                                                                                          | 58 |

| 5   | BRT  | 分岐取得デバッグイベント有効。<br>0:-BRTデバッグイベントは無効。<br>1:-BRTデバッグイベントは有効。                                                                                                                                                            | 60 |

| 6:7 | -    | 予約済み                                                                                                                                                                                                                   | 61 |

【図6】

| ビット   | 名前   | 説明                                                                                                                                                                                                      |    |

|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 8     | IAC1 | 命令アドレス比較1デバッグイベント可能<br>0:-IAC1デバッグイベントは無効。<br>1:-IAC1デバッグイベントは有効。                                                                                                                                       | 62 |

| 9     | IAC2 | 命令アドレス比較2デバッグイベント可能<br>0:-IAC2デバッグイベントは無効。<br>1:-IAC2デバッグイベントは有効。                                                                                                                                       | 64 |

| 10:11 | DAC1 | データアドレス比較1デバッグイベント可能<br>00:-DAC1デバッグイベントは無効。<br>01:-記憶型データストレージアクセスに対してのみ<br>DAC1デバッグイベントは有効。<br>10:-ロード型データストレージアクセスに対してのみ<br>DAC1デバッグイベントは有効。<br>11:-記憶型またはロード型データストレージアクセスに対してのみ<br>DAC1デバッグイベントは有効。 | 66 |

| 12:13 | DAC2 | データアドレス比較2デバッグイベント可能<br>00:-DAC2デバッグイベントは無効。<br>01:-記憶型データストレージアクセスに対してのみ<br>DAC2デバッグイベントは有効。<br>10:-ロード型データストレージアクセスに対してのみ<br>DAC2デバッグイベントは有効。<br>11:-記憶型またはロード型データストレージアクセスに対してのみ<br>DAC2デバッグイベントは有効。 | 68 |

| 14    | DVC1 | データ値比較1修飾子<br>0:-DAC1デバッグイベントはデータ値比較による影響を受けない<br>1:-DAC1デバッグイベントはデータ値比較によって修飾される                                                                                                                       | 70 |

| 15    | DVC2 | データ値比較2修飾子<br>0:-DAC2デバッグイベントはデータ値比較による影響を受けない<br>1:-DAC2デバッグイベントはデータ値比較によって修飾される                                                                                                                       | 72 |

| 16-31 | -    | 予約済み                                                                                                                                                                                                    | 73 |

【図7】

【図8】

| ビット   | 名前      | 説明                                                                                                                                                                                                                             |     |

|-------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 0     | IDE     | 意味デバッグイベント<br>デバッグ例外が無効の場合は1にセットされ、デバッグイベントによって<br>そのデバッグ状態レジスタビットは1にセットされる。                                                                                                                                                   | 76  |

| 1     | ICMP    | 命令完了デバッグイベント<br>命令完了デバッグイベントが発生した場合は1にセットされる。                                                                                                                                                                                  | 78  |

| 2     | BRT     | 分岐取得デバッグイベント<br>分岐取得デバッグが発生した場合は1にセットされる。                                                                                                                                                                                      | 80  |

| 3     | IAC1    | 命令アドレス比較1デバッグイベント<br>IAC1デバッグイベントが発生した場合は1にセットされる。                                                                                                                                                                             | 82  |

| 4     | IAC2    | 命令アドレス比較2デバッグイベント<br>IAC2デバッグイベントが発生した場合は1にセットされる。                                                                                                                                                                             | 84  |

| 5     | IAC3    | 命令アドレス比較3デバッグイベント<br>IAC3デバッグイベントが発生した場合は1にセットされる。                                                                                                                                                                             | 86  |

| 6     | IAC4    | 命令アドレス比較4デバッグイベント<br>IAC4デバッグイベントが発生した場合は1にセットされる。                                                                                                                                                                             | 88  |

| 7     | DAC1R   | データアドレス比較1読取りデバッグイベント<br>DBCR0[DAC1]=0b10 または DBCR0[DAC1]=0b11において、<br>読取型のDAC1デバッグイベントが発生した場合は1にセットされる。                                                                                                                       | 90  |

| 8     | DAC1W   | データアドレス比較1書き込みデバッグイベント<br>DBCR0[DAC1]=0b01 または DBCR0[DAC1]=0b11において、<br>書き込み型のDAC1デバッグイベントが発生した場合は1にセットされる。                                                                                                                    | 92  |

| 9     | DAC2R   | データアドレス比較2読取りデバッグイベント<br>DBCR0[DAC2]=0b10 または DBCR0[DAC2]=0b11において、<br>読取型のDAC2デバッグイベントが発生した場合は1にセットされる。                                                                                                                       | 94  |

| 10    | DAC2W   | データアドレス比較2書き込みデバッグイベント<br>DBCR0[DAC2]=0b01 または DBCR0[DAC2]=0b11において、<br>書き込み型のDAC2デバッグイベントが発生した場合は1にセットされる。                                                                                                                    | 96  |

| 11:12 | DACOFST | データアドレス比較オフセット<br>同時にDTLBまたはDSLRが発生しない限り、DACデバッグ例外を得るロードまたは記憶命令のアドレスからの保存されたDSRROの値の<br>オフセト1を表示し、発生した場合、このフィールドは0b00にセットされ、<br>DBSR[IDE]は1にセットされる。正常な場合、Ob00Cがセットされている。<br>DVC DACでは、このフィールドは、Ob01, Ob10, またはOb11に<br>セットされる。 | 98  |

| 13-31 | -       | 予約済み                                                                                                                                                                                                                           | 100 |

【図9】

【図10】

【図11】

【図12】

|     | 第1ロード／記憶クラス命令<br>(I0) | 第2命令<br>(他に指定のない<br>限り、ロード／<br>記憶クラス)<br>(I1) | 第3命令<br>(他に指定のない<br>限り、ロード／<br>記憶クラス)<br>(I2) | 結果                                                                                                                                        |

|-----|-----------------------|-----------------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 201 | DTLBエラー、<br>DACなし     | -                                             | -                                             | DTLB例外を取り、DBSR更新なし。                                                                                                                       |

| 202 | DSI、<br>DACなし         | -                                             | -                                             | DSI例外を取り、DBSR更新なし。                                                                                                                        |

| 203 | DTLBエラー、<br>DACxあり    | -                                             | -                                             | デバッグ例外を取り、DBSRはDACxおよびIDEの設定を更新し、DAC_OFSTは0b00にセットされる。DSRROポインタは第1ロード／記憶クラス命令を指す。                                                         |

| 204 | DSI、<br>DACxあり        | -                                             | -                                             | デバッグ例外を取り、DBSRはDACxの設定を更新し、DAC_OFSTは0b00にセットされる。DSRROポインタは第1ロード／記憶クラス命令を指す。                                                               |

| 205 | DACx                  | -                                             | -                                             | デバッグ例外を取り、DBSRはDACxの設定を更新し、DAC_OFSTは0b00にセットされる。DSRROポインタは第2ロード／記憶クラス命令を指す。                                                               |

| 206 | DVCx DACx             | 例外なし、<br>任意の命令                                | 例外なし、<br>非LD／ST命令                             | デバッグ例外を取り、DBSRはDACxの設定を更新し、DAC_OFSTは0b00にセットされる。DSRROポインタは第3ロード／記憶クラス命令を指す。                                                               |

| 207 | DVCx DACx<br>(図9)     | 例外なし、<br>LD／ST命令                              | -                                             | デバッグ例外を取り、DBSRはDACxの設定を更新し、DAC_OFSTは0b10にセットされる。DSRROポインタは第3命令の後の命令を指す。                                                                   |

| 208 | DVCx DACx<br>(図11)    | DTLBエラー、<br>DACなし                             | -                                             | デバッグ例外を取り、DBSRはDACxの設定を更新し、DAC_OFSTは0b00にセットされる。DSRROポインタは第2ロード／記憶クラス命令を指す。<br>注:この場合、第2LD／ST例外はマスクされる。この挙動は実装に応じる。また、他のプロセッサに対して異なってもよい。 |

【図13】

|     | 第1ロード／記憶クラス命令<br>(I0) | 第2命令<br>(他に指定のない<br>限り、ロード／<br>記憶クラス)<br>(I1) | 第3命令<br>(他に指定のない<br>限り、ロード／<br>記憶クラス)<br>(I2) | 結果                                                                                                                                        |

|-----|-----------------------|-----------------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 209 | DVCx DACx             | DSI、DACなし                                     | -                                             | デバッグ例外を取り、DBSRはDACxの設定を更新し、DAC_OFSTは0b00にセットされる。DSRROポインタは第2ロード／記憶クラス命令を指す。<br>注:この場合、第2LD／ST例外はマスクされる。この挙動は実装に応じる。また、他のプロセッサに対して異なってもよい。 |

| 210 | DVCx DACx             | DTLBエラー、<br>DACyあり                            | -                                             | デバッグ例外を取り、DBSRはDACxの設定を更新し、DAC_OFSTは0b00にセットされる。DSRROポインタは第2ロード／記憶クラス命令を指す。<br>注:この場合、第2LD／ST例外はマスクされる。この挙動は実装に応じる。また、他のプロセッサに対して異なってもよい。 |

| 211 | DVCx DACx             | DSI、DACyあり                                    | -                                             | デバッグ例外を取り、DBSRはDACxの設定を更新し、DAC_OFSTは0b00にセットされる。DSRROポインタは第2ロード／記憶クラス命令を指す。<br>注:この場合、第2LD／ST例外はマスクされる。この挙動は実装に応じる。また、他のプロセッサに対して異なってもよい。 |

| 212 | DVCx DACx             | DACy                                          | -                                             | デバッグ例外を取り、DBSRはDACx、DACyの更新し、DAC_OFSTは0b10にセットされる。DSRROポインタは第3命令を指す。<br>注:この場合、X=Yであるとき、待られるDBSRおよびDSRROの状態は「DACyなし」の場合と区別できないことがある。      |

【図14】

|     | 第1ロード／記憶クラス命令<br>(10) | 第2命令<br>(他に指定のない限り、ロード／記憶クラス)<br>(11) | 第3命令<br>(他に指定のない限り、ロード／記憶クラス)<br>(12) | 結果                                                                                                                                                                                                        |

|-----|-----------------------|---------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 213 | DVCx DACx             | DVCy DACy,<br>正常なLD／ST                | 非LD／ST命令                              | デバッグ例外を取り、DBSRはDACx, DACyの設定を更新し、DAC_OFSTは0b01にセットされる。DSRROのポインタは第3命令を指す。<br>注: この場合、X=Yであるとき、得られるDBSRおよびDSRROの状態は「DACYなし」の場合と区別できないことがある。                                                                |

| 214 | DVCx DACx             | DVCy DACy,<br>正常なLD／ST                | LD／ST命令<br>例外なし                       | デバッグ例外を取り、DBSRはDACx, DACyの設定を更新し、DAC_OFSTは0b10にセットされる。DSRROのポインタは第3ロード／記憶クラス命令の後の命令を指す。<br>注: この場合、X=Yであるとき、得られるDBSRおよびDSRROの状態は「DACYなし」の場合と区別できないことがある。                                                  |

| 215 | DVCx DACx             | DVCy DACy,<br>正常なLD／ST                | DSI, DAC<br>ありまたはなし                   | デバッグ例外を取り、DBSRはDACx, DACyの設定を更新し、DAC_OFSTは0b01にセットされる。DSRROのポインタは第3命令を指す。<br>注: この場合、X=Yであるとき、得られるDBSRおよびDSRROの状態は「DACYなし」の場合と区別できないことがある。<br>注: この場合、第3LD／ST例外はマスクされる。この挙動は実装に応じる。また、他のプロセッサに対して異なってもよい。 |

【図15】

|     | 第1ロード／記憶クラス命令<br>(10) | 第2命令<br>(他に指定のない限り、ロード／記憶クラス)<br>(11)   | 第3命令<br>(他に指定のない限り、ロード／記憶クラス)<br>(12)                   | 結果                                                                                                                                                                                                        |

|-----|-----------------------|-----------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 216 | DVCx DACx             | DVCy DACy,<br>正常なLD／ST                  | DTLB, DAC<br>ありまたはなし                                    | デバッグ例外を取り、DBSRはDACx, DACyの設定を更新し、DAC_OFSTは0b01にセットされる。DSRROのポインタは第3命令を指す。<br>注: この場合、X=Yであるとき、得られるDBSRおよびDSRROの状態は「DACYなし」の場合と区別できないことがある。<br>注: この場合、第3LD／ST例外はマスクされる。この挙動は実装に応じる。また、他のプロセッサに対して異なってもよい。 |

| 217 | DVCx DACx             | DVCy DACy,<br>正常なLD／ST                  | DACy, または<br>DVCy DACy,<br>正常なLD／ST<br>または多ワード<br>LD／ST | デバッグ例外を取り、DBSRはDACx, DACyの設定を更新し、DAC_OFSTは0b10にセットされる。DSRROのポインタは第3ロード／記憶クラス命令の後の命令を指す。<br>注: この場合、X=Yであるとき、得られるDBSRおよびDSRROの状態は「DACYなし」の場合と区別できないことがある。                                                  |

| 218 | DVCx DACx             | DVCy DACy,<br>LD／ST,<br>多(LMW,<br>STMW) | LD／STを<br>含む任意の命令                                       | デバッグ例外を取り、DBSRはDACx, DACyの設定を更新し、DAC_OFSTは0b01にセットされる。DSRROのポインタは第3命令を指す。<br>注: この場合、X=Yであるとき、得られるDBSRおよびDSRROの状態は「DACYなし」の場合と区別できないことがある。                                                                |

【図16】

|     | 第1ロード／記憶クラス命令<br>(10) | 第2命令<br>(他に指定のない限り、ロード／記憶クラス)<br>(11) | 第3命令<br>(他に指定のない限り、ロード／記憶クラス)<br>(12)                   | 結果                                                                                                                                                 |

|-----|-----------------------|---------------------------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 219 | DVCx DACx<br>(図10)    | 任意の命令<br>(例外なし)                       | DSI, DAC<br>ありまたはなし,<br>正常なLD／ST<br>または多ワード<br>LD／ST    | デバッグ例外を取り、DBSRはDACx, DACyの設定を更新し、DAC_OFSTは0b01にセットされる。DSRROのポインタは第3命令を指す。<br>注: この場合、第3LD／ST例外はマスクされる。この挙動は実装に応じる。また、他のプロセッサに対して異なってもよい。           |

| 220 | DVCx DACx             | 任意の命令<br>(例外なし)                       | DACy, または<br>DVCy DACy,<br>正常なLD／ST<br>または多ワード<br>LD／ST | デバッグ例外を取り、DBSRはDACx, DACyの設定を更新し、DAC_OFSTは0b10にセットされる。DSRROのポインタは第3クラス命令の後の命令を指す。<br>注: この場合、X=Yであるとき、得られるDBSRおよびDSRROの状態は「DACYなし」の場合と区別できないことがある。 |

【図17】

【図18】

---

フロントページの続き

(56)参考文献 特開平08-185336(JP,A)

特開平06-139107(JP,A)

特開平10-222393(JP,A)

特開平10-333939(JP,A)

特開昭62-239238(JP,A)

特開2002-163126(JP,A)

米国特許第06591378(US,B1)

米国特許第05257358(US,A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 11/28 - 11/34

G 06 F 9/38