(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6009228号

(P6009228)

(45) 発行日 平成28年10月19日(2016.10.19)

(24) 登録日 平成28年9月23日(2016.9.23)

(51) Int.Cl.

H05K 3/46 (2006.01)

F 1

H05K 3/46

H05K 3/46Q

N

請求項の数 8 (全 18 頁)

(21) 出願番号 特願2012-122588 (P2012-122588)

(22) 出願日 平成24年5月30日 (2012.5.30)

(65) 公開番号 特開2013-247353 (P2013-247353A)

(43) 公開日 平成25年12月9日 (2013.12.9)

審査請求日 平成27年5月19日 (2015.5.19)

前置審査

(73) 特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100091672

弁理士 岡本 啓三

(72) 発明者 佐藤 淳史

長野県長野市小島田町80番地 新光電氣

工業株式会社内

(72) 発明者 野村 智弘

長野県長野市小島田町80番地 新光電氣

工業株式会社内

(72) 発明者 大島 一宏

長野県長野市小島田町80番地 新光電氣

工業株式会社内

最終頁に続く

(54) 【発明の名称】電子部品内蔵基板の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

コア材に開口部を形成する工程と、

前記開口部内に電子部品を搭載する工程と、

前記コア材の一方の面に第1樹脂層を形成すると共に、前記コア材の開口部の側面と前記電子部品との隙間に前記第1樹脂層を充填して充填樹脂部を形成する工程と、

前記コア材の他方の面に第2補助絶縁層を形成する共に、前記コア材の一方の面の前記第1樹脂層の上に第2樹脂層を積層して、前記第1樹脂層と前記第2樹脂層とからなる第1補助絶縁層を形成する工程と、

前記第2補助絶縁層に、前記電子部品の接続端子に到達する第1ビアホールを形成する工程と、

前記第2補助絶縁層の上に、前記第1ビアホールを介して前記電子部品の接続端子に接続される第1配線層を形成する工程とを有し、 10

前記コア材は前記一方の面及び他方の面の全体にわたって前記第1補助絶縁層及び前記第2補助絶縁層と直接接触しており、前記コア材、前記第1補助絶縁層及び前記第2補助絶縁層により基板が形成されることを特徴とする電子部品内蔵基板の製造方法。

## 【請求項 2】

前記コア材の厚みは、前記電子部品の厚みに対応していることを特徴とする請求項1に記載の電子部品内蔵基板の製造方法。

## 【請求項 3】

前記電子部品を搭載する工程は、

前記コア材の他方の面に仮付テープを貼り付ける工程と、

前記コア材の開口部内の前記仮付テープに前記電子部品を搭載する工程とを含み、

前記充填樹脂部を充填する工程の後に、前記仮付テープを除去する工程を有することを特徴とする請求項 1 又は 2 に記載の電子部品内蔵基板の製造方法。

【請求項 4】

前記第 1 配線層を形成する工程の後に、

前記第 2 補助絶縁層の上に層間絶縁層を形成する工程と、

前記層間絶縁層に、前記第 1 配線層に到達する第 2 ピアホールを形成する工程と、

前記層間絶縁層の上に、前記第 2 ピアホールを介して前記第 1 配線層に接続される第 2 配線層を形成する工程とを有することを特徴とする請求項 1 乃至 3 のいずれか一項に記載の電子部品内蔵基板の製造方法。 10

【請求項 5】

前記層間絶縁層を形成する工程において、前記層間絶縁層は銅箔付プリプレグを熱プレスすることにより形成され、前記層間絶縁層の上に銅箔が接着されており、

前記第 2 ピアホールを形成する工程において、前記銅箔及び前記層間絶縁層をレーザで加工し、

前記第 2 配線層を形成する工程において、前記第 2 配線層は前記銅箔を含んで形成されることを特徴とする請求項 4 に記載の電子部品内蔵基板の製造方法。

【請求項 6】

前記第 1 配線層の厚みは、前記電子部品の接続端子の厚みより厚いことを特徴とする請求項 1 乃至 5 のいずれか一項に記載の電子部品内蔵基板の製造方法。 20

【請求項 7】

前記第 1 補助絶縁層を形成する前記第 1 樹脂層と前記第 2 樹脂層との間に配線層は存在しないこと特徴とする請求項 1 乃至 6 のいずれか一項に記載の電子部品内蔵基板の製造方法。

【請求項 8】

前記電子部品は、チップキャパシタであることを特徴とする請求項 1 乃至 7 のいずれか一項に記載の電子部品内蔵基板の製造方法。

【発明の詳細な説明】

30

【技術分野】

【0001】

本発明は電子部品内蔵基板の製造方法に関する。

【背景技術】

【0002】

近年の電子機器の発達に伴い、電子機器に使用される電子部品装置の配線基板は、小型化及び高性能化などが要求されている。これに対応するため、配線基板内に電子部品が内蔵された電子部品内蔵基板が実用化されている。

【0003】

そのような電子部品内蔵基板の一例では、コア基板の開口部に電子部品が配置され、コア基板の両面側にビルドアップ配線が形成される。 40

【先行技術文献】

【特許文献】

【0004】

【特許文献 1】特開 2011 - 216740 号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

後述する予備的事項の欄で説明するように、電子部品内蔵基板を製造する際には、コア基板の開口部に仮付テープで仮接着された電子部品の周りの隙間を、樹脂フィルムを熱プ

50

レスして樹脂で埋め込む工程がある。このとき、コア基板の厚みは電子部品より厚く設定されていることから、埋め込む空間の体積が大きく、厚い樹脂フィルムを高い押圧力で熱プレスする必要がある。

#### 【0006】

このため、電子部品が仮付テープから剥がれてコア基板の開口部内で傾いた状態で樹脂封止されてしまうことがある。さらに、埋め込む空間の体積が大きいため、電子部品の周りの隙間を信頼性よく樹脂で埋め込むことは困難である。

#### 【0007】

電子部品内蔵基板の製造方法において、電子部品を信頼性よく搭載することを目的とする。

10

#### 【課題を解決するための手段】

#### 【0009】

以下の開示の一観点によれば、コア材に開口部を形成する工程と、前記開口部内に電子部品を搭載する工程と、前記コア材の一方の面に第1樹脂層を形成すると共に、前記コア材の開口部の側面と前記電子部品との隙間に前記第1樹脂層を充填して充填樹脂部を形成する工程と、前記コア材の他方の面に第2補助絶縁層を形成する共に、前記コア材の一方の面の前記第1樹脂層の上に第2樹脂層を積層して、前記第1樹脂層と前記第2樹脂層とからなる第1補助絶縁層を形成する工程と、前記第2補助絶縁層に、前記電子部品の接続端子に到達する第1ビアホールを形成する工程と、前記第2補助絶縁層の上に、前記第1ビアホールを介して前記電子部品の接続端子に接続される第1配線層を形成する工程とを有し、前記コア材は前記一方の面及び他方の面の全体にわたって前記第1補助絶縁層及び前記第2補助絶縁層と直接接触しており、前記コア材、前記第1補助絶縁層及び前記第2補助絶縁層により基板が形成される電子部品内蔵基板の製造方法が提供される。

20

#### 【発明の効果】

#### 【0010】

以下の開示によれば、電子部品内蔵基板の一つの好適な態様では、コア材の厚みを電子部品の厚みに対応させている。このため、コア材の開口部に配置された電子部品の周りの隙間を、樹脂フィルムを熱プレスして埋め込む際に、埋め込む空間の体積を小さくすることができます。

30

#### 【0011】

これにより、薄い樹脂フィルムを低い押圧力で熱プレスすることで、電子部品の周りを隙間なく樹脂で埋め込むことができる。また、樹脂フィルムを熱プレスする際の押圧力を低く設定できるので、電子部品が傾くことが防止される。

#### 【0012】

そして、コア材の厚みの不足分を両面側の第1、第2補助絶縁層によって補うことにより、所望の厚みのコア基板を得ることができる。

#### 【0013】

また、電子部品の接続端子は、第2補助絶縁層のビアホールを介して厚みの厚い第1配線層によってかさ上げされている。

40

#### 【0014】

このため、銅箔及びプリプレグから形成される層間絶縁層を高出力のレーザで加工して第1配線層の上にビアホールを形成する場合であっても、かさ上げされた第1配線層がレーザ加工時のストップ層として機能し、電子部品の接続端子に損傷が生じるおそれがない。

#### 【図面の簡単な説明】

#### 【0015】

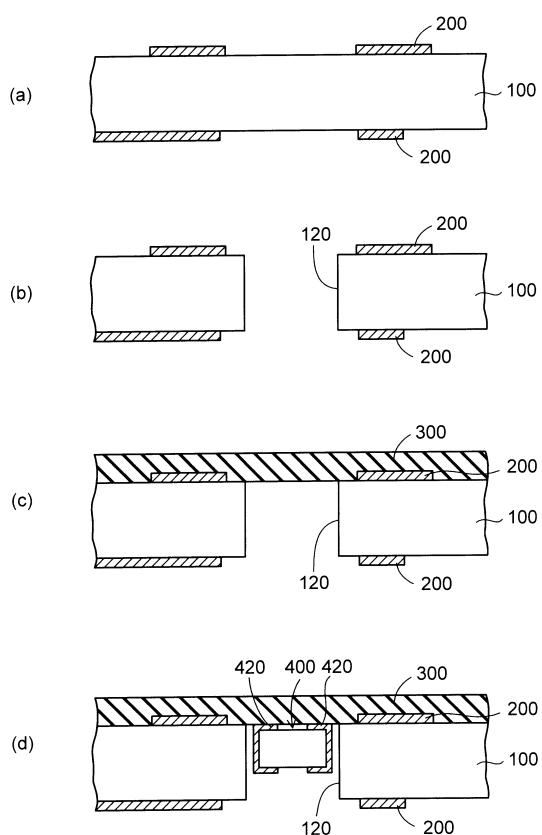

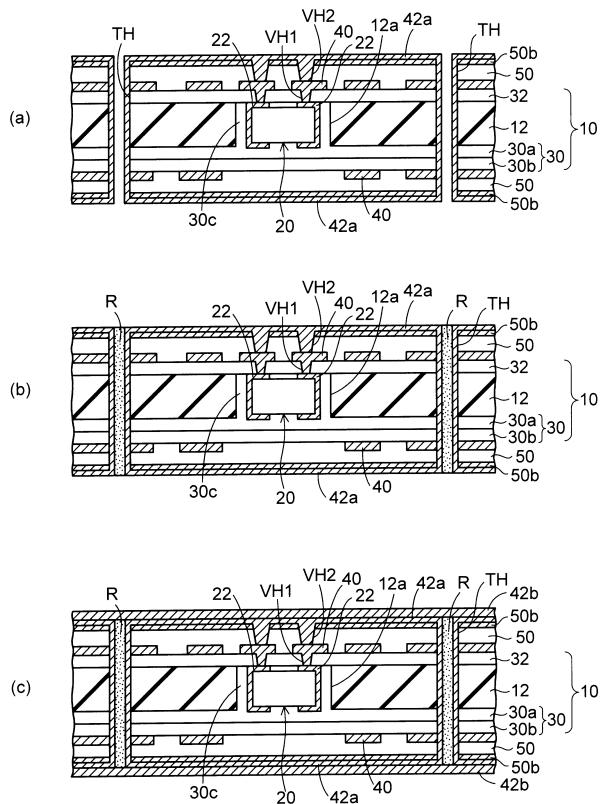

【図1】図1(a)～(d)は予備的事項に係る電子部品内蔵基板の製造方法を示す断面図(その1)である。

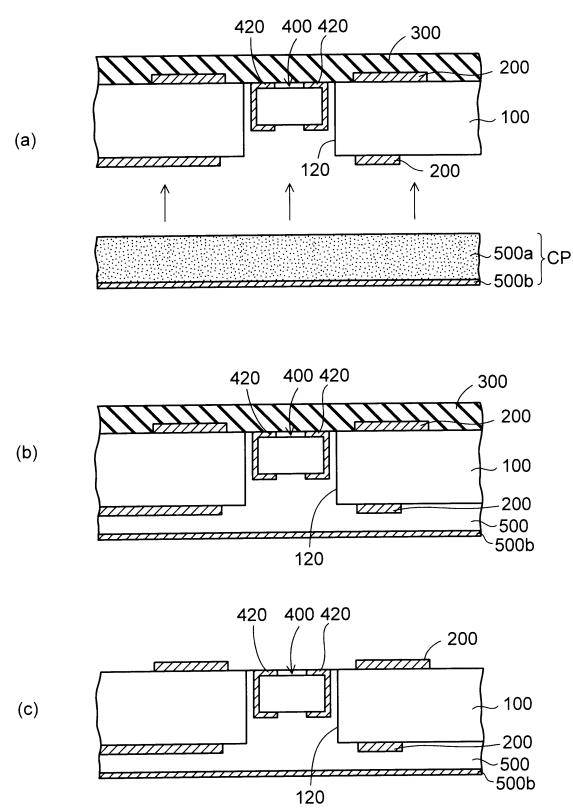

【図2】図2(a)～(c)は予備的事項に係る電子部品内蔵基板の製造方法を示す断面図(その2)である。

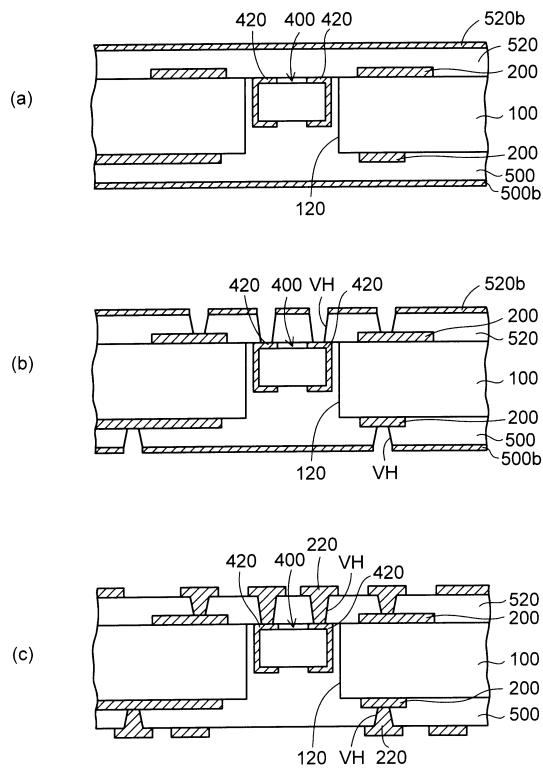

50

【図3】図3(a)～(c)は予備的事項に係る電子部品内蔵基板の製造方法を示す断面図(その3)である。

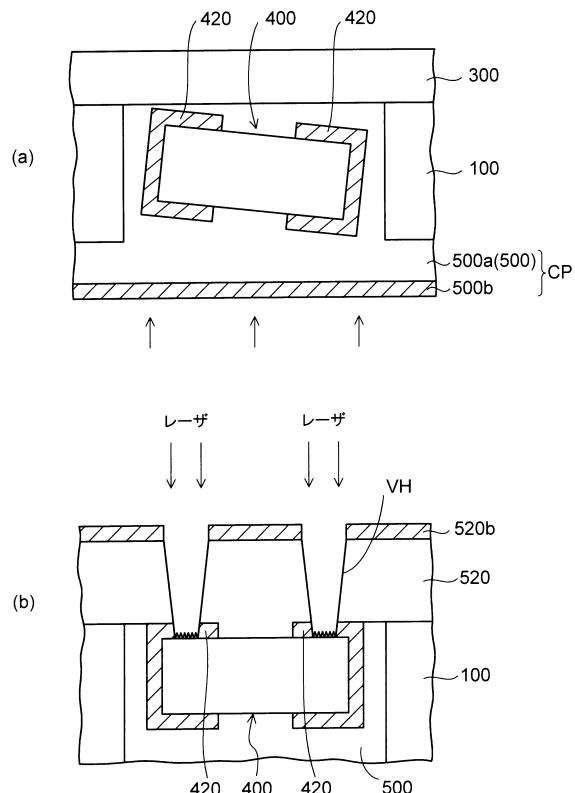

【図4】図4(a)及び(b)は予備的事項に係る電子部品内蔵基板の製造方法の問題点を説明するための断面図である。

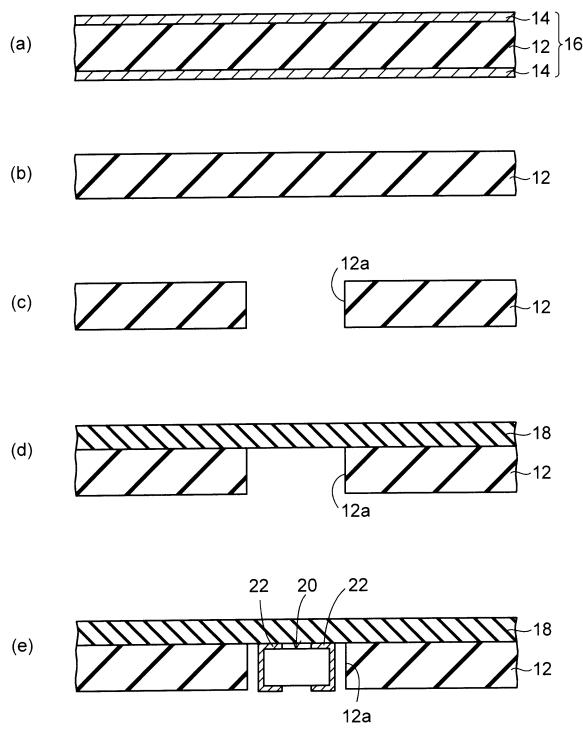

【図5】図5(a)～(e)は実施形態の電子部品内蔵基板の製造方法を示す断面図(その1)である。

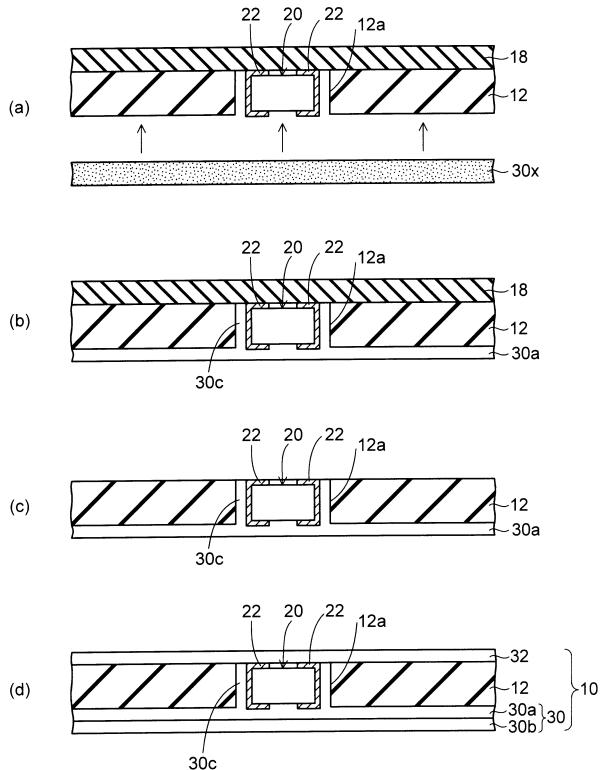

【図6】図6(a)～(d)は実施形態の電子部品内蔵基板の製造方法を示す断面図(その2)である。

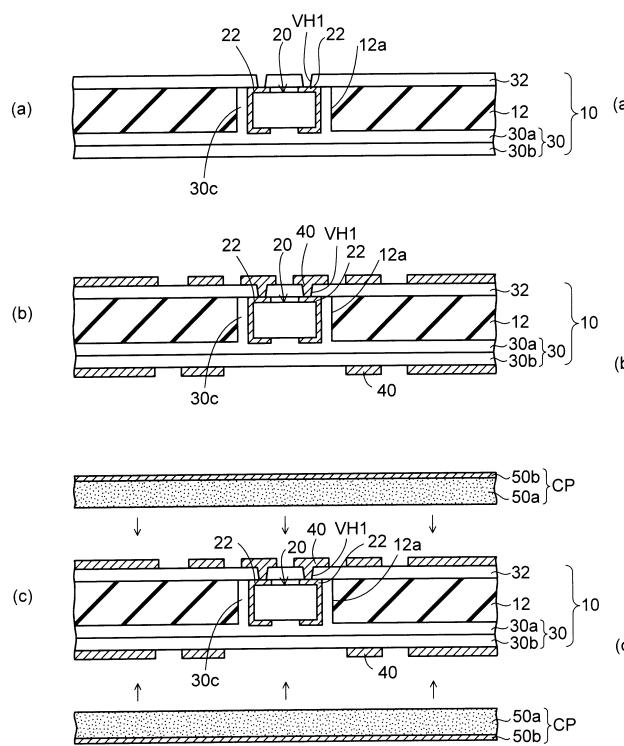

【図7】図7(a)～(c)は実施形態の電子部品内蔵基板の製造方法を示す断面図(その3)である。

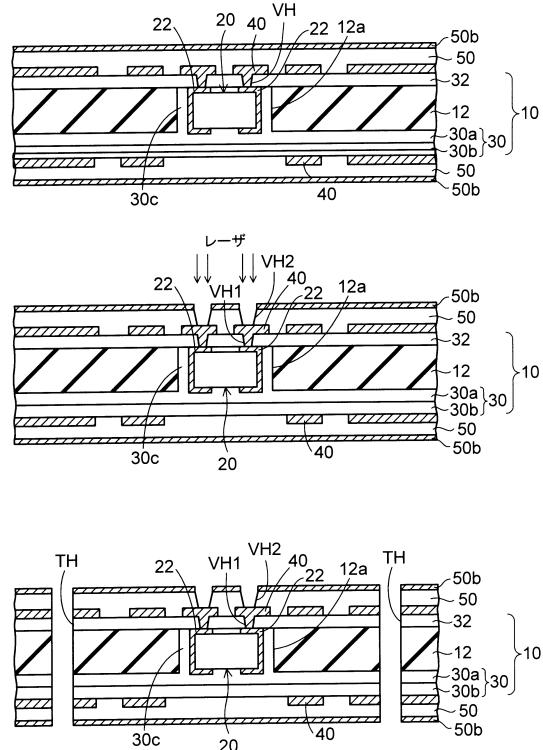

【図8】図8(a)～(c)は実施形態の電子部品内蔵基板の製造方法を示す断面図(その4)である。

【図9】図9(a)～(c)は実施形態の電子部品内蔵基板の製造方法を示す断面図(その5)である。

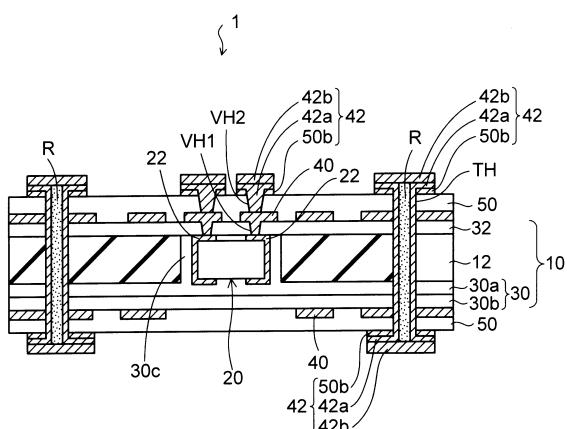

【図10】図10は実施形態の電子部品内蔵基板を示す断面図である。

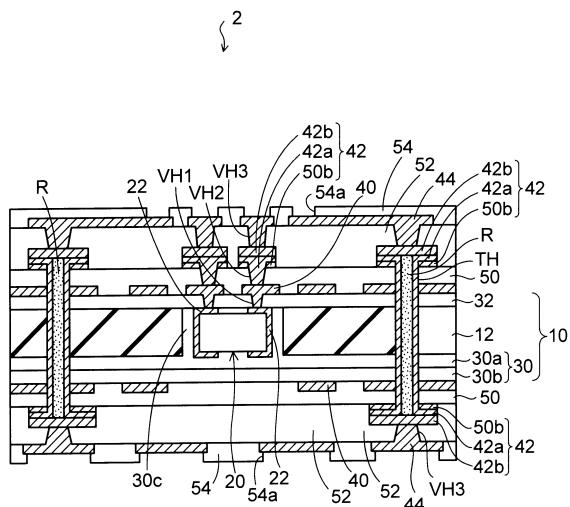

【図11】図11は実施形態の別の電子部品内蔵基板を示す断面図である。

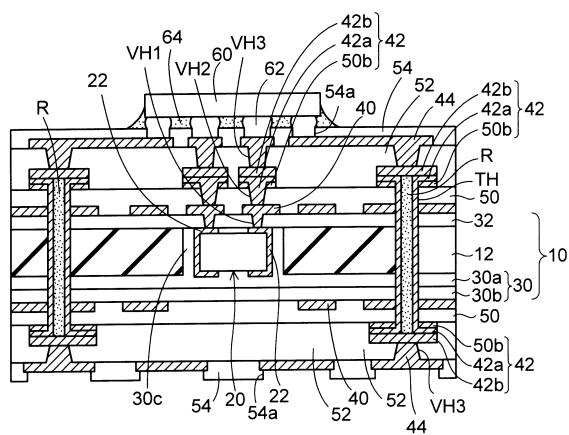

【図12】図12は図11の電子部品内蔵基板に半導体チップが実装された様子を示す断面である。

#### 【発明を実施するための形態】

##### 【0016】

以下、実施の形態について、添付の図面を参照して説明する。

##### 【0017】

実施形態を説明する前に、基礎となる予備的事項について説明する。予備的事項に係る電子部品内蔵基板の製造方法では、図1(a)に示すように、まず、両面側に第1配線層200がそれぞれ形成されたコア基板100を用意する。コア基板100はガラスエポキシ樹脂などの絶縁材料から形成され、その厚みは0.6mmである。

##### 【0018】

次いで、図1(b)に示すように、ルータなどによってコア基板100を厚み方向に貫通加工することにより、開口部120を形成する。

##### 【0019】

続いて、図1(c)に示すように、粘着性を有する仮付テープ300をコア基板100の上面に貼り付ける。さらに、図1(d)に示すように、コア基板100の開口部120内の仮付テープ300にチップキャパシタ400を仮接着して搭載する。

##### 【0020】

チップキャパシタ400は、横方向の両端側に一対の接続端子420を備えている。チップキャパシタ400の厚みは0.5mmであり、コア基板100の厚み：0.6mmに比べて薄く設定されている。

##### 【0021】

次いで、図2(a)に示すように、プリプレグ500aの一方の面に銅箔500bが接着された銅箔付プリプレグCPを用意する。プリプレグ500aは、ガラス繊維などの繊維補強材にエポキシ樹脂などを含浸させた中間素材である。

##### 【0022】

そして、図2(a)及び(b)に示すように、銅箔付プリプレグCPのプリプレグ500aの面をコア基板100の下面に積層し、加熱処理しながら金型でプレス成形する。

##### 【0023】

これにより、コア基板100の開口部120にプリプレグ500aの樹脂が溶融して充填され、硬化することにより、チップキャパシタ400が配置された開口部120がプリプレグ500aから形成される第1絶縁層500によって封止される。同時に、コア基板100の下面に第1絶縁層500が形成される。第1絶縁層500は、その下面側に銅箔500bが接着した状態で形成される。

**【0024】**

その後に、図2(c)に示すように、図2(b)の構造体から仮付テープ300を除去する。

**【0025】**

続いて、図3(a)に示すように、図2(a)及び(b)の工程と同様な方法で、銅箔付プリプレグCPのプリプレグ500aの面をコア基板100の上面に積層し、加熱処理しながら金型でプレス成形する。これにより、コア基板100の上面に第2絶縁層520及び銅箔520bが形成され、チップキャパシタ400の上面が第2絶縁層520で被覆される。

**【0026】**

次いで、図3(b)に示すように、コア基板100の上面側において、銅箔520b及び第2絶縁層520をレーザで加工することにより、チップキャパシタ400の接続端子420に到達するピアホールVHを形成する。

**【0027】**

また同様に、コア基板100の下面側において、銅箔500b及び第1絶縁層500をレーザで加工することにより、コア基板100の下面側の第1配線層200に到達するピアホールVHを形成する。

**【0028】**

さらに、図3(c)に示すように、コア基板100の上面側において、ピアホールVHを介してチップキャパシタ400の接続端子420に接続される第2配線層220を第2絶縁層520の上に形成する。第2配線層220は銅箔520bを含んで形成される。

**【0029】**

また同様に、コア基板100の下面側において、ピアホールVHを介してコア基板100の下面側の第1配線層200に接続される第2配線層220を第1絶縁層500の上に形成する。

**【0030】**

以上により、コア基板100の両面側に2層の多層配線が形成され、同様な工程を繰り返すことにより、所要の多層配線を備えた電子部品内蔵基板を製造することができる。

**【0031】**

次に、前述した予備的事項に係る電子部品内蔵基板の製造方法の問題点について説明する。第1に、前述した図2(a)及び(b)の工程において、伝送経路のインピーダンス整合などの要求から、コア基板100の厚みは調整されており、チップキャパシタ400の厚みより厚くなっている。このため、コア基板100の開口部120を銅箔付プリプレグCPで埋め込む際に、埋め込む空間の体積が大きく、樹脂の充填量を多く必要とする。

**【0032】**

従って、図4(a)に示すように、厚いプリプレグ500aを有する銅箔付プリプレグCPを使用し、高い押圧力で熱プレスして成形する必要がある。このため、チップキャパシタ400が仮付テープ300から剥がれてしまい、コア基板100の開口部120内で傾いた状態で第1絶縁層500で封止されてしまうことがある。

**【0033】**

さらには、埋め込む空間の体積が大きいため、厚いプリプレグ500aを有する銅箔付プリプレグCPなどを使用するとしても、1回の熱プレスでチップキャパシタ400の周りを隙間なく樹脂で埋め込むことは困難であり、十分な信頼性が得られない場合が多い。

**【0034】**

第2に、前述した図3(b)のピアホールVHを形成する工程では、銅箔520b及びプリプレグから形成された纖維補強材を含む第2絶縁層520をレーザで加工する必要があり、銅ダイレクトレーザ加工となる。このため、レーザ加工の条件として、銅箔520b及纖維補強材を含む第2絶縁層520を加工できる高出力の条件に設定される。

**【0035】**

しかし、図4(b)に示すように、チップキャパシタ400の接続端子420は、厚み

10

20

30

40

50

が 5 μm 程度の薄膜の銅電極から形成される。このため、レーザ加工でビアホール V H を形成する際にチップキャパシタ 400 の接続端子 420 が極端に薄くなったり、ひいては消失したりする。

#### 【0036】

さらには、後に、チップキャパシタ 400 の接続端子 420 に接続される配線層をめっき法に基づいて形成する際に、ビアホール V H 内の接続端子 420 がめっきの前処理のライトエッティングによって膜減りしてしまう。

#### 【0037】

このように、チップキャパシタ 400 の接続端子 420 をビアホール V H 内に十分に残すことは困難であり、チップキャパシタ 400 と第 2 配線層 220 との電気的な接続の信頼性が十分に得られない課題がある。10

#### 【0038】

以下に説明する実施形態では、前述した不具合を解消することができる。

#### 【0039】

##### (実施の形態)

図 5 ~ 図 9 は実施形態の電子部品内蔵基板の製造方法を示す断面図、図 10 は実施形態の電子部品内蔵基板を示す断面図である。

#### 【0040】

実施形態の電子部品内蔵基板の製造方法では、図 5 (a) に示すように、まず、コア材 12 の両面側に銅箔 14 がそれぞれ積層された銅張積層板 16 を用意する。20

#### 【0041】

次いで、図 5 (b) に示すように、銅張積層板 16 の両面側の銅箔 14 をウェットエッティングによって除去することにより、単層のコア材 12 を得る。本実施形態の例では、コア材 12 の厚みは 0.5 mm であり、後述するチップキャパシタの厚みに対応させている。

#### 【0042】

コア材 12 は、例えば、ガラスエポキシ樹脂などの絶縁材料から形成される。あるいは、コア材 12 として、セラミックス板又は銅板などの金属板を使用してもよい。

#### 【0043】

図 5 (a) 及び (b) の例では、銅張積層板 16 を出発材料とし、銅張積層板 16 から銅箔 14 を除去することでコア材 12 を得ているが、銅箔が積層されていないガラスエポキシ樹脂基板をコア材 12 として使用してもよい。本実施形態では、コア材 12 の下面を一方の面とし、上面を他方の面とする。30

#### 【0044】

続いて、図 5 (c) に示すように、ルータ又は金型プレス機によってコア材 12 を厚み方向に貫通加工することにより、開口部 12a を形成する。開口部 12a はキャビティとも呼ばれる。コア材 12 として金属板を使用する場合は、必要に応じて樹脂の電着などによって開口部を含む金属板の両面に絶縁層を形成する。

#### 【0045】

コア材 12 の開口部 12a は、平面視して例えば四角形状で形成され、搭載される電子部品より一回り大きな寸法で形成される。多面取り用の大型のコア材 12 を使用する場合は、複数で画定された製品領域に開口部 12a がそれぞれ形成される。40

#### 【0046】

その後に、図 5 (d) に示すように、コア材 12 の上面(他方の面)に、粘着性を有する仮付テープ 18 を貼り付ける。仮付テープ 18 の一例としては、PET フィルムの表面に絶縁層を設けた樹脂フィルムが使用される。さらに、図 5 (e) に示すように、コア材 12 の開口部 12a 内の仮付テープ 18 にチップキャパシタ 20 を仮接着して搭載する。

#### 【0047】

チップキャパシタ 20 は、横方向の両端側に一対の接続端子 22 を備えており、一対の接続端子 22 がコア材 12 の表面と平行な方向に配置される。チップキャパシタ 20 の接

続端子 22 は両側侧面から上下面の端部まで延在して形成されている。チップキャパシタ 20 の全体の厚みは 0.6 mm であり、コア材 12 の厚みとほぼ同一に設定される。

#### 【0048】

このように、コア材 12 はチップキャパシタ 20 の全体の厚みに対応する厚みに設定される。コア材 12 の厚みは、好適には、チップキャパシタ 20 (電子部品) の厚みから ± 20 % 以内に設定され、さらに好適には、チップキャパシタ 20 の厚みから ± 10 % 以内に設定される。チップキャパシタ 20 の全体の厚みが 0.5 mm の場合は、コア材 12 の厚みは 0.5 mm ± 50 μm に設定される。

#### 【0049】

チップキャパシタ 20 の一例としては、直方体からなるキャパシタ本体の長手方向の両端に電極が設けられたセラミックチップキャパシタがある。 10

#### 【0050】

電子部品として、チップキャパシタ 20 を例示するが、半導体チップ、抵抗素子、インダクタ素子などの接続端子を備えた各種の電子部品を使用することができる。

#### 【0051】

次いで、図 6 (a) に示すように、半硬化状態 (B ステージ) の樹脂フィルム 30 × を用意し、熱プレス機能を備えた真空ラミネーターによってコア材 12 の下面 (一方の面) に樹脂フィルム 30 × を積層する。樹脂フィルム 30 × として、エポキシ樹脂又はポリイミド樹脂などが使用される。 20

#### 【0052】

さらに、P E T フィルムなどの保護フィルム (不図示) を介して 150 ~ 190 の温度で熱プレスすることにより樹脂フィルム 30 × を硬化させた後に、保護フィルムを除去する。保護フィルムは、熱プレス時に真空ラミネーターに樹脂フィルム 30 × が付着することを防止するために設けられる。 30

#### 【0053】

これにより、図 6 (b) に示すように、コア材 12 の下面に第 1 内側補助絶縁層 30 a が形成される。本実施形態の例では、第 1 内側補助絶縁層 30 a の厚みは 25 μm に設定される、このとき、コア材 12 の開口部 12 a の側面とチップキャパシタ 20 との隙間が第 1 内側補助絶縁層 30 a の充填樹脂部 30 c で埋め込まれ、チップキャパシタ 20 が第 1 内側補助絶縁層 30 a によって封止された状態となる。 30

#### 【0054】

本実施形態では、コア材 12 の厚みとチップキャパシタ 20 の厚みとがほぼ同一に設定されている。このため、コア材 12 の開口部 12 a 内のチップキャパシタ 20 を樹脂封止する際に、樹脂を埋め込む空間の体積が小さい構造となるので、樹脂の充填量を少なくすることができる。 40

#### 【0055】

従って、薄い樹脂フィルム 30 × を低い押圧力で熱プレスすることによって、チップキャパシタ 20 の周りを隙間なく樹脂で埋め込むことができる。

#### 【0056】

これにより、チップキャパシタ 20 にかかる圧力も小さくなるので、チップキャパシタ 20 が仮付テープ 18 から剥がれて傾くことが防止される。さらには、樹脂フィルム 30 × をラミネートする工程の処理時間を短縮することができる。 40

#### 【0057】

なお、本実施形態の例では、コア材 12 の上面に仮付テープ 18 を貼り付け、コア材 12 の下面に第 1 内側補助絶縁層 30 a を形成しているが、これらを逆に配置してもよい。つまり、コア材 12 の上下面のいずれかの一方の面上に仮付テープ 18 を貼り付け、コア材 12 の反対側の他方の面上に第 1 内側補助絶縁層 30 a を形成すればよい。

#### 【0058】

その後に、図 6 (c) に示すように、図 6 (b) の構造体から仮付テープ 18 を除去して、コア材 12 及びチップキャパシタ 20 の上面を露出させる。 50

## 【0059】

続いて、図6(d)に示すように、上記した図6(a)及び(b)と同様な方法により、コア材12の上面に第2補助絶縁層32を形成してチップキャパシタ20の上面を封止する。このとき同時に、コア材12の下面側の第1内側補助絶縁層30aの上に第1外側補助絶縁層30bを形成する。

## 【0060】

第1内側補助絶縁層30a及び第1外側補助絶縁層30bにより第1補助絶縁層30が形成される。本実施形態の例では、第2補助絶縁層32の厚みは50μmに設定され、第1外側補助絶縁層30bの厚みは25μmに設定される。

## 【0061】

ここで、第1内側補助絶縁層30aの上に第1外側補助絶縁層30bをさらに形成する理由について説明する。第1外側補助絶縁層30bを形成しない場合は、第2補助絶縁層32を形成する際に、第1内側補助絶縁層30aの下面がさらに加熱処理されるため、第1内側補助絶縁層30aの下面の表面粗さが第2補助絶縁層32の上面の表面粗さより大きくなってしまう。

## 【0062】

後述するように、第1補助絶縁層30及び第2補助絶縁層32の上にはめっき法に基づいて配線層が形成される。このとき、第1補助絶縁層30及び第2補助絶縁層32の表面粗さは配線層の密着性及びパターン精度に影響を与える。このため、第1補助絶縁層30及び第2補助絶縁層32の表面粗さは、所望の値で同一に設定されることが好ましいからである。

## 【0063】

このようにして、コア材12の下面に第1内側補助絶縁層30a及び第1外側補助絶縁層30bから形成される第1補助絶縁層30が得られ、コア材12の上面に第2補助絶縁層32が得られる。

## 【0064】

コア材12はその下面全体にわたって第1補助絶縁層30と直接接触している。また同様に、コア材12はその上面全体にわたって第2補助絶縁層32と直接接触している。このようにして、コア材12、第1補助絶縁層30及び第2補助絶縁層32からコア基板10が形成される。

## 【0065】

配線基板では、伝送経路のインピーダンス整合などの要求から、コア基板の誘電率や厚みが最適値に調整される。本実施形態では、コア材12の開口部12aに配置されたチップキャパシタ20を樹脂で信頼性よく容易に埋め込むために、コア材12の厚みをチップキャパシタ20の厚みとほぼ同一に設定している。

## 【0066】

しかし、コア材12の厚みはインピーダンス整合のための設計値より薄くなるため、コア材12の両面に第1補助絶縁層30及び第2補助絶縁層32を形成することにより、設計スペックの厚みのコア基板10を得ている。本実施形態の例では、コア基板10の厚みは合計で0.6mmとなっており、チップキャパシタ20の厚み：0.5mmより厚くすることができる。

## 【0067】

このように、第1補助絶縁層30及び第2補助絶縁層32は、コア材12に積層されて所望の厚みのコア基板10を得るために形成される。このため、コア材12と第1補助絶縁層30及び第2補助絶縁層32との各界面には配線層は介在しておらず、コア材12は上下面の全体にわたって第1補助絶縁層30及び第2補助絶縁層32と直接接触した構造となる。

## 【0068】

コア材12と第1補助絶縁層30及び第2補助絶縁層32とによりコア基板10が形成されるので、それらは同一の誘電率の絶縁材料から形成されることが好ましい。

10

20

30

40

50

## 【0069】

なお、前述した形態では、コア材12の両面側の第1、第2補助絶縁層30、32の表面粗さを同一に設定するために、コア材12の下面に第1内側補助絶縁層30a及び第1外側補助絶縁層30bを積層している。

## 【0070】

この形態の他に、コア材12の両面側の第1、第2補助絶縁層の表面粗さが異なっても問題ない場合は、第1外側補助絶縁層30bを形成する必要はない。また、第1外側補助絶縁層30bの形成の有無に係らず、コア材12の両面側の第1、第2補助絶縁層30、32の厚みは、所望の厚みのコア基板10を得るために任意に設定することができる。

## 【0071】

次いで、図7(a)に示すように、コア材12の上面側において、第2補助絶縁層32をレーザで加工することにより、チップキャパシタ20の接続端子22に到達する第1ビアホールVH1を形成する。

## 【0072】

このとき、樹脂から形成された第2補助絶縁層32のみをレーザで加工するので、レーザ加工の条件として、チップキャパシタ20の接続端子22をほとんど加工しない低出力の条件に設定することができる。

## 【0073】

従って、チップキャパシタ20の接続端子22が厚み:5μm程度の薄膜の銅電極から形成される場合であっても、レーザ加工によって接続端子22が極端に薄くなったり、消失したりすることはない。また、第2補助絶縁層32は、厚みをかなり薄く設定できるという観点からも、レーザ加工時のチップキャパシタ20の接続端子22の損傷を防止できる。

## 【0074】

その後に、過マンガン酸法などのデスマニア処理によって、第1ビアホールVH1内の樹脂スミアを除去してクリーニングする。

## 【0075】

続いて、図7(b)に示すように、コア材12の上面側において、第1ビアホールVH1を介してチップキャパシタ20の接続端子22に接続される第1配線層40を形成する。また、コア材12の下面側の第1補助絶縁層30の上に第1配線層40を形成する。第1配線層40の厚みは10μm~50μmであり、チップキャパシタ20の接続端子22の厚み:5μmよりかなり厚く設定される。

## 【0076】

第1配線層40は、例えば、サブトラクティブ法によって形成される。詳しく説明すると、コア材12の上面側では、まず、第1ビアホールVH1内及び第2補助絶縁層32の上に無電解めっきによって銅などのシード層(不図示)を形成する。その後に、シード層をめっき給電経路に利用する電解めっきにより、シード層の上に銅などの金属めっき層(不図示)を形成する。

## 【0077】

さらに、フォトリソグラフィ及びエッティングにより、金属めっき層及びシード層をパターニングして第1配線層40を得る。サブトラクティブ法の他に、セミアディティブ法などの各種の配線形成方法を採用することができる。コア材12の下面側にも同様な方法で第1配線層40が形成される。

## 【0078】

次いで、図7(c)に示すように、プリプレグ50aの一方の面に銅箔50bが接着された銅箔付プリプレグCPを用意する。プリプレグ50aは、ガラス繊維、アラミド繊維、炭素繊維などの繊布又は不織布の繊維補強材に熱硬化性樹脂、例えばエポキシ樹脂を含浸させ、加熱乾燥することによって半硬化状態(Bステージ)にしたものである。金属箔として銅箔50bを例示するが、各種の金属箔が接着された繊維補強材含有樹脂を使用することができる。

**【0079】**

そして、図7(b)の構造体の両面に、銅箔付プリプレグCPのプリプレグ50aの面をそれぞれ配置し、190～220の温度で加熱処理しながら金型でプレス成形する。

**【0080】**

銅箔付プリプレグCPの銅箔50bは、プリプレグ50aを加熱して溶融させる際に、金型への樹脂の付着を防止すると共に、後に配線層の一部として利用される。

**【0081】**

これにより、図8(a)に示すように、コア材12の下面側の第1補助絶縁層30及び第1配線層40の上に、プリプレグ50aから形成された第1層間絶縁層50が得られる。また同様に、コア材12の上面側の第2補助絶縁層32及び第1配線層40の上に、プリプレグ50aから形成された第1層間絶縁層50が得られる。10

**【0082】**

コア材12の両面側の第1層間絶縁層50は、その外面に銅箔50bが接着された状態でそれぞれ形成される。

**【0083】**

例えば、第1層間絶縁層50の厚みは50μm～100μmであり、銅箔50bの厚みは10μm～35μmである。

**【0084】**

図7(c)及び図8(a)の例では、銅箔付プリプレグCPを積層して第1層間絶縁層50を得ている。この他に、分離された別体のプリプレグ及び銅箔をコア材12の両面側に順に積層し、加熱及び加圧して第1層間絶縁層50を得てもよい。20

**【0085】**

次いで、図8(b)に示すように、コア材12の上面側において、銅箔50b及び第1層間絶縁層50をレーザで加工することにより、第1配線層40に到達する第2ビアホールVH2を形成する。

**【0086】**

このとき、銅ダイレクトレーザ加工となり、レーザ加工の条件として、銅箔50b及びプリプレグ50aから形成された第1層間絶縁層50を加工できる高出力の条件に設定される。このため、第2ビアホールVH2をレーザ加工で形成する際に、第1配線層40がレーザによって多少削られるが、第1配線層40は十分な厚みを有するため、第1配線層40が極端に薄くなったり、消失したりすることはない。30

**【0087】**

このように、チップキャパシタ20の接続端子22の上に第1ビアホールVH1を介して第1配線層40がかさ上げされて配置されている。これにより、第1配線層40が第2ビアホールVH2を形成する際の高出力のレーザ加工のストップ層として機能し、チップキャパシタ20の接続端子22を保護することができる。

**【0088】**

なお、本実施形態では、第1層間絶縁層50を銅箔付プリプレグCPから形成したが、エポキシ樹脂などの樹脂フィルムから第1層間絶縁層50を形成してもよい。この場合、厚い樹脂フィルムをラミネートするとしても、第1配線層40がレーザ加工のストップ層となるため、厚い層間絶縁層を有するビア接続構造を信頼性よく形成することができる。40

**【0089】**

続いて、図8(c)に示すように、図8(b)の構造体の最上の銅箔50bから最下の銅箔50bまで、ドリル又はレーザによって貫通加工することによりスルーホールTHを形成する。このとき、スルーホールTHの側面に第1配線層40の断面が露出した状態となる。

**【0090】**

その後に、過マンガン酸法などのデスマニア処理によって、第2ビアホールVH2内及びスルーホールTH内の樹脂スミアを除去してクリーニングする。50

**【0091】**

次いで、図8(c)の構造体の両面側、及びスルーホールTHの内面に、無電解めっきによって銅などのシード層を形成する。その後に、シード層をめっき給電経路に利用する電解めっきにより銅などの金属層を形成する。

**【0092】**

これにより、図9(a)に示すように、図8(c)の構造体の両面側、及びスルーホールTHの内面に第1金属めっき層42aが得られる。このとき、スルーホールTHの側面に配置された第1配線層40に第1金属めっき層42aが電気的に接続された状態となる。

**【0093】**

さらに、図9(b)に示すように、コア材12の両面側において、スルーホールTH内の残りの孔に樹脂体Rを充填した後に、スルーホールTHからはみ出した余分な樹脂を研磨する。

**【0094】**

これにより、コア材12の両面側において、スルーホールTH内の樹脂体Rの外面と第1金属めっき層42aの外面とが同一面となって平坦化される。その後に、デスマニア処理によって、両面側の第1金属めっき層42aの表面をクリーニングする。

**【0095】**

続いて、図9(c)に示すように、前述した図9(a)の工程と同様な方法により、図9(b)の構造体の両面側の第1金属めっき層42aの上に、第2金属めっき層42bを形成する。さらに、コア材12の両面側において、フォトリソグラフィ及びエッチングにより、第2金属めっき層42b、第1金属めっき層42a及び銅箔50bをパターニングする。

**【0096】**

これにより、図10に示すように、コア材12の両面側において、第1層間絶縁層50の上に第2配線層42がそれぞれ形成される。第2配線層42は、下から順に、銅箔50b、第1金属めっき層42a及び第2金属めっき層42bが配置されて形成される。

**【0097】**

コア材12の上面側では、第2配線層42は第2ビアホールVH2を介して第1配線層40に接続される。両面側の第2配線層42は、スルーホールTHの側面に延在する第1金属めっき層42aを介して相互接続される。以上により、本実施形態の電子部品内蔵基板1が得られる。

**【0098】**

なお、多面取り用の大型のコア材12を使用する場合は、各製品領域から個々の電子部品内蔵基板1が得られるように分割される。

**【0099】**

また、本実施形態の例では、コア材12の両面側に2層の多層配線をそれぞれ形成しているが、配線層の積層数は任意に設定することができる。また、コア材12の両面側において、最上層及び最下層として、配線層の接続部上に開口部が設けられたソルダレジストを形成してもよい。

**【0100】**

図10に示すように、実施形態の電子部品内蔵基板1では、厚み方向の中央部にコア材12が配置されており、コア材12はその厚み方向に貫通する開口部12aを備えている。コア材12の開口部12aにチップキャパシタ20が配置されている。チップキャパシタ20は横方向の両端側に接続端子22を備えている。コア材12の厚みはチップキャパシタ20の全体の厚みに対応している。

**【0101】**

コア材12の下面(一方の面)には、第1内側補助絶縁層30aが形成されており、コア材12の開口部12aの側面とチップキャパシタ20との隙間が充填樹脂部30cで埋め込まれている。第1内側補助絶縁層30aの下には第1外側補助絶縁層30bが積層さ

10

20

30

40

50

れており、第1内側補助絶縁層30a及び第1外側補助絶縁層30bによって第1補助絶縁層30が形成される。

#### 【0102】

このように、コア材12の下面側の第1補助絶縁層30は、複数の樹脂層が積層されて形成され、コア材12に接触する第1内側補助絶縁層30aがコア材12の開口部12aに充填されて、充填樹脂部30cが形成される。また、コア材12の上面（他方の面）には第2補助絶縁層32が形成されている。

#### 【0103】

コア材12は、その一方の面及び他方の面の全体にわたって第1補助絶縁層30及び第2補助絶縁層32と直接接觸しており、それらの界面に配線層は介在していない。これにより、コア材12、第1補助絶縁層30及び第2補助絶縁層32によってコア基板10が形成されている。10

#### 【0104】

コア材12の上面側において、第2補助絶縁層32にはチップキャパシタ20の接続端子22に到達する第1ビアホールVH1が形成されている。第2補助絶縁層32の上には、第1ビアホールVH1を介してチップキャパシタ20の接続端子22に接続される第1配線層40が形成されている。さらに、コア材12の下面側の第1補助絶縁層30の上に第1配線層40が形成されている。

#### 【0105】

また、コア材12の上面側において、第2補助絶縁層32及び第1配線層40の上に第1層間絶縁層50が形成されており、第1層間絶縁層50の中央部には第1配線層40に到達する第2ビアホールVH2が形成されている。上面側の第1層間絶縁層50の上には第2ビアホールVH2を介して第1配線層40に接続される第2配線層42が形成されている。20

#### 【0106】

コア材12の上面側の第1配線層40は、第2ビアホールVH2を形成する工程で高出力のレーザ加工を行う際のストッパ層として機能し、チップキャパシタ20の接続端子22がそのレーザ加工から保護される。このため、第1配線層40の厚みはチップキャパシタ20の接続端子22の厚みより厚く設定される。

#### 【0107】

コア材12の両面側の第1層間絶縁層50は、銅箔付プリプレグCPを熱プレスすることによりそれぞれ形成される。このため、第2配線層42は銅箔50b（金属箔）を含み、銅箔50bの上に第1金属めっき層42a及び第2金属めっき層42bが積層されて形成される。30

#### 【0108】

また、コア材12の下面側において、第1補助絶縁層30及び第1配線層40の上に第1層間絶縁層50が形成されている。

#### 【0109】

さらに、電子部品内蔵基板1の両端部には、上面側の第1層間絶縁層50から下面側の第1層間絶縁層50まで貫通して形成されたスルーホールTHが設けられている。両面側の第1層間絶縁層50上において、スルーホールTHの上に配置された第2配線層42は、スルーホールTHの側面に延在する第1金属めっき層42aを介して相互接続されている。また、両面側の第2配線層42は、スルーホールTHの側面の第1金属めっき層42aを介して第1配線層40に接続されている。40

#### 【0110】

前述したように、本実施形態の電子部品内蔵基板の製造方法では、コア材12の厚みをチップキャパシタ20の厚みに対応させている。これにより、コア材12の開口部12aに配置されたチップキャパシタ20の周りの隙間を、樹脂フィルム30xを熱プレスして埋め込む際に、埋め込む空間の体積を小さくすることができる。

#### 【0111】

10

20

30

40

50

これにより、樹脂フィルム 30 ×を低い押圧力で熱プレスすることによって、チップキャパシタ 20 の周辺を隙間なく樹脂で信頼性よく埋め込むことができる。従って、チップキャパシタ 20 にかかる圧力も小さくなるため、チップキャパシタ 20 が仮付フィルム 18 から剥がれて傾くことが防止される。

#### 【0112】

そして、コア材 12 の厚みの不足分を第 1 補助絶縁層 30 及び第 2 補助絶縁層 32 によって補って調整することにより、所望の厚みのコア基板 10 を得ることができる。これによって、伝送経路のインピーダンス整合などの設計スペックを満足させることができる。

#### 【0113】

また、チップキャパシタ 20 の接続端子 22 は、第 2 補助絶縁層 32 の第 2 ピアホール VH2 を介して厚みの厚い第 1 配線層 40 によってかさ上げされている。そして、第 1 配線層 40 の上に銅箔付プリプレグ CP が積層されて、銅箔 50b が接着された第 1 層間絶縁層 50 が形成される。10

#### 【0114】

このため、銅箔 50b 及びプリプレグ 50a から形成される第 1 層間絶縁層 50 を高出力のレーザで加工して第 2 ピアホール VH2 を形成する際に、厚みの厚い第 1 配線層 40 がレーザ加工にストップ層として機能する。

#### 【0115】

これにより、チップキャパシタ 20 の接続端子 22 は第 1 配線層 40 によって保護されるため、レーザ加工で損傷が生じるおそれがない。このため、チップキャパシタ 20 の接続端子 22 は、第 1 、第 2 配線層 40 , 42 と信頼性よく電気的に接続される。20

#### 【0116】

以上のように、本実施形態では、設計スペックの所望の特性を有する電子部品内蔵基板を歩留りよく製造できると共に、電子部品内蔵基板の信頼性を向上させることができる。

#### 【0117】

図 11 には、最上の配線層に半導体チップが接続される場合に好適に使用される電子部品内蔵基板 2 が示されている。図 11 の電子部品内蔵基板 2 では、図 10 の電子部品内蔵基板 1 の両面側に第 2 層間絶縁層 52 がそれぞれ形成されている。

#### 【0118】

第 2 層間絶縁層 52 はエポキシ樹脂やポリイミド樹脂などの樹脂フィルムが積層されて形成される。両面側の第 2 層間絶縁層 52 には、第 2 配線層 42 に到達する第 3 ピアホール VH3 が形成されている。第 3 ピアホール VH3 は、第 2 層間絶縁層 52 がレーザによつて加工されて形成される。30

#### 【0119】

さらに、コア材 12 の両面側の第 2 層間絶縁層 52 の上に、第 3 ピアホール VH3 を介して第 2 配線層 42 に接続される第 3 配線層 44 がそれぞれ形成されている。第 3 配線層 44 はセミアディティブ法などで形成される。

#### 【0120】

また、コア材 12 の両面側の第 2 層間絶縁層 52 の上に、第 3 配線層 44 のパッド部上に開口部 54a が設けられたソルダーレジスト 54 がそれぞれ形成されている。必要に応じて、両面側の第 3 配線層 44 のパッド部にニッケル／金めっき層などのコンタクト層（不図示）が形成される。配線層の積層数は任意に設定することができる。40

#### 【0121】

そして、図 12 に示すように、図 11 の電子部品内蔵基板 2 の上面側の第 3 配線層 44 のパッド部に半導体チップ 60 のバンプ電極 62 がフリップチップ接続される。さらに、半導体チップ 60 の下側の隙間にアンダーフィル樹脂 64 が充填される。

#### 【符号の説明】

#### 【0122】

1 , 2 ... 電子部品内蔵基板、 10 ... コア基板、 12 ... コア材、 12a , 54a ... 開口部、

14 , 50b ... 銅箔、 16 ... 銅張積層板、 18 ... 仮付テープ、 20 ... チップキャパシタ、50

2 2 ...接続端子、3 0 ...第1補助絶縁層、3 0 a ...第1内側補助絶縁層、3 0 b ...第1外側補助絶縁層、3 0 c ...充填樹脂部、3 0 x ...樹脂フィルム、3 2 ...第2補助絶縁層、4 0 ...第1配線層、4 2 ...第2配線層、4 2 a ...第1金属めっき層、4 2 b ...第2金属めっき層、4 4 ...第3配線層、5 0 ...第1層間絶縁層、5 0 a ...プリプレグ、5 2 ...第2層間絶縁層、5 4 ...ソルダレジスト、6 0 ...半導体チップ、6 2 ...バンプ電極、6 4 ...アンダーフィル樹脂、C P ...銅箔付プリプレグ、V H 1 ...第1ビアホール、V H 2 ...第2ビアホール、V H 3 ...第3ビアホール、R ...樹脂体、T H ...スルーホール。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

---

フロントページの続き

審査官 岡崎 克彦

(56)参考文献 特開2009-302563(JP,A)

特開2011-187919(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 05 K 3 / 46

H 01 L 23 / 12