(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6230329号

(P6230329)

(45) 発行日 平成29年11月15日(2017.11.15)

(24) 登録日 平成29年10月27日(2017.10.27)

|                       |               |

|-----------------------|---------------|

| (51) Int.Cl.          | F 1           |

| HO4N 5/369 (2011.01)  | HO4N 5/369    |

| HO4N 5/357 (2011.01)  | HO4N 5/357    |

| HO4N 5/374 (2011.01)  | HO4N 5/374    |

| HO1L 27/146 (2006.01) | HO1L 27/146 A |

請求項の数 12 (全 16 頁)

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願2013-169507 (P2013-169507) |

| (22) 出願日  | 平成25年8月19日 (2013.8.19)       |

| (65) 公開番号 | 特開2015-39124 (P2015-39124A)  |

| (43) 公開日  | 平成27年2月26日 (2015.2.26)       |

| 審査請求日     | 平成28年8月9日 (2016.8.9)         |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74) 代理人  | 100126240<br>弁理士 阿部 琢磨                     |

| (74) 代理人  | 100124442<br>弁理士 黒岩 創吾                     |

| (72) 発明者  | 岩根 正晃<br>東京都大田区下丸子3丁目30番2号キヤノン株式会社内        |

| (72) 発明者  | 沖田 彰<br>東京都大田区下丸子3丁目30番2号キヤノン株式会社内         |

審査官 松永 隆志

最終頁に続く

(54) 【発明の名称】撮像装置

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の光電変換素子と、前記複数の光電変換素子で生じた信号を増幅する増幅トランジスタと、前記複数の光電変換素子で生じた信号をリセットするリセットトランジスタと、を有する画素ユニットを複数備える撮像装置であって、

前記画素ユニットから出力されるノイズ信号を保持し、後段の回路に出力するノイズ信号保持部と、

前記画素ユニットから出力される、N個（Nは1以上の整数）の前記光電変換素子で生じた信号に基づく第1の光信号を保持し、前記後段の回路に出力する第1の信号保持部と、

前記画素ユニットから出力される、M個（Mは2以上の整数でNよりも大きい）の前記光電変換素子で生じた信号に基づく第2の光信号を保持し、前記後段の回路に出力する第2の信号保持部と、を有し、

平面視において、

前記ノイズ信号保持部は、第1のシールド配線と第2のシールド配線の間に配され、

前記第2の信号保持部は、前記第2のシールド配線と第3のシールド配線の間に配され

、前記第1の信号保持部は、前記第3のシールド配線と第4のシールド配線の間に配され

、前記第1の信号保持部と前記第4のシールド配線との距離は、前記ノイズ信号保持部と

前記第2のシールド配線との距離、及び前記第2の信号保持部と前記第3のシールド配線との距離のいずれよりも大きいことを特徴とする撮像装置。

**【請求項2】**

前記第1の信号保持部と前記第4のシールド配線との距離は、前記ノイズ信号保持部と前記第1のシールド配線との距離、及び前記第2の信号保持部と前記第2のシールド配線との距離のいずれよりも大きいことを特徴とする請求項1に記載の撮像装置。

**【請求項3】**

複数の光電変換素子と、前記複数の光電変換素子で生じた信号を増幅する増幅トランジスタと、前記複数の光電変換素子で生じた信号をリセットするリセットトランジスタと、

を有する画素ユニットを複数備える撮像装置であって、

10

前記画素ユニットから出力されるノイズ信号を保持するノイズ信号保持部と、

前記画素ユニットから出力される、N個（Nは1以上の整数）の前記光電変換素子で生じた信号に基づく第1の光信号を保持する第1の信号保持部と、

前記画素ユニットから出力される、M個（Mは2以上の整数でNよりも大きい）の前記光電変換素子で生じた信号に基づく第2の光信号を保持する第2の信号保持部と、を有し、

前記ノイズ信号保持部及び前記第2の信号保持部は、並進対称となるように配置され、

前記第1の信号保持部は、前記ノイズ信号保持部及び前記第2の信号保持部のいずれに対しても並進対称ではないことを特徴とする撮像装置。

**【請求項4】**

20

複数の光電変換素子と、前記複数の光電変換素子で生じた信号を増幅する増幅トランジスタと、前記複数の光電変換素子で生じた信号をリセットするリセットトランジスタと、

を有する画素ユニットを複数備える撮像装置であって、

前記画素ユニットから出力されるノイズ信号を保持するノイズ信号保持部と、

前記画素ユニットから出力される、N個（Nは1以上の整数）の前記光電変換素子で生じた信号に基づく第1の光信号を保持する第1の信号保持部と、

前記画素ユニットから出力される、M個（Mは2以上の整数でNよりも大きい）の前記光電変換素子で生じた信号に基づく第2の光信号を保持する第2の信号保持部と、を有し、前記第1の信号保持部を平面視した際の面積は、少なくとも前記第2の信号保持部および前記ノイズ信号保持部の1つを平面視した際の面積よりも小さいことを特徴とする撮像装置。

30

**【請求項5】**

前記画素ユニットと、前記ノイズ信号保持部、前記第1の信号保持部、前記第2の信号保持部のいずれかとの間には、前記画素ユニットから出力された信号を増幅する増幅回路を有することを特徴とする請求項1～4のいずれか1項に記載の撮像装置。

**【請求項6】**

各々が、前記ノイズ信号保持部、前記第1の信号保持部及び前記第2の信号保持部の各々に対応して設けられた、複数のバッファを有することを特徴とする請求項1～5のいずれか1項に記載の撮像装置。

**【請求項7】**

40

前記ノイズ信号保持部で保持された信号をバッファするバッファ及び前記第2の信号保持部で保持された信号をバッファするバッファは、前記第1の信号保持部で保持された信号をバッファするバッファに比べて、入力インピーダンスあるいはオープンループゲインが大きく、出力インピーダンスが小さいことを特徴とする請求項6に記載の撮像装置。

**【請求項8】**

前記ノイズ信号保持部で保持された信号をバッファするバッファ、及び、前記第2の信号保持部で保持された信号をバッファするバッファは、前記第1の信号保持部で保持された信号をバッファするバッファに比べて、バイアス電流が大きいことを特徴とする請求項6に記載の撮像装置。

**【請求項9】**

50

前記ノイズ信号保持部と前記第2の信号保持部の信号を、それぞれ対応するバッファから同時に読み出し、その後、差分処理を行い、

次に前記ノイズ信号保持部と前記第1の信号保持部の信号を、それぞれ対応するバッファから同時に読み出し、その後、差分処理を行うことを特徴とする請求項6乃至8のいずれか1項に記載の撮像装置。

#### 【請求項10】

前記複数のバッファから出力された信号を保持する信号保持部を有することを特徴とする請求項6～9のいずれか1項に記載の撮像装置。

#### 【請求項11】

前記第1の信号保持部が保持する第1の光信号は焦点検出用の信号であり、前記第2の信号保持部が保持する第2の光信号は撮像用の信号であることを特徴とする請求項1～10のいずれか1項に記載の撮像装置。 10

#### 【請求項12】

前記第1の信号保持部は、第1のバッファ及び第1のスイッチを介して第3の信号保持部に接続され、

前記第2の信号保持部は、第2のバッファ及び第2のスイッチを介して前記第3の信号保持部に接続され、

前記ノイズ信号保持部は、第3のバッファ及び第3のスイッチを介して第4の信号保持部に接続されていることを特徴とする請求項1～5及び11のいずれか1項に記載の撮像装置。 20

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は撮像装置に関し、特に撮像装置の列回路の信号保持部のレイアウトに関する。

##### 【背景技術】

##### 【0002】

C MOSエリアセンサチップをはじめ撮像装置には画素微細化や高機能化をしながら高いS/Nが求められる。高いS/Nを得るために、特許文献1の図12に示されているように、ノイズ信号用アナログメモリと撮像信号用アナログメモリは列信号線が伸びる方向に対して並列に配置されている。 30

##### 【先行技術文献】

##### 【特許文献】

##### 【0003】

【特許文献1】特開2009-224524号公報

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0004】

列回路は画素ピッチまたは画素ピッチの整数倍内に配置する必要がある、しかしながら、画素から撮像信号と共にフォーカス信号を読み出すような構成においては、列回路の規模が大きくなる傾向にある。このような構成においては、所定の領域内に列回路を配置するのが困難になる場合がある。本発明は、列回路の好適なレイアウトを提供することである。 40

##### 【課題を解決するための手段】

##### 【0005】

本発明の一様態は、複数の光電変換素子と、前記複数の光電変換素子で生じた信号を増幅する増幅トランジスタと、前記複数の光電変換素子で生じた信号をリセットするリセットトランジスタと、を有する画素ユニットを複数備える撮像装置であって、前記画素ユニットから出力されるノイズ信号を保持するノイズ信号保持部と、前記画素ユニットから出力される、N個（Nは1以上の整数）の前記光電変換素子で生じた信号に基づく、第1の光信号を保持する第1の信号保持部と、前記画素ユニットから出力される、M個（Mは2

以上の整数でNよりも大きい)の前記光電変換素子で生じた信号に基づく、第2の光信号を保持する第2の信号保持部と、を有し、前記第2の信号保持部で保持された後の第2の光信号と、前記ノイズ信号保持部で保持された後のノイズ信号とを差分する際のノイズ除去率が、前記第1の信号保持部で保持された後の第1の光信号と、前記ノイズ信号保持部で保持された後のノイズ信号とを差分する際のノイズ除去率よりも大きい撮像装置に関する。

また、本発明の一様態は、複数の光電変換素子と、前記複数の光電変換素子で生じた信号を増幅する増幅トランジスタと、前記複数の光電変換素子で生じた信号をリセットするリセットトランジスタと、を有する画素ユニットを複数備える撮像装置であって、

前記画素ユニットから出力されるノイズ信号を保持するノイズ信号保持部と、

前記画素ユニットから出力される、N個(Nは1以上の整数)の前記光電変換素子で生じた信号に基づく第1の光信号を保持する第1の信号保持部と、

前記画素ユニットから出力される、M個(Mは2以上の整数でNよりも大きい)の前記光電変換素子で生じた信号に基づく第2の光信号を保持する第2の信号保持部と、を有し、

前記第1の信号保持部は、前記ノイズ信号保持部及び前記第1の信号保持部のいずれに対しても並進対称ではない撮像装置に関する。

本発明の別の一様態は、複数の光電変換素子と、前記複数の光電変換素子で生じた信号を増幅する増幅トランジスタと、前記複数の光電変換素子で生じた信号をリセットするリセットトランジスタと、を有する画素ユニットを複数備える撮像装置であって、

前記画素ユニットから出力されるノイズ信号を保持するノイズ信号保持部と、

前記画素ユニットから出力される、N個(Nは1以上の整数)の前記光電変換素子で生じた信号に基づく第1の光信号を保持する第1の信号保持部と、

前記画素ユニットから出力される、M個(Mは2以上の整数でNよりも大きい)の前記光電変換素子で生じた信号に基づく第2の光信号を保持する第2の信号保持部と、を有し、前記第1の信号保持部を平面視した際の面積は、少なくとも前記第2の信号保持部および前記ノイズ信号保持部の1つを平面視した際の面積よりも小さいことを特徴とする撮像装置に関する。

#### 【発明の効果】

#### 【0006】

本発明によれば、列回路の好適なレイアウトを提供することが可能となる。

#### 【図面の簡単な説明】

#### 【0007】

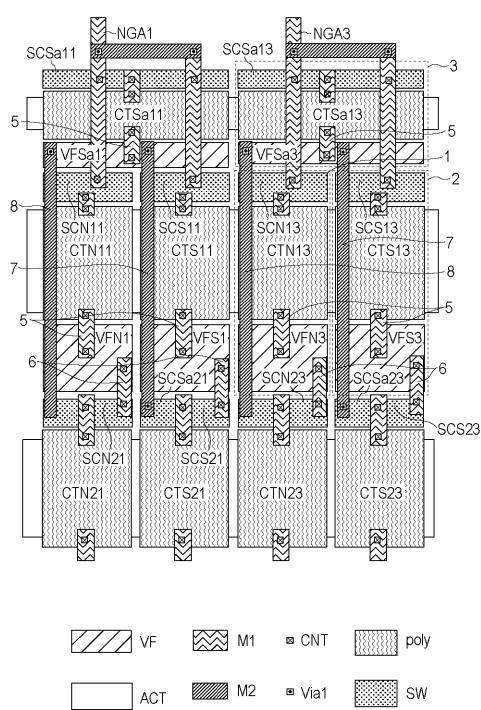

【図1】実施例1の撮像装置の平面レイアウトの概略図

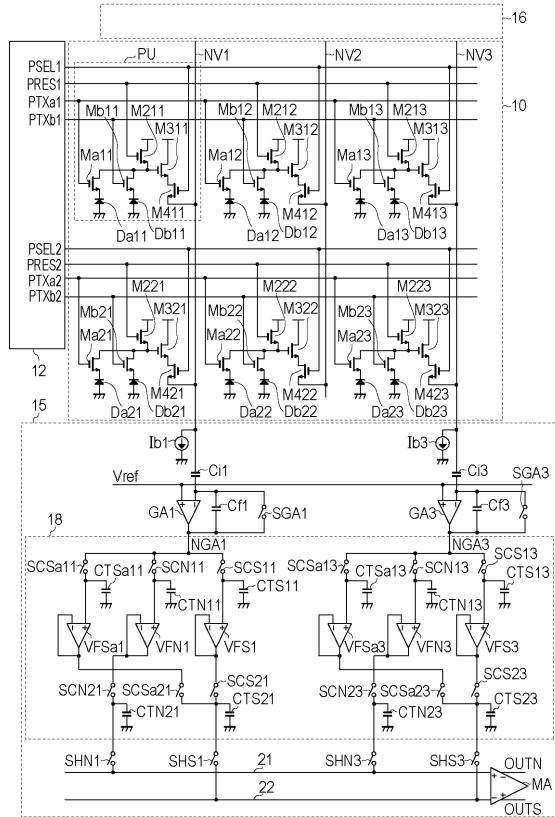

【図2】実施例1の撮像装置の等価回路図

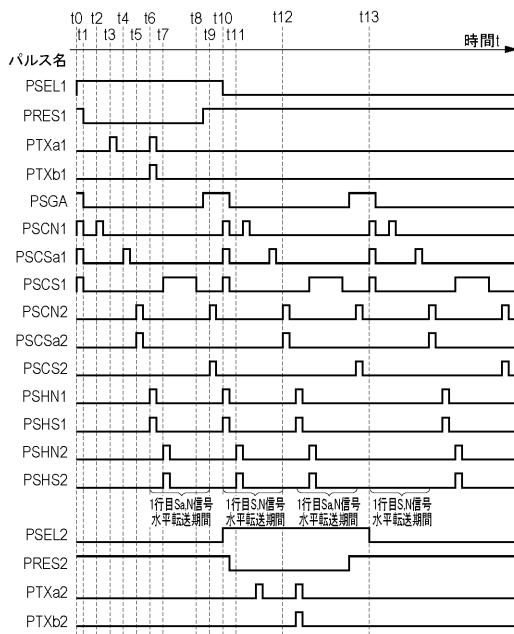

【図3】実施例1の撮像装置のタイミングチャート

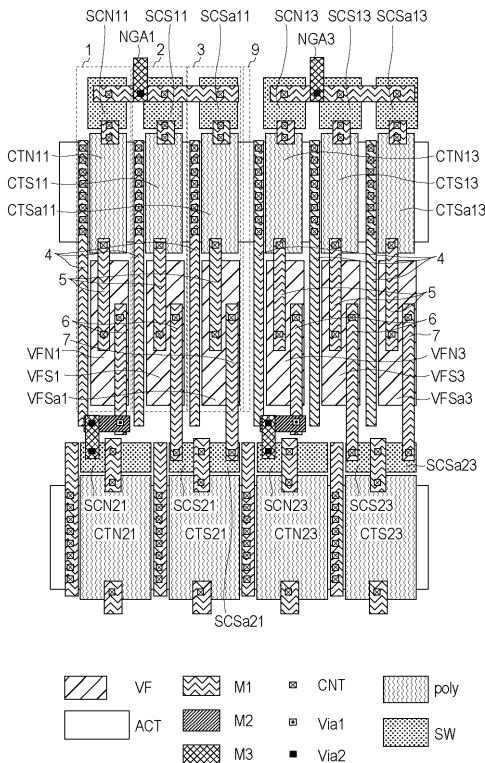

【図4】実施例2の撮像装置の撮像装置の平面レイアウトの概略図

【図5】実施例3の撮像装置の撮像装置の平面レイアウトの概略図

#### 【発明を実施するための形態】

#### 【0008】

まず本発明を実現する一実施形態を説明する。

#### 【0009】

本発明の撮像装置は、複数の光電変換素子と、複数の光電変換素子で生じた信号を増幅する増幅トランジスタと、複数の光電変換素子で生じた信号をリセットするリセットトランジスタとを有する画素ユニットを複数備える。一例として図2には画素ユニットP Uが2行×3列で配されて画素領域10が形成された例が示されている。

#### 【0010】

例えば一例として画素ユニットが2つの光電変換素子(D a、D b)を有すると仮定する。このような画素ユニットから、ノイズ信号、一方の光電変換素子で生じた信号に基づく第1の光信号、両方の光電変換素子で生じた信号に基づく第2の光信号を出力する。こ

10

20

30

40

50

のような信号を出力する撮像装置の一例としては、撮像面で位相差型の焦点検出を行なう構成が知られている。

【0011】

画素ユニットの後段には、上述のノイズ信号を保持するノイズ信号保持部、第1の光信号を保持する第1の信号保持部、第2の光信号を保持する第2の信号保持部が設けられている。図2では第1の信号保持部としてCTS<sub>a</sub>、ノイズ信号保持部としてCTN、第2の信号保持部としてCTSが示されている。

【0012】

このような構成において、第1の信号保持部で保持された後の第1の光信号と、ノイズ信号保持部で保持された後のノイズ信号とを後段の回路により差分処理を行なう。これにより第1の差分処理信号が得られる。そしてさらに、第2の信号保持部で保持された後の第2の光信号と、ノイズ信号保持部で保持された後のノイズ信号とを後段の回路により差分処理を行なう。これにより第2の差分処理信号が得られる。ここで上述の後段の回路は撮像装置内に配されていてもよいし、撮像装置外に設けられていてもよい。

【0013】

本発明は、第1の差分処理信号と第2の差分処理信号とを比較した際に、第2の差分処理信号の同相ノイズ除去率が第1の差分処理信号の同相ノイズ除去率よりも大きいことを特徴としている。

【0014】

本発明は、撮像装置内で差分処理まで行う例に限らず、後段の回路で上記差分処理を行なうにあたって、上記ノイズ除去率の関係を満たすような信号を後段回路に提供する構成も含む。

【0015】

通常であれば、全ての信号保持部で保持された信号に対して後段の回路で行う差分処理における同相ノイズ除去率は等しい方が好ましい。しかしながら、高S/Nを維持しつつ、同相ノイズ除去率が等しくなるように回路素子をレイアウトすると、全体の回路規模が大きくなり、チップサイズが大きくなり好ましくない。これに対し、本発明のように、同相ノイズ除去率を異ならせることにより、チップ上に占める回路面積を増加させることなく、好適な信号読み出しを行なうことが可能となる。

【0016】

特に第1の信号保持部で保持される信号が焦点検出用の信号であり、第2の信号保持部で保持される信号が撮像用の信号である場合にその効果が高い。撮像用の信号は、画像を形成するための信号であるため、高S/Nが要求される。これに対し、焦点検出用の信号は、位相差検出を行なうに十分な特性があれば十分であり、それほど高いS/Nは要求されない。したがって、このような構成に対し本発明の構成を適用することで、列回路の面積の増加を抑えつつ、好適な信号読み出しを可能となる。

【0017】

更に好ましくは、ノイズ信号保持部と第2の信号保持部とのレイアウトが並進対称であるのがよい。

【0018】

ここで並進対称とは、ノイズ信号保持部及び第2の信号保持部をそれらが並んで配置される方向において並進操作させた際に、リセット信号保持部と第2の信号保持部のレイアウトが一致することをいう。本発明は、少なくとも、一の列回路において並進対象となつていればよい。しかしながら、一般に撮像装置の列回路は、水平方向に沿って繰り返し配置される。したがって、一の列回路のみではなく全ての列回路において、並進対象となっているのがよい。

【0019】

以下本発明を、実施例を挙げて説明する。それぞれの実施形態の有意な組み合わせも本発明の範囲内である。なお図面において数字の符号が振られているものはアドレスを示すものであり、それぞれ行、列の位置を示す。また以下では撮像面で焦点検出を行なうこと

10

20

30

40

50

が可能な構成を例に説明するが、これに限られるものではなく例えば三次元計測用の光電変換装置などにも適用することができる。

#### 【0020】

##### (実施例1)

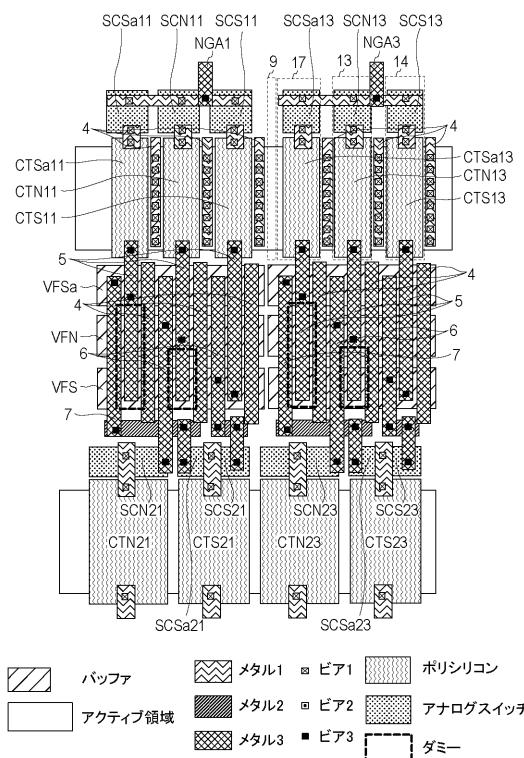

図1、2を用いて、本実施例の撮像装置の説明を行なう。図1は本実施例の撮像装置の等価回路図を示す。また図2は図1の構成において、列回路の一部の平面レイアウトを示すものである。

#### 【0021】

本実施例は、撮像用の信号と焦点検出用の信号とを読み出すことが可能である。このため、撮像装置の各画素ユニットには、位相差検出用であるA像用とB像用の光電変換素子として機能する2つのフォトダイオードD<sub>a</sub>、D<sub>b</sub>が含まれる。カメラなどに用いられるCMOSセンサなどの撮像装置は、画素領域の任意の領域において、A像信号とB像信号のピーク値の位置の違いからフォーカス状態にするためのレンズの移動量を算出し、フォーカス制御を行う。オートフォーカス以外にも、被写体の距離計測ができるので3次元映像情報を得ることも可能である。

#### 【0022】

図1において、画素領域10には、複数の画素ユニットPUが配されている。好ましくは、画素ユニットPUは行列状に配され、例えば数千万の画素ユニットPUが配されて画素領域10が構成される。垂直走査回路12により各画素ユニットPUに駆動パルスが供給される。

10

20

#### 【0023】

次に各画素ユニットの構成に関して説明する。

#### 【0024】

転送トランジスタM<sub>a</sub>11～M<sub>a</sub>23、M<sub>b</sub>11～M<sub>b</sub>23は、対応する光電変換素子の電荷を転送する。転送トランジスタはMOSトランジスタにより構成することができる。

#### 【0025】

リセットトランジスタM<sub>2</sub>11～M<sub>2</sub>23は光電変換素子で生じた信号をリセットする。光電変換素子に信号が存在する状態で光電変換素子をリセットしてもよいし、後述する增幅トランジスタの入力ノードに信号が転送された後の状態で、增幅トランジスタの入力ノードをリセットしてもよい。リセットトランジスタはMOSトランジスタで構成することができる。他には、接合型電界効果トランジスタで構成してもよい。

30

#### 【0026】

増幅トランジスタM<sub>3</sub>11～M<sub>3</sub>23は同一画素ユニットの複数の光電変換素子で生じた信号を増幅する。各増幅トランジスタM<sub>3</sub>11～M<sub>3</sub>23は、複数の光電変換素子に共通に設けられている。増幅トランジスタM<sub>3</sub>11～M<sub>3</sub>23はMOSトランジスタで構成することができる。他には接合型電界効果トランジスタで構成してもよい。

#### 【0027】

選択トランジスタM<sub>4</sub>11～M<sub>4</sub>23は、対応する列出力線に選択的に画素ユニットPUの信号を読み出す。選択トランジスタM<sub>4</sub>11～M<sub>4</sub>23はMOSトランジスタにより構成することができる。もしくはリセットトランジスタなどの動作を工夫することなどによって、選択トランジスタM<sub>4</sub>11～M<sub>4</sub>23を省略することも可能である。

40

#### 【0028】

次に画素ユニット以降の構成に関して説明する。

#### 【0029】

列信号線NVは各画素ユニット列に対応して設けられる。本例では列信号線VNは、各画素ユニット列に対し1本設けられているが複数本設けてもよい。電流源I<sub>b</sub>は、対応する列信号線を介して、増幅トランジスタM<sub>3</sub>11～M<sub>3</sub>23にバイアス電流を供給することで増幅トランジスタM<sub>3</sub>11～M<sub>3</sub>23に増幅動作を行なわせる。増幅動作としては例えばソースフォロワ動作である。

50

**【0030】**

列回路15、16は、垂直走査回路12により走査され画素ユニットPUから列出力線を介して出力された信号を受けて処理する回路である。列回路15は、奇数列の画素ユニットPUからの信号を処理する回路である。列回路16は偶数列の画素ユニットPUからの信号を処理する。列回路15、16で行われる処理は、ノイズ除去、信号の増幅、アナログデジタル変換などである。

**【0031】**

増幅回路GAは、列回路15に設けられ、画素ユニットPUから出力された信号を好ましくは可変ゲインで増幅するものである。クランプ容量Cは画素ユニットから出力されたノイズ信号を低減させるためのものである。

10

**【0032】**

信号保持部18は増幅回路GAで増幅された後の信号を保持する回路である。増幅回路GAから見て、並列に3系統の回路が設けられている。それぞれノイズ信号を保持する回路（ノイズ信号保持部）と第1の光信号を保持する回路（第1の信号保持部）及び第2の光信号を保持する回路（第2の信号保持部）を含んでいる。ここで第1の光信号と第2の光信号との違いは、第1の光信号は、所定の画素ユニットのN個（Nは1以上の整数）の光電変換素子で生じた信号に基づく光信号である。これは例えば焦点検出用の信号である。そして第2の光信号は、所定の画素ユニットのM個（Mは2以上の整数でNよりも大きい）の光電変換素子で生じた信号に基づく光信号である。これは例えば撮像用の信号である。

20

**【0033】**

図1のレイアウト図は信号保持部18に該当する部分である。図1と図2とで同様の部分には同じ符号を付している。

**【0034】**

出力アンプMAは、列回路15で処理された後、水平出力線21、22を伝達してきた信号を撮像装置外へ出力する。

**【0035】**

図2に示すように、列回路16は、画素領域10を挟んで列回路15の反対側に配置されている。1列分の列回路15と列回路16は、画素領域10の2画素分のピッチ内に配される。画素領域10の奇数列のフォトダイオードDa11、Db11、Da13、Db13で検出された光信号は列回路15に読みだされる。一方、画素部10の偶数列のフォトダイオードDa12、Db12で検出された光信号は列回路16に読みだされる。以下、列回路15について詳述するが、列回路16も同様の回路およびレイアウトとすることができます。

30

**【0036】**

次に図1の凡例に関して説明する。図面右側に各構成要素の凡例を示している。

**【0037】**

回路構成要素として、枠線内が荒い斜線でハッチングされた領域（VF）にはバッファが配置される。また枠線内がドットで示された領域（SW）にはアナログスイッチが配置される。

40

**【0038】**

また、各回路構成要素間をつなぐ部材、もしくは、アナログメモリを構成する部材としては、アクティブ領域、各種配線層、ポリシリコン、コンタクトプラグ、ビアプラグなどがある。枠線内が空白となった領域にはアクティブ領域が配置される。枠線内が横方向の波線でハッチングされた領域（M1）には第1の配線層が配置される。枠線内が細かい斜線でハッチングされた領域（M2）には第2の配線層が配置される。第2の配線層は第1の配線層よりも上層に配される層である。枠線内に×印で示される領域（CNT）には、アクティブ領域と第1の配線層もしくはポリシリコンと第1の配線層を接続するコンタクトプラグが配置される。枠線内黒丸で示された領域（Via1）には、第1の配線層と第2の配線層とを接続するビアプラグが配置される。各回路要素を構成する枠線内が縦方向

50

の波線でハッチングされた領域 ( p o l y ) にはポリシリコンが配置される。

**【 0 0 3 9 】**

バッファ及びアナログスイッチが配される領域内の詳細なレイアウトは図示していないが、アクティブ領域、ポリシリコン、各配線層、コンタクトプラグ、ビアプラグで構成される。

**【 0 0 4 0 】**

リセット信号保持部は、ノイズ信号サンプリング用のスイッチ S C N とアナログメモリ C T N を有する。また、アナログメモリ C T N の後段にはこれに対応してバッファ V F N が配されている。第 1 の信号保持部は、第 1 光信号サンプリング用のスイッチ S C S a とアナログメモリ C T S a を有する。アナログメモリ C T S a の後段にはこれに対応して、バッファ V F S a が配されている。第 2 の信号保持部は、第 2 光信号サンプリング用のスイッチ S C S とアナログメモリ C T S を有する。アナログメモリ C T S の後段にはこれに 10 対応してバッファ V F S が配されている。

**【 0 0 4 1 】**

図 1において、セット 1 は、ノイズ信号用スイッチ S C N 1 3 とアナログメモリ C T N 1 3 とバッファ V F N 3 を有する。セット 2 は、第 2 光信号用スイッチ S C S 1 3 とアナログメモリ C T S 1 3 とバッファ V F S 3 を有する。セット 3 は第 1 光信号用スイッチ S C S a 1 3 とアナログメモリ C T S a 1 3 とバッファ V F S a 3 を有する。

**【 0 0 4 2 】**

導電パターン N G A は、増幅回路 G A の出力ノードを構成する。

20

**【 0 0 4 3 】**

導電パターン 5 は、バッファ V F S a 1 、 V F S a 3 、 V F N 1 、 V F N 3 、 V F S 1 、 V F S 3 の入力ノードを構成する。導電パターン 5 は第 1 の配線層で構成される。

**【 0 0 4 4 】**

導電パターン 6 は、バッファ V F N 1 、 V F N 3 、 V F S 1 、 V F S 3 の出力ノードを構成する。導電パターン 6 は第 1 の配線層で構成される。

**【 0 0 4 5 】**

導電パターン 7 は、第 1 の光信号用バッファ V F S a 1 、 V F S a 3 の出力ノードを構成する。導電パターン 7 は第 2 の配線層で構成される。

**【 0 0 4 6 】**

導電パターン 8 は、ダミーパターンとして設けられたものであり、例えば寄生容量などの調整用に配されたものであり、実回路の本質的な機能には影響を与えない。導電パターン 8 は、導電パターン 7 が、 C T S 1 1 、 C T S 1 3 の上部に配され、 C T N 1 1 、 C T N 1 3 の上部に配されないがために生じる寄生容量の差を低減するためのものである。したがって、バッファ V F S a 1 、 V F S a 3 に電気的に接続されるが、アナログスイッチ S C N 2 1 、 S C N 2 3 には電気的に接続されない。

30

**【 0 0 4 7 】**

更に本実施例においては、第 1 の信号保持部を平面視した際の面積は、第 2 の信号保持部および / またはノイズ信号保持部を平面視した際の面積よりも小さいレイアウトとなっている。

40

**【 0 0 4 8 】**

次に、図 3 に本実施例の撮像装置のタイミングチャートを示す。図 3 において、各パルスはトランジスタをオンとオフ状態に制御するものであり、ハイレベルでオン状態となりローレベルでオフ状態となるものとする。

**【 0 0 4 9 】**

P S E L 1 は選択トランジスタ M 4 1 1 ~ M 4 1 3 を、 P R E S 1 はリセットトランジスタ M 2 1 1 ~ M 2 1 3 用のパルスである。 P T X A 1 は転送トランジスタ M a 1 1 ~ M a 1 3 を、 P T X B 1 は転送トランジスタ M b 1 1 ~ M b 1 3 用のパルスである。

**【 0 0 5 0 】**

P S E L 2 は選択トランジスタ M 4 2 1 ~ M 4 2 3 用のパルスである。 P R E S 2 はリ

50

セットトランジスタM 2 2 1 ~ M 2 2 3用のパルスである。P TX A 2は転送トランジスタM a 2 1 ~ M a 2 3用のパルスである。P TX B 2は転送トランジスタM b 2 1 ~ M b 2 3用のパルスである。PSGAはスイッチSGA 1、SGA 3用のパルスである。P SCN 1はスイッチSCN 1 1、SCN 1 3用のパルスである。P SCS 1はスイッチSCS 1 1、SCS 1 3用のパルスである。P SCS a 1はスイッチSCSa 1 1、SCSa 1 3用のパルスである。P SCS a 2はスイッチSCSa 2 1、SCSa 2 3用のパルスである。P SCN 2はスイッチSCN 2 3、SCN 2 3のパルスである。P SCS 2はスイッチSCS 2 1、SCS 2 3用のパルスである。P SHN 1はスイッチSHN 1を、P SHS 1はスイッチSHS 1用の駆動パルスであり、P SHN 3はスイッチSHN 3用の駆動パルスであり、P SHS 3はスイッチSHS 3用の駆動パルスである。

10

#### 【0051】

まず、時刻t 0で、垂直走査回路1 2からP SEL 1がハイレベルとなる信号が送られ、選択トランジスタM 4 1 1 ~ M 4 1 3がオンし、画素領域1 0の1行目が選択される。同時刻には、PSGAがハイレベルとなっており、増幅回路GA 1、GA 3がバイアス電圧V refに対するボルテージフォロア状態になる。また、P SCN 1、P SCS a 1、P SCS 1がハイレベルとなることによりスイッチSCN 1 1、SCSa 1 1、SCS 1 1、SCN 1 3、SCSa 1 3 1、SCS 1 3がオン状態となる。その結果、図示している全てのアナログメモリに電圧V refが書き込まれる。

#### 【0052】

時刻t 1で垂直走査回路1 2からP RES 1にローレベルの信号が送られリセットトランジスタM 2 1 1 ~ M 2 1 3がオフ状態となり、増幅トランジスタの入力ノードの電位がフロー・ティング状態となりノイズ信号Nを読み出す状態となる。この状態で、電流源I b 1、I b 3により駆動された増幅トランジスタM 3 1 1 ~ M 3 1 3により増幅されたノイズ信号Nが、列信号線NV 1 ~ NV 3に現れる。同時刻に、PSGAに供給される信号がローレベルとなり、増幅回路GA 1、GA 3が列信号線NV 1、NV 3から見て増幅率Ci 1 / Cf 1、Ci 3 / Cf 3となるゲインモードとなる。ここでCiは増幅回路GAの入力容量Cの容量値でありCfは増幅回路GAのフィードバック容量Cfの容量値である。

20

#### 【0053】

また同時に、P SCN 1、P SCS a 1、P SCS 1のレベルがローレベルとなることによりスイッチSCN 1 1、SCSa 1 1、SCS 1 1、SCN 1 3、SCSa 1 3 1、SCS 1 3がオフ状態となる。

30

#### 【0054】

時刻t 2では、P SCN 1のレベルがハイレベルとなりスイッチSCN 1 1、SCN 1 3がオンし、列ごとにある増幅回路GA 1、GA 3を通じて増幅されたノイズ信号Nが、アナログメモリCTN 1 1とCTN 1 3に書き込まれる。

#### 【0055】

時刻t 3で垂直走査回路1 2からP TX a 1のレベルがハイレベルとなる信号が送られ転送トランジスタMa 1 1 ~ Ma 1 3がオン状態となり、フォトダイオードDa 1 1 ~ Da 1 3の電荷が増幅トランジスタの入力ノードに転送される。そして、これらの増幅トランジスタの入力ノードの電圧が変化し、列信号線NV 1 ~ NV 3にA像信号Saが現れる。

40

#### 【0056】

時刻t 4では、P SCS a 1のレベルがハイレベルとなり、増幅回路GA 1、GA 3を通じて増幅されたA像信号Saが、アナログメモリCTS a 1 1とCTS a 1 3に書き込まれる。

#### 【0057】

時刻t 5では、P SCN 2のレベルがハイレベルとなり、スイッチSCN 2 1、SCN 2 3がオン状態となる。そしてノイズ信号NがアナログメモリCTN 1 1、CTN 1 3からバッファVF N 1、VF N 2を通じてアナログメモリCTN 2 1、CTN 2 3に書き込

50

まれる。時刻  $t_5$  では同時に、 $PSCSa_2$  のレベルもハイレベルとなり、スイッチ  $SCSa_2$  1、 $SCSa_2$  3 がオン状態となる。そして、A 像信号  $S_a$  がアナログメモリ  $CTS_{11}$ 、 $CTS_{13}$  からバッファ  $VFS_{a1}$ 、 $VFS_{a2}$  を通じてアナログメモリ  $CTS_{21}$ 、 $CTS_{23}$  に書き込まれる。

#### 【0058】

時刻  $t_6$  で、 $PSHN_1$  と  $PSHS_1$  のレベルがハイレベルとなりスイッチ  $SHN_1$  と  $SHS_1$  がオン状態となる。そしてアナログメモリ  $CTN_{21}$  のノイズ信号  $N$  と、アナログメモリ  $CTS_{21}$  の A 像信号  $S_a$  がそれぞれ、ノイズ信号用水平信号線 2 1 と撮像信号用水平信号線 2 2 に水平転送される。すると、出力アンプ  $MA$  で A 像信号  $S_a$  からノイズ信号  $N$  の差分処理が行われ、端子  $OUT_N$  と  $OUT_S$  を通じてチップ外へ 1 行 1 列目のノイズ補正された A 像信号 ( $S_a - N$ ) が出力される。10

#### 【0059】

また、時刻  $t_6$  で、垂直走査回路 1 2 から  $PTX_{a1}$ 、 $PTX_{b1}$  のレベルがハイレベルとなる信号が送られ、転送トランジスタ  $Ma_{11} \sim Ma_{13}$  と転送トランジスタ  $Mb_{11} \sim Mb_{13}$  がオン状態となる。その結果、フォトダイオード  $D_{b11} \sim D_{b13}$  の B 像信号に対応する電荷が、増幅トランジスタの入力ノードに転送され、A 像信号電荷と B 像信号電荷とが加算される。そして、列信号線  $NV_1 \sim NV_3$  に A 像信号  $S_a$  と B 像信号  $S_b$  が加算された撮像信号  $S$  ( $S = S_a + S_b$ ) が出力される。

#### 【0060】

時刻  $t_7$  で、 $PSHN_2$  と  $PSHS_2$  のレベルがハイとなり、スイッチ  $SHN_3$  と  $SHS_3$  がオン状態となる。そして、アナログメモリ  $CTN_{23}$  のノイズ信号  $N$  と、アナログメモリ  $CTS_{23}$  の A 像信号  $S_a$  がそれぞれ、ノイズ信号用水平信号線 2 1 と撮像信号用水平信号線 2 2 に水平転送される。すると、出力アンプ  $MA$  で A 像信号  $S_a$  からノイズ信号  $N$  の差分処理が行われ、端子  $OUT_N$  と  $OUT_S$  を通じて撮像素子外へ 1 行 2 列目の A 像信号 ( $S_a - N$ ) が出力される。20

#### 【0061】

時刻  $t_7$  では、 $PSCS_1$  のレベルがハイレベルとなり、スイッチ  $SCS_{11}$ 、 $SCS_{13}$  がオン状態となり、列ごとにある増幅回路  $GA_1$ 、 $GA_3$  を通じて増幅された撮像信号  $S$  が、アナログメモリ  $CTS_{11}$  と  $CTS_{13}$  に書き込まれる。

#### 【0062】

時刻  $t_8$  では、 $PSCS_1$  のレベルがローレベルとなりスイッチ  $SCS_{11}$ 、 $SCS_{13}$  がオフ状態となり、撮像信号  $S$  のアナログメモリ  $CTS_{11}$  と  $CTS_{13}$  への書き込みが終了する。30

#### 【0063】

時刻  $t_9$  では、図示していない 3 列目以降の水平転送も終わる。また、時刻  $t_9$  で、 $PSCN_2$  のレベルがハイレベルとなり、スイッチ  $SCN_{21}$ 、 $SCN_{23}$  がオンとなりノイズ信号  $N$  がアナログメモリ  $CTN_{11}$ 、 $CTN_{13}$  からバッファ  $VFN_1$ 、 $VFN_3$  を通じてアナログメモリ  $CTN_{21}$ 、 $CTN_{23}$  に再び書き込まれる。時刻  $t_9$  では同時に、 $PSCS_2$  のレベルもハイレベルとなり、スイッチ  $SCS_{21}$ 、 $SCS_{23}$  がオン状態となる。そして、撮像信号  $S$  がアナログメモリ  $CTS_{11}$ 、 $CTS_{13}$  からバッファ  $VFS_1$ 、 $VFS_3$  を通じてアナログメモリ  $CTS_{21}$ 、 $CTS_{23}$  に書き込まれる。40

#### 【0064】

期間  $t_6 \sim t_9$  は、A 像信号 ( $S_a - N$ ) の水平転送と、アナログメモリ  $CTS_{11}$ 、 $CTS_{13}$  への撮像信号  $S$  の書き込みを並列に行っている。このため、焦点検出用の情報を得ながらも、1 水平走査期間を小さくすることができる。ひいては、フレームレートもしくはコマ速を速くすることができる。

#### 【0065】

時刻  $t_{10}$  で、 $PSHN_1$  と  $PSHS_1$  のレベルがハイレベルとなり、スイッチ  $SHN_1$  と  $SHS_1$  とがオン状態となる。そして、アナログメモリ  $CTN_{21}$  のノイズ信号  $N$  と、アナログメモリ  $CTS_{21}$  の撮像信号  $S$  がそれぞれ、ノイズ信号用水平信号線 2 1 と撮像信号用水平信号線 2 2 に水平転送される。50

像信号用水平信号線 2 2 に水平転送される。そして、出力アンプ M A で撮像信号 S からノイズ信号 N が差分され、端子 O U T N と O U T S を通じてチップ外へ 1 行 1 列目のオフセット補正された撮像信号 ( S - N ) が出力される。カメラは、この時点で 1 行 1 列目の撮像信号 ( S - N ) と A 像信号 ( S a - N ) を得るため、両者を差分処理することで B 像信号 S b が得られる。

#### 【 0 0 6 6 】

また、時刻 t 1 0 では、垂直走査回路 1 2 から P S E L 2 のレベルがハイレベルとなる信号が送られ、選択トランジスタ M 4 2 1 、 M 4 2 2 がオン状態となり、画素領域 1 0 の 2 行目が選択され、2 行目の読み出し動作が始まっている。

#### 【 0 0 6 7 】

時刻 t 1 1 で、 P S H N 2 と P S H S 2 のレベルがハイレベルとなり、スイッチ S H N 3 と S H S 3 がオン状態となる。そして、アナログメモリ C T N 2 3 のノイズ信号 N と、アナログメモリ C T S 2 3 の撮像信号 S がそれぞれ、ノイズ信号用水平信号線 2 1 と撮像信号用水平信号線 2 2 に水平転送される。

#### 【 0 0 6 8 】

時刻 t 1 2 では、図示していない 3 列目以降の水平転送も終わる。時刻 t 1 3 では、垂直走査回路 1 2 から P S E L 2 のレベルがローレベルとなる信号が送られ、選択トランジスタ M 4 2 1 ~ M 4 2 3 がオフ状態となり、画素領域 1 0 の 2 行目が非選択となり、2 行目の読み出し動作が終わる。

#### 【 0 0 6 9 】

本実施例では、図 1 で示すように、ノイズ信号保持部のセット 1 と、撮像信号用のセット 2 を列信号線 N V 1 ~ N V 3 の配列方向に平行な方向に並進対称にレイアウトする。並進対称とは並進移動させたとき配置が一致することをいう。そして、フォーカス信号用スイッチ S C S a 1 3 とアナログメモリ C T S a 1 3 とバッファ V N S a 3 のセット 3 は、セット 1 とセット 2 から見て画素領域 1 0 側に配置する。また導電パターン 6 を設けて、導電パターン 6 の電位を、フォーカス信号用バッファ V F S a 1 、 V F S a 3 の出力ノードと同じ電位にする。これにより、導電パターン 7 のセット 1 とセット 2 に与える影響の差を低減している。このため、ノイズ信号 N と撮像信号 S は、外乱ノイズの影響を受けてもほぼ同じノイズを受け、チップ外部に撮像信号 ( S - N ) を出力するとき、撮像信号とノイズ信号とを差分処理することによりノイズの影響はキャンセルされる。

#### 【 0 0 7 0 】

一方、セット 1 とセット 3 は並進対称では無く配置も離れている。よって、ノイズ信号 N とフォーカス信号 S a は、別の外乱ノイズの影響を受け得る。このため、出力アンプ M A によって S a と N との差分処理された外部出力用フォーカス信号 ( S a - N ) は、撮像信号 ( S - N ) に比べればノイズが大きくなり得る。

#### 【 0 0 7 1 】

つまり、後段の回路における、第 2 の信号保持部が出力する信号とノイズ信号保持部が出力する信号との差分処理の同相ノイズ除去率が、第 1 の信号保持部が出力する信号とノイズ信号保持部が出力する信号との差分処理の同相ノイズ除去率よりも大きい。

#### 【 0 0 7 2 】

図 1 に示すように、フォーカス信号用バッファ V F S a 1 、 V F S a 3 は、ノイズ信号用バッファ V F N 1 、 V F N 3 や撮像信号用バッファ V F S 1 、 V F S 3 と比べ異なったレイアウトとなっている。このため、フォーカス信号用バッファ V F S a 1 、 V F S a 3 は、ノイズ信号用バッファ V F N 1 、 V F N 3 や撮像信号用バッファ V F S 1 、 V F S 3 とレイアウト差による入力インピーダンス、出力インピーダンスまたはオープンループゲインが異なる。つまり、ノイズ信号用バッファ ( V F N ) と撮像信号用バッファ ( V F S ) の入力インピーダンス、出力インピーダンスまたはオープンループゲインの差は、ノイズ信号用バッファ ( V F N ) とフォーカス信号用バッファ ( V F S a ) の差より小さい。または、フォーカス信号用バッファ V F S a 1 、 V F S a 3 のバイアス電流を小さくし、低消費電力化しても良い。

10

20

30

40

50

**【 0 0 7 3 】**

本実施例では、バッファ  $V_{FN1}$ 、 $V_{FS1}$ 、 $V_{FSA1}$ 、 $V_{FN3}$ 、 $V_{FS3}$ 、 $V_{FSA3}$  は、ボルテージフォロア回路であるとして説明したが、ソースフォロア回路でも、1より大きいゲインをかけるゲインアンプ構成でも良い。スイッチ  $S_{CN111}$ 、 $S_{CN121}$ 、 $S_{CS111}$ 、 $S_{CS121}$  などは、n型MOSトランジスタとp型MOSトランジスタが組み合わされたアナログスイッチが望ましいが、n型MOSトランジスタ、p型MOSトランジスタのいずれか一方で構成してもよい。

**【 0 0 7 4 】**

図2では列ごとに増幅回路  $G_A$  が設けられているが、これに限られるものではなく、複数の画素に共通に設けられた列アンプを複数有していれば本実施例を適用可能である。

10

**【 0 0 7 5 】**

本実施例によれば、列回路上のチップ上での占有面積の増加を抑えつつ、撮像信号を高  $S/N$  で読み出すことが可能となる。

**【 0 0 7 6 】****(実施例2)**

本実施例の撮像装置の平面レイアウトの概念図を示す。実施例1と同様の部分には同様の符号を付し詳細な説明は省略する。本実施例の実施例1との違いは、第1の信号保持部を、ノイズ信号保持部、第2の信号保持部とこれらの配列方向に対して並べて配置した点である。

**【 0 0 7 7 】**

20

枠線内が黒く塗りつぶされた領域には、第2の配線層  $M_2$  と第3の配線層  $M_3$  とを電気的に接続する2層目のピアラグが配置される。枠線内がクロス線でハッキングされた領域 ( $M_3$ ) には、第3の配線層が配置される。また導電パターン4はシールド配線である。

**【 0 0 7 8 】**

図4のレイアウト図は、実施例1で説明した図2の回路図の点線18内に対応する。

**【 0 0 7 9 】**

図4に示すように、フォーカス信号用のスイッチとアナログメモリとバッファのセット3の右側にはスペース9が存在する。一方、ノイズ信号用のスイッチとアナログメモリとバッファのセット1と、撮像信号用のスイッチとアナログメモリとバッファのセット2の右側のスペースは実質的に存在しておらず、並進対称となっている。

30

**【 0 0 8 0 】**

つまり、セット1とセット2は並進対称である一方、セット3は、セット1とセット2に対して並進対称ではない。

**【 0 0 8 1 】**

このことはアナログメモリ  $C_{TN11}$ 、 $C_{TS11}$ 、 $C_{TSA11}$  をノイズ信号用、撮像信号用、フォーカス信号用の3つとし、アナログメモリ  $C_{TN21}$ 、 $C_{TS21}$  をノイズ信号用、撮像信号用の2つにしたためである。レイアウトの配線引きまわしの都合、または、フォトマスクのコストの削減のためグリッドを大きめに取る都合で、前述のすき間の違いが生じ得る。本実施例では、製造プロセス上やむなく生じるこのスペースの違いを有効活用すべく、フォーカス信号用のスイッチとアナログメモリとバッファのセット3を並進対称ではないレイアウトとした。その結果、フォーカス信号用アナログメモリ  $C_{TSA11}$  のポリシリコンは、その右側のシールド配線4との距離が大きくなる。このため、寄生容量も含めて考えると、フォーカス信号用アナログメモリ  $C_{TSA11}$  の容量は、アナログメモリ  $C_{TN11}$ 、 $C_{TS11}$  より小さくなる。

40

**【 0 0 8 2 】**

また、フォーカス信号用バッファ  $V_{FSA1}$  は、その右側に生じるスペースが大きいため、寄生抵抗や寄生容量を含めるとバッファ  $V_{FN1}$ 、 $V_{FS1}$  とは、入力インピーダンス、出力インピーダンス、またはレイアウト差によるオープンループゲインが異なる。ここでバッファ  $V_{FN1}$ 、 $V_{FS1}$  に比べれば、フォーカス信号用バッファ  $V_{FSA1}$  の出

50

力は、精度を求められないため、フォーカス信号用バッファ V F S a 1、3 のバイアス電流を小さくしてもよい。

#### 【0083】

##### (実施例3)

図5に本実施例の撮像装置のレイアウトの概念図を示す。図5のレイアウト図は、実施例1で説明した図2の回路図の点線18内に対応する。実施例1、2と同様の機能を有する部分には同様の符号を付し詳細な説明は省略する。本実施例の実施例2との違いは、バッファ V F S a、V F Nの入力ノードとなる導電パターン5がダミー部を有する点である。

#### 【0084】

10

図5において、ノイズ信号用スイッチとアナログメモリのセット13、撮像信号用スイッチとアナログメモリのセット14、フォーカス信号用スイッチとアナログメモリのセット17が、一方向に並んで配置されている。

#### 【0085】

図5に示すように、バッファ V F S a、V F Nの入力ノードとなる導電パターン5は、バッファ V F S の入力ノードに生じる寄生容量との差が小さくなるように、図5の太破線に示すようなダミー部を有する。

#### 【0086】

20

図5のレイアウト図に示すように、フォーカス信号用のスイッチ S C S a 13とアナログメモリ C T S a のセット17の左側に生じるスペースは大きい。一方、ノイズ信号用のスイッチ S C N 13とアナログメモリ C T N 13のセット13と、撮像信号用のスイッチ S C S 13とアナログメモリ C T S 13のセット14の左側に生じるスペースは小さい。また、セット13とセット14はシールド配線4に囲まれた領域を考えると並進対称性を保っている。一方、セット17は、上記スペースの違いのためにセット13とセット14に対して並進対称性を保っていない。

#### 【0087】

30

このことはアナログメモリ C T N 11、C T S 11、C T S a 11をノイズ信号用、撮像信号用、フォーカス信号用と3つとし、アナログメモリ C T N 21、C T S 21をノイズ信号用、撮像信号用と2つにしたことから生じる。レイアウトの配線引き回しの都合、または、フォトマスクのコストの削減のためグリッドを大きめに取る都合で、前述のスペースの違いが生じ得る。

#### 【0088】

本実施例では、このスペースの違いを有効活用し、スペースをそれぞれの信号保持部に対し不均等に配分している。その結果、フォーカス信号用アナログメモリ C T S a 11のポリシリコンは、その左側のシールド配線4との距離が大きくなる。このため、寄生容量も含めて考えると、フォーカス信号用アナログメモリ C T S a 11の容量は、アナログメモリ C T N 11、C T S 11より小さくなる。

#### 【符号の説明】

#### 【0089】

40

10 画素領域

15、16 列回路

18 信号保持部

D 1 1 a ~ D b 2 3 フォトダイオード

M 2 1 1 ~ M 2 4 3 リセットトランジスタ

M 3 1 1 ~ M 3 4 3 増幅トランジスタ

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(56)参考文献 特開2013-106194(JP,A)

特開2006-080937(JP,A)

特開2009-224524(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/369

H01L 27/146

H04N 5/357

H04N 5/374