(19)

(10)

**AT 15574 U2 2018-03-15**

(12)

## Gebrauchsmusterschrift

(21) Anmeldenummer: GM 104/2017

(22) Anmeldetag: 11.05.2017

(24) Beginn der Schutzdauer: 15.02.2018

(45) Veröffentlicht am: 15.03.2018

(51) Int. Cl.: **C23C 14/24** (2006.01)

**C23C 14/14** (2006.01)

(73) Gebrauchsmusterinhaber:

Plansee SE

6600 Reutte (AT)

(72) Erfinder:

Köstenbauer Harald

6600 Breitenwang (AT)

Winkler Jörg

6600 Breitenwang (AT)

**(54) Flexibles Bauteil mit Schichtaufbau mit metallischer Lage**

(57) Die vorliegende Erfindung betrifft ein beschichtetes flexibles Bauteil enthaltend ein flexibles Substrat (100) und mindestens einen auf dem Substrat (100) unmittelbar oder über eine oder mehrere Zwischenschichten angeordneten Schichtaufbau, der eine metallische Lage (120; 170a; 170b) mit einer zu der einen Seite an die metallische Lage unmittelbar angrenzenden halbleitenden oder elektrisch isolierenden Lage (100; 110; 140; 150; 180) sowie zu der anderen Seite an die metallische Lage unmittelbar angrenzenden halbleitenden oder elektrisch isolierenden Lage (100; 110; 140; 150; 180) aufweist. Die metallische Lage (120; 170a; 170b) wird gebildet aus einer Einzelschicht aus MoX, oder aus einem Zweischichtsystem aus MoX in Kombination mit einer Cu-basierten Schicht oder aus MoX in Kombination mit einer Al-basierten Schicht, oder aus einem Dreischichtsystem aus zwei MoX-Schichten mit dazwischenliegender Cu-basierter Schicht oder aus zwei MoX-Schichten mit dazwischenliegender Al-basierter Schicht, wobei X eines oder mehrere Elemente aus der Gruppe von Cu, Ag, Au ist.

Fig. 6

## Beschreibung

### FLEXIBLES BAUTEIL MIT SCHICHTAUFBAU MIT METALLISCHER LAGE

**[0001]** Die Erfindung betrifft eine Verwendung eines Additivs zur Bewahrung einer elektrischen Leitfähigkeit einer Mo-basierten Schicht innerhalb der Schichtebene mit den Merkmalen des Oberbegriffs des Anspruchs 1, ein beschichtetes flexibles Bauteil mit den Merkmalen des Oberbegriffs des Anspruchs 2 und ein Verfahren zur Herstellung eines beschichteten flexiblen Bauteils mit den Merkmalen des Oberbegriffs des Anspruchs 20.

**[0002]** Der technische Fortschritt auf dem Gebiet der flexiblen, biegsamen Bauteile ist eng mit Fortschritten auf dem Gebiet der Dünnschichtmaterialien verknüpft. Insbesondere ermöglicht dieser Fortschritt weitere Entwicklungen auf dem Gebiet der Elektronik, insbesondere Dünnschicht-Bauteile, wie beispielsweise Dünnschichttransistoren (Thin Film Transistor / TFT), als Teil einer Struktur zur aktiven Ansteuerung (aktiv Matrix bzw. in Englisch „active matrix“) von elektronischen Bildschirmen (Displays), z.B. Flüssigkristallanzeigen (liquid crystal displays; TFT-LCDs), AM-OLEDs (active matrix organic light emitting diodes; organische lichtemittierende Dioden mit aktiv Matrix Ansteuerung), oder Micro-LED (light emitting diodes) Displays. Die active matrix Struktur kann auch in anderen Anwendungen, z.B. Sensoranordnungen (sensor arrays) für Röntgenstrahlung zum Einsatz kommen. In diesen Anwendungen sind elektrische Leiterbahnen matrix-artig, als Zeilen („gate lines“; „rows“) und Spalten („signal lines“; „column lines“; „data lines“) angeordnet. Die Leiterbahnen stellen einen elektrisch leitfähigen Pfad zur Übertragung elektrischer Signale, elektrischem Strom, oder elektrischer Spannung von einem Punkt zu einem anderen zur Verfügung.

**[0003]** Jede aktive Matrix-Zeile bzw. -Spalte besteht aus einer langen, schmalen Leiterbahn (z. B. mit einer Länge von einigen Zentimetern bis zu knapp 2 Metern, einer Breite von einigen Mikrometern bis einigen zehn Mikrometern und einer Gesamtschichtdicke von einigen zehn bis einigen hundert Nanometern), die im Bereich der Dünnschichttransistoren jeweils eine oder mehrere Erweiterungen hat, welche die gate („Steuerelektrode“) bzw. source/drain Elektroden („Zufluss- und „Abfluss-Elektrode“) des TFTs bilden. Die Leiterbahnen verbinden die gate bzw. source/drain Elektroden des TFTs mit dem Randbereich des Substrats, wo entweder Kontaktbereiche („contact pads“) zur externen Kontaktierung, oder die Gate- und Data-Treiberstrukturen (Zeilen- und Spaltentreiber) zur Ansteuerung des Displays angeordnet sind.

**[0004]** Mit Hilfe der active matrix Ansteuerung kann die Helligkeit eines jeden einzelnen Bildpunktes (Pixels) über einen (z.B. TFT-LCD) oder mehrere (z.B. AM-OLED-Display) TFTs individuell geregelt werden; dabei ist entscheidend, dass der Spannungsabfall entlang der langen gate- und signal-Leiterbahnen möglichst gering ist, da sich sonst längenabhängige, unerwünschte Helligkeitsunterschiede in den Bildpunkten ergeben würden. (Das menschliche Auge reagiert auf Helligkeitsunterschiede sehr empfindlich.)

**[0005]** Bei active matrix Strukturen, die auf biegsamen, flexiblen, oder verdrehbaren Substraten angeordnet sind, sind insbesondere die langen Zeilen- und Spalten-Leiterbahnen einer hohen Verformungs- bzw. Biege- bzw. Torsionsbeanspruchung unterworfen, wobei diese Beanspruchung bei den gate- und source/drain Elektroden in der TFT-Struktur aufgrund der viel geringeren räumlichen Ausdehnung (typischerweise eine rechteckige Fläche mit Kantenlängen von einigen Mikrometern bis einigen zehn Mikrometern) viel geringer ist. Aufgrund dieser Beanspruchung kann es insbesondere bei spröden Leiterbahnwerkstoffen schnell zu einer Erhöhung des elektrischen Widerstands um mehrere Größenordnungen kommen. Damit werden die entlang der Leiterbahn angeordneten TFTs nicht mehr gleichmäßig mit einer definierten Spannung versorgt und es kann zu längenabhängigen Helligkeitsunterschieden bei einer Display-Anwendung kommen. Im Extremfall verliert die Leiterbahn vollständig ihre elektrische Leitfähigkeit und es kommt zum Totalausfall von Bildpunkten.

**[0006]** Insbesondere bei Displays für mobile Anwendungen, z. B. Mobiltelefone, Tablet PCs, PDAs (Personal Digital Assistants), werden auf dem Display-Substrat neben der eigentlichen

Einheit zur Anzeige des Bildinhalts noch weitere periphere elektrische Schaltkreise integriert. Dies können z. B. Schaltungen zur Ansteuerung der Gate-Elektroden (Gate-Treiber), Schaltungen zur Ansteuerung der Source/Drain-Elektroden (Data-Treiber), DC-DC Konverter, Digital-Analog-Wandler, Timing Controller, oder Puffer- und Interface Schaltungen sein. Eine solche Kombination aus Display und dessen Ansteuereinheit wird als System-On-Panel (SOP) (System auf Displaypanel), oder - falls das Substrat aus Glas besteht - als System-On-Glass (SOG) (System auf Glas) bezeichnet. Es ist vorteilhaft, die peripheren elektrischen Schaltungen zur Ansteuerung des Displays direkt auf dem Substrat anzutragen, anstatt sie als externe Integrierte Schaltkreise (ICs), mit separatem Gehäuse, auszuführen; wesentliche Vorteile sind geringere Herstellkosten, geringerer Stromverbrauch, geringerer Platzbedarf und eine höhere Zuverlässigkeit. System-On-Panel Displays werden häufig mittels low temperature poly-Silicon (Niedrig-Temperatur-poly-Silizium) (LTPS)-Technologie realisiert, sind aber auch mit anderen Halbleitern wie amorphem Silizium, oder Metalloxiden möglich.

**[0007]** Teile der auf dem Substrat angeordneten peripheren Schaltkreise sind über elektrische Leiterbahnen, den Gate-Lines und Signal-Lines mit den TFTs der einzelnen Bildpunkte verbunden, wobei die Länge je nach Displaygröße von einigen mm bis zu 200 cm betragen kann. Die Widerstandsänderung der Leiterbahnen unter Verformungs-, Biege- oder Torsionsbelastung soll möglichst minimal sein, um einen Ausfall von einzelnen Bildpunkten, oder ganzen Zeilen oder Spalten des Displays zu verhindern bzw. um unerwünschte Unterschiede in der Helligkeit oder Farbe („Mura“) der Anzeige zu verhindern.

**[0008]** Auch flexible Berührungssensoren (z. B. resistive oder kapazitive Sensoren) verwenden matrix-artig angeordnete x- und y-Elektroden, in der Regel allerdings ohne aktive TFT-Strukturen. Bei größeren Sensoren von einigen Zentimetern bis Metern Größe kommen ebenfalls sehr lange, schmale Leiterbahnstrukturen zum Einsatz, z. B. mit einer Länge von 10 - 100 cm und einer Breite von 5-50 µm. Auch bei dieser Anwendung soll die Widerstandsänderung (Erhöhung) der Leiterbahnen unter Verformungs-, Biege- oder Torsionsbelastung möglichst minimal sein, da es sonst zu einem Ausfall des Sensors (z. B. durch Verringerung des Signal-Rauschabstands) kommen kann.

**[0009]** In der WO 2016/032175 (Figur 7) werden zur Verringerung der mechanischen Spannungen in Leiterbahnen, die einer Biegebelastung ausgesetzt sind, nichtgeradlinige, z. B. sinusförmige, gewellte, rechteckwellige, mäanderförmige, oder sägezahnwellenförmige Leiterbahnstrukturen vorgeschlagen. Um die Rissausbreitung zu verhindern werden des Weiteren sich verzweigende und sich wiedervereinigende Leiterbahnstrukturen (Figur 8c in der o. g. Schrift) vorgeschlagen. Alle diese Strukturen benötigen allerdings mehr Platz als eine einfache geradlinige Leiterbahn und der elektrische Strom muss insgesamt einen längeren Weg zwischen zwei Punkten zurücklegen, was zu einem zusätzlichen Spannungsabfall oder einer Verringerung des Signal-zu-Rausch Verhältnisses führen kann.

**[0010]** Weiter ermöglichen Fortschritte bei der Entwicklung neuer Integrationsprozesse auch die Kombination von Elektronik mit flexiblen Substraten und in weiterer Folge die Herstellung flexibler elektronischer Bauteile. Der gattungsgemäße Stand der Technik wird durch die AT 15 048 U1 gebildet. Für weitere Informationen zum Stand der Technik wird auf diese Schrift verwiesen.

**[0011]** Aufgabe der Erfindung ist die Bewahrung der elektrischen Leitfähigkeit einer metallischen Lage, die auf einem flexiblen Substrat aufgebracht ist, das einer einmaligen oder wiederholten Biege-, Zug- und/oder Torsionsbelastung unterworfen ist. Insbesondere besteht die Aufgabe der vorliegenden Erfindung in der Bereitstellung von elektrischen Leiterbahnen (metallischen Lagen) auf einem flexiblen Substrat, wobei sich der elektrische Widerstand der Leiterbahnen, entlang der Leiterbahn, d. h. innerhalb der Lagenebene, bei einer Verformungs-, Biege- oder Torsionsbelastung möglichst wenig, insbesondere um weniger als 10%, ändert.

**[0012]** Diese Aufgabe wird durch eine Verwendung gemäß Anspruch 1, ein beschichtetes flexibles Bauteil gemäß Anspruch 2 und ein Verfahren zur Herstellung eines beschichteten flexiblen Bauteils mit den Merkmalen des Anspruchs 20 gelöst. Vorteilhafte Ausführungsformen der Erfindung sind in den abhängigen Ansprüchen definiert.

**[0013]** Durch die Erfindung wird sichergestellt, dass es bei einer einmaligen oder wiederholten Biege- und/oder Zug- und/oder Torsionsbelastung des flexiblen Bauteils die elektrische Leitfähigkeit der Mo-basierten (Molybdän-basierten) Schicht bzw. der metallischen Lage innerhalb der Schichtebene gewahrt bleibt. Dies erfolgt durch eine Erhöhung der Duktilität.

**[0014]** Auf einem flexiblen Substrat können auch mehrere metallische Lagen, wie sie in Anspruch 2 definiert sind, vorgesehen sein, wobei dann für jede metallische Lage die Beschränkung gilt, dass zu beiden Seiten unmittelbar eine halbleitende oder elektrisch isolierende Lage angrenzt und die metallische Lage selbst gemäß Anspruch 2 als Einzelschicht, Zweischichtsystem oder Dreischichtsystem ausgebildet ist.

**[0015]** Eine Mo-basierte Schicht bzw. die MoX-Schicht enthält mindestens 50 Gew% Mo, insbesondere mindestens 60 Gew% Mo.

**[0016]** Die MoX-Schicht kann aus mehreren MoX mit unterschiedlichem X enthaltenden MoX-Teilschichten aufgebaut sein.

**[0017]** Abgesehen von der Bewahrung der elektrischen Leitfähigkeit, bewirkt die Erhöhung der Duktilität eine Steigerung der mechanischen Schadenstoleranz. Z. B. sinkt das Risiko einer Delamination im mehrschichtigen Verbund.

**[0018]** Natürlich muss es sich bei der Mo-basierten Schicht (MoX-Schicht) abgesehen von dem Additiv X nicht um reines Mo handeln, sondern es können auch Verunreinigungen vorhanden sein, insbesondere solche, die aus der Prozessatmosphäre eines PVD (physical vapor deposition; physikalische Dampfphasenabscheidung) Verfahrens, insbesondere eines Sputterverfahrens (Kathodenerstäubung), stammen (z. B. Ar, O, N, C). Die metallischen Verunreinigungen sollten aber < 0,5 at% sein.

**[0019]** Von den genannten Elementen Cu, Ag, Au ist Cu besonders bevorzugt. Hier genügt bereits eine geringere Konzentration in at% um den gewünschten Effekt zu erreichen. Des Weiteren ist es kostengünstiger als Ag und Au.

**[0020]** Erfindungsgemäß weist der Schichtaufbau eine metallische Lage mit einer zu der einen Seite an die metallische Lage unmittelbar angrenzenden halbleitenden oder elektrisch isolierenden Schicht sowie zu der anderen Seite an die metallische Lage unmittelbar angrenzenden halbleitenden oder elektrisch isolierenden Schicht auf, wobei diese Eigenschaften zumindest in einem gewissen Bereich eines beschichteten, flexiblen Bauteils erfüllt sind (nicht aber zwingend in allen Bereichen eines flexiblen Bauteils, insbesondere eines flexiblen elektronischen Bauteils, erfüllt sein müssen). Weitere mögliche angrenzende Schichten sind weiter unten näher beschrieben. Unter „elektrisch isolierend“ wird dabei verstanden, dass der elektrische Widerstand größer ist als 1 Megaohm.

**[0021]** Unter Flexibilität und „flexibel“ ist hier die Eigenschaft zu verstehen, eine Biegebeanspruchung ohne nachteilige Auswirkungen auf die für die Verwendung des Bauteils relevanten Eigenschaften aufzunehmen, bzw. einer solchen standzuhalten. Ausreichend flexible Bauteile weisen also auch eine signifikant verbesserte Zähigkeit auf.

**[0022]** Unter signifikant verbesserter Zähigkeit ist im Sinne der vorliegenden Erfindung zu verstehen, dass das Bauteil bzw. natürlich auch die enthaltene Schicht oder Schichten einen erhöhten Widerstand gegen Rissbildung und Risswachstum aufweisen, dass sich also Risse bis zu einer bestimmten Dehnung nicht bilden oder sich erst bei höherer Dehnung bilden oder einen modifizierten Rissverlauf aufweisen.

**[0023]** Um die Zähigkeit und in weiterer Folge also die Flexibilität zu beschreiben wird im Rahmen der vorliegenden Erfindung die kritische Dehnung verwendet. Als kritische Dehnung wird jene Dehnung  $\epsilon_k$  definiert, bei der der elektrische Widerstand R der Schicht oder der Schichten auf dem flexiblen Substrat um 10 % gegenüber dem Ausgangszustand angestiegen ist ( $R/R_0=1,1$ ). Bei Bauteilen mit ausreichend hoher Flexibilität ist die kritische Dehnung  $\epsilon_k$  signifikant erhöht, es bleibt also die Leitfähigkeit der Schicht oder Schichten deutlich länger erhalten.

**[0024]** Unter einem flexiblen Substrat ist im Rahmen der vorliegenden Erfindung ein Substrat zu

verstehen, das bei Anlegen einer Biegebeanspruchung eine Dehnung  $\epsilon$  in einer darauf abgeschiedenen Schicht oder darauf abgeschiedenen Schichten (Beschichtung) hervorruft. Wenn die Schicht oder Schichten sehr viel dünner als das Substrat ist oder sind, wird die Dehnung näherungsweise durch  $\epsilon = ds/2R$  beschrieben (ds ist die Dicke des Substrates und R der Biegeradius). Ist die Schicht oder sind die Schichten sehr dünn im Vergleich zum Substrat, kann die Dehnung in der Schicht oder in den Schichten näherungsweise einer reinen Zug- oder Druckbeanspruchung gleichgesetzt werden. Beispielsweise kann ein flexibles Substrat auf Basis eines oder mehrerer polymerer Werkstoffe, beispielsweise Polyimid, Polycarbonat, Polyethylen-terephthalat, Polyethylen-naphthalat, Polyethersulfon, Polyarylat oder Polyzyklisches Olefin aufgebaut sein. Die meisten flexiblen Substrate auf Basis eines oder mehrerer polymerer Werkstoffe weisen einen E-Modul von kleiner oder gleich 8 GPa auf. Auch Dünnglas (Glas mit einer Dicke von kleiner 1 mm), Metallfolien, beispielsweise Stahlblech mit einer Dicke von kleiner 1 mm, Aluminium-, Kupferoder Titanfolien mit einer Dicke von kleiner 1 mm, oder mineralische Materialien, wie beispielsweise Mica, sind geeignete flexible Substrate für ein erfindungsgemäßes flexibles Bauteil.

**[0025]** Ein für die Erfindung geeignetes flexibles Substrat kann wiederum aus einer Schicht oder mehreren Schichten bzw. einem oder mehreren Werkstoffen oder Materialien bestehen. Ebenso kann ein solches Substrat bereits vorab komplett oder nur teilweise mit ein oder mehreren Schichten aus anderen Materialien beschichtet sein.

**[0026]** Bevorzugt ist dieses Bauteil ein beschichtetes flexibles elektronisches Bauteil. Im Gegensatz zu einem beschichteten flexiblen Bauteil wie beispielsweise Verpackungsfolien mit metallischen Dampfsperrsichten oder optischen Schichten weist ein beschichtetes flexibles elektronisches Bauteil mindestens eine den elektrischen Strom leitende Schicht auf. Dies ist beispielsweise in flexiblen Schaltkreisen, flexiblen Displays, flexiblen Sensorelementen, flexiblen Dünnschichtkondensatoren, flexiblen Dünnschichtbatterien oder einfachen elektrisch leitenden Folien, z. B. flexiblen Leiterplatten (printed circuit boards) der Fall. Beispiele solcher flexibler elektronischer Bauteile, die gemäß der vorliegenden Erfindung ausgebildet sein können, sind im einleitenden Teil beschrieben.

**[0027]** Die metallische Lage eines erfindungsgemäßen beschichteten flexiblen Bauteils weist bevorzugt eine Dicke von kleiner 1  $\mu\text{m}$  auf. Die metallische Lage weist bevorzugt eine Minstdicke von 5 nm auf, weiter bevorzugt eine Dicke von mindestens 10 nm. Bevorzugt ist auch eine Dicke von 5 bis 300 nm, noch weiter bevorzugt von 5 bis 100 nm. Solche Schichtdicken sind besonders vorteilhaft, wenn die metallische Lage als Haftvermittlerschicht oder Diffusionsbarriereforschicht verwendet wird. Alternativ bevorzugt ist ein Dickenbereich von 150 bis 400 nm. Eine Schichtdicke von 150 bis 400 nm ist besonders gut für einen Einsatz eines erfindungsgemäßen beschichteten flexiblen Bauteils in einem Display, beispielsweise als Gateelektrodenschicht, geeignet.

**[0028]** Eine oder mehrere metallische Lage(n), wie sie in Anspruch 2 und gegebenenfalls in einer der Weiterbildungen konkretisiert ist/sind, kann/können Teil eines Dünnschichttransistors (TFT) sein.

**[0029]** Bei einem Ausführungsbeispiel des erfindungsgemäßen Bauteils kann vorgesehen sein, dass in mindestens einer MoX-Schicht X das Element Cu ist und diese MoCu-Schicht mehr als 0,5 at% und weniger als 50 at% Cu enthält, vorzugsweise mehr als 1 at% und weniger als 20 at% Cu enthält. Dabei ist besonders bevorzugt vorgesehen, dass sämtliche MoX-Schichten der metallischen Lage aus MoCu sind.

**[0030]** Bei einem Ausführungsbeispiel des erfindungsgemäßen Bauteils kann vorgesehen sein, dass in mindestens einer MoX-Schicht X das Element Ag ist und diese MoAg-Schicht mehr als 10 at% und weniger als 50 at% Ag enthält, vorzugsweise mehr als 20 at% und weniger als 50 at% Ag enthält. Dabei ist besonders bevorzugt vorgesehen, dass sämtliche MoX-Schichten der metallischen Lage aus MoAg sind.

**[0031]** Bei einem Ausführungsbeispiel des erfindungsgemäßen Bauteils kann vorgesehen sein,

dass in mindestens einer MoX-Schicht X das Element Au ist und diese metallische MoAu-Schicht mehr als 5 at% und weniger als 20 at% Au enthält. Dabei ist besonders bevorzugt vorgesehen, dass sämtliche MoX-Schichten der metallischen Lage aus MoAu sind.

[0032] Bei einem Ausführungsbeispiel des erfindungsgemäßen Bauteils kann vorgesehen sein, dass die einzelne MoX-Schicht einen Schichtwiderstand  $\rho$  von kleiner 200  $\mu\text{Ohmcm}$ , bevorzugt kleiner 100  $\mu\text{Ohmcm}$ , besonders bevorzugt kleiner 50  $\mu\text{Ohmcm}$  aufweist.

[0033] Bei einem Ausführungsbeispiel des erfindungsgemäßen Bauteils kann vorgesehen sein, dass mindestens eine der an die metallische Lage unmittelbar angrenzenden halbleitenden oder elektrisch isolierenden Lagen als Schichten ausgebildet sind. Es kann vorgesehen sein, dass beide unmittelbar angrenzenden halbleitenden oder elektrisch isolierenden Lagen als Schichten ausgebildet sind.

[0034] Bei einem Ausführungsbeispiel des erfindungsgemäßen Bauteils kann vorgesehen sein, dass die metallische Lage insgesamt einen Schichtwiderstand  $\rho$  kleiner 50  $\mu\text{Ohmcm}$ , bevorzugt kleiner 10  $\mu\text{Ohmcm}$ , besonders bevorzugt kleiner 3,5  $\mu\text{Ohmcm}$  aufweist.

[0035] Bei einem erfindungsgemäßen Verfahren wird mindestens eine MoX-Schicht abgeschieden, die mehr als 0,5 at% und weniger als 50 at % X enthält, wobei X eines oder mehrere Elemente aus der Gruppe von Cu, Ag, Au ist. Die MoX-Schicht kann dabei eine metallische Lage, wie sie in Anspruch 2 definiert ist, bilden oder ein Teil derselben sein.

[0036] Eine Abscheidung der mindestens einen MoX-Schicht bzw. der metallischen Lage kann über verschiedenartige Abscheidungsverfahren realisiert werden. Beispielsweise kann eine solche Beschichtung über physikalische oder chemische Gasphasenabscheidung realisiert werden.

[0037] Vorteilhaft ist es aber, wenn das Abscheiden der mindestens einen MoX-Schicht bzw. der metallischen Lage mittels eines PVD Verfahrens, insbesondere eines Sputterverfahrens realisiert wird. PVD Verfahren (physical vapour deposition, physikalische Gasphasenabscheidung) sind bekannte Dünnschicht-Beschichtungstechnologien, bei denen Teilchen des Beschichtungsmaterials in die Dampfphase übergeführt und dann auf dem Substrat abgeschieden werden. Durch ein Abscheiden mittels eines PVD Verfahrens kann eine besonders homogene Beschichtung abgeschieden werden, deren Eigenschaften über die beschichtete Fläche gleich und isotrop sind. Weitere Vorteile dieses Verfahrens sind die geringen Substrattemperaturen, die damit realisiert werden können. Damit wird beispielsweise die Beschichtung von Polymeren ermöglicht. Weiters zeichnen sich PVD-Schichten durch sehr gute Adhäsion auf dem Substrat aus.

[0038] Besonders bevorzugt ist es, wenn die MoX-Schicht bzw. die metallische Lage über ein Sputterverfahren (auch: Kathodenzerstäubungsverfahren) abgeschieden wird.

[0039] Ein Sputterprozess kann relativ einfach zur homogenen Beschichtung großer Flächen eingesetzt werden und ist somit ein kostengünstiges Verfahren für die Massenproduktion.

[0040] Ganz besonders bevorzugt ist es, wenn das erfindungsgemäße Verfahren weiter folgenden Schritt enthält:

[0041] - Bereitstellen eines Targets auf Mo-Basis, das zwischen 0,5 at% und weniger als 50 at% X enthält.

[0042] Die Bereitstellung eines Targets auf Mo-Basis, das zwischen 0,5 at% und weniger als 50 at% X enthält, erfolgt vor dem Abscheiden mindestens einer MoX-Schicht bzw. mindestens einer metallischen Lage. Die MoX-Schicht bzw. die metallische Lage wird also von dem bereitgestellten Target abgeschieden.

[0043] Unter Target ist dabei eine Beschichtungsquelle für eine Beschichtungsanlage zu verstehen. In einem bevorzugten Verfahren handelt es sich bei dem verwendeten Target um ein Sputter Target für ein Sputterverfahren.

[0044] Die chemische Zusammensetzung der Beschichtung wird über die chemische Zusam-

mensetzung des verwendeten Targets bestimmt. Durch leicht unterschiedliches Sputterverhalten (Sputterausbeuten) der im Target enthaltenen Elemente kann es jedoch zu Abweichungen der Beschichtungszusammensetzung von der Targetzusammensetzung kommen.

[0045] Beispielsweise kann durch bevorzugtes Sputtern von Cu aus einem MoCu Target der Cu Gehalt in der abgeschiedenen Beschichtung leicht erhöht sein. Um beispielsweise Beschichtungen, die mehr als 10 at% Cu enthalten sollen, zu erzeugen, kann ein entsprechendes Target auch weniger als 10 at% Cu enthalten.

[0046] Alternativ zur Verwendung eines einzelnen Targets kann die metallische Lage auch über Co-Abscheiden, bevorzugt Co-Sputtern, von einzelnen Targets abgeschieden werden. In diesem Fall kann die chemische Zusammensetzung der Beschichtung zusätzlich über die Wahl der unterschiedlichen Targets gesteuert werden.

[0047] Die Herstellung von Sputter Targets, die geeignet für die Abscheidung von metallischen Lagen sind, kann beispielsweise auf pulvermetallurgischem Weg erfolgen.

[0048] Mögliche pulvermetallurgische Routen zur Herstellung von Sputter Targets basieren auf Heißpresstechnologien wie Heißpressen (HP) oder Spark-Plasma-Sintering (SPS). In beiden Fällen wird eine Pulvermischung in eine Form einer Presse gefüllt, in der Form erhitzt und bei hohem Pressdruck und hoher Temperatur zu einem dichten Bauteil gesintert/verdichtet. Dabei stellt sich eine homogene Mikrostruktur mit gleichförmigen Körnern ein, die keine Vorzugsorientierung (Textur) aufweist.

[0049] Eine ähnliche pulvermetallurgische Route zur Herstellung von Sputter Targets ist das Heißisostatische Pressen (HIP). Das zu verdichtende Material wird dabei in einen deformierbaren, dichten Behälter (meist eine Stahlkanne) gefüllt. Dabei kann es sich um Pulver, Pulvermischungen oder Grünkörper (in Form gepresstes Pulver) handeln. Das sich in diesem Behälter befindende Material wird im Behälter in einem mit Druck beaufschlagten Kessel bei hohen Temperaturen und Drücken unter Schutzgas (z. B. Ar) gesintert/verdichtet. Der Gasdruck wirkt von allen Seiten, deshalb wird dieser Vorgang als isostatisches Pressen bezeichnet. Typische Prozessparameter sind z. B. 1100°C und 100 MPa mit einer Haltezeit von 3 h. Dabei stellt sich eine homogene Mikrostruktur mit gleichförmigen Körnern ein, die keine Vorzugsorientierung (Textur) aufweist.

[0050] Eine weitere Möglichkeit zur Herstellung von Sputter Targets über eine pulvermetallurgische Route ist Sintern und nachfolgendes Umformen. Dabei wird ein Pulverpressling bei hoher Temperatur unter Wasserstoff oder Vakuum gesintert.

[0051] Nach dem Sintern erfolgt ein Umformschritt, wie beispielsweise Walzen oder Schmieden, um eine hohe relative Dichte von >99 % zu erhalten. Dabei stellt sich eine Mikrostruktur mit langgestreckten Körnern ein, die eine Vorzugsorientierung (Textur) aufweist. Bei einer optionalen nachfolgenden Spannungsarmglühung oder Rekristallisationsglühung stellt sich eine homogene Mikrostruktur mit gleichförmigen Körnern ein, die aber weiterhin eine Vorzugsorientierung (Textur) aufweist.

[0052] Eine weitere Möglichkeit zur Herstellung von Sputter Targets über eine pulvermetallurgische Route ist das Auftragen eines Pulvers oder einer Pulvermischung auf eine entsprechende Stützstruktur, beispielsweise eine Platte oder ein Rohr, mittels eines thermischen Spritzverfahrens, beispielsweise Kaltgasspritzen oder Vakuumplasmaspritzen (VPS).

[0053] Im Folgenden wird die Erfindung anhand von Ausführungsbeispielen und anhand der Figuren näher beschrieben.

[0054] Es zeigen:

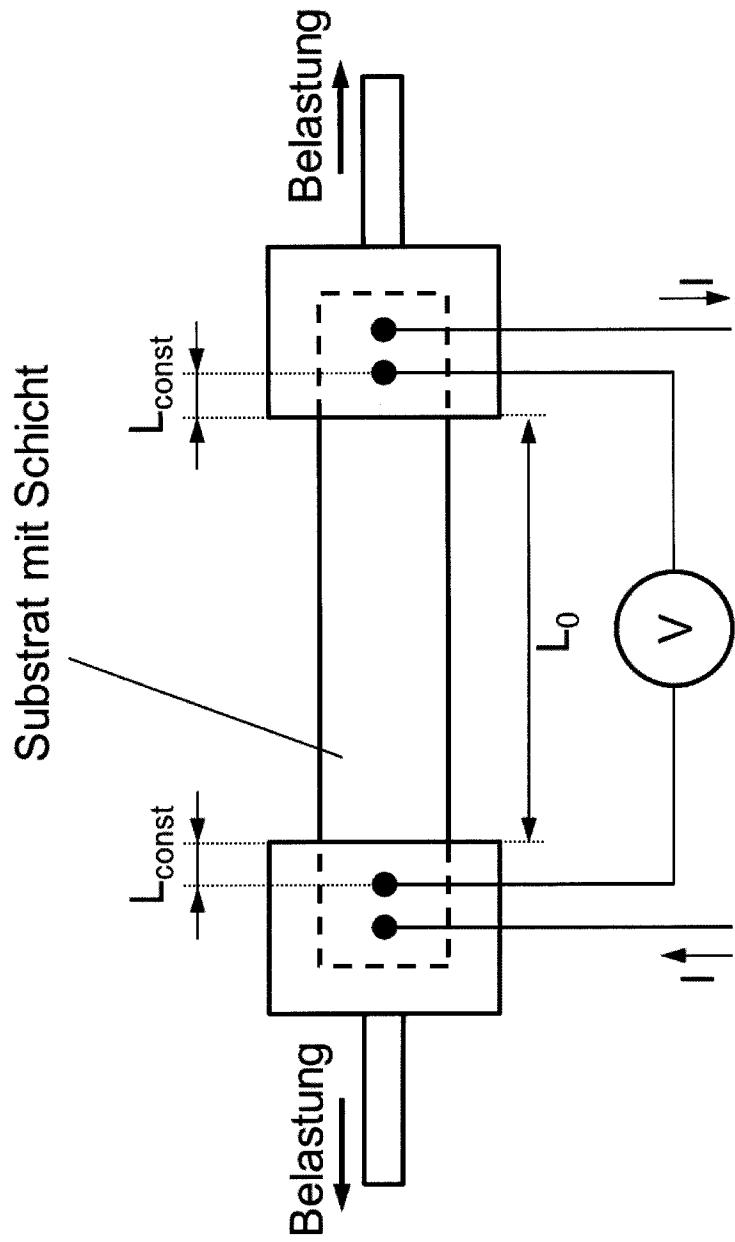

[0055] Figur 1 einen schematischen Aufbau des verwendeten einachsigen Zugversuchs mit elektrischer Widerstandsmessung zur Bestimmung der kritischen Bruchdehnung  $\epsilon_k$

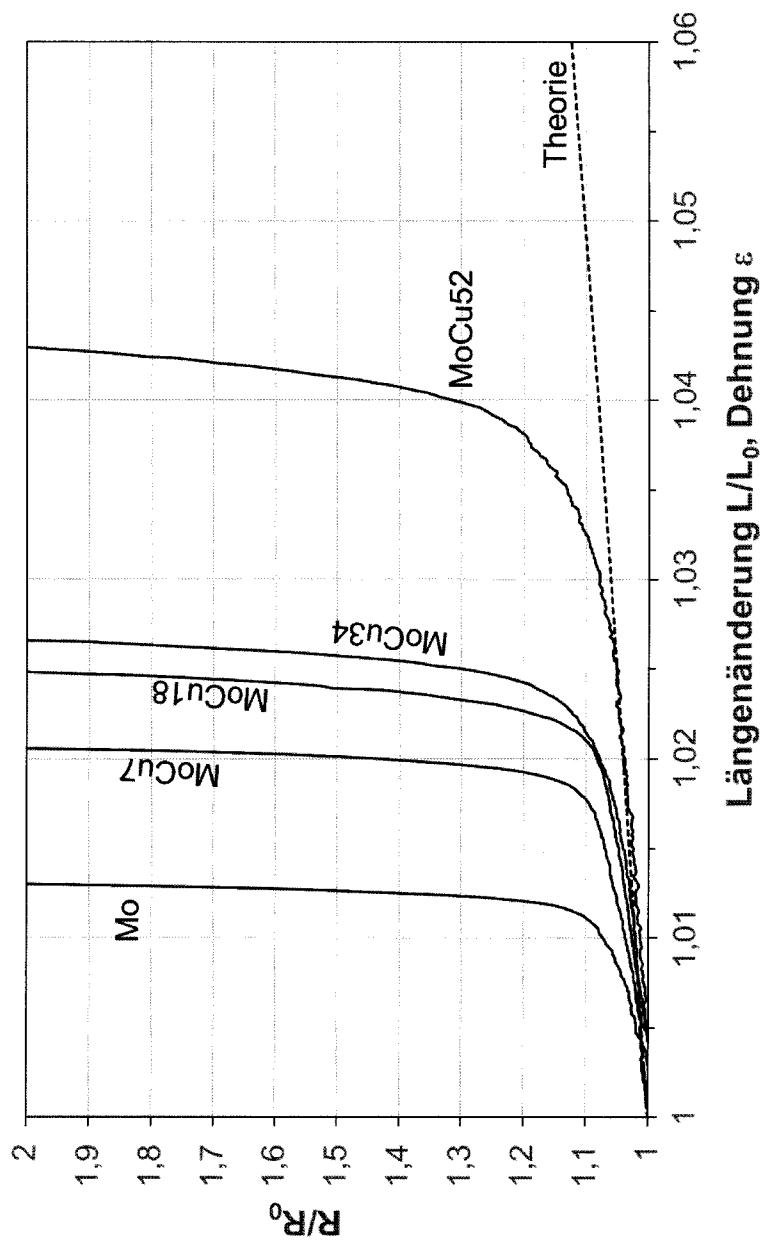

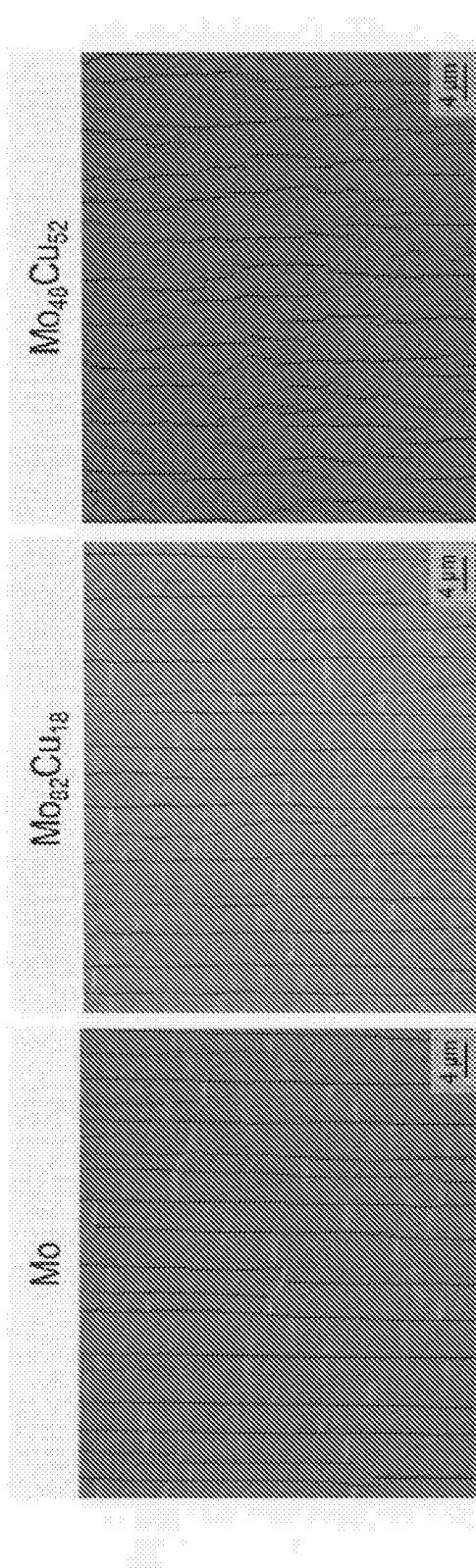

- [0056] Figur 2 R/R<sub>0</sub> Kurven für Mo und MoCu-Legierungen abhängig vom Cu-Gehalt in der Schicht

- [0057] Figur 3 Elektronenmikroskopische Aufnahmen des Rissbildes einer Mo Schicht und verschiedener MoCu Schichten nach einer maximalen Dehnung von 15%

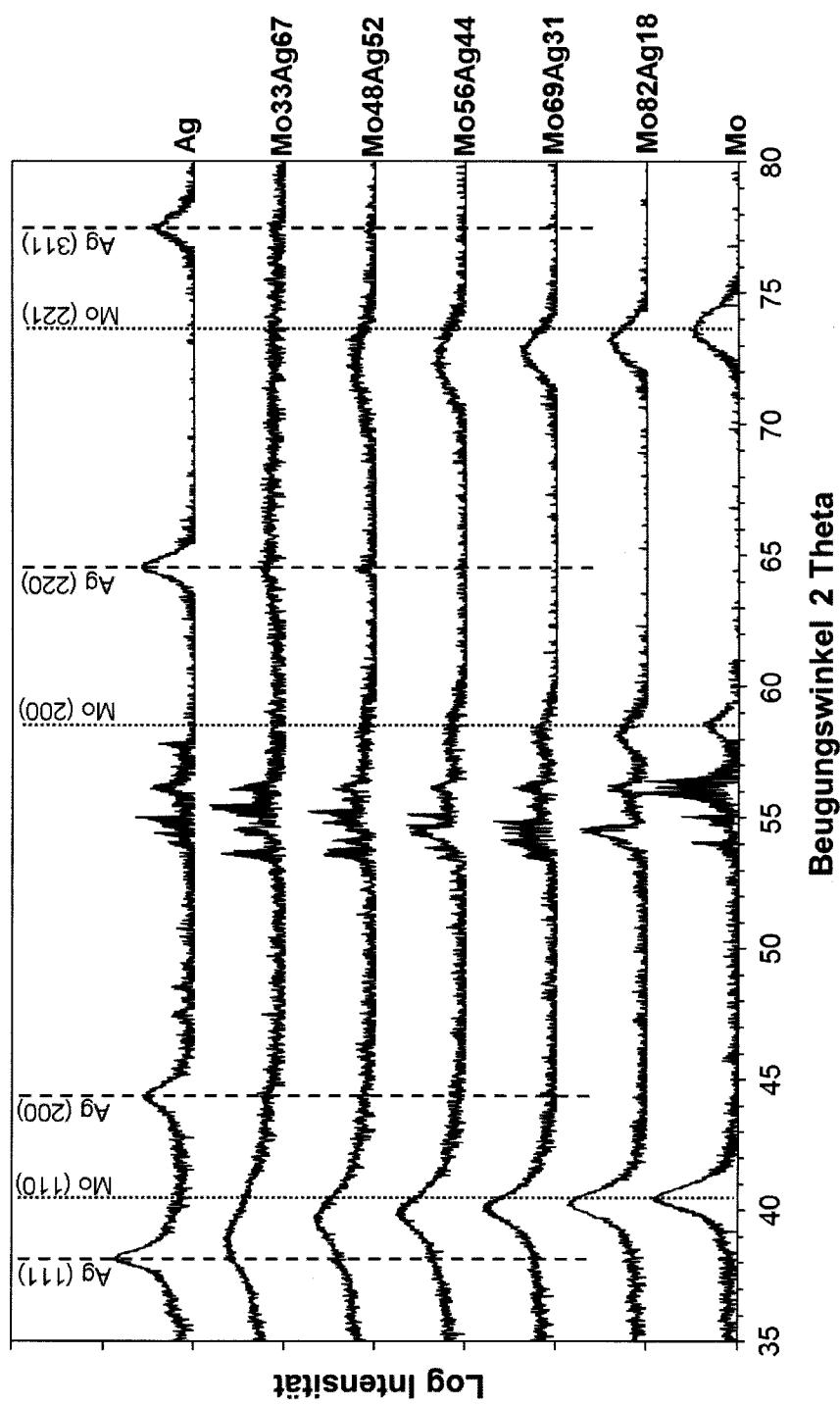

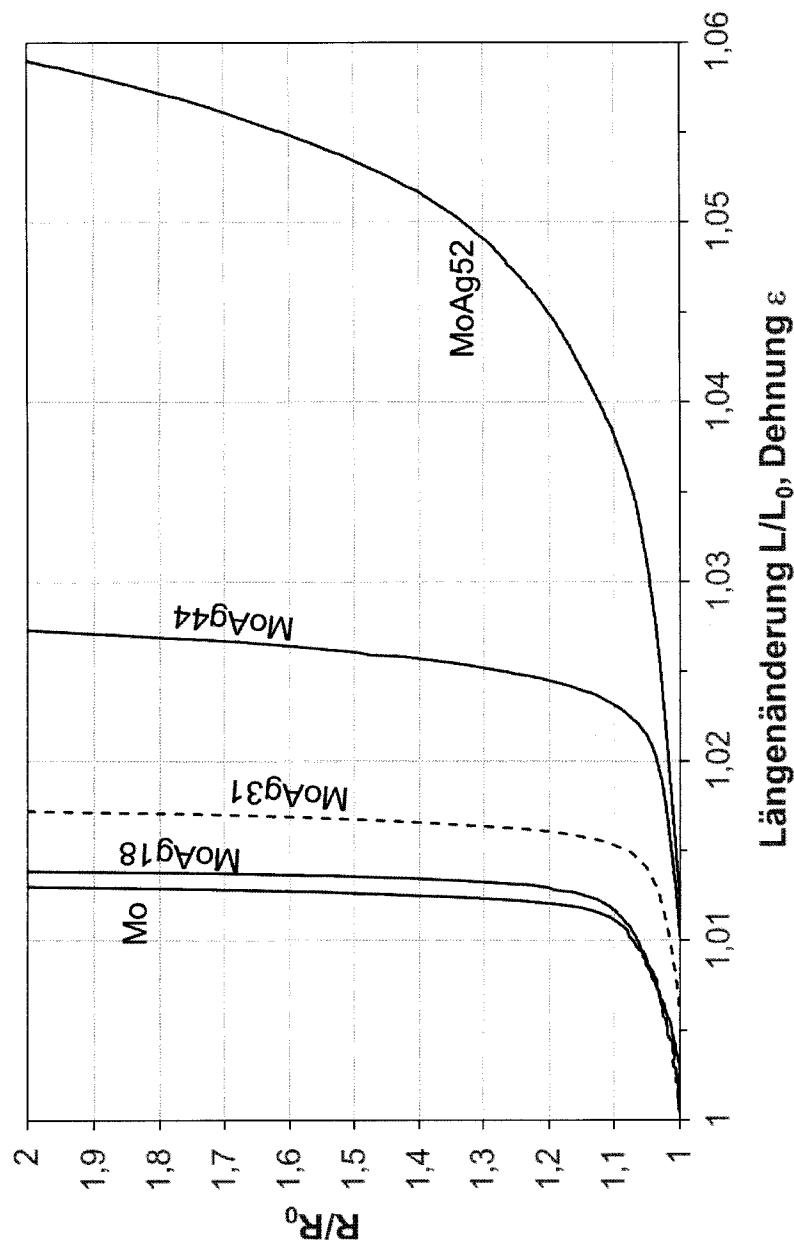

- [0058] Figur 4 R/R<sub>0</sub> Kurven für Mo und MoAg-Legierungen abhängig vom Ag-Gehalt in der Schicht

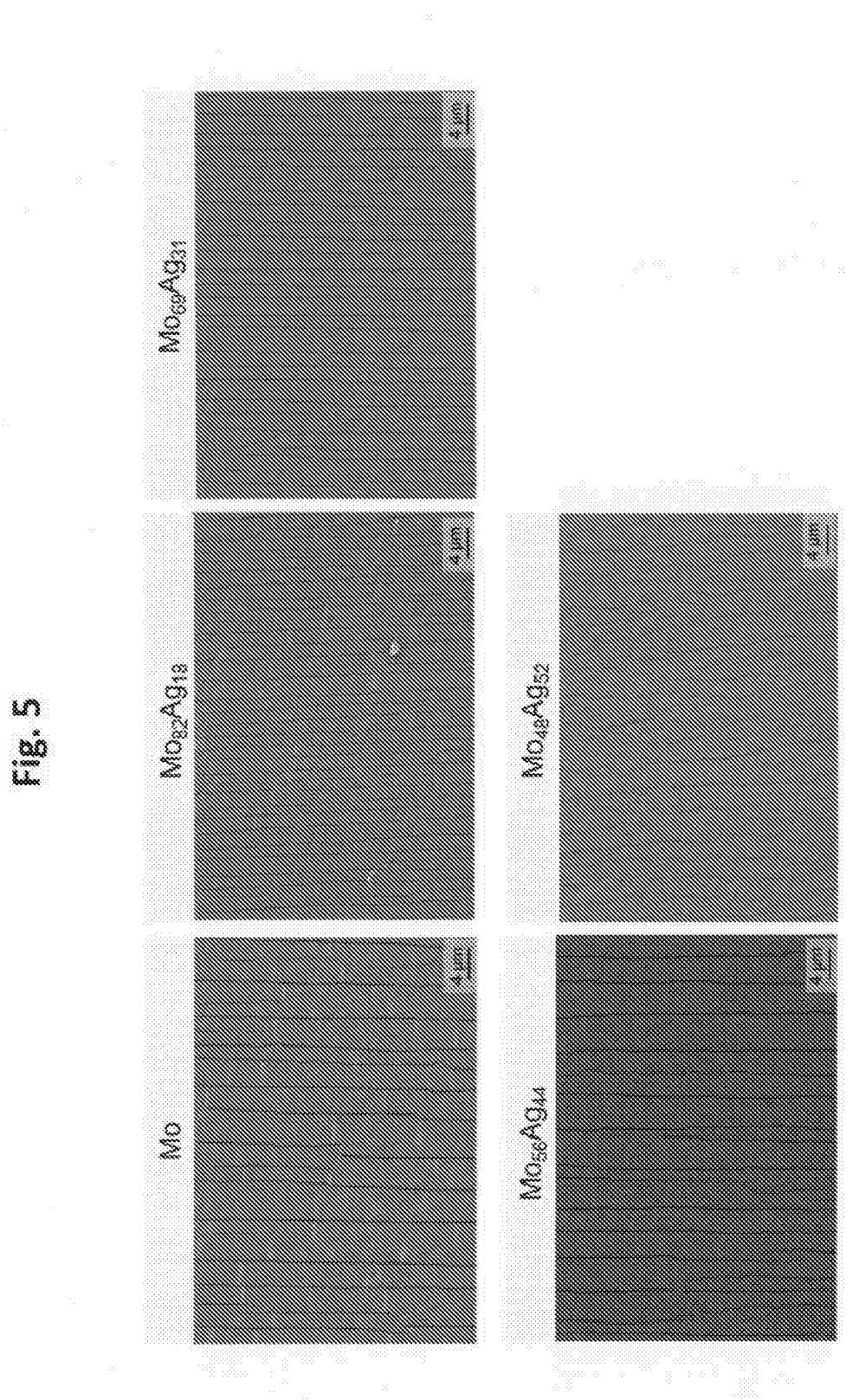

- [0059] Figur 5 Elektronenmikroskopische Aufnahmen des Rissbildes einer Mo Schicht und verschiedener MoAg Schichten nach einer maximalen Dehnung von 15%

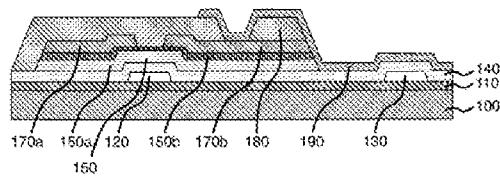

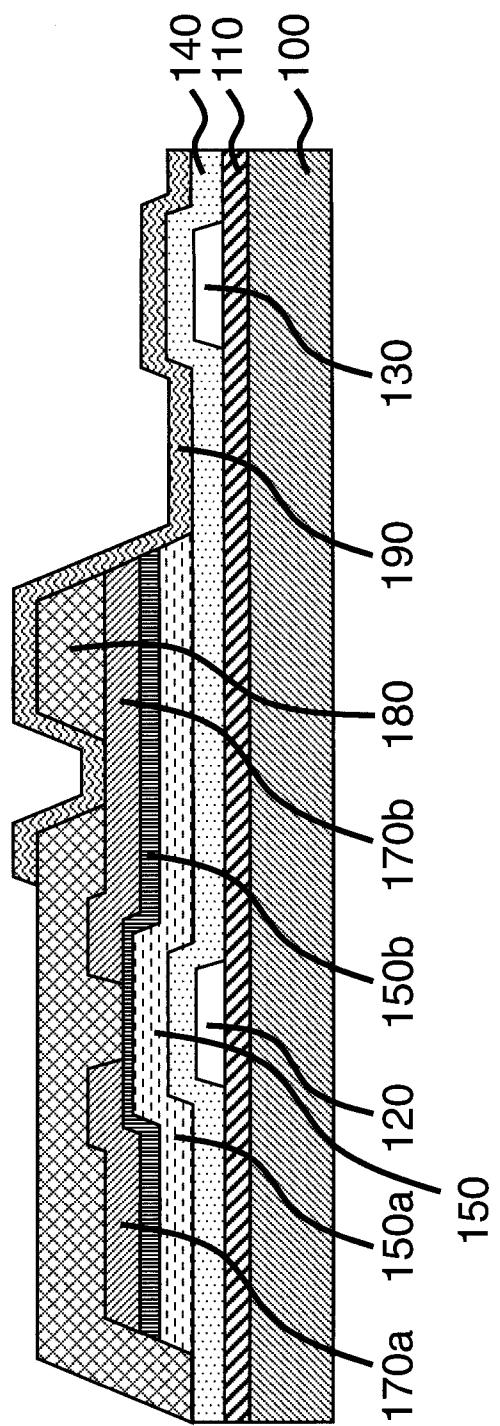

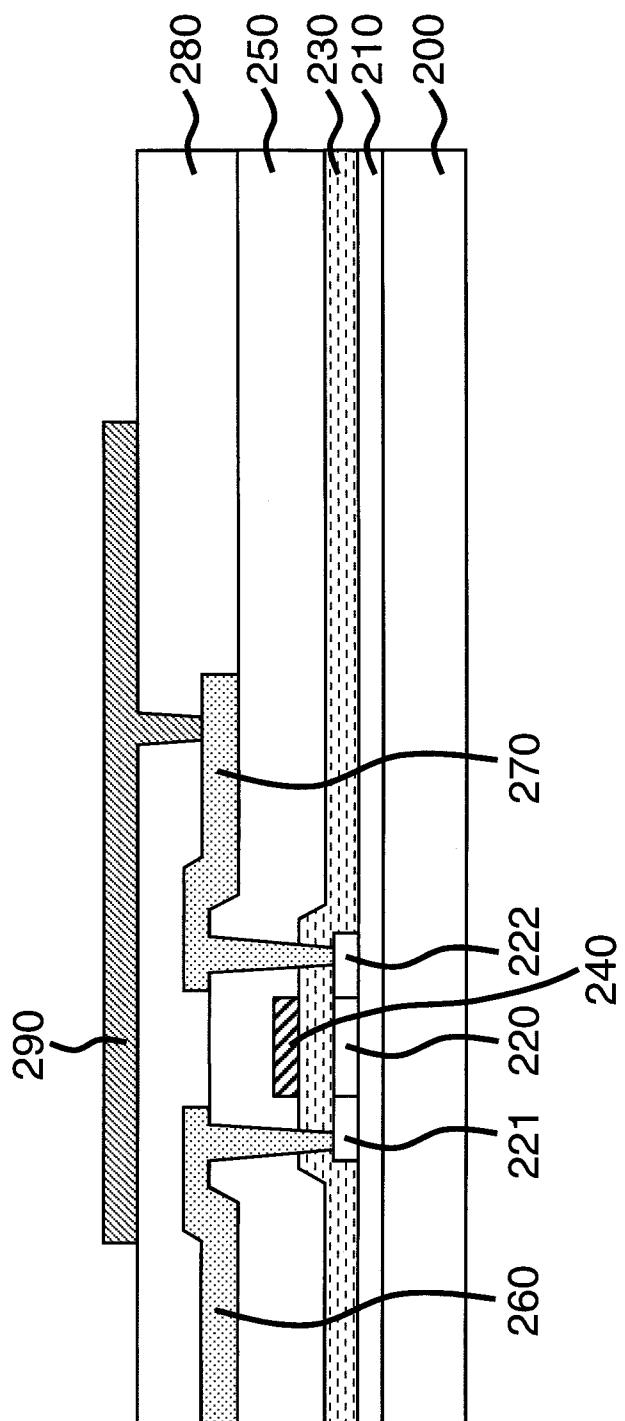

- [0060] Figur 6 Schichtaufbau eines bottom gate Dünnschichttransistors im Querschnitt

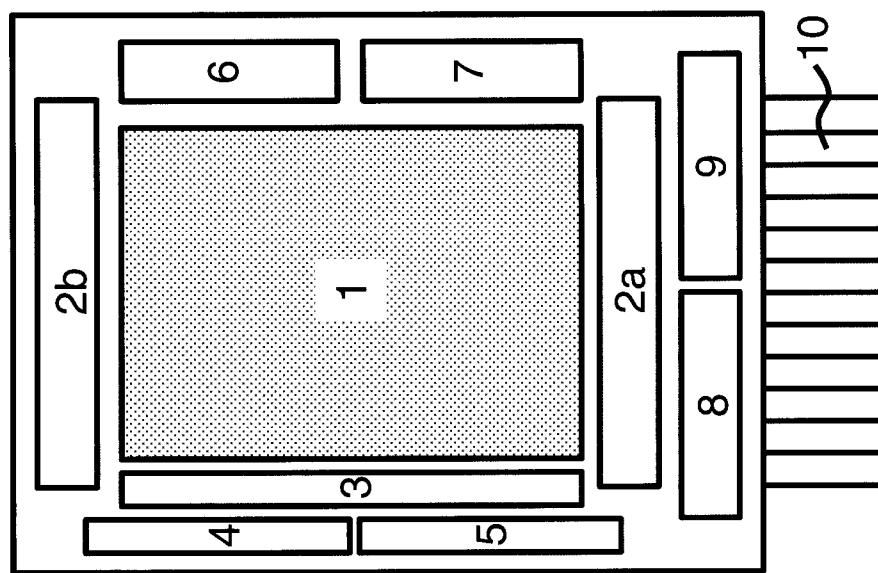

- [0061] Figur 7 Schematisches Blockdiagramm eines System-On-Panel Displays (von oben)

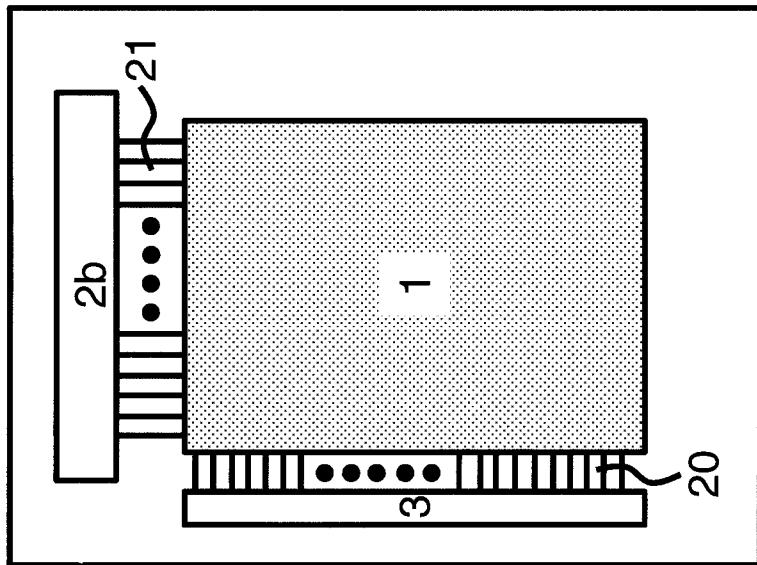

- [0062] Figur 8 Ausschnitt eines System-On-Panel Displays, der die Leiterbahnstrukturen zwischen Treiberschaltungen und TFT-Displaybereich von oben zeigt

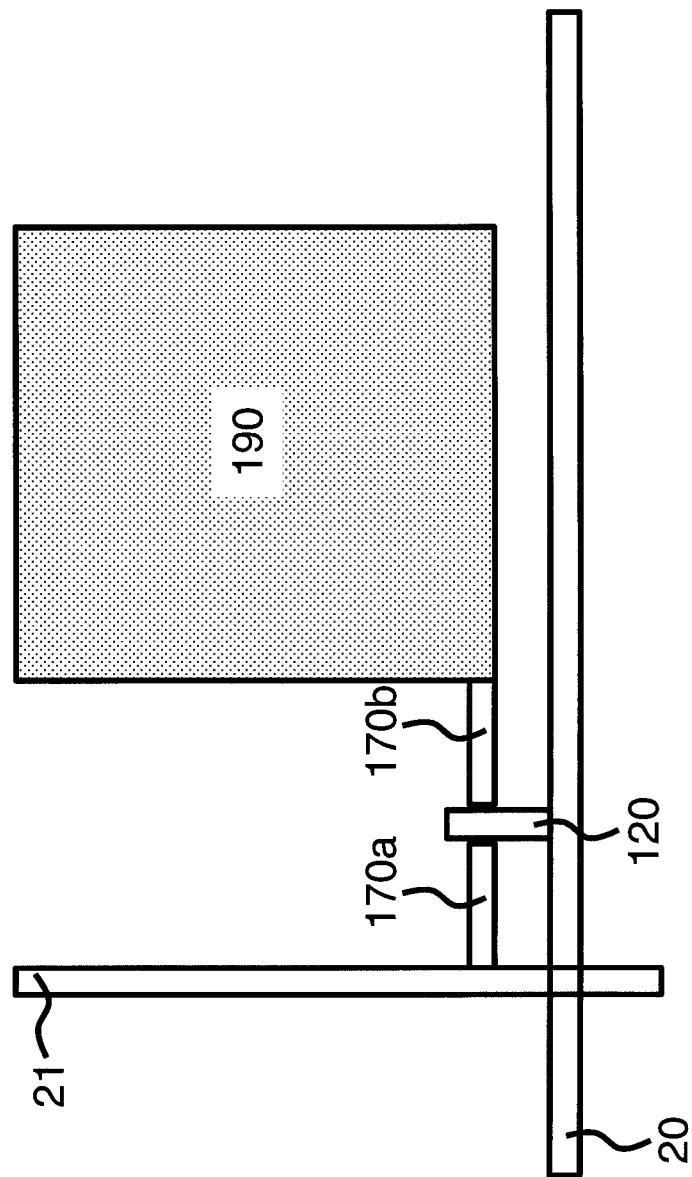

- [0063] Figur 9 Ausschnitt der TFT-Displaystruktur (von oben; Draufsicht), der zeigt, wie die Gate- und Source-/Drain-Elektroden des TFTs mit den Gate- und Data-Lines verbunden sind.

- [0064] Figur 10 Schichtaufbau eines top gate LTPS-TFTs im Querschnitt

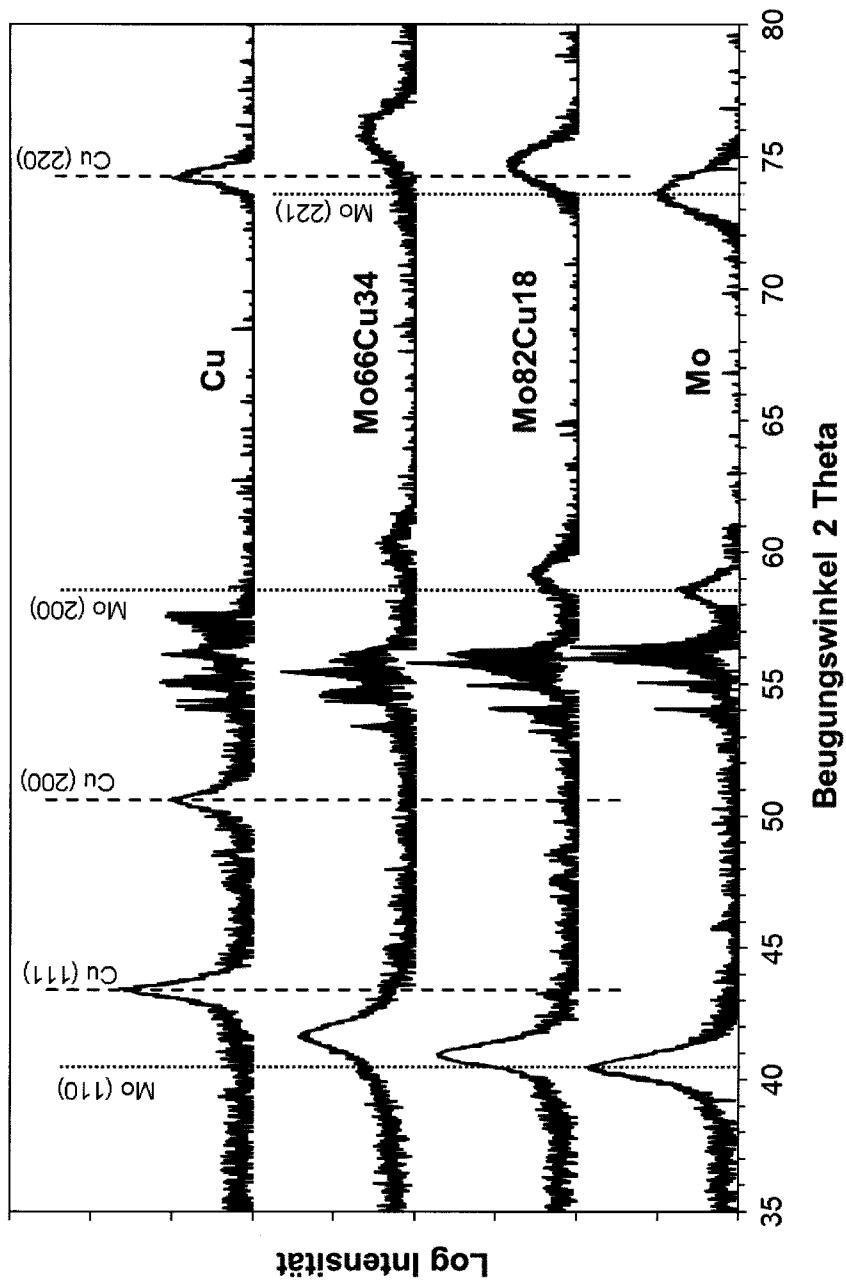

- [0065] Figur 11 Röntgendiffraktogramme von gesputterten 500 nm dicken MoCu Dünnschichten auf einem Siliziumwafer

- [0066] Figur 12 Röntgendiffraktogramme von gesputterten 500 nm dicken MoAg Dünnschichten auf einem Siliziumwafer

#### BEISPIEL 1:

[0067] Im Rahmen mehrerer Versuchsserien wurden unterschiedliche metallische Schichten auf Mo-Basis auf Polyimid Substrate abgeschieden. Dabei wurden Schichten mit unterschiedlicher chemischer Zusammensetzung gefertigt.

[0068] Die Zusammensetzungen der metallischen Schichten auf Mo-Basis sind in Tabelle 1 zusammengefasst.

[0069] Tabelle 1: Chemische Zusammensetzung der gesputterten MoCu Schichten

|           | Mo [at%] | Cu [at%] |

|-----------|----------|----------|

| Schicht 1 | 93       | 7        |

| Schicht 2 | 82       | 18       |

| Schicht 3 | 66       | 34       |

| Schicht 4 | 48       | 52       |

[0070] Als Referenzmaterial für die Molybdänbasislegierungen wurde reines Mo, in Form einer Molybdänschicht mit 50nm Dicke verwendet.

[0071] Alle Schichten wurden auf eine 50µm dicke Folie aus Polyimid (PI, z. B. „Kapton®“) bei Raumtemperatur abgeschieden. Die Prozessparameter wurden dabei konstant gehalten, um einen Einfluss unterschiedlicher Prozessbedingungen auf die Ergebnisse so weit als möglich auszuschließen. Die Schichtdicke wurde mit 50nm konstant gehalten um einen Einfluss geometrischer Effekte auf die Ergebnisse zu vermeiden.

[0072] Die Substratoberfläche war komplett beschichtet, es wurden keine kleineren Strukturen durch z. B. Ätzverfahren hergestellt.

[0073] An den Schichtproben auf den Polyimid Substraten wurde ein uniaxialer Zugversuch mit

einer MTS Tyron 250® Universalprüfmaschine durchgeführt. Der Versuchsaufbau ist schematisch in Figur 1 dargestellt. Dabei wurden die Substrate bis zu einer maximalen Dehnung 8 von 15% elastisch verformt. Während der Zugprüfung wurde der elektrische Widerstand der Schichten R unter Verwendung der Vierpunkt-Methode kontinuierlich aufgezeichnet. Der elektrische Widerstand zu Beginn der Messung wird als  $R_0$  bezeichnet. Die Probenlänge (freie Länge zwischen den Einspannungen) im Ausgangszustand betrug dabei 20mm und die Breite 5mm.

**[0074]** Der Messaufbau ist schematisch in Figur 1 dargestellt.  $L_{const}$  bezeichnet dabei die fixe Klemmlänge innerhalb der keine Dehnung stattfindet. Als kritische Dehnung wurde jene Dehnung  $\varepsilon_k$  definiert, bei der der elektrische Widerstand der Schichten R auf dem flexiblen Substrat um 10% gegenüber dem Ausgangszustand angestiegen ist, also  $R/R_0 = 1,1$ .

**[0075]** Die mittels dieses Zugversuches ermittelten kritischen Dehnungen  $\varepsilon_k$  sind in Tabelle 2 aufgeführt.

**[0076]** Tabelle 2: Kritische Dehnung  $\varepsilon_k$  der untersuchten Mo und MoCu Schichten, sowie die Differenz zur Referenzprobe aus reinem Mo. Des Weiteren ist der Schichtwiderstand einer 500 nm dicken Schicht auf einem nichtleitfähigen Boro-Silikatglas (Corning Eagle XG®) angegeben.

| Material    | kritische Dehnung $\varepsilon_k$ | $\Delta\varepsilon_k$ | Schichtwiderstand $\rho$ ( $\mu\text{Ohmcm}$ ) |

|-------------|-----------------------------------|-----------------------|------------------------------------------------|

| Mo          | 1,10%                             | Referenz              | 22                                             |

| MoCu 7at%   | 1,76%                             | 0,66                  | 77                                             |

| MoCu 18at%  | 2,09%                             | 0,99                  | 119                                            |

| MoCu 34at%  | 2,13%                             | 1,03                  | 132                                            |

| MoCu 52at.% | 3,23%                             | 2,13                  | 97                                             |

**[0077]** Die Figur 2 zeigt den Anstieg des elektrischen Widerstands im Vergleich zum Ausgangswiderstand ( $R/R_0$ ) gegenüber der aufgebrachten Dehnung  $\varepsilon$ . Die Kurve „Theorie“ bezeichnet die Zunahme des elektrischen Widerstandes, welche nur über die Formänderung der Probe entsteht. Wie in den an den Referenzmaterialien gemessenen Kurven ersichtlich, steigt der elektrische Widerstand sehr stark mit steigender Dehnung an.

**[0078]** Nach der oben beschriebenen Zugprüfung wurden die getesteten Schichten im Lichtmikroskop und Rasterelektronenmikroskop untersucht. Dabei wurden die Form der Risse und der mittlere Abstand zwischen den in den Schichten aufgetretenen Rissen beurteilt.

**[0079]** In einer Schicht auf Basis eines spröden Werkstoffes, wie beispielsweise reinem Mo, tritt beim Versagen der Probe unter Zugbelastung üblicherweise ein Rissbild auf, das für ein sprödes Werkstoffverhalten typisch ist. Dieses ist durch ein Netzwerk aus geraden, parallel verlaufenden Rissen, die sich annähernd im rechten Winkel zur Belastungsrichtung bilden, gekennzeichnet. Ein solches Rissbild ist beispielsweise in den Figuren 3 (Mo, links) zu erkennen. Diese geraden Risse verlaufen meist über die gesamte Breite der Probe von einer Seite zur anderen sowie durch die gesamte Dicke der Schicht. Solche Risse werden auch Through Thickness Cracks (TTC) genannt. TTCs reduzieren die elektrische Leitfähigkeit der Schicht beträchtlich, da im schlimmsten Fall keine durchgehende leitfähige Verbindung mehr in der Schicht vorhanden ist.

**[0080]** Die der Tabelle 2 zu entnehmenden kritischen Dehnungen aus dem Versagenskriterium  $R/R_0 = 1,1$  zeigen, dass mit steigendem Cu Gehalt in der Schicht die Zähigkeit der Schicht gesteigert wird. Es wird vermutet, dass diese Steigerung der Zähigkeit durch eine erleichterte Versetzungsbewegung im Material verursacht wird. Dies führt in weiterer Folge zu einer Erhöhung der kritischen Dehnung und zu einem reduzierten Auftreten von TTCs.

**[0081]** Als Beispiel zeigt Figur 2 die Widerstandskurve  $R/R_0$  der Proben MoCu 7at.%. Das Erscheinungsbild der Risse entspricht noch den TTCs, jedoch ist die kritische Dehnung  $\varepsilon_k$  bereits signifikant erhöht.

**[0082]** Ein weiterer Effekt der zusätzlich zur Erhöhung der kritischen Dehnung  $\epsilon_k$  beobachtet werden kann, ist, dass das Erscheinungsbild der Risse sich von einem spröden zu einem zähen Werkstoffverhalten ändert. Risse die für ein zähes Werkstoffverhalten typisch sind, sind daran zu erkennen, dass die Risse nicht mehr geradlinig sind, sondern eher einen Zick-Zack Verlauf aufweisen. Eine Umlenkung der Risse an den Riss spitzen ist eine mögliche Erklärung für ein solches Rissverhalten.

**[0083]** In Figur 3 (mittleres Bild, MoCu 18at%) ist zu erkennen, dass bei MoCu 18at% die Risse zwar weitestgehend parallel aber nicht mehr geradlinig verlaufen. In Figur 3 (rechtes Bild, MoCu 52at%) ist deutlich ein bereits zäheres Rissbild zu erkennen. Risse mit zäherem Charakter verlaufen meist durch die gesamte Schichtdicke, aber nicht zwangsläufig über die gesamte Probenbreite, wodurch noch leitfähige Verbindungen im Material vorhanden bleiben. Die Steigung der  $R/R_0$  Kurve ist in diesem Fall niedriger (die Kurve steigt weniger schnell an) wie dies in Figur 2 zu erkennen ist.

**[0084]** Schon ab einem kleinen Cu-Gehalt in der Schicht auf Mo-Basis wird somit die kritische Dehnung  $\epsilon_k$  signifikant erhöht und das Auftreten von Rissen reduziert. Bei weiterer Steigerung des Cu-Gehaltes wird das Rissverhalten von spröd in Richtung zäh verändert. Cu als Additiv zu Mo zeichnet sich folglich besonders dadurch aus, dass bereits niedrige Zugaben zu einer erheblichen Steigerung der Zähigkeit der Mo-basierten Schicht führen und dass Cu als Werkstoff vergleichsweise günstig ist.

**[0085]** In Figur 11 sind Röntgendiffraktogramme von zwei MoCu-Schichten mit einem Cu-Gehalt von 18at.% bzw. 34at.% gezeigt. Als Referenz sind auch Diffraktogramme von einer reinen Mo- bzw. Cu-Schicht inkludiert. Alle Schichten wurden mittels DC-Sputtern auf einem Siliziumwafer bei Raumtemperatur (ohne Substratheizung) abgeschieden und weisen eine Dicke von 500 nm auf. Die Kristallstruktur wurde mit einem Bruker-AXS D8 Diffraktometer, das mit einer Cu-Ka Röntgenstrahlungsquelle versehen ist, in streifendem Einfall (grazing incidence mode) mit einem Einfallswinkel von 2° aufgenommen. Als vertikale gepunktete Linie sind die Positionen der Röntgenreflexe von kubisch-raumzentriertem (krz) Molybdän (Raumgruppe Im-3m) bzw. als vertikale gestrichelte Linie die Reflexpositionen von kubisch flächenzentriertem (kfz) Kupfer (Raumgruppe Fm-3m) als Referenz eingezeichnet; die Daten wurden der Datenbank des ICDD (International Centre for Diffraction Data) entnommen. Wie in Figur 11 zu erkennen ist, weisen die beiden hoch-kupferhaltigen Systeme MoCu-18 at.% und MoCu-34 at% keine separate Cu-Phase auf, da die entsprechenden Reflexe im Diffraktogramm fehlen. Es ist daher davon auszugehen, dass das Cu im Molybdän zwangsgelöst, in Form eines Mischkristalls vorliegt, d. h. dass die Kupferatome Molybdän-Gitterplätze einnehmen. Die Kupferatome führen auf diese Art zu einer Verzerrung des Mo-Gitters. Auf das verzerrte Mo-Gitter deuten auch die beiden Mo (110) und Mo (200)-Reflexe hin, die im Vergleich zur unverzerrten Referenz zu höheren Beugungswinkeln (2 Theta) hin verschobenen sind, da das Cu-Atom (Atomradius 128 pm) kleiner als ein Mo-Atom (140 pm) ist.

**[0086]** Des Weiteren ist in Tabelle 2 in der letzten Spalte der Schichtwiderstand  $\rho$  ( $\mu\text{Ohmcm}$ ) von den verschiedenen Mo- bzw. MoCu-Dünnenschichten angegeben (500 nm Schichtdicke auf einem isolierenden Glassubstrat). Zur Messung wurde mittels Vierpunktmetode der spezifische Flächenwiderstand  $R_s$  ( $\text{Ohm}/\text{Sheet}$ ) gemessen und mit der Schichtdicke multipliziert. Der Schichtwiderstand der MoCu-Schichten steigt bis zu einem Cu-Gehalt von 34at.% an, und nimmt dann mit steigendem Cu-Gehalt wieder ab. Alle MoCu-Schichten weisen einen Schichtwiderstand kleiner 150  $\mu\text{Ohmcm}$  auf.

**[0087]** Im Falle von mehrlagigen Schichten aus MoCu/Cu oder MoCu/Al wird der Schichtwiderstand entlang einer langen Leiterbahn vor allem durch den jeweils besser leitfähigen Werkstoff Cu oder Al bestimmt. Eine zweilagige Schicht aus 50 nm MoCu34-at.% und 300 nm Cu darüber (abgeschieden auf einem nichtleitfähigen Glassubstrat) weist einen Schichtwiderstand von 2,0  $\mu\text{Ohmcm}$  auf. Eine zweilagige Schicht aus 50 nm MoCu34-at.% und 300 nm Al darüber weist einen Schichtwiderstand von 3,1  $\mu\text{Ohmcm}$  auf.

**[0088]** Es wird vermutet, dass die mechanischen Eigenschaften der untersuchten Schichten

noch weiter optimiert werden können. So ist es wahrscheinlich, dass über gezielte Wärmebehandlungen die Mikrostruktur und der Eigenspannungszustand der abgeschiedenen Schichten auf Mo-Basis weiter optimiert werden können. Auch über eine gezielte Einstellung der Abscheidebedingungen kann das Wachstum der Schichten gezielt beeinflusst und sehr wahrscheinlich eine weitere Steigerung der Zähigkeit erzielt werden.

#### BEISPIEL 2:

**[0089]** Im Rahmen mehrerer Versuchsserien wurden unterschiedliche metallische Schichten auf Mo-Basis auf Polyimid Substrate abgeschieden. Dabei wurden Schichten mit unterschiedlicher chemischer Zusammensetzung gefertigt.

**[0090]** Die Zusammensetzungen der metallischen Schichten auf Mo-Basis sind in Tabelle 3 zusammengefasst.

**[0091]** Tabelle 3: Chemische Zusammensetzung der gesputterten MoAg Schichten

|           | Mo [at%] | Ag [at%] |

|-----------|----------|----------|

| Schicht 1 | 82       | 18       |

| Schicht 2 | 69       | 31       |

| Schicht 3 | 56       | 44       |

| Schicht 4 | 48       | 52       |

**[0092]** Als Referenzmaterial für die Molybdänbasislegierungen wurde reines Mo in Form einer Molybdänschicht mit 50nm Dicke verwendet.

**[0093]** Alle Schichten wurden auf eine 50pm dicke Folie aus Polyimid (PI, z. B. „Kapton®“) bei Raumtemperatur abgeschieden. Die Prozessparameter wurden dabei konstant gehalten, um einen Einfluss unterschiedlicher Prozessbedingungen auf die Ergebnisse so weit als möglich auszuschließen. Die Schichtdicke wurde mit 50 nm konstant gehalten um einen Einfluss geometrischer Effekte auf die Ergebnisse zu vermeiden.

**[0094]** Die Substratoberfläche war komplett beschichtet, es wurden keine kleineren Strukturen durch z. B. Ätzverfahren hergestellt.

**[0095]** Die mittels eines Zugversuches, wie in Beispiel 1 beschrieben, ermittelten kritischen Dehnungen  $\epsilon_k$  sind in Tabelle 4 aufgeführt.

**[0096]** Tabelle 4: Kritische Dehnung  $\epsilon_k$  der untersuchten Mo und MoAg Schichten, sowie die Differenz zur Referenzprobe aus reinem Mo. Des Weiteren ist der Schichtwiderstand einer 500 nm dicken Schicht auf einem nichtleitfähigen Boro-Silikatglas (Corning Eagle XG) angegeben.

| Material    | kritische Dehnung $\epsilon_k$ | $\Delta\epsilon_k$ | Schichtwiderstand $\rho$ ( $\mu\text{Ohmcm}$ ) |

|-------------|--------------------------------|--------------------|------------------------------------------------|

| Mo          | 1,10%                          | Referenz           | 22                                             |

| MoAg 18at%  | 1,16%                          | 0,06               | 96                                             |

| MoAg 31at%  | 1,52%                          | 0,42               | 138                                            |

| MoAg 44at%  | 2,31%                          | 1,21               | 111                                            |

| MoAg 52at.% | 3,81%                          | 2,71               | 101                                            |

**[0097]** Nach der oben beschriebenen Zugprüfung wurden die getesteten Schichten im Lichtmikroskop und Rasterelektronenmikroskop untersucht. Dabei wurden die Form der Risse und der mittlere Abstand zwischen den in den Schichten aufgetretenen Rissen beurteilt.

**[0098]** In einer Schicht auf Basis eines spröden Werkstoffes, wie beispielsweise reinem Mo, tritt beim Versagen der Probe unter Zugbelastung üblicherweise ein Rissbild auf, das für ein sprödes Werkstoffverhalten typisch ist. Dieses ist durch ein Netzwerk aus geraden, parallel verlauf-

fenden Rissen, die sich annähernd im rechten Winkel zur Belastungsrichtung bilden, gekennzeichnet. Ein solches Rissbild ist beispielsweise in den Figuren 5 (Mo, links) zu erkennen. Diese geraden Risse verlaufen meist über die gesamte Breite der Probe von einer Seite zur anderen sowie durch die gesamte Dicke der Schicht. Solche Risse werden auch Through Thickness Cracks (TTC) genannt. TTCs reduzieren die elektrische Leitfähigkeit der Schicht beträchtlich, da im schlimmsten Fall keine durchgehende leitfähige Verbindung mehr in der Schicht vorhanden ist. Wie in den an den Referenzmaterialien gemessenen Kurven ersichtlich, steigt der elektrische Widerstand sehr stark mit steigender Dehnung an.

**[0099]** Dies ist Figur 4 zu entnehmen, die den Anstieg des elektrischen Widerstands im Vergleich zum Ausgangswiderstand ( $R/R_0$ ) gegenüber der aufgebrachten Dehnung  $\varepsilon$  zeigt.

**[00100]** Die der Tabelle 4 zu entnehmenden kritischen Dehnungen aus dem Versagenskriterium  $R/R_0 = 1,1$  zeigen, dass ab einem kritischen Ag Gehalt in der Schicht von größer 18 at.% die Zähigkeit der Schicht merklich gesteigert wird, wie aus der Figur 4 und der Tabelle 4 ersichtlich ist. Es wird vermutet, dass diese Steigerung der Zähigkeit durch eine erleichterte Versetzungsbewegung im Material verursacht wird. Dies führt in weiterer Folge zu einer Erhöhung der kritischen Dehnung und zu einem reduzierten Auftreten von TTCs. Ag als Additiv zu Mo zeichnet sich folglich besonders dadurch aus, dass höhere Zugaben zu einer sehr hohen Steigerung der Zähigkeit der Mo-basierten Schicht führen.

**[00101]** Als Beispiel zeigt Figur 4 die Widerstandskurven  $R/R_0$  der verschiedenen MoAg Proben. Das Erscheinungsbild der Risse entspricht noch den TTCs wie aus Figur 5 (oben rechts) ersichtlich ist, jedoch ist die kritische Dehnung  $\varepsilon_k$  bereits signifikant erhöht.

**[00102]** Ein weiterer Effekt, der zusätzlich zur Erhöhung der kritischen Dehnung  $\varepsilon_k$  beobachtet werden kann, ist, dass das Erscheinungsbild der Risse sich von einem spröden zu einem zähen Werkstoffverhalten ändert. Risse, die für ein zähes Werkstoffverhalten typisch sind, sind daran zu erkennen, dass die Risse nicht mehr geradlinig sind, sondern eher einen Zick-Zack Verlauf aufweisen. Eine Umlenkung der Risse an den Riss spitzen ist eine mögliche Erklärung für ein solches Rissverhalten.

**[00103]** In Figur 5 (Bild MoAg 44at%) ist zu erkennen, dass bei MoAg 44at% die Risse zwar weitestgehend parallel aber nicht mehr geradlinig verlaufen. In Figur 5 (MoAg 52at%) ist deutlich ein bereits zäheres Rissbild zu erkennen. Risse mit zäherem Charakter verlaufen meist durch die gesamte Schichtdicke, aber nicht zwangsläufig über die gesamte Probenbreite, wodurch noch leitfähige Verbindungen im Material vorhanden bleiben. Die Steigung der  $R/R_0$  Kurve ist in diesem Fall niedriger (die Kurve steigt weniger schnell an), wie dies in Figur 4 zu erkennen ist.

**[00104]** Ab einem kritischen Ag-Gehalt in der Schicht auf Mo-Basis von 18at.% wird die kritische Dehnung  $\varepsilon_k$  signifikant erhöht und das Auftreten von Rissen reduziert. Bei weiterer Steigerung des Ag-Gehaltes wird das Rissverhalten von spröd in Richtung zäh verändert.

**[00105]** In Figur 12 sind die Röntgendiffraktogramme der abgeschiedenen MoAg-Schichten dargestellt. Die Schichtabscheidung und Analyse der Kristallstruktur erfolgte analog dem MoCu-System (Figur 11). Als Referenz sind auch die Diffraktogramme von einer reinen Mo- bzw. Ag-Schicht inkludiert. Als vertikale gepunktete Linie sind in Figur 12 die Positionen der Röntgenreflexe von kubisch-raumzentriertem (krz) Molybdän (Raumgruppe Im-3m) bzw. als vertikale gestrichelte Linie die Reflexpositionen von kubisch flächenzentriertem (kfz) Silber (Raumgruppe Fm-3m) als Referenz eingezeichnet; die Daten wurden der Datenbank des ICDD (International Centre for Diffraction Data) entnommen. Wie in Figur 12 zu erkennen ist, weisen die MoAg-Systeme bis zu einem Silbergehalt von 44at.% keine separate Ag-Phase auf, da die entsprechenden Reflexe im Diffraktogramm fehlen. Es ist daher davon auszugehen, dass das Ag im Molybdän zwangsgelöst, in Form eines Mischkristalls vorliegt, d. h., dass die Silberatome Molybdän-Gitterplätze einnehmen. Die Silberatome führen auf diese Art zu einer Verzerrung des Mo-Gitters. Auf das verzerrte Mo-Gitter deuten auch die beiden Mo (110) und Mo (200)-Reflexe hin, die im Vergleich zur unverzerrten Referenz zu niedrigeren Beugungswinkeln (2 Theta) hin

verschobenen sind, da das Ag-Atom (Atomradius 165 pm) größer als ein Mo-Atom (140 pm) ist. Lediglich bei der MoAg-52at.% Schicht ist andeutungsweise ein (220) Silberreflex erkennbar, der auf eine beginnende Ausscheidung einer separaten Silberphase in der krz-Molybdänmatrix hindeutet.

**[00106]** In den MoCu- bzw. MoAg-Dünnschichten liegt das Kupfer bzw. Silber (Element X) also zwangsgelöst im krz-Molybdängitter vor. Die Kristallstruktur von reinem Gold (Au) ist die gleiche wie die von Cu und Ag (Raumgruppe Fm-3m). Alle drei Elemente stehen in der gleichen Nebengruppe (11) des Periodensystems der chemischen Elemente und zeigen in vielerlei Hinsicht ein ähnliches chemisches und physikalisches Verhalten. Daher ist davon auszugehen, dass auch gesputterte MoAu-Dünnschichten mit Au-Gehalten unter 40at.% in Form eines Mischkristalls vorliegen, in dem die Goldatome in der krz-Mo-Matrix zwangsgelöst sind.

**[00107]** Des Weiteren ist in Tabelle 4 in der letzten Spalte der Schichtwiderstand  $\rho$  ( $\mu\text{Ohmcm}$ ) der verschiedenen Mo- bzw. MoAg-Dünnschichten angegeben (500 nm Schichtdicke auf einem isolierenden Glassubstrat). Zur Messung wurde mittels Vierpunktmetode der spezifische Fächchenwiderstand  $R_s$  (Ohm/Sheet) gemessen und mit der Schichtdicke multipliziert. Der Schichtwiderstand der MoAg-Schichten steigt bis zu einem Ag-Gehalt von 31at.% an, und nimmt dann mit steigendem Ag-Gehalt wieder ab. Alle MoAg-Schichten weisen einen Schichtwiderstand kleiner 150  $\mu\text{Ohmcm}$  auf.

**[00108]** Im Falle von mehrlagigen Schichten aus MoAg/Cu oder MoAg/Al wird der Schichtwiderstand entlang einer langen Leiterbahn vor allem durch den jeweils besser leitfähigen Werkstoff Cu oder Al bestimmt. Eine zweilagige Schicht aus 50 nm MoAg 31at.% und 300 nm Cu darüber (abgeschieden auf einem nichtleitfähigen Glassubstrat) weist einen Schichtwiderstand von 2,0  $\mu\text{Ohmcm}$  auf. Eine zweilagige Schicht aus 50 nm MoAg 31at.% und 300 nm Al darüber weist einen Schichtwiderstand von 3,1  $\mu\text{Ohmcm}$  auf.

**[00109]** Eine oder mehrere metallische Lage(n), wie sie in Anspruch 2 und gegebenenfalls in einer der Weiterbildungen konkretisiert ist/sind, kann/können Teil eines Dünnschichttransistors (TFT) sein. Der Schichtaufbau eines solchen elektrischen Dünnschichtbauelements ist in Figur 6 im Querschnitt gezeigt. Der TFT besteht aus einer Halbleiterschicht 150, einer Gate-Elektrode 120, einer Source-Elektrode 170a, und einer Drain-Elektrode 170b, wobei zumindest eine dieser drei metallisch leitfähigen Elektrodenschichten aus der erfindungsgemäßen metallischen Lage besteht. Die Gate-Elektrode 120 ist von der Halbleiterschicht 150 durch eine elektrisch isolierende Schicht (Gate-Isolator, Gate Dielektrikum) 140 getrennt. Die Source-Elektrode 170a ist von der Drain-Elektrode 170b durch eine elektrisch isolierende Passivierungsschicht 180 getrennt. Des Weiteren trennt diese Passivierungsschicht 180 die Source-/Drain-Elektroden 170a/170b auch von der Pixel-Elektrodenschicht 190 (abgesehen von dem unterhalb beschriebenen Kontaktloch).

**[00110]** Im Folgenden wird der allgemeine Schichtaufbau eines bottom-gate TFTs, wie er in Fig. 6 gemäß einer Ausführungsform dargestellt ist, beschrieben. Der TFT- Schichtaufbau ist auf einem flexiblen Substrat 100 angeordnet. Zunächst kann auf dem flexiblen Substrat 100 eine Pufferschicht 110 angeordnet sein, die das gesamte Substrat 100 überdeckt, um etwaige Unebenheiten auf der Oberseite des flexiblen Substrats 100 auszugleichen oder das Eindringen von unerwünschten Verunreinigungen in die Halbleiterschicht 150, beispielsweise durch Diffusion oder Permeation, zu verhindern. Die Pufferschicht kann z.B. aus einer einlagigen oder mehrlagigen Schicht bestehen, die Siliziumoxid oder Siliziumnitrid beinhaltet.

**[00111]** Die Gate-Elektrode 120 ist über der Pufferschicht 110 angeordnet. Durch Anlegen einer elektrischen Spannung kann aufgrund eines elektrischen Feldeffektes in der Halbleiterschicht 150 ein elektrisch leitfähiger Kanal entstehen, der die Source-Elektrode 170a mit der Drain-Elektrode 170b elektrisch leitend verbindet. Die Gate-Elektrode 120 kann aus der erfindungsgemäßen metallischen Lage bestehen, oder aus einer dem Stand der Technik entsprechenden Metallisierung aus einer ein- oder mehrlagigen Schicht, die zumindest Aluminium (Al), Kupfer (Cu), Silber (Ag), Gold (Au), Platin (Pt), Molybdän (Mo), Wolfram (W), Titan (Ti), Chrom, (Cr), Niob (Nb), Tantal (Ta) beinhaltet.

**[00112]** Über der Gate-Elektrode 120 ist eine elektrisch isolierende Schicht (Gate-Dielektrikum) 140 angeordnet. Diese elektrisch isolierende Schicht 140 kann beispielsweise eine Schicht aus Siliziumoxid, Siliziumnitrid, Aluminiumoxid, oder einen elektrisch isolierenden organischen Werkstoff wie z.B. Benzocyclobuten (BCB) oder einen Acryl-haltigen Werkstoff beinhalten.

**[00113]** Die Halbleiterschicht 150 grenzt an die elektrisch isolierende Schicht (Gate-Dielektrikum) 140 an und kann z. B. amorphes Silizium (a-Si), poly-Silizium, einen Metalloxid-Halbleiter wie Indium-Gallium-Zink-Oxid (IGZO), oder einen organischen Halbleiter beinhalten. Im Falle einer Halbleiterschicht 150a, die a-Si beinhaltet, kann über dieser Schicht noch eine n+ dotierte Halbleiterschicht 150b angeordnet sein, beispielsweise phosphordotiertes a-Si beinhaltet. Im Falle einer Halbleiterschicht 150a, die einen Metalloxid-Halbleiter wie IGZO beinhaltet, entfällt in der Regel die dotierte Halbleiterschicht 150b.

**[00114]** Über der Halbleiterschicht 150 sind die Source- und Drain-Elektrodenschichten 170a und 170b angeordnet. Diese Schichten können aus der erfindungsgemäßen metallischen Lage bestehen, oder aus einer dem Stand der Technik entsprechenden Metallisierung aus einer ein- oder mehrlagigen Schicht, die zum mindesten Aluminium (Al), Kupfer (Cu), Silber (Ag), Gold (Au), Platin (Pt), Molybdän (Mo), Wolfram (W), Titan (Ti), Chrom, (Cr), Niob (Nb), Tantal (Ta) beinhaltet.

**[00115]** Über der Halbleiterschicht 150 und der Source-/Drain-Elektrodenschichten 170a/170b ist die Passivierungsschicht 180 angeordnet. Diese elektrisch isolierende Passivierungsschicht 180 kann beispielsweise eine Schicht aus Siliziumoxid, Siliziumnitrid, Aluminiumoxid, oder einen elektrisch isolierenden organischen Werkstoff wie z.B. Benzocyclobuten (BCB) oder einen Acryl-haltigen Werkstoff beinhalten.

**[00116]** Die Passivierungsschicht 180 ist durch ein Kontaktloch unterbrochen, das die angrenzende Pixel-Elektrodenschicht 190 mit der Drain-Elektrode 170b elektrisch verbindet. Die Pixel-Elektrodenschicht 190 ist elektrisch leitfähig und kann als optisch transparente Schicht oder als optisch reflektierende Schicht ausgebildet sein und ein- oder multilagig ausgeführt sein. Wenn die Pixel-Elektrodenschicht 190 als optisch transparente Schicht ausgebildet ist, kann sie beispielsweise Indium-Zinn-Oxid (ITO), Indium-Zink-Oxid (IZO), Zinkoxid (ZnO), oder Aluminium-Zink-Oxid (AZO) beinhalten. Wenn die Pixel-Elektrodenschicht 190 als optisch reflektierende Schicht ausgebildet ist, kann sie eine reflektierende Schicht aus Al, Ag, Mg, Pt, Pd, Au, Nd, Ni, Ir beinhalten, sowie eine Schicht beinhaltend Indium-Zinn-Oxid (ITO), Indium-Zink-Oxid (IZO), Zinkoxid (ZnO), oder Aluminium-Zink-Oxid (AZO).

**[00117]** Der hier beschriebene TFT kann Teil eines flexiblen TFT-LCD Displays oder OLED-Displays sein.

**[00118]** Eine oder mehrere metallische Lage(n), wie sie in Anspruch 2 und gegebenenfalls in einer der Weiterbildungen konkretisiert ist/sind, können Teil eines System-on-Panel (SOP) Systems sein, bei dem eine TFT-Aktiv-Matrixanzeige mit peripheren elektronischen Ansteuer-einheiten auf einem Substrat gemeinsam angeordnet ist. Ein SOP ist in Figur 7 gezeigt. Die Anzeigeeinheit 1 kann beispielsweise aus einer Flüssigkristallanzeige (LCD), einer Organischen Leuchtdiode (OLED), einer anorganischen Leuchtdiode (LED), oder einem elektrophoretischen Display („E-Ink®“; „e-paper“) bestehen. Die Anzeigeeinheit 1 stellt den eigentlichen sichtbaren Teil des Displays dar, auf dem der Bildinhalt dargestellt wird. Um diesen Bereich sind auf dem Substrat mehrere Treiber- und Ansteuerschaltkreise angeordnet, die in der Regel hinter einem lichtundurchlässigen Teil des Gehäuses, für den Benutzer nicht sichtbar, verborgen sind. Prinzipiell können eine oder mehrere der im Folgenden beschriebenen elektronischen Schaltungen auf dem SOP angeordnet sein, wobei diese Aufzählung nicht abschließend ist und je nach verwendeter Anzeigeeinheit noch weitere Schaltkreise zur Ansteuerung notwendig sein können.

**[00119]** Zur Ansteuerung der Anzeigeeinheit 1 kann eine horizontale Data-Treiberschaltung (Spaltentreiber) 2a/b auf dem Substrat angeordnet sein, die über die Data Lines (nicht eingezeichnet) mit den Source/Drain-Elektroden 170a/b des TFTs (nicht eingezeichnet) verbunden ist. Zur Ansteuerung der Gate-Elektroden 120 kann sich auf dem Substrat eine Gate-

Treiberstruktur (Zeilentreiber) 3 befinden, die über die Gate Lines (nicht eingezeichnet) mit den Gate-Elektroden 120 der TFTs (nicht eingezeichnet) verbunden ist.

[00120] Des Weiteren kann im peripheren Bereich eine DC-DC Konverter-Schaltung 4 angeordnet sein, die eine niedrigere Eingangsspannung in eine höhere Ausgangsspannung umwandelt; zur Ansteuerung eines TFT-LCD Displays könnte z.B. am Eingang eine Spannung von +3,3 bis +5,0 V anliegen, die in eine höhere Ausgangsspannung im Bereich -40 bis +40V umgewandelt wird („charge pump“), die zur Ansteuerung des Flüssigkristalls benötigt wird.

[00121] Des Weiteren kann auf dem SOP eine elektrische Schaltung 5 angeordnet sein, die eine Referenzspannung (Vcom, z.B. +5V für ein LCD Display) für die Anzeigeeinheit 1 bereitstellt.

[00122] Des Weiteren könnte auf dem Substrat eine Timing Controller Schaltung (TCon) 6, eine Digital-Analog-Wandlerschaltung 7, eine Entladungsstufe 8, und eine Vcom Pufferschaltung 9 angeordnet sein.

[00123] Das SOP ist über einen Kontaktierungsbereich 10 mit den übrigen Komponenten der Displayansteuerelektronik oder einer Grafikkarte verbunden.

[00124] Die peripheren Schaltkreise 2 bis 9 sind untereinander, mit der Anzeigeeinheit 1 und dem Kontaktierungsbereich („Pad-Kontakte“) 10 mit der erfindungsgemäßen metallischen Lage (nicht eingezeichnet) verbunden.

[00125] In Figur 8 ist die Kontaktierung der Anzeigeeinheit 1 beispielhaft dargestellt. Der Zeilentreiber 3 ist über elektrische Leiterbahnen 20 mit der Anzeigeeinheit 1 verbunden, der Spaltentreiber 2b ist über elektrische Leiterbahnen 21 mit der Anzeigeeinheit 1 verbunden. Eine oder beide Leiterbahnen 20 oder 21 können aus der erfindungsgemäßen metallischen Lage, wie sie in Anspruch 2 und gegebenenfalls in einer der Weiterbildungen konkretisiert ist, bestehen.

[00126] In Figur 9 ist die Kontaktierung eines Dünnschichttransistors (TFT) mit den Gate- und Data-Lines gezeigt. Die Gate-Leiterbahn 20 hat im Bereich des TFTs eine Erweiterung, die die Gate-Elektrode 120 des TFTs bildet. Die Data-Leiterbahn 21 hat im Bereich des TFTs eine Erweiterung, die die Source-Elektrode 170a des TFT bildet, sowie einen von der Source-Elektrode unterbrochenen Bereich, der die Drain-Elektrode 170b des TFT bildet, und der mit der Pixel-Elektrode 190 verbunden ist. Eine oder beide Leiterbahnen 20 oder 21 bzw. der TFT-Elektroden 120, 170a/b können aus der erfindungsgemäßen metallischen Lage, wie sie in Anspruch 2 und gegebenenfalls in einer der Weiterbildungen konkretisiert ist, bestehen.

[00127] Ferner können eine oder mehrere metallische Lage(n), wie sie in Anspruch 2 und gegebenenfalls in einer der Weiterbildungen konkretisiert ist/sind, Teil eines low temperature poly-Silicon (LTPS) Dünnschichttransistors (TFT) sein, dessen Schichtaufbau im Querschnitt in Figur 10 exemplarisch gezeigt ist. Im Vergleich zur TFT Struktur aus Figur 6 handelt es sich in diesem Fall um einen top-gate TFT, d.h. die Gate-Elektrode 240 ist über der Halbleiterschicht 220 angeordnet, und nicht darunter. LTPS-TFTs werden bevorzugt als top-gate TFT ausgeführt. Der LTPS-Halbleiter weist im Vergleich zum amorphen Silizium ( $0,5 - 1,5 \text{ cm}^2/\text{Vs}$ ) eine deutlich höhere Ladungsträgermobilität auf ( $50 - 200 \text{ cm}^2/\text{Vs}$ ). Damit kann ein solcher TFT auch zur Ansteuerung von stromgetriebenen Anzeigen wie z.B. OLEDs oder Micro-LEDs eingesetzt werden.

[00128] Im Folgenden wird der Schichtaufbau für einen top-gate LTPS TFT exemplarisch beschrieben. Der LTPS-TFT ist auf einem flexiblen Substrat 200 angeordnet. Zunächst kann auf dem flexiblen Substrat 200 eine Pufferschicht 210 angeordnet sein, die das gesamte Substrat 200 überdeckt, um etwaige Unebenheiten auf der Oberseite des flexiblen Substrats 200 auszugleichen oder das Eindringen von unerwünschten Verunreinigungen in die Halbleiterschicht 220 oder in dotierte Halbleiterbereiche 221 (Source-Elektrode) und 222 (Drain-Elektrode), beispielsweise durch Diffusion oder Permeation, zu verhindern. Die Pufferschicht 210 kann z.B. aus einer einlagigen oder mehrlagigen Schicht bestehen, die Siliziumoxid, Siliziumnitrid, oder

Siliziumoxynitrid beinhaltet. Je nach Beschaffenheit des Substrates kann auch auf die Pufferschicht verzichtet werden.

**[00129]** Die Halbleiterschicht 220, die aus undotiertem, polykristallinem Silizium bestehen kann, ist auf der Pufferschicht 210 angeordnet. An diese Schicht 220 (auch „channel area“ genannt) angrenzend befindet sich auf der einen Seite eine Source-Elektrode 221 und auf der anderen Seite eine Drain-Elektrode 222, die jeweils aus dotiertem Polysilizium bestehen können. Die Dotierung kann beispielsweise durch Ionenimplantation erfolgen; durch Verwendung von Bor (B), oder  $B_2H_6$  kann beispielsweise eine p-Dotierung erzielt werden. Je nach Ausführung des TFTs kann die Art der Dotierung (p oder n), bzw. die Art des Dotanden allerdings variieren.

**[00130]** Eine Gate-Isolatorschicht 230 ist über den Halbleiterschichten 220, 221 und 222 angeordnet. Diese Gate-Isolatorschicht 230 kann z.B. aus Siliziumnitrid oder Siliziumoxid bestehen. Auf der Gate-Isolatorschicht 230 ist die Gate-Elektrode 240 so angeordnet, dass sie zumindest einen gewissen Bereich Überlapp (in vertikaler Richtung) zur channel area (Halbleiterschicht 220) aufweist. Die Gate-Elektrode 240 kann aus der erfindungsgemäßen metallischen Lage bestehen, oder aus einer dem Stand der Technik entsprechenden Metallisierung aus einer ein- oder mehrlagigen Schicht, die zumindest Aluminium (Al), Kupfer (Cu), Silber (Ag), Gold (Au), Platin (Pt), Molybdän (Mo), Wolfram (W), Titan (Ti), Chrom, (Cr), Niob (Nb), Tantal (Ta) beinhaltet. Die Gate-Elektrode 240 ist über Gate-Lines (nicht gezeigt) mit der Ansteuerelektronik (nicht gezeigt), u.a. die Zeilentreiber, verbunden.

**[00131]** Über der Gate-Elektrode 240 bzw. der Gate-Isolatorschicht 230 ist eine isolierende Schicht 250 aufgebracht, die aus einem ähnlichen Material wie die Gate-Isolatorschicht 230 bestehen kann, z. B. Siliziumnitrid oder Siliziumoxid. Die isolierende Schicht 250 und die Gate-Isolatorschicht 230 sind mit Durchgangslöchern („through holes“) versehen, die die Source- und Drain-Elektroden 221/222 der Halbleiterschicht (elektrisch) zugänglich machen.

**[00132]** Eine Ansteuer- bzw. Kontaktierungs-Source-Elektrodenschicht 260 sowie eine Ansteuer- bzw. Kontaktierungs-Drain-Elektrodenschicht 270 sind über der isolierenden Schicht 250 angeordnet und über die oben beschriebenen Durchgangslöcher mit den Source-/Drain-Elektroden 221/222 des Halbleiters verbunden. Die Ansteuer- bzw. Kontaktierungs-Source-/Drain-Elektrodenschichten 260/270 können aus der erfindungsgemäßen metallischen Lage bestehen oder aus einer dem Stand der Technik entsprechenden Metallisierung aus einer ein- oder mehrlagigen Schicht, die zumindest Aluminium (Al), Kupfer (Cu), Silber (Ag), Gold (Au), Platin (Pt), Molybdän (Mo), Wolfram (W), Titan (Ti), Chrom, (Cr), Niob (Nb), Tantal (Ta) beinhaltet. Die Ansteuer- bzw. Kontaktierungs-Source-Elektrodenschicht 260 ist über die Data-Lines (Signal-Lines; nicht gezeigt) mit der Ansteuerelektronik, u. a. den Spaltentreibern (nicht gezeigt) verbunden.

**[00133]** Der Dünnschichttransistor wird aus der Halbleiterschicht 220, der Gate-Elektrode 240, und den Ansteuer- bzw. Kontaktierungs-Source-/Drain-Elektrodenschichten 260/270 gebildet. Die Konfiguration des TFT ist jedoch nicht auf das oben beschriebene Ausführungsbeispiel beschränkt, sondern kann auch zahlreiche andere Konfigurationen aufweisen, die durch einen Experten leicht umgesetzt werden können.

**[00134]** Über der TFT-Struktur kann noch eine Planarisierungsschicht 280 angeordnet sein, insbesondere wenn über dem TFT noch weitere lichtemittierende Schichten, z.B. OLED-Schichten, angeordnet sind (nicht gezeigt). Die Planarisierungsschicht 280 kann z.B. ein Polyacrylatharz, ein Epoxidharz, ein Phenolharz, ein Polyamidharz, ein Polyimidharz, ein ungesättigtes Polyesterharz, ein Polyphenylen-Ether-Harz, ein Polyphenylen-Sulfid-Harz, oder Benzocyclobutene (BCB) beinhalten. Die Planarisierungsschicht 280 ist mit einem Durchgangsloch versehen, das einen Bereich der Ansteuer- bzw. Kontaktierungs-Drain-Elektrodenschicht 270 zugänglich macht.

**[00135]** Exemplarisch ist in Figur 10 noch eine Pixel-Elektrodenschicht 290 gezeigt, die über der Planarisierungsschicht 280 angebracht ist und die über das Durchgangsloch mit der Ansteuer- bzw. Kontaktierungs-Drain-Elektrodenschicht 270 elektrisch leitend verbunden ist. Im

Falle eines LTPS-OLED Displays bildet die Pixel-Elektrodenschicht 290 die erste Elektrode (in der Regel die Anode bei einer nach oben emittierenden Struktur) einer lichtemittierenden Struktur. Wenn die Pixel-Elektrodenschicht 290 als optisch transparente Schicht ausgebildet ist kann sie beispielsweise Indium-Zinn-Oxid (ITO), Indium-Zink-Oxid (IZO), Zinkoxid (ZnO), oder Aluminium-Zink-Oxid (AZO) beinhalten.

**[00136]** Wenn die Pixel-Elektrodenschicht 290 als optisch reflektierende Schicht ausgebildet ist kann sie eine reflektierende Schicht aus Al, Ag, Mg, Pt, Pd, Au, Nd, Ni, Ir beinhalten, sowie eine Schicht beinhaltend Indium-Zinn-Oxid (ITO), Indium-Zink-Oxid (IZO), Zinkoxid (ZnO), oder Aluminium-Zink-Oxid (AZO).

**[00137]** Es wird vermutet, dass die mechanischen Eigenschaften der untersuchten Schichten noch weiter optimiert werden können. So ist es wahrscheinlich, dass über gezielte Wärmebehandlungen die Mikrostruktur und der Eigenspannungszustand der abgeschiedenen Schichten auf Mo-Basis weiter optimiert werden können. Auch über eine gezielte Einstellung der Abscheidebedingungen kann das Wachstum der Schichten gezielt beeinflusst und sehr wahrscheinlich eine weitere Steigerung der Zähigkeit erzielt werden.

## BEZUGSZEICHENLISTE:

|                    |                                                         |

|--------------------|---------------------------------------------------------|

| R                  | elektrischer Widerstand der Schichten                   |

| $R_0$              | elektrischer Widerstand zu Beginn der Messung           |

| $R_0$              | spezifischer Flächenwiderstand                          |

| $\epsilon$         | maximale Dehnung                                        |

| $\epsilon_k$       | kritische Dehnung                                       |

| $L_{\text{const}}$ | fixe Klemmlänge innerhalb der keine Dehnung stattfindet |

| $\rho$             | Schichtwiderstand                                       |

| 1                  | Anzeigeeinheit                                          |

| 2a/b               | Data-Treiberschaltung (Spaltentreiber)                  |

| 3                  | Gate-Treiberstruktur (Zeilentreiber)                    |

| 4                  | DC-DC Konverter-Schaltung                               |

| 5                  | elektrische Schaltung                                   |

| 6                  | Timing Controller Schaltung (TCon)                      |

| 7                  | Digital-Analog-Wandlerschaltung                         |

| 8                  | Entladungsstufe                                         |

| 9                  | Pufferschaltung                                         |

| 10                 | Kontaktierungsbereich („Pad-Kontakte“)                  |

| 20                 | elektrische Leiterbahnen                                |

| 21                 | elektrische Leiterbahnen                                |

| 100                | flexibles Substrat                                      |

| 110                | Pufferschicht                                           |

| 120                | Gate-Elektrode                                          |

| 140                | isolierende Schicht (Gate-Isolator, Gate Dielektrikum)  |

| 150                | Halbleiterschicht                                       |

| 170a               | Source-Elektrode                                        |

| 170b               | Drain-Elektrode                                         |

| 180                | elektrisch isolierende Passivierungsschicht             |

| 190                | Pixel-Elektrodenschicht                                 |

| 200                | flexibles Substrat                                      |

| 210                | Pufferschicht                                           |

| 220                | Halbleiterschicht                                       |

| 221                | dotierte Halbleiterbereiche (Source-Elektrode)          |

| 222                | dotierte Halbleiterbereiche (Drain-Elektrode)           |

| 230                | Gate-Isolatorschicht                                    |

| 240                | Gate-Elektrode                                          |

| 250                | isolierende Schicht                                     |

| 260                | Ansteuer- bzw. Kontaktierungs-Source-Elektrodenschicht  |

| 270                | Ansteuer- bzw. Kontaktierungs-Drain-Elektrodenschicht   |

| 280                | Planarisierungsschicht                                  |

| 290                | Pixel-Elektrodenschicht                                 |

## Ansprüche

1. Beschichtetes flexibles Bauteil enthaltend:

- ein flexibles Substrat (100, 200)

- mindestens einen auf dem Substrat (100, 200) unmittelbar oder über eine oder mehrere Zwischenschichten angeordneten Schichtaufbau, der eine metallische Lage mit einer zu der einen Seite an die metallische Lage unmittelbar angrenzenden halbierenden oder elektrisch isolierenden Lage sowie zu der anderen Seite an die metallische Lage unmittelbar angrenzenden halbleitenden oder elektrisch isolierenden Lage aufweist,

**dadurch gekennzeichnet**, dass die metallische Lage gebildet wird aus:

- einer Einzelschicht aus MoX, oder

- einem Zweischichtsystem aus MoX in Kombination mit einer Cu-basierten Schicht oder aus MoX in Kombination mit einer Al-basierten Schicht, oder

- einem Dreischichtsystem aus zwei MoX-Schichten mit dazwischenliegender Cu-basierter Schicht oder aus zwei MoX-Schichten mit dazwischenliegender Al-basierter Schicht,wobei X eines oder mehrere Elemente aus der Gruppe von Cu, Ag, Au ist.

2. Bauteil nach dem vorangehenden Anspruch, wobei in mindestens einer MoX-Schicht X das Element Cu ist und diese MoCu-Schicht mehr als 0,5 at% und weniger als 50 at% Cu enthält.

3. Bauteil nach Anspruch 1 oder 2, wobei in mindestens einer MoX-Schicht X das Element Ag ist und diese MoAg-Schicht mehr als 10 at% und weniger als 50 at% Ag enthält.

4. Bauteil nach wenigstens einem der Ansprüche 1 bis 3, wobei in mindestens einer MoX-Schicht X das Element Au ist und diese metallische MoAu-Schicht mehr als 5 at% und weniger als 20 at% Au enthält.

5. Bauteil nach wenigstens einem der Ansprüche 1 bis 4, wobei X in der Mo-Schicht gelöst in Form eines Mischkristalls vorliegt.

6. Bauteil nach wenigstens einem der Ansprüche 1 bis 5, wobei die einzelne MoX-Schicht einen Schichtwiderstand  $\rho$  von kleiner 200  $\mu\text{Ohmcm}$  aufweist.

7. Bauteil nach wenigstens einem der vorangehenden Ansprüche, wobei das flexible Substrat (100, 200) gesondert von den elektrisch isolierenden Lagen ausgebildet ist.

8. Bauteil nach wenigstens einem der Ansprüche 1 bis 6, wobei das flexible Substrat (100, 200) durch eine der an die metallische Lage unmittelbar angrenzenden halbleitenden oder elektrisch isolierenden Lagen gebildet wird.

9. Bauteil nach wenigstens einem der vorangehenden Ansprüche, wobei mindestens eine der an die metallische Lage unmittelbar angrenzenden halbleitenden oder elektrisch isolierenden Lagen als Schichten (140, 150, 220, 250) ausgebildet sind.

10. Bauteil nach wenigstens einem der vorangehenden Ansprüche, wobei die Dicke der metallischen Lage kleiner 1  $\mu\text{m}$ , bevorzugt kleiner 500 nm bevorzugt 5 bis 100 nm, ist.

11. Bauteil nach wenigstens einem der vorangehenden Ansprüche, wobei das flexible Substrat (100, 200) transparent ist.

12. Bauteil nach wenigstens einem der vorangehenden Ansprüche, wobei die metallische Lage insgesamt einen Schichtwiderstand  $\rho$  kleiner 50  $\mu\text{Ohmcm}$  aufweist.

13. Bauteil nach wenigstens einem der vorangehenden Ansprüche, wobei das flexible Substrat (100, 200) zumindest ein Material der folgenden Gruppe umfasst:

- Polymer

- Dünnglas

- Metallfolie

- mineralisches Material.

14. Bauteil nach wenigstens einem der vorangehenden Ansprüche, wobei die metallische Lage bei 2% elastischer Dehnung ( $\epsilon$ ) ein Verhältnis des elektrischen Widerstands ( $R$ ) zum elektrischen Widerstand am Beginn der Messung ( $R_0$ ), ( $R/R_0$ ) von kleiner 1,2 aufweist.

15. Bauteil nach wenigstens einem der vorangehenden Ansprüche, wobei das beschichtete flexible Bauteil (100, 200) mindestens eine Leiterbahnstruktur aufweist und vorzugsweise vorgesehen ist, dass die metallische Lage Teil der mindestens einen Leiterbahnstruktur ist.

16. Bauteil nach wenigstens einem der vorangehenden Ansprüche, wobei die metallische Lage Teil einer TFT Struktur ist.

17. Bauteil nach wenigstens einem der vorangehenden Ansprüche, wobei die metallische Lage Teil einer aktiv Matrix Struktur ist.

18. Bauteil nach wenigstens einem der vorangehenden Ansprüche, wobei das beschichtete flexible Bauteil ein Bauteil aus der folgenden Gruppe ist: flexibles LCD Display, flexibles OLED Display, flexibles elektrophoretisches Display (e-Paper, E-Ink®), flexible Solarzelle, elektrochrome flexible Folie, flexible Dünnschichtbatterie.

19. Verfahren zur Herstellung eines beschichteten flexiblen Bauteils nach einem der Ansprüche 1 bis 18, umfassend zumindest die folgenden Schritte:

- Bereitstellen eines flexiblen Substrats (100, 200)

- Beschichten des flexiblen Substrats (100, 200) - unmittelbar oder über eine oder mehrere Zwischenschichten -durch Abscheiden mindestens einer MoX-Schicht, **dadurch gekennzeichnet**, dass die MoX-Schicht mehr als 0,5 at% X enthält, wobei X eines oder mehrere Elemente aus der Gruppe von Cu, Ag, Au ist.

20. Verfahren nach dem vorangehenden Anspruch, wobei das Abscheiden der mindestens einen metallischen Lage mittels eines PVD Verfahrens realisiert wird.

Hierzu 12 Blatt Zeichnungen

1/12

Fig. 1

2/12

Fig. 2

3/12

Fig. 3

4/12

Fig. 4

S/12

Fig. 5

6/12

Fig. 6

7/12

**Fig. 7**

8/12

Fig. 8

9/12

**Fig. 9**

10/12

**Fig. 10**

11/12

Fig. 11

12/12

Fig. 12