(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6104784号

(P6104784)

(45) 発行日 平成29年3月29日(2017.3.29)

(24) 登録日 平成29年3月10日(2017.3.10)

(51) Int.Cl.

G05F 3/24 (2006.01)

F 1

G 05 F 3/24

B

請求項の数 8 (全 10 頁)

(21) 出願番号 特願2013-252159 (P2013-252159)

(22) 出願日 平成25年12月5日 (2013.12.5)

(65) 公開番号 特開2015-109019 (P2015-109019A)

(43) 公開日 平成27年6月11日 (2015.6.11)

審査請求日 平成28年2月22日 (2016.2.22)

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100107582

弁理士 関根 毅

(74) 代理人 100117787

弁理士 勝沼 宏仁

(74) 代理人 100118843

弁理士 赤岡 明

(74) 代理人 100167933

弁理士 松野 知絵

(72) 発明者 門脇 宏和

東京都港区芝浦一丁目1番1号 株式会社

東芝内

最終頁に続く

(54) 【発明の名称】基準電圧生成回路

## (57) 【特許請求の範囲】

## 【請求項1】

第1端が第1電源に接続可能であり、制御端と第2端とが短絡された第1導電型の第1スイッチング素子と、

第2端が前記第1スイッチング素子の第2端に接続され、制御端にバイアス電圧が供給される、ノーマリオン型かつ第2導電型の第2スイッチング素子と、

第2端が前記第2スイッチング素子の第1端に接続され、第1端と制御端とが短絡され、この第1端が基準電圧を出力する、ノーマリオン型かつ第2導電型の第3スイッチング素子と、

前記基準電圧に基づいて前記基準電圧より低い前記バイアス電圧を生成するように構成されたバイアス電圧生成部と、

第2端に前記バイアス電圧が供給され、制御端が前記第3スイッチング素子の制御端に接続され、第1端が第2電源に接続可能である、ノーマリオフ型かつ第2導電型の第4スイッチング素子と、を備えることを特徴とする基準電圧生成回路。

## 【請求項2】

前記バイアス電圧生成部は、前記第3スイッチング素子と、前記第4スイッチング素子との間に設けられる第1抵抗素子を有することを特徴とする請求項1に記載の基準電圧生成回路。

## 【請求項3】

第1端が第1電源に接続可能であり、制御端と第2端とが短絡された第1導電型の第1

10

20

スイッチング素子と、

第2端が前記第1スイッチング素子の第2端に接続され、制御端にバイアス電圧が供給される、ノーマリオン型かつ第2導電型の第2スイッチング素子と、

第2端が前記第2スイッチング素子の第1端に接続され、第1端と制御端とが短絡され、この第1端が基準電圧を出力する、ノーマリオン型かつ第2導電型の第3スイッチング素子と、

第1端が前記第3スイッチング素子の第1端に接続され、第2端が前記第2スイッチング素子の制御端に接続され、この第2端が前記バイアス電圧を出力する第1抵抗素子を有するバイアス電圧生成部と、

第2端に前記バイアス電圧が供給され、制御端が前記第3スイッチング素子の制御端に接続され、第1端が第2電源に接続可能である、ノーマリオフ型かつ第2導電型の第4スイッチング素子と、を備えることを特徴とする基準電圧生成回路。 10

【請求項4】

前記バイアス電圧生成部は、前記第1抵抗素子の抵抗値に応じた前記バイアス電圧を生成することを特徴とする請求項2または3に記載の基準電圧生成回路。

【請求項5】

前記第1抵抗素子の抵抗値は、前記バイアス電圧によって前記第2スイッチング素子および前記第4スイッチング素子がオンする大きさであることを特徴とする請求項4に記載の基準電圧生成回路。 20

【請求項6】

前記バイアス電圧生成部は、前記第3スイッチング素子と、前記第4スイッチング素子との間に設けられる、ノーマリオフ型かつ第2導電型の第5スイッチング素子を有することを特徴とする請求項1に記載の基準電圧生成回路。

【請求項7】

前記バイアス電圧生成部は、

第2端が前記第3スイッチング素子の第1端に接続され、制御端が前記第3スイッチング素子の制御端と接続される第6スイッチング素子と、

前記第6スイッチング素子と、前記第4スイッチング素子と、の間に設けられる第2抵抗素子と、を有することを特徴とする請求項1に記載の基準電圧生成回路。 30

【請求項8】

前記第4スイッチング素子は、前記第3スイッチング素子の温度特性をキャンセルする温度特性を持つことを特徴とする請求項1乃至7のいずれかに記載の基準電圧生成回路。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、基準電圧生成回路に関する。

【背景技術】

【0002】

基準電圧生成回路は、リニアレギュレータなどに用いられる基準電圧を生成する回路である。基準電圧生成回路は、基準電圧生成回路を構成する素子の温度が変動したとしても、生成される基準電圧ができるだけ変動しないことが望ましい。 40

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2011-113321号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明の実施形態が解決しようとする課題は、温度依存性を抑制できる基準電圧生成回路を提供することである。 50

## 【課題を解決するための手段】

## 【0005】

実施形態によれば、第1端が第1電源に接続可能であり、制御端と第2端とが短絡された第1導電型の第1スイッチング素子と、第2端が前記第1スイッチング素子の第2端に接続可能であり、制御端にバイアス電圧が供給される、ノーマリオン型かつ第2導電型の第2スイッチング素子と、第2端が前記第2スイッチング素子の第1端に接続され、第1端と制御端とが短絡され、この第1端が基準電圧を出力する、ノーマリオン型かつ第2導電型の第3スイッチング素子と、前記基準電圧に基づいて前記基準電圧より低い前記バイアス電圧を生成するように構成されたバイアス電圧生成部と、第2端に前記バイアス電圧が供給され、制御端が前記第3スイッチング素子の制御端に接続され、第1端が第2電源に接続可能である、ノーマリオフ型かつ第2導電型の第4スイッチング素子と、を備えることを特徴とする基準電圧生成回路が提供される。

## 【図面の簡単な説明】

## 【0006】

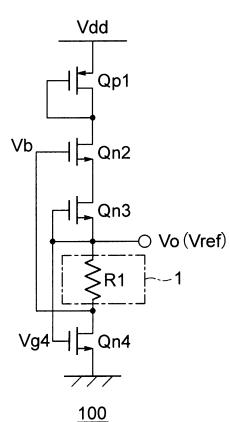

【図1】一実施形態に係る基準電圧生成回路100の回路図。

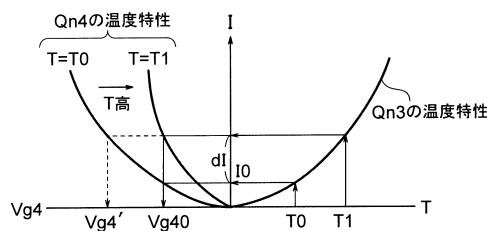

【図2】トランジスタQn3, Qn4の温度特性を模式的に示す図。

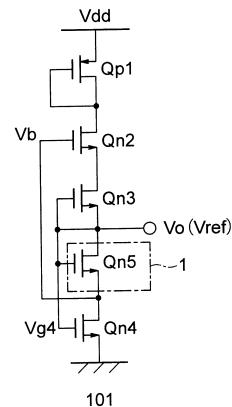

【図3】図1の基準電圧生成回路100の第1変形例である基準電圧生成回路101の回路図。

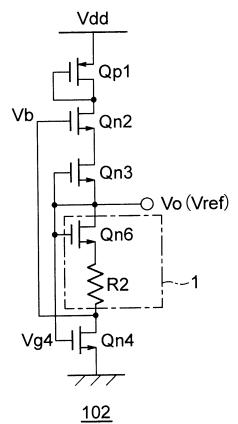

【図4】図1の基準電圧生成回路100の第2変形例である基準電圧生成回路102の回路図。

## 【発明を実施するための形態】

## 【0007】

以下、実施形態について、図面を参照しながら具体的に説明する。

## 【0008】

図1は、一実施形態に係る基準電圧生成回路100の回路図である。基準電圧生成回路100は、p型（第1導電型）MOS（Metal Oxide Semiconductor）トランジスタ（第1スイッチング素子）Qp1と、デプレッション型のn型（第2導電型）MOSトランジスタ（第2スイッチング素子）Qn2と、デプレッション型のnMOSトランジスタ（第3スイッチング素子）Qn3と、抵抗素子R1と、エンハンスマント型のnMOSトランジスタ（第4スイッチング素子）Qn4とを備えている。

## 【0009】

トランジスタQp1のソース電極（第1端）は電源端子に接続可能である。電源端子は、例えば5Vの電源電圧（第1電源）Vddが供給される端子である。トランジスタQp1はダイオード接続を構成しており、そのゲート電極（制御端）とドレイン電極（第2端）とが短絡されている。

## 【0010】

トランジスタQn2のドレイン電極（第2端）は、トランジスタQp1のドレイン電極（第2端）に接続される。トランジスタQn2のゲート電極（制御端）には、後述するバイアス電圧Vbが供給される。

## 【0011】

トランジスタQn3のドレイン電極（第2端）は、トランジスタQn2のソース電極（第1端）と接続される。また、トランジスタQn3のゲート電極（制御端）とソース電極（第1端）とが短絡され、出力端子V0に基準電圧Vrefを出力する。基準電圧Vrefは、例えば4.5Vである。

## 【0012】

抵抗素子R1は本実施形態の特徴の1つであるバイアス電圧生成部1の例である。抵抗素子R1は、トランジスタQn3のゲート電極（すなわち出力端子V0）に接続される第1端子と、トランジスタQn2のゲート電極に接続される第2端子とを有する。抵抗素子R1は下記（1）式に示すバイアス電圧Vbを第2端子から出力する。

$$Vb = Vref - r * I0 \quad \dots \quad (1)$$

10

20

30

40

50

## 【0013】

ここで、 $r$  は抵抗素子  $R_1$  の抵抗値であり、 $I_0$  は抵抗素子  $R_1$  に流れる電流値である。すなわち、バイアス電圧生成部 1 としての抵抗素子  $R_1$  は、基準電圧  $V_{ref}$  に基づいて、基準電圧  $V_{ref}$  より低いバイアス電圧  $V_b$  を生成する。このバイアス電圧  $V_b$  はトランジスタ  $Q_{n2}$  のゲート電極に供給される。

## 【0014】

従って、抵抗素子  $R_1$  を設けてバイアス電圧  $V_b$  を生成することで、外部からバイアス電圧  $V_b$  を供給する必要がなくなる。また、抵抗値  $r$  を調整することで、抵抗素子  $R_1$  は基準電圧  $V_{ref}$  より低い任意のバイアス電圧  $V_b$  を生成できる。さらに、後述するように、抵抗素子  $R_1$  を設けることで、基準電圧  $V_{ref}$  の温度依存性を抑えることができる。

10

## 【0015】

トランジスタ  $Q_{n4}$  のドレイン電極（第 2 端）は、抵抗素子  $R_1$  の第 2 端子に接続され、バイアス電圧  $V_b$  が供給される。トランジスタ  $Q_{n4}$  のゲート電極（制御端）は、トランジスタ  $Q_{n3}$  のゲート電極（すなわち出力端子  $V_o$ ）に接続される。トランジスタ  $Q_{n4}$  のソース電極（第 1 端）は、接地端子（第 2 基準電圧端子）に接続可能である。接地端子は接地電圧（第 2 電圧）が供給される端子である。そして、トランジスタ  $Q_{n4}$  はトランジスタ  $Q_{n3}$  の温度特性をキャンセルするような温度特性を持っている。

## 【0016】

図 1 の基準電圧生成回路 100 は以下のように動作する。トランジスタ  $Q_{n3}$  のゲート電極は、ソース電極と短絡されている。すなわち、トランジスタ  $Q_{n3}$  のゲート - ソース間電圧  $V_{gs3} = 0$  である。ここでトランジスタ  $Q_{n3}$  はデプレッショント（ノーマリオン）型であるため、トランジスタ  $Q_{n3}$  はオンし、ドレイン領域からソース領域に向かって電流  $I_0$  が流れる。

20

## 【0017】

この電流  $I_0$  は抵抗素子  $R_1$  を介してトランジスタ  $Q_{n4}$  に流れ込む。これにより、トランジスタ  $Q_{n4}$  のゲート電極には、電流  $I_0$  を流すための電圧  $V_{g4}$  が発生する。この電圧  $V_{g4}$  が基準電圧  $V_{ref}$  となる。

## 【0018】

そして、抵抗素子  $R_1$  は、上記（1）式に示すバイアス電圧  $V_b$  を、トランジスタ  $Q_{n2}$  のゲート電極に供給する。トランジスタ  $Q_{n2}$  では、ソース電圧よりゲート電圧の方が低くなる。しかしながら、トランジスタ  $Q_{n2}$  もデプレッショント型であるため、その場合でもトランジスタ  $Q_{n2}$  がオンする。結果として、電源端子からトランジスタ  $Q_{p1}$ ,  $Q_{n2}$  を介してトランジスタ  $Q_{n3}$  に安定して一定の電流  $I_0$  が供給される。

30

## 【0019】

このようにして、基準電圧生成回路 100 は基準電圧  $V_{ref}$  を生成できる。

## 【0020】

ここで、トランジスタ  $Q_{p1}$ ,  $Q_{n2}$  を設けることで、電源電圧  $V_{dd}$  の変動が基準電圧  $V_{ref}$  に与える影響を抑制できる。以下、このことを説明する。

## 【0021】

ダイオード接続されたトランジスタ  $Q_{p1}$  は抵抗とみなせるため、トランジスタ  $Q_{n2}$  のドレイン電極に供給される電圧は、電源電圧  $V_{dd}$  より低くなる。よって、トランジスタ  $Q_{p1}$  を設けない場合に比べて、電源電圧  $V_{dd}$  が変動した場合のトランジスタ  $Q_{n2}$  のドレイン電圧の変動を相対的に小さくできる。

40

## 【0022】

さらに、トランジスタ  $Q_{n2}$  はソースフォロアを形成している。トランジスタ  $Q_{n2}$  のソース電極のインピーダンスは低いため、トランジスタ  $Q_{n2}$  のドレイン電圧が多少変動したとしても、トランジスタ  $Q_{n2}$  のソース電圧はほとんど変動しない。よって、トランジスタ  $Q_{n2}$  のソース電極と接続されるトランジスタ  $Q_{n3}$  のドレイン電圧もほとんど変動しない。

50

## 【0023】

すなわち、電源電圧  $V_{dd}$  が変動したとしても、トランジスタ  $Q_{n3}$  のドレイン電圧の変動は小さく、トランジスタ  $Q_{n3}$  に流れる電流  $I_0$  の変動を抑えることができる。

## 【0024】

ここで、トランジスタ  $Q_{p1}$  のみを設け、トランジスタ  $Q_{n2}$  を設けない場合、基準電圧  $V_{ref}$  の温度依存性が大きくなる可能性がある。すなわち、温度が上昇すると、トランジスタ  $Q_{p1}$  のゲート-ソース間電圧が小さくなり、トランジスタ  $Q_{p1}$  に流れる電流が小さくなる。そのため、トランジスタ  $Q_{p1}$  のドレイン電圧が高くなり、このドレイン電圧が直接トランジスタ  $Q_{n3}$  のドレイン電極に供給される。そうすると、トランジスタ  $Q_{n3}$  に流れる電流  $I_0$  が大きくなり、基準電圧  $V_{ref}$  が高くなってしまう。

10

## 【0025】

これに対し、ソースフォロアを形成するトランジスタ  $Q_{n2}$  を設けることで、上述のように、トランジスタ  $Q_{n2}$  のソース電圧はほとんど変動しない。よって、トランジスタ  $Q_{n3}$  のドレイン電圧もほとんど変動せず、トランジスタ  $Q_{n3}$  に流れる電流  $I_0$  の変動を抑えることができる。

## 【0026】

また、トランジスタ  $Q_{n3}$ ,  $Q_{n4}$  を設けることで、温度に依存して基準電圧  $V_{ref}$  が変動するのを抑制できる。以下、このことを説明する。

## 【0027】

図2は、トランジスタ  $Q_{n3}$ ,  $Q_{n4}$  の温度特性を模式的に示す図である。より具体的には、図2は、温度  $T$ 、トランジスタ  $Q_{n3}$  が流す電流  $I$ 、および、トランジスタ  $Q_{n4}$  のゲート電圧  $V_{g4}$  の関係を模式的に示している。同図の右半分に示すように、温度  $T$  が高くなるほど、トランジスタ  $Q_{n3}$  が流す電流  $I$  は大きくなる。一方、同図の左半分に示すように、温度  $T$  が高くなるほど、ある電流  $I_0$  を流すためのトランジスタ  $Q_{n4}$  のゲート電圧  $V_{g4}$  は低くなる。

20

## 【0028】

図2において、温度  $T_0$  の場合、トランジスタ  $Q_{n3}$  には電流  $I_0$  が流れ、かつ、電圧  $V_{g4} = V_{g40}$  である。温度が  $T_0$  から  $T_1$  に上昇すると、トランジスタ  $Q_{n3}$  はより大きな電流 ( $I_0 + dI$ ) を流そうとする。仮にトランジスタ  $Q_{n4}$  に温度依存性がないとすると、電流 ( $I_0 + dI$ ) を流すための電圧  $V_{g4}$  は、 $V_{g40}$  より高い  $V_{g4'}$  になってしまう。

30

## 【0029】

しかしながら、本実施形態では、トランジスタ  $Q_{n4}$  が図2のような温度特性を持っており、温度  $T$  が高くなった分、電圧  $V_{g4}$  が低くても大きな電流を流せる。結果として、電流 ( $I_0 + dI$ ) を流すための電圧  $V_{g4}$  を、やはり  $V_{g40}$  とすることができます。このように、トランジスタ  $Q_{n3}$  の温度特性をキャンセルするような温度特性をトランジスタ  $Q_{n4}$  に持たせることで、電圧  $V_{g4}$  すなわち基準電圧  $V_{ref}$  の変動を抑制できる。

## 【0030】

このような温度特性を持たせるには、トランジスタ  $Q_{n3}$ ,  $Q_{n4}$  のサイズ等を適切に調整すればよい。一例として、トランジスタ  $Q_{n3}$  については、そのゲート幅とゲート長との比を  $1:3$  とし、トランジスタ  $Q_{n4}$  については、そのゲート幅とゲート長との比を  $1:5$  とすればよい。

40

## 【0031】

ただし、そのような調整を行ったとしても、温度特性を完全にはキャンセルできない場合があり得る。その場合でも、抵抗素子  $R_1$  を設けることで、温度に依存して基準電圧  $V_{ref}$  が変動することを抑制できる。以下、このことを詳しく説明する。

## 【0032】

温度が  $T_0$  から  $T_1$  に上昇したことに起因する、トランジスタ  $Q_{n3}$  に流れる電流増加をトランジスタ  $Q_{n4}$  が完全にはキャンセルできなかった場合、基準電圧  $V_{ref}$  は高くなる。

50

## 【0033】

仮に抵抗素子R1を設けず、基準電圧Vrefをバイアス電圧としてトランジスタQn2のゲート電極に供給する場合、高くなつた基準電圧VrefがトランジスタQn2のゲート電極に供給されることになる。結果として、トランジスタQn2, Qn3に流れる電流も大きくなる。このように、抵抗素子R1を設けない場合、トランジスタQn3に流れる電流の増加を抑えることが困難であり、基準電圧Vrefが変動してしまう。

## 【0034】

これに対し、本実施形態では、抵抗素子R1を設ける。よって、トランジスタQn3に流れる電流が増加すると、抵抗素子R1での電圧降下により、トランジスタQn2のゲート電極に供給されるバイアス電圧Vbを低くすることができる。これに伴つて、トランジスタQn2のソース電圧も低くなる。このように、トランジスタQn3のドレイン電圧(すなわちトランジスタQn2のソース電圧)が低くなるため、トランジスタQn3のソース-ドレイン間電圧が小さくなる。結果として、トランジスタQn3に流れる電流の増加を抑えることができ、ひいては、基準電圧Vrefの変動を抑えることができる。

10

## 【0035】

なお、温度上昇に伴つてトランジスタQn2のソース電圧が高くなることも考えられる。この場合、抵抗素子R1を設けることによってバイアス電圧Vbを下げる効果が小さくなつてしまふ。よって、トランジスタQn2は、温度が上昇したとしてもソース電圧ができるだけ高くならないよう、そのサイズが調整される。より具体的には、温度上昇によるトランジスタQn2のソース電圧上昇より、抵抗素子R1による電圧降下が大きくなるよう、トランジスタQn2のサイズが調整される。

20

## 【0036】

基準電圧Vrefの温度依存性を抑えるという観点からは、抵抗素子R1の抵抗値rができるだけ大きいのが望ましい。その理由は、抵抗値rが大きいほど、バイアス電圧Vbの変動分dVbを小さくできるためである。一方で、抵抗値rを大きくしすぎるとバイアス電圧Vbが小さくなりすぎ、トランジスタQn2, Qn4がオンしなくなる。そうするとトランジスタQn3に電流が流れなくなり、適切な基準電圧Vrefが生成されない。

## 【0037】

よつて、抵抗素子R1の抵抗値rは、バイアス電圧VbによりトランジスタQn2がオンする範囲で、できるだけ大きな値とするのが望ましい。

30

## 【0038】

以上説明したように、本実施形態では、基準電圧生成回路100が抵抗素子R1を備える。そして、抵抗素子R1により、基準電圧Vrefより小さいバイアス電圧Vbが生成される。そのため、温度依存性が小さい基準電圧Vrefを生成できる。

## 【0039】

以下、いくつかの変形例を説明する。

## 【0040】

図3は、図1の基準電圧生成回路100の第1変形例である基準電圧生成回路101の回路図である。図1との相違点として、基準電圧生成回路101は、バイアス電圧生成部1を構成するエンハンスマント型のn型MOSトランジスタ(第5スイッチング素子)Qn5を備えている。トランジスタQn5のドレイン電極(第2端)およびゲート電極(制御端)は、トランジスタQn3のゲート電極(すなわち出力端子V0)に接続される。また、トランジスタQn5のソース電極(第1端)は、トランジスタQn4のドレイン電極に接続される。さらに、トランジスタQn5は、温度が上昇したとしてもソース電圧ができるだけ高くならないよう、そのサイズが調整される。

40

## 【0041】

トランジスタQn5は、図1における抵抗素子R1と同様に機能するため、基準電圧生成回路101の動作原理は基準電圧生成回路100とほぼ同様である。すなわち、トランジスタQn5はバイアス電圧Vbを生成する。この場合のバイアス電圧VbはトランジスタQn5のサイズおよび閾値電圧に依存する。よつて、トランジスタQn5のサイズおよ

50

び閾値電圧を調整することで、基準電圧  $V_{ref}$  より低い任意のバイアス電圧  $V_b$  を生成できる。

【0042】

また、温度が上昇した場合であっても、上述のように、トランジスタ  $Q_{n5}$  のソース電圧はそれほど上昇することではなく、むしろトランジスタ  $Q_{n3}$  から流れる電流の増加に伴って、バイアス電圧  $V_b$  は低くなる。よって、図1の基準電圧生成回路100と同様に、基準電圧  $V_{ref}$  の温度依存性を抑えることができる。

【0043】

抵抗素子に代えてトランジスタ  $Q_{n5}$  を用いることで、図1の基準電圧生成回路100に比べて、基準電圧生成回路101の回路規模を小さくできる。

10

【0044】

図4は、図1の基準電圧生成回路100の第2変形例である基準電圧生成回路102の回路図である。図1および図3との相違点として、基準電圧生成回路102は、バイアス電圧生成部1を構成するエンハンスマント型のn型MOSトランジスタ(第6スイッチング素子)  $Q_{n6}$  および抵抗素子  $R_2$  を備えている。トランジスタ  $Q_{n6}$  および抵抗素子  $R_2$  は、トランジスタ  $Q_{n3}$  とトランジスタ  $Q_{n4}$  との間に縦続接続される。

【0045】

より具体的には、トランジスタ  $Q_{n6}$  のドレイン電極(第2端)およびゲート電極(制御端)は、トランジスタ  $Q_{n3}$  のゲート電極(すなわち出力端子  $V_o$ )に接続される。抵抗素子  $R_2$  は、トランジスタ  $Q_{n6}$  のソース電極(第1端)に接続される第1端子と、トランジスタ  $Q_{n4}$  のドレイン電極に接続される第2端子とを有する。図4の基準電圧生成回路102は図1と図3とを組み合わせたものであるため、基準電圧生成回路102の動作原理は基準電圧生成回路100, 101とほぼ同様である。

20

【0046】

基準電圧生成回路102では、トランジスタ  $Q_{n6}$  のサイズおよび閾値電圧により、バイアス電圧  $V_b$  を粗調整してもよい。そして、抵抗素子  $R_2$  により、バイアス電圧  $V_b$  を微調整してもよい。トランジスタ  $Q_{n6}$  を用いることで回路規模を抑えることができ、かつ、抵抗素子  $R_2$  を用いることでバイアス電圧  $V_b$  を精度よく所望の値に設定できる。

【0047】

以上説明したように、基準電圧生成回路内にバイアス電圧生成部を設け、基準電圧より低いバイアス電圧を生成する。よって、温度依存性が小さい基準電圧を生成できる。

30

【0048】

なお、図1、図3および図4の基準電圧生成回路は一例に過ぎず、種々の変形が可能である。例えば、トランジスタの導電型を逆にし、それに応じて電源端子と接地端子の接続位置を逆にした基準電圧生成回路を構成してもよい。この場合も基本的な動作原理は同じである。

【0049】

また、各実施形態では、ノーマリオン型、すなわち、制御端と第1端とが同電位の場合に電流が流れるタイプのスイッチング素子として、デプレッション型のMOSトランジスタを用いる例を示した。しかしながら、デプレッション型のMOSトランジスタに代えて、ノーマリオン型のGaN HEMT (High Electron Mobility Transistor) など他の素子をノーマリオン型のスイッチング素子として用いてもよい。

40

【0050】

同様に、各実施形態では、ノーマリオフ型、すなわち、制御端と第1端とが同電位の場合に電流が流れないタイプのスイッチング素子として、エンハンスマント型のMOSトランジスタ用いる例を示した。しかしながら、エンハンスマント型のMOSトランジスタに代えて、ノーマリオフ型のGaN HEMTなど他の素子をノーマリオン型のスイッチング素子として用いてもよい。

【0051】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したも

50

のであり、発明の範囲を限定することは意図していない。これら実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれると同様に、特許請求の範囲に記載された発明とその均等の範囲に含まれるものである。

## 【符号の説明】

## 【0052】

1 バイアス電圧生成部

100 ~ 102 基準電圧生成回路

Qp1 p型MOSトランジスタ

10

Qn2, Qn3 デプレッシャン型n型MOSトランジスタ

Qn4, Qn5, Qn6 エンハンスメント型n型MOSトランジスタ

R1, R2 抵抗素子

【図1】

【図3】

【図2】

【図4】

102

---

フロントページの続き

(72)発明者 三好 秀暁

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 田中 明広

東京都港区芝浦一丁目1番1号 株式会社東芝内

審査官 栗栖 正和

(56)参考文献 特開2011-113321(JP, A)

特開2010-176258(JP, A)

特開2008-070953(JP, A)

特開平11-265227(JP, A)

米国特許出願公開第2010/0207686(US, A1)

(58)調査した分野(Int.Cl., DB名)

G 05 F 3 / 24