(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-71284

(P2009-71284A)

(43) 公開日 平成21年4月2日(2009.4.2)

| (51) Int.Cl.           | F 1        | テーマコード (参考) |

|------------------------|------------|-------------|

| HO1L 29/786 (2006.01)  | HO1L 29/78 | 618E 3K107  |

| HO1L 21/336 (2006.01)  | HO1L 29/78 | 618Z 5FO38  |

| HO1L 21/8234 (2006.01) | HO1L 29/78 | 623A 5FO48  |

| HO1L 27/06 (2006.01)   | HO1L 29/78 | 613A 5F110  |

| HO1L 21/8238 (2006.01) | HO1L 27/06 | 102A        |

審査請求 未請求 請求項の数 7 O L (全 41 頁) 最終頁に続く

|              |                              |          |                                                |

|--------------|------------------------------|----------|------------------------------------------------|

| (21) 出願番号    | 特願2008-202552 (P2008-202552) | (71) 出願人 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (22) 出願日     | 平成20年8月6日 (2008.8.6)         | (72) 発明者 | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (31) 優先権主張番号 | 特願2007-213055 (P2007-213055) | (72) 発明者 | 荒井 康行<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (32) 優先日     | 平成19年8月17日 (2007.8.17)       | (72) 発明者 | 鈴木 幸恵<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (33) 優先権主張国  | 日本国 (JP)                     | (72) 発明者 | 黒川 義元<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

最終頁に続く

## (54) 【発明の名称】表示装置

## (57) 【要約】

【課題】電気特性が優れ、信頼性の高いpチャネル型薄膜トランジスタ及びnチャネル型薄膜トランジスタを有する表示装置、及びそれを生産性よく作製する方法を提案する。

【解決手段】逆スタガ型のpチャネル型薄膜トランジスタと、nチャネル型薄膜トランジスタとを有し、前記pチャネル型薄膜トランジスタ及びnチャネル型薄膜トランジスタは、ゲート電極上にゲート絶縁膜、微結晶半導体膜、及び非晶質半導体膜が順に積層され、非晶質半導体膜上に形成された一対のn型半導体膜またはp型半導体膜と、一対のn型半導体膜またはp型半導体膜上に形成された一対の配線とを有し、微結晶半導体膜は $1 \times 10^{16} \text{ atoms/cm}^2$ 以下、酸素を含む表示装置である。また、nチャネル型薄膜トランジスタの移動度は $10$ 以上 $45 \text{ cm}^2/\text{V}\cdot\text{s}$ 以下であり、pチャネル型薄膜トランジスタの移動度は $0.3 \text{ cm}^2/\text{V}\cdot\text{s}$ 以下である。

【選択図】図1

## 【特許請求の範囲】

## 【請求項 1】

第 1 のゲート電極と、

前記第 1 のゲート電極上に形成されるゲート絶縁膜と、

前記ゲート絶縁膜上に形成される第 1 の微結晶半導体膜と、

前記第 1 の微結晶半導体膜上に形成される第 1 のバッファ層と、

前記第 1 のバッファ層上に形成される一対の n 型半導体膜と、

前記一対の n 型半導体膜上に形成される一対の第 1 の配線とを有する n チャネル型薄膜トランジスタと、

第 2 のゲート電極と、

前記第 2 のゲート電極上に形成される前記ゲート絶縁膜と、

前記ゲート絶縁膜上に形成される第 2 の微結晶半導体膜と、

前記第 2 の微結晶半導体膜上に形成される第 2 のバッファ層と、

前記第 2 のバッファ層上に形成される一対の p 型半導体膜と、

前記一対の p 型半導体膜上に形成される一対の第 1 の配線とを有する p チャネル型薄膜トランジスタと、

を有し、

前記第 1 の微結晶半導体膜及び前記第 2 の微結晶半導体膜は、 $1 \times 10^{16}$  atoms/cm<sup>3</sup> 以下の酸素を含むことを特徴とする表示装置。

## 【請求項 2】

請求項 1において、前記 n チャネル型薄膜トランジスタの移動度は 10 以上 45 cm<sup>2</sup>/V・s であり、前記 p チャネル型薄膜トランジスタの移動度は 0.3 cm<sup>2</sup>/V・s 以下であることを特徴とする表示装置。

## 【請求項 3】

請求項 1 または 2 において、前記 n チャネル型薄膜トランジスタまたは p チャネル型薄膜トランジスタの一方に接続する画素電極を有する画素を有することを特徴とする表示装置。

## 【請求項 4】

請求項 1 または 2 において、前記 n チャネル型薄膜トランジスタ及び前記 p チャネル型薄膜トランジスタは保護回路を構成し、前記 n チャネル型薄膜トランジスタ及び前記 p チャネル型薄膜トランジスタはそれぞれダイオード接続されることを特徴とする表示装置。

## 【請求項 5】

請求項 1 乃至 4 のいずれか一項において、前記表示装置は液晶表示装置であることを特徴とする表示装置。

## 【請求項 6】

請求項 1 乃至 4 のいずれか一項において、前記一対の第 1 の配線の一方と、前記第 2 のゲート電極とが接続することを特徴とする表示装置。

## 【請求項 7】

請求項 6 において、前記表示装置は発光表示装置であることを特徴とする表示装置。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、n チャネル型薄膜トランジスタ及び p チャネル型薄膜トランジスタを用いた表示装置に関する。

## 【背景技術】

## 【0002】

近年、絶縁表面を有する基板上に形成された半導体薄膜（厚さ数十～数百 nm 程度）を用いて薄膜トランジスタを構成する技術が注目されている。薄膜トランジスタは IC や電気光学装置のような電子デバイスに広く応用され、特に画像表示装置のスイッチング素子として開発が急がれている。

10

20

30

40

50

## 【0003】

画像表示装置のスイッチング素子として、非晶質シリコン膜をチャネル形成領域に用いた薄膜トランジスタ、または多結晶シリコン膜をチャネル形成領域に用いた薄膜トランジスタ等が用いられている。多結晶シリコン膜の形成方法としては、パルス発振のエキシマレーザビームを光学系により線状に加工して、非晶質シリコン膜に対し線状ビームを走査させながら照射して結晶化する技術が知られている。

## 【0004】

また、画像表示装置のスイッチング素子として、微結晶シリコン膜をチャネル形成領域に用いた薄膜トランジスタが用いられている（特許文献1 非特許文献1）。

【特許文献1】特開平4-242724号公報

【非特許文献1】トシアキ・アライ（Toshiaki Arai）他、エス・アイ・ディー 07 ダイジェスト（SID 07 DIGEST）、2007、p. 1370-1373

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0005】

多結晶シリコン膜をチャネル形成領域に用いた薄膜トランジスタは、非晶質シリコン膜をチャネル形成領域に用いた薄膜トランジスタに比べて移動度が2桁以上高く、半導体表示装置の画素部とその周辺の駆動回路を同一基板上に一体形成できるという利点を有している。しかしながら、非晶質シリコン膜をチャネル形成領域に用いた場合に比べて、半導体膜の結晶化が必要なために工程が複雑化し、その分歩留まりが低減し、コストが高まるという問題がある。また、エキシマレーザビームを非晶質シリコン膜に照射して形成した多結晶シリコン膜は、レーザビームのエネルギーのばらつきにより結晶粒の大きさが不揃いな場合があり、このような多結晶シリコンを用いて薄膜トランジスタを形成すると電気特性がばらつくという問題がある。

## 【0006】

一方、非晶質シリコン膜をチャネル形成領域に用いた薄膜トランジスタは、少ないフォトマスク数で作製することが可能であるため工程が簡易であるが、閾値の変動が大きく、また移動度が低い。さらに、非晶質シリコン膜をチャネル形成領域に用いた薄膜トランジスタにおいて、pチャネル型の薄膜トランジスタを作製することが困難であった。

## 【0007】

また、微結晶シリコン膜をチャネル形成領域に用いた逆スタガ型の薄膜トランジスタにおいては、ゲート絶縁膜及び微結晶半導体膜の界面領域における結晶性が低く、薄膜トランジスタの電気的特性が悪い。さらに微結晶シリコン膜をチャネル形成領域に用いた逆スタガ型のpチャネル型薄膜トランジスタを作製することは困難である。

## 【0008】

上述した問題に鑑み、本発明は、電気特性が優れ、信頼性の高いpチャネル型薄膜トランジスタ及びnチャネル薄膜トランジスタを有する表示装置、及びそれを生産性よく作製する方法を提案する。

## 【課題を解決するための手段】

## 【0009】

本発明の一は、逆スタガ型のpチャネル型薄膜トランジスタと、nチャネル型薄膜トランジスタとを有し、前記pチャネル型薄膜トランジスタ及びnチャネル型薄膜トランジスタは、ゲート電極上にゲート絶縁膜、微結晶半導体膜、及び非晶質半導体膜が順に積層され、非晶質半導体膜上に形成された一対のn型半導体膜またはp型半導体膜と、一対のn型半導体膜またはp型半導体膜上に形成された一対の配線とを有し、微結晶半導体膜は $1 \times 10^{16} \text{ atoms/cm}^3$ 以下の酸素を含む表示装置である。また、nチャネル型薄膜トランジスタの移動度は $10 \text{ cm}^2/\text{V}\cdot\text{s}$ 以上 $45 \text{ cm}^2/\text{V}\cdot\text{s}$ 以下であり、pチャネル型薄膜トランジスタの移動度は $0.3 \text{ cm}^2/\text{V}\cdot\text{s}$ 以下である。

## 【0010】

10

20

30

40

50

また、上記逆スタガ型の p チャネル型薄膜トランジスタと、 n チャネル型薄膜トランジスタを作製する工程において、真空度が  $10^{-5}$  Pa よりも低い圧力に超高真空排気されたチャンバー内に基板を設け、基板温度  $100 \sim 300$  、好ましくは  $120 \sim 280$  、好ましくは  $120 \sim 220$  としたプラズマ CVD 法により、  $1 \times 10^{-6}$  atoms / cm<sup>3</sup> 以下の酸素を含む微結晶半導体膜を形成することができる。

## 【 0011 】

酸素は微結晶半導体膜の形成を阻害する。しかしながら、成膜チャンバー内を超高真空排気することでチャンバー内の酸素濃度を低減できるため、微結晶半導体膜の形成を促進させることができる。また、微結晶半導体膜中において、酸素は欠陥となると共に、ドナーとして作用する。このため、特に、 p チャネル型薄膜トランジスタにおいては、ドナーとして働く酸素の濃度を低減することが可能であるため、 p チャネル型薄膜トランジスタの移動度を上昇させることができると 10 。

## 【 0012 】

また、微結晶半導体膜の成膜温度を  $100 \sim 300$  、好ましくは  $120 \sim 280$  、好ましくは  $120 \sim 220$  とすることで、ゲート絶縁膜及び微結晶半導体膜の界面における格子歪を低減することが可能であり、ゲート絶縁膜及び微結晶半導体膜の界面特性を向上させることができる。このため、当該微結晶半導体膜を有する薄膜トランジスタの電気特性を向上させることができる。

## 【 0013 】

また、本発明の一は、逆スタガ型の p チャネル型薄膜トランジスタ及び n チャネル型薄膜トランジスタを表示素子のスイッチングとして機能させた画素を有する表示装置である。表示装置としては、液晶表示装置、発光表示装置等がある。液晶表示装置は液晶素子を含む。発光表示装置は発光素子を含み、発光素子は、電流または電圧によって輝度が制御される素子をその範疇に含んでおり、具体的には無機 EL ( Electro Luminescence ) 素子、有機 EL 素子等が含まれる。

## 【 0014 】

また、本発明の一は、逆スタガの p チャネル型薄膜トランジスタ、 n チャネル型薄膜トランジスタそれぞれがダイオード接続された保護回路を、画素部の周辺に有する表示装置である。保護回路を画素部及び駆動回路の間、または画素部を挟んで駆動回路の反対側に設けることで、静電気等による破壊や劣化を防止することができる。

## 【 0015 】

また、本発明の一は、微結晶半導体膜を用いて形成された n チャネル型薄膜トランジスタ及び p チャネル型薄膜トランジスタを画素部、さらには駆動回路に有する表示装置である。微結晶半導体膜をチャネル形成領域に用いた n チャネル型薄膜トランジスタ及び p チャネル型薄膜トランジスタを用いて駆動回路の一部または全体を、画素部と同じ基板上に一体形成し、システムオンパネルを形成することができる。

## 【 0016 】

また、表示装置は、表示素子が封止された状態にあるパネルと、該パネルにコントローラを含む IC 等を実装した状態にあるモジュールとを含む。さらに本発明は、該表示装置を作製する過程における、表示素子が完成する前の一形態に相当する素子基板に関し、該素子基板は、表示素子に電流または電圧を供給するための手段を複数の各画素に備える。素子基板は、具体的には、表示素子の画素電極のみが形成された状態であっても良いし、画素電極となる導電膜を成膜した後であって、エッティングして画素電極を形成する前の状態であっても良いし、あらゆる形態があてはまる。

## 【 0017 】

なお、本明細書中における表示装置とは、画像表示デバイス、発光デバイス、もしくは光源（照明装置含む）を指す。また、コネクター、例えば FPC ( Flexible printed circuit ) もしくは TAB ( Tape Automated Bonding ) テープもしくは TCP ( Tape Carrier Package ) が取り付けられたモジュール、 TAB テープや TCP の先にプリント配線板が設けられたモジュ

10

20

30

40

50

ール、または表示素子に C O G ( C h i p O n G l a s s ) 方式により I C ( 集積回路 ) が直接実装されたモジュールも全て表示装置に含むものとする。

【発明の効果】

【 0 0 1 8 】

本発明により、電気特性が優れ、信頼性の高い p チャネル型薄膜トランジスタ及び n チャネル型薄膜トランジスタを有する表示装置を生産性よく作製することができる。

【発明を実施するための最良の形態】

【 0 0 1 9 】

以下、本発明の実施の形態について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。なお、以下に示す図面において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

10

【 0 0 2 0 】

( 実施の形態 1 )

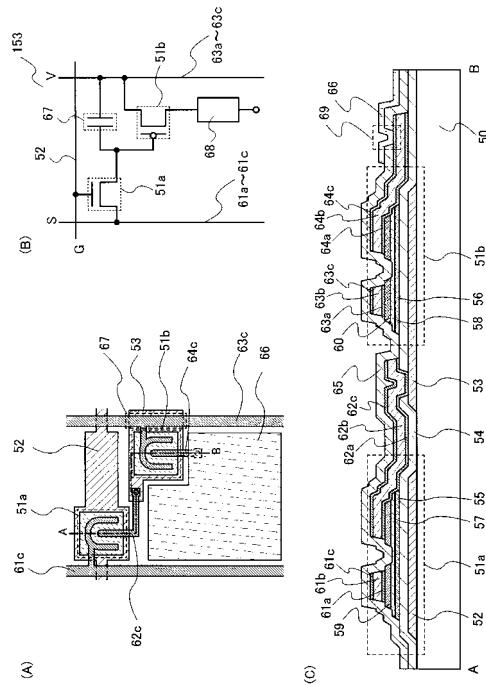

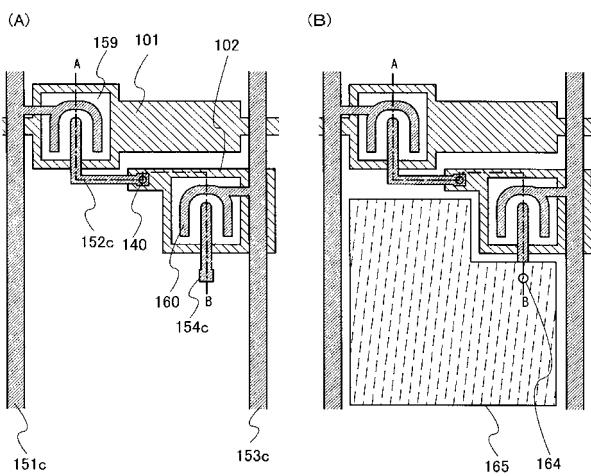

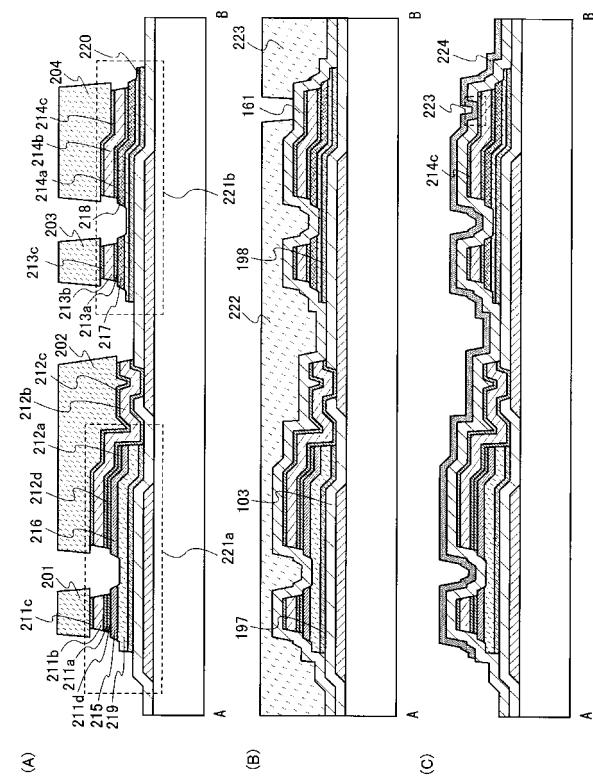

本実施の形態の表示装置が有する画素の構成について説明する。図 1 ( A ) に、画素の上面図の一形態を示し、図 1 ( B ) に画素の等価回路図の一形態を示し、図 1 ( C ) に図 1 ( A ) の A - B に対応する画素の断面構造の一形態を示す。

20

【 0 0 2 1 】

図 1 ( A ) ~ 図 1 ( C ) において、第 1 の薄膜トランジスタ 5 1 a 及び第 2 の薄膜トランジスタ 5 1 b は画素電極への信号の入力を制御するためのスイッチング用の薄膜トランジスタまたは発光素子 6 8 への電流または電圧の供給を制御するための駆動用の薄膜トランジスタに相当する。

30

【 0 0 2 2 】

第 1 の薄膜トランジスタ 5 1 a のゲート電極は走査線 5 2 に、ソースまたはドレインの一方は信号線として機能する配線 6 1 a ~ 6 1 c に接続され、ソースまたはドレインの他方は第 2 の薄膜トランジスタ 5 1 b のゲート電極 5 3 に接続する。第 2 の薄膜トランジスタ 5 1 b のソースまたはドレインの一方は電源線として機能する配線 6 3 a ~ 6 3 c に接続され、ソースまたはドレインの他方は表示装置の画素電極 6 6 に接続される。また、図 1 ( B ) に示すように、第 1 の薄膜トランジスタ 5 1 a のソースまたはドレインの他方及び第 2 の薄膜トランジスタ 5 1 b のゲートは容量素子 6 7 に接続され、容量素子 6 7 は電源線として機能する配線 6 3 a ~ 6 3 c に接続される。

30

【 0 0 2 3 】

なお、容量素子 6 7 は、第 1 の薄膜トランジスタ 5 1 a がオフのときに第 2 の薄膜トランジスタ 5 1 b のゲート / ソース間電圧またはゲート / ドレイン間電圧 ( 以下、ゲート電圧とする ) を保持するための容量素子に相当し、必ずしも設ける必要はない。

40

【 0 0 2 4 】

本実施の形態では、第 1 の薄膜トランジスタ 5 1 a を n チャネル型薄膜トランジスタで形成し、第 2 の薄膜トランジスタ 5 1 b を p チャネル型薄膜トランジスタで形成する。なお、第 1 の薄膜トランジスタ 5 1 a を p チャネル型の薄膜トランジスタで形成し、第 2 の薄膜トランジスタ 5 1 b を n チャネル型薄膜トランジスタで形成してもよい。

【 0 0 2 5 】

次に、第 1 の薄膜トランジスタ 5 1 a 及び第 2 の薄膜トランジスタ 5 1 b の構造について、図 1 ( C ) を用いて説明する。

【 0 0 2 6 】

第 1 の薄膜トランジスタ 5 1 a は、基板 5 0 上にゲート電極 5 2 、ゲート電極上にゲート絶縁膜 5 4 、ゲート絶縁膜上に微結晶半導体膜 5 5 、微結晶半導体膜 5 5 上にバッファ層 5 7 、バッファ層 5 7 上に一対の n 型半導体膜 5 9 、一対の n 型半導体膜 5 9 上に配線 6 1 a ~ 6 1 c 、 6 2 a ~ 6 2 c が形成される。また、第 1 の薄膜トランジスタ 5 1 a は、

50

移動度が 10 以上  $45 \text{ cm}^2 / \text{V} \cdot \text{s}$  以下である。

【0027】

第2の薄膜トランジスタ 51b は、基板 50 上にゲート電極 53、ゲート電極 53 上にゲート絶縁膜 54、ゲート絶縁膜 54 上に微結晶半導体膜 56、微結晶半導体膜 56 上にバッファ層 58、バッファ層 58 上に一对の p 型半導体膜 60、一对の p 型半導体膜 60 上に配線 63a ~ 63c、64a ~ 64c が形成される。また、第1の薄膜トランジスタ 51a の配線 62a 及び第2の薄膜トランジスタ 51b のゲート電極 53 がゲート絶縁膜 54 のコンタクトホールにおいて接続される。また、第2の薄膜トランジスタ 51b の移動度は  $0.3 \text{ cm}^2 / \text{V} \cdot \text{s}$  以下である。

【0028】

本実施の形態では、微結晶半導体膜 55、56 はそれぞれ第1の薄膜トランジスタ 51a 及び第2の薄膜トランジスタ 51b のチャネル形成領域として機能し、且つ微結晶半導体膜 55、56 に含まれる酸素の濃度が  $1 \times 10^{16} \text{ atoms/cm}^3$  以下であることを特徴とする。微結晶半導体膜中において、酸素は欠陥となる。このため、微結晶半導体膜 55、56 の酸素濃度を低減することで、膜中の欠陥を低減することが可能となるため、キャリアの移動を向上させることが可能である。また、チャネル形成領域として微結晶半導体膜を用いるため、閾値の変動を抑えることが可能である。このため、第1の薄膜トランジスタ 51a、及び第2の薄膜トランジスタ 51b の電気特性を向上させることができる。さらに、p チャネル型薄膜トランジスタにおいては、ドナーとして働く酸素の濃度を低減することで、p チャネル型薄膜トランジスタの移動度を上昇させることができ。このため、微結晶半導体膜をチャネル形成領域に用いた逆スタガ型の薄膜トランジスタにおいても、p チャネル型の薄膜トランジスタを作製することができる。

【0029】

また、微結晶半導体膜 55 及び n 型半導体膜 59 の間、並びに微結晶半導体膜 56 及び p 型半導体膜 60 の間に、バッファ層 57、58 を有することを特徴とする。バッファ層 57、58 は、微結晶半導体膜 55、56 の酸化保護膜として機能するとともに、高抵抗領域として機能する。このため、微結晶半導体膜 55、56 に酸化物が形成され、移動度が低下するのを回避すると共に、薄膜トランジスタのオフ電流を低減することができる。このため、表示装置のコントラストを向上させることができる。

【0030】

なお、本実施の形態において、画素の等価回路は図 1 (B) に限定されるものではなく、逆スタガ型の p チャネル型薄膜トランジスタ、逆スタガ型の n チャネル型薄膜トランジスタ、及び画素電極を有し、画素電極が逆スタガ型の p チャネル型薄膜トランジスタまたは逆スタガ型の n チャネル型薄膜トランジスタに接続する等価回路を構成する画素であればよい。

【0031】

基板 50 は、バリウムホウケイ酸ガラス、アルミノホウケイ酸ガラス、若しくはアルミニシリケートガラスなど、フュージョン法やフロート法で作製される無アルカリガラス基板、セラミック基板の他、本作製工程の処理温度に耐えうる耐熱性を有するプラスチック基板等を用いることができる。また、ステンレス合金などの金属基板の表面に絶縁膜を設けた基板を適用しても良い。基板 50 がマザーガラスの場合、基板の大きさは、第1世代 ( $320 \text{ mm} \times 400 \text{ mm}$ )、第2世代 ( $400 \text{ mm} \times 500 \text{ mm}$ )、第3世代 ( $550 \text{ mm} \times 650 \text{ mm}$ )、第4世代 ( $680 \text{ mm} \times 880 \text{ mm}$ 、または  $730 \text{ mm} \times 920 \text{ mm}$ )、第5世代 ( $1000 \text{ mm} \times 1200 \text{ mm}$  または  $1100 \text{ mm} \times 1250 \text{ mm}$ )、第6世代  $1500 \text{ mm} \times 1800 \text{ mm}$ )、第7世代 ( $1900 \text{ mm} \times 2200 \text{ mm}$ )、第8世代 ( $2160 \text{ mm} \times 2460 \text{ mm}$ )、第9世代 ( $2400 \text{ mm} \times 2800 \text{ mm}$ 、 $2450 \text{ mm} \times 3050 \text{ mm}$ )、第10世代 ( $2950 \text{ mm} \times 3400 \text{ mm}$ ) 等を用いることができる。

【0032】

ゲート電極 52、53、及び容量電極 (図示しない。) は、金属材料で形成される。金属

10

20

30

40

50

材料としてはアルミニウム、クロム、チタン、タンタル、モリブデン、銅などが適用される。ゲート電極52、53及び容量電極の好適例は、アルミニウム又はアルミニウムとバリア金属の積層構造体によって形成される。バリア金属としては、チタン、モリブデン、クロムなどの高融点金属が適用される。バリア金属はアルミニウムのヒロック防止、酸化防止のために設けることが好ましい。ゲート電極52、53上には半導体膜や配線を形成するので、段切れ防止のため端部がテーパー状になるように加工することが望ましい。

#### 【0033】

ゲート電極52、53は、スパッタリング法、CVD法、蒸着法、印刷法、液滴吐出法等を用いて形成する。なお、スパッタリング法、CVD法等で形成する場合は、基板50全面に金属材料膜を形成した後、フォトリソグラフィ工程により形成されたレジストマスクを用いて金属材料膜を部分的にエッチングして、ゲート電極52、53、及び容量電極を形成する。

10

#### 【0034】

ゲート絶縁膜54は、厚さ50nm～300nmの窒化シリコン、酸化シリコン、窒化酸化シリコン、酸化窒化シリコン、窒化アルミニウム、窒化酸化アルミニウムなどの絶縁材料で形成する。

#### 【0035】

ゲート絶縁膜54の一例は、ゲート電極52、53、及び容量電極上に第1ゲート絶縁膜として窒化シリコン膜（又は窒化酸化シリコン膜）を設け、その上に第2ゲート絶縁膜として酸化シリコン膜（又は酸化窒化シリコン膜）を設ける構成がある。このようにゲート絶縁膜54を複数の層で形成することで、複数の機能をゲート絶縁膜54に付与することができる。例えば、第1ゲート絶縁膜として窒化シリコン膜（又は窒化酸化シリコン膜）を設けることで素子基板からの不純物拡散を防止し、他の効果としてゲート電極52、53などの酸化防止を図ることができる。また、ゲート電極52、53としてアルミニウムを使用する場合には、アルミニウムのヒロックを防止することができる。第2ゲート絶縁膜として酸化シリコン膜（又は酸化窒化シリコン膜）を設けることで、その上に形成される微結晶シリコン膜との密着性を高め、第1ゲート絶縁膜の応力歪みの影響を緩和する効果がある。第1ゲート絶縁膜は10nm～100nm、第2ゲート絶縁膜は50nm～150nmの厚さで形成することが好ましい。さらには、酸化シリコン膜上に5nm～10nmの窒化シリコン膜を形成しても良い。特に表示装置が発光表示装置の場合、直流駆動のため、ゲート絶縁膜は高耐圧であることが好ましい。このため、ゲート絶縁膜を上記の3層構造とすることが好ましい。また、ゲート絶縁膜に酸化窒化シリコンまたは酸化シリコンを用いることで、閾値の変動を抑制することができる。

20

#### 【0036】

ゲート絶縁膜54は、スパッタリング法、CVD法、塗布法等を用いて形成する。

30

#### 【0037】

微結晶半導体膜55、56は、非晶質と結晶構造（単結晶、多結晶を含む）の中間的な構造の半導体を含む膜である。この半導体は、自由エネルギー的に安定な（すなわち、熱力学的に安定な）第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する結晶質なものであり、粒径が0.5～50nm、好ましくは1nm～20nmの柱状または針状結晶が基板表面に対して法線方向に成長している。また、微結晶半導体と非単結晶半導体とが混在している。微結晶半導体の代表例である微結晶シリコンは、そのラマンスペクトルが単結晶シリコンを示す $520.5\text{ cm}^{-1}$ よりも低波数側に、シフトしている。即ち、単結晶シリコンを示す $520.5\text{ cm}^{-1}$ とアモルファスシリコンを示す $480\text{ cm}^{-1}$ の間に微結晶シリコンのラマンスペクトルのピークがある。また、未結合手（ダンギリングボンド）を終端するため水素またはハロゲンを少なくとも1原子%またはそれ以上含ませている。さらに、ヘリウム、アルゴン、クリプトン、ネオンなどの希ガス元素を含ませて格子歪みをさらに助長させることで、安定性が増し良好な微結晶半導体膜が得られる。このような微結晶半導体膜に関する記述は、例えば、米国特許4,409,134号で開示されている。

40

50

## 【0038】

微結晶半導体膜55、56の厚さは10nm～500nm(好ましくは100nm～250nm)の厚さとする。微結晶半導体膜55、56の厚さを10nm以上500nm以下とすることで、後に形成される薄膜トランジスタは、完全空乏型となる。また、微結晶半導体膜55、56として、微結晶シリコン膜や、ゲルマニウムまたは炭素が添加された微結晶シリコン膜を形成する。

## 【0039】

また、微結晶半導体膜は、価電子制御を目的とした不純物元素を意図的に添加しないときに弱いn型の電気伝導性を示すので、薄膜トランジスタのチャネル形成領域として機能する微結晶半導体膜に対しては、p型を付与する不純物元素を、成膜と同時に、或いは成膜後に添加して、しきい値制御をしてよい。p型を付与する不純物元素としては、代表的には硼素であり、B<sub>2</sub>H<sub>6</sub>、BF<sub>3</sub>などの不純物気体を1ppm～1000ppm、好ましくは1～100ppmの割合で水素化珪素に混入させると良い。そしてボロンの濃度を、例えば $1 \times 10^{14} \sim 6 \times 10^{16}$ atoms/cm<sup>3</sup>とすると良い。

10

## 【0040】

また、微結晶半導体膜の窒素及び炭素の濃度それぞれを $3 \times 10^{18}$ atoms/cm<sup>3</sup>以下とすることが好ましい。微結晶半導体膜の不純物の濃度を低減することで、微結晶半導体膜の欠陥を低減することができる。

20

## 【0041】

微結晶半導体膜55、56の成膜方法については、実施の形態2で詳細に説明する。

## 【0042】

バッファ層57、58は、厚さ50～400nmの非晶質半導体膜を用いて形成する。代表的には、非晶質シリコン膜を用いて形成する。または、窒素、フッ素、塩素、ヘリウム、アルゴン、クリプトン、若しくはネオン一種以上を含む非晶質シリコン膜を用いて形成する。

30

## 【0043】

バッファ層57、58は、SiH<sub>4</sub>、Si<sub>2</sub>H<sub>6</sub>などの水素化珪素を用いて、プラズマCVD法により形成することができる。また、上記水素化珪素に、ヘリウム、アルゴン、クリプトン、ネオンから選ばれた一種または複数種の希ガス元素で希釈して非晶質半導体膜を形成することができる。水素化珪素の流量の1倍以上10倍未満、更に好ましくは1倍以上5倍以下の流量の水素を用いて、水素を含む非晶質半導体膜を形成することができる。さらには、上記原料ガスに、窒素、アンモニア、フッ素、塩素、臭素、またはヨウ素を含む気体(F<sub>2</sub>、Cl<sub>2</sub>、HF、HCl等)の一一種類以上を添加して、バッファ層57、58を形成する。

30

## 【0044】

または、スパッタリング法によりバッファ層57、58を形成することができる。

## 【0045】

n型半導体膜59及びp型半導体膜60は、価電子制御を目的とした一導電型不純物が添加されている。n型半導体膜59にはリン又は砒素が添加され、p型半導体膜60には硼素が添加される。n型半導体膜59の代表例は、リンが添加された非晶質シリコン膜又は微結晶シリコン膜であり、p型半導体膜60の代表例はボロンが添加された非晶質シリコン膜又は微結晶シリコン膜である。

40

## 【0046】

配線61a～61c、63a～63cは、ゲート電極52と接続する走査線と交差する方向に延び、第1の薄膜トランジスタ51aのソース若しくはドレインの電位が付与される。配線62a～62cは、第2の薄膜トランジスタ51bのゲート電極53と接続し、第2の薄膜トランジスタ51bのゲート電極の電位が付与される。配線64a～64cは、画素電極と接続し、第2の薄膜トランジスタ51bのドレイン若しくはソースの電位が付与される。

40

## 【0047】

50

配線 6 1 a ~ 6 1 c、6 2 a ~ 6 2 c、6 3 a ~ 6 3 c、6 4 a ~ 6 4 c は、アルミニウム、銅、若しくは銅、シリコン、チタン、ネオジム、スカンジウムなどの耐熱性向上元素が添加されたアルミニウムを用いて形成することが好ましい。アルミニウム膜をスパッタリング法若しくは蒸着法で形成し、フォトリソグラフィ技術を利用して所定のパターンに形成する。また、銀、銅などの導電性ナノペーストを用いてスクリーン印刷法、インクジェット法、ナノインプリント法を用いて形成しても良い。

#### 【 0 0 4 8 】

配線 6 1 a ~ 6 1 c、6 2 a ~ 6 2 c、6 3 a ~ 6 3 c、6 4 a ~ 6 4 c は上記のようにアルミニウム、銅などで形成すれば良いが、下地との密着性向上と拡散を防ぐバリア層として機能する導電性材料を組み合わせた積層構造としても良い。例えば、バリア層として機能する配線 6 1 a ~ 6 4 a をモリブデン、クロム、チタン、タンタル、窒化チタン等の高融点金属で形成し、配線 6 1 b ~ 6 4 b を上述のアルミニウム、若しくは耐熱性向上元素が添加されたアルミニウム等で形成し、配線 6 1 c ~ 6 4 c を配線 6 1 a ~ 6 4 a と同等の導電性材料で形成する。

10

#### 【 0 0 4 9 】

保護絶縁膜 6 5 は、バッファ層 5 7、5 8、配線 6 1 a ~ 6 1 c、6 2 a ~ 6 2 c、6 3 a ~ 6 3 c、6 4 a ~ 6 4 c などを被覆するように形成する。保護絶縁膜 6 5 は、窒化シリコン、窒化酸化シリコンで形成することが好ましい。保護絶縁膜 6 5 には配線 6 4 c を露出するコンタクトホール 6 9 が形成される。

20

#### 【 0 0 5 0 】

保護絶縁膜 6 5 は、スパッタリング法または CVD 法で形成される。

#### 【 0 0 5 1 】

画素電極 6 6 はコンタクトホール 6 9 で配線 6 4 c と接続する。画素電極 6 6 は酸化インジウムスズ、酸化亜鉛、酸化スズなどの透光性を有する導電性材料で形成する。または、アルミニウム、窒化アルミニウム、チタン、窒化チタン、タンタル、窒化タンタル、もしくは銀等の遮光性導電材料を用いて形成する。または、有機導電性材料で形成しても良い。

30

#### 【 0 0 5 2 】

なお、図 1 ( C ) においては、薄膜トランジスタ 5 1 a、5 1 b としては、配線 6 1 a ~ 6 1 c、6 2 a ~ 6 2 c、6 3 a ~ 6 3 c、6 4 a ~ 6 4 c と、n 型半導体膜 5 9、p 型半導体膜 6 0 とを分離するとき、バッファ層 5 7、5 8 の一部もエッチングされ、一部に凹部が形成されたチャネルエッチ型の薄膜トランジスタを示したが、これに限定されるものではない。

30

#### 【 0 0 5 3 】

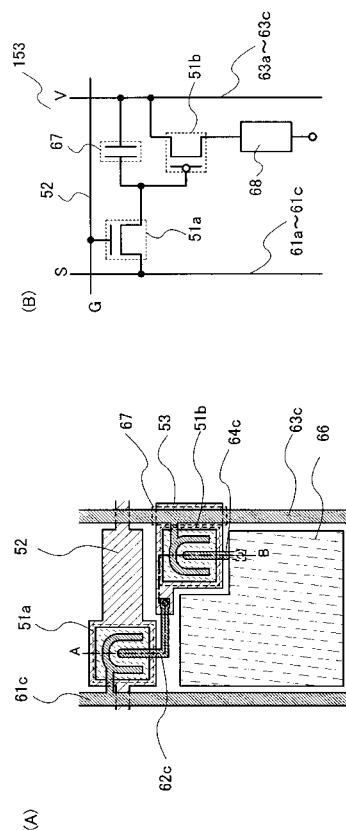

図 2 に示すように、ゲート電極 5 2 上にゲート絶縁膜 5 4 が形成され、ゲート絶縁膜 5 4 上には微結晶半導体膜 5 5 が形成され、微結晶半導体膜 5 5 上にはバッファ層 7 1 が形成され、バッファ層 7 1 上にチャネル保護膜 7 3 が形成され、チャネル保護膜 7 3 上に一対の n 型半導体膜 7 5 が形成され、n 型半導体膜 7 5 上に、一対の配線 6 1 a ~ 6 1 c、6 2 a ~ 6 2 c が形成されるチャネル保護型の薄膜トランジスタを、第 1 の薄膜トランジスタ 7 0 a とすることができる。また、同様に、ゲート電極 5 3 上にゲート絶縁膜 5 4 が形成され、ゲート絶縁膜 5 4 上には微結晶半導体膜 5 6 が形成され、微結晶半導体膜 5 6 上にはバッファ層 7 2 が形成され、バッファ層 7 2 上にチャネル保護膜 7 4 が形成され、チャネル保護膜 7 4 上に一対の p 型半導体膜 7 6 が形成され、p 型半導体膜 7 6 上に、一対の配線 6 3 a ~ 6 3 c、6 4 a ~ 6 4 c が形成されるチャネル保護型の薄膜トランジスタを、第 2 の薄膜トランジスタ 7 0 b とすることができる。

40

#### 【 0 0 5 4 】

なお、図 1 ( C )、及び図 2 では、シングルゲート構造の薄膜トランジスタを示したが、複数の薄膜トランジスタが直列に接続され、なおかつ複数の薄膜トランジスタが一つの微結晶半導体膜を共有しているような構成を有する、マルチゲート構造としてもよい。マルチゲート構造とすることで、薄膜トランジスタのオフ電流を低減させることができる。

50

## 【0055】

本実施の形態で示す表示装置は、画素電極への信号の入力を制御するためのスイッチング用の薄膜トランジスタまたは発光素子68への電流または電圧の供給を制御するための駆動用の薄膜トランジスタとして、nチャネル型薄膜トランジスタ及びpチャネル型薄膜トランジスタを用いて形成した画素を有する。nチャネル型薄膜トランジスタ及びpチャネル型薄膜トランジスタは、チャネル形成領域として微結晶半導体膜を用いているため、閾値の変動を抑えることが可能である。また、微結晶半導体膜の酸素濃度が $1 \times 10^{-6}$  atom s / cm<sup>3</sup>以下である。このため、欠陥を低減することができる。また、pチャネル型薄膜トランジスタにおいては、ドナーとして働く酸素の濃度を低減することが可能である。これらのため、nチャネル型薄膜トランジスタ及びpチャネル型薄膜トランジスタの移動度を上昇させることができる。代表的には、nチャネル型薄膜トランジスタの移動度は10以上 $45\text{ cm}^2/\text{V}\cdot\text{s}$ 以下であり、pチャネル型薄膜トランジスタの移動度は $0.3\text{ cm}^2/\text{V}\cdot\text{s}$ 以下とすることができます。

10

## 【0056】

## (実施の形態2)

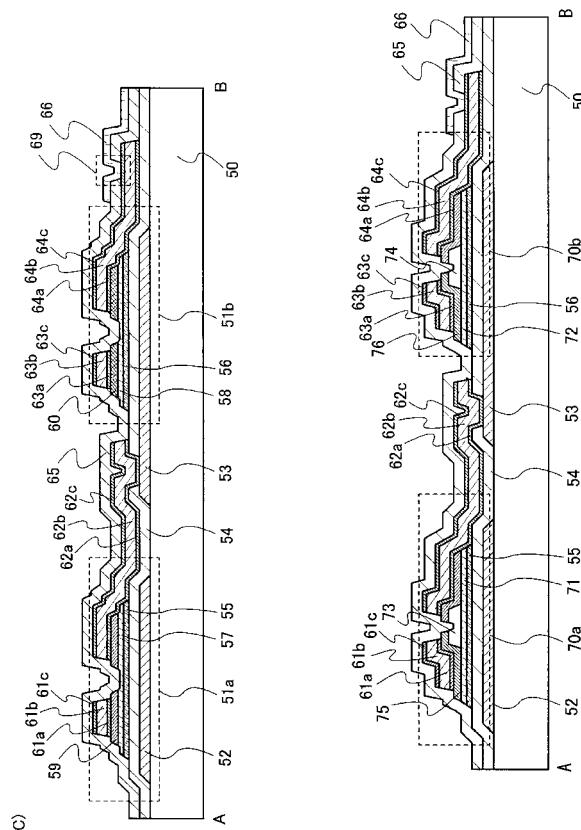

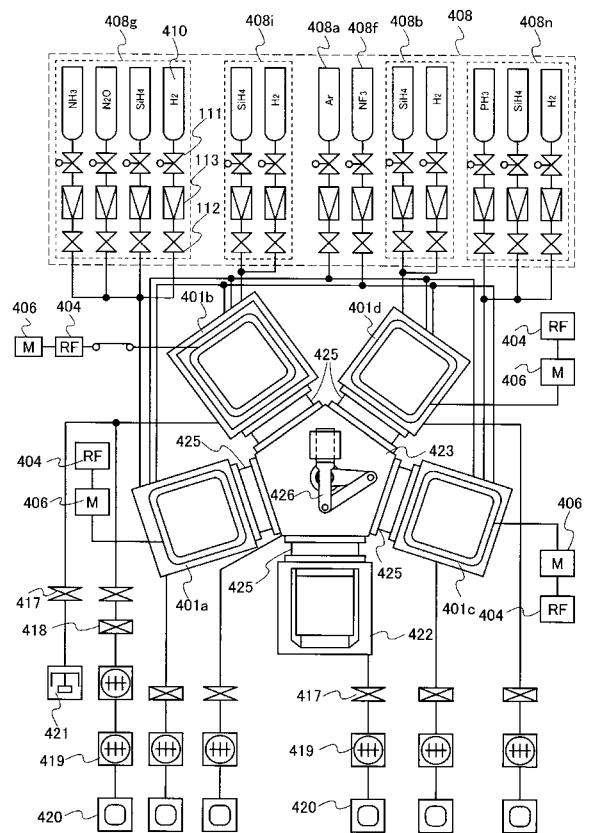

本実施の形態では、実施の形態1で示すゲート絶縁膜、微結晶半導体膜、バッファ層、n型半導体膜、p型半導体膜、保護絶縁膜等を成膜するために用いるプラズマCVD装置及びその成膜方法について、図3乃至図5、及び図24を用いて説明する。

20

## 【0057】

図3は高周波電力が印加されるプラズマCVD装置の一構成例を示す。反応室400はアルミニウム又はステンレスなど剛性のある素材で形成され、内部を真空排気できるように構成されている。反応室400には第1の電極401と第2の電極402が備えられている。

30

## 【0058】

第1の電極401には高周波電力供給手段403が連結され、第2の電極402は接地電位が与えられ、基板を載置できるように構成されている。第1の電極401は絶縁材416により反応室400と絶縁分離され、高周波電力が漏洩しないように構成されている。なお、図3では、第1の電極401と第2の電極402について容量結合型(平行平板型)の構成を示しているが、高周波電力を印加して反応室400の内部にプラズマを生成できるものであれば、誘導結合型など他の構成を適用することもできる。

30

## 【0059】

高周波電力供給手段403は、高周波電源404、及びそれらに対応して整合器406が含まれている。高周波電源404から出力される高周波電力は、第1の電極401に供給される。

40

## 【0060】

高周波電源404が供給する高周波電力は、概ね波長として10m以上の高周波が適用され、HF帯である3MHzから30MHz、代表的には13.56MHzの周波数、またはVHF帯の周波数であり概ね波長が10m未満の高周波が適用され、30MHz～300MHzの高周波電力が適用される。

## 【0061】

第1の電極401はガス供給手段408にも連結されている。ガス供給手段408は、反応ガスが充填されるシリンダ410、圧力調整弁411、ストップバルブ412、マスフローコントローラ413などで構成されている。反応室400内において、第1の電極401は基板と対向する面がシャワー板状に加工され、多数の細孔が設けられている。第1の電極401に供給される反応ガスは、中空構造である第1の電極の細孔から反応室400内に供給される。

## 【0062】

反応室400に接続される排気手段409は真空排気と、反応ガスを流す場合において反応室400内を所定の圧力に保持するように制御する機能が含まれている。排気手段409の構成としては、バタフライバルブ417、コンダクタンスバルブ418、ターボ分子

50

ポンプ 419、ドライポンプ 420などが含まれる。バタフライバルブ 417とコンダクタンスバルブ 418を並列に配置する場合には、バタフライバルブ 417を閉じてコンダクタンスバルブ 418を動作させることで、反応ガスの排気速度を制御して反応室 400の圧力を所定の範囲に保つことができる。また、コンダクタンスの大きいバタフライバルブ 417を開くことで高真空排気が可能となる。

#### 【0063】

真空度として  $10^{-5}$  Paよりも低い圧力の超高真空排気する場合には、クライオポンプ 421を併用することが好ましい。その他、到達真空度として超高真空まで排気する場合には、反応室 400の内壁を鏡面加工し、内壁からのガス放出を低減するためにベーキング用のヒータを設けても良い。

10

#### 【0064】

ヒータコントローラ 415により温度制御される基板加熱ヒータ 414は第2の電極 402に設けられている。基板加熱ヒータ 414は第2の電極 402内に設けられる場合、熱伝導加熱方式が採用され、シーズヒータなどで構成される。第1の電極 401と第2の電極 402の間隔は適宜変更できるようになっている。この間隔の調節は、反応室 400内で第2の電極 402の高さ変更ができるようにベローズを用いて構成されている。

#### 【0065】

本形態に係るプラズマ CVD 装置の反応室を用いることで、酸化シリコン膜、窒化シリコン膜に代表される絶縁膜、微結晶シリコン膜、非晶質シリコン膜に代表される半導体膜、その他薄膜トランジスタなどで使用される各種薄膜の形成が可能となる。

20

#### 【0066】

以下に、薄膜を形成する方法について、代表例として微結晶シリコン膜を成膜する工程について、図 4 を参照して時系列的に説明する。

#### 【0067】

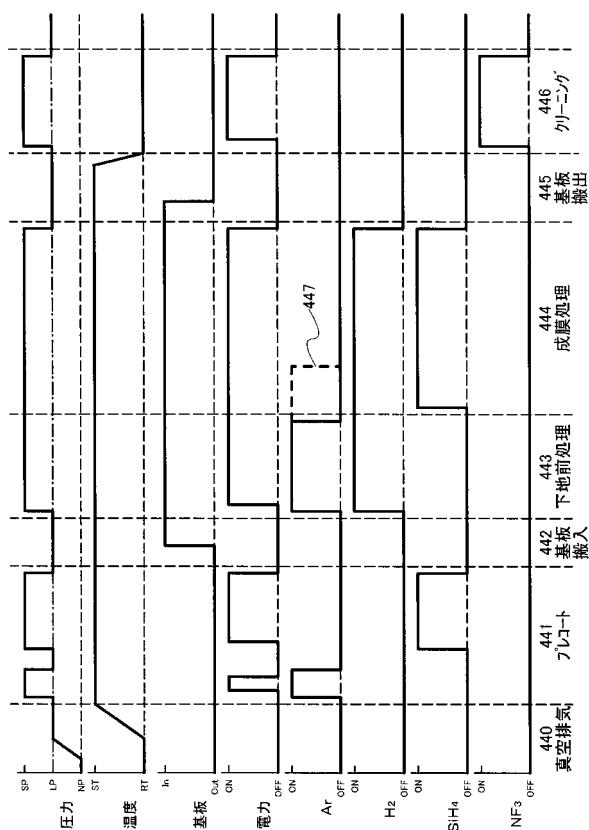

図 4 は微結晶シリコン膜を形成する工程を説明するタイムチャートであり、代表的な一例を示す。図 4 の説明は反応室を大気圧から真空排気 440 する段階から示されており、その後に行われるプレコート 441、基板搬入 442、下地前処理 443、成膜処理 444、基板搬出 445、クリーニング 446 の各処理が時系列的に示されている。

#### 【0068】

まず、反応室内を所定の真空度 (Normal Pressure : NP) まで真空排気する。真空度として  $10^{-5}$  Paよりも低い圧力の超高真空排気する場合には、ターボ分子ポンプによる排気を行い、さらにクライオポンプを使って真空排気する。また、反応室を室温 (Room Temperature : RT) から加熱処理して内壁からの脱ガス処理を行うことが好ましい。また、基板を加熱するヒータも動作させて温度を安定化させる。基板の加熱温度 (Setting Temperature : ST) は 100 ~ 300、好ましくは 120 ~ 280、さらに好ましくは 120 ~ 220 で行う。

30

#### 【0069】

プレコート 441 は、反応室の内壁に吸着した気体（酸素及び窒素などの大気成分、若しくは反応室のクリーニングに使用したエッティングガス）を除去するためにアルゴンなどの希ガスを導入して、所定の圧力 (Setting Pressure : SP) でプラズマ処理をすることが好ましい。この処理により圧力を下げて真空度を高めることができる。また、反応室の内壁を基板上に堆積されるべき膜と同種の膜で被覆する処理が含まれている。本形態は微結晶シリコン膜を形成する工程を示す。従って、内壁被覆膜としてシリコン膜を形成する処理が行われる。プレコート 441 はシランガスが導入された後、高周波電力を印加してプラズマを生成する。シランガスは酸素、水分等と反応するので、シランガスを流し、さらにシランプラズマを生成することで反応室内の酸素、水分を除去することができる。

40

#### 【0070】

プレコート 441 の後、基板搬入 442 が行われる。微結晶シリコン膜が堆積されるべき基板は、真空排気された圧力 (Load Lock Pressure : LP) のロード

50

室に保管されているので、基板を搬入したとしても真空度が著しく悪化することはない。

#### 【0071】

下地前処理443は、微結晶シリコン膜を形成する場合において、特に有効な処理であり行うことが好ましい。すなわち、ガラス基板表面、絶縁膜の表面若しくは非晶質シリコンの表面上に微結晶シリコン膜をプラズマCVD法で成膜する場合には、不純物や格子不整合などに起因して堆積初期段階において非晶質層が形成されてしまう。この非晶質層の厚さを極力低減し、可能であれば無くするために下地前処理443を行うことが好ましい。下地前処理としては希ガスプラズマ処理、水素プラズマ処理若しくはこの両者の併用により行うことが好ましい。希ガスプラズマ処理としては、アルゴン、クリプトン、キセノンなど質量数の大きい希ガス元素を用いることが好ましい。表面に付着した酸素、水分、有機物、金属元素などをスパッタリングの作用で除去するためである。水素プラズマ処理は、水素ラジカルにより、表面に吸着した前記不純物の除去と、絶縁膜若しくは非晶質シリコン膜に対するエッチング作用により清浄表面を形成するのに有効である。また、希ガスプラズマ処理と水素プラズマ処理を併用することにより微結晶核生成を促進する作用も期待される。

10

#### 【0072】

微結晶核の生成を促進させるという意味においては、図4中の破線447で示すように、微結晶シリコン膜の成膜初期段階においてアルゴンなどの希ガスを供給し続けることは有効である。

20

#### 【0073】

微結晶シリコン膜を形成する成膜処理444は、下地前処理443に続いて行われる処理である。微結晶シリコン膜は、シランガス（不純物半導体とする場合には、シランに加えドーピングガスが添加される）と水素及び／又は希ガスの混合ガス内でグロー放電プラズマにより成膜する。シランは水素及び／又は希ガスで10倍から2000倍に希釈される。基板の加熱温度は100～300、好ましくは120～280、さらに好ましくは120～220で行う。微結晶シリコン膜の成長表面を水素で不活性化し、微結晶シリコンの成長を促進するためには120～220で成膜を行うことが好ましい。

#### 【0074】

グロー放電プラズマの生成は、本形態で示されるように、1MHzから20MHz、代表的には13.56MHzの高周波電力、または20MHzより大きく120MHz程度までのVHF帯の高周波電力を印加することで行われる。

30

#### 【0075】

この場合、プレコート441の処理をしておくことで、微結晶シリコン膜中に反応室を構成する金属を不純物として導入してしまうのを防ぐことができる。すなわち、反応室内をシリコンで被覆しておくことで、反応室内がプラズマにより食刻されるのを防ぐことができ、微結晶シリコン膜中に含まれる不純物濃度を低減することができる。

#### 【0076】

成膜処理444においては、反応ガスにヘリウムを加えても良い。ヘリウムは24.5eVとすべての気体中で最も高いイオン化工エネルギーを持ち、そのイオン化工エネルギーよりも少し低い、約20eVの準位に準安定状態があるので、放電持続中においては、イオン化にはその差約4eVしか必要としない。そのため放電開始電圧も全ての気体中最も低い値を示す。このような特性から、ヘリウムはプラズマを安定的に維持することができる。また、均一なプラズマを形成することができるので、微結晶シリコン膜を堆積する基板の面積が大きくなってもプラズマ密度の均一化を図る効果を奏する。

40

#### 【0077】

微結晶シリコンの成膜が終了した後、シラン、水素などの反応ガス及び高周波電力の供給を止めて基板搬出445を行う。引き続き別基板に対して成膜処理を行う場合には、基板搬入442の段階に戻り同じ処理が行われる。反応室内に付着した被膜や粉末を除去するには、クリーニング446を行う。

#### 【0078】

50

クリーニング 446 は  $\text{NF}_3$ 、 $\text{SF}_6$  に代表されるエッチングガスを導入してプラズマエッチングを行う。また、 $\text{ClF}_3$  のようにプラズマを利用しなくともエッチングが可能なガスを導入して行う。クリーニング 446においては基板加熱用のヒータを切って、反応室の温度を下げて行なうことが好ましい。エッチングにおける反応副生成物の生成を抑えるためである。クリーニング 446 の終了後はプレコート 441 に戻り、以下同様の処理を行えば良い。

#### 【0079】

本形態では図 4 を参照して微結晶シリコン膜の成膜方法について説明したが、本形態はこれに限定されず、反応ガスを替えれば各種薄膜を形成することができる。半導体膜としては、非晶質シリコン膜、非晶質シリコンゲルマニウム膜、非晶質シリコンカーバイト膜、微結晶シリコンゲルマニウム膜、微結晶シリコンカーバイト膜などの成膜に本形態を用いることができる。絶縁膜としては、酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜、窒化酸化シリコン膜などの成膜に本形態を利用することができる。

10

#### 【0080】

なお、酸化窒化シリコン膜とは、その組成として、窒素よりも酸素の含有量が多いものであって、ラザフォード後方散乱法 (RBS : Rutherford Backscattering Spectrometry) 及び水素前方散乱法 (HFS : Hydrogen Forward Scattering) を用いて測定した場合に、組成範囲として酸素が 50 ~ 70 原子%、窒素が 0.5 ~ 1.5 原子%、シリコンが 25 ~ 35 原子%、水素が 0.1 ~ 1.0 原子% の範囲で含まれるものという。また、窒化酸化シリコン膜とは、その組成として、酸素よりも窒素の含有量が多いものであって、RBS 及び HFS を用いて測定した場合に、組成範囲として酸素が 5 ~ 30 原子%、窒素が 20 ~ 55 原子%、シリコンが 25 ~ 35 原子%、水素が 10 ~ 30 原子% の範囲で含まれるものという。但し、酸化窒化シリコンまたは窒化酸化シリコンを構成する原子の合計を 100 原子%としたとき、窒素、酸素、シリコン及び水素の含有比率が上記の範囲内に含まれるものとする。

20

#### 【0081】

以上のように、本形態によれば酸素濃度が  $1 \times 10^{16} \text{ atoms/cm}^3$  以下である薄膜、代表的には微結晶シリコン膜を形成することができる。

#### 【0082】

次に、上記反応室が適用されるプラズマ CVD 装置の一例として、TFT を構成するゲート絶縁膜及び半導体膜の成膜に適した構成の一例を示す。

30

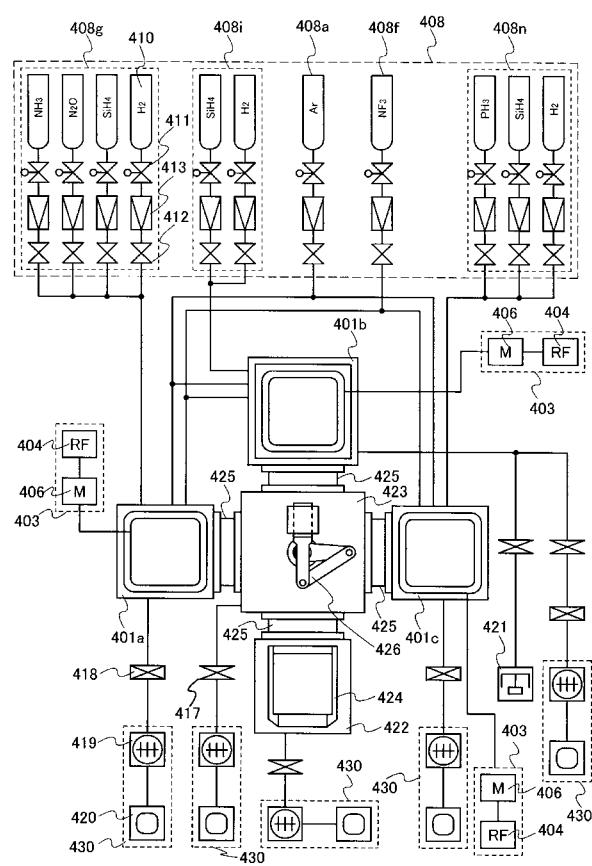

#### 【0083】

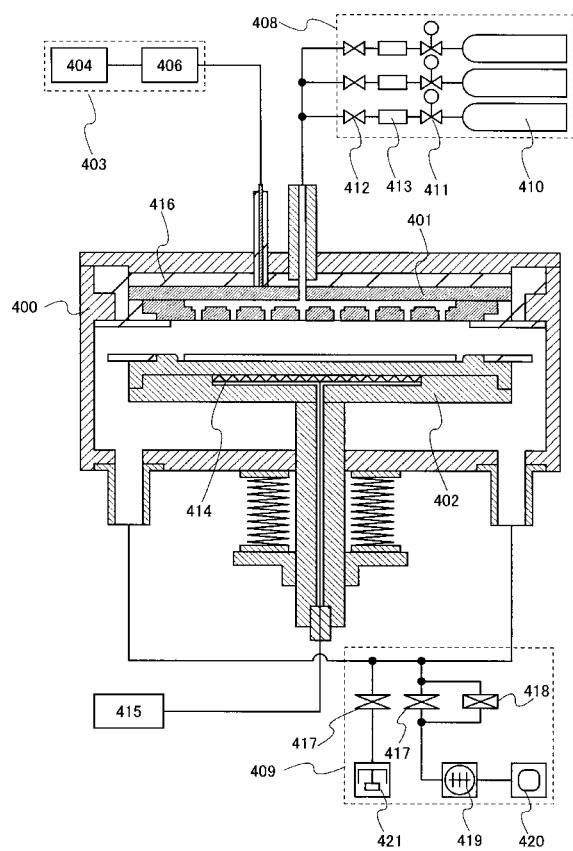

図 5 は複数の反応室を備えたマルチ・チャンバ・プラズマ CVD 装置の一例を示す。この装置は共通室 423 と、ロード / アンロード室 422、第 1 反応室 401a、第 2 反応室 401b、第 3 反応室 401c を備えた構成となっている。ロード / アンロード室 422 のカセットに装填される基板は、共通室 423 の搬送機構 426 によって各反応室に搬入される枚葉式の構成である。共通室 423 と各室の間にはゲートバルブ 425 が備えられ、各反応室で行われる処理が、相互に干渉しないように構成されている。

#### 【0084】

各反応室は形成する薄膜の種類によって区分されている。例えば、第 1 反応室 401a はゲート絶縁膜などの絶縁膜を成膜し、第 2 反応室 401b はチャネルを形成する微結晶半導体層を成膜し、第 3 反応室 401c はソース及びドレインを形成する一導電型の不純物半導体層を成膜する反応室として充当される。勿論、反応室の数は図 5 に示された数に限定されるわけではなく、必要に応じて任意に増減することができる。また、一の反応室で一の膜を成膜するようにしても良いし、一の反応室で複数の膜を成膜するように構成しても良い。

40

#### 【0085】

各反応室には排気手段 430 としてターボ分子ポンプ 419 とドライポンプ 420 が接続されている。排気手段はこれらの真空ポンプの組み合わせに限定されるものではなく、概略  $10^{-1} \text{ Pa}$  から  $10^{-5} \text{ Pa}$  の真空度にまで排気できるものであれば他の真空ポンプ

50

を適用することができる。また、微結晶半導体膜を形成する第2反応室401bは超高真

空まで真空排気するものとして、クライオポンプ421が連結されている。排気手段43

0と各反応室との間にはバタフライバルブ417が設けられており、これによって真空排

気を遮断させることができ、コンダクタンスバルブ418によって排気速度を制御して、

それぞれの反応室の圧力を調節することができる。

## 【0086】

ガス供給手段408はシランに代表される半導体材料ガス若しくは希ガスなどプロセスに

用いるガスが充填されるシリンダ410、ストップバルブ412、マスフローコントローラ

413などで構成されている。ガス供給手段408gは第1反応室401aに接続され

、ゲート絶縁膜を成膜するためのガスを供給する。ガス供給手段408iは第2反応室4

01bに接続され、微結晶半導体膜用のガスを供給する。ガス供給手段408nは第3反

応室401cに接続され、例えはn型半導体膜用のガスを供給する。ガス供給手段408

aは水素を供給し、ガス供給手段408fは反応室内のクリーニングに用いるエッチング

ガスを供給する系統であり、これらは各反応室に接続されている。

10

## 【0087】

各反応室にはプラズマを形成するための高周波電力供給手段403が連結されている。高

周波電力供給手段403は高周波電源404と整合器406が含まれる。

## 【0088】

図24は、図5のマルチ・チャンバ・プラズマCVD装置の構成に、第4反応室401d

を追加した構成を示す。第4反応室401dには、ガス供給手段408bが連結されてい

る。その他、高周波電力供給手段、排気手段の構成は同様である。各反応室は形成する薄

膜の種類によって使い分けることが可能である。例えは、第1反応室401aはゲート絶

縁膜などの絶縁膜を成膜し、第2反応室401bはチャネルを形成する微結晶半導体層を成

膜し、第4反応室401dではチャネル形成用の半導体層を保護するバッファ層を形成

し、第3反応室401cはソース及びドレインを形成する一導電型の不純物半導体層を成

膜する反応室として用いることができる。それぞれの薄膜は最適な成膜温度があるので、

各反応室の温度を個別に制御する必要がある。反応室を個別に分けておくことで成膜温度

を管理することが容易となる。さらに、同じ膜種を繰り返し成膜することができるので、

成膜履歴に係る残留不純物の影響を排除することができる。

20

## 【0089】

本形態で示すように、図5及び図24で示すような、反応室を複数個用い共通室で連結す

ることにより、複数の異なる層を大気に触れさせることなく連続して積層することが可能

となる。

30

## 【0090】

なお、図5、及び図24では示していないが、p型半導体膜用のガス（代表的には、ジボ

ラン、シラン、及び水素）を供給するガス供給手段、及び当該ガス供給手段が連結される

反応室が設けられる。

40

## 【0091】

## (実施の形態3)

次に、表示装置の一形態である発光装置について、図1、図6、及び図7を用いて説明

する。発光装置としては、ここではエレクトロルミネッセンスを利用する発光素子を用い

て示す。エレクトロルミネッセンスを利用する発光素子は、発光材料が有機化合物である

か、無機化合物であるかによって区別され、一般的に、前者は有機EL素子、後者は無機

EL素子と呼ばれている。

## 【0092】

有機EL素子は、発光素子に電圧を印加することにより、一対の電極から電子および正

孔がそれぞれ発光性の有機化合物を含む層に注入され、電流が流れる。そして、それらキ

ャリア（電子および正孔）が再結合することにより、発光性の有機化合物が励起状態を形

成し、その励起状態が基底状態に戻る際に発光する。このようなメカニズムから、このよ

うな発光素子は、電流励起型の発光素子と呼ばれる。

50

## 【0093】

無機EL素子は、その素子構成により、分散型無機EL素子と薄膜型無機EL素子とに分類される。分散型無機EL素子は、発光材料の粒子をバインダ中に分散させた発光層を有するものであり、発光メカニズムはドナー準位とアクセプター準位を利用するドナー・アクセプター再結合型発光である。薄膜型無機EL素子は、発光層を誘電体層で挟み込み、さらにそれを電極で挟んだ構造であり、発光メカニズムは金属イオンの内殻電子遷移を利用する局在型発光である。

## 【0094】

ここでは、発光素子として有機EL素子を用いて説明する。また、薄膜トランジスタとして、図1(C)に示すチャネルエッチ型の薄膜トランジスタを用いて示すが、図2に示すチャネル保護型の薄膜トランジスタを適宜用いることができる。10

## 【0095】

発光装置の一形態としては、図1(A)と図1(C)に示す構成及び図1(B)に示す等価回路を有する画素がある。代表的には、図6(A)に示すように、基板50上に、第2の薄膜トランジスタ51bのスイッチング用の薄膜トランジスタとして機能する第1の薄膜トランジスタ51aと、発光素子の駆動用の薄膜トランジスタとして機能する第2の薄膜トランジスタ51bと、保護絶縁膜65のコンタクトホールにおいて第2の薄膜トランジスタ51bの配線64cに接続する画素電極66が形成される。

## 【0096】

図6(A)に示すように、保護絶縁膜65及び画素電極66の端部上に、隔壁70が形成される。隔壁70は開口部を有しており、該開口部において画素電極66が露出している。隔壁70は、シロキサンポリマーなどの有機樹脂膜、または無機絶縁膜を用いて形成する。特に感光性の材料を用い、画素電極上に開口部を形成し、その開口部の側壁が連続した曲率を持って形成される傾斜面となるように形成することが好ましい。20

## 【0097】

次に、隔壁70の開口部において画素電極66と接するように、発光層82が形成され、発光層82を覆うように対向電極83が形成され、対向電極83及び隔壁70を覆うように保護絶縁膜84が形成される。

## 【0098】

発光層82は、単数の層で構成されていても、複数の層が積層されるように構成されてもどちらでも良い。また、第2の薄膜トランジスタ51bがpチャネル型薄膜トランジスタの場合、仕事関数が大きい導電材料で形成される陽極を画素電極66として用い、第2の薄膜トランジスタ51bがnチャネル型薄膜トランジスタの場合は、仕事関数が小さい導電性材料で形成される陰極を画素電極66として用いる。30

## 【0099】

隔壁70の開口部において、画素電極66、発光層82、対向電極83が重なり合うことで、発光素子90が構成される。

## 【0100】

保護絶縁膜84は、発光素子90に酸素、水素、水分、二酸化炭素等が侵入しないように、窒化シリコン膜、窒化酸化シリコン膜、DLC膜等を用いて形成する。40

## 【0101】

さらに、実際には、外気に曝されないようにガスバリア性が高く、脱ガスの少ない保護フィルム(ラミネートフィルム、紫外線硬化樹脂フィルム等)やカバー材で保護絶縁膜84をパッケージング(封入)することが好ましい。

## 【0102】

次に、発光素子の構成について、図6を用いて説明する。ここでは、駆動用の薄膜トランジスタである第2の薄膜トランジスタ51bが、p型の場合を例に挙げて、発光素子の断面構造について説明する。

## 【0103】

発光素子は発光を取り出すために少なくとも陽極又は陰極の一方が透明であればよい。

10

20

30

40

50

そして、基板上に薄膜トランジスタ及び発光素子を形成し、基板とは逆側の面から発光を取り出す上面射出や、基板側の面から発光を取り出す下面射出や、基板側及び基板とは反対側の面から発光を取り出す両面射出構造の発光素子があり、本実施の形態の画素構成はどの射出構造の発光素子にも適用することができる。

#### 【0104】

下面射出構造の発光素子について図6(A)を用いて説明する。駆動用の薄膜トランジスタ51bがp型で、発光素子90から発せられる光が画素電極66を通して射出する場合の、発光素子の断面図を示す。ここでは、画素電極66は陽極として機能する。駆動用薄膜トランジスタである第2の薄膜トランジスタ51bと電気的に接続された透光性を有する導電性材料で形成される画素電極66が成膜されており、画素電極66上に発光層82、対向電極83が順に積層されている。この例では、対向電極83は陰極として機能する。画素電極66は、仕事関数が大きく、光を透過する透光性を有する導電性材料を用いて形成し、例えば酸化インジウムスズ、酸化亜鉛、酸化スズなどの透光性を有する導電性導電膜を用いても良い。対向電極83は仕事関数が小さく、なおかつ遮光性を有する導電膜であれば公知の材料を用いることができる。例えば、Ca、Al、MgAg、AlLi等が望ましい。発光層82は、単数の層で構成されても、複数の層が積層されるように構成されてもどちらでも良い。複数の層で構成されている場合、画素電極66上にホール注入層、ホール輸送層、発光層、電子輸送層、電子注入層の順に積層する。なおこれらの層を全て設ける必要はない。

10

#### 【0105】

対向電極83及び画素電極66で発光層82を挟んでいる領域が発光素子90に相当する。図6(A)に示した画素の場合、発光素子90から発せられる光は、白抜きの矢印で示すように画素電極66側に射出する。

20

#### 【0106】

次に、両面射出構造の発光素子について、図6(B)を用いて説明する。図6(B)では、駆動用の薄膜トランジスタである第2の薄膜トランジスタ51bと電気的に接続された透光性を有する画素電極66上に発光層82、陰極85が順に積層されている。画素電極66は陽極として機能する。陰極85は、図6(A)の場合と同様に、仕事関数が小さい導電膜であれば公知の材料を用いることができる。ただしその膜厚は、光を透過する程度とする。例えば20nmの膜厚を有するAlまたはMgAgを、陰極85として用いることができる。発光層82は、図6(A)と同様に、単数の層で構成されても、複数の層が積層されるように構成されてもどちらでも良い。画素電極66は、図6(A)と同様に、仕事関数が大きく光を透過する透光性を有する導電性材料を用いて形成することができる。

30

#### 【0107】

画素電極66と、発光層82と、陰極85とが重なっている部分が発光素子90に相当する。図6(B)に示した画素の場合、発光素子90から発せられる光は、白抜きの矢印で示すように画素電極66側と陰極85側の両方に射出する。

#### 【0108】

上面射出構造の発光素子について図6(C)を用いて説明する。

40

#### 【0109】

図6(C)に、駆動用の薄膜トランジスタ51bがp型で、発光素子90から発せられる光が陰極93側に抜ける場合の、画素の断面図を示す。図6(C)では、発光素子90の陽極91と駆動用の薄膜トランジスタ51bが電気的に接続されており、陽極91上に発光層92、陰極93が順に積層されている。陽極91は、光を遮光する導電材料を用いて形成する。代表的には、アルミニウム、チタン、窒化チタン、タンタル、窒化タンタル、銀等の遮光性を有する導電材料と、図6(A)で示す陽極材料との積層構造とすることが好ましい。陰極93は、図6(A)に示す仕事関数が小さい導電膜を用いることができる。ただしその膜厚は、光を透過する程度とする。例えば5~20nmの膜厚を有するAlまたはAgMgを、陰極93として用いることができる。発光層92は、図6(A)に

50

示す発光層 8 2 と同様に、単数の層で構成されていても、複数の層が積層されるように構成されていてもどちらでも良い。

【0110】

陽極 9 1 と、発光層 9 2 と、陰極 9 3 とが重なっている部分が発光素子 9 0 に相当する。図 6 ( C ) に示した画素の場合、発光素子 9 0 から発せられる光は、白抜きの矢印で示すように陰極 9 3 側に射出する。

【0111】

なお、上面射出構造の発光素子は、第 1 の薄膜トランジスタ 5 1 a、第 2 の薄膜トランジスタ 5 1 b 上でも発光することが可能であるため、発光面積を増大することが可能である。しかしながら、発光層 9 2 の下に存在する層が凹凸を有すると、当該凹凸において膜厚分布が不均一となり陽極 9 1 及び陰極 9 3 がショートし、表示欠陥となってしまう。このため、保護絶縁膜 6 5 上に平坦化膜 8 6 を形成し、平坦化膜 8 6 及び保護絶縁膜 6 5 に形成されるコンタクトホールにおいて、配線 6 4 c に接続する陽極 9 1 が形成される。平坦化膜 8 6 は、アクリル、ポリイミド、ポリアミドなどの有機樹脂、またはシロキサンポリマーを用いて形成することが好ましい。なお、陽極 9 1 は、平坦化膜 8 6 上に形成されるため、保護絶縁膜 6 5 の表面の凹凸を低減することが可能である。なお、コンタクトホールにおいては、陽極 9 1 が凹凸を有するため、当該凹凸部分を覆い、且つ開口部を有する隔壁 7 0 を設ける。隔壁 7 0 の開口部において陽極 9 1 と接するように、発光層 9 2 が形成され、発光層 9 2 を覆うように陰極 9 3 が形成され、陰極 9 3 及び隔壁 7 0 を覆うように保護絶縁膜 8 4 が形成される。

10

20

30

40

50

【0112】

なお、ここでは、発光素子として有機 E L 素子について述べたが、発光素子として無機 E L 素子を設けることも可能である。

【0113】

以上の工程により、発光装置を作製することができる。本実施の形態の発光装置は、オフ電流が少なく、電気特性が優れ、信頼性の高い薄膜トランジスタを用いているため、コントラストが高く、視認性の高い発光装置である。

【0114】

次に、本実施の形態で示す発光表示装置の画素 1 5 3 の等価回路の一例を図 1 ( B ) に示す。

【0115】

画素 1 5 3 は、第 1 の薄膜トランジスタ 5 1 a、第 2 の薄膜トランジスタ 5 1 b、容量素子 6 7 及び発光素子 6 8 を有している。なお、ここでは、第 1 の薄膜トランジスタ 5 1 a を n チャネル型薄膜トランジスタで設け、第 2 の薄膜トランジスタ 5 1 b を p チャネル型の薄膜トランジスタで設けている例を示しているが、これに限られない。第 1 の薄膜トランジスタ 5 1 a を p チャネル型薄膜トランジスタで設け、第 2 の薄膜トランジスタ 5 1 b を n チャネル型の薄膜トランジスタで設けてもよい。

【0116】

第 1 の薄膜トランジスタ 5 1 a は、ゲートが走査線 G 1 ~ G y のうちいずれかの走査線（ここでは、「走査線 G」とする）に電気的に接続され、ソース又はドレインの一方が信号線 S 1 ~ S x のうちいずれかの信号線（ここでは、「信号線 S」とする）に電気的に接続され、ソース又はドレインの他方が容量素子 6 7 の一方の電極及び第 2 の薄膜トランジスタ 5 1 b のゲートに電気的に接続されている。なお、第 1 の薄膜トランジスタ 5 1 a は、スイッチング薄膜トランジスタ又はスイッチ用薄膜トランジスタと呼ばれることがある。

【0117】

第 2 の薄膜トランジスタ 5 1 b は、ゲートが第 1 の薄膜トランジスタ 5 1 a のソース又はドレインの他方及び容量素子 6 7 の一方の電極に電気的に接続され、ソース又はドレインの一方が電源供給線 V 1 ~ V x のうちいずれかの電源供給線（ここでは、「電源供給線 V」とする）に電気的に接続され、ソース又はドレインの他方が発光素子 6 8 の一方の電

極に電気的に接続されている。発光素子 6 8 の他方の電極は、低電源電位が設定されてもよい。なお、第 2 の薄膜トランジスタ 5 1 b は、駆動用薄膜トランジスタと呼ばれることがある。

#### 【 0 1 1 8 】

なお、低電源電位とは、電源供給線 V に設定される高電源電位を基準にして低電源電位 < 高電源電位を満たす電位であり、低電源電位としては、例えば、G N D、0 V 等を設定することができる。

#### 【 0 1 1 9 】

容量素子 6 7 の他方の電極は、電源供給線 V 1 ~ V x のうちいずれかの電源供給線（ここでは、「電源供給線 V」とする）に電気的に接続されている。なお、容量素子 6 7 は、第 2 の薄膜トランジスタ 5 1 b のゲート容量を代用して省略した構成とすることも可能である。第 2 の薄膜トランジスタ 5 1 b のゲート容量は、ソース領域、ドレイン領域又は L D D 領域等とゲート電極とが重畳してオーバーラップしている領域で形成されていてもよいし、チャネル形成領域とゲート電極との間で形成されていてもよい。

10

#### 【 0 1 2 0 】

次に、発光表示装置の動作について説明する。なお、本実施の形態では定電流アナログ階調方式で動作させる発光表示装置について説明する。なお定電流駆動とは、1 フレーム期間等映像を保持する期間において、一定の電流で駆動させることであり、常時同じ電流で駆動させるという意味でない。

20

#### 【 0 1 2 1 】

走査線 G が選択された画素において、信号線 S の電位は、オン状態（導通状態）になった第 1 の薄膜トランジスタ 5 1 a を介して、容量素子 6 7 の一方の電極に入力される。そして、ビデオ信号に相当する電圧分の電荷が容量素子 6 7 に蓄積され、容量素子 6 7 はその電圧を保持する。この電圧は第 2 の薄膜トランジスタ 5 1 b のゲートとソース間電圧 V g s に相当する。

20

#### 【 0 1 2 2 】

そして、容量素子 6 7 の電極間の電圧が第 2 の薄膜トランジスタ 5 1 b のゲートに印加され、この印加電圧に応じて第 2 の薄膜トランジスタ 5 1 b を介して電源供給線 V から発光素子 6 8 に電流が流れ、発光素子 6 8 が発光する。

30

#### 【 0 1 2 3 】

発光素子 6 8 の発光輝度は、発光素子 6 8 を流れる電流にほぼ比例する。従って、発光素子 6 8 に流れる電流を変化させることによって画素の階調を表現することが可能となる。

#### 【 0 1 2 4 】

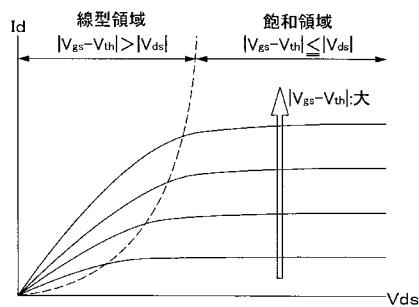

本実施の形態で示す発光表示装置では、発光素子 6 8 に流れる電流は、第 2 の薄膜トランジスタ 5 1 b のゲートに印加される電圧に応じて電源供給線 V より入力される。ここで一般に薄膜トランジスタのドレインとソース間電圧 V d s と、そのドレイン電流 I d とは、図 7 に示す様な関係を持っている。

30

#### 【 0 1 2 5 】

図 7 には、異なるゲート電圧 V g s に対応する複数のグラフを示している。ゲート電圧 V g s と第 2 の薄膜トランジスタ 5 1 b のしきい値電圧 V t h との差の絶対値 | V g s - V t h | が大きくなるほど、言い換えればゲート電圧 V g s の絶対値 | V g s | が大きくなるほど、ドレイン電流 I d は大きくなる。

40

#### 【 0 1 2 6 】

ゲート電圧 V g s と第 2 の薄膜トランジスタ 5 1 b のしきい値電圧 V t h との差の絶対値 | V g s - V t h | が、ドレインとソース間電圧 V d s の絶対値 | V d s | よりも大きい場合は、薄膜トランジスタは線形領域で動作し、ドレインとソース間電圧 V d s の絶対値 | V d s | 以下の場合は、薄膜トランジスタは飽和領域で動作する。飽和領域で動作する場合には、ドレインとソース間電圧 V d s が変化しても電流値はほとんど変化せず、V g s の大きさだけによって電流値が決まる。

50

## 【0127】

本実施の形態で示す発光表示装置では、発光素子68の発光時において、第2の薄膜トランジスタ51bを、ドレインとソース間電圧Vdsの絶対値|Vds|がゲート電圧Vgsと第2の薄膜トランジスタ51bのしきい値電圧Vthとの差の絶対値|Vgs-Vth|以上の飽和領域で動作させる。なお、発光素子68を非発光とする場合には、第2の薄膜トランジスタ51bをオフさせればよい。

## 【0128】

また、発光表示装置の画素の階調の表現は、第2の薄膜トランジスタ51bのゲートに印加される電圧を変化させて（信号線Sに入力する電位を変化させて）、発光素子68に流れる電流を変化させること（定電流アナログ階調方式）によって行う。つまり、定電流アナログ階調方式では、信号線Sに入力されるアナログ映像信号を変化させること（信号線Sの電位を変化させること）で階調表示が行われる。

10

## 【0129】

なお、本実施の形態に示す発光表示装置としては、図1(B)に示す等価回路を用いた画素の駆動方法を示したが、当該等価回路に限定されず、適宜ELの画素の様々な等価回路及び駆動方法を適用することができる。また、アナログ階調方式を用いた駆動方法に限らず、デジタル階調方式を用いた駆動方法を適用することが可能であり、且つデジタル階調方式の駆動方法が可能な画素を構成することも可能である。

## 【0130】

20

一般的に、発光素子68の発光時に第2の薄膜トランジスタ51bを飽和領域で動作させる場合、画素間で薄膜トランジスタの移動度やしきい値がばらつくとそれがそのままドレイン電流のばらつきとなり発光表示装置の表示むらとして現れる問題がある。特に、多結晶半導体膜や非晶質半導体膜を用いて薄膜トランジスタを形成する場合には、画素ごとの薄膜トランジスタの移動度やしきい値のばらつきが大きく、発光表示装置を定電流駆動で動作させることは困難であった。これは、半導体層の結晶化（レーザー結晶化等）において、画素部を構成する全領域において均一な結晶粒径を有する多結晶半導体膜を得ることが難しいためである。

## 【0131】

30

一方、本実施の形態で示す発光表示装置では、微結晶半導体膜を有する薄膜トランジスタによって画素を構成する薄膜トランジスタ等を形成するため、画素ごとにより薄膜トランジスタの移動度やしきい値がばらつくことを低減することができる。その結果、第2の薄膜トランジスタ51bを飽和領域で動作させた場合であっても、薄膜トランジスタの特性の変化が小さいため、定電流アナログ階調方式で動作させる場合であっても、発光表示装置の表示むらを防止することが可能となる。

## 【0132】

また、本実施の形態で示す発光表示装置は、定電流駆動で動作させ発光素子68の発光を電流で制御するため、発光素子68の発光を電圧で制御する定電圧駆動で動作させる場合と比較して、温度変化や発光素子の劣化により発光素子のV-I特性が変動した場合であっても一定の輝度を保持することが可能となる。

## 【0133】

40

## (実施の形態4)

本実施の形態では、静電破壊を防止することが可能な表示装置の構成について、図8乃至図10を用いて説明する。ここでは、画素部と駆動回路の間に、微結晶半導体膜を有するnチャネル型薄膜トランジスタ及びpチャネル型薄膜トランジスタを用いて保護回路を形成する。

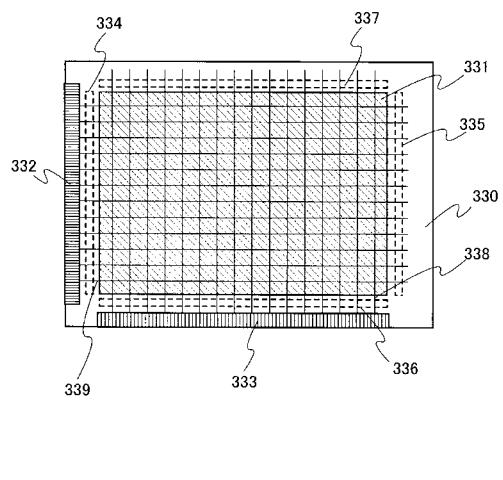

## 【0134】

まず、本実施の形態の表示装置の構成について図8を参照して説明する。図8は、表示装置が形成された基板330の上面図を示す。基板330上に、画素部331が形成されている。また、入力端子は、基板330上に形成された画素回路に対して信号又は電源電位を供給する。

50

## 【0135】

なお、本実施の形態は図8に示す形態に限定されない。すなわち、基板330上に走査線駆動回路又は信号線駆動回路が形成されていてもよい。

## 【0136】

基板330上に形成された走査線側の入力端子332及び信号線側の入力端子333と、画素部331とは縦横に伸びた配線によって接続されており、該配線は保護回路334～337に接続されている。

## 【0137】

画素部331と、入力端子332とは、配線339によって接続されている。保護回路334は、画素部331と、入力端子332との間に配置され、配線339に接続されている。保護回路334によって、画素部331が有する薄膜トランジスタ等の各種半導体素子を保護し、劣化又は破壊することを防止することができる。なお、配線339は、図中では一の配線を指し示しているが、配線339と平行に設けられている複数の配線のすべてが配線339と同様の接続関係を有する。なお、配線339は、走査線として機能する。

10

## 【0138】

なお、走査線側の保護回路は、入力端子332と画素部331との間に設けられている保護回路334のみならず、画素部331を挟んで入力端子332の反対側にも設けられても良い(図8の保護回路335を参照)。

20

## 【0139】

また、画素部331と、入力端子333とは配線338によって接続されている。保護回路336は、画素部331と、入力端子333との間に配置され、配線338に接続されている。保護回路336によって、画素部331が有する薄膜トランジスタ等の各種半導体素子を保護し、劣化又は破壊を防止することができる。なお、配線338は、図中では一の配線を指し示しているが、配線338と平行に設けられている複数の配線のすべてが配線338と同様の接続関係を有する。なお、配線338は、信号線として機能する。

20

## 【0140】

なお、信号線側の保護回路は、入力端子333と画素部331との間に設けられている保護回路336のみならず、画素部331を挟んで入力端子333の反対側にも設けられても良い(図8の保護回路337を参照)。

30

## 【0141】

なお、保護回路334～337は全て設ける必要はないが、少なくとも保護回路334は設ける必要がある。配線339に過大な電流が生じることで、画素部331が有する薄膜トランジスタのゲート絶縁膜が破壊され、多数の点欠陥を生じうるからである。

30

## 【0142】

更には、保護回路334のみならず保護回路336を設けることで配線338に過大な電流が生じることを防止することができる。そのため、保護回路334のみを設ける場合と比較して、信頼性が向上し、歩留まりが向上する。保護回路336を有することで、薄膜トランジスタ形成後のラビング工程にて生じうる、静電気による破壊を防止することができる。

40

## 【0143】

更には、保護回路335及び保護回路337を有することで、信頼性を更に向上させ、歩留まりを向上させることができる。保護回路335及び保護回路337は、入力端子332及び入力端子333とは反対側に設けられているため、これらは表示装置の作製工程中に生じる、各種半導体素子の劣化又は破壊の防止に寄与する。

## 【0144】

なお、図8では、基板330とは別に形成した信号線駆動回路及び走査線駆動回路をCOG方式やTAB方式等の公知の方式により基板330に実装する。また、走査線駆動回路と画素部とを基板330上に形成し、信号線駆動回路は別に形成したものと実装してもよい。また、走査線駆動回路の一部又は信号線駆動回路の一部を、画素部331と共に基

50

板330上に形成し、走査線駆動回路の他の部分又は信号線駆動回路の他の部分を実装するようにしても良い。走査線駆動回路の一部が画素部331と走査線側の入力端子332との間に設けられている場合には、走査線側の入力端子332と基板330上の走査線駆動回路の一部との間に保護回路を設けても良いし、走査線駆動回路の一部と画素部331との間に保護回路を設けても良いし、これらの双方に保護回路を設けても良い。また、信号線駆動回路の一部が画素部331と信号線側の入力端子333との間に設けられている場合には、信号線側の入力端子333と基板330上の信号線駆動回路の一部との間に保護回路を設けても良いし、信号線駆動回路の一部と画素部331との間に保護回路を設けても良いし、これらの双方に保護回路を設けても良い。つまり、駆動回路の形態は様々であるため、保護回路はその形態に合わせて設ける数及び場所を定める。

10

#### 【0145】

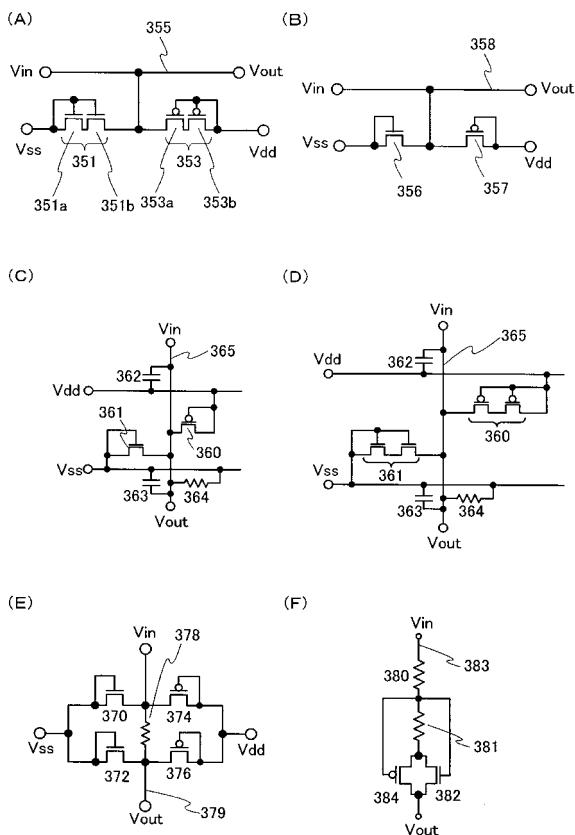

次に、図8における保護回路334～337に用いられる保護回路の具体的な回路構成の例について、図9を参照して説明する。

#### 【0146】

図9(A)に示す保護回路は、複数の薄膜トランジスタを用いた保護ダイオード351、353を有する。保護ダイオード351は、直列に接続されたnチャネル型薄膜トランジスタ351a及びnチャネル型薄膜トランジスタ351bを有している。nチャネル型薄膜トランジスタ351a及びnチャネル型薄膜トランジスタ351bのソース及びドレインの一方は、nチャネル型薄膜トランジスタ351a及びnチャネル型薄膜トランジスタ351bのゲートと接続され、且つ電位Vssに保たれている。nチャネル型薄膜トランジスタ351aのソースまたはドレインの他方はnチャネル型薄膜トランジスタ351bのソース及びドレインの一方に接続されている。nチャネル型薄膜トランジスタ351bのソースまたはドレインの他方は、保護ダイオード353に接続されている。

20

#### 【0147】

保護ダイオード353は、直列に接続されたpチャネル型薄膜トランジスタ353a及びpチャネル型薄膜トランジスタ353bを有している。pチャネル型薄膜トランジスタ353bのソースまたはドレインの一方は、pチャネル型薄膜トランジスタ353a及びpチャネル型薄膜トランジスタ353bのゲートと接続され、且つ電位Vddに保たれている。pチャネル型薄膜トランジスタ353bのソースまたはドレインの他方はpチャネル型薄膜トランジスタ353aのソースまたはドレインの一方に接続されている。pチャネル型薄膜トランジスタ353aのソースまたはドレインの他方は保護ダイオード351に接続されている。

30

#### 【0148】

なお本実施の形態において、各保護ダイオード351、353が有する薄膜トランジスタの数及び極性は、図9(A)に示す構成に限定されない。

#### 【0149】

また、保護ダイオード351、353は順に直列に接続されており、且つ保護ダイオード351と保護ダイオード353の間は、配線355に接続されている。なお、配線355は、表示部において保護対象となる半導体素子に接続されている。

40

#### 【0150】

なお、図9(A)に示す保護回路は図9(B)に示すものに置き換えることも可能である。特に、本実施の形態で用いる保護回路は、耐圧が高いため、図9(B)のような、構成を用いることができる。具体的には、図9(A)の保護ダイオード351の代わりにダイオード接続されたnチャネル型薄膜トランジスタで構成される保護ダイオード356を用い、保護ダイオード353の代わりにダイオード接続されたpチャネル型薄膜トランジスタで構成される保護ダイオード357を用いた構成とすることができる。

#### 【0151】

図9(C)に示す保護回路は、保護ダイオード360、保護ダイオード361、容量素子362、容量素子363、抵抗素子364を有する。抵抗素子364は2端子の抵抗であり、一端には配線365に与えられる電位Vinが、他端には電位Vssが与えられる

50

。抵抗素子 364 は、電位  $V_{in}$  が与えられなくなったときに、配線 365 の電位を電位  $V_{ss}$  に落とすために設けられており、その抵抗値は配線 365 の配線抵抗よりも十分に大きくなるように設定する。保護ダイオード 360 は、ダイオード接続された p チャネル型薄膜トランジスタを用いており、保護ダイオード 361 は、ダイオード接続された n チャネル型薄膜トランジスタを用いている。

#### 【0152】

図 9 (D) に示す保護回路は、保護ダイオード 360 を 2 つの p チャネル型薄膜トランジスタで代用し、保護ダイオード 361 を 2 つの n チャネル型薄膜トランジスタで代用した等価回路図である。

#### 【0153】

なお、図 9 (C) 及び図 9 (D) に示す保護回路は、保護ダイオードとしてダイオード接続された n チャネル型薄膜トランジスタ及び p チャネル型薄膜トランジスタを用いているが、本実施の形態はこの構成に限定されない。

#### 【0154】

また、図 9 (E) に示す保護回路は、保護ダイオード 370、372、374、376 と、抵抗素子 378 と、を有する。抵抗素子 378 は配線 379 と直列に接続されている。保護ダイオード 370、372 は、それぞれダイオード接続された n チャネル型薄膜トランジスタを用いており、保護ダイオード 374、376 は、各々ダイオード接続された p チャネル型薄膜トランジスタを用いている。

#### 【0155】

保護ダイオード 370 及び保護ダイオード 372 それぞれのソース及びドレインの一方は電位  $V_{ss}$  に保持され、ソース及びドレインの他方は配線 379 に接続されている。保護ダイオード 374 及び保護ダイオード 376 それぞれのソース及びドレインの一方は電位  $V_{dd}$  に保持され、ソース及びドレインの他方は配線 379 に接続されている。

#### 【0156】

なお、保護ダイオード 370、372、374、376 は、それぞれ一つの薄膜トランジスタを示したが、極性の同じ薄膜トランジスタを複数直列接続しても良い。

#### 【0157】

ここで、p チャネル型薄膜トランジスタで形成された保護ダイオード 353、357、360、374、376 のソース及びドレインにおいて、 $V_{dd}$  と接続する側をドレインとし、他方をソースとする。また、n チャネル型薄膜トランジスタで形成された保護ダイオード 351、356、361、370、372 のソース及びドレインにおいて、 $V_{ss}$  と接続する側をドレインとし、他方をソースとする。また、p チャネル型薄膜トランジスタで形成された保護ダイオード 353、357、360、374、376 のしきい値電圧を  $V_{th}(p)$  と示し、n チャネル型薄膜トランジスタで形成された保護ダイオード 351、356、361、370、372 のしきい値電圧を  $V_{th}(n)$  と示す。また、 $V_{th}(p) > V_{th}(n)$  である。

#### 【0158】

また、p チャネル型薄膜トランジスタで形成された保護ダイオード 353、357、360、374、376 においては、 $V_{in}$  が  $V_{dd} - V_{th}(p)$  より高い場合に、オンし、 $V_{in}$  から  $V_{dd}$  へ電流が流れる。また、n チャネル型薄膜トランジスタで形成された保護ダイオード 351、356、361、370、372 は、 $V_{in}$  が  $V_{ss} - V_{th}(n)$  より低い場合に、オンし、 $V_{ss}$  から  $V_{in}$  へ電流が注入される。

#### 【0159】

また、n チャネル型薄膜トランジスタで形成された保護ダイオード 351、356、361、370、372 は  $V_{in}$  が  $V_{ss}$  より大きいときに逆バイアスの電圧がかかり、電流が流れにくい。また、p チャネル型薄膜トランジスタで形成された保護ダイオード 353、357、360、374、376 は、 $V_{in}$  が  $V_{dd}$  より小さいときに逆方向バイアスの電圧がかかり、電流が流れにくい。

#### 【0160】

10

20

30

40

50

ここでは、電位  $V_{out}$  が電位  $V_{ss}$  及び電位  $V_{dd}$  の間で動作するような保護回路の動作について説明する。

#### 【0161】

電位  $V_{in}$  が電位  $V_{dd}$  よりも高い場合を考える。電位  $V_{in}$  が電位  $V_{dd}$  よりも高い場合、保護ダイオード 353、357、360、374、376 のゲート電極とソース電極間の電位差  $V_{gs} = V_{dd} - V_{in} < V_{th}(p)$  のときに、当該 p チャネル型薄膜トランジスタはオンする。ここでは、 $V_{in}$  が異常に高い場合を想定しているため、当該 p チャネル型薄膜トランジスタはオンする。このとき、保護ダイオード 351、356、361、370、372 が有する n 型薄膜トランジスタは、オフする。そうすると、保護ダイオード 353、357、360、374、376 を介して、配線 355、358、365、379 の電位が  $V_{dd}$  となる。従って、雑音等により電位  $V_{in}$  が電位  $V_{dd}$  より異常に高くなつたとしても、配線 355、358、365、379 の電位は、電位  $V_{dd}$  よりも高くなることはない。

10

#### 【0162】

一方で、電位  $V_{in}$  が電位  $V_{ss}$  よりも低い場合、保護ダイオード 351、356、361、370、372 のゲート電極とソース電極間の電位差  $V_{gs} = V_{ss} - V_{in} > V_{th}(n)$  のときに、当該 n 型薄膜トランジスタはオンする。ここでは、 $V_{in}$  が異常に低い場合を想定しているため、n 型薄膜トランジスタはオンする。このとき、保護ダイオード 353、357、360、374、376 が有する p 型薄膜トランジスタはオフする。そうすると、保護ダイオード 351、356、361、370、372 を介して、配線 355、358、365、379 の電位が  $V_{ss}$  となる。従って、雑音等により、電位  $V_{in}$  が電位  $V_{ss}$  より異常に低くなつたとしても、配線 355、358、365、379 の電位は、電位  $V_{ss}$  よりも低くなることはない。さらに、容量素子 362、363、は、入力電位  $V_{in}$  が有するパルス状の雑音を鈍らせ、雑音による電位の急峻な変化を緩和する働きをする。

20

#### 【0163】

なお、電位  $V_{in}$  が、 $V_{ss} - V_{th}(n)$  から  $V_{dd} - V_{th}(p)$  の間の場合は、p チャネル型薄膜トランジスタで形成された保護ダイオード 353、357、360、374、376、及び n チャネル型薄膜トランジスタで形成された保護ダイオード 351、356、361、370、372 はオフとなり、電位  $V_{in}$  が  $V_{out}$  へ印加される。

30

#### 【0164】

以上説明したように保護回路を配置することで、配線 355、358、365、379 の電位は、電位  $V_{ss}$  と電位  $V_{dd}$  の間に概ね保たれることになる。従って、配線 355、358、365、379 がこの範囲から大きくはずれる電位となることを防止することができる。つまり、配線 355、358、365、379 が異常に高い電位又は異常に低い電位となることを防止し、当該保護回路の後段の回路を破壊又は劣化から保護することができる。

#### 【0165】

さらに、図 9 (C) 及び (D) に示すように、入力端子に抵抗素子 364 を有する保護回路を設けることで、信号が入力されていないときに、信号が与えられる全ての配線の電位を、一定（ここでは電位  $V_{ss}$ ）に保つことができる。つまり信号が入力されていないときは、配線同士をショートさせることができるショートリングとしての機能も有する。そのため、配線間に生じる電位差に起因する静電破壊を防止することができる。また、抵抗素子 364 の抵抗値が十分に大きいので、信号の入力時には、配線 355、358、365、379 に与えられる信号が電位  $V_{ss}$  まで降下することを防止することができる。

40

#### 【0166】

また、図 9 (F) に示す保護回路は、抵抗素子 380 と、抵抗素子 381 と、n チャネル型薄膜トランジスタ 382 と、p チャネル型薄膜トランジスタ 384 と、を有する。図 9 (F) では、抵抗素子 380 と、抵抗素子 381 と、n チャネル型薄膜トランジスタ 382、p チャネル型薄膜トランジスタ 384 とは、配線 383 に直列に接続されており、

50

抵抗素子 380 は配線 383 に接続されている。配線 383 には電位  $V_{in}$  が与えられ、n チャネル型薄膜トランジスタ 382、p チャネル型薄膜トランジスタ 384 のそれぞれソース及びドレインの一方には電位  $V_{out}$  が与えられる。

いる。

#### 【0167】

図 9 (A) 乃至 (F) に示す保護回路の n チャネル型薄膜トランジスタおよび p チャネル型薄膜トランジスタを、実施の形態 1 に示す n チャネル型薄膜トランジスタ及び p チャネル型薄膜トランジスタで作製することができる。ここでは、代表例として、図 9 (A) に示す保護ダイオード 351 の n チャネル型薄膜トランジスタ及び保護ダイオード 353 の p チャネル型薄膜トランジスタを、図 10 に示す。

10

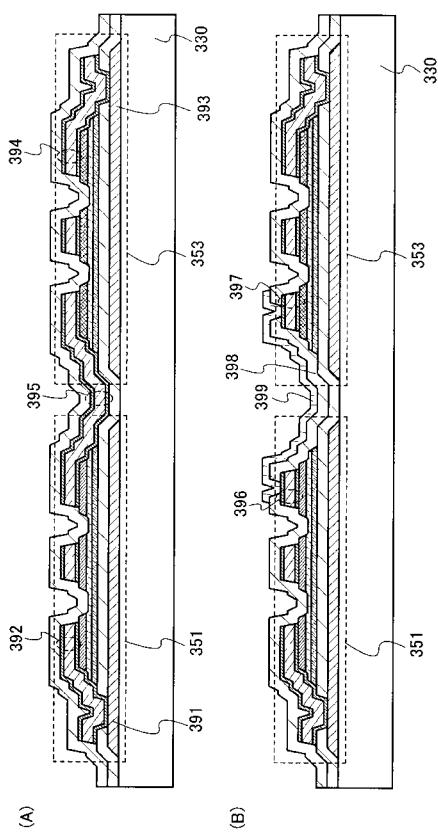

#### 【0168】

図 10 (A) に示すように、基板 330 上に n チャネル型薄膜トランジスタで形成される保護ダイオード 351 及び p チャネル型薄膜トランジスタで形成される保護ダイオード 353 が設けられる。n チャネル型薄膜トランジスタで形成される保護ダイオード 351においては、ゲート電極 391 とソースまたはドレインの一方 392 とが接続される。p チャネル型薄膜トランジスタで形成される保護ダイオード 353 は、ゲート電極 393 とソースまたはドレインの一方 394 とが接続される。また、保護ダイオード 351 及び保護ダイオード 353 は、配線 395 で接続される。

#### 【0169】

なお、図 10 (B) に示すように、保護ダイオード 351 及び保護ダイオード 353 は、ソース及びドレイン 396、397 上に形成される保護絶縁膜 398 のコンタクトホールにおいて、保護ダイオード 351 のソースまたはドレインの一方 396 と、保護ダイオード 353 のソースまたはドレインの一方 397 が、画素電極と同時に形成される配線 399 で接続されてもよい。

20

#### 【0170】

図 9 (A) 乃至 (F) に示す保護回路の n チャネル型薄膜トランジスタおよび p チャネル型薄膜トランジスタを、実施の形態 1 に示す微結晶半導体膜を有する n チャネル型薄膜トランジスタ及び p チャネル型薄膜トランジスタで作製することにより、電位の変動により配線 383 に逆方向バイアスの電流が流れることを防止することができる。また、抵抗素子 380 及び抵抗素子 381 によって、配線 383 の電位の急激な変動を緩和し、半導体素子の劣化又は破壊を防止することができる。

30

#### 【0171】

なお、抵抗素子のみを配線に直列に接続する場合、配線の電位の急激な変動を緩和し、半導体素子の劣化又は破壊を防止することができる。また、保護ダイオードのみを配線に直列に接続する場合、電位の変動により配線に逆方向の電流が流れるのを防ぐことができる。

#### 【0172】

なお、本実施の形態に用いられる保護回路は図 9 に示す構成に限定されるものではなく、同様の働きをする回路構成であれば、適宜設計変更が可能である。

40

#### 【0173】

また、本実施の形態の保護回路が有する保護ダイオードとして、ダイオード接続された薄膜トランジスタが用いられる。ダイオード接続された該薄膜トランジスタとしては、耐圧の高い薄膜トランジスタを用いている。そのため、従来の保護回路では保護回路自体が破壊されうる程度の電圧がかかる場合であっても、本実施の形態の保護回路を有することで、配線が異常に高い電位又は異常に低い電位となることを防止することができる。

#### 【0174】

(実施の形態 5)

次に、本発明の表示装置の一形態である表示パネルの構成について、以下に示す。

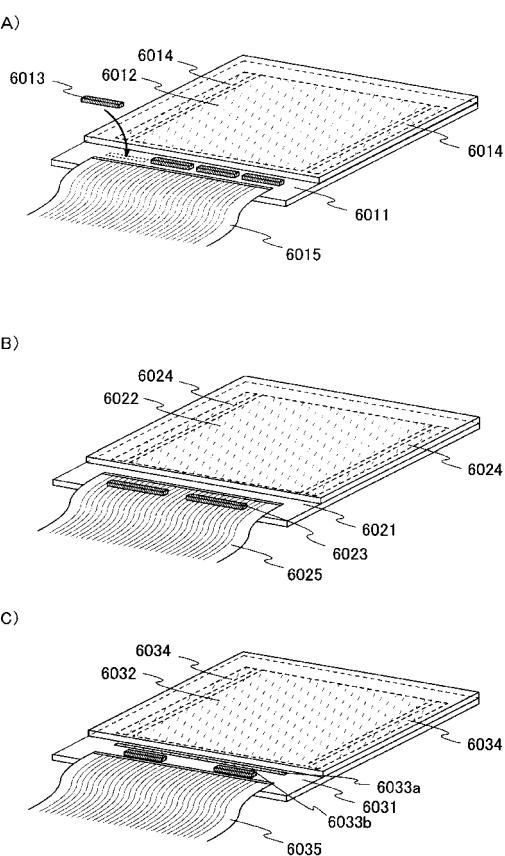

#### 【0175】

図 11 (A) に、信号線駆動回路 6013 のみを別途形成し、基板 6011 上に形成さ

50

れた画素部 6012 と接続している表示パネルの形態を示す。画素部 6012 及び走査線駆動回路 6014 は、微結晶半導体膜をチャネル形成領域に用いた薄膜トランジスタを用いて形成する。微結晶半導体膜をチャネル形成領域に用いた薄膜トランジスタよりも高い移動度が得られるトランジスタで信号線駆動回路を形成することで、走査線駆動回路よりも高い駆動周波数が要求される信号線駆動回路の動作を安定させることができる。なお、信号線駆動回路 6013 は、単結晶の半導体をチャネル形成領域に用いたトランジスタ、多結晶の半導体をチャネル形成領域に用いた薄膜トランジスタ、または SOI をチャネル形成領域に用いたトランジスタであっても良い。画素部 6012 と、信号線駆動回路 6013 と、走査線駆動回路 6014 とに、それぞれ電源の電位、各種信号等が、FPC 6015 を介して供給される。

10

## 【0176】

また、駆動回路を別途形成する場合、必ずしも駆動回路が形成された基板を、画素部が形成された基板上に貼り合わせる必要はなく、例えば FPC 上に貼り合わせるようにしても良い。図 11 (B) に、信号線駆動回路 6023 のみを別途形成し、基板 6021 上に形成された画素部 6022 及び走査線駆動回路 6024 と接続している表示パネルの形態を示す。画素部 6022 及び走査線駆動回路 6024 は、微結晶半導体膜をチャネル形成領域に用いた薄膜トランジスタを用いて形成する。信号線駆動回路 6023 は、FPC 6025 を介して画素部 6022 と接続されている。画素部 6022 と、信号線駆動回路 6023 と、走査線駆動回路 6024 とに、それぞれ電源の電位、各種信号等が、FPC 6025 を介して供給される。

20

## 【0177】

また、信号線駆動回路の一部または走査線駆動回路の一部のみを、微結晶半導体膜をチャネル形成領域に用いた薄膜トランジスタを用いて画素部と同じ基板上に形成し、残りを別途形成して画素部と電気的に接続するようにしても良い。図 11 (C) に、信号線駆動回路が有するアナログスイッチ 6033a を、画素部 6032、走査線駆動回路 6034 と同じ基板 6031 上に形成し、信号線駆動回路が有するシフトレジスタ 6033b を別途異なる基板に形成して貼り合わせる表示パネルの形態を示す。画素部 6032 及び走査線駆動回路 6034 は、微結晶半導体膜をチャネル形成領域に用いた薄膜トランジスタを用いて形成する。信号線駆動回路が有するシフトレジスタ 6033b は、FPC 6035 を介して画素部 6032 と接続されている。画素部 6032 と、信号線駆動回路と、走査線駆動回路 6034 とに、それぞれ電源の電位、各種信号等が、FPC 6035 を介して供給される。

30

## 【0178】

図 11 に示すように、本実施の形態の表示パネルは、駆動回路の一部または全部を、画素部と同じ基板上に、微結晶半導体膜をチャネル形成領域に用いた逆スタガ型の薄膜トランジスタを用いて形成することができる。

## 【0179】

なお、別途形成した基板の接続方法は、特に限定されるものではなく、公知の COG 方法、ワイヤボンディング方法、或いは TAB 方法などを用いることができる。また接続する位置は、電気的な接続が可能であるならば、図 11 に示した位置に限定されない。また、コントローラ、CPU、メモリ等を別途形成し、接続するようにしても良い。

40

## 【0180】

(実施の形態 6) 本発明により得られる表示装置等をアクティブマトリクス型表示装置モジュールに用いることができる。即ち、それらを表示部に組み込んだ電子機器全てに本発明を実施できる。

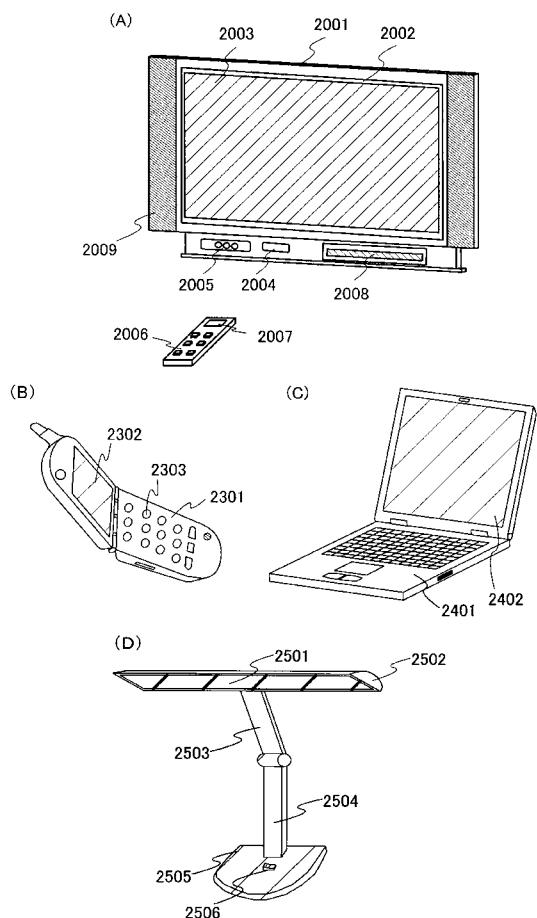

## 【0181】

その様な電子機器としては、ビデオカメラ、デジタルカメラ等のカメラ、ヘッドマウントディスプレイ(ゴーグル型ディスプレイ)、カーナビゲーション、プロジェクタ、カーステレオ、パーソナルコンピュータ、携帯情報端末(モバイルコンピュータ、携帯電話または電子書籍等)などが挙げられる。それらの一例を図 12 に示す。

50

## 【0182】

図12(A)はテレビジョン装置である。表示モジュールを、図12(A)に示すように、筐体に組みこんで、テレビジョン装置を完成させることができる。FPCまで取り付けられた表示パネルのことを表示モジュールとも呼ぶ。表示モジュールにより主画面2003が形成され、その他付属設備としてスピーカ部2009、操作スイッチなどが備えられている。このように、テレビジョン装置を完成させることができる。

## 【0183】

図12(A)に示すように、筐体2001に表示素子を利用した表示用パネル2002が組みこまれ、受信機2005により一般的なテレビ放送の受信をはじめ、モデム2004を介して有線又は無線による通信ネットワークに接続することにより一方向(送信者から受信者)又は双方向(送信者と受信者間、又は受信者間同士)の情報通信をすることもできる。テレビジョン装置の操作は、筐体に組みこまれたスイッチ又は別体のリモコン操作機2006により行うことが可能であり、このリモコン操作機2006にも出力する情報を表示する表示部2007が設けられていても良い。

10

## 【0184】

また、テレビジョン装置にも、主画面2003の他にサブ画面2008を第2の表示用パネルで形成し、チャネルや音量などを表示する構成が付加されていても良い。この構成において、主画面2003を視野角の優れた液晶表示パネルで形成し、サブ画面を低消費電力で表示可能な発光表示パネルで形成しても良い。また、低消費電力化を優先させるためには、主画面2003を発光表示パネルで形成し、サブ画面を発光表示パネルで形成し、サブ画面は点滅可能とする構成としても良い。

20

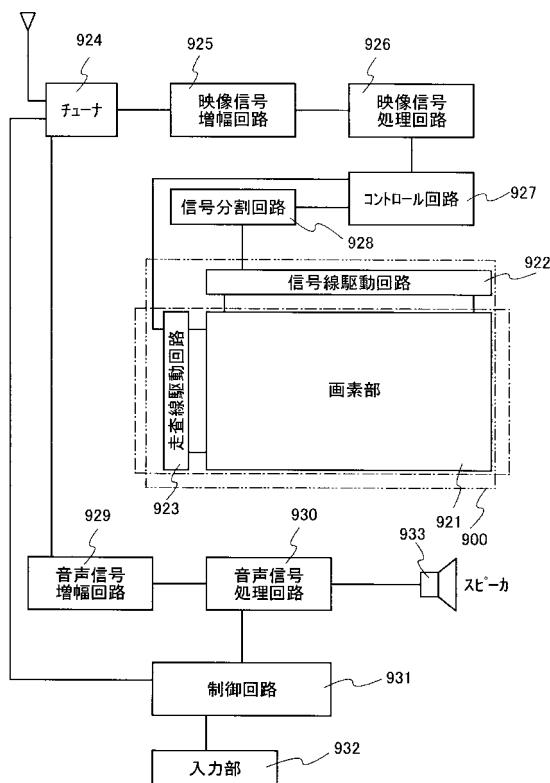

## 【0185】

図13はテレビ装置の主要な構成を示すブロック図を示している。表示パネル900には、画素部921が形成されている。信号線駆動回路922と走査線駆動回路923は、表示パネル900にCOG方式により実装されていても良い。

## 【0186】

その他の外部回路の構成として、映像信号の入力側では、チューナ924で受信した信号のうち、映像信号を增幅する映像信号增幅回路925と、そこから出力される信号を赤、緑、青の各色に対応した色信号に変換する映像信号処理回路926と、その映像信号をドライバICの入力仕様に変換するためのコントロール回路927などを有している。コントロール回路927は、走査線側と信号線側にそれぞれ信号が出力する。デジタル駆動する場合には、信号線側に信号分割回路928を設け、入力デジタル信号をm個に分割して供給する構成としても良い。

30

## 【0187】

チューナ924で受信した信号のうち、音声信号は、音声信号增幅回路929に送られ、その出力は音声信号処理回路930を経てスピーカ933に供給される。制御回路931は受信局(受信周波数)や音量の制御情報を入力部932から受け、チューナ924や音声信号処理回路930に信号を送出する。

## 【0188】

勿論、本発明はテレビジョン装置に限定されず、パーソナルコンピュータのモニタをはじめ、鉄道の駅や空港などにおける情報表示盤や、街頭における広告表示盤など大面積の表示媒体としても様々な用途に適用することができる。

40

## 【0189】

図12(B)は携帯電話機2301の一例を示している。この携帯電話機2301は、表示部2302、操作部2303などを含んで構成されている。表示部2302においては、上記実施の形態で説明した表示装置を適用することで、量産性を高めることができる。

## 【0190】

また、図12(C)に示す携帯型のコンピュータは、本体2401、表示部2402等を含んでいる。表示部2402に、上記実施の形態に示す表示装置を適用することにより、量産性を高めることができる。

50

## 【0191】

図12(D)は卓上照明器具であり、照明部2501、傘2502、可変アーム2503、支柱2504、台2505、電源2506を含む。本発明の発光表示装置を照明部2501に用いることにより作製される。なお、照明器具には天井固定型の照明器具または壁掛け型の照明器具なども含まれる。上記実施の形態に示す表示装置を適用することにより、量産性を高めることができ、安価な卓上照明器具を提供することができる。

## 【実施例1】

## 【0192】

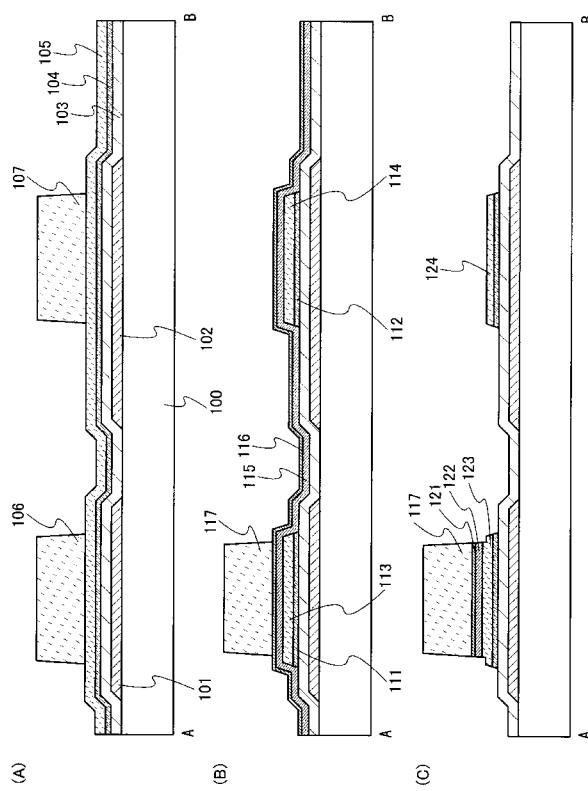

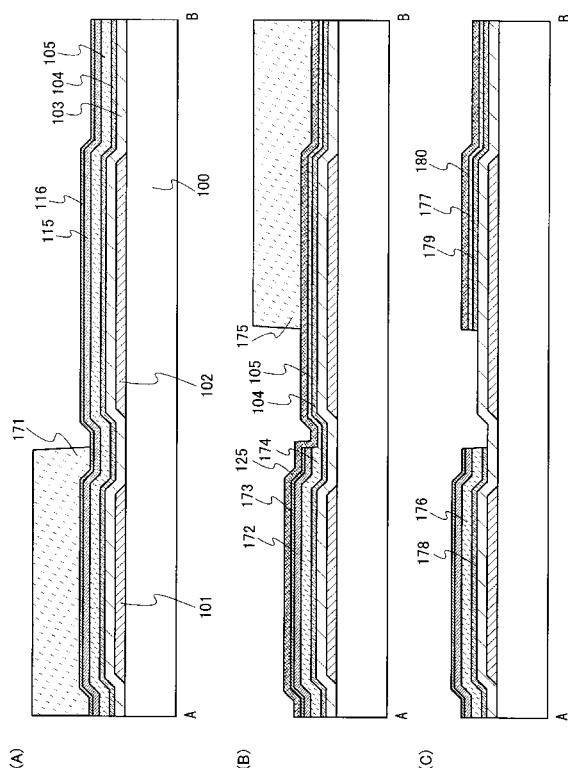

本実施例では、実施の形態1に示す画素を作製する工程を図14乃至図17を用いて説明する。なお、図14乃至図16は、薄膜トランジスタの作製工程を示す断面図であり、図17は一画素における薄膜トランジスタ及び画素電極の接続領域の上面図である。

10

## 【0193】

図14(A)に示すように、基板100上にゲート電極101、102を形成する。基板100は、ガラス基板を用いる。

## 【0194】

厚さ150nmのアルミニネオジム合金膜、及び厚さ50~150nmのモリブデン膜をそれぞれスパッタリング法により順に積層し、基板100上に導電膜を形成する。次に、第1のフォトマスクを用いて形成したレジストマスクを用いて形成された導電膜をエッチングしてゲート電極101、102を形成する。

20

## 【0195】

次に、ゲート電極101、102上に、ゲート絶縁膜103を形成する。ここでは、ゲート絶縁膜103として厚さ50~150nmの窒化シリコン膜、厚さ50~150nmの酸化窒化シリコン膜、厚さ1~5nmの窒化シリコン膜をそれぞれプラズマCVD法により成膜する。

## 【0196】

次に、ゲート絶縁膜103上に、20nm~500nm(好ましくは100nm~250nm)の厚さの微結晶シリコン膜104を形成する。微結晶シリコン膜104は、図3に示すような、高真空排気が可能な排気手段409を有するプラズマCVD装置を用いて成膜することで、膜中の酸素濃度が $1 \times 10^{-6}$ atoms/cm<sup>3</sup>以下である微結晶シリコン膜を形成することができる。ここでは、シランガスと、シランガスの流量の10倍以上2000倍以下、好ましくは12倍以上1000倍以下、好ましくは50倍以上200倍以下の流量の水素ガスを用いたプラズマCVD法により微結晶シリコン膜を形成する。なお、このときの基板100の温度を、基板の加熱温度は100~300、好ましくは120~220とすることで、ゲート絶縁膜103及び微結晶シリコン膜104の界面における微結晶シリコンの成長を促進させることができる。

30

## 【0197】

次に、微結晶シリコン膜104上に、厚さ50~200nmのバッファ層105を形成する。バッファ層105としては、非晶質シリコン膜を用いて形成する。バッファ層105に形成される非晶質シリコン膜は、シランガスの流量の1倍以上10倍未満、更に好ましくは1倍以上5倍以下の流量の水素を用いたプラズマCVD法により形成する。なお、バッファ層105に形成される非晶質シリコン膜を微結晶シリコン膜104と同様に高真空排気が可能な排気手段409を有するプラズマCVD装置を用いて成膜することで、欠陥の少ない非晶質シリコン膜が形成されるため、高抵抗のバッファ層を形成することができ、薄膜トランジスタのオフ電流を低減させることができる。

40

## 【0198】

なお、バッファ層105を300~400の温度にて成膜することが好ましい。この成膜処理により水素が微結晶シリコン膜104に供給され、微結晶シリコン膜104を水素化したのと同等の効果が得られる。すなわち、微結晶シリコン膜104上にバッファ層105を堆積することにより、微結晶シリコン膜104に水素を拡散させて、ダングリングボンドの終端をすることができる。

50

## 【0199】

次に、バッファ層105上にレジストを塗布した後、第2のフォトマスクを用いたフォトリソグラフィ工程によりレジストマスク106、107を形成する。

## 【0200】

次に、図14(B)に示すように、レジストマスク106、107を用いて微結晶シリコン膜104及びバッファ層105を選択的にエッチングして微結晶シリコン膜111、112、バッファ層113、114を形成する。ここでは、ドライエッチング法により微結晶シリコン膜104及びバッファ層105を選択的にエッチングする。この後、レジストマスク106、107を除去する。

## 【0201】

次に、厚さ10~100nm、好ましくは40~80nmのn型半導体膜115を形成する。n型半導体膜115は、0.2~1%のフォスフィンガス、シランガス、及び水素を用いたプラズマCVD法により、リンを含む微結晶シリコン膜で形成する。n型半導体膜115も図3に示すプラズマCVD装置によって形成してもよい。

10

## 【0202】

次に、n型半導体膜115上に厚さ20~70nmの導電膜116を形成する。導電膜116は、後に形成されるp型半導体膜に対してエッチングに対する高い選択比を得ることが可能な導電材料を用いて形成する。ここでは、スパッタリング法により厚さ10~60nmのモリブデン膜を形成する。

20

## 【0203】

次に、第3のフォトマスクを用いたフォトリソグラフィ工程により、ゲート電極101と重畳する導電膜116上にレジストマスク117を形成する。

## 【0204】

次に、図14(C)に示すように、レジストマスク117を用いて、導電膜116及びn型半導体膜115を選択的にエッチングして、導電膜121、n型半導体膜122を形成する。このとき、バッファ層113の一部もエッチングされ、端部に段差を有するバッファ層123となる。当該工程においては、ゲート電極102上に形成される導電膜116及びn型半導体膜115をエッチングする。この際、エッチング工程の終点の確認は、エッチング装置内の発光強度変化を測定することによって判断する。即ち、n型半導体膜115をエッチングしたときの活性種と、バッファ層114をエッチングしたときの活性種によって、プラズマの発光強度が異なる。この発光強度の変化を測定することで、エッチングの終点を検出することができる。従って、バッファ層113の一部、およびバッファ層114の一部がエッチングされるに留まる。ここで、ゲート電極102上に形成されたバッファ層をバッファ層124と示す。こののち、レジストマスク117を除去する。

30

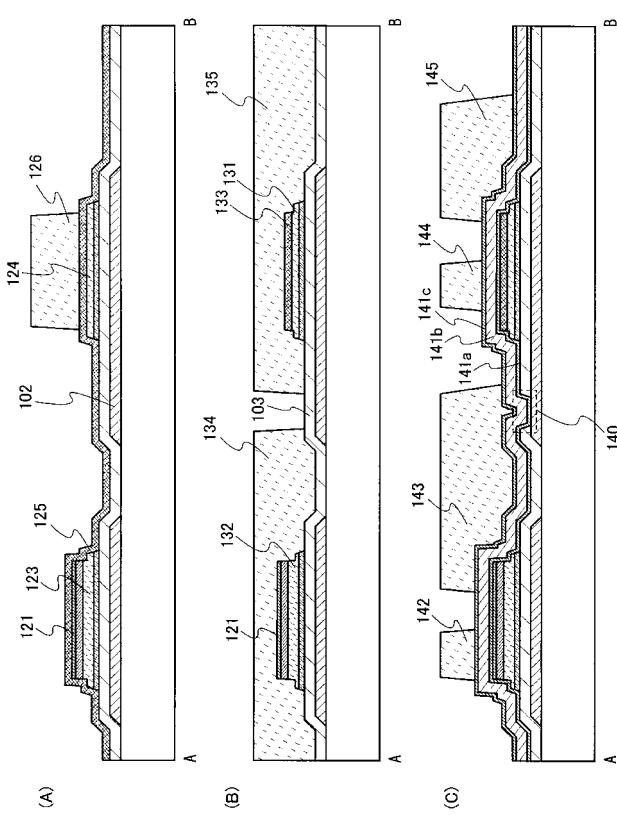

## 【0205】

次に、図15(A)に示すように、10~100nm、好ましくは40~80nmのp型半導体膜125を形成する。p型半導体膜125は、1~10%のテトラメチルボロン、シラン、水素、及び希ガス(代表的にはヘリウムまたはネオン)を用いたプラズマCVD法により、ボロンを含む微結晶シリコン膜で形成する。p型半導体膜125も図3に示すプラズマCVD装置によって形成してもよい。

40

## 【0206】

次に、p型半導体膜125上にレジストを塗布した後、第4のフォトマスクを用いたフォトリソグラフィ工程により、ゲート電極102と重畳するp型半導体膜125上にレジストマスク126を形成する。

## 【0207】

次に、図15(B)に示すように、レジストマスク126を用いて、p型半導体膜125を選択的にエッチングして、p型半導体膜133を形成する。このとき、バッファ層124の一部もエッチングされ、端部に段差を有するバッファ層131となる。また、導電膜121上においては、p型半導体膜が選択的にエッチングされる。しかしながら、導電膜121に覆われていないバッファ層123の端部は更にエッチングされ、端部に段差を有

50

するバッファ層 132 となる。

【0208】

次に、第5のフォトマスクを用いたフォトリソグラフィ工程により、ゲート電極 102 と重畳するゲート絶縁膜 103 の一部をエッチングするためのレジストマスク 134、135 を形成する。

【0209】

次に、図 15 (C) に示すように、ゲート絶縁膜 103 の一部をエッチングしてコンタクトホール 140 を形成する。

【0210】

次に、導電膜 121、p 型半導体膜 133、ゲート絶縁膜 103、及びゲート電極 102 の露出部上に、導電膜 141a ~ 141c を積層形成する。導電膜 141a として厚さ 30 ~ 60 nm のモリブデン膜、導電膜 141b として厚さ 150 ~ 300 nm のアルミニウム膜、導電膜 141c として厚さ 50 nm ~ 100 nm のモリブデン膜をそれぞれスパッタリング法により形成する。

【0211】

次に、導電膜 141c 上にレジストを塗布した後、第6のフォトマスクを用いたフォトリソグラフィ工程により、導電膜 141a ~ 141c から配線を形成するためのレジストマスク 142 ~ 145 を形成する。

【0212】

次に、図 16 (A) に示すように、レジストマスク 142 ~ 145 を用いて導電膜 141a ~ 141c、及び導電膜 121 をエッチングする。ここでは、導電膜 141a ~ 141c をウエットエッチング法により等方的にエッチングするため、レジストマスク 142 ~ 145 より面積の狭い配線 151a ~ 151d、配線 152a ~ 152d、配線 153a ~ 153c、配線 154a ~ 154c を形成する。

【0213】

次に、レジストマスク 142 ~ 145 を用いて、n 型半導体膜 122 及び p 型半導体膜 133 をエッチングして一対の n 型半導体膜 155、156、及び一対の p 型半導体膜 157、158 を形成する。ここでは、レジストマスク 142 ~ 145 を用いてドライエッチング法により異方的にエッチングするため、配線 151a ~ 151d、配線 152a ~ 152d、配線 153a ~ 153c、配線 154a ~ 154c と、一対の n 型半導体膜 155、156、一対の p 型半導体膜 157、158 の端部の位置がずれており、一対の n 型半導体膜 155、156、及び一対の p 型半導体膜 157、158 の端部が、配線 151a ~ 151d、配線 152a ~ 152d、配線 153a ~ 153c、配線 154a ~ 154c より外側に突出している。

【0214】

なお、当該エッチング工程において、バッファ層 132、131 の一部がオーバエッチングされることで、完全に分離された一対の n 型半導体膜 155、156、及び一対の p 型半導体膜 157、158 を形成することができる。一部オーバエッチングされ、凹部 (n 型半導体膜または p 型半導体膜と重なる領域よりも膜厚の薄いバッファ層の領域) が形成されたバッファ層をバッファ層 159、160 と示す。ソース領域及びドレイン領域として機能する一対の n 型半導体膜 155、156、及び一対の p 型半導体膜 157、158 の形成工程と、バッファ層の凹部とを同一工程で形成することができる。バッファ層の凹部の深さをバッファ層の一一番膜厚の厚い領域の 1/2 ~ 1/3 とすることで、ソース領域及びドレイン領域の距離を離すことが可能であるため、ソース領域及びドレイン領域の間でのリーク電流を低減することができる。この後、レジストマスク 142 ~ 145 を除去する。

【0215】

なお、図 16 (A) は、図 17 (A) の A - B の断面図に相当する。配線 151c、153c はそれぞれ配線 152c、154c を囲む形状 (具体的には、U 字型または C 字型) である。このため、キャリアが移動する領域の面積を増加させることができるために、

10

20

30

40

50

電流量を増やすことが可能であり、薄膜トランジスタの面積を縮小することができる。また、ゲート電極より狭い上面面積で微結晶シリコン膜 111、112、バッファ層 113、114 が形成され、且つゲート電極上において、微結晶半導体膜、ソース電極及びドレイン電極が重畳されているため、微結晶シリコン膜 111、112、バッファ層 113、114 においてゲート電極の凹凸の影響が少なく、被覆率の低減及びリーク電流の発生を抑制することができる。

#### 【0216】

以上の工程により、チャネルエッチ型の第 1 の薄膜トランジスタ 155a 及び第 2 の薄膜トランジスタ 155b を形成することができる。

#### 【0217】

次に、図 16 (B) に示すように、配線 151a ~ 151d、配線 152a ~ 152d、配線 153a ~ 153c、配線 154a ~ 154c、一対の n 型半導体膜 155、156 及び一対の p 型半導体膜 157、158、バッファ層 159、160、微結晶シリコン膜 111、112、及びゲート絶縁膜 103 上に保護絶縁膜 161 を形成する。保護絶縁膜 161 は、プラズマ CVD 法により厚さ 50 ~ 200 nm の窒化シリコン膜を形成する。

#### 【0218】

次に、保護絶縁膜 161 上にレジストを塗布した後、第 7 のフォトマスクを用いたフォトリソグラフィ工程により、保護絶縁膜 161 にレジストマスク 162、163 形成する。

#### 【0219】

次に、図 16 (C) に示すように、レジストマスク 162、163 を用いて保護絶縁膜 161 の一部をエッチングしてコンタクトホール 164 を形成する。

#### 【0220】

次に、当該コンタクトホールにおいて配線 154c に接する画素電極 165 を形成する。ここでは、スパッタリング法により厚さ 50 ~ 100 nm の ITO を成膜する。次に、第 8 のフォトマスクを用いたフォトリソグラフィ工程により、ITO 上にレジストマスクを形成した後、ITO を選択的にエッチングして画素電極 165 を形成する。

#### 【0221】

なお、図 16 (C) は、図 17 (B) の A - B の断面図に相当する。

#### 【0222】

以上により表示装置に用いることが可能な素子基板を形成することができる。

#### 【実施例 2】

#### 【0223】

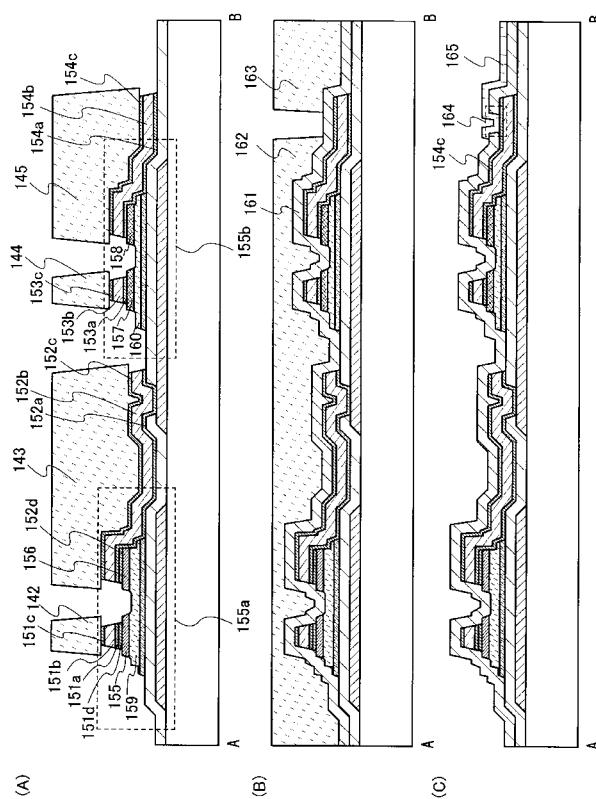

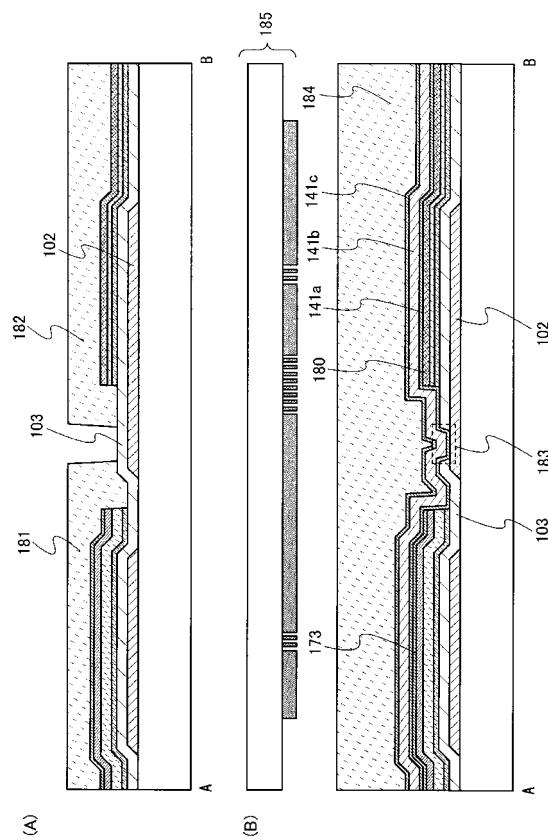

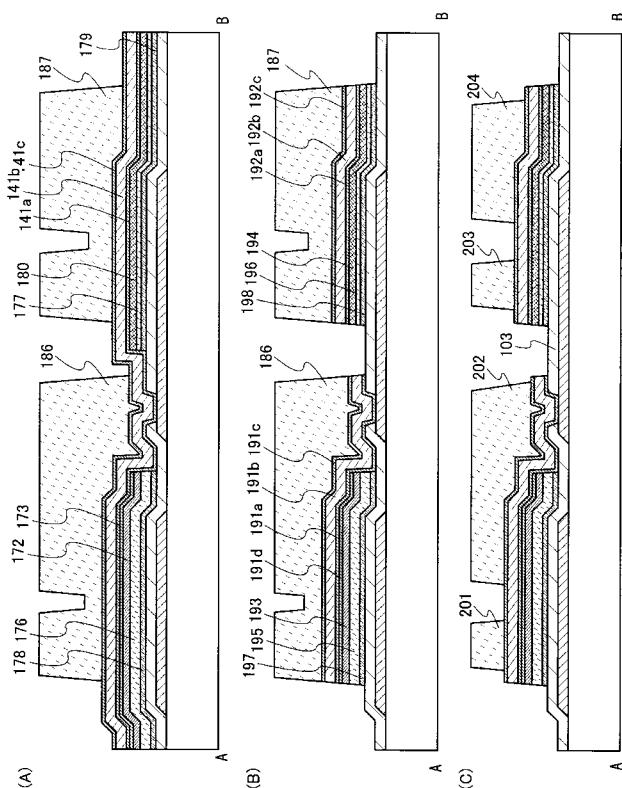

本実施例では、上記実施例とは異なる薄膜トランジスタの作製方法について、図 18 乃至図 23 を用いて説明する。ここでは、上記実施例よりフォトマスク数を削減することができるプロセスを用いて薄膜トランジスタを作製する工程について示す。

#### 【0224】

図 14 (A) と同様に、図 18 (A) に示すように基板 100 上に導電膜を形成し、導電膜上にレジストを塗布し、第 1 のフォトマスクを用いたフォトリソグラフィ工程により形成したレジストマスクを用いて導電膜の一部をエッチングして、ゲート電極 101、102 を形成する。次に、ゲート電極 101、102 上に、ゲート絶縁膜 103、微結晶シリコン膜 104、バッファ層 105 を順に形成する。

#### 【0225】

次に、バッファ層 105 上に n 型半導体膜 115 を形成し、n 型半導体膜 115 上に導電膜 116 を形成する。

#### 【0226】

次に、導電膜 116 上にレジストを塗布した後、第 2 のフォトマスクを用いたフォトリソグラフィ工程により、導電膜 116 にレジストマスク 171 を形成する。

#### 【0227】

次に、図 18 (B) に示すように、導電膜 116、及び n 型半導体膜 115 を選択的に工

10

20

30

40

50

ツチングして、n型半導体膜172、導電膜173を形成する。このとき、レジストマスク171に覆われていないバッファ層105の一部もエッチングされる。導電膜173に覆われる領域は、導電膜173に覆われない領域と比較して厚いバッファ層174となる。この際、エッチング工程の終点の検出は、図15(B)に示すエッチングと同様に、エッチング装置内の発光強度変化を測定することによって判断する。

## 【0228】

次に、10~100nm、好ましくは40~80nmのp型半導体膜125を形成する。

## 【0229】

次に、第3のフォトマスクを用いたフォトリソグラフィ工程により、ゲート電極102と重畠するp型半導体膜125上にレジストマスク175を形成する。

10

## 【0230】

次に、図18(C)に示すように、レジストマスク175を用いて、p型半導体膜125を選択的にエッチングして、p型半導体膜180を形成する。このとき、バッファ層174の一部もエッチングされ、バッファ層176、177となる。また、微結晶シリコン膜104もエッチングされ、微結晶シリコン膜178、179となる。

## 【0231】

次に、レジストを塗布した後、第4のフォトマスクを用いたフォトリソグラフィ工程により、図19(A)に示すように、ゲート電極102と重畠するゲート絶縁膜103の一部をエッチングするためのレジストマスク181、182を形成する。

20

## 【0232】

次に、図19(B)に示すように、ゲート絶縁膜103の一部をエッチングしてコンタクトホール183を形成する。

## 【0233】

次に、導電膜173、p型半導体膜180、ゲート絶縁膜103、及びゲート電極102の露出部上に、図15(C)と同様に導電膜141a~141cを形成する。

## 【0234】

次に、導電膜141c上にレジスト184を塗布する。

## 【0235】

次に、第4のフォトマスクとして多階調マスク185を用いて、レジスト184に光を照射して、レジスト184を露光する。

30

## 【0236】

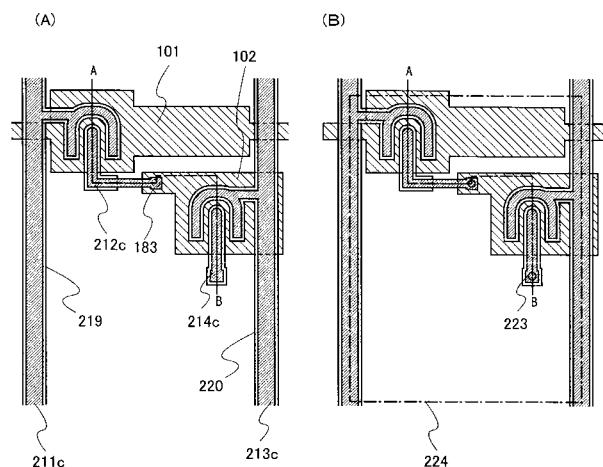

ここで、多階調マスク185を用いた露光について、図23を用いて説明する。

## 【0237】

多階調マスクとは、露光部分、中間露光部分、及び未露光部分に3つの露光レベルを行うことが可能なマスクであり、一度の露光及び現像工程により、複数(代表的には二種類)の厚さの領域を有するレジストマスクを形成することが可能である。このため、多階調マスクを用いることで、フォトマスクの枚数を削減することが可能である。

## 【0238】

多階調マスクの代表例としては、図23(A)に示すようなグレートーンマスク185a、図23(C)に示すようなハーフトーンマスク185bがある。

40

## 【0239】

図23(A)に示すように、グレートーンマスク185aは、透光性を有する基板231及びその上に形成される遮光部232並びに回折格子233で構成される。遮光部232においては、光の透過率が0%である。一方、回折格子233はスリット、ドット、メッシュ等の光透過部の間隔を、露光に用いる光の解像度限界以下の間隔とすることにより、光の透過率を制御することができる。なお、回折格子233は、周期的なスリット、ドット、メッシュ、または非周期的なスリット、ドット、メッシュどちらも用いることができる。

## 【0240】

透光性を有する基板231としては、石英等を用いることができる。遮光部232及び回

50

折格子 233 は、クロムや酸化クロム等の光を吸収する遮光材料を用いて形成することができる。

【0241】

グレートーンマスク 185a に露光光を照射した場合、図 23(B) に示すように、遮光部 232 においては、光透過率 234 は 0 % であり、遮光部 232 及び回折格子 233 が設けられていない領域では光透過率 234 は 100 % である。また、回折格子 233 においては、10 ~ 70 % の範囲で調整可能である。回折格子 233 における光の透過率の調整は、回折格子 233 のスリット、ドット、またはメッシュの間隔及びピッチの調整により可能である。

【0242】

図 23(C) に示すように、ハーフトーンマスク 185b は、透光性を有する基板 231 及びその上に形成される半透過部 235 並びに遮光部 236 で構成される。半透過部 235 は、MoSiN、MoSi、MoSiO、MoSiON、CrSi などを用いることができる。遮光部 236 は、クロムや酸化クロム等の光を吸収する遮光材料を用いて形成することができる。

【0243】

ハーフトーンマスク 185b に露光光を照射した場合、図 23(D) に示すように、遮光部 236 においては、光透過率 237 は 0 % であり、遮光部 236 及び半透過部 235 が設けられていない領域では光透過率 237 は 100 % である。また、半透過部 235 においては、10 ~ 70 % の範囲で調整可能である。半透過部 235 に於ける光の透過率の調整は、半透過部 235 の材料により可能である。

【0244】

多階調マスクを用いて露光した後、現像することで、図 20(A) に示すように、膜厚の異なる領域を有するレジストマスク 186、187 を形成することができる。

【0245】

次に、レジストマスク 186、187 により、微結晶シリコン膜 178、179、バッファ層 176、177、n 型半導体膜 172、導電膜 173、p 型半導体膜 180、及び導電膜 141a ~ 141c をエッティングし、二つの薄膜トランジスタを分離する。この結果、図 20(B) に示すような、微結晶シリコン膜 197、198、バッファ層 195、196、n 型半導体膜 193、p 型半導体膜 194、及び導電膜 191a ~ 191d、192a ~ 192c を形成することができる。

【0246】

次に、レジストマスク 186、187 をアッシングする。この結果、レジストの面積が縮小し、厚さが薄くなる。このとき、膜厚の薄い領域のレジスト（ゲート電極 101、102 の一部と重畳する領域）は除去され、図 20(C) に示すように、分離されたレジストマスク 201 ~ 204 を形成することができる。

【0247】

次に、レジストマスク 201 ~ 204 を用いて、導電膜 191a ~ 191d、192a ~ 192c をエッティングし分離する。この結果、図 21(A) に示すような、一対の配線 211a ~ 211d、212a ~ 212d、213a ~ 213c、214a ~ 214c を形成することができる。レジストマスク 201 ~ 204 を用いて導電膜 191a ~ 191d、192a ~ 192c の端部が等方的にエッティングされる。この結果、レジストマスク 201 ~ 204 より面積の小さい配線 211a ~ 211d、212a ~ 212d、213a ~ 213c、214a ~ 214c を形成することができる。

【0248】

次に、レジストマスク 201 ~ 204 を用いて、n 型半導体膜 193、p 型半導体膜 194、をエッティングして、一対の n 型半導体膜 215、216、一対の p 型半導体膜 217、218 を形成する。ここでは、ドライエッティング法により異方的に n 型半導体膜 193 及び p 型半導体膜 194 をエッティングするため、配線 211a ~ 211d、212a ~

10

20

30

40

50

212d、213a～213c、214a～214cと、一対のn型半導体膜215、216、一対のp型半導体膜217、218の端部の位置がずれており、一対のn型半導体膜215、216、一対のp型半導体膜217、218の端部が、配線211a～211d、212a～212d、213a～213c、214a～214cより外側に突出している。

#### 【0249】

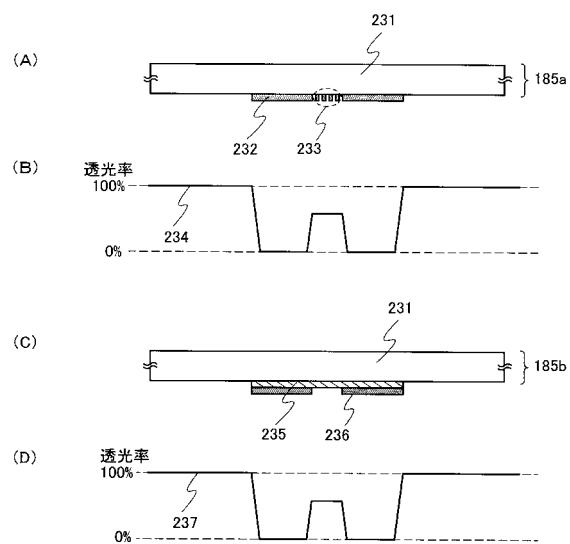

なお、当該エッティング工程において、バッファ層176、177の一部がオーバエッティングされることで、完全に分離された一対のn型半導体膜215、216、一対のp型半導体膜217、218を形成することができる。一部オーバエッティングされ、凹部が形成されたバッファ層をバッファ層219、220と示す。ソース領域及びドレイン領域として機能する一対のn型半導体膜215、216、一対のp型半導体膜217、218の形成工程と、バッファ層の凹部とを同一工程で形成することができる。バッファ層の凹部の深さをバッファ層の一番膜厚の厚い領域の1/2～1/3とすることで、ソース領域及びドレイン領域の距離を離すことが可能であるため、ソース領域及びドレイン領域の間でのリーク電流を低減することができる。この後、レジストマスク201～204を除去する。なお、図21(B)は、図22(A)のA-Bの断面図に相当する。

#### 【0250】

以上の工程により、チャネルエッチ型の薄膜トランジスタ221a、221bを形成することができる。

#### 【0251】

次に、図21(B)に示すように、配線211a～211d、212a～212d、213a～213c、214a～214c、一対のn型半導体膜215、216、一対のp型半導体膜217、218、バッファ層219、220、微結晶シリコン膜197、198、及びゲート絶縁膜103上に保護絶縁膜161を形成する。

#### 【0252】

次に、保護絶縁膜161上にレジストを塗布した後、第5のフォトマスクを用いたフォトリソグラフィ工程により、保護絶縁膜161にレジストマスク222、223形成する。

#### 【0253】

次に、図21(C)に示すように、レジストマスク222を用いて保護絶縁膜161の一部をエッティングしてコンタクトホール223を形成する。

#### 【0254】

次に、当該コンタクトホールにおいて配線214cに接する画素電極224を形成する。ここでは、スパッタリング法により厚さ50～100nmのアルミニウム膜を成膜する。

#### 【0255】

次に、第6のフォトマスクを用いたフォトリソグラフィ工程により、アルミニウム膜上にレジストマスクを形成した後、アルミニウム膜を選択的にエッティングして画素電極224を形成する。

#### 【0256】

なお、図21(C)は、図22(B)のA-Bの断面図に相当する。

#### 【0257】

以上により表示装置に用いることが可能な素子基板を形成することができる。

#### 【図面の簡単な説明】

#### 【0258】

【図1】本発明の表示装置の構成を説明する上面図、等価回路図、及び断面図である。

#### 【図2】本発明の表示装置の構成を説明する断面図である。

#### 【図3】プラズマCVD装置の反応室の構成を説明する図である。

#### 【図4】本発明の表示装置の作製方法を説明するタイムチャート図である。

【図5】複数の反応室を備えたマルチ・チャンバ・プラズマCVD装置の構成を示す図である。

#### 【図6】本発明の表示装置の構成を説明する断面図である。

10

20

30

40

50

【図 7】本発明の表示装置の動作を説明する図である。

【図 8】本発明の表示装置の構成を説明する上面図である。

【図 9】本発明の表示装置に適用可能な保護回路の構成を説明する等価回路図である。

【図 10】本発明の表示装置に適用可能な保護回路の構成を説明する断面図である。

【図 11】本発明の表示パネルの構成を説明する斜視図である。

【図 12】本発明の表示装置を用いた電子機器を説明する斜視図である。

【図 13】本発明の表示装置を用いた電子機器を説明する図である。

【図 14】本発明の表示装置の作製方法を説明する断面図である。

【図 15】本発明の表示装置の作製方法を説明する断面図である。

【図 16】本発明の表示装置の作製方法を説明する断面図である。

【図 17】本発明の表示装置の作製方法を説明する上面図である。

【図 18】本発明の表示装置の作製方法を説明する断面図である。

【図 19】本発明の表示装置の作製方法を説明する断面図である。

【図 20】本発明の表示装置の作製方法を説明する断面図である。

【図 21】本発明の表示装置の作製方法を説明する断面図である。

【図 22】本発明の表示装置の作製方法を説明する上面図である。

【図 23】本発明に適用可能な多階調マスクを説明する図である。

【図 24】複数の反応室を備えたマルチ・チャンバ・プラズマ CVD 装置の構成を示す図である。

10

【図 1】

【図 2】

【 図 3 】

【 図 4 】

【 义 5 】

【 図 6 】

【図7】

【図8】

【図9】

【図10】

【図11】

【 図 1 2 】

【 図 1 3 】

【 図 1 4 】

【 図 1 5 】

【図16】

【図17】

【図18】

【図19】

【 図 2 0 】

【 図 2 1 】

【図22】

【 図 2 3 】

【図24】

## フロントページの続き

| (51) Int.CI.             | F I           | テーマコード(参考) |

|--------------------------|---------------|------------|

| H 0 1 L 27/092 (2006.01) | H 0 1 L 27/08 | 3 2 1 N    |

| H 0 1 L 27/08 (2006.01)  | H 0 1 L 27/08 | 3 3 1 E    |

| H 0 1 L 21/822 (2006.01) | H 0 1 L 27/08 | 3 2 1 H    |

| H 0 1 L 27/04 (2006.01)  | H 0 1 L 27/04 | H          |

| H 0 1 L 51/50 (2006.01)  | H 0 5 B 33/14 | A          |

F ターム(参考) 3K107 AA01 BB01 CC21 CC33 CC45 EE04 FF04 FF14

5F038 AC05 AC15 AC16 AC19 BH02 BH03 BH04 BH07 BH13 DF01

EZ03 EZ06 EZ20

5F048 AA07 AB10 AC04 AC10 BA16 BB01 BB02 BB09 BB11 BB12

BC11 BC15 BD04 BF07 BF11 BF12 BF15 BF16 BG01 BG07

CC01 CC05 CC06 CC09 CC15 CC16 CC19

5F110 AA01 AA16 AA22 BB02 CC07 DD01 DD02 EE02 EE03 EE04

EE06 EE14 EE23 EE28 EE38 EE42 EE43 EE44 EE45 FF01

FF02 FF03 FF04 FF09 FF10 FF27 FF28 FF29 FF30 GG01

GG02 GG06 GG14 GG15 GG16 GG19 GG22 GG25 GG32 GG33

GG34 GG43 GG45 GG57 HK01 HK02 HK03 HK04 HK06 HK09

HK15 HK16 HK22 HK25 HK32 HK33 HK35 HL01 HL02 HL03

HL04 HL07 HM04 HM12 NN04 NN12 NN22 NN24 NN34 NN35

NN71 NN73 QQ02 QQ09