등록특허 10-2719147

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2024년10월17일

(11) 등록번호 10-2719147

(24) 등록일자 2024년10월15일

- (51) 국제특허분류 (Int. Cl.)

*G06T 15/00* (2006.01) *G06T 1/20* (2018.01)

*G06T 15/50* (2006.01) *G06T 17/20* (2006.01)

*G06T 3/00* (2024.01)

- (52) CPC특허분류

*G06T 15/005* (2013.01)

*G06T 1/20* (2013.01)

- (21) 출원번호 10-2018-7019465

- (22) 출원일자(국제) 2016년12월02일

심사청구일자 2021년11월16일

- (85) 번역문제출일자 2018년07월06일

- (65) 공개번호 10-2018-0102563

- (43) 공개일자 2018년09월17일

- (86) 국제출원번호 PCT/US2016/064769

- (87) 국제공개번호 WO 2017/123341

국제공개일자 2017년07월20일

- (30) 우선권주장

14/993,760 2016년01월12일 미국(US)

- (56) 선행기술조사문현

US06577329 B1\*

US20060071877 A1\*

US20140347363 A1\*

\*는 심사관에 의하여 인용된 문현

전체 청구항 수 : 총 26 항

심사관 : 김성권

(54) 발명의 명칭 **다수의 레벨들의 디테일을 렌더링하기 위한 시스템들 및 방법들****(57) 요약**

전자 디바이스가 설명된다. 전자 디바이스는 프로세서를 포함한다. 프로세서는 이미지의 제 1 존을 렌더링하도록 구성된다. 프로세서는 또한, 이미지의 제 2 존을 렌더링하도록 구성된다. 제 1 존은 제 2 존보다 더 높은 테슬레이팅된 레벨의 디테일을 갖는다. 프로세서는 또한, 제 1 존 및 제 2 존을 적어도 하나의 차량 윈도우 상에 제시하도록 구성된다.

**대표도**

(52) CPC특허분류

*G06T 15/503* (2013.01)

*G06T 17/20* (2013.01)

*G06T 3/04* (2024.01)

*G06T 2210/36* (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

전자 디바이스로서,

메모리; 및

상기 메모리에 연결된 프로세서를 포함하고,

상기 프로세서는,

우선순위 사용자 및 비우선순위 사용자를 포함하는 복수의 사용자들에 대한 아이 (eye) 추적을 수행하고;

상기 우선순위 사용자의 상기 아이 추적에 기초하여 상기 우선순위 사용자에 대응하는 제 1 존에 기초한 제 1 기하학적 테슬레이팅된 (tessellated) 레벨의 디테일에서 이미지의 상기 제 1 존을 렌더링하고;

상기 비우선순위 사용자의 상기 아이 추적에 기초하여 상기 비우선순위 사용자에 대응하는 제 2 존에 기초한 상기 제 1 기하학적 테슬레이팅된 레벨의 디테일보다 낮은 제 2 기하학적 테슬레이팅된 레벨의 디테일에서 상기 이미지의 상기 제 2 존을 렌더링하는 것으로서, 상기 제 1 기하학적 테슬레이팅된 레벨의 디테일은 적어도 하나의 디스플레이의 적어도 섹션에 대응하고, 상기 프로세서는 단일의 드로우 콜 (draw call)에서 상기 상이한 제 1 및 제 2 기하학적 테슬레이팅된 레벨들의 디테일로 상기 제 1 존의 적어도 부분 및 상기 제 2 존의 적어도 부분을 렌더링하도록 구성되고, 상기 단일의 드로우 콜은 다수의 기하학적 테슬레이팅된 레벨들의 디테일을 핸들링하는 하나의 프로그래밍적 요청인, 상기 이미지의 상기 제 2 존을 렌더링하며;

상기 적어도 하나의 디스플레이를 사용하여 상기 제 1 존 및 상기 제 2 존을 제시하도록 구성된 프로세서를 포함하는, 전자 디바이스.

#### 청구항 2

제 1 항에 있어서,

상기 프로세서는 상기 제 1 존 및 상기 제 2 존을 상기 적어도 하나의 디스플레이로 전송하여 상기 제 1 존 및 상기 제 2 존을 적어도 하나의 차량 윈도우 상에 제시하도록 구성되는, 전자 디바이스.

#### 청구항 3

제 2 항에 있어서,

상기 적어도 하나의 디스플레이는 윈도우 프로젝터 또는 통합형 윈도우 디스플레이 패널인, 전자 디바이스.

#### 청구항 4

제 1 항에 있어서,

상기 프로세서는 상기 제 1 존을 제 1 윈도우 상에 제시하고 상기 제 2 존을 제 2 윈도우 상에 제시하도록 구성되는, 전자 디바이스.

#### 청구항 5

제 4 항에 있어서,

상기 제 1 윈도우는 차량의 전방 윈드쉴드이고 상기 제 2 윈도우는 상기 차량의 다른 윈도우인, 전자 디바이스.

#### 청구항 6

제 1 항에 있어서,

상기 프로세서는 상기 제 1 존을 윈도우의 제 1 섹션 상에 제시하고 상기 제 2 존을 상기 윈도우의 제 2 섹션

상에 제시하도록 구성되는, 전자 디바이스.

### 청구항 7

제 6 항에 있어서,

상기 제 1 섹션은 원드실드의 사이드 섹션이고 상기 제 2 섹션은 상기 원드실드의 다른 사이드 섹션인, 전자 디바이스.

### 청구항 8

제 6 항에 있어서,

상기 제 1 섹션은 원드실드를 가로지르는 제 1 수평 바이고 상기 제 2 섹션은 상기 원드실드를 가로지르는 제 2 수평 바인, 전자 디바이스.

### 청구항 9

삭제

### 청구항 10

삭제

### 청구항 11

제 1 항에 있어서,

상기 프로세서는 제 3 존을 렌더링하도록 구성되고,

상기 제 3 존은 상기 제 1 존 및 상기 제 2 존보다 더 낮은 기하학적 테슬레이팅된 레벨의 디테일을 갖는, 전자 디바이스.

### 청구항 12

제 11 항에 있어서,

상기 프로세서는 적어도 하나의 차량 윈도우 상에 제 3 존을 제시하도록 구성되는, 전자 디바이스.

### 청구항 13

제 1 항에 있어서,

상기 전자 디바이스는 차량 내의 착탈형 모듈의 적어도 부분인, 전자 디바이스.

### 청구항 14

전자 디바이스에 의해 수행된 방법으로서,

우선순위 사용자 및 비우선순위 사용자를 포함하는 복수의 사용자들에 대한 아이 (eye) 추적을 수행하는 단계;

상기 우선순위 사용자의 아이 추적에 기초하여 상기 우선순위 사용자에 대응하는 제 1 존에 기초한 제 1 기하학적 테슬레이팅된 (tessellated) 레벨의 디테일에서 이미지의 상기 제 1 존을 렌더링하는 단계;

상기 비우선순위 사용자의 상기 아이 추적에 기초하여 상기 비우선순위 사용자에 대응하는 제 2 존에 기초한 상기 제 1 기하학적 테슬레이팅된 레벨의 디테일보다 낮은 제 2 기하학적 테슬레이팅된 레벨의 디테일에서 상기 이미지의 상기 제 2 존을 렌더링하는 단계로서, 상기 제 1 기하학적 테슬레이팅된 레벨의 디테일은 적어도 하나의 디스플레이의 적어도 섹션에 대응하고, 상이한 상기 제 1 및 제 2 기하학적 테슬레이팅된 레벨들의 디테일로 상기 제 1 존의 적어도 부분 및 상기 제 2 존의 적어도 부분이 단일의 드로우 콜 (draw call)에서 렌더링되고, 상기 단일의 드로우 콜은 다수의 기하학적 테슬레이팅된 레벨들의 디테일을 핸들링하는 하나의 프로그래밍적 요청인, 상기 이미지의 상기 제 2 존을 렌더링하는 단계; 및

상기 적어도 하나의 디스플레이를 사용하여 상기 제 1 존 및 상기 제 2 존을 제시하는 단계를 포함하는, 전자

디바이스에 의해 수행된 방법.

### 청구항 15

제 14 항에 있어서,

상기 제 1 존 및 상기 제 2 존을 상기 적어도 하나의 디스플레이로 전송하여 상기 제 1 존 및 상기 제 2 존을 적어도 하나의 차량 원도우 상에 제시하는 단계를 더 포함하는, 전자 디바이스에 의해 수행된 방법.

### 청구항 16

제 15 항에 있어서,

상기 적어도 하나의 디스플레이는 원도우 프로젝터 또는 통합형 원도우 디스플레이 패널인, 전자 디바이스에 의해 수행된 방법.

### 청구항 17

제 14 항에 있어서,

상기 제 1 존을 제 1 원도우 상에 제시하는 단계; 및

상기 제 2 존을 제 2 원도우 상에 제시하는 단계를 더 포함하는, 전자 디바이스에 의해 수행된 방법.

### 청구항 18

제 17 항에 있어서,

상기 제 1 원도우는 차량의 전방 윈드쉴드이고 상기 제 2 원도우는 상기 차량의 다른 원도우인, 전자 디바이스에 의해 수행된 방법.

### 청구항 19

제 14 항에 있어서,

상기 제 1 존을 원도우의 제 1 섹션 상에 제시하는 단계; 및

상기 제 2 존을 상기 원도우의 제 2 섹션 상에 제시하는 단계를 더 포함하는, 전자 디바이스에 의해 수행된 방법.

### 청구항 20

제 19 항에 있어서,

상기 제 1 섹션은 윈드쉴드의 사이드 섹션이고 상기 제 2 섹션은 상기 윈드쉴드의 다른 사이드 섹션인, 전자 디바이스에 의해 수행된 방법.

### 청구항 21

제 19 항에 있어서,

상기 제 1 섹션은 윈드쉴드를 가로지르는 제 1 수평 바이고 상기 제 2 섹션은 상기 윈드쉴드를 가로지르는 제 2 수평 바인, 전자 디바이스에 의해 수행된 방법.

### 청구항 22

삭제

### 청구항 23

제 14 항에 있어서,

제 3 존을 렌더링하는 단계를 더 포함하고,

상기 제 3 존은 상기 제 1 존 및 상기 제 2 존보다 더 낮은 기하학적 테슬레이팅된 레벨의 디테일을 갖는, 전자

디바이스에 의해 수행된 방법.

#### 청구항 24

제 14 항에 있어서,

상기 전자 디바이스는 차량 내의 차량형 모듈의 적어도 부분인, 전자 디바이스에 의해 수행된 방법.

#### 청구항 25

명령들을 갖는 비일시적 유형의 컴퓨터 판독가능 저장매체에 저장된 컴퓨터 프로그램으로서,

상기 명령들은,

전자 디바이스로 하여금 우선순위 사용자 및 비우선순위 사용자를 포함하는 복수의 사용자들에 대한 아이 (eye) 추적을 수행하게 하는 코드;

상기 전자 디바이스로 하여금 상기 우선순위 사용자의 상기 아이 추적에 기초하여 상기 우선순위 사용자에 대응하는 제 1 존에 기초한 제 1 기하학적 테슬레이팅된 (tessellated) 레벨의 디테일에서 이미지의 상기 제 1 존을 렌더링하게 하는 코드;

상기 전자 디바이스로 하여금 상기 비우선순위 사용자의 상기 아이 추적에 기초하여 상기 비우선순위 사용자에 대응하는 제 2 존에 기초한 상기 제 1 기하학적 테슬레이팅된 레벨의 디테일보다 낮은 제 2 기하학적 테슬레이팅된 레벨의 디테일에서 상기 이미지의 상기 제 2 존을 렌더링하게 하는 코드로서, 상기 제 1 기하학적 테슬레이팅된 레벨의 디테일은 적어도 하나의 디스플레이의 적어도 섹션에 대응하고, 상기 제 1 존을 상기 전자 디바이스로 하여금 렌더링하게 하는 코드 및 상기 제 2 존을 상기 전자 디바이스로 하여금 렌더링하게 하는 코드는 단일의 드로우 콜 (draw call)에서 상이한 상기 제 1 및 제 2 기하학적 테슬레이팅된 레벨들의 디테일로 상기 제 1 존의 적어도 부분 및 상기 제 2 존의 적어도 부분을 상기 전자 디바이스로 하여금 렌더링하게 하는 코드를 포함하고, 상기 단일의 드로우 콜은 다수의 기하학적 테슬레이팅된 레벨들의 디테일을 핸들링하는 하나의 프로그래밍적 요청인, 상기 이미지의 상기 제 2 존을 렌더링하게 하는 코드; 및

상기 전자 디바이스로 하여금 상기 적어도 하나의 디스플레이를 사용하여 상기 제 1 존 및 상기 제 2 존을 제시하게 하는 코드를 포함하는, 비일시적 유형의 컴퓨터 판독가능 저장매체에 저장된 컴퓨터 프로그램.

#### 청구항 26

제 25 항에 있어서,

상기 명령들은 상기 전자 디바이스로 하여금 상기 제 1 존 및 상기 제 2 존을 상기 적어도 하나의 디스플레이로 전송하여 상기 제 1 존 및 상기 제 2 존을 적어도 하나의 차량 윈도우 상에 제시하게 하는 코드를 포함하는, 비일시적 유형의 컴퓨터 판독가능 저장매체에 저장된 컴퓨터 프로그램.

#### 청구항 27

제 25 항에 있어서,

상기 전자 디바이스로 하여금 상기 제 1 존 및 상기 제 2 존을 제시하게 하는 코드는,

상기 전자 디바이스로 하여금 상기 제 1 존을 제 1 윈도우 상에 제시하고 상기 제 2 존을 제 2 윈도우 상에 제시하게 하는 코드를 포함하는, 비일시적 유형의 컴퓨터 판독가능 저장매체에 저장된 컴퓨터 프로그램.

#### 청구항 28

장치로서,

우선순위 사용자 및 비우선순위 사용자를 포함하는 복수의 사용자들에 대한 아이 (eye) 추적을 수행하기 위한 수단;

상기 우선순위 사용자의 상기 아이 추적에 기초하여 상기 우선순위 사용자에 대응하는 제 1 존에 기초한 제 1 기하학적 테슬레이팅된 (tessellated) 레벨의 디테일에서 이미지의 상기 제 1 존을 렌더링하기 위한 수단;

상기 비우선순위 사용자의 상기 아이 추적에 기초하여 상기 비우선순위 사용자에 대응하는 제 2 존에 기초한 상

기 제 1 기하학적 테슬레이팅된 레벨의 디테일보다 낮은 제 2 기하학적 테슬레이팅된 레벨의 디테일에서 상기 이미지의 상기 제 2 존을 렌더링하기 위한 수단으로서, 상기 제 1 기하학적 테슬레이팅된 레벨의 디테일은 적어도 하나의 디스플레이의 적어도 섹션에 대응하고, 상기 제 1 존을 렌더링하기 위한 수단 및 상기 제 2 존을 렌더링하기 위한 수단은 단일의 드로우 콜 (draw call)에서 상이한 상기 제 1 및 제 2 기하학적 테슬레이팅된 레벨들의 디테일로 상기 제 1 존의 적어도 부분 및 상기 제 2 존의 적어도 부분을 렌더링하기 위한 수단을 포함하고, 상기 단일의 드로우 콜은 다수의 기하학적 테슬레이팅된 레벨들의 디테일을 핸들링하는 하나의 프로그래밍적 요청인, 상기 이미지의 상기 제 2 존을 렌더링하기 위한 수단; 및

상기 적어도 하나의 디스플레이를 사용하여 상기 제 1 존 및 상기 제 2 존을 제시하기 위한 수단을 포함하는, 장치.

### 청구항 29

삭제

### 청구항 30

제 28 항에 있어서,

상기 제시하기 위한 수단은 상기 제 1 존을 제 1 윈도우 상에 제시하기 위한 수단; 및

상기 제 2 존을 제 2 윈도우 상에 제시하기 위한 수단을 포함하는, 장치.

## 발명의 설명

### 기술 분야

[0001] 본 개시물은 일반적으로 전자 디바이스들에 관한 것이다. 보다 구체적으로, 본 개시물은 다수의 레벨들의 디테일을 렌더링하기 위한 시스템들 및 방법들에 관한 것이다.

### 배경 기술

[0002] 일부 전자 디바이스들 (예를 들어, 스마트 폰들, 컴퓨터들, 텔레비전들, 자동차들, 비디오게임 시스템들, 미디어 플레이어들, 카메라들, 셀룰러 폰들, 퍼스널 카메라들, 셋-톱 박스들, 프로젝터들, 모니터들, 등)은 이미지를 디스플레이한다. 예를 들어, 스마트폰은 스틸 및/또는 비디오 이미지를 캡처 및/또는 프로세싱할 수도 있다. 이미지를 프로세싱하는 것은 상대적으로 대량의 시간, 메모리 및 에너지 리소스들을 요구할 수도 있다. 요구된 리소스들은 프로세싱의 복잡성에 따라 가변할 수도 있다.

[0003] 대량의 이미지 데이터를 프로세싱하는 것은 특히 어려울 수도 있다. 예를 들어, 대량의 이미지 데이터는 상대적으로 대량의 리소스들, 예컨대 전력, 시간, 프로세서 대역폭, 메모리 및/또는 사용 요금들을 요구할 수도 있다. 본 논의로부터 관측될 수 있는 바와 같이, 이미지 프로세싱을 개선시키는 시스템들 및 방법들이 유리할 수도 있다.

## 발명의 내용

### 과제의 해결 수단

[0004] 전자 디바이스가 설명된다. 전자 디바이스는 이미지의 제 1 존을 렌더링하도록 구성된 프로세서를 포함한다. 프로세서는 또한, 이미지의 제 2 존을 렌더링하도록 구성된다. 제 1 존은 제 2 존보다 더 높은 테슬레이팅된 (tessellated) 레벨의 디테일을 갖는다. 프로세서는 또한, 적어도 하나의 차량 윈도우 상에 제 1 존 및 제 2 존을 제시하도록 구성된다. 전자 디바이스는 차량 내의 차탈형 모듈의 적어도 부분일 수도 있다.

[0005] 전자 디바이스는 적어도 하나의 디스플레이를 포함할 수도 있다. 프로세서는 제 1 존 및 제 2 존을 적어도 하나의 디스플레이로 전송하여 제 1 존 및 제 2 존을 제시하도록 구성될 수도 있다. 적어도 하나의 디스플레이에는 윈도우 프로젝터 또는 통합형 윈도우 디스플레이 패널일 수도 있다.

[0006] 프로세서는 제 1 윈도우 상에 제 1 존을 제시하고 제 2 윈도우 상에 제 2 존을 제시하도록 구성될 수도 있다. 제 1 윈도우는 전방 윈드쉴드일 수도 있고 제 2 윈도우는 차량의 다른 윈도우일 수도 있다.

[0007] 프로세서는 윈도우의 제 1 섹션 상에 제 1 존을 제시하도록 구성될 수도 있고, 윈도우의 제 2 섹션 상에 제 2 존을 제시하도록 구성될 수도 있다. 제 1 섹션은 윈드실드의 사이드 섹션일 수도 있고 제 2 섹션은 윈드실드의 다른 사이드 섹션일 수도 있다. 제 1 섹션은 윈드실드를 가로지르는 제 1 수평 바일 수도 있고 제 2 섹션은 윈드실드를 가로지르는 제 2 수평 바일 수도 있다.

[0008] 프로세서는 아이 추적을 수행하도록 구성될 수도 있다. 프로세서는 또한, 아이 추적에 기초하여 제 1 존 및 제 2 존을 렌더링하도록 구성될 수도 있다. 프로세서는 다수의 사용자들에 대한 아이 추적을 수행하도록 구성될 수도 있다. 프로세서는 아이 추적에 기초하여 존 렌더링을 우선순위화할 수도 있다.

[0009] 프로세서는 제 3 존을 렌더링하도록 구성될 수도 있다. 제 3 존은 제 1 존 및 제 2 존보다 더 낮은 테슬레이팅된 레벨의 디테일을 가질 수도 있다. 프로세서는 적어도 하나의 차량 윈도우 상에 제 3 존을 제시하도록 구성될 수도 있다.

[0010] 전자 디바이스에 의해 수행된 방법이 또한, 설명된다. 방법은 이미지의 제 1 존을 렌더링하는 단계를 포함한다. 방법은 또한, 이미지의 제 2 존을 렌더링하는 단계를 포함한다. 제 1 존은 제 2 존보다 더 높은 테슬레이팅된 레벨의 디테일을 갖는다. 방법은 적어도 하나의 차량 윈도우 상에 제 1 존 및 제 2 존을 제시하는 단계를 더 포함한다.

[0011] 컴퓨터-프로그램 제품이 또한, 설명된다. 컴퓨터-프로그램 제품은 명령들을 갖는 비일시적 유형의 컴퓨터 판독가능 매체를 포함한다. 명령들은 전자 디바이스로 하여금 이미지의 제 1 존을 렌더링하게 하는 코드를 포함한다. 명령들은 또한, 전자 디바이스로 하여금 이미지의 제 2 존을 렌더링하게 하는 코드를 포함한다. 제 1 존은 제 2 존보다 더 높은 테슬레이팅된 레벨의 디테일을 갖는다. 명령들은 전자 디바이스로 하여금 적어도 하나의 차량 윈도우 상에 제 1 존 및 제 2 존을 제시하게 하는 코드를 더 포함한다.

[0012] 장치가 또한, 설명된다. 장치는 이미지의 제 1 존을 렌더링하기 위한 수단을 포함한다. 장치는 또한, 이미지의 제 2 존을 렌더링하기 위한 수단을 포함한다. 제 1 존은 제 2 존보다 더 높은 테슬레이팅된 레벨의 디테일을 갖는다. 장치는 적어도 하나의 차량 윈도우 상에 제 1 존 및 제 2 존을 제시하기 위한 수단을 더 포함한다.

### 도면의 간단한 설명

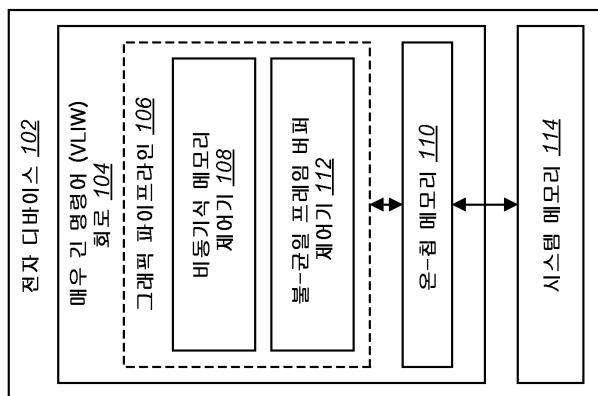

[0013] 도 1 은 다수의 레벨들의 디테일을 렌더링하기 위한 시스템들 및 방법들이 구현될 수도 있는 전자 디바이스의 일 구성을 예시하는 블록도이다;

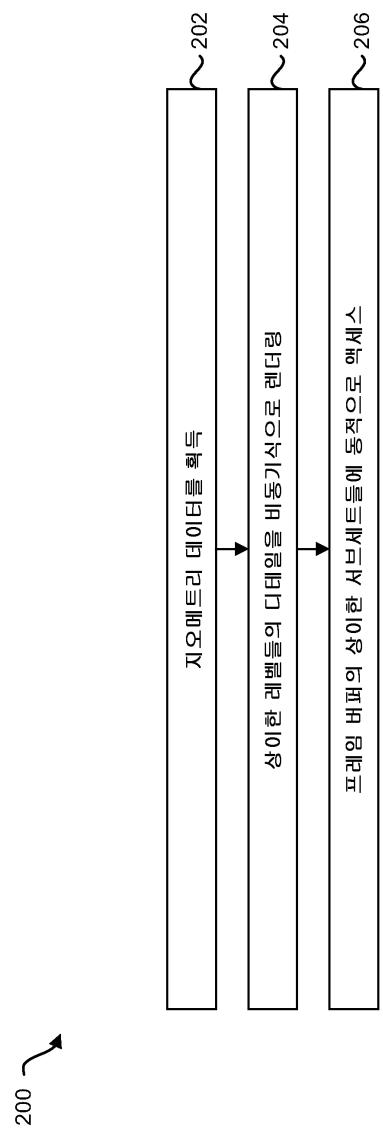

도 2 는 다수의 레벨들의 디테일을 렌더링하는 방법의 일 구성을 예시하는 흐름도이다;

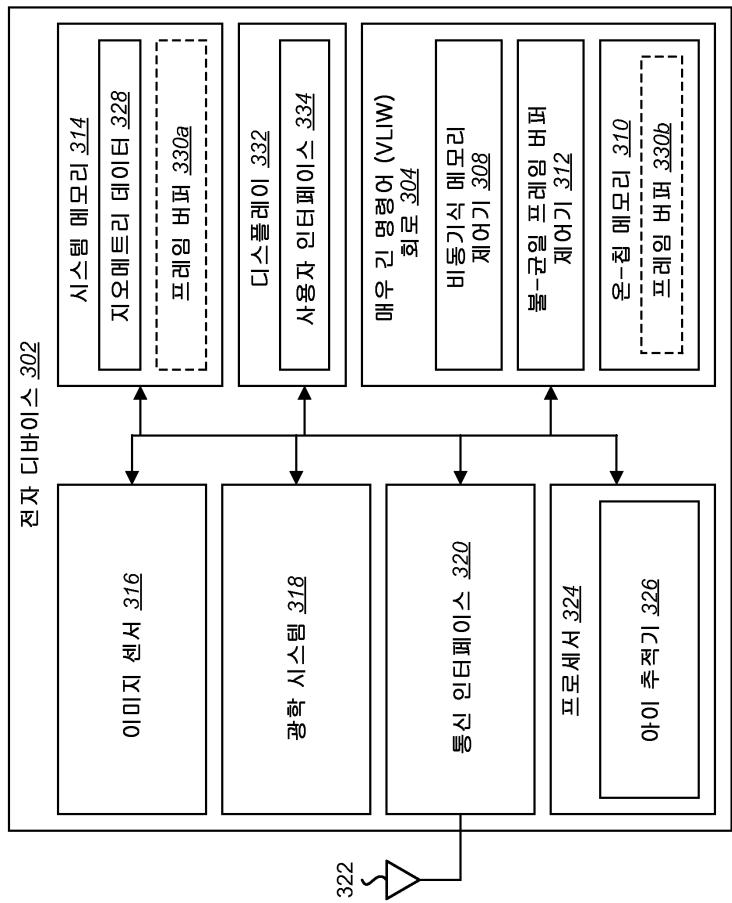

도 3 은 다수의 레벨들의 디테일을 렌더링하기 위한 시스템들 및 방법들이 구현될 수도 있는 전자 디바이스의 일 구성을 예시하는 블록도이다;

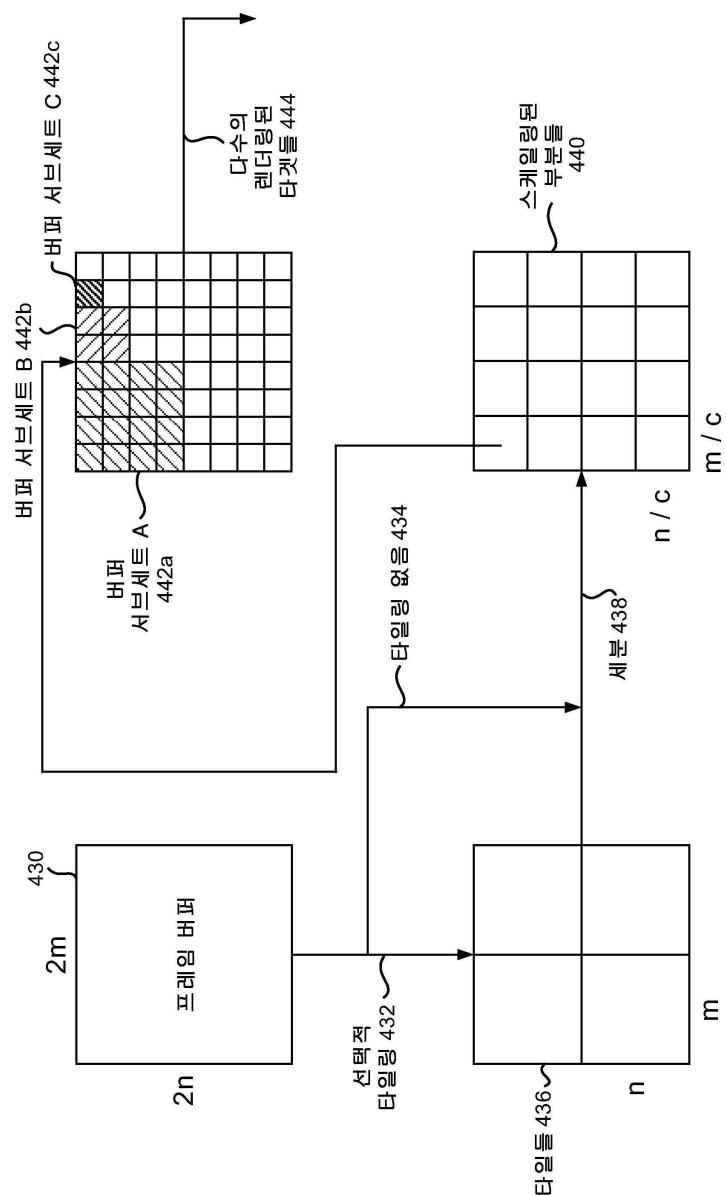

도 4 는 불-균일 프레임 버퍼의 일 예를 예시하는 다이어그램이다;

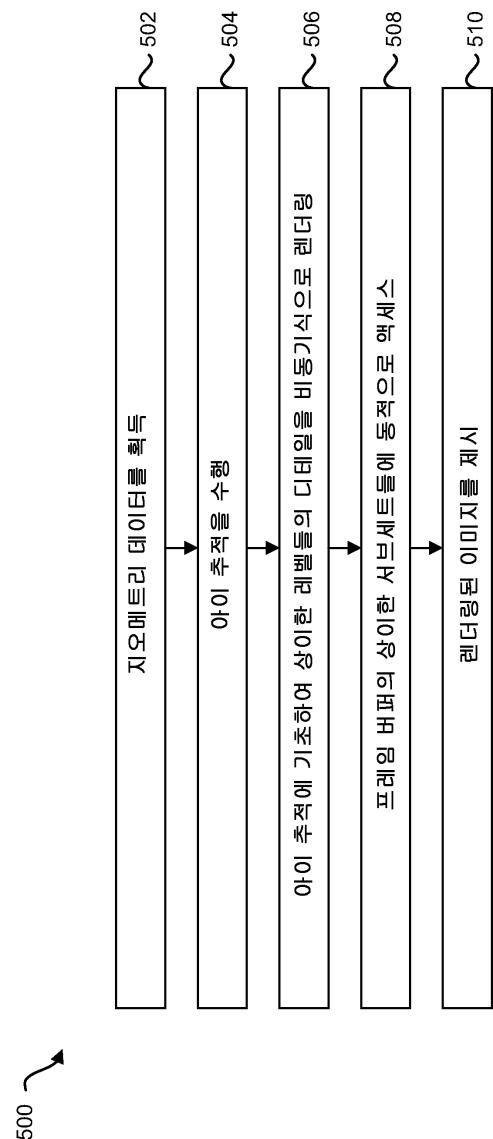

도 5 는 다수의 레벨들의 디테일을 렌더링하는 방법의 더 많은 특정 구성을 예시하는 흐름도이다;

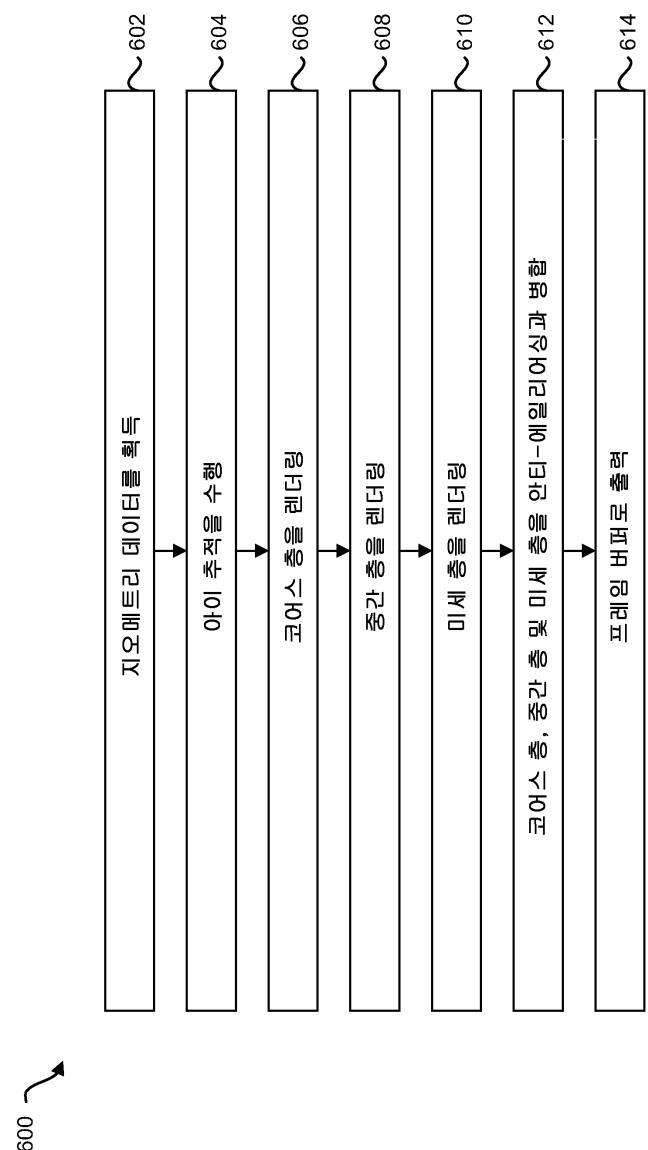

도 6 은 포비에이티드 (foveated) 렌더링을 위한 방법의 예를 예시하는 흐름도이다;

도 7 은 포비에이티드 렌더링의 일 예를 예시한다;

도 8 은 매우 긴 명령어 (VLIW) 회로를 포함하는 전자 디바이스의 예를 예시하는 블록도이다;

도 9 는 도 8 와 연관되어 설명된 아키텍처에서 구현된 본원에 개시된 시스템들 및 방법들의 예를 예시하는 블록도이다;

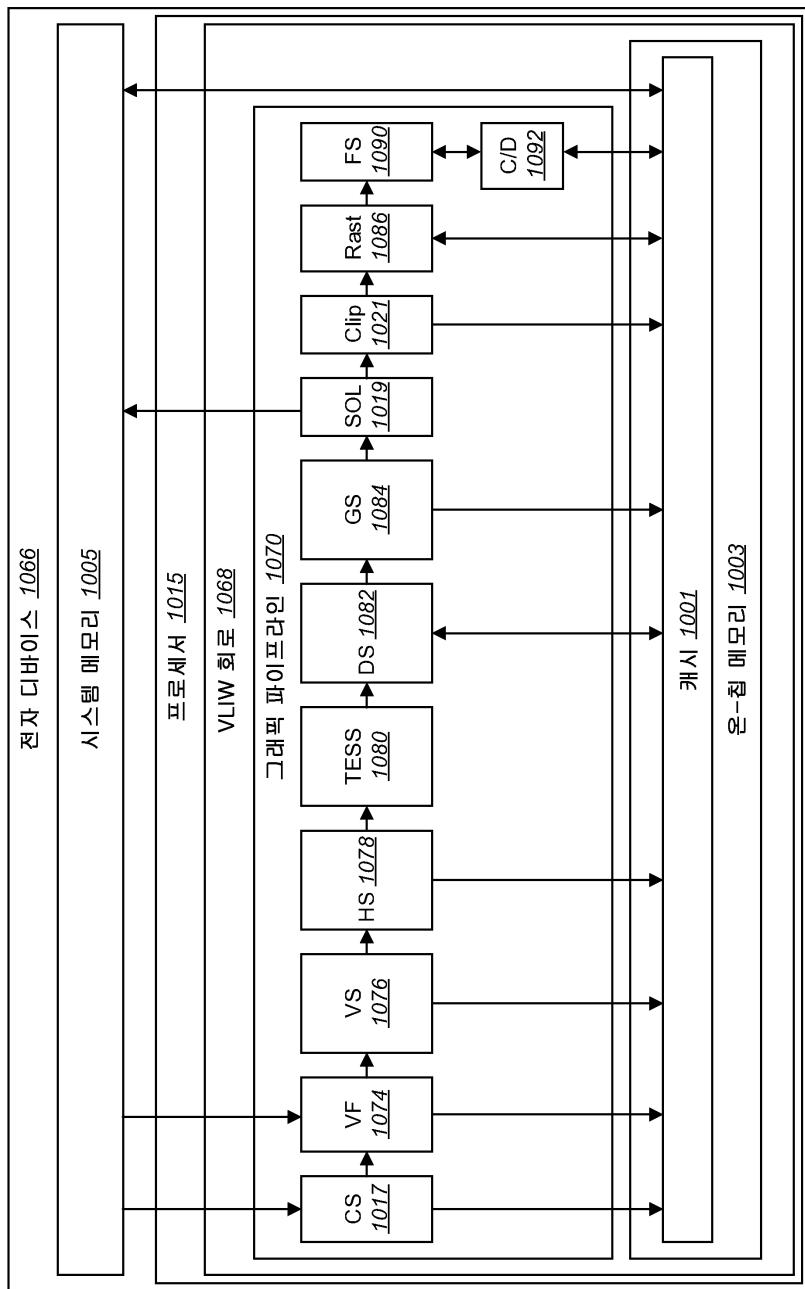

도 10 은 매우 긴 명령어 (VLIW) 회로를 포함하는 전자 디바이스의 다른 예를 예시하는 블록도이다;

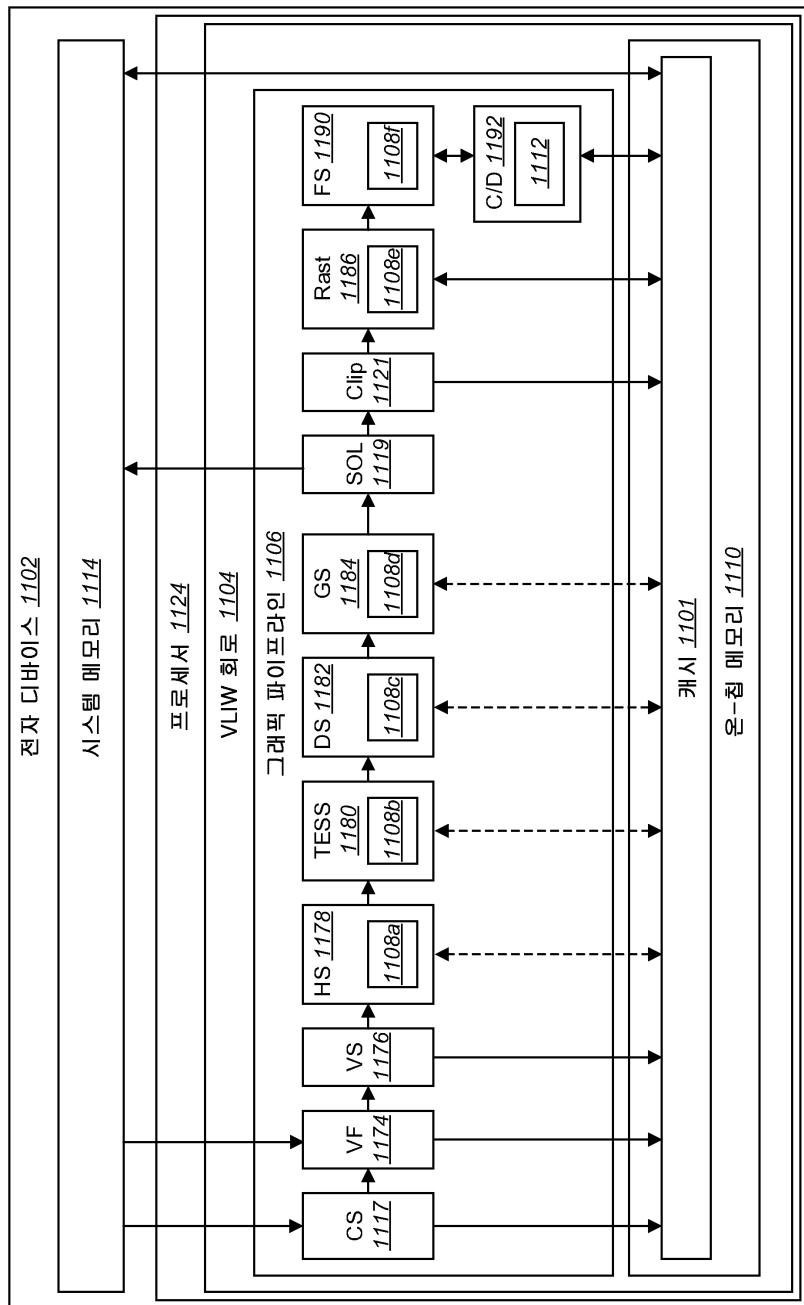

도 11 은 도 10 과 연관되어 설명된 아키텍처에서 구현된 본원에 개시된 시스템들 및 방법들의 다른 예를 예시하는 블록도이다;

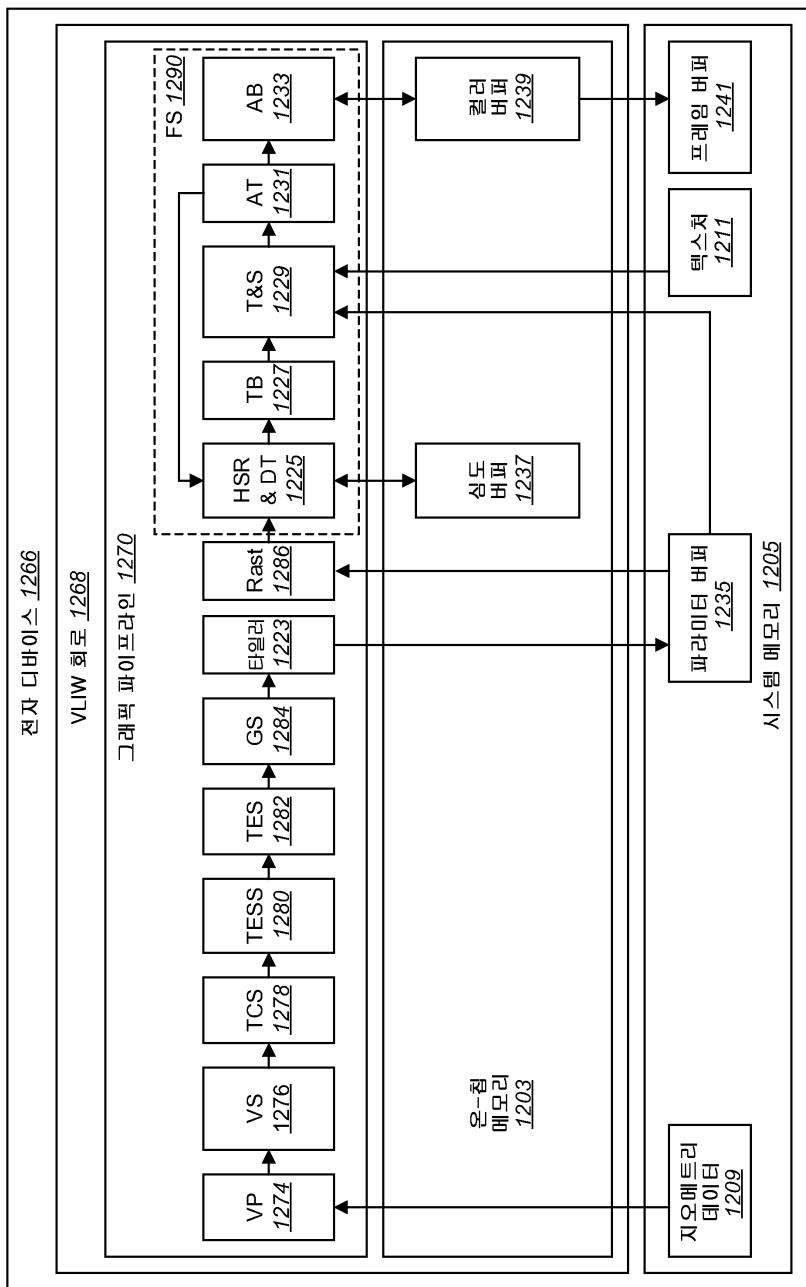

도 12 는 매우 긴 명령어 (VLIW) 회로를 포함하는 전자 디바이스의 다른 예를 예시하는 블록도이다;

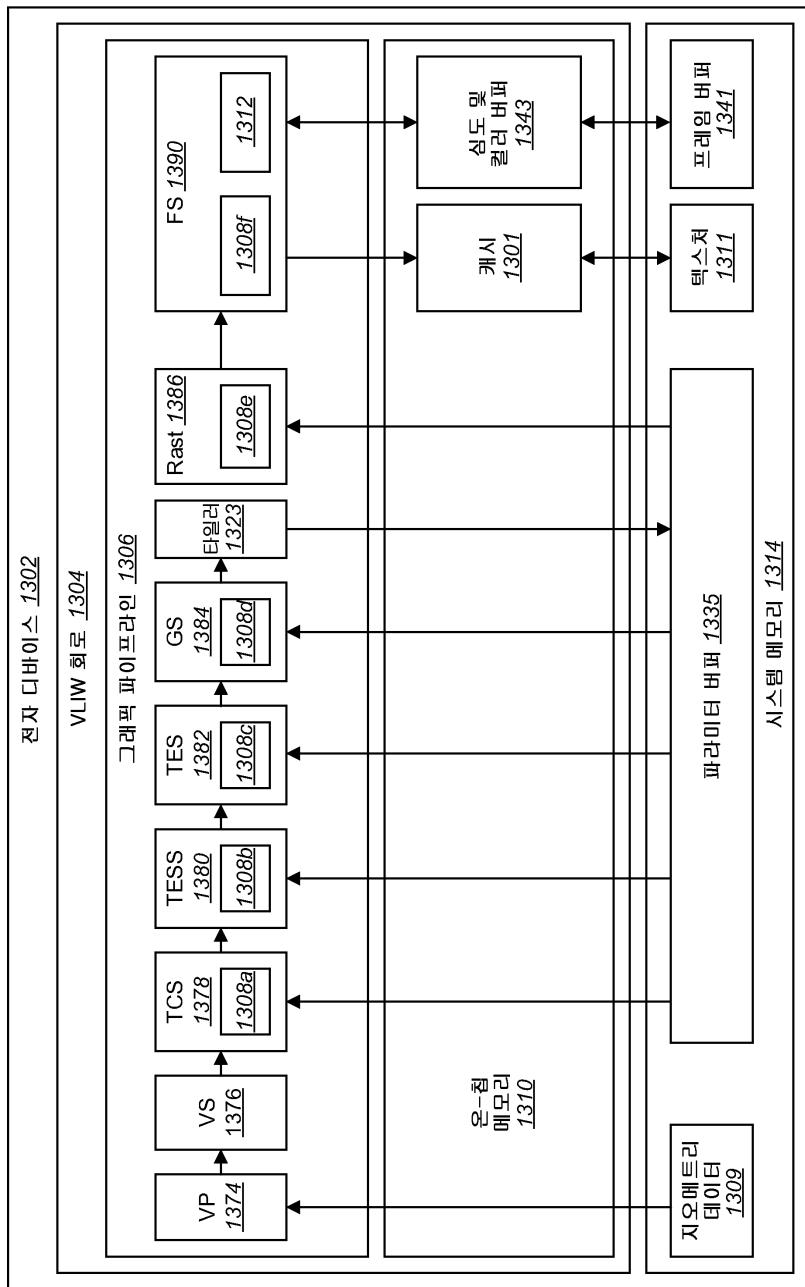

도 13 은 도 12 와 연관되어 설명된 아키텍처에서 구현된 본원에 개시된 시스템들 및 방법들의 예를 예시하는 블록도이다;

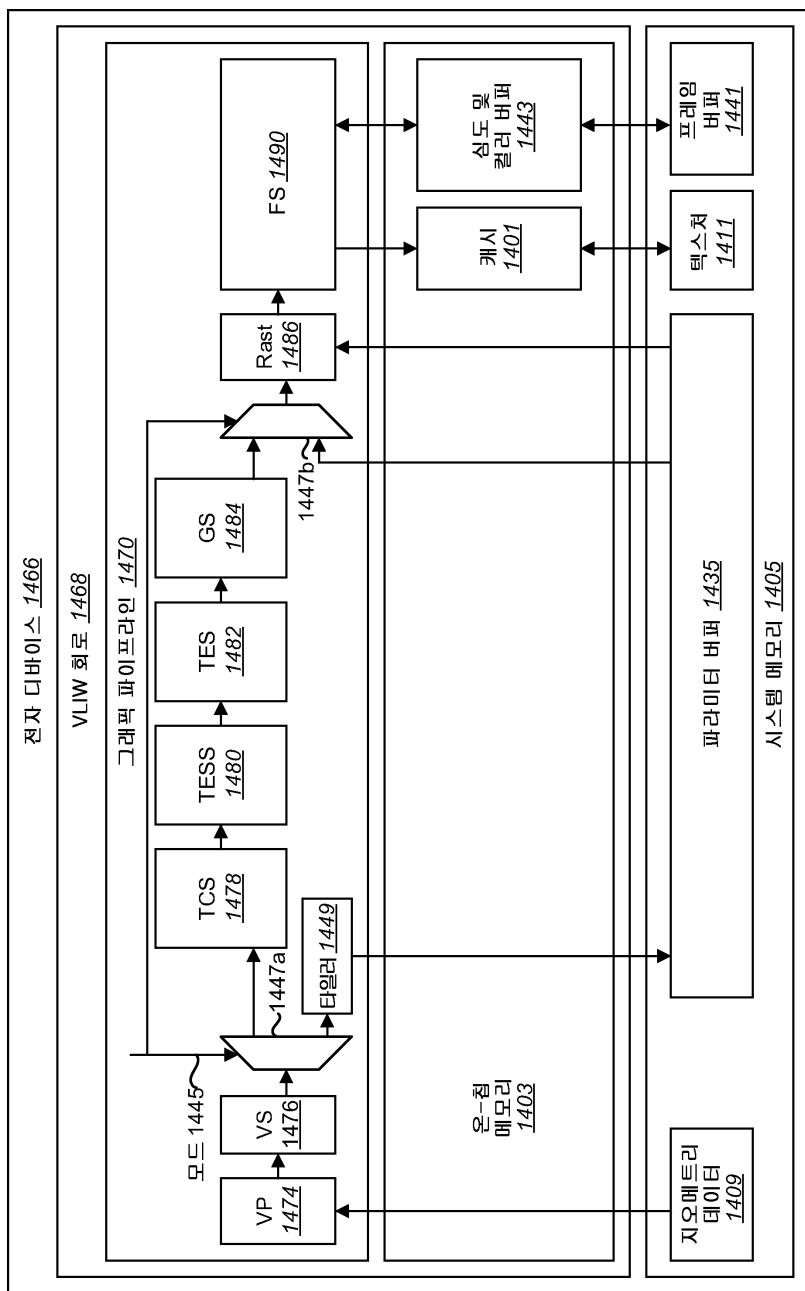

도 14 는 매우 긴 명령어 (VLIW) 회로를 포함하는 전자 디바이스의 다른 예를 예시하는 블록도이다;

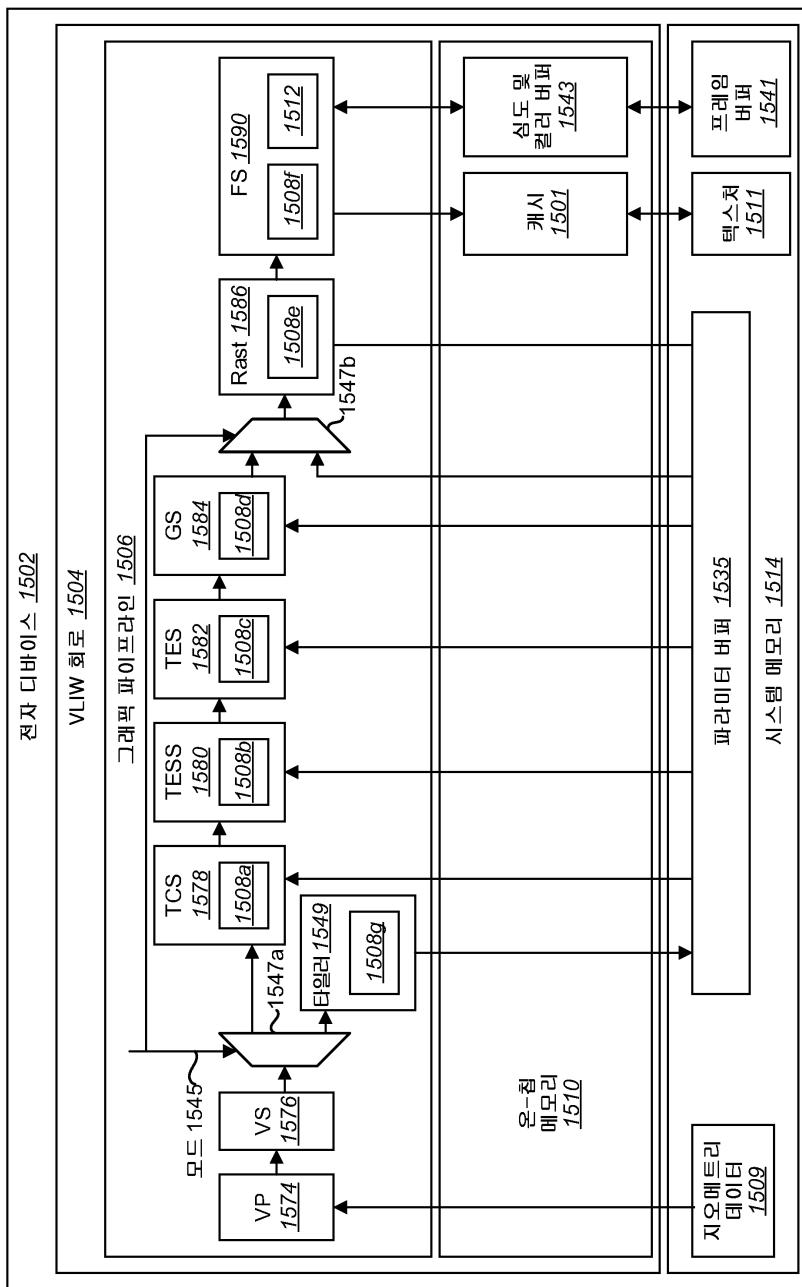

도 15 는 도 14 와 연관되어 설명된 아키텍처에서 구현된 본원에 개시된 시스템들 및 방법들의 예를 예시하는 블록도이다;

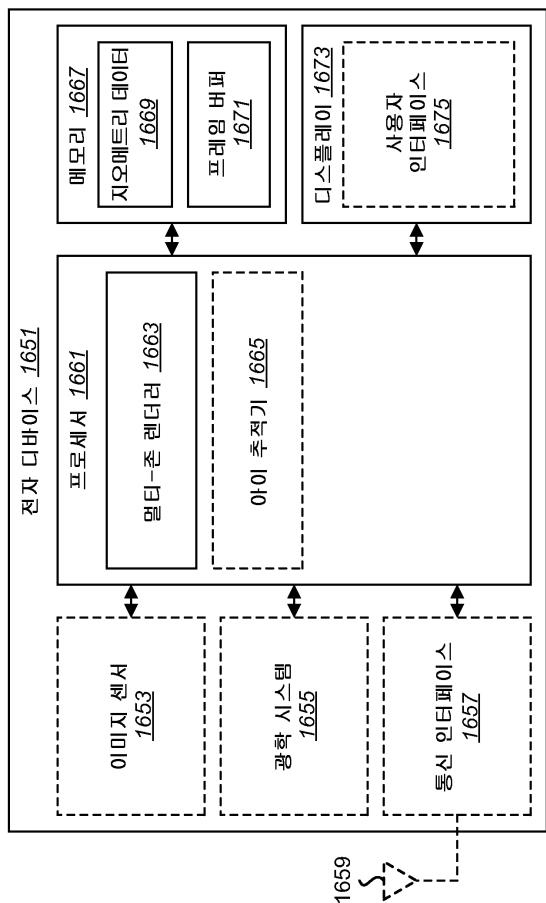

도 16 은 다수의 존들을 렌더링하기 위한 시스템들 및 방법들이 구현될 수도 있는 전자 디바이스의 일 구성 예시하는 블록도이다;

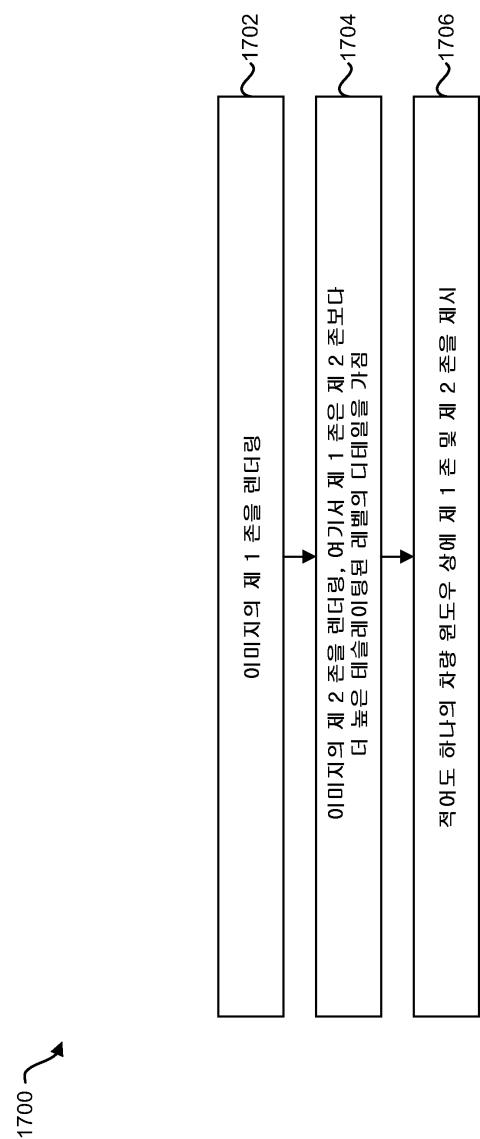

도 17 은 다수의 존들을 렌더링하는 방법을 예시하는 흐름도이다;

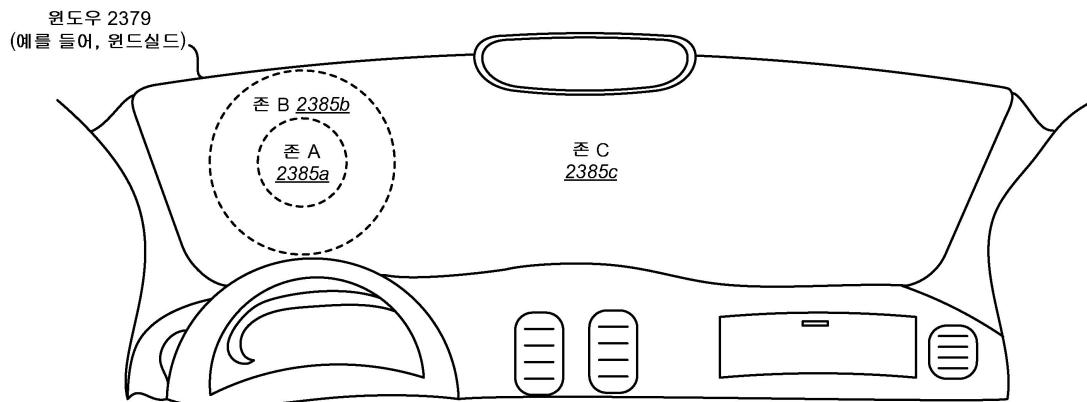

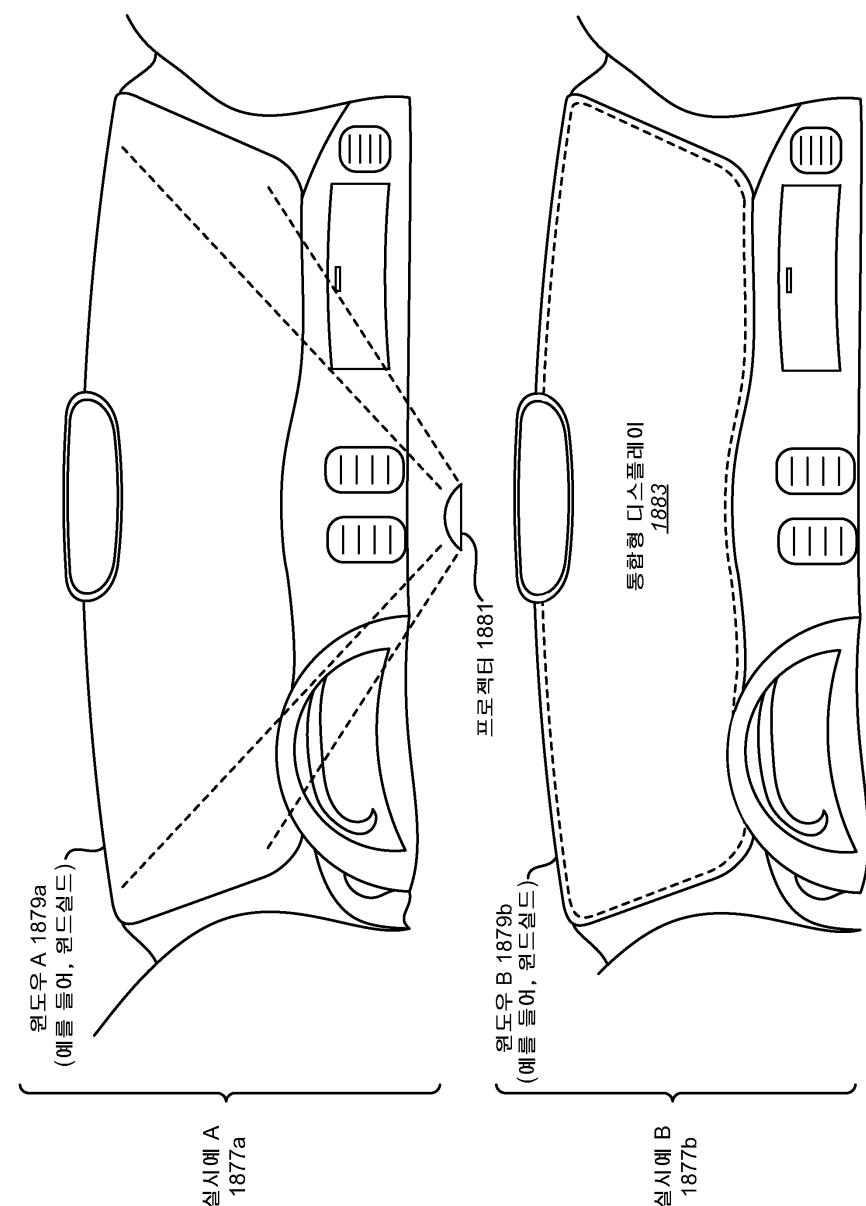

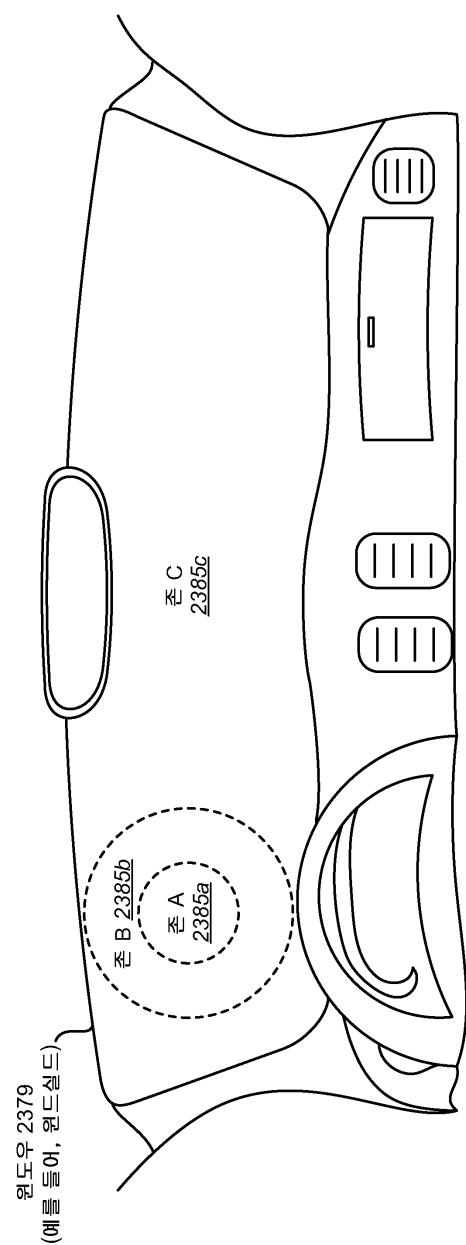

도 18 은 윈도우 디스플레이들의 일부 예들을 예시하는 다이어그램이다;

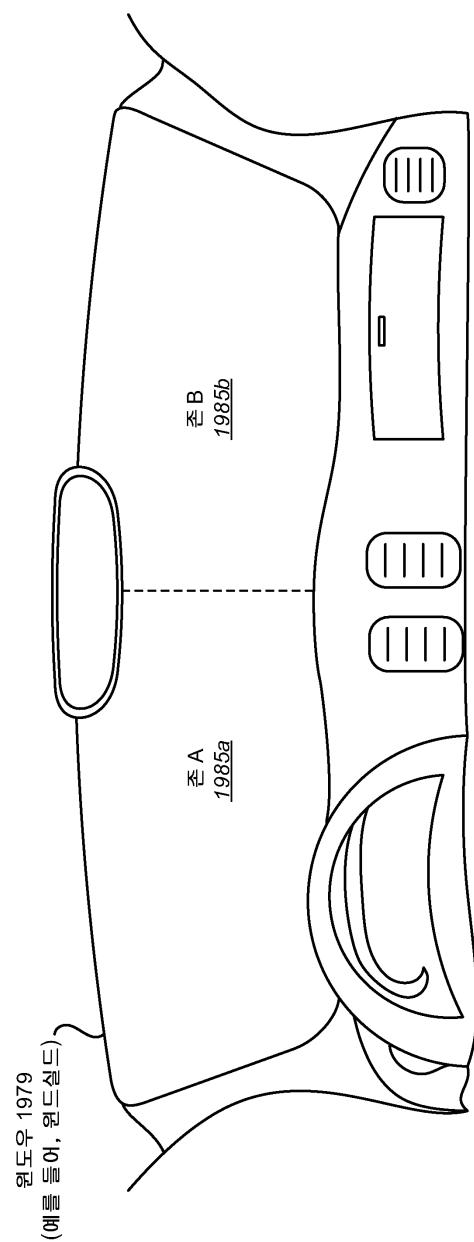

도 19 는 윈도우 상의 존들의 일 예를 예시하는 다이어그램이다;

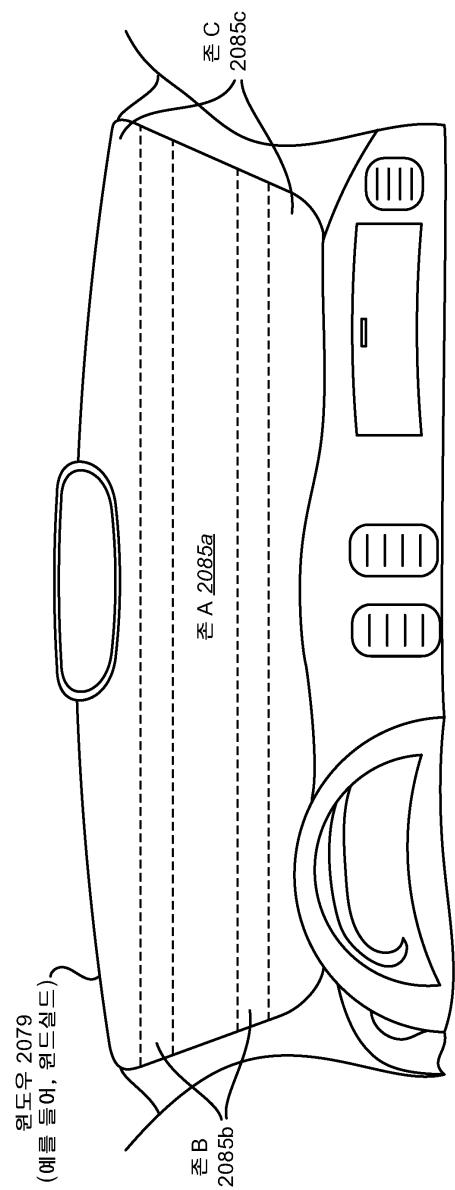

도 20 은 윈도우 상의 존들의 다른 예를 예시하는 다이어그램이다;

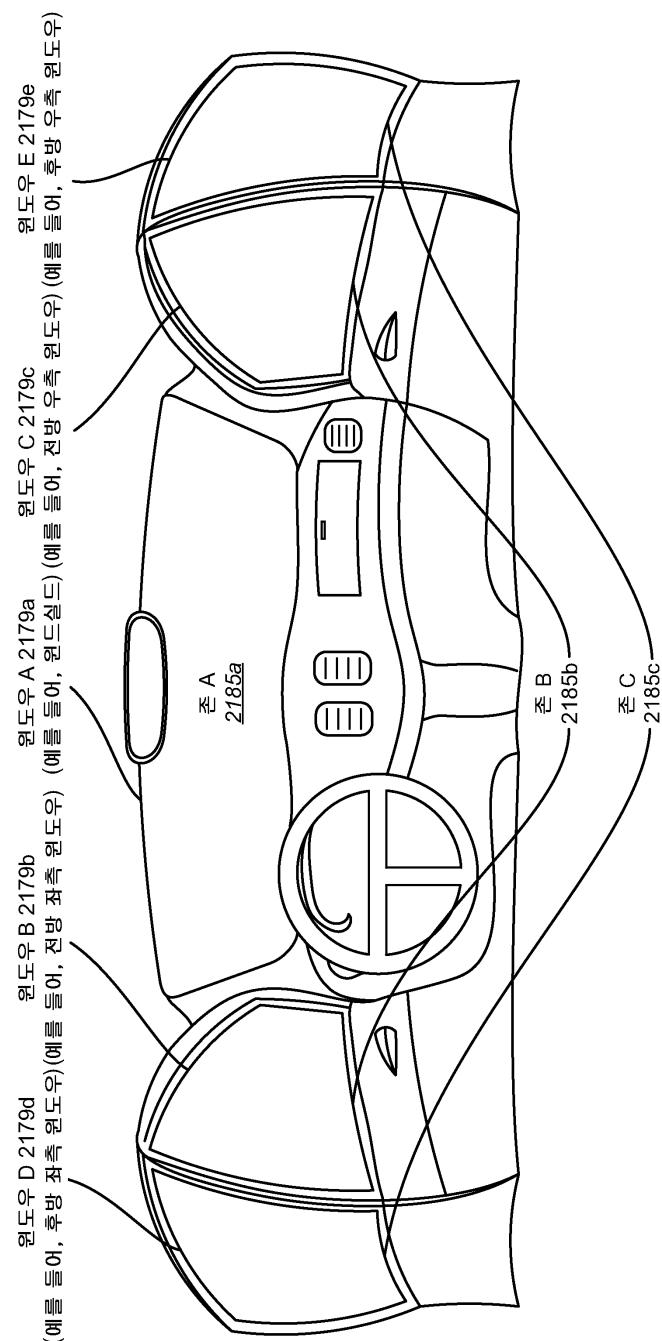

도 21 은 다수의 윈도우들 상에 존들의 다른 예를 예시하는 다이어그램이다;

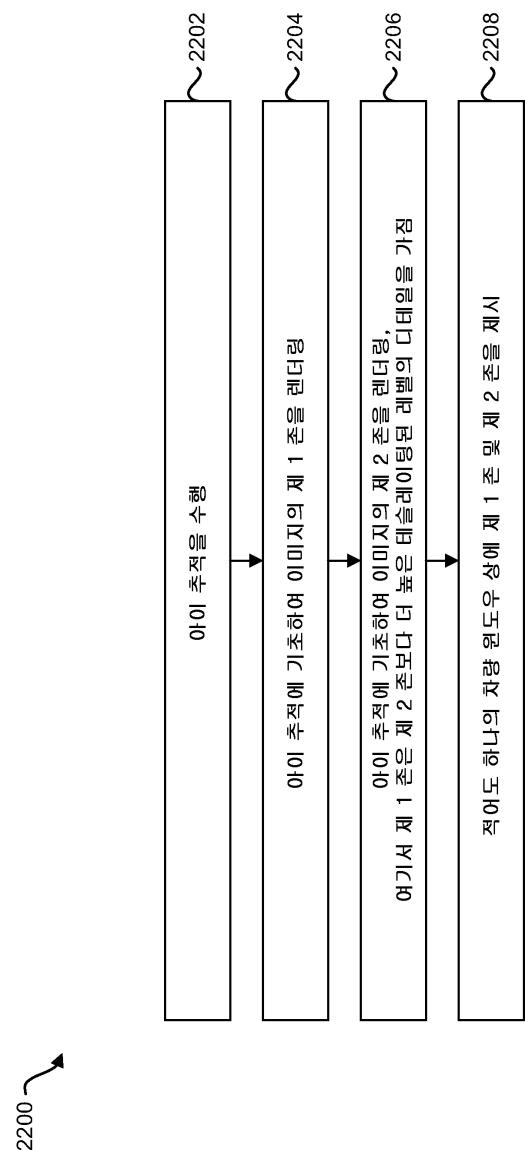

도 22 는 다수의 존들을 렌더링하는 방법의 더 많은 특정 구성 예시하는 흐름도이다;

도 23 은 윈도우 상의 존들의 다른 예를 예시하는 다이어그램이다;

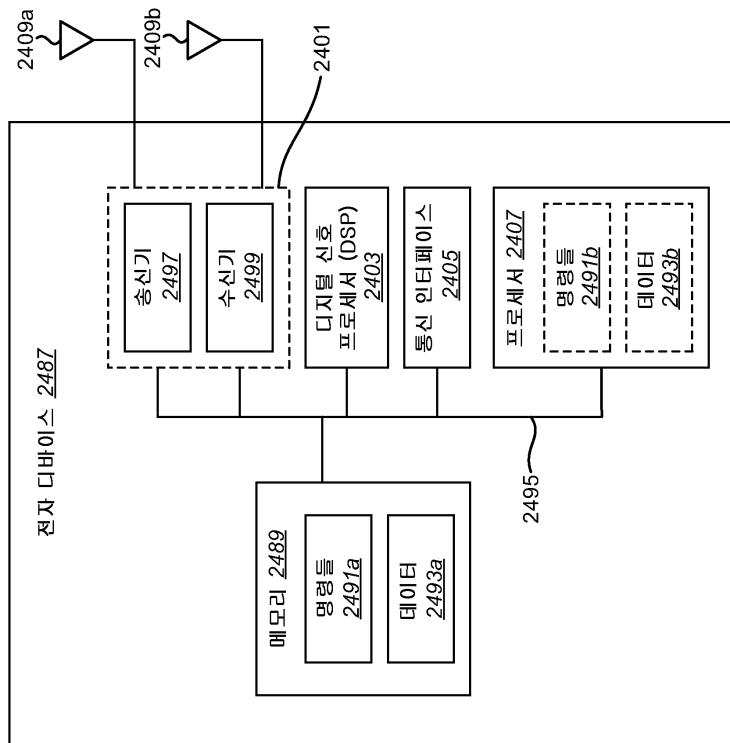

도 24 는 전자 디바이스 내에 포함될 수도 있는 소정 컴포넌트들을 예시한다.

### 발명을 실시하기 위한 구체적인 내용

[0014]

본원에 개시된 시스템들 및 방법들은 다수의 레벨들의 디테일을 렌더링하기 위한 접근들을 제공할 수도 있다. 예를 들어, 다수의 상이한 레벨들의 디테일은 동일한 이미지에서 렌더링될 수도 있다. 이것은 렌더링 효율성 및/또는 사용자 경험을 개선시킬 수도 있다. 본원에 사용된 바와 같이, 용어 "렌더" 및 그 변형들은 이미지 데이터를 생성하기 위한 하나 이상의 동작들을 수행하는 것을 의미할 수도 있다. 예를 들어, 렌더링하는 것은 지오메트리 데이터 (예를 들어, 기하학적 모델들, 정점들, 다각형들 등)를 이미지 데이터 (예를 들어, 픽셀 데이터, 픽셀들, 비주얼 도메인 데이터, 등)로 컨버팅하기 위한 하나 이상의 동작들을 수행하는 것을 포함할 수도 있다. 렌더링에서 비롯되는 이미지 데이터는 디스플레이 상에 제시되고, 저장 및/또는 송신될 수도 있다. 예를 들어, 렌더링된 이미지 데이터는 디스플레이 상에 즉시 제시되거나 또는 제시되지 않을 수도 있다. 렌더링된 이미지 데이터는 (예를 들어, 디스플레이 상의 추후의 프리젠테이션을 위해) 저장될 수도 있고, (예를 들어, 디스플레이 상에 렌더링된 이미지 데이터를 제시할 수도 있는) 다른 디바이스로 송신될 수도 있고/있거나 디스플레이 상에 제시될 수도 있다.

[0015]

렌더링 비효율성은 하나의 현재 문제일 수도 있다. 예를 들어, 가상 현실 (VR) 은 장면의 2 개의 뷰들을 렌더링하는 것을 포함할 수도 있고, 이것은 콘텐트를 렌더링하는데 2 배 느려지게 할 수도 있다. 하나의 접근은 (정확하고 저렴하게 수행될 수도 있는) 아이 추적을 수행하는 것, 상이한 레벨들의 조약함으로 3 개의 지오메트리 패스들을 렌더링하는 것, 안티-에일리어싱을 수행하는 것, 및 3 개의 상이한 프레임 버퍼 품질들을 함께 블렌딩하는 것을 수반할 수도 있다. 그러나, 이 접근은, 다수의 지오메트리 패스들이 오버랩되어 일부 픽셀들에서 반복적으로 프로세싱되는 것을 초래하기 때문에 비효율적일 수도 있다.

[0016]

일부 구성들에서, 본원에 개시된 시스템들 및 방법들은 단일-패스 멀티-레벨의 디테일 (멀티-LOD) 렌더링 (예를 들어, 단일-패스 포비에이티드 렌더링) 에 대한 접근들을 제공할 수도 있다. 예를 들어, 일부 접근들은 테슬레이터 (tessellator) (예를 들어, 테슬레이션 엔진 (tessellation engine)), 멀티샘플 안티-에일리어싱 (MSAA), 동적 커널 디스패치 및/또는 멀티-레졸루션 (예를 들어, 불-균일) 프레임 버퍼 (예를 들어, 프레임 버퍼 오브젝트 (FBO)) 를 이용할 수도 있다. 일부 접근들에서, 단지 하나의 지오메트리 패스가 필요할 수도 있다. 이 개선은 지오메트리 대역폭 사용을 감소시키고/시키거나 MSAA 를 재사용할 수도 있다.

[0017]

본원에 개시된 시스템들 및 방법들의 일부 구성들은 하나 이상의 성능 이익들을 제공할 수도 있다. 예를 들어, 멀티-레졸루션 FBO 및/또는 동적 커널 디스패치를 포함하는 하드웨어가 구현될 수도 있다. 이것은 대역폭 소비를 감소시킬 수도 있다. 예를 들어, 다수 (예를 들어, 3 개) 의 지오메트리 패스들은 테슬레이터 (예를 들어, 테슬레이션 엔진) 를 사용하여 하나로 콜랩스될 수도 있다. 래스터화 하드웨어 안티-에일리어싱이 일부 구성들에서 재사용될 수도 있다. 이것은, 규칙적인 콘텐트 렌더링에 대한 개선들을 가능하게 할 수도 있다. 부가적으로 또는 대안으로, 프래그먼트 커널들의 동적 디스패치는 연산을 감소시킬 수도 있다. 이들 개선들은 가상 현실 (VR) 및/또는 중강 현실 (AR) 의 맥락에서 특히 유리할 수도 있고, 여기서 장면의

다수의 뷔들은 (예를 들어, 입체적 뷔들을 위해) 한 번에 렌더링될 수도 있다. 일부 구성들에서, VR 및 AR은 조합될 수도 있다. 본원에 개시된 시스템들 및 방법들은, 그래픽 프로세싱 산업이 몰입형 경험들을 제공하기 위한 방식들을 검색할 때 유리할 수도 있다.

[0018] 본원에 개시된 시스템들 및 방법들은 또한, 원도우들 상의 프리젠테이션을 위한 다수의 존들을 렌더링하기 위한 접근들을 설명한다. 이들 시스템들 및 방법들은 운전자 보조 및 자율주행 차량들 (예를 들어, 셀프-드라이빙 카들)과 같은 애플리케이션들에서 사용자 경험을 강화하기 위해 차량들의 맵상에서 특히 유리할 수도 있다.

[0019] 다양한 구성들은 이제, 도면들을 참조하여 설명되고, 여기서 유사한 참조 부호들은 기능적으로 유사한 엘리먼트들을 나타낼 수도 있다. 본원에 일반적으로 설명되고 도면들에서 예시된 바와 같은 시스템들 및 방법들은 광범위한 상이한 구성들에서 배열 및 설계될 수 있다. 따라서, 도면들에서 나타난 바와 같은 여러 구성들의 다음의 더 상세한 설명은 청구하는 바와 같은 범위를 제한하도록 의도되지 않고, 단지 시스템들 및 방법들의 대표이다.

[0020] 도 1 은, 다수의 레벨들의 디테일을 렌더링하기 위한 시스템들 및 방법들이 구현될 수도 있는 전자 디바이스 (102) 의 하나의 구성을 예시하는 블록도이다. 전자 디바이스 (102) 의 예들은 스마트 폰들, 컴퓨터들 (예를 들어, 데스크톱 컴퓨터들, 랩톱 컴퓨터들, 등), 헤드-장착 디스플레이들 (예를 들어, 가상 현실 (VR) 헤드셋들, 증강 현실 (AR) 헤드셋들, 등), VR 디바이스들, AR 디바이스들, 태블릿 디바이스들, 미디어 플레이어들, 텔레비전들, 자동차들, 차량들, 카메라들, 비디오 캡코더들, 디지털 카메라들, 셀룰러 폰들, 퍼스널 카메라들, 액션 카메라들, 에어크래프트, 드론들, 무인 항공기 (UVA)들, 헬스케어 장비, 게이밍 콘솔들, 개인 휴대 정보 단말 (PDA)들, 셋-톱 박스들, 미디어 플레이어들 등을 포함한다. 전자 디바이스 (102) 는 하나 이상의 컴퓨트를 또는 엘리먼트들을 포함할 수도 있다. 컴퓨트를 또는 엘리먼트들 중 하나 이상은 하드웨어 (예를 들어, 회로부), 퀼웨어 및/또는 하드웨어와 소프트웨어 (예를 들어, 명령들을 갖는 프로세서) 의 조합에서 구현될 수도 있다.

[0021] 일부 구성들에서, 전자 디바이스 (102) 는 매우 긴 명령어 (VLIW) 회로 (104) 및 시스템 메모리 (114) 를 포함할 수도 있다. VLIW 회로 (104) 는 명령 레벨 병렬성을 구현하는 회로 (예를 들어, 프로세서) 일 수도 있다. 예를 들어, VLIW 회로 (104) 는 명령들을 병렬로 (예를 들어, 동시에) 실행시킬 수도 있다. VLIW 회로 (104) 는 시스템 메모리 (114) 에 (예를 들어, 전자 통신적으로) 커플링될 수도 있다. VLIW 회로 (104) 는 이미지들을 렌더링하기 위한 디바이스일 수도 있다. 예를 들어, VLIW 회로 (104) 는 지오메트리 데이터 (예를 들어, 기하학적 모델(들), 2-차원 (2D) 또는 3 차원 (3D) 지오메트리 데이터, 정점들, 다각형들, 등) 를 하나 이상의 이미지들로 컨버팅할 수도 있다. 결과의 이미지(들)은 하나 이상의 디스플레이들 상에 제시될 수도 있다. 예를 들어, 이미지(들)은 2D 뷔를 생성하기 위한 단일 이미지일 수도 있고 또는 3D 뷔를 생성하기 위한 다중 이미지들 (예를 들어, 입체적 이미지들) 일 수도 있다. 예를 들어, VLIW 회로 (104) 는 입체적 뷔 (예를 들어, 좌안에 대한 하나의 이미지 및 우안에 대한 다른 이미지) 를 위한 다수의 이미지들 (예를 들어, 상이한 뷔들) 을 생성할 수도 있다. VLIW 회로 (104) 는 일련의 이미지들 (예를 들어, 비디오) 을 렌더링할 수도 있다는 것이 주목되어야 한다. VLIW 회로 (104) 는 하드웨어에서 또는 하드웨어와 소프트웨어의 조합에서 구현될 수도 있다. VLIW 회로 (104) 의 일 예는 그래픽 프로세싱 유닛 (GPU) 이다.

[0022] 일부 구성들에서, 전자 디바이스 (102) 는 도 2 내지 도 5, 도 9, 도 11, 도 13, 및 도 15 내지 도 24 중 하나 이상과 연관되어 설명된 기능들, 절차들, 방법들, 단계들 등 중 하나 이상을 수행할 수도 있다. 부가적으로 또는 대안으로, 전자 디바이스 (102) 는 도 2 내지 도 5, 도 9, 도 11, 도 13 및 도 15 내지 도 24 중 하나 이상과 연관되어 설명된 구조들 중 하나 이상을 포함할 수도 있다.

[0023] 시스템 메모리 (114) 는 명령들 및/또는 데이터를 저장할 수도 있다. 시스템 메모리 (114) 의 예들은 랜덤 액세스 메모리 (RAM), 동적 랜덤 액세스 메모리 (DRAM), 동기식 동적 랜덤 액세스 메모리 (SDRAM), 이중 데이터 레이트 동기식 동적 랜덤 액세스 메모리 (DDR SDRAM), DDR2, DDR3, DDR4, 정적 랜덤 액세스 메모리 (SRAM), 레지스터들, 판독-전용 메모리 (ROM), 소거가능 프로그래머블 판독-전용 메모리 (EPROM), 전기적으로 소거 가능한 프로그래머블 판독-전용 메모리 (EEPROM), NAND 플래시 메모리, NOR 플래시 메모리 등을 포함한다. VLIW 회로 (104) 는 시스템 메모리 (114) 에 액세스 (예를 들어, 시스템 메모리로부터 판독 및/또는 시스템 메모리에 기입) 할 수도 있다. 시스템 메모리 (114) 는 하나 이상의 프로세서들 (예를 들어, 중앙 처리 장치 (CPU 들)) 과 같은 전자 디바이스 (102) 의 (있다면) 다른 엘리먼트들에 의해 액세스 가능할 수도 있다. 시스템 메모리 (114) 는 VLIW 회로 (104) 로부터 분리될 수도 있다. 시스템 메모리 (114) 에 의해 저장될 수도 있는 명령들 및/또는 데이터의 예들은 명령들, 커맨드 데이터, 지오메트리 데이터 (예를 들어, 정점들, 다각형들,

법선들 (예를 들어, 객체 배향들), 프리미티브들, 메타데이터, 등), 텍스처 데이터, 비순서화된 액세스 뷰 데이터, 렌더링 파라미터(들)(예를 들어, 디테일 파라미터(들)의 레벨)), 등을 포함할 수도 있다. 일부 구성들에서, 전자 디바이스 (102)(예를 들어, 시스템 메모리 (114))는 하나 이상의 프레임 버퍼들을 포함할 수도 있다. 프레임 버퍼(들)은 이미지 데이터를 버퍼링 (예를 들어, 저장) 할 수도 있다. 버퍼링된 이미지 데이터는 하나 이상의 디스플레이들 상에 제시될 수도 있다.

[0024] VLIW 회로 (104)는 이미지들을 렌더링하기 위한 하나 이상의 엘리먼트들을 포함할 수도 있다. 엘리먼트들의 일부 예들은 프론트 엔드 (FE), 정점 프로세서 (VP들, 정점 페처 (vertex fetcher; VF), 정점 셰이더 (vertex shader; VS), 테슬레이션 채어 셰이더 (TCS), 헬 셰이더 (hull shader; HS), 테슬레이터 (예를 들어, 테슬레이션 엔진) (TESS), 테슬레이션 평가 셰이더 (TES), 도메인 셰이더 (DS), 지오메트리 셰이더 (GS), 레스터라이저 (Rast), 프래그먼트 셰이더 (FS), 픽셀 셰이더 (PS), 타일러, 렌더 출력 유닛 (ROP), 클립퍼 (Clip) 및/또는 스트림 출력 (SOL), 등을 포함할 수도 있다. 일부 구성들에서, 이들 엘리먼트들 중 하나 이상은 그 래픽 파이프라인 (106)으로서 지정될 수도 있다. 테슬레이터는 일부 구성들에서 고정된 기능의 테슬레이션 엔진일 수도 있다는 것이 주목되어야 한다. 테슬레이터 (및/또는 그래픽 파이프라인의 하나 이상의 다른 엘리먼트들)는 하드웨어, 소프트웨어 또는 하드웨어와 소프트웨어의 조합에서 구현될 수도 있다.

[0025] VLIW 회로 (104)는 온-칩 메모리 (110)를 포함할 수도 있다. 온-칩 메모리 (110)는 빠른 메모리 액세스를 제공하도록 VLIW 회로 (104) 상에서 구현될 수도 있다. 예를 들어, 온-칩 메모리 (110)는 시스템 메모리 (114) 보다 더 빨리 액세스될 수도 있다. 온-칩 메모리 (110)의 예들은 랜덤 액세스 메모리 (RAM), 동적 랜덤 액세스 메모리 (DRAM), 동기식 동적 랜덤 액세스 메모리 (SDRAM), 이중 데이터 레이트 동기식 동적 랜덤 액세스 메모리 (DDR SDRAM), DDR2, DDR3, DDR4, 정적 랜덤 액세스 메모리 (SRAM), 레지스터들, 판독-전용 메모리 (ROM), 소거가능 프로그래머블 판독-전용 메모리 (EPROM), 전기적으로 소거 가능한 프로그래머블 판독-전용 메모리 (EEPROM), NAND 플래시 메모리, NOR 플래시 메모리 등을 포함한다. 일부 구성들에서, 온-칩 메모리 (110)는 다수의 레벨들 (예를 들어, 레벨 1 (L1) 캐시, 레벨 2 (L2) 캐시, 레벨 3 (L3) 캐시, 등)에서 구현될 수도 있다. 온-칩 메모리 (110)에 의해 저장될 수도 있는 데이터의 예들은 지오메트리 데이터 (예를 들어, 정점들, 다각형들, 법선들, 프리미티브들, 메타데이터, 등), 텍스처 데이터, 비순서화된 액세스 뷰 데이터, 하나 이상의 렌더링 파라미터들 (예를 들어, 디테일의 레벨 (LOD) 파라미터(들)), 등을 포함할 수도 있다. 일부 구성들에서, 온-칩 메모리 (110)는 (예를 들어, 시스템 메모리 (114)에 추가하여 또는 이의 대안으로) 하나 이상의 프레임 버퍼(들)을 포함할 수도 있다. 프레임 버퍼(들)은 이미지 데이터를 버퍼링 (예를 들어, 저장) 할 수도 있다. 버퍼링된 이미지 데이터는 하나 이상의 디스플레이들 상에 제시될 수도 있다.

[0026] 일부 구성들에서, VLIW 회로 (104)는 비동기식 메모리 제어기 (108)를 포함할 수도 있다. 비동기식 메모리 제어기 (108)는 하드웨어 또는 하드웨어와 소프트웨어의 조합에서 구현될 수도 있다. 비동기식 메모리 제어기 (108)는 VLIW 회로 (104)에서, VLIW 회로로부터 분리되어 구현될 수도 있고, 또는 VLIW 회로 (104)에서 부분적으로 및 VLIW 회로 (104)로부터 분리되어 부분적으로 구현될 수도 있다. 비동기식 메모리 제어기 (108)는 메모리 (예를 들어, 온-칩 메모리 (110) 및/또는 시스템 메모리 (114))에 비동기식으로 액세스하도록 구성될 수도 있다. 일부 구성들에서, 비동기식 메모리 제어기 (108)는, 비동기식 메모리 제어기 (108)가 프로세싱 (예를 들어, 테슬레이팅) 되고 있는 데이터의 세트와는 동떨어져 메모리 (예를 들어, 파라미터(들), 디테일의 레벨 (LOD) 파라미터(들), 등)에 액세스할 수 있다는 점에서 "비동기식으로" 동작한다. 예를 들어, VLIW 회로 (104)는 데이터의 세트들을 주기적으로 프로세싱할 수도 있다. 데이터의 단일 세트를 프로세싱 (예를 들어, 테슬레이팅) 하는 것은 드로우 콜 (draw call)로서 지정될 수도 있다. 예를 들어, 드로우 콜은 데이터의 세트를 프로세싱 (예를 들어, 렌더링) 하기 위한 VLIW 회로 (104)에 대한 명령 (예를 들어, 프로그래밍적 요청, 명령, 등) 일 수도 있다. 하나 이상의 파라미터들 (예를 들어, LOD 파라미터, 테슬레이션 설정, 하나 이상의 다른 파라미터들, 등)은 드로우 콜과 연관되고/되거나 이에 대한 세트일 수도 있다. 따라서, 드로우 콜은, 예를 들어 데이터의 세트에 대해 렌더링되도록 LOD를 확립할 수도 있다.

[0027] 알려진 접근들에서, 데이터 (예를 들어, 드로우 콜)의 각각의 세트는 고정된 레벨의 디테일 (LOD)을 갖는다. 이들 접근들에서, 데이터의 세트에 대한 LOD는, 일단 프로세싱이 데이터의 그 세트 상에서 시작했으면 변화할 수 없다 (예를 들어, 드로우 콜 동안 변화할 수 없다). 부가적으로, 데이터의 각각의 세트는 알려진 접근들에서 단일의 LOD만을 가질 수도 있다.

[0028] 본원에 개시된 시스템들 및 방법들에 따르면, 비동기식 메모리 제어기 (108)는 단일의 데이터 세트 내에서 (예를 들어, 드로우 콜의 프로세싱 동안) 상이한 레벨들의 디테일 (예를 들어, 상이한 레벨들의 디테일을 갖는 상

이한 존들) 을 렌더링할 수 있도록 메모리 (예를 들어, 온-칩 메모리 (110) 및/또는 시스템 메모리 (114))에 비동기식으로 액세스할 수도 있다. 예를 들어, 비동기식 메모리 제어기 (108)는 데이터의 세트 상의 프로세싱 (예를 들어, 테슬레이션, 셰이딩, 등)이 시작한 후에 그리고 데이터의 세트 상의 프로세싱이 완료되기 전에 메모리 (예를 들어, 파라미터(들), LOD 파라미터(들), 등)에 액세스할 수도 있다. 이것은 VLIW 회로 (104)가 데이터의 세트의 프로세싱 동안 LOD를 변화시켜 데이터의 하나의 세트에서 상이한 LOD들을 생성할 수 있도록 할 수도 있다. 데이터의 각각의 세트는 다수의 프리미터브들 (예를 들어, 포인트들, 다각형들, 등)을 포함할 수도 있다. 일부 구성들에서, 데이터의 각각의 세트는 (초기)에 할당된 단일의 LOD를 가질 수도 있다. 그러나, 비동기식 메모리 제어기 (108)는 데이터의 세트에 그 데이터 세트의 프로세싱 동안 상이한 LOD를 할당할 수도 있다. 다시 말해, 비동기식 메모리 제어기 (108)는 (데이터의 그 세트 상의 프로세싱 (예를 들어, 테슬레이션, 셰이딩, 등)이 시작한 후지만 데이터의 그 세트 상의 프로세싱 (예를 들어, 테슬레이션, 셰이딩, 등)이 완료되기 전에) 데이터의 세트에 대한 LOD를 변화시킬 수도 있다. 예를 들어, 본원에 개시된 시스템들 및 방법들은 (예를 들어, 데이터의 세트 내에서도) 광센-당 및/또는 프리미터브 단위-당 LOD를 변화시키는 것을 허용할 수도 있다. 일부 구성들에서, 파라미터들 (예를 들어, 파라미터(들), LOD 파라미터(들), 등)은 프로세싱 동안 업데이트될 수도 있다. 예를 들어, 프로세서 (예를 들어, 중앙 처리 장치 (CPU), 디지털 신호 프로세서 (DSP), 등) 또는 임의의 전용 하드웨어 블록 (예를 들어, 센서 데이터 (예를 들어, 아이 추적 센서 데이터, 모션 센서 데이터, 등)을 처리하는 임의의 하드웨어)이 파라미터들을 업데이트 할 수도 있다. VLIW 회로 (104) (예를 들어, GPU)는 파라미터들을 포함하는 메모리의 섹션 (예를 들어, 온-칩 메모리 (110) 및/또는 시스템 메모리 (114))으로부터 판독할 수도 있다 (예를 들어, 항상 판독하고, 연속적으로 판독하고, 주기적으로 판독 등을 할 수도 있다). 따라서, VLIW 회로 (104) (예를 들어, GPU)는 전체 드로우 콜에 대한 것 대신에 프리미터브마다 대응하여 조정할 수도 있다. 일부 구성들에서, VLIW 회로 (104)는 단일의 드로우 콜에서 상이한 레벨들의 디테일을 렌더링할 수도 있다.

[0029] 본원에 개시된 시스템들 및 방법들은 하나 이상의 이점들을 제공할 수도 있다. 예를 들어, 비동기식 메모리 제어기 (108)는, 다수의 LOD들을 렌더링하는 경우 더 효율적인 프로세싱을 가능하게 할 수도 있다. 알려진 접근들에서, 다수의 오버랩하는 층들이 렌더링될 수도 있고, 여기서 각각의 층은 상이한 LOD를 갖는다. 그 후, 오버랩하는 층들은 블렌딩될 수도 있다. 그러나, 이 접근은, 동일한 데이터가 여러 번 렌더링되기 때문에 비효율적이다. 본원에 개시된 시스템들 및 방법들에 따르면, 상이한 LOD들이 단일 패스로 렌더링될 수도 있다. 이것은 동일한 데이터를 재-렌더링하는 것을 회피하고/하거나 상이한 레벨들의 디테일을 갖는 다수의 층들을 블렌딩하는 것을 회피할 수도 있다.

[0030] 부가적으로 또는 대안으로, 본원에 개시된 시스템들 및 방법들은 LOD를 비동기식으로 변화시키는 것을 허용할 수도 있다. 예를 들어, 이미지의 하나 이상의 존들을 렌더링하는 것은 아이 추적에 기초할 수도 있다. 예를 들어, 전자 디바이스 (102)는 상이한 레벨들의 디테일을 갖는 다수의 존들을 렌더링할 수도 있고, 여기서 최고 레벨의 디테일을 갖는 존은 사용자가 현재 보고 있는 영역에서 렌더링된다. 아이 추적은, 사용자가 이미지의 상이한 부분을 살피도록 시선을 변화시키는 때를 검출할 수도 있다. 본원에 개시된 시스템들 및 방법들 (예를 들어, 비동기식 메모리 제어기 (108))은 아이 추적에 기초하여 렌더링된 LOD를 즉시 변화시킬 수도 있다. 예를 들어, VLIW 회로 (104)는, 데이터 세트의 프로세싱 동안에도, 사용자가 보기 위해 시선을 변화시킨 이미지의 영역에서 LOD를 증가시킬 수도 있다. 이것은 더 좋은 사용자 경험을 제공할 수도 있다.

부가적으로, 본원에 개시된 시스템들 및 방법들 (예를 들어, 비동기식 메모리 제어기 (108))은 사용자의 시선이 더 이상 지향하지 않는 이미지의 영역에서 LOD를 감소시킬 수도 있다. 이것은 불필요한 프로세싱을 감소시킬 수도 있다.

[0031] VLIW 회로 (104)는 불-균일 프레임 버퍼 제어기 (112)를 포함할 수도 있다. 불-균일 프레임 버퍼 제어기 (112) (예를 들어, 멀티-레벨루션 FBO)는 하드웨어 또는 하드웨어와 소프트웨어의 조합에서 구현될 수도 있다.

불-균일 프레임 버퍼 제어기 (112)는 VLIW 회로 (104)에서, VLIW 회로로부터 분리되어 구현될 수도 있고, 또는 VLIW 회로 (104)에서 부분적으로 및 VLIW 회로 (104)로부터 분리되어 부분적으로 구현될 수도 있다.

일부 구성들에서, 불-균일 프레임 버퍼 제어기 (112)는 그래픽 파이프라인 (106)의 부분으로서 구현될 수도 있다. 대안으로, 불-균일 프레임 버퍼 제어기 (112)는 온-칩 메모리 (110)의 부분으로서 구현될 수도 있다. 다른 구현에서, 불-균일 프레임 버퍼 제어기 (112)는 VLIW 회로 (104)에서 구현되지만 그래픽 파이프라인 (106) 및 온-칩 메모리 (110)로부터 분리되어 구현될 수도 있다.

[0032] 불-균일 프레임 버퍼 제어기 (112)는 하나 이상의 프레임 버퍼(들)의 상이한 서브세트들에 동적으로 액세스하도록 구성될 수도 있다. 일부 구성들에서, 프레임 버퍼의 상이한 서브세트들은 상이한 레벨들의 디테일, 상

이한 레벨들의 디테일을 갖는 존들 및/또는 상이한 맵맵 레벨들에 대응할 수도 있다. 예를 들어, 불-균일 프레임 버퍼 제어기 (112)는 프레임 버퍼의 상이한 서브세트들 상에서 동적으로 동작하도록 구성될 수도 있다.

2 이상의 프레임 버퍼 서브세트들이 존재할 수도 있다는 것이 주목되어야 한다. 일부 구성들에서, 불균일 프레임 버퍼의 상이한 서브세트들은 상이한 뷰들 (예를 들어, 입체적 렌더링을 위한 좌안 뷰 및 우안 뷰)에 대응할 수도 있다. 불-균일 프레임 버퍼는 대역폭 이용을 개선시킬 수도 있다. 불-균일 프레임 버퍼로, 예를 들어 좌안 뷰 및 우안 뷰는 하나의 패스로, 동시에 (예를 들어, 일제히) 프로세싱되고 시스템 메모리 (114)에 저장될 수도 있다. 부가적으로 또는 대안으로, 예를 들어 불균일 프레임 버퍼는 하나의 패스로 다수의 LOD들을 렌더링하기 위한 메모리 이용을 가능하게 하고/하거나 개선시킬 수도 있다.

[0033]

일부 구성들에서, 프레임 버퍼의 상이한 서브세트들에 동적으로 액세스하는 것은 제 2 존의 적어도 하나의 픽셀과는 상이한 레이트에서 제 1 존의 적어도 하나의 픽셀에 액세스하는 것을 포함할 수도 있다. 제 1 존 및 제 2 존은 상이한 레벨들의 디테일에 대응할 수도 있다. 예를 들어, 불-균일 프레임 버퍼 제어기 (112)는 (예를 들어, 더 높은 LOD를 갖는) 하나의 존의 픽셀들이 (예를 들어, 더 낮은 LOD를 갖는) 다른 존의 픽셀들 보다 더 높은 레이트에서 프로세싱되게 할 수도 있다. 이 접근은 하나 이상의 존들 (예를 들어, 더 낮은-LOD 존들)의 프로세싱을 천천히함으로써 전력 절감을 허용할 수도 있다. 2 이상의 상이한 레이트들에서 액세스될 수도 있는 2 이상의 존들로부터의 픽셀들이 존재할 수도 있다는 것이 주목되어야 한다.

[0034]

부가적으로 또는 대안으로, 프레임 버퍼의 상이한 서브세트들에 동적으로 액세스하는 것은 세이더 서브-루틴 스왑핑을 가능하게 하는 것을 포함할 수도 있다. 예를 들어, 세이더 서브-루틴 스왑핑은, 제 1 픽셀의 프로세싱이 진행 중이고 제 2 픽셀의 프로세스가 완료되는 경우 수행될 수도 있다. 예를 들어, 프레임 버퍼의 제 1 서브세트는 제 1 세이더 서브-루틴으로 프로세싱된 하나 이상의 픽셀들에 대해 할당될 수도 있는 한편, 프레임 버퍼의 제 2 서브세트는 제 2 세이더 서브-루틴으로 프로세싱된 하나 이상의 픽셀들에 대해 할당될 수도 있다. 하나 이상의 제 2 세이더 서브-루틴 픽셀들의 프로세싱이 완료될 때, 전자 디바이스 (102)는 프레임 버퍼의 제 2 서브세트를 차지하도록 세이더 서브-루틴들을 스왑핑할 수도 있다. 이것은 프레임 버퍼 능력이 더 효율적으로 이용될 수 있도록 함으로써 더 효율적인 프로세싱을 제공할 수도 있다. 프레임 버퍼의 2 이상의 서브세트들은 서브세트들 중 하나 이상에 대한 서브-루틴 스왑핑을 가능하게 하도록 이용될 수도 있다는 것이 주목되어야 한다.

[0035]

불-균일 프레임 버퍼 제어기 (112)는 제 2 픽셀의 제 2 샘플을 제 1 픽셀의 프로세싱된 제 1 샘플로 대체하여 제 2 픽셀의 제 2 샘플을 프로세싱하는 것을 회피하도록 구성될 수도 있다. 제 1 픽셀은 제 2 픽셀과는 상이한 상이한 수의 샘플들을 가질 수도 있다. 예를 들어, 제 1 존으로부터의 제 1 픽셀은 더 낮은 LOD를 갖는 제 2 존으로부터 이웃하는 제 2 픽셀보다 더 높은 LOD를 가질 수도 있다. 불-균일 프레임 버퍼 제어기 (112)는 제 2 픽셀의 (프로세싱되지 않은) 샘플을 제 1 픽셀의 (프로세싱된) 샘플로 대체할 수도 있다. 이 방식에서, 불-균일 프레임 버퍼 제어기 (112)는 프로세싱을 감소시킬 수도 있다. 불-균일 프레임 버퍼 제어기 (112)는 하나 이상의 픽셀들의 하나 이상의 (프로세싱되지 않은) 샘플들을 하나 이상의 다른 픽셀들의 하나 이상의 (프로세싱된) 샘플들로 대체할 수도 있다는 것이 주목되어야 한다.

[0036]

일부 구성들에서, 전자 디바이스 (102)는 하나 이상의 디스플레이들 (예를 들어, 헤드-장착 디스플레이들)을 포함할 수도 있고/있거나 이에 커플링될 수도 있다. 디스플레이(들)은 상이한 레벨들의 디테일을 제시하도록 구성될 수도 있다.

[0037]

도 2는 다수의 레벨들의 디테일을 렌더링하는 방법 (200)의 하나의 구성을 예시하는 흐름도이다. 방법 (200)은 도 1과 연관되어 설명된 전자 디바이스 (102)에 의해 수행될 수도 있다.

[0038]

전자 디바이스 (102)는 지오메트리 데이터를 획득할 수도 있다 (202). 예를 들어, 전자 디바이스 (102)는 스토리지 (예를 들어, 하드 디스크 스토리지, 착탈형 스토리지, 예컨대 외부 하드 드라이브, 디지털 비디오 디스크 (DVD) 드라이브, 블루-레이 드라이브, 컴팩트 디스크 (CD), 셀 드라이브, 등)로부터의 지오메트리 데이터를 메모리 (예를 들어, 시스템 메모리 (114) 및/또는 온-칩 메모리 (110))로 로딩할 수도 있다. 부가적으로 또는 대안으로, 전자 디바이스 (102)는 다른 디바이스로부터 지오메트리 데이터를 수신할 수도 있다. 예를 들어, 전자 디바이스 (102)는 통신 인터페이스 (예를 들어, 이더넷, 전기전자 협회 (IEEE) 802.11 인터페이스, 셀룰러 네트워크 인터페이스, 등)를 통해 지오메트리 데이터를 수신하고, 지오메트리 데이터를 메모리 (예를 들어, 시스템 메모리 (114) 및/또는 온-칩 메모리 (110))로 로딩할 수도 있다. 지오메트리 데이터의 예들은 포인트들, 라인들 및/또는 다각형들 (예를 들어, 삼각형들), 등을 포함할 수도 있다.

[0039]

전자 디바이스 (102)는 상이한 레벨들의 디테일을 비동기식으로 렌더링할 수도 있다 (204). 이것은 도 1

과 연관되어 전술된 바와 같이 달성될 수도 있다. 예를 들어, 전자 디바이스 (102)는 메모리 (예를 들어, 시스템 메모리 (114) 및/또는 온-칩 메모리 (110))에 비동기식으로 액세스하여 상이한 레벨들의 디테일을 렌더링할 수도 있다. 예를 들어, 전자 디바이스 (102)는 프로세싱 동안 데이터의 세트에 대한 LOD를 변화시킬 수도 있다 (여기서, 예를 들어 데이터의 세트는 처음에 상이한 LOD를 갖는다). 일부 구성들에서, 상이한 레벨들의 디테일을 비동기식으로 렌더링하는 것 (204)은 동적 LOD 테슬레이션을 수행하는 것을 포함할 수도 있다.

[0040] 전자 디바이스 (102)는 프레임 버퍼의 상이한 서브세트들에 동적으로 액세스할 수도 있다 (206). 이것은 도 1과 연관되어 전술된 바와 같이 달성될 수도 있다. 예를 들어, 전자 디바이스 (102)는 제 2 존의 적어도 하나의 픽셀과는 상이한 레이트에서 제 1 존의 적어도 하나의 픽셀에 액세스할 수도 있다. 부가적으로 또는 대안으로, 전자 디바이스 (102)는, 제 1 픽셀의 프로세싱이 진행 중이고 제 2 픽셀의 프로세스가 완료되는 경우 세이더 서브-루틴 스왑핑을 가능하게 할 수도 있다. 부가적으로 또는 대안으로, 전자 디바이스 (102)는 제 2 픽셀의 제 2 샘플을 제 1 픽셀의 프로세싱된 제 1 샘플로 대체하여 제 2 픽셀의 제 2 샘플을 프로세싱하는 것을 회피할 수도 있다.

[0041] 도 3은, 다수의 레벨들의 디테일을 렌더링하기 위한 시스템들 및 방법들이 구현될 수도 있는 전자 디바이스 (302)의 하나의 구성을 예시하는 블록도이다. 도 3과 연관되어 설명된 전자 디바이스 (302)는 도 1과 연관되어 설명된 전자 디바이스 (102)의 예일 수도 있다. 일부 구성들에서, 전자 디바이스 (302)의 컴포넌트들 또는 엘리먼트들 중 하나 이상은 도 1과 연관되어 설명된 대응하는 컴포넌트들 또는 엘리먼트들과 유사할 수도 있다. 컴포넌트들 또는 엘리먼트들 중 하나 이상은 하드웨어 (예를 들어, 회로부) 또는 하드웨어와 소프트웨어 (예를 들어, 명령들을 갖는 프로세서)의 조합에서 구현될 수도 있다.

[0042] 일부 구성들에서, 전자 디바이스 (302)는 매우 긴 명령어 (VLIW) 회로 (304), 시스템 메모리 (314), 하나 이상의 디스플레이들 (332), 하나 이상의 이미지 센서들 (316), 하나 이상의 광학 시스템들 (318), 하나 이상의 통신 인터페이스들 (320), 하나 이상의 안테나들 (322) 및/또는 하나 이상의 프로세서들 (324)을 포함할 수도 있다. 도 3과 연관되어 설명된 엘리먼트들 또는 컴포넌트들 중 2 이상은 서로와 전자 통신할 수도 있다. 예를 들어, VLIW 회로 (304)는 시스템 메모리 (314)에 (예를 들어, 전자 통신적으로) 커플링될 수도 있다.

VLIW 회로 (304)는 도 1 및 도 2 중 하나 이상과 연관되어 전술된 바와 같이 이미지들을 렌더링하기 위한 디바이스일 수도 있다. 일부 구성들에서, 결과의 이미지(들)은 하나 이상의 디스플레이들 (332) 상에 제시될 수도 있다. VLIW 회로 (304)는 일부 구현들에서 프로세서 (324)로부터 분리될 수도 있다. 다른 구현들에서, VLIW 회로 (304)는 프로세서 (324) 안에 통합될 수도 있다.

[0043] 통신 인터페이스 (320)는 전자 디바이스 (302)가 하나 이상의 다른 전자 디바이스들과 통신하게 할 수도 있다. 예를 들어, 통신 인터페이스 (320)는 유선 및/또는 무선 통신을 위해 인터페이스를 제공할 수도 있다. 일부 구성들에서, 통신 인터페이스 (320)는 무선 주파수 (RF) 신호들을 송신 및/또는 수신하기 위해 하나 이상의 안테나들 (322)에 커플링될 수도 있다. 부가적으로 또는 대안으로, 통신 인터페이스 (320)는 하나 이상의 종류들의 와이어라인 (예를 들어, 유니버설 시리얼 버스 (USB), 이더넷, 비디오 그래픽 어레이 (VGA), 디지털 비주얼 인터페이스 (DVI), 고화질 멀티미디어 인터페이스 (HDMI), 디스플레이포트, 모바일 고-화질 링크 (MHL), 등) 통신을 가능하게 할 수도 있다.

[0044] 일부 구성들에서, 다수의 통신 인터페이스들 (320)이 구현 및/또는 이용될 수도 있다. 예를 들어, 하나의 통신 인터페이스 (320)는 셀룰러 (예를 들어, 3G, 롱 텀 애볼루션 (LTE), CDMA, 등) 통신 인터페이스 (320)일 수도 있고, 다른 통신 인터페이스 (320)는 이더넷 인터페이스일 수도 있고, 다른 통신 인터페이스 (320)는 유니버설 시리얼 버스 (USB) 인터페이스일 수도 있고, 또 다른 통신 인터페이스 (320)는 무선 로컬 영역 네트워크 (WLAN) 인터페이스 (예를 들어, 전기전자 협회 (IEEE) 802.11 인터페이스)일 수도 있으며, 또 다른 통신 인터페이스 (320)는 블루투스 인터페이스일 수도 있다.

[0045] 일부 구성들에서, 전자 디바이스 (302)는 도 1, 도 3 내지 도 5, 도 9, 도 11, 도 13, 및 도 15 내지 도 24 중 하나 이상과 연관되어 설명된 기능들, 절차들, 방법들, 단계들 등 중 하나 이상을 수행할 수도 있다. 부가적으로 또는 대안으로, 전자 디바이스 (302)는 도 1, 도 3 내지 도 5, 도 9, 도 11, 도 13 및 도 15 내지 도 24 중 하나 이상과 연관되어 설명된 구조들 중 하나 이상을 포함할 수도 있다.

[0046] 시스템 메모리 (314)는 명령들 및/또는 데이터를 저장할 수도 있다. 도 3과 연관되어 설명된 시스템 메모리 (314)는 도 1과 연관되어 설명된 시스템 메모리 (114)의 예일 수도 있다. VLIW 회로 (304)는 시스템 메모리 (314)에 액세스 (예를 들어, 시스템 메모리로부터 판독 및/또는 시스템 메모리에 기입) 할 수도 있다.

시스템 메모리 (314)는 또한, 프로세서(들)(324)에 의해 액세스 가능할 수도 있다. 시스템 메모리 (314)는 지오메트리 데이터 (328)를 저장할 수도 있다. 일부 구성들에서, 시스템 메모리 (314)는 프레임 버퍼 (330a)를 포함할 수도 있다. 프레임 버퍼 (330a)는 이미지 데이터를 저장하기 위한 시스템 메모리 (314)의 일부일 수도 있다. 버퍼링된 이미지 데이터는 일부 구성들에서 하나 이상의 디스플레이들 (332) 상에 제시될 수도 있다.

[0047] VLIW 회로 (304)는 이미지들을 렌더링하기 위한 하나 이상의 엘리먼트들을 포함할 수도 있다. 엘리먼트들의 일부 예들은 프론트 엔드 (FE), 정점 프로세서 (VP들), 정점 폐처 (VF), 정점 세이더 (VS), 테슬레이션 제어 세이더 (TCS), 혈 세이더 (HS), 테슬레이터 (예를 들어, 테슬레이션 엔진) (TESS), 테슬레이션 평가 세이더 (TES), 도메인 세이더 (DS), 지오메트리 세이더 (GS), 래스터라이저 (Rast), 프래그먼트 세이더 (FS), 퍽셀 세이더 (PS), 타일러, 렌더 출력 유닛 (ROP), 클립퍼 (Clip) 및/또는 스트림 출력 (SOL), 등을 포함할 수도 있다. 일부 구성들에서, 이들 엘리먼트들 중 하나 이상은 그래픽 파이프라인으로서 지정될 수도 있다.

[0048] VLIW 회로 (304)는 온-칩 메모리 (310)를 포함할 수도 있다. 도 3 과 연관되어 설명된 온-칩 메모리 (310)는 도 1 과 연관되어 설명된 온-칩 메모리 (110)의 예일 수도 있다. 일부 구성들에서, 온-칩 메모리 (310)는 (예를 들어, 시스템 메모리 (314)에서 프레임 버퍼 (330a)에 추가하여 또는 이의 대안으로) 프레임 버퍼 (330a)를 포함할 수도 있다. 프레임 버퍼는 이미지 데이터를 저장하기 위한 온-칩 메모리 (310)의 일부일 수도 있다. 버퍼링된 이미지 데이터는 일부 구성들에서 하나 이상의 디스플레이들 (332) 상에 제시될 수도 있다.

[0049] 일부 구성들에서, VLIW 회로 (304)는 비동기식 메모리 제어기 (308)를 포함할 수도 있다. 비동기식 메모리 제어기 (308)는 하드웨어 또는 하드웨어와 소프트웨어의 조합에서 구현될 수도 있다. 비동기식 메모리 제어기 (308)는 VLIW 회로 (304)에서, VLIW 회로로부터 분리되어 구현될 수도 있고, 또는 VLIW 회로 (304)에서 부분적으로 및 VLIW 회로 (304)로부터 분리되어 부분적으로 구현될 수도 있다. 비동기식 메모리 제어기 (308)는 메모리 (예를 들어, 온-칩 메모리 (310) 및/또는 시스템 메모리 (314))에 비동기식으로 액세스하도록 구성될 수도 있다. 비동기식 메모리 제어기 (308)는 온-칩 메모리 (110) 및/또는 시스템 메모리 (114) (예를 들어, 어느 하나 또는 양자 모두)를 이용 (예를 들어, 액세스) 할 수도 있다. 일부 구성들은 사용 케이스에 의존할 수도 있다. 예를 들어, 센서 데이터 (예를 들어, 이미지 센서 (316) 데이터)가 고레이트 (예를 들어, 1000 헤르츠 (Hz))에서 기입된다면, 캐싱은 시간, 배터리 및/또는 다른 리소스들을 낭비할 수도 있다. 도 3 과 연관되어 설명된 비동기식 메모리 제어기 (308)는 도 1 과 연관되어 설명된 비동기식 메모리 제어기 (108)의 일 예일 수도 있다. 도 3 과 연관되어 설명된 비동기식 메모리 제어기 (308)는 도 1 과 연관되어 설명된 비동기식 메모리 제어기 (108)와 연관되어 설명된 바와 같이 동작할 수도 있다.

[0050] VLIW 회로 (304)는 불-균일 프레임 버퍼 제어기 (312)를 포함할 수도 있다. 불-균일 프레임 버퍼 제어기 (312)는 하드웨어 또는 하드웨어와 소프트웨어의 조합에서 구현될 수도 있다. 불-균일 프레임 버퍼 제어기 (312)는 VLIW 회로 (304)에서, VLIW 회로로부터 분리되어 구현될 수도 있고, 또는 VLIW 회로 (304)에서 부분적으로 및 VLIW 회로 (304)로부터 분리되어 부분적으로 구현될 수도 있다. 일부 구성들에서, 불-균일 프레임 버퍼 제어기 (312)는 그래픽 파이프라인의 부분으로서 구현될 수도 있다. 대안으로, 불-균일 프레임 버퍼 제어기 (312)는 온-칩 메모리 (310)의 부분으로서 구현될 수도 있다. 다른 구현에서, 불-균일 프레임 버퍼 제어기 (312)는 VLIW 회로 (304)에서 구현되지만 그래픽 파이프라인 (306) 및 온-칩 메모리 (310)로부터 분리되어 구현될 수도 있다. 도 3 과 연관되어 설명된 불-균일 프레임 버퍼 제어기 (312)는 도 1 과 연관되어 설명된 불-균일 프레임 버퍼 제어기 (112)의 예일 수도 있다. 도 3 과 연관되어 설명된 불-균일 프레임 버퍼 제어기 (312)는 도 1 과 연관되어 설명된 불-균일 프레임 버퍼 제어기 (112)와 연관되어 설명된 바와 같이 동작할 수도 있다.

[0051] 일부 구성들에서, 전자 디바이스 (302)는 단일-패스 멀티-LOD 렌더링을 수행할 수도 있다. 멀티-LOD 렌더링은 상이한 레벨들의 디테일을 갖는 이미지의 상이한 존들을 렌더링하는 것을 포함할 수도 있다. 단일-패스 멀티-LOD 렌더링은 (예를 들어, 임의의 퍽셀을 반복적으로 프로세싱하지 않고) 단일 패스로 상이한 레벨들의 디테일 (예를 들어, 테슬레이팅된 레벨들의 디테일)을 갖는 상이한 존들을 렌더링하는 것을 포함할 수도 있다.

단일-패스 포비에이티드 렌더링은 단일-패스 멀티-LOD 렌더링의 예일 수도 있고, 여기서 상이한 레벨들의 디테일을 갖는 상이한 존들은 아이 추적에 기초할 수도 있다. 예를 들어, 존은 사용자가 보고 있는 디스플레이의 포인트 (예를 들어, 이미지) 상에 거의 센터링된 원형 영역 (또는 다른 형상의 영역) 일 수도 있다. 부가적으로 또는 대안으로, 단일-패스 렌더링 (예를 들어, 단일-패스 멀티-LOD 렌더링)은, 좌안 뷰 및 우안 뷰 양자 모두가 렌더링될 필요가 있더라도, 렌더링될 데이터 및/또는 텍스처에 걸쳐 하나의 패스 (예를 들어, 프로

세션 패스)를 수행하는 것을 포함할 수도 있다. 따라서, 본원에 개시된 시스템들 및 방법들의 일부 구성들은 시스템 메모리와 온-칩 메모리(예를 들어, GPU 메모리)간에 데이터를 이동시키기 전에 가능한 한 많이 양쪽 아이 뷰들에 대한 많은 데이터를 이용할 수도 있다. 일부 구성들에서, 비동기식 메모리 제어기(308) 및 /또는 불-균일 프레임 버퍼 제어기(312)는 단일-패스 멀티-LOD 렌더링(예를 들어, 단일-패스 포비에이티드 렌더링)의 수행을 가능하게 할 수도 있다. 예를 들어, 비동기식 메모리 제어기(308)는 휘발성 메모리 블록으로부터 파라미터(들)(예를 들어, 디테일의 레벨(LOD) 파라미터(들))을 판독(예를 들어, 드로우 콜 동안 동적으로 적응)하는 것을 허용할 수도 있다. 예를 들어, 비동기식 메모리 제어기(308)는 테슬레이션 제어 세이더(TCS), 테슬레이터(TESS), 테슬레이션 평가 세이더(TES), 지오메트리 세이더(GS), 레스터화 및 프래그먼트 세이더(FS)가(예를 들어, 드로우 콜 동안 동적으로 적응시키기 위해) 휘발성 메모리 블록으로부터 하나 이상의 파라미터들에 액세스할 수 있도록 할 수도 있다.

[0052] 일부 구성들에서, VLIW 회로(304)는 레스터라이저를 포함할 수도 있다. 레스터라이저는 MSAA가 프리미티브들의 더 많은 샘플링을 수행하게 할 수도 있고, 이것은 또한 더 많은 프래그먼트 세이더(FS) 평가들을 활성화시킬 수도 있다. 부가적으로, 프리미티브들의 샘플링은, 프로세싱되고 평균화되고 있는 샘플들이 충분하지 않기 때문인, 재기(jaggy)들과 같은 아티팩트들을 방지하도록 수행될 수도 있다.

[0053] 전자 디바이스(302)는 하나 이상의 이미지들(예를 들어, 디지털 이미지들, 이미지 프레임들, 비디오 등)을 획득할 수도 있다. 하나 이상의 이미지들은 하나 이상의 사용자들의 이미지들 및/또는 장면(예를 들어, 하나 이상의 객체들 및/또는 배경)일 수도 있다. 예를 들어, 전자 디바이스(302)는 하나 이상의 이미지 센서들(316) 및/또는 광학 시스템(들)(318)의 시야 내에 위치되는 객체들의 이미지들을 이미지 센서(들)(316)상으로 포커싱하는 하나 이상의 광학 시스템들(318)(예를 들어, 렌즈들)을 포함할 수도 있다. 일부 구성들에서, 이미지 센서(들)(316)은 하나 이상의 이미지들을 캡처할 수도 있다. 이미지 센서(들)(316) 및/또는 광학 시스템(들)(318)은 프로세서(324)에 커플링되고/되거나 이에 의해 제어될 수도 있다.

[0054] 부가적으로 또는 대안으로, 전자 디바이스(302)는 다른 디바이스(예를 들어, 전자 디바이스(302)에 커플링된 외부 이미지 센서, 네트워크 서버, 트래픽 카메라, 드롭 카메라, 자동차 카메라, 웹 카메라, 등)로부터 하나 이상의 이미지들을 요청 및/또는 수신할 수도 있다. 일부 구성들에서, 전자 디바이스(302)는 통신 인터페이스(320)를 통해 하나 이상의 이미지들을 요청 및/또는 수신할 수도 있다. 예를 들어, 전자 디바이스(302)는 카메라(예를 들어, 이미지 센서(316) 및/또는 광학 시스템(318))를 포함하거나 포함하지 않을 수도 있고, 원격 디바이스로부터 이미지들을 수신할 수도 있다.

[0055] 일부 구성들에서, 전자 디바이스(302)에 포함된 하나 이상의 이미지 센서들(316) 및/또는 전자 디바이스(302)에 커플링된 하나 이상의 다른 이미지 센서들은 사용자의 하나 이상의 이미지들을 캡처하도록 배향될 수도 있다. 예를 들어, 스마트폰은 디스플레이(예를 들어, 디스플레이(332))와 동일한 면상에 장착된 카메라를 포함할 수도 있다. 이 방식에서, 카메라는, 사용자가 디스플레이를 보고 있는 동안 사용자의 이미지들을 캡처할 수도 있다. 다른 예에서, 카메라는 사용자(예를 들어, 운전자)의 이미지들을 캡처하도록 차량의 콘솔 및/또는 스티어링 휠에 장착될 수도 있다.

[0056] 부가적으로 또는 대안으로, 전자 디바이스(302)에 포함된 하나 이상의 이미지 센서들(316) 및/또는 전자 디바이스(302)에 커플링된 하나 이상의 다른 이미지 센서들은 풍경을 캡처하도록 배향될 수도 있다. 예를 들어, 하나 이상의 카메라들은 스마트 폰의 뒷면에 장착될 수도 있다. 다른 예에서, 하나 이상의 카메라들은 차량의 외부에 장착될 수도 있다. 일부 구성들에서, 전자 디바이스(302)는 중강 현실(AR) 애플리케이션들, 가상 현실(VR) 애플리케이션들 및/또는 다른 애플리케이션들(예를 들어, 전망뷰 시각화, 운전자 보조, 운전자 보조 시스템들(ADAS), 등)에서 풍경의 이미지들을 이용할 수도 있다.

[0057] 일부 구성들에서, 이미지 센서(들)(316)에 의해 캡처되고/되거나 통신 인터페이스(들)(320)을 통해 수신된 이미지(들)은 아이 추적을 위해 전자 디바이스(302)에 의해 이용될 수도 있다. 예를 들어, 프로세서(324)는 아이 추적기(326)를 포함 및/또는 구현할 수도 있다. 아이 추적기(326)는 하나 이상의 사용자들의 눈(들)의 시선(예를 들어, 주시 방향(look direction))을 추적할 수도 있다. 예를 들어, 아이 추적기(326)는 이미지(들)에 하나 이상의 사용자들의 눈(들)을 위치시킬 수도 있고 사용자(들)의 시선(예를 들어, 주시 방향)을 추정할 수도 있다. 예를 들어, 아이 추적기(326)는, 사용자가 디스플레이(예를 들어, 디스플레이(332) 또는 외부 디스플레이)상에서 보고 있는 곳 및/또는 사용자가 디스플레이에 의해 제시된 이미지 상에서 보고 있는 곳을 결정(예를 들어, 추정)할 수도 있다. 다시 말해, 아이 추적기(326)는, 사용자의 시선이 이미지 및/또는 디스플레이에 대해 지향되는 곳을 결정(예를 들어, 추정)할 수도 있다.

[0058]

본원에 개시된 시스템들 및 방법들은 단일 패스로 LOD 를 비동기식으로 변화시키고/시키거나 다수의 레벨들의 디테일을 렌더링하는 것을 허용할 수도 있다. 일부 구성들에서, 이미지의 하나 이상의 존들을 렌더링하는 것은 아이 추적에 기초할 수도 있다. 이미지의 존들은 상이한 레벨들의 디테일을 가질 수도 있다. 예를 들어, 전자 디바이스 (302) 는 상이한 레벨들의 디테일을 갖는 다수의 존들을 렌더링할 수도 있고, 여기서 최고 레벨의 디테일을 갖는 존은 사용자가 현재 보고 있는 영역에서 렌더링된다. 일부 구성들에서, 이것은 포비 에이티드 렌더링으로서 지칭될 수도 있다. 아이 추적기 (326) 는 아이 추적 정보를 생성할 수도 있다. 아이 추적 정보는, 사용자의 시선이 디스플레이 및/또는 이미지에 대해 지향되는 (예를 들어, 사용자들의 시선이 지향되는) 곳을 나타낼 수도 있다. 일부 구성들에서, 프로세서 (324) 및/또는 VLIW 회로 (304) 는 아이 추적 정보에 기초하여 하나 이상의 LOD 파라미터들을 결정할 수도 있다. LOD 파라미터(들)은 이미지의 하나 이상의 존들에 대해 렌더링될 LOD 를 나타낼 수도 있다. LOD 파라미터(들)은 시스템 메모리 (314) 및/또는 온-칩 메모리 (310) 에 저장될 수도 있다. LOD 파라미터(들)은 VLIW 회로 (304) 에 의해 프로세싱되고 있는 데이터의 세트 (예를 들어, 드로우 콜) 와 관련되어 비동기식으로 업데이트될 수도 있다. 비동기식 메모리 제어기 (308) 는 데이터 세트 (예를 들어, 드로우 콜) 의 프로세싱 동안 (시스템 메모리 (314) 및/또는 온-칩 메모리 (310)로부터) LOD 파라미터(들)을 판독할 수도 있다. 예를 들어, 비동기식 메모리 제어기 (308) 는 데이터 세트 (예를 들어, 드로우 콜) 의 프로세싱 동안 테슬레이션 설정들을 업데이트할 수도 있다.

[0059]

아이 추적기 (326) 는, 사용자가 이미지의 상이한 부분을 살피도록 시선을 변화시키는 때를 검출할 수도 있다. 본원에 개시된 시스템들 및 방법들 (예를 들어, 비동기식 메모리 제어기 (308)) 은 아이 추적 (예를 들어, 아이 추적 정보 및/또는 LOD 파라미터(들)) 에 기초하여 렌더링된 LOD 를 즉시 변화시킬 수도 있다. 예를 들어, 비동기식 메모리 제어기 (308) 는 데이터 세트 (예를 들어, 드로우 콜) 의 프로세싱 동안 변화시킬 수도 있는 하나 이상의 파라미터들 (예를 들어, LOD 파라미터들) 을 판독할 수도 있다. 예를 들어, VLIW 회로 (304) 는, 데이터 세트의 프로세싱 동안에도, 사용자가 보기 위해 시선을 변경했던 이미지의 영역 (예를 들어, 존) 에서 LOD 를 증가시킬 수도 있다. 부가적으로 또는 대안으로, 본원에 개시된 시스템들 및 방법들 (예를 들어, 비동기식 메모리 제어기 (308)) 은 사용자의 시선이 더 이상 지향하지 않는 이미지의 영역 (예를 들어, 존) 에서 LOD 를 감소시킬 수도 있다. 일부 구성들에서, 존은 사용자가 보고 있는 디스플레이의 포인트 (예를 들어, 이미지) 상에 거의 센터링된 원형 영역 (또는 다른 형상의 영역) 일 수도 있다. 다른 구성들에서, 존은 사용자가 보고 있는 윈도우에 대응하는 이미지의 전체 영역일 수도 있다.

[0060]

일부 구성들에서, 전자 디바이스 (302) 는 카메라 애플리케이션 및/또는 디스플레이 (332) 를 포함할 수도 있다. 카메라 애플리케이션이 실행되고 있을 때, 광학 시스템 (318) 의 시야 내에 위치되는 객체들의 이미지들은 이미지 센서 (316) 에 의해 캡처될 수도 있다. 이미지 센서 (316) 에 의해 캡처되고 있는 이미지들은 디스플레이 (332) 상에 제시될 수도 있다. 일부 구성들에서, 이들 이미지들은, 소정 시점에, 광학 시스템 (318) 의 시야 내에 위치되는 객체들이 디스플레이 (332) 상에 제시되도록 상대적으로 높은 프레임 레이트에서 빠르게 연속적으로 디스플레이될 수도 있다.

[0061]

전자 디바이스 (302) 에 예시된 엘리먼트들 중 하나 이상은 선택적일 수도 있다는 것이 주목되어야 한다. 예를 들어, 전자 디바이스 (302) 에 예시된 엘리먼트들 중 하나 이상은 포함 및/또는 구현되거나 또는 그렇지 않을 수도 있다. 부가적으로 또는 대안으로, 프로세서 (324) 및/또는 VLIW 회로 (304) 에 예시된 엘리먼트들 중 하나 이상은 프로세서 (324) 및/또는 VLIW 회로 (304)로부터 분리되어 (예를 들어, 다른 회로부에서, 다른 프로세서 상에서, 별개의 전자 디바이스 등에서) 구현될 수도 있다. 예를 들어, 이미지 센서 (316), 광학 시스템 (318), 통신 인터페이스 (320), 프로세서 (324), 아이 추적기 (326) 및/또는 디스플레이 (332) 는 전자 디바이스 (302) 상에서 구현되지 않을 수도 있다. 일부 구성들에서, 전자 디바이스 (302) 는 다른 디바이스로부터 이미지를 및/또는 아이 추적 정보를 수신할 수도 있다. 부가적으로 또는 대안으로, 하나 이상의 디스플레이들은 하나 이상의 별개의 디바이스들 상에서 구현될 수도 있다.

[0062]

일부 구성들에서, 전자 디바이스 (302) 는 디스플레이 (332) 상에 사용자 인터페이스 (334) 를 제시할 수도 있다. 예를 들어, 사용자 인터페이스 (334) 는 사용자가 전자 디바이스 (302) 와 상호작용하게 할 수도 있다. 일부 구성들에서, 디스플레이 (332) 는 물리적 터치로부터 (예를 들어, 손가락, 스타일러스 또는 다른 툴에 의해) 입력을 수신하는 터치스크린일 수도 있다. 부가적으로 또는 대안으로, 전자 디바이스 (302) 는 다른 입력 인터페이스를 포함하거나 이에 커플링될 수도 있다. 예를 들어, 전자 디바이스 (302) 는 사용자를 대면하는 카메라를 포함할 수도 있고 사용자 제스처들 (예를 들어, 손 제스처들, 팔 제스처들, 아이 추적, 눈꺼풀 깜박거림 등) 을 검출할 수도 있다. 다른 예에서, 전자 디바이스 (302) 는 마우스에 커플링될 수도 있고 마우스 클릭을 검출할 수도 있다. 일부 구성들에서는 사용자 입력이 필요하지 않을 수도 있다는 것이 주목되

어야 한다.

[0063]

일부 구성들에서, 전자 디바이스 (302) 는 선택적으로, 모션 센서 (예를 들어, 자이로스코프(들), 가속계(들), 등) 을 포함할 수도 있다. 예를 들어, 모션 센서는 (예를 들어, 전자 디바이스 (302) 의) 모션 및/또는 배향을 검출할 수도 있다. 일부 구성들에서, 렌더링되고 있는 이미지는 모션 및/또는 배향 정보에 기초할 수도 있다. 예를 들어, 전자 디바이스 (302) 는 헤드-장착 디스플레이 (예를 들어, 가상 현실 (VR) 헤드셋, 증강 현실 (AR) 헤드셋, 등), 차량들 (예를 들어, 자동차, 드론, 비행기 등), 모바일 디바이스 (예를 들어, 스마트폰) 또는 이미지를 렌더링하기 위해 모션 및/또는 배향 정보를 이용할 수도 있는 다른 디바이스일 수도 있다. 예를 들어, 모션 및/또는 배향 정보는 렌더링된 장면에서 일반적인 뷰잉 방향을 나타낼 수도 있다. 전자 디바이스 (302) 는 일부 구성들에서 아이 추적 정보에 추가하여 또는 이로부터의 대안으로 이 뷰잉 정보에 기초하여 이미지를 렌더링할 수도 있다. 모션 센서의 사용은 비동기식 메모리 제어기 (308) 의 비동기식 동작의 다른 양태를 예시할 수도 있다. 예를 들어, 모션 센서는 모션 정보 및/또는 배향 정보를 특정 레이트 (예를 들어, 1000 헤르츠 (Hz)) 에서 메모리 (예를 들어, 시스템 메모리 (314) 및/또는 온-칩 메모리 (310)) 에 제공할 수도 있는 한편, VLIW 회로 (304) 는 비교적 더 낮은 레이트 (예를 들어, 초당 30 프레임들 (fps)) 에서 프레임들을 렌더링할 수도 있다. 비동기식 메모리 제어기 (308) 는 모션 정보 및/또는 배향 정보에 기초하여 데이터의 세트를 렌더링하는 중에 하나 이상의 렌더링 동작들 (예를 들어, 테슬레이션) 을 비동기식으로 변화시킬 수도 있다.

[0064]

도 4 는 불-균일 프레임 버퍼 (430) 의 일 예를 예시하는 다이어그램이다. 이 예에서, 프레임 버퍼 (430) 는  $2n \times 2m$  픽셀들의 용량을 갖는다. 일부 구성들에서, 전자 디바이스 (302) 는 선택적으로, 프레임 버퍼 (430) 를 타일들 (436) 로 타일링할 수도 있다 (432). 도 4 에 예시된 예에서, 사이즈 ( $n, m$ ) 의 4 개의 타일들 (436) 이 예시된다. 일부 구현들에서, 온-칩 메모리 (310) 또는 온-칩 메모리 (310) 의 일부는 타일 (436) 의 사이즈에 제한될 수도 있다. 따라서, 전자 디바이스 (302) 는 프레임 버퍼 (430) 를 타일들 (436) 로 스플릿할 수도 있다. 다른 구현들에서, 온-칩 메모리 (310) 또는 온-칩 메모리 (310) 의 부분은 전체 프레임 버퍼 (430) 를 수용하기에 충분히 클 수도 있고, 털팅 (434) 이 수행되지 않을 수도 있다.

[0065]

전자 디바이스 (302) 는 프레임 버퍼 (430) 및/또는 타일들 (436) 을 스케일링된 부분들 (440) 로 세분할 수도 있다 (438). 예를 들어, 프레임 버퍼 (430) 및/또는 타일들 (436) 은 다수의 레졸루션들 및/또는 레벨들의 디테일을 피팅하도록 세분될 수도 있다. 도 4 에 예시된 예에서, 스케일링된 부분들 (440) 은 사이즈 ( $n/c, m/c$ ) 이고, 여기서  $c$  는 스케일링 팩터이다. 이 스케일링 팩터 ( $c$ ) 는 가변적일 수도 있고/있거나 구성에 기초하여 선택될 수도 있다.

[0066]

전자 디바이스 (302) (예를 들어, 불-균일 프레임 버퍼 제어기 (312)) 는 프레임 버퍼 (430) 의 상이한 서브세트들 (442a-c) 에 동적으로 액세스할 수도 있다. 도 4 에 예시된 예에서, 전자 디바이스 (302) 는 버퍼 서브세트 A (442a), 버퍼 서브세트 B (442b) 및 버퍼 서브세트 C (442c) 에 동적으로 액세스할 수도 있다. 더 적은 또는 더 많은 버퍼 서브세트들이 이용될 수도 있다는 것이 주목되어야 한다. 또한, 프레임 버퍼 (430) 의 전부 또는 단지 일부가 버퍼 서브세트들에 의해 차지될 수도 있다는 것이 주목되어야 한다. 예를 들어, 프레임 버퍼의 다른 비-해칭된 부분들은 하나 이상의 다른 서브세트들에 의해 이용될 수도 있다.

[0067]

상이한 프레임 버퍼 서브세트들 (예를 들어, 버퍼 서브세트들 (442a-c)) 의 동적 액세스 (예를 들어, 판독 및/또는 기입) 는 이미지들을 렌더링하는 것에서 더 높은 제어 및/또는 효율성을 제공하도록 하나 이상의 접근들을 가능하게 할 수도 있다. 일부 접근들에서, 상이한 프레임 버퍼 서브세트들의 동적 액세스는 단일-패스 멀티-LOD 렌더링을 가능하게 할 수도 있다. 이것은, 하나의 LOD 에서 존을 렌더링하는 것이 상이한 LOD 에서 다른 존을 렌더링하는 것이 시작될 수 있기 전에 완료될 필요가 없기 때문이다. 이 접근에서, 버퍼 서브세트들 (442a-c) 중 하나 이상은 상이한 이미지 존들에 대응할 수도 있다. 예를 들어, 버퍼 서브세트 A (442a) 는 최고 LOD 를 갖는 존에 대응할 수도 있고, 버퍼 서브세트 B (442b) 는 중간 LOD 를 갖는 존에 대응할 수도 있으며 버퍼 서브세트 C (442c) 는 더 낮은 LOD 를 갖는 존에 대응할 수도 있다. 예를 들어, VLIW 회로 (304) 는 버퍼 서브세트 A (442a) 에 기입될 수도 있는 최고 LOD 존을 렌더링할 수도 있으면서 동시에 또는 순차적으로 버퍼 서브세트 B (442b) 에 기입될 수도 있는 중간 LOD 존을 렌더링한다. 상이한 LOD 존들은 임의의 순서로 (예를 들어, 최고 LOD 에서부터 최하로, 역의 순서로 또는 다른 순서로) 렌더링될 수도 있다는 것이 주목되어야 한다. 부가적으로 또는 대안으로, 상이한 프레임 버퍼 서브세트들의 동적 액세스는 상이한 레이트들에서 상이한 존들을 프로세싱하는 것을 허용할 수도 있다 (예를 들어, 더 큰 프레임 버퍼 서브세트는 더 빠르게 프로세싱되도록 하나의 존에 대해 할당될 수도 있는 한편, 더 작은 프레임 버퍼 서브세트는 더 천천히 프

로 세팅되도록 다른 존에 대해 할당될 수도 있다).

[0068] 일부 접근들에서, 상이한 프레임 버퍼 서브세트들의 동적 액세스는 병렬 세이더 프로세스들 (예를 들어, 서브-루틴들)을 가능하게 할 수도 있다. 예를 들어, 상이한 세이더 프로세스들은 병렬로 실행될 수도 있고, 여기서 하나의 세이더 프로세스는 프레임 버퍼의 하나의 서브세트에 액세스하고 다른 세이더 프로세스는 프레임 버퍼의 다른 서브세트에 액세스한다. 부가적으로 또는 대안으로, 상이한 프레임 버퍼 서브세트들의 동적 액세스는 세이더 서브-루틴 스왑핑을 허용할 수도 있다. 예를 들어, 버퍼 서브세트 A (442a)에 액세스하는 제 1 세이더 서브-루틴이 실행될 수도 있다. 제 1 세이더 서브-루틴이 진행 중인 동안, 버퍼 서브세트 B (442b)에 액세스하는 제 2 세이더 서브-루틴은 끝날 수도 있다. 제 1 세이더 서브-루틴이 진행 중인 동안 제 2 세이더 서브-루틴은 (예를 들어, 버퍼 서브세트 B (442b)에 액세스할 수도 있는) 다른 세이더 서브-루틴에 대해 스왑핑될 수도 있다. 이것은, 다른 것이 시작될 수 있기 전에 세이더 서브-루틴이 완성되기를 대기하는 것보다는, 프레임 버퍼의 공간을 이용하는 것에서 더 좋은 효율성을 허용할 수도 있다.

[0069] 일부 접근들에서, 상이한 프레임 버퍼 서브세트들의 동적 액세스는 샘플 대체를 가능하게 할 수도 있다. 예를 들어, 불-균일 프레임 버퍼 제어기 (312)는 다른 픽셀의 하나 이상의 샘플들에 대한 프로세싱된 픽셀의 하나 이상의 샘플들을 스왑핑할 수도 있다. 일부 구성들에서, VLIW 회로 (304)는 안티-에일리어싱 (예를 들어, 멀티-샘플 안티-에일리어싱 (MSAA))을 수행할 수도 있다. 안티-에일리어싱을 수행하는데 있어서, 상이한 픽셀들은 상이한 수들의 샘플들을 가질 수도 있다. 예를 들어, 버퍼 서브세트 A (442a)에서의 제 1 (예를 들어, "미세") 픽셀은 4 개의 샘플들을 가질 수도 있고 고 품질의 세이딩을 사용할 수도 있는 한편, 버퍼 서브세트 B (442b)에서의 부근의 (예를 들어, 이웃하는) 제 2 (예를 들어, "코어스") 픽셀은 1 개의 샘플을 가질 수도 있고 저 품질의 세이딩을 사용할 수도 있다. 제 2 픽셀 상에서 프로세싱 (예를 들어, 세이딩)을 수행하는 대신에, 불-균일 프레임 버퍼 제어기 (312)는 제 2 픽셀의 샘플을 제 1 픽셀의 샘플로 대체할 수도 있다. 이것은 제 2 픽셀에 대한 임의의 프로세싱을 수행하는 것을 회피할 수도 있다. 부가적으로 또는 대안으로, 불-균일 프레임 버퍼 제어기 (312)는 백맵들을 프로세싱하는데 있어서 샘플 대체를 수행할 수도 있다. 예를 들어, 불-균일 프레임 버퍼 제어기 (312)는 (예를 들어, 버퍼 서브세트 B (442b)에서) 더 낮은 레벨로 부터의 샘플을 (예를 들어, 버퍼 서브세트 A (442a)에서) 더 높은 레벨로부터의 샘플로 대체할 수도 있다. 이것은 하나 이상의 더 낮은 레벨들에서 일부 또는 프로세싱을 회피할 수도 있다.

[0070] 불-균일 프레임 버퍼 제어기 (312)는 세이더 프로세싱 (예를 들어, 서브-루틴들, 커널들, 등)의 동적 디스패치를 가능하게 할 수도 있고, 픽셀 샘플 대체를 가능하게 할 수도 있고/있거나 멀티-LOD 프레임 버퍼를 제공할 수도 있다. 도 4에 예시된 바와 같이, 프레임 버퍼 (430)는 다수의 렌더링된 타겟들 (444)로서 스트림 아웃될 수도 있는 이미지 데이터를 저장할 수도 있다.

[0071] 리스트팅 (1)은 불-균일 프레임 버퍼 기능성에 대한 하나의 접근을 예시하는 의사코드의 일 예를 예시한다. GLSL은 OpenGL Shading Language의 약어이고 SSBO는 Shader Storage Buffer Object의 약어이다. 리스트팅 (1)은 상이한 레벨들의 디테일을 갖는 다수의 존들을 예시한다.

```

void main() { //compute buffer_subset_A using GLSL + arbitrary textures.

//imageStore()/color buffer/SSBO as a writing mechanism.

}

void main_lod_1(samplerTile/imageTile red_square) {

//compute green square using GLSL + arbitrary textures

//and possibly texture(red_square, uv)/imageRead()

}

...

void main_lod_n(samplerTile last_square) {

/*_lod_<n>() would be triggered after the rendering of level 0

(buffer_subset_A).

```

```

//could be simulated via a full-screen triangle and changing viewport.

//"_lod_<i>()" can either execute forward [0 to n - 1] or reverse [n - 1 to 0].

}

```

[0073] 리스팅 (1)

[0075] 도 5 는 다수의 레벨들의 디테일을 렌더링하는 방법 (500)의 더 많은 특정 구성을 예시하는 흐름도이다. 방법 (500)은 도 3과 연관되어 설명된 전자 디바이스 (302)에 의해 수행될 수도 있다.

[0076] 전자 디바이스 (302)는 지오메트리 데이터 (예를 들어, 지오메트리 데이터 (328))를 획득할 수도 있다 (502).

이것은 도 1 내지 도 3 중 하나 이상과 연관되어 설명된 바와 같이 달성될 수도 있다. 예를 들어, 전자 디바이스 (302)는 지오메트리 데이터를 스토리지로부터 메모리 (예를 들어, 시스템 메모리 (314) 및/또는 온-칩 메모리 (310))로 로딩할 수도 있고/있거나 다른 디바이스로부터 지오메트리 데이터를 수신하고 이 지오메트리 데이터를 메모리 (예를 들어, 시스템 메모리 (314) 및/또는 온-칩 메모리 (310))로 로딩할 수도 있다.

[0077] 전자 디바이스 (302)는 아이 추적을 수행할 수도 있다 (504). 이것은 도 3과 연관되어 설명된 바와 같이 달성될 수도 있다. 예를 들어, 전자 디바이스 (302)는 하나 이상의 이미지들을 획득 (예를 들어, 캡처 및/또는 수신) 할 수도 있고 하나 이상의 이미지들에 기초하여 사용자의 시선이 지향되는 곳 (예를 들어, 사용자가 디스플레이 상에서 보고 있는 곳 및/또는 디스플레이 상에 제시되고 있는 이미지)을 결정할 수도 있다.

[0078] 전자 디바이스 (302)는 아이 추적에 기초하여 상이한 레벨들의 디테일을 비동기식으로 렌더링할 수도 있다 (506). 이것은 도 1 내지 도 3 중 하나 이상과 연관되어 전술된 바와 같이 달성될 수도 있다. 예를 들어, 전자 디바이스 (302)는 메모리 (예를 들어, 시스템 메모리 (314) 및/또는 온-칩 메모리 (310))에 비동기식으로 액세스하여, 아이 추적에 기초하여 상이한 레벨들의 디테일을 렌더링할 수도 있다. 예를 들어, 전자 디바이스 (302)는, 아이 추적에 기초하여 데이터의 세트에 대한 존이 변화하는 경우 프로세싱 동안 데이터의 세트에 대한 LOD를 변화시킬 수도 있다 (여기서, 예를 들어 데이터의 세트는 처음에 상이한 LOD를 갖는다).

일부 구성들에서, 전자 디바이스 (302)는, 사용자의 시선 방향이 데이터의 세트에 대응하는 이미지의 영역으로 지향되는 경우 데이터의 세트에 대한 LOD를 증가시킬 수도 있다. 부가적으로 또는 대안으로, 전자 디바이스 (302)는, 사용자의 시선이 데이터의 세트에 대응하는 이미지의 영역으로부터 멀리 이동하는 경우 데이터의 세트에 대한 LOD를 감소시킬 수도 있다.

[0079] 일부 구성들에서, 상이한 레벨들의 디테일을 비동기식으로 렌더링하는 것 (506)은 동적 LOD 테슬레이션을 수행하는 것을 포함할 수도 있다. 예를 들어, 메모리 (예를 들어, 시스템 메모리 (314) 및/또는 온-칩 메모리 (310))는 LOD 테슬레이션 파라미터(들) (예를 들어, 테슬레이션의 정도)에서의 변화를 나타내도록 업데이트될 수도 있다. 비동기식 메모리 제어기 (308)는 업데이트된 LOD 테슬레이션 파라미터에 액세스하여 LOD 테슬레이션을 비동기식으로 변화시킬 수도 있다.

[0080] 전자 디바이스 (302)는 프레임 버퍼의 상이한 서브세트들에 동적으로 액세스할 수도 있다 (508). 이것은 도 1 내지 도 4 중 하나 이상과 연관되어 전술된 바와 같이 달성될 수도 있다. 예를 들어, 전자 디바이스 (302)는 제 2 존의 적어도 하나의 픽셀과는 상이한 레이트에서 제 1 존의 적어도 하나의 픽셀에 액세스할 수도 있다. 부가적으로 또는 대안으로, 전자 디바이스 (302)는, 제 1 픽셀의 프로세싱이 진행 중이고 제 2 픽셀의 프로세스가 완료될 때 세이더 서브-루틴 스왑핑을 가능하게 할 수도 있다. 부가적으로 또는 대안으로, 전자 디바이스 (302)는 제 2 픽셀의 제 2 샘플을 제 1 픽셀의 프로세싱된 제 1 샘플로 대체하여 제 2 픽셀의 제 2 샘플을 프로세싱하는 것을 회피할 수도 있다.

[0081] 전자 디바이스 (302)는 렌더링된 이미지를 제시할 수도 있다 (510). 예를 들어, 전자 디바이스 (302)는 상이한 레벨들의 디테일을 갖고 비동기식으로 렌더링되고 있는 (506) 이미지 데이터를 스트림 아웃할 수도 있다. 일부 구성들에서, 이미지 데이터는 통합형 디스플레이 (332)에 제공될 수도 있다. 다른 구성들에서, 이미지 데이터는 전자 디바이스 (302)와 통신하는 원격 디스플레이에 제공될 수도 있다. 예를 들어, 전자 디바이스 (302)는 (VGA, DVI, HDMI, 등을 통해) 전자 디바이스 (302)에 커플링되는 디스플레이에 이미지 데이터를 제공할 수도 있다.

[0082] 도 6은 포비에이티드 렌더링을 위한 방법 (600)의 예를 예시하는 흐름도이다. 이 방법에서, 지오메트리 데이터가 획득된다 (602). 아이 추적이 또한, 수행된다 (604). 코어스 층이 렌더링되고 (606), 중간 층이 렌더링되며 (608), 미세 층이 렌더링된다 (610). 예를 들어, 미세 층은, 사용자의 시선이 지향되는 이미지 데이터를 제공할 수도 있다.

지 상에 렌더링될 수도 있다 (610). 중간 층은 미세 층 영역을 오버랩하는 더 큰 영역에서 렌더링될 수도 있다 (608). 코어스 층은 중간 층 영역 및 미세 층 영역을 포함하는 더욱 더 큰 영역 (예를 들어, 전체 이미지)에서 렌더링될 수도 있다 (606). 따라서, 층들 간의 상당한 오버랩이 존재할 수도 있다. 코어스 층, 중간 층 및 미세 층은 안티-에일리어싱으로 병합될 수도 있다 (612). 결과의 이미지는 프레임 버퍼로 출력될 수도 있다 (614).

[0083] 관측될 수 있는 바와 같이, 방법 (600)은 오버랩하는 영역들의 상당한 양들을 렌더링하는 것을 포함할 수도 있다. 예를 들어, 미세 디테일 영역은 3 번 렌더링될 수도 있다: 일단 코어스 층에서 한 번, 중간 층에서 한번, 및 미세 층에서 한 번. 이것은 동일한 픽셀들에 걸쳐 다수의 렌더링 패스들을 수행하는 것과 같이 비효율적일 수도 있다.

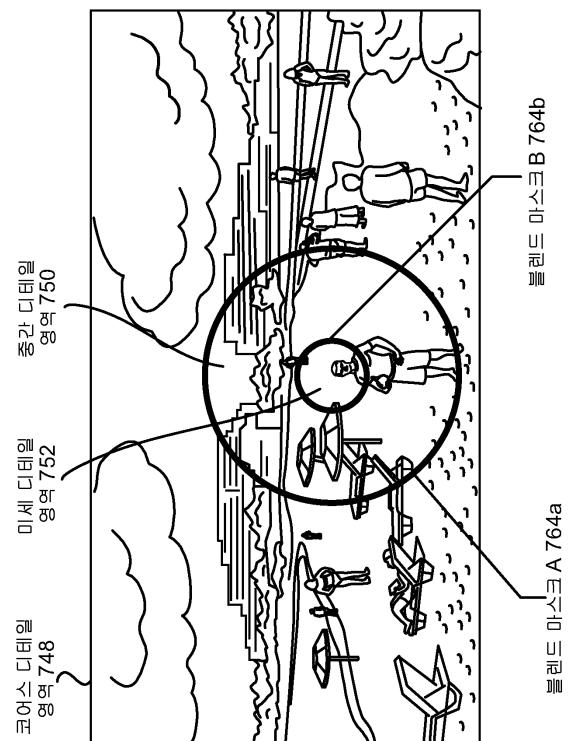

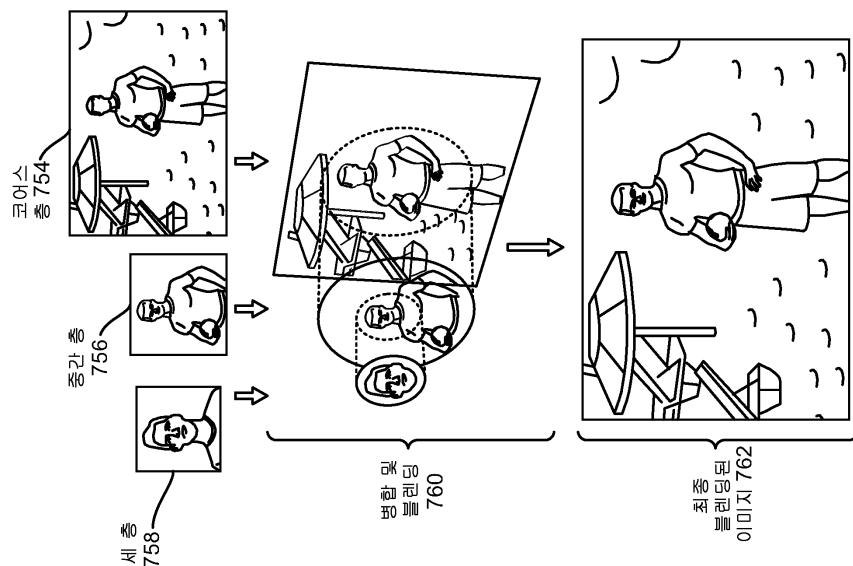

[0084] 도 7 은 포비에이티드 렌더링의 일 예를 예시한다. 특히, 도 7 은 포비에이티드 렌더링을 위한 장면의 예를 예시한다. 포비에이티드 렌더링을 위한 장면은 코어스 디테일 영역 (748), 중간 디테일 영역 (750) 및 미세 디테일 영역 (752)을 포함한다. 도 6 과 연관되어 설명된 바와 같이, 포비에이티드 렌더링에 대한 하나의 접근은 코어스 층 (754)을 렌더링하는 것, 중간 층 (756)을 렌더링하는 것 및 미세 층 (758)을 렌더링하는 것을 포함한다. 그 후, 코어스 층 (754), 중간 층 (756) 및 미세 층 (758) 상에서 병합 및 블렌딩 (760)이 수행되어 최종 블렌딩된 이미지 (762)를 생성할 수도 있다. 예를 들어, 중간 층 (756)과 코어스 층 (754) 간의 블렌드 마스크 A (764a)는 중간 층 (756) 및 코어스 층 (754)을 블렌딩하는데 사용될 수도 있다.

부가적으로, 중간 층 (756)과 미세 층 (758) 간의 블렌드 마스크 B (764b)는 중간 층 (756) 및 미세 층 (756)을 블렌딩하는데 사용될 수도 있다. 관측될 수 있는 바와 같이, 이 접근은 동일한 픽셀들을 다수의 패스들에서 렌더링하여, 비효율성을 초래한다. 블렌드 마스크들 (764a-b) 중 하나 이상은 일부 구성들에서 가중화된 (예를 들어, 점진적인) 블렌드를 제공할 수도 있고, 여기서 블렌딩 가중치는 블렌드 마스크들의 외측 에지들로부터 내측 영역으로 증가한다. 또한, 코어스 층 (754) 및/또는 최종 블렌딩된 이미지 (762)가 편의를 위해 전체 장면의 서브세트들로서 도 7 에 예시된다는 것이 주목되어야 한다. 그러나, 코어스 층 (754) 및/또는 최종 블렌딩된 이미지 (762)는 전체 장면을 커버할 수도 있다.

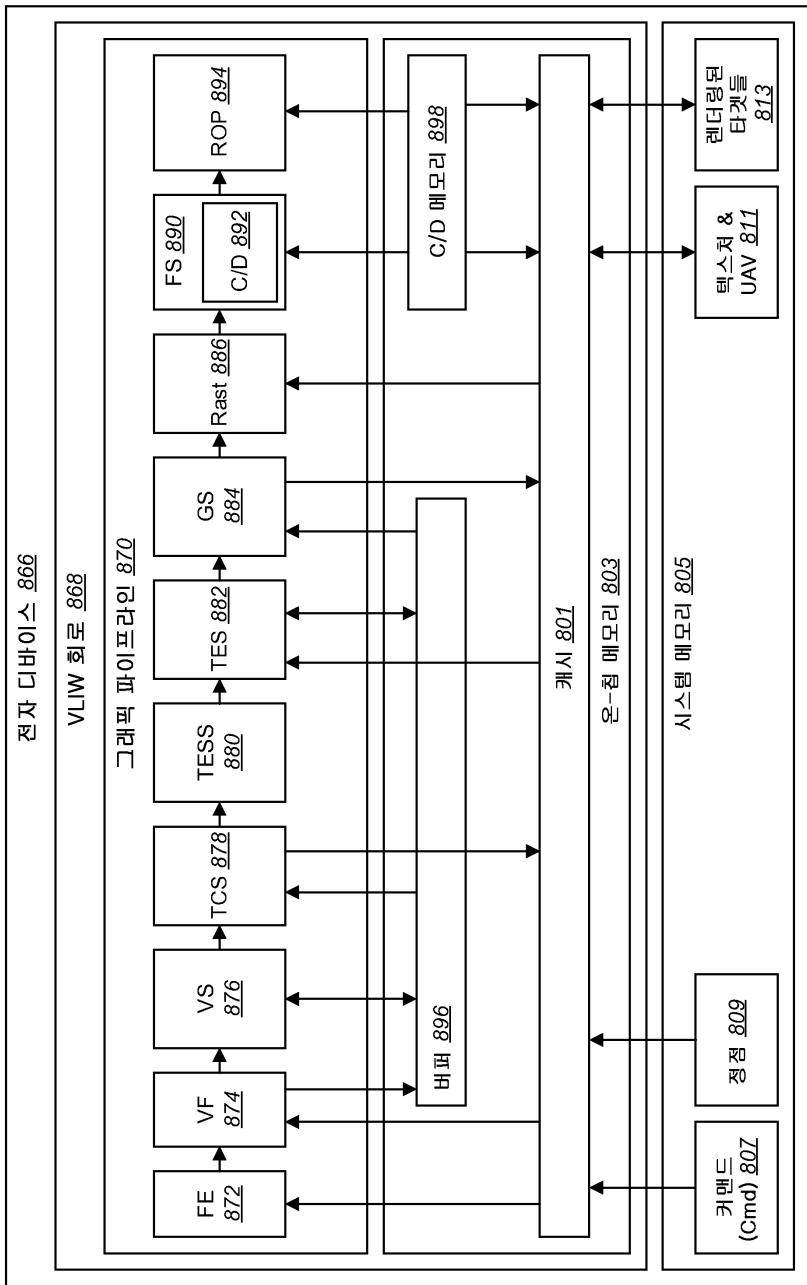

[0085] 도 8 은 매우 긴 명령어 (VLIW) 회로 (868)를 포함하는 전자 디바이스 (866)의 예를 예시하는 블록도이다. 특히, 도 8 은 그래픽 프로세싱을 위한 아키텍처의 일 예를 예시한다. 도 8 과 연관되어 설명된 아키텍처의 하나 이상의 양태들은 엔비디아 (Nvidia) 아키텍처의 양태들과 유사하게 기능할 수도 있다. 이 아키텍처는 전력 및 다이 영역의 회생으로 고-대역폭 설계를 갖는 즉각 모드 렌더링 (IMR)을 제공할 수도 있다. 이 설계에서, 캐시 (801)는 (예를 들어, 반복된 샘플링, 시스템 메모리 (805)로부터 판독 및/또는 시스템 메모리에 기입하는 것을 회피하기 위해) 대역폭을 감소시키도록 이용될 수도 있다. 예를 들어, 캐시 (801)는 전체 이미지 프레임에 대한 데이터를 수용하기에 충분히 클 수도 있다. 본원에 설명된 그래픽 파이프라인들 중 하나 이상은 DirectX 및/또는 OpenGL 파이프라인들 및/또는 애플리케이션 프로그래밍 인터페이스 (API)들과 유사한 하나 이상의 양태들을 가질 수도 있다는 것이 주목되어야 한다. 미국 특허출원 공개 제 2014/0347363 호는 DirectX 파이프라인과 유사성을 가질 수도 있는 그래픽 프로세싱의 일부 양태들을 설명한다.

[0086] 전자 디바이스 (866)는 VLIW 회로 (868) (예를 들어, GPU) 및 시스템 메모리 (805) (예를 들어, DRAM)을 포함할 수도 있다. VLIW 회로 (868)는 그래픽 파이프라인 (870) 및 온-칩 메모리 (803)를 포함할 수도 있다. 그래픽 파이프라인 (870)은 프론트-엔드 (FE)(872), 정점 페처 (VF)(874), 정점 세이더 (VS)(876), 테슬레이션 채어 세이더 (TCS)(878), 테슬레이터 (TESS)(880) (예를 들어, 테슬레이션 엔진), 테슬레이션 평가 세이더 (TES)(882), 지오메트리 세이더 (GS)(884), 래스터라이저 (Rast)(886), 프래그먼트 세이더 (FS)(890) 및 렌더 출력 유닛 (ROP)(894) 중 하나 이상을 포함할 수도 있다. 많은 엘리먼트 라벨들이 편의를 위해 축약되어 있다. 온-칩 메모리 (803)는 버퍼 (896), 구성/해체 (composition/decomposition; C/D) 메모리 (898) 및 캐시 (801)를 포함할 수도 있다. 일부 구성들에서, 버퍼 (896)는 텍스처 버퍼, 프레임 버퍼 및/또는 온-칩 메모리 (910)의 다른 블록이고/이거나 이들을 포함할 수도 있다. 시스템 메모리 (805)는 커맨드 데이터 (Cmd)(807), 정점 데이터 (809), 텍스처 데이터 및 비순서화된 액세스 뷰 데이터 (811) 및 렌더링된 타겟들 데이터 (813)를 포함할 수도 있다.

[0087] 장면을 렌더링하기 위해, 전자 디바이스 (866)는 커맨드 데이터 (807) 및 정점 데이터 (809)를 시스템 메모리 (805)로부터 온-칩 메모리 (803)에서의 캐시 (801)로 로딩할 수도 있다. 정점 데이터 (809)는 하나 이상의 포인트들 (예를 들어, 정점들), 라인들 및/또는 다각형들을 나타낼 수도 있다. 정점 데이터 (809)는 장면 및/또는 장면에서의 하나 이상의 객체들을 나타낼 수도 있다.

- [0088] FE (872) 는 캐시 (801) 와 그래픽 파이프라인 (870)(예를 들어, VF (874)) 간의 인터페이스를 제공할 수도 있다. 예를 들어, FE (872) 는 VF (874) 에 의해 변형될 데이터를 획득할 수도 있고/있거나 캐시 (801) 로부터 취출되는 데이터 (예를 들어, 정점 데이터) 에 관한 VF (874) 를 제어할 수도 있다.

- [0089] VF (874) 는 정점 데이터를 캐시 (801) 로부터 그래픽 파이프라인 (870) 으로 페치할 수도 있다. VF (874) 는 버퍼 (896) 에 액세스할 수도 있다. 예를 들어, VF 는 데이터를 버퍼 (896) 에 기입할 수도 있다. VF (874) 는 정점 데이터를 VS (876) 에 제공할 수도 있다. 부가적으로 또는 대안으로, VS (876) 는 버퍼 (896) 로부터 정점 데이터를 취출할 수도 있다.

- [0090] VS (876) 는 정점 데이터를 상이한 공간으로 변환할 수도 있다. 예를 들어, VS (876) 는 정점 데이터를 3-차원 (3D) 공간으로부터 2-차원 (2D) 공간으로 변환할 수도 있다. VS (876) 는 변환된 정점 데이터를 TCS (878) 에 제공할 수도 있고/있거나 변환된 정점 데이터를 버퍼 (896) 에 저장할 수도 있다.

- [0091] TCS (878) 는 정점 데이터 (예를 들어, 변환된 정점 데이터) 를 VS (876) 로부터 및/또는 버퍼 (896) 로부터 수신할 수도 있다. TCS (878) 는 정점 데이터 (예를 들어, 변환된 정점 데이터) 의 단위를 변환할 수도 있다. 예를 들어, TCS (878) 는 정점 데이터의 단위를 테슬레이션을 위한 (예를 들어, 삼각형들과 같은 다각형들로 효율적으로 세분하기 위한) 단위로 변환할 수도 있다. TCS (878) 는 정보를 캐시 (801) 에 저장할 수도 있다. 예를 들어, TCS (878) 는 TCS (878) 에 의해 수행된 단위 변환을 나타내는 단위 표시자 (basis indicator) 를 저장할 수도 있다. 단위-변환된 정점 데이터는 TESS (880) 에 제공될 수도 있다.

- [0092] TESS (880) 는 정점 데이터 (예를 들어, 단위-변환된 정점 데이터) 를 테슬레이팅할 수도 있다. 예를 들어, TESS (880) 는 정점 데이터에 기초하여 더 많은 정점들을 생성할 수도 있다 (예를 들어, 삼각형들을 더 많은 삼각형들로 세분할 수도 있다). TESS (880) 는 LOD 파라미터에 기초하여 동작할 수도 있다. LOD 파라미터는 LOD 를 지정할 수도 있고/있거나 수행할 TESS (880) 에 대한 테슬레이션의 정도를 나타낼 수도 있다. 테슬레이팅된 정점 데이터는 TES (882) 에 제공될 수도 있다.

- [0093] TES (882) 는 정점 데이터 (예를 들어, 테슬레이팅된 정점 데이터) 의 단위를 변환할 수도 있다. 예를 들어, TES (882) 는 정점 데이터의 단위를 TCS (878) 에 의해 적용된 단위 변환 전의 단위로 다시 변환할 수도 있다. 일부 구성들에서, TES (882) 는 정점 데이터의 단위를 변환 (예를 들어, 역 변환) 하기 위해 캐시 (801) 로부터 단위 표시자를 판독할 수도 있다. TES (882) 는 정점 데이터 (예를 들어, 역 단위-변환된 정점 데이터) 를 GS (884) 에 제공하고/하거나 정점 데이터를 버퍼 (896) 에 저장할 수도 있다.

- [0094] GS (884) 는 정점 데이터 (예를 들어, 역 단위-변환된 정점 데이터) 상에서 하나 이상의 동작들을 수행할 수도 있다. 예를 들어, GS (884) 는 정점 데이터에 기초하여 추가적인 지오메트리를 생성할 수도 있다. GS (884) 는 (예를 들어, 추가적인 지오메트리를 갖는) 정점 데이터를 래스터라이저 (886) 및/또는 캐시 (801) 에 제공할 수도 있다.

- [0095] 래스터라이저 (886) 는 GS (884) 및/또는 캐시 (801) 로부터 정점 데이터를 수신할 수도 있다. 래스터라이저 (886) 는 정점 데이터를 래스터화할 수도 있다. 예를 들어, 래스터라이저는 정점 데이터를 픽셀 데이터를 컨버팅할 수도 있다. 픽셀 데이터는 FS (890) 에 제공될 수도 있다.

- [0096] FS (890) 는 픽셀 데이터 상에서 프래그먼트 셰이딩 또는 픽셀 셰이딩을 수행할 수도 있다. 예를 들어, FS (890) 는 하나 이상의 픽셀들의 하나 이상의 속성들 (예를 들어, 컬러, 밝기, 투명도 등) 을 결정할 수도 있다. 일부 구성들에서, FS (890) 는 숨은 면 제거 (hidden surface removal; HSR) 를 수행할 수도 있다. FS (890) 는 구성/분해 (C/D) 블록 (892) 을 포함할 수도 있다. 대안으로, C/D (892) 는 FS (890) 로부터 분리되고/되거나 FS (890) 에 커플링될 수도 있다.

- [0097] 일부 구성들에서, C/D (892) 는 텍스처링 및/또는 블렌딩과 같은 동작들을 수행할 수도 있다. 예를 들어, C/D (892) 는 다수의 층들을 블렌딩하여 최종 픽셀 값을 결정할 수도 있다. 일부 구성들에서, C/D (892) 는 상이한 프레임 버퍼들을 조합할 수도 있다 (예를 들어, 픽셀 마다 다수의 이미지들을 함께 블렌딩할 수도 있다). C/D (892) 는 칩 상에서 (VLIW 회로 (868) 상에서), 그래픽 파이프라인 (870) 에서, 온-칩 메모리 (803) 에서 구현될 수도 있고/있거나 VLIW 회로 (868) 로부터 분리될 수도 있다는 것이 주목되어야 한다. C/D (892) 는 일부 구성들에서 시스템 메모리 (805) 에서 구현되지 않을 수도 있다. C/D (892) 는, 이미지 데이터가 시스템 메모리 (805) 에 및/또는 다른 스트리밍 아웃 (예를 들어, HDMI 스트리밍 아웃) 에 기입되기 전에 이미지 데이터 상에서 동작할 수도 있다. FS (890) (및/또는 C/D (892)) 는 C/D 메모리 (898) 에 액세스할 수도 있다. 예를 들어, 시스템 메모리 (805) 는 텍스처 데이터 및/또는 비순서화된 액세스 뷰 데이터 (811)

를 캐시 (801)에 제공할 수도 있다. FS (890)는 C/D 메모리 및/또는 캐시 (801)에 액세스함으로써 하나 이상의 동작들을 수행할 수도 있다. FS (890)는 픽셀 데이터 (예를 들어, 프로세싱된 픽셀 데이터)를 ROP (894)에 제공할 수도 있다.

[0098] ROP (894)는 픽셀 데이터 (예를 들어, 프로세싱된 픽셀 데이터)를 출력할 수도 있다. 예를 들어, ROP (894)는 C/D 메모리 (898) 및/또는 캐시 (801)를 통해 픽셀 데이터를 렌더링된 타겟들 데이터 (813)로서 시스템 메모리 (805)로 출력할 수도 있다. 렌더링된 타겟들 데이터 (813)는 프리젠테이션을 위해 제공 (예를 들어, 출력) 될 수도 있다. 예를 들어, 렌더링된 타겟들 데이터 (813)는 프리젠테이션을 위해 디스플레이로 전송될 수도 있다.

[0099] 본원에 개시된 시스템들 및 방법들 없이, 도 8과 연관되어 설명된 동작들은 데이터 세트들 (예를 들어, 정점, 픽셀 및/또는 이미지 데이터의 세트들)의 관점에서 수행될 수도 있고, 여기서 각각의 데이터 세트는 렌더링을 위한 하나 이상의 확립된 파라미터들 (예를 들어, 렌더링 파라미터(들))을 가질 수도 있다는 것이 주목되어야 한다. 예를 들어, 각각의 데이터 세트는 테슬레이션 동작들을 위해 할당된 고정된 LOD를 가질 수도 있다.

따라서, LOD는 데이터 세트에 대한 렌더링 동안 (예를 들어, 드로우 콜 동안) 변화되지 않을 수도 있다. 이것은, 예를 들어 도 6 및 도 7과 연관되어 설명된 바와 같이 다수의 LOD들을 렌더링하기 위한 다수의 패스들을 초래할 수도 있다. 부가적으로 또는 대안으로, (온-칩 메모리 (803), 버퍼 (896) 및/또는 캐시 (801)에서 구현될 수도 있는) 프레임 버퍼는 균일할 수도 있다.

[0100] 예를 들어, 프레임 버퍼는 균일한 데이터 (예를 들어, 동일한 LOD를 갖는 데이터, 동일한 수의 픽셀 샘플들을 갖는 데이터, 동일한 세이더 서브-루틴으로부터의 데이터, 등)를 포함할 수도 있다. 예를 들어, 버퍼의 서브세트들은 독립적으로 (예를 들어, 상이한 세이더 서브-루틴들에 의해 동시에) 액세스되지 않을 수도 있다.

예를 들어, 프레임 버퍼는, 프레임 버퍼로의 단지 하나의 데이터 기입이 한 번에 발생할 수도 있다는 점에서 균일할 수도 있다. 부가적으로 또는 대안으로, 프레임 버퍼는, 각각의 데이터가 한 번에 단일의 세이더 서브-루틴으로부터의 것일 수도 있다는 점에서 균일할 수도 있다. 부가적으로 또는 대안으로, 프레임 버퍼는, 각각의 데이터 기입이 동일한 LOD를 갖는 및/또는 동일한 수의 픽셀 샘플들을 갖는 데이터 만을 포함할 수도 있다는 점에서 균일할 수도 있다.

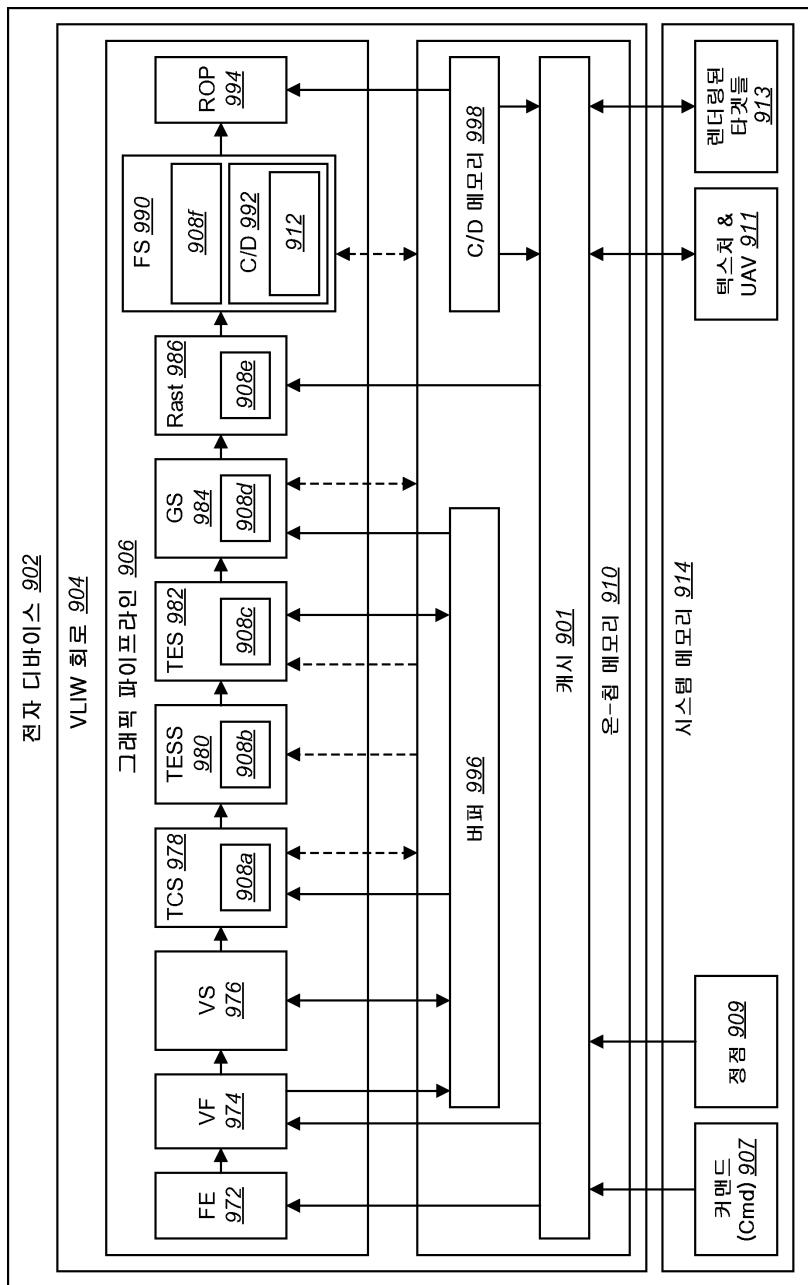

[0101] 도 9는 도 8와 연관되어 설명된 아키텍처에서 구현된 본원에 개시된 시스템들 및 방법들의 예를 예시하는 블록도이다. 구체적으로, 도 9는 전자 디바이스 (902)를 예시한다. 도 9와 연관되어 설명된 전자 디바이스 (902)는 도 1 내지 도 5 중 하나 이상과 연관되어 전술된 전자 디바이스들 (102, 302) 중 하나 이상의 예일 수도 있다. 전자 디바이스 (902)는 도 1 내지 도 5 중 하나 이상과 연관되어 설명된 방법들, 기능들, 단계들, 동작들, 등 중 하나 이상을 수행하도록 구성될 수도 있다.

[0102] 전자 디바이스 (902)는 VLIW 회로 (904) (예를 들어, GPU) 및 시스템 메모리 (914)를 포함할 수도 있다. VLIW 회로 (904)는 도 1 내지 도 5 중 하나 이상과 연관되어 전술된 VLIW 회로들 (104, 304) 중 하나 이상의 일 예일 수도 있다. 부가적으로 또는 대안으로, 시스템 메모리 (914)는 도 1 내지 도 5 중 하나 이상과 연관되어 설명된 시스템 메모리들 (114, 314) 중 하나 이상의 예일 수도 있다. 시스템 메모리 (914)는 커맨드 데이터 (Cmd)(907), 정점 데이터 (909), 텍스처 및 비순서화된 액세스 뷰 데이터 (911) 및/또는 렌더링된 타겟 데이터 (913)를 포함할 수도 있다. 커맨드 데이터 (Cmd)(907), 정점 데이터 (909), 텍스처 및 비순서화된 액세스 뷰 데이터 (911) 및/또는 렌더링된 타겟 데이터 (913) 중 하나 이상은 도 8과 연관되어 설명된 대응하는 데이터와 유사할 수도 있다.

[0103] VLIW 회로 (904)는 그래픽 파이프라인 (906) 및 온-칩 메모리 (910)를 포함할 수도 있다. 도 9와 연관되어 설명된 그래픽 파이프라인 (906)은 도 1 내지 도 5 중 하나 이상과 연관되어 설명된 그래픽 파이프라인들 (106, 306) 중 하나 이상의 일 예일 수도 있다. 부가적으로 또는 대안으로, 도 9와 연관되어 설명된 온-칩 메모리 (910)는 도 1 내지 도 5 중 하나 이상과 연관되어 설명된 온-칩 메모리들 (110, 310) 중 하나 이상의 일 예일 수도 있다.

[0104] 온-칩 메모리 (910)는 버퍼 (996), 캐시 (901) 및/또는 C/D 메모리 (998)를 포함할 수도 있다. 일부 구성들에서, 온-칩 메모리 (910), 버퍼 (996), 캐시 (901) 및/또는 C/D 메모리 (998) 중 하나 이상은 도 8과 연관되어 설명된 대응하는 엘리먼트들과 유사할 수도 있다. 온-칩 메모리 (910)는 도 3 및 도 4 중 하나 이상과 연관되어 설명된 바와 같이 하나 이상의 프레임 버퍼들을 포함할 수도 있다는 것이 주목되어야 한다. 프레임 버퍼(들)은 온-칩 메모리 (910), 버퍼 (996), 캐시 (901) 및/또는 C/D 메모리 (998) 중 하나 이상에 포함될 수도 있다. 부가적으로 또는 대안으로, 프레임 버퍼(들)은 시스템 메모리 (914)에 포함될 수도 있다.

일부 구성들에서, 하나 이상의 프레임 버퍼들은 온-칩 메모리 (910), 시스템 메모리 (914) 또는 양자 모두에 포함될 수도 있다.

[0105] 그래픽 파이프라인 (906) 은 FE (972), VF (974), VS (976), TCS (978), TESS (980), TES (982), GS (984), 래스터라이저 (986), FS (990) 및 ROP (994) 중 하나 이상을 포함할 수도 있다. 일부 구성들에서, FE (972), VF (974), VS (976), TCS (978), TESS (980), TES (982), GS (984), 래스터라이저 (986), FS (990) 및 ROP (994) 중 하나 이상은 도 8 과 연관되어 설명된 하나 이상의 대응하는 엘리먼트들의 동작들 중 하나 이상을 수행할 수도 있다.

[0106] 도 9 에 예시된 구성들에서, VLIW 회로 (904)(예를 들어, 그래픽 파이프라인 (906)) 는 비동기식 메모리 제어기 (908) 를 포함할 수도 있다. 비동기식 메모리 제어기 (908) 는 TCS (978), TESS (980), TES (982), GS (984), 래스터라이저 (986) 및 FS (990) 중 하나 이상을 포함하고/하거나 이들에서 구현될 수도 있다. 완전히 또는 부분적으로, 예를 들어 비동기식 메모리 제어기 (908a) 는 TCS (978), TESS (980), TES (982), GS (984), 래스터라이저 (986) 및/또는 FS (990) 에서 구현될 수도 있다. 일반적인 라벨 "908" 은, 비동기식 메모리 제어기 (908) 가 도 9 에 예시된 엘리먼트들 (908a-f) 중 어느 하나 또는 전부에서 구현될 수도 있다는 것을 가리킬 수도 있다. 일부 구성들에서, 비동기식 메모리 제어기 (908) 는 TCS (978), TESS (980), TES (982) 및 GS (984) 중 하나 이상에서만 구현될 수도 있다. 예를 들어, 비동기식 메모리 제어기 (908) 는, 데이터가 추후의 단계들로 포워딩될 수도 있기 때문에, TCS (978), TESS (980), TES (982), 및/또는 GS (984) 에서 하나 이상의 파라미터들을 단지 비동기식으로 판독할 수도 있다.

[0107] 도 9 와 연관되어 설명된 비동기식 메모리 제어기 (908) 는 도 1 내지 도 5 중 하나 이상과 연관되어 설명된 비동기식 메모리 제어기들 (108, 308) 중 하나 이상의 예일 수도 있다. 예를 들어, 비동기식 메모리 제어기 (908) 는 (예를 들어, 데이터 세트의 프로세싱 동안) 온-칩 메모리 (910) 및/또는 시스템 메모리 (914) 로부터 하나 이상의 파라미터들 (예를 들어, LOD 파라미터들) 을 비동기식으로 판독할 수도 있다. 일부 구성들에서, 업데이트된 파라미터(들)은 TCS (978), TESS (980), TES (982), GS (984), 래스터라이저 (986) 및 FS (990) 중 하나 이상에 제공될 수도 있다. 따라서, TCS (978), TESS (980), TES (982), GS (984), 래스터라이저 (986) 및 FS (990) 중 하나 이상은 데이터 세트가 프로세싱되고 있는 동안, 데이터 세트에 대해 초기에 확립된 프로세싱과는 상이하도록 데이터 세트의 프로세싱을 변화시킬 수도 있다.

[0108] 일부 구성들에서, 이것은 전자 디바이스 (302) 가 단일-패스 멀티-LOD 렌더링을 수행하게 할 수도 있다. 예를 들어, 비동기식 메모리 제어기 (908) 는, 현재 프로세싱 및/또는 렌더링 (예를 들어, 테슬레이팅) 되고 있는 데이터의 세트에 대해 초기에 확립된 다른 LOD 파라미터와 상이한 LOD 파라미터를 판독할 수도 있다. 업데이트된 LOD 파라미터는 TCS (978), TESS (980), TES (982), GS (984), 래스터라이저 (986) 및 FS (990) 중 하나 이상에 제공될 수도 있다. 따라서, TCS (978), TESS (980), TES (982), GS (984), 래스터라이저 (986) 및 FS (990) 중 하나 이상은 하나 이상의 상이한 파라미터들로 개시되었던 데이터 세트의 프로세싱 동안 업데이트된 LOD 파라미터에 따라 데이터 세트의 프로세싱을 변화 (예를 들어, 테슬레이션 레벨을 변화) 시킬 수도 있다.

[0109] VLIW 회로 (904)(예를 들어, 그래픽 파이프라인 (906)) 는 불-균일 프레임 버퍼 제어기 (912) 를 포함할 수도 있다. 도 9 에 예시된 바와 같이, 불-균일 프레임 버퍼 제어기 (912) 는 FS (990)(예를 들어, C/D (992)) 에 포함되고/되거나 이에서 구현될 수도 있다. 불-균일 프레임 버퍼 제어기 (912) 는 부가적으로 또는 대안으로, FS (990), C/D (992), 그래픽 파이프라인 (906) 및 온-칩 메모리 (910) 중 하나 이상에 포함되고/되거나 이에서 구현될 수도 있다는 것이 주목되어야 한다. 완전히 또는 부분적으로, 예를 들어 불-균일 프레임 버퍼 제어기 (912) 는 FS (990), C/D (992), 그래픽 파이프라인 (906), 온-칩 메모리 (910) 및 전자 디바이스 (902) 중 하나 이상에서 구현될 수도 있다. 불-균일 프레임 버퍼 제어기 (912) 는 C/D (992) 에서 구현될 수도 있다. 다르게는 추가의 레이턴시가 발생될 수도 있다는 것이 주목되어야 한다.

[0110] 도 9 와 연관되어 설명된 불-균일 프레임 버퍼 제어기 (912) 는 도 1 내지 도 5 중 하나 이상과 연관되어 설명된 불-균일 프레임 버퍼 제어기들 (112, 312) 중 하나 이상의 예일 수도 있다. 예를 들어, 불-균일 프레임 버퍼 제어기 (912) 는 하나 이상의 프레임 버퍼(들)의 상이한 서브세트들에 동적으로 액세스할 수도 있다. 일부 구성들에서, 프레임 버퍼의 상이한 서브세트들에 동적으로 액세스하는 것은 제 2 존의 적어도 하나의 픽셀과는 상이한 레이트에서 제 1 존의 적어도 하나의 픽셀에 액세스하는 것을 포함할 수도 있다. 부가적으로 또는 대안으로, 프레임 버퍼의 상이한 서브세트들에 동적으로 액세스하는 것은 (예를 들어, 제 1 픽셀의 프로세싱이 진행 중이고 제 2 픽셀의 프로세스가 완료될 때) 동적 세이더 서브-루틴 스왑핑을 가능하게 하는 것을 포

함할 수도 있다.      부가적으로 또는 대안으로, 불-균일 프레임 버퍼 제어기 (912)는 제 2 핵심의 제 2 샘플을 제 1 핵심의 프로세싱된 제 1 샘플을 대체하여 제 2 핵심의 제 2 샘플로 프로세싱하는 것을 회피하도록 구성될 수도 있다.

[0111]      일부 구성들에서, 전용 캐시는 특정 텍스처들을 핸들링하고 타겟들을 렌더링하도록 구현될 수도 있다.      캐시는 텍스처들의 세트 그 자체들 만큼 클 수도 있다.

[0112]      도 10 은 매우 긴 명령어 (VLIW) 회로 (1068)를 포함하는 전자 디바이스 (1066)의 다른 예를 예시하는 블록도이다.      특히, 도 10 은 그래픽 프로세싱을 위한 아키텍처의 다른 예를 예시한다.      도 10 과 연관되어 설명된 아키텍처의 하나 이상의 양태들은 인텔 (Intel) 아키텍처의 양태들과 유사하게 기능할 수도 있다.      이 아키텍처는 즉각 모드 렌더링 (IMR) 뿐만 아니라 공유된 물리적 및 가상 메모리와 통합된 메모리 아키텍처 (UMA)를 제공할 수도 있다.      이 아키텍처는 제로-복사 공유 뿐만 아니라 포인터-공유를 가능하게 할 수도 있다.

[0113]      전자 디바이스 (1066)는 프로세서 (1015) (예를 들어, CPU)를 포함할 수도 있다.      이 예에서, 프로세서 (1015)는 VLIW 회로 (1068)를 포함할 수도 있다.      예를 들어, VLIW 회로 (1068)는 프로세서 (1015)에 통합될 수도 있다.

[0114]      전자 디바이스 (1066)는 VLIW 회로 (1068) (예를 들어, GPU) 및 시스템 메모리 (1005)를 포함할 수도 있다.      VLIW 회로 (1068)는 그래픽 파이프라인 (1070) 및 온-칩 메모리 (1003)를 포함할 수도 있다.      그래픽 파이프라인 (1070)은 커맨드 스트리머 (CS) (1017), 정점 폐처 (VF) (1074), 정점 세이더 (VS) (1076), 훌 셰이더 (HS) (1078), 테슬레이터 (TESS) (1080) (예를 들어, 테슬레이션 엔진), 도메인 세이더 (DS) (1082), 지오메트리 세이더 (GS) (1084), 스트립 아웃 (SOL) (1019), 클립퍼 (Clip) (1021), 래스터라이저 (Rast) (1086) 및 프래그먼트 세이더 (FS) (1090) 중 하나 이상을 포함할 수도 있다.      많은 엘리먼트 라벨들이 편의를 위해 축약되어 있다.      온-칩 메모리 (1003)는 하나 이상의 버퍼들, 하나 이상의 캐시들, 등을 포함할 수도 있다.      일부 구성들에서, 온-칩 메모리 (1003)는 텍스처 버퍼, 프레임 버퍼 및/또는 온-칩 메모리 (1110)의 다른 블록을 포함할 수도 있다.      시스템 메모리 (1005)는 커맨드 데이터, 정점 데이터 (예를 들어, 지오메트리 데이터) 및/또는 텍스처 데이터를 포함할 수도 있다.

[0115]      장면을 렌더링하기 위해서, 전자 디바이스 (1066)는 시스템 메모리로부터 커맨드 데이터 및 정점 데이터를 획득할 수도 있다.      예를 들어, CS (1017)는 시스템 메모리 (1005)로부터 렌더링 커맨드(들)을 수신 및/또는 실행시킬 수도 있다.      정점 데이터는 하나 이상의 포인트들 (예를 들어, 정점들), 라인들 및/또는 다각형들을 나타낼 수도 있다.      정점 데이터 (1009)는 장면 및/또는 장면에서의 하나 이상의 객체들을 나타낼 수도 있다.

[0116]      VF (1074)는 정점 데이터를 시스템 메모리 (1005)로부터 VLIW 회로 (1068) (예를 들어, 그래픽 파이프라인 (1070))으로 폐치할 수도 있다.      VF (1074)는 정점 데이터를 VS (1076)에 제공할 수도 있고/있거나 정점 데이터를 캐시 (1001)에 저장할 수도 있다.

[0117]      VS (1076)는 정점 데이터를 상이한 공간으로 변환할 수도 있다.      예를 들어, VS (1076)는 정점 데이터를 3-차원 (3D) 공간으로부터 2-차원 (2D) 공간으로 변환할 수도 있다.      VS (1076)는 변환된 정점 데이터를 HS (1078)에 제공할 수도 있고/있거나 변환된 정점 데이터를 캐시 (1001)에 저장할 수도 있다.

[0118]      HS (1078)는 정점 데이터 (예를 들어, 변환된 정점 데이터)를 VS (1076)로부터 및/또는 캐시 (1001)로부터 수신할 수도 있다.      HS (1078)는 정점 데이터 (예를 들어, 변환된 정점 데이터)의 단위를 변환할 수도 있다.      예를 들어, HS (1078)는 정점 데이터의 단위를 테슬레이션을 위한 (예를 들어, 삼각형들과 같은 다각형들로 효율적으로 세분하기 위한) 단위로 변환할 수도 있다.      HS (1078)는 정보를 캐시 (1001)에 저장할 수도 있다.      예를 들어, HS (1078)는 HS (1078)에 의해 수행된 단위 변환을 나타내는 단위 표시자를 저장할 수도 있다.      단위-변환된 정점 데이터는 TESS (1080)에 제공될 수도 있다.

[0119]      TESS (1080)는 정점 데이터 (예를 들어, 단위-변환된 정점 데이터)를 테슬레이팅할 수도 있다.      예를 들어, TESS (1080)는 정점 데이터에 기초하여 더 많은 정점들을 생성할 수도 있다 (예를 들어, 삼각형들을 더 많은 삼각형들로 세분할 수도 있다).      TESS (1080)는 LOD 파라미터에 기초하여 동작할 수도 있다.      LOD 파라미터는 LOD 를 지정할 수도 있고/있거나 수행할 TESS (1080)에 대한 테슬레이션의 정도를 나타낼 수도 있다.      테슬레이팅된 정점 데이터는 DS (1082)에 제공될 수도 있다.

[0120]      DS (1082)는 정점 데이터 (예를 들어, 테슬레이팅된 정점 데이터)의 단위를 변환할 수도 있다.      예를

들어, DS (1082) 는 정점 데이터의 단위를 HS (1078) 에 의해 적용된 단위 변환 전의 단위로 다시 변환할 수도 있다. 일부 구성들에서, DS (1082) 는 정점 데이터의 단위를 변환 (예를 들어, 역 변환) 하기 위해 캐시 (1001)로부터 단위 표시자를 판독할 수도 있다. 다른 구성들에서, DS (1082) 는 HS (1078) 에 직접 커플링 될 수도 있고, 정점 데이터의 단위를 변환 (예를 들어, 역 변환) 하기 위해 HS (1078)로부터 단위 표시자를 수신할 수도 있다. DS (1082) 는 정점 데이터 (예를 들어, 역 단위-변환된 정점 데이터) 를 GS (1084) 에 제공하고/하거나 정점 데이터를 캐시 (1001) 에 저장할 수도 있다.

[0121] GS (1084) 는 정점 데이터 (예를 들어, 역 단위-변환된 정점 데이터) 상에서 하나 이상의 동작들을 수행할 수도 있다. 예를 들어, GS (1084) 는 정점 데이터에 기초하여 추가적인 지오메트리를 생성할 수도 있다. GS (1084) 는 (예를 들어, 추가적인 지오메트리를 갖는) 정점 데이터를 SOL (1019) 에 제공할 수도 있다.

[0122] SOL (1019) 은 (예를 들어, 추가적인 지오메트리를 갖는) 정점 데이터를 스트리밍하고/하거나 정점 데이터를 시스템 메모리 (1005) 에 저장할 수도 있다. SOL (1019) 는 (예를 들어, 추가적인 지오메트리를 갖는) 정점 데이터를 클립퍼 (1021) 에 제공할 수도 있다.

[0123] 클립퍼 (1021) 는 (예를 들어, 추가적인 지오메트리를 갖는) 정점 데이터의 일부를 폐기할 수도 있다. 예를 들어, 클립퍼 (1021) 는 뷰 (예를 들어, 뷰잉 절단체) 밖에 있는 정점 데이터를 폐기할 수도 있다. 클립퍼 (1021) 는 클립핑된 정점 데이터를 래스터라이저 (1086) 및/또는 캐시 (1001) 에 제공할 수도 있다.

[0124] 래스터라이저 (1086) 는 클립핑된 정점 데이터를 클립퍼 (1021) 및/또는 캐시 (1001)로부터 수신할 수도 있다. 래스터라이저 (1086) 는 정점 데이터를 래스터화할 수도 있다. 예를 들어, 래스터라이저는 정점 데이터를 픽셀 데이터로 컨버팅할 수도 있다. 픽셀 데이터는 FS (1090) 에 및/또는 캐시 (1001) 에 제공될 수도 있다.

[0125] FS (1090) 는 픽셀 데이터 상에서 프래그먼트 세이딩 또는 픽셀 세이딩을 수행할 수도 있다. 예를 들어, FS (1090) 는 하나 이상의 픽셀들의 하나 이상의 속성들 (예를 들어, 컬러, 밝기, 투명도 등) 을 결정할 수도 있다. 일부 구성들에서, FS (1090) 는 숨은 면 제거 (HSR) 를 수행할 수도 있다. 일부 구성들에서, FS (1090) 는 구성/분해 (C/D) 블록 (1092) 을 포함할 수도 있다. 대안으로, C/D (1092) 는 도 10 에 예시된 바와 같이 FS (1090)로부터 분리되고/되거나 FS (1090) 에 커플링될 수도 있다.

[0126] 일부 구성들에서, C/D (1092) 는 텍스처링 및/또는 블렌딩과 같은 동작들을 수행할 수도 있다. 예를 들어, C/D (1092) 는 다수의 층들을 블렌딩하여 최종 픽셀 값을 결정할 수도 있다. 일부 구성들에서, C/D (1092) 는 상이한 프레임 버퍼들을 조합할 수도 있다 (예를 들어, 픽셀마다 다수의 이미지들을 함께 블렌딩할 수도 있다). C/D (1092) 는 칩 상에서 (VLIW 회로 (1068) 상에서), 그래픽 파이프라인 (1070) 에서, 온-칩 메모리 (1003) 에서 구현될 수도 있고/있거나 VLIW 회로 (1068)로부터 분리될 수도 있다는 것이 주목되어야 한다. C/D (1092) 는, 이미지 데이터가 시스템 메모리 (1005) 에 및/또는 다른 스트리밍 아웃 (예를 들어, HDMI 스트리밍 아웃) 에 기입되기 전에 이미지 데이터 상에서 동작할 수도 있다. 일부 구성들에서, 시스템 메모리 (1005) 는 텍스처 데이터를, FS (1090) 및/또는 C/D (1092) 에 의해 엑세스될 수도 있는 캐시 (1001) 에 제공할 수도 있다. FS (1090) 는 캐시 (1001) 에 액세스함으로써 하나 이상의 동작들을 수행할 수도 있다. FS (1090) 는 픽셀 데이터 (예를 들어, 프로세싱된 픽셀 데이터) 를 구성/분해를 수행할 수도 있는 C/D (1092) 에 제공할 수도 있고, 픽셀 데이터를 캐시 (1001) 에 제공할 수도 있다.

[0127] 픽셀 데이터는 캐시 (1001) 를 통해 시스템 메모리 (1005) 로 출력될 수도 있다. 픽셀 데이터는 프리젠테이션을 위해 제공 (예를 들어, 출력) 될 수도 있다. 예를 들어, 픽셀 데이터는 프리젠테이션을 위해 디스플레이로 전송될 수도 있다.

[0128] 본원에 개시된 시스템들 및 방법들 없이, 도 10 과 연관되어 설명된 동작들은 도 8 과 연관되어 설명된 바와 같이 데이터 세트들 (예를 들어, 정점, 픽셀 및/또는 이미지 데이터의 세트들) 의 관점들에서 수행될 수도 있다는 것이 주목되어야 한다.

[0129] 도 11 은 도 10 과 연관되어 설명된 아키텍처에서 구현된 본원에 개시된 시스템들 및 방법들의 다른 예를 예시하는 블록도이다. 구체적으로, 도 11 은 전자 디바이스 (1102) 를 예시한다. 도 11 과 연관되어 설명된 전자 디바이스 (1102) 는 도 1 내지 도 5 중 하나 이상과 연관되어 전술된 전자 디바이스들 (102, 302) 중 하나 이상의 예일 수도 있다. 전자 디바이스 (1102) 는 도 1 내지 도 5 중 하나 이상과 연관되어 설명된 방법들, 기능들, 단계들, 동작들, 등 중 하나 이상을 수행하도록 구성될 수도 있다.

[0130] 전자 디바이스 (1102) 는 프로세서 (1124) (예를 들어, CPU) 를 포함할 수도 있다. 프로세서 (1124) 는 도

3 과 연관되어 설명된 프로세서 (324) 의 일 예일 수도 있다. 이 예에서, 프로세서 (1015) 는 VLIW 회로 (1104) 를 포함할 수도 있다. 예를 들어, VLIW 회로 (1104) 는 프로세서 (1124) 에 통합될 수도 있다.

[0131] 전자 디바이스 (1102) 는 VLIW 회로 (1104) (예를 들어, GPU) 및 시스템 메모리 (1114) 를 포함할 수도 있다. VLIW 회로 (1104) 는 도 1 내지 도 5 중 하나 이상과 연관되어 전술된 VLIW 회로들 (104, 304) 중 하나 이상의 일 예일 수도 있다. 부가적으로 또는 대안으로, 시스템 메모리 (1114) 는 도 1 내지 도 5 중 하나 이상과 연관되어 설명된 시스템 메모리들 (114, 314) 중 하나 이상의 예일 수도 있다. 시스템 메모리 (1114) 는 커맨드 데이터, 정점 데이터 (예를 들어, 지오메트리 데이터), 텍스처 데이터 및/또는 렌더링된 타겟 데이터 (예를 들어, 픽셀 데이터) 를 포함할 수도 있다.

[0132] VLIW 회로 (1104) 는 그래픽 파이프라인 (1106) 및 온-칩 메모리 (1110) 를 포함할 수도 있다. 도 11 과 연관되어 설명된 그래픽 파이프라인 (1106) 은 도 1 내지 도 5 중 하나 이상과 연관되어 설명된 그래픽 파이프라인들 (106, 306) 중 하나 이상의 일 예일 수도 있다. 부가적으로 또는 대안으로, 도 11 과 연관되어 설명된 온-칩 메모리 (1110) 는 도 1 내지 도 5 중 하나 이상과 연관되어 설명된 온-칩 메모리들 (110, 310) 중 하나 이상의 일 예일 수도 있다.

[0133] 온-칩 메모리 (1110) 는 하나 이상의 버퍼들, 하나 이상의 캐시들 (1101), 등을 포함할 수도 있다. 예를 들어, 레벨 1 (L1) 및/또는 레벨 2 (L2) 캐시들은 온-칩 스토리지로서 이용될 수도 있다. 일부 구성들에서, 파이프라인 예측 하드웨어는 디스에이블될 수도 있다. 온-칩 메모리 (1110) 는 도 3 및 도 4 중 하나 이상과 연관되어 설명된 바와 같이 하나 이상의 프레임 버퍼들을 포함할 수도 있다는 것이 주목되어야 한다. 프레임 버퍼(들)은 온-칩 메모리 (1110), 캐시 (1101), 등 중 하나 이상에 포함될 수도 있다. 부가적으로 또는 대안으로, 프레임 버퍼(들)은 시스템 메모리 (1114) 에 포함될 수도 있다. 일부 구성들에서, 하나 이상의 프레임 버퍼들은 온-칩 메모리 (1110), 시스템 메모리 (1114) 또는 양자 모두에 포함될 수도 있다.

[0134] 그래픽 파이프라인 (1106) 은 CS (1117), VF (1174), VS (1176), HS (1178), TESS (1180), DS (1182), GS (1184), SOL (1119), 클립퍼 (1121), 래스터라이저 (1186), FS (1190) 및 C/D (1192) 중 하나 이상을 포함할 수도 있다. 일부 구성들에서, CS (1117), VF (1174), VS (1176), HS (1178), TESS (1180), DS (1182), GS (1184), SOL (1119), 클립퍼 (1121), 래스터라이저 (1186), FS (1190) 및 C/D (1192) 중 하나 이상은 도 10 과 연관되어 설명된 하나 이상의 대응하는 엘리먼트들의 동작들 중 하나 이상을 수행할 수도 있다.

[0135] 도 11 에 예시된 구성들에서, VLIW 회로 (1104) (예를 들어, 그래픽 파이프라인 (1106)) 는 비동기식 메모리 제어기 (1108) 를 포함할 수도 있다. 비동기식 메모리 제어기 (1108) 는 HS (1178), TESS (1180), DS (1182), GS (1184), 래스터라이저 (1186) 및 FS (1190) 중 하나 이상을 포함하고/하거나 이들에서 구현될 수도 있다. 완전히 또는 부분적으로, 예를 들어 비동기식 메모리 제어기 (1108a) 는 HS (1178), TESS (1180), DS (1182), GS (1184), 래스터라이저 (1186) 및 FS (1190) 에서 구현될 수도 있다. 일반적인 라벨 "1108" 은, 비동기식 메모리 제어기 (1108) 가 도 11 에 예시된 엘리먼트들 (1108a-f) 중 어느 하나 또는 전부에서 구현될 수도 있다는 것을 가리킬 수도 있다. 일부 구성들에서, 비동기식 메모리 제어기 (1108) 는 HS (1178), TESS (1180), DS (1182) 및 GS (1184) 중 하나 이상에서만 구현될 수도 있다. 예를 들어, 비동기식 메모리 제어기 (1108) 는, 데이터가 추후의 단계들로 포워딩될 수도 있기 때문에, HS (1178), TESS (1180), DS (1182) 및/또는 GS (1184) 에서 하나 이상의 파라미터들을 단지 비동기식으로 판독할 수도 있다.

[0136] 도 11 과 연관되어 설명된 비동기식 메모리 제어기 (1108) 는 도 1 내지 도 5 중 하나 이상과 연관되어 설명된 비동기식 메모리 제어기들 (108, 308) 중 하나 이상의 예일 수도 있다. 예를 들어, 비동기식 메모리 제어기 (1108) 는 (예를 들어, 데이터 세트의 프로세싱 동안) 온-칩 메모리 (1110) 및/또는 시스템 메모리 (1114) 로부터 하나 이상의 파라미터들 (예를 들어, LOD 파라미터들) 을 비동기식으로 판독할 수도 있다. 일부 구성들에서, 업데이트된 파라미터(들)은 HS (1178), TESS (1180), DS (1182), GS (1184), 래스터라이저 (1186) 및 FS (1190) 중 하나 이상에 제공될 수도 있다. 따라서, HS (1178), TESS (1180), DS (1182), GS (1184), 래스터라이저 (1186) 및 FS (1190) 중 하나 이상은 데이터 세트가 프로세싱되고 있는 동안, 데이터 세트에 대해 초기에 확립된 프로세싱과는 상이하도록 데이터 세트의 프로세싱을 변화시킬 수도 있다.

[0137] 일부 구성들에서, 이것은 전자 디바이스 (1102) 가 단일-패스 멀티-LOD 렌더링을 수행하게 할 수도 있다. 예를 들어, 비동기식 메모리 제어기 (1108) 는, 현재 프로세싱 및/또는 렌더링 (예를 들어, 테슬레이팅) 되고 있는 데이터의 세트에 대해 초기에 확립된 다른 LOD 파라미터와는 상이한 LOD 파라미터를 판독할 수도 있다. 업데이트된 LOD 파라미터는 HS (1178), TESS (1180), DS (1182), GS (1184), 래스터라이저 (1186) 및 FS (1190) 중 하나 이상에 제공될 수도 있다. 따라서, HS (1178), TESS (1180), DS (1182), GS (1184), 래스터라이저 (1186) 및 FS (1190) 중 하나 이상에 제공될 수도 있다.

터라이저 (1186) 및 FS (1190) 중 하나 이상은 하나 이상의 상이한 파라미터들로 개시되었던 데이터 세트의 프로세싱 동안 업데이트된 LOD 파라미터에 따라 데이터 세트의 프로세싱을 변화 (예를 들어, 테슬레이션 레벨을 변화) 시킬 수도 있다.

[0138] VLIW 회로 (1104)(예를 들어, 그래픽 파이프라인 (1106))는 불-균일 프레임 버퍼 제어기 (1112)를 포함할 수도 있다. 도 11에 예시된 바와 같이, 불-균일 프레임 버퍼 제어기 (1112)는 C/D (1192)에 포함되고/되거나 구현될 수도 있다. 불-균일 프레임 버퍼 제어기 (1112)는 부가적으로 또는 대안으로, FS (1190), C/D (1192), 그래픽 파이프라인 (1106) 및 온-칩 메모리 (1110) 중 하나 이상에 포함되고/되거나 이들에서 구현될 수도 있다는 것이 주목되어야 한다. 완전히 또는 부분적으로, 예를 들어 불-균일 프레임 버퍼 제어기 (1112)는 FS (1190), C/D (1192), 그래픽 파이프라인 (1106), 온-칩 메모리 (1110) 및 전자 디바이스 (1102) 중 하나 이상에서 구현될 수도 있다.

[0139] 도 11과 연관되어 설명된 불-균일 프레임 버퍼 제어기 (1112)는 도 1 내지 도 5 중 하나 이상과 연관되어 설명된 불-균일 프레임 버퍼 제어기들 (112, 312) 중 하나 이상의 예일 수도 있다. 예를 들어, 불-균일 프레임 버퍼 제어기 (1112)는 하나 이상의 프레임 버퍼(들)의 상이한 서브세트들에 동적으로 액세스할 수도 있다. 일부 구성들에서, 프레임 버퍼의 상이한 서브세트들에 동적으로 액세스하는 것은 제 2 존의 적어도 하나의 픽셀과는 상이한 레이트에서 제 1 존의 적어도 하나의 픽셀에 액세스하는 것을 포함할 수도 있다. 부가적으로 또는 대안으로, 프레임 버퍼의 상이한 서브세트들에 동적으로 액세스하는 것은 (예를 들어, 제 1 픽셀의 프로세싱이 진행 중이고 제 2 픽셀의 프로세스가 완료될 때) 동적 세이더 서브-루틴 스왑핑을 가능하게 하는 것을 포함할 수도 있다. 부가적으로 또는 대안으로, 불-균일 프레임 버퍼 제어기 (1112)는 제 2 픽셀의 제 2 샘플을 제 1 픽셀의 프로세싱된 제 1 샘플로 대체하여 제 2 픽셀의 제 2 샘플을 프로세싱하는 것을 회피하도록 구성될 수도 있다. 일부 구성들에서, 도 11과 연관되어 설명된 전자 디바이스 (1102)는 공유된 메모리 및/또는 적응적 멀티-주파수 세이딩을 사용하여 비동기식 적응적 안티-에일리어싱을 수행하도록 구현될 수도 있다는 것이 주목되어야 한다.

[0140] 도 12는 매우 긴 명령어 (VLIW) 회로 (1268)를 포함하는 전자 디바이스 (1266)의 다른 예를 예시하는 블록도이다. 특히, 도 12는 그래픽 프로세싱을 위한 아키텍처의 일 예를 예시한다. 도 12와 연관되어 설명된 아키텍처의 하나 이상의 양태들은 이매진 테크놀로지 (Imagine Technologies)(예를 들어, PowerVR 그래픽) 아키텍처의 양태들과 유사하게 기능할 수도 있다. 이 아키텍처는 타일-기반 연기된 렌더링 (Tile-Based Deferred Rendering; TBDR)을 제공할 수도 있는 타일링된 아키텍처이다. 불분명한 지오메트리는 (예를 들어, 캐싱 대신에) 타일들로 소팅될 수도 있다.

[0141] 전자 디바이스 (1266)는 VLIW 회로 (1268) (예를 들어, GPU) 및 시스템 메모리 (1205) (예를 들어, DRAM)을 포함할 수도 있다. VLIW 회로 (1268)는 그래픽 파이프라인 (1270) 및 온-칩 메모리 (1203)를 포함할 수도 있다. 그래픽 파이프라인 (1270)은 정점 프로세서 (VP)(1274), 정점 세이더 (VS)(1276), 테슬레이션 제어 세이더 (TCS)(1278), 테슬레이터 (TESS)(1280) (예를 들어, 테슬레이션 엔진), 테슬레이션 평가 세이더 (TES)(1282), 지오메트리 세이더 (GS)(1284), 타일러 (1223), 래스터라이저 (Rast)(1286) 및 프래그먼트 세이더 (FS)(1290) 중 하나 이상을 포함할 수도 있다. 많은 엘리먼트 라벨들이 편의를 위해 축약되어 있다. 온-칩 메모리 (1203)는 심도 버퍼 (1237) 및 컬러 버퍼 (1239)를 포함할 수도 있다. 시스템 메모리 (1205)는 지오메트리 데이터 (1209), 파라미터 버퍼 (1235), 텍스처 데이터 (1211) 및 프레임 버퍼 (1241)를 포함할 수도 있다. 지오메트리 데이터 (1209)는 하나 이상의 포인트들 (예를 들어, 정점들), 라인들 및/또는 다각형들을 나타낼 수도 있다. 지오메트리 데이터 (1209)는 장면 및/또는 장면에서의 하나 이상의 객체들을 나타낼 수도 있다.

[0142] VP (1274)는 지오메트리 데이터를 시스템 메모리 (1205)로부터 VLIW 회로 (1268)(예를 들어, 그래픽 파이프라인 (1270))으로 페치할 수도 있다. VP (1274)는 지오메트리 데이터를 VS (1276)에 제공할 수도 있다.

[0143] VS (1276)는 지오메트리 데이터를 상이한 공간으로 변환 (예를 들어, 프로젝트) 할 수도 있다. 예를 들어, VS (1276)는 지오메트리 데이터를 3-차원 (3D) 공간으로부터 2-차원 (2D) 공간으로 변환할 수도 있다. 일부 구성들에서, VS (1276)는 클립핑, 프로젝션 및/또는 선별 (culling)을 수행할 수도 있다. 예를 들어, VS (1276)는 뷔잉 절단체 밖에 있는 지오메트리 데이터를 클립 아웃할 수도 있다. VS (1276)는 지오메트리 데이터를 3D 공간으로부터 2D 공간으로 프로젝팅할 수도 있다. VS (1276)는 또한, 지오메트리 데이터의 일부를 선별할 수도 있다. 예를 들어, 가려진 지오메트리 (예를 들어, 다른 지오메트리에 의해 차단되기 때문에 볼 수 없는 지오메트리)에 대응하는 지오메트리 데이터는 제거될 수도 있다. VS (1276)는 변환된 지

오메트리 데이터를 TCS (1278)에 제공할 수도 있다.

[0144] TCS (1278)는 지오메트리 데이터 (예를 들어, 변환된 지오메트리 데이터)를 VS (1276)로부터 및/또는 버퍼 (1296)로부터 수신할 수도 있다. TCS (1278)는 지오메트리 데이터 (예를 들어, 변환된 지오메트리 데이터)의 단위를 변환할 수도 있다. 예를 들어, TCS (1278)는 지오메트리 데이터의 단위를 테슬레이션을 위한 (예를 들어, 삼각형들과 같은 다각형들로 효율적으로 세분하기 위한) 단위로 변환할 수도 있다. 예를 들어, TCS (1278)는 TCS (1278)에 의해 수행된 단위 변환을 나타내는 단위 표시자를 생성할 수도 있다. 단위-변환된 지오메트리 데이터는 TESS (1280)에 제공될 수도 있다.

[0145] TESS (1280)는 지오메트리 데이터 (예를 들어, 단위-변환된 지오메트리 데이터)를 테슬레이팅할 수도 있다. 예를 들어, TESS (1280)는 지오메트리 데이터에 기초하여 더 많은 지오메트리 데이터 (예를 들어, 정점들)를 생성할 수도 있다 (예를 들어, 삼각형들을 더 많은 삼각형들로 세분할 수도 있다). TESS (1280)는 LOD 파라미터에 기초하여 동작할 수도 있다. LOD 파라미터는 LOD를 지정할 수도 있고/있거나 수행할 TESS (1280)에 대한 테슬레이션의 정도를 나타낼 수도 있다. 테슬레이팅된 지오메트리 데이터는 TES (1282)에 제공될 수도 있다.

[0146] TES (1282)는 지오메트리 데이터 (예를 들어, 테슬레이팅된 지오메트리 데이터)의 단위를 변환할 수도 있다. 예를 들어, TES (1282)는 지오메트리 데이터의 단위를 TCS (1278)에 의해 적용된 단위 변환 전의 단위로 다시 변환할 수도 있다. 일부 구성들에서, TES (1282)는 지오메트리 데이터의 단위를 변환 (예를 들어, 역 변환)하기 위해 TCS (1278) 및/또는 메모리 (예를 들어, 온-칩 메모리 (1203) 및/또는 시스템 메모리 (1205))로부터 단위 표시자를 획득할 수도 있다. TESS (1282)는 지오메트리 데이터 (예를 들어, 역 단위-변환된 지오메트리 데이터)를 GS (1284)에 제공할 수도 있다.

[0147] GS (1284)는 지오메트리 데이터 (예를 들어, 역 단위-변환된 지오메트리 데이터)상에서 하나 이상의 동작들을 수행할 수도 있다. 예를 들어, GS (1284)는 지오메트리 데이터에 기초하여 추가적인 지오메트리를 생성할 수도 있다. GS (1284)는 (예를 들어, 추가적인 지오메트리를 갖는) 지오메트리 데이터를 타일러 (1223)에 제공할 수도 있다.

[0148] 타일러 (1223)는 (예를 들어, 추가적인 지오메트리를 갖는) 지오메트리 데이터를 타일들로 스플릿할 수도 있다. 예를 들어, 타일러 (1223)는 지오메트리 데이터를 더 작은 그룹들의 지오메트리 데이터로 분할할 수도 있다. 타일들은 연속적인 지오메트리 데이터를 포함할 수도 있다. 타일러 (1223)는 타일들을 파라미터 버퍼 (1235)에 제공할 수도 있다.

[0149] 파라미터 버퍼 (1235)는 타일들을 저장할 수도 있다. 예를 들어, 파라미터 버퍼 (1235)는 프리미티브들 (예를 들어, 지오메트리 데이터, 정점들, 라인들, 다각형들, 등)의 리스트를 저장할 수도 있다. 도 12에 설명된 타일링된 아키텍처에서, 타일 프로세싱은 시스템 메모리 액세스들의 공간적 집약성 (locality)을 래버리징할 수도 있다. 예를 들어, 타일에 국부적인 동작들은 비교적 "저렴" 할 수도 있다 (예를 들어, 매우 적은 프로세싱, 전력, 메모리 및/또는 시간 리소스들을 이용할 수도 있다). 일부 구성들에서, VLIW 회로 (1268)는 지오메트리 데이터를 테슬레이팅하고 이를 지오메트리 데이터를 타일링을 위해 파라미터 버퍼 (1235)로 전송할 수도 있다. 지오메트리 데이터 (예를 들어, 타일링된 지오메트리 데이터, 프리미티브들, 등)는 래스터라이저 (1286)에 제공될 수도 있다. 파라미터 버퍼 (1235)에 저장된 파라미터들은 파라미터(들) (예를 들어, LOD 파라미터(들))을 렌더링하는 것을 포함하지 않을 수도 있다는 것이 주목되어야 한다.

[0150] 래스터라이저 (1286)는 파라미터 버퍼 (1235)로부터 지오메트리 데이터 (예를 들어, 타일링된 지오메트리 데이터, 프리미티브들, 등)를 수신할 수도 있다. 래스터라이저 (1286)는 지오메트리 데이터를 래스터화할 수도 있다. 예를 들어, 래스터라이저는 지오메트리 데이터를 픽셀 데이터를 컨버팅할 수도 있다. 픽셀 데이터는 FS (1290)에 제공될 수도 있다.

[0151] FS (1290)는 픽셀 데이터 상에서 프래그먼트 셰이딩 또는 픽셀 셰이딩을 수행할 수도 있다. 예를 들어, FS (1290)는 하나 이상의 픽셀들의 하나 이상의 속성을 (예를 들어, 컬러, 밝기, 투명도 등)을 결정할 수도 있다. 일부 구성들에서, FS (1290)는 숨겨진 면 제거 (HSR) 및 심도 테스트 (DT) 블록 (1225), 태그 버퍼 (TB) (1227), 텍스처 및 셰이드 (T&S) 블록 (1229), 알파 테스트 (AT) 블록 (1231) 및 알파 블렌드 (AB) 블록 (1223) 중 하나 이상을 포함할 수도 있다. HSR & DT (1225)는 심도 테스팅 및 숨겨진 면 제거를 수행할 수도 있다. 예를 들어, 심도 테스팅은 픽셀들에 대응하는 심도를 결정하는 것을 포함할 수도 있다. HSR & DT는 각각의 픽셀에 대한 심도를 결정하고 심도 표시자들을 심도 버퍼 (1237)에 저장할 수도 있다. 숨겨

진 면 제거를 수행하는 것은 다른 픽셀들보다 더 큰 심도에 있는 (예를 들어, 다른 픽셀들에 의해 가려지는) 픽셀들을 폐기하는 것을 포함할 수도 있다. 일부 접근들에서, 태그 버퍼 (TB)(1227)는 선택적으로, 더 빠른 실행을 위해 픽셀들을 재그루핑할 수도 있다. T&S (1229)는 시스템 메모리로부터 텍스처 데이터 (1211)를 획득할 수도 있다. AT (1231)는 커스텀 "스텐실" 테스트 (예를 들어, 다른 심도 테스트)를 수행할 수도 있다. 일부 구성들에서, AT (1231)는 HSR & DT (1225)를 업데이트할 수도 있다. AB (1233)는 픽셀들 (예를 들어, 하나 이상의 계층들 및/또는 프레임 버퍼들로부터의 픽셀들)을 블렌딩할 수도 있다. 예를 들어, AB (1233)는 구성 및/또는 분해 동작을 수행할 수도 있고, 여기서 2 개의 이미지들은 알파 값을 사용하여 블렌딩될 수도 있다.

[0152] AB (1233)는 픽셀 데이터를 컬러 버퍼 (1239)에 제공할 수도 있다. 도 12에 예시된 바와 같이, 컬러 및 심도 버퍼 데이터는 칩 상에 저장될 수도 있다. 컬러 버퍼 (1239)는 픽셀 데이터를 프레임 버퍼 (1241)에 제공할 수도 있다. 프레임 버퍼 (1241)는 픽셀 데이터를 출력할 수도 있다. 픽셀 데이터는 프리젠테이션을 위해 제공 (예를 들어, 출력) 될 수도 있다. 예를 들어, 픽셀 데이터는 프리젠테이션을 위해 디스플레이로 전송될 수도 있다.

[0153] 본원에 개시된 시스템들 및 방법들 없이, 도 12와 연관되어 설명된 동작들은 도 8과 연관되어 설명된 바와 같이 데이터 세트들 (예를 들어, 정점, 픽셀 및/또는 이미지 데이터의 세트들)의 관점들에서 수행될 수도 있다는 것이 주목되어야 한다.

[0154] 도 13은 도 12와 연관되어 설명된 아키텍처에서 구현된 본원에 개시된 시스템들 및 방법들의 예를 예시하는 블록도이다. 이 아키텍처는 TBDR을 제공할 수도 있다. 구체적으로, 도 13은 전자 디바이스 (1302)를 예시한다. 도 13과 연관되어 설명된 전자 디바이스 (1302)는 도 1 내지 도 5 중 하나 이상과 연관되어 전술된 전자 디바이스들 (102, 302) 중 하나 이상의 예일 수도 있다. 전자 디바이스 (1302)는 도 1 내지 도 5 중 하나 이상과 연관되어 설명된 방법들, 기능들, 단계들, 동작들, 등 중 하나 이상을 수행하도록 구성될 수도 있다.

[0155] 전자 디바이스 (1302)는 VLIW 회로 (1304) (예를 들어, GPU) 및 시스템 메모리 (1314)를 포함할 수도 있다. VLIW 회로 (1304)는 도 1 내지 도 5 중 하나 이상과 연관되어 전술된 VLIW 회로들 (104, 304) 중 하나 이상의 일 예일 수도 있다. 부가적으로 또는 대안으로, 시스템 메모리 (1314)는 도 1 내지 도 5 중 하나 이상과 연관되어 설명된 시스템 메모리들 (114, 314) 중 하나 이상의 예일 수도 있다. 시스템 메모리 (1314)는 지오메트리 데이터 (1309), 파라미터 버퍼 (1335), 텍스처 데이터 (1311) 및/또는 프레임 버퍼 (1341)를 포함할 수도 있다. 지오메트리 데이터 (1309), 파라미터 버퍼 (1335), 텍스처 데이터 (1311) 및/또는 프레임 버퍼 (1341) 중 하나 이상은 도 12와 연관되어 설명된 대응하는 엘리먼트들과 유사할 수도 있다. 시스템 메모리 (1314)는 도 3 및 도 4 중 하나 이상과 연관되어 설명된 바와 같이 하나 이상의 프레임 버퍼들을 포함할 수도 있다는 것이 주목되어야 한다. 예를 들어, 프레임 버퍼 (1341)는 도 3 및 도 4 중 하나 이상과 연관되어 설명된 프레임 버퍼들 중 하나 이상의 예일 수도 있다. 일부 구성들에서, 하나 이상의 프레임 버퍼들은 온-칩 메모리 (1310), 시스템 메모리 (1314) 또는 양자 모두에 포함될 수도 있다.

[0156] VLIW 회로 (1304)는 그래픽 파이프라인 (1306) 및 온-칩 메모리 (1310)를 포함할 수도 있다. 도 13과 연관되어 설명된 그래픽 파이프라인 (1306)은 도 1 내지 도 5 중 하나 이상과 연관되어 설명된 그래픽 파이프라인들 (106, 306) 중 하나 이상의 일 예일 수도 있다. 부가적으로 또는 대안으로, 도 13과 연관되어 설명된 온-칩 메모리 (1310)는 도 1 내지 도 5 중 하나 이상과 연관되어 설명된 온-칩 메모리들 (110, 310) 중 하나 이상의 일 예일 수도 있다.

[0157] 온-칩 메모리 (1310)는 캐시 (1301) 및/또는 심도 및 컬러 버퍼 (1343)를 포함할 수도 있다. 일부 구성들에서, 온-칩 메모리 (1310), 캐시 (1301) 및/또는 심도 및 컬러 버퍼 (1343) 중 하나 이상은 도 12와 연관되어 설명된 대응하는 엘리먼트들과 유사할 수도 있다.

[0158] 그래픽 파이프라인 (1306)은 VP (1374), VS (1376), TCS (1378), TESS (1380), TES (1382), GS (1384), 타일러 (1323), 래스터라이저 (1386) 및 FS (1390) 중 하나 이상을 포함할 수도 있다. 일부 구성들에서, VP (1374), VS (1376), TCS (1378), TESS (1380), TES (1382), GS (1384), 타일러 (1323), 래스터라이저 (1386) 및 FS (1390) 중 하나 이상은 도 12와 연관되어 설명된 하나 이상의 대응하는 엘리먼트들의 동작들 중 하나 이상을 수행할 수도 있다. FS (1390)는 일부 구성들에서 도 12와 연관되어 설명된 바와 같이 HSR & DT, TB, T&S, AT 및 AB 중 하나 이상을 포함할 수도 있다.

[0159]

도 13 에 예시된 구성들에서, VLIW 회로 (1304)(예를 들어, 그래픽 파이프라인 (1306)) 는 비동기식 메모리 제어기 (1308) 를 포함할 수도 있다. 비동기식 메모리 제어기 (1308) 는 TCS (1378), TESS (1380), TES (1382), GS (1384), 래스터라이저 (1386) 및 FS (1390) 중 하나 이상을 포함하고/하거나 이들에서 구현될 수도 있다. 완전히 또는 부분적으로, 예를 들어 비동기식 메모리 제어기 (1308) 는 TCS (1378), TESS (1380), TES (1382), GS (1384), 래스터라이저 (1386) 및/또는 FS (1390) 에서 구현될 수도 있다. 일반적인 라벨 "1308" 은, 비동기식 메모리 제어기 (1308) 가 도 13 에 예시된 엘리먼트들 (1308a-f) 중 어느 하나 또는 전부에서 구현될 수도 있다는 것을 가리킬 수도 있다. 일부 구성들에서, 비동기식 메모리 제어기 (1308) 는 TCS (1378), TESS (1380), TES (1382) 및 GS (1384) 중 하나 이상에서만 구현될 수도 있다. 예를 들어, 비동기식 메모리 제어기 (1308) 는, 데이터가 추후의 단계들로 포워딩될 수도 있기 때문에, TCS (1378), TESS (1380), TES (1382), 및/또는 GS (1384) 에서 하나 이상의 파라미터들을 단지 비동기식으로 판독할 수도 있다.

[0160]

도 13 과 연관되어 설명된 비동기식 메모리 제어기 (1308) 는 도 1 내지 도 5 중 하나 이상과 연관되어 설명된 비동기식 메모리 제어기들 (108, 308) 중 하나 이상의 예일 수도 있다. 예를 들어, 비동기식 메모리 제어기 (1308) 는 (예를 들어, 데이터 세트의 프로세싱 동안) 시스템 메모리 (1314) 로부터 하나 이상의 파라미터들 (예를 들어, LOD 파라미터들) 을 비동기식으로 판독할 수도 있다. 일부 구성들에서, 업데이트된 파라미터 (들)은 TCS (1378), TESS (1380), TES (1382), GS (1384), 래스터라이저 (1386) 및 FS (1390) 중 하나 이상에 제공될 수도 있다. 따라서, TCS (1378), TESS (1380), TES (1382), GS (1384), 래스터라이저 (1386) 및 FS (1390) 중 하나 이상은 데이터 세트가 프로세싱되고 있는 동안, 데이터 세트에 대해 초기에 확립된 프로세싱과는 상이하도록 데이터 세트의 프로세싱을 변화시킬 수도 있다.

[0161]

일부 구성들에서, 이것은 전자 디바이스 (1302) 가 단일-패스 멀티-LOD 렌더링을 수행하게 할 수도 있다. 예를 들어, 비동기식 메모리 제어기 (1308) 는, 현재 프로세싱 및/또는 렌더링 (예를 들어, 테슬레이팅) 되고 있는 데이터의 세트에 대해 초기에 확립된 다른 LOD 파라미터와 상이한 LOD 파라미터를 판독할 수도 있다. 업데이트된 LOD 파라미터는 TCS (1378), TESS (1380), TES (1382), GS (1384), 래스터라이저 (1386) 및 FS (1390) 중 하나 이상에 제공될 수도 있다. 따라서, TCS (1378), TESS (1380), TES (1382), GS (1384), 래스터라이저 (1386) 및 FS (1390) 중 하나 이상은 하나 이상의 상이한 파라미터들로 개시되었던 데이터 세트의 프로세싱 동안 업데이트된 LOD 파라미터에 따라 데이터 세트의 프로세싱을 변화 (예를 들어, 테슬레이션 레벨을 변화) 시킬 수도 있다.

[0162]

VLIW 회로 (1304)(예를 들어, 그래픽 파이프라인 (1306)) 는 불-균일 프레임 버퍼 제어기 (1312) 를 포함할 수도 있다. 도 13 에 예시된 바와 같이, 불-균일 프레임 버퍼 제어기 (1312) 는 FS (1390) 에 포함되고/되거나 이에서 구현될 수도 있다. 불-균일 프레임 버퍼 제어기 (1312) 는 부가적으로 또는 대안으로, FS (1390), 그래픽 파이프라인 (1306) 및 온-칩 메모리 (1310) 중 하나 이상에 포함되고/되거나 이들에서 구현될 수도 있다는 것이 주목되어야 한다. 완전히 또는 부분적으로, 예를 들어 불-균일 프레임 버퍼 제어기 (1312) 는 FS (1390), 그래픽 파이프라인 (1306), 온-칩 메모리 (1310) 및 전자 디바이스 (1302) 중 하나 이상에서 구현될 수도 있다.

[0163]

도 13 과 연관되어 설명된 불-균일 프레임 버퍼 제어기 (1312) 는 도 1 내지 도 5 중 하나 이상과 연관되어 설명된 불-균일 프레임 버퍼 제어기들 (112, 312) 중 하나 이상의 예일 수도 있다. 예를 들어, 불-균일 프레임 버퍼 제어기 (1312) 는 하나 이상의 프레임 버퍼(들)의 상이한 서브세트들에 동적으로 액세스할 수도 있다.

일부 구성들에서, 프레임 버퍼의 상이한 서브세트들에 동적으로 액세스하는 것은 제 2 존의 적어도 하나의 픽셀과는 상이한 레이트에서 제 1 존의 적어도 하나의 픽셀에 액세스하는 것을 포함할 수도 있다. 부가적으로 또는 대안으로, 프레임 버퍼의 상이한 서브세트들에 동적으로 액세스하는 것은 (예를 들어, 제 1 픽셀의 프로세싱이 진행 중이고 제 2 픽셀의 프로세스가 완료될 때) 동적 세이더 서브-루틴 스왑핑을 가능하게 하는 것을 포함할 수도 있다. 부가적으로 또는 대안으로, 불-균일 프레임 버퍼 제어기 (1312) 는 제 1 픽셀의 프로세싱된 제 1 샘플로 제 2 픽셀의 제 2 샘플을 대체하여 제 2 픽셀의 제 2 샘플을 프로세싱하는 것을 회피하도록 구성될 수도 있다. 도 13 에 예시된 아키텍처는 온-칩 버퍼들 (예를 들어, 심도 및 컬러 버퍼들) 의 커스텀 구성을 허용할 수도 있다. 이것은 VR 에 대한 렌더링, 밍맵 생성 등을 나란히 허용할 수도 있다.

[0164]

도 14 는 매우 긴 명령어 (VLIW) 회로 (1468) 를 포함하는 전자 디바이스 (1466) 의 다른 예를 예시하는 블록도이다. 특히, 도 14 는 그래픽 프로세싱을 위한 아키텍처의 일 예를 예시한다. 이 아키텍처는 즉각 모드 (예를 들어, IMR) 및 타일링된 모드 (예를 들어, TBDR) 양자 모두를 제공 (예를 들어, 지원) 할 수도 있다. 예를 들어, 아키텍처는 즉각 모드 또는 타일링된 모드의 선택을 제공할 수도 있다. 도 14 에 예시된 예는

(예를 들어, 중간 지오메트리에 대해 필요한) 대형 온-칩 캐시/버퍼들을 회피할 수도 있다.

[0165] 전자 디바이스 (1466)는 VLIW 회로 (1468) (예를 들어, GPU) 및 시스템 메모리 (1405) (예를 들어, DRAM)을 포함할 수도 있다. VLIW 회로 (1468)는 그래픽 파이프라인 (1470) 및 온-칩 메모리 (1403)를 포함할 수도 있다. 그래픽 파이프라인 (1470)은 정점 프로세서 (VP)(1474), 정점 세이더 (VS)(1476), 스위치들 A-B (1447a-b) (예를 들어, 멀티플렉서들), 테슬레이션 제어 세이더 (TCS)(1478), 테슬레이터 (TESS)(1480) (예를 들어, 테슬레이션 엔진), 테슬레이션 평가 세이더 (TES)(1482), 지오메트리 세이더 (GS)(1484), 타일러 (1449), 래스터라이저 (Rast)(1486) 및 프래그먼트 세이더 (FS)(1490) 중 하나 이상을 포함할 수도 있다. 많은 엘리먼트 라벨들이 편의를 위해 축약되어 있다. 온-칩 메모리 (1403)는 캐시 (1401) 및 심도 및 컬러 버퍼 (1443)를 포함할 수도 있다. 시스템 메모리 (1405)는 지오메트리 데이터 (1409), 파라미터 버퍼 (1435), 텍스처 데이터 (1411) 및 프레임 버퍼 (1441)를 포함할 수도 있다. 지오메트리 데이터 (1409)는 하나 이상의 포인트들 (예를 들어, 정점들), 라인들 및/또는 다각형들을 나타낼 수도 있다. 지오메트리 데이터 (1409)는 장면 및/또는 장면에서의 하나 이상의 객체들을 나타낼 수도 있다.

[0166] VP (1474)는 지오메트리 데이터를 시스템 메모리 (1405)로부터 VLIW 회로 (1468) (예를 들어, 그래픽 파이프라인 (1470))으로 페치할 수도 있다. VP (1474)는 지오메트리 데이터를 VS (1476)에 제공할 수도 있다.