(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4327096号

(P4327096)

(45) 発行日 平成21年9月9日(2009.9.9)

(24) 登録日 平成21年6月19日(2009.6.19)

(51) Int.Cl.

H01L 21/60 (2006.01)

H01L 23/48 (2006.01)

F 1

H01L 21/60 321 E

H01L 23/48 P

請求項の数 17 (全 13 頁)

(21) 出願番号 特願2004-555560 (P2004-555560)

(86) (22) 出願日 平成15年11月21日 (2003.11.21)

(65) 公表番号 特表2006-507688 (P2006-507688A)

(43) 公表日 平成18年3月2日 (2006.3.2)

(86) 國際出願番号 PCT/US2003/037314

(87) 國際公開番号 WO2004/049435

(87) 國際公開日 平成16年6月10日 (2004.6.10)

審査請求日 平成17年6月29日 (2005.6.29)

(31) 優先権主張番号 10/303,523

(32) 優先日 平成14年11月22日 (2002.11.22)

(33) 優先権主張国 米国(US)

(73) 特許権者 502109876

インターナショナル レクティファイアー

コーポレーション

アメリカ合衆国 90245 カリフォルニア州

エルセグンド カンサスストリート 233

(74) 代理人 100067828

弁理士 小谷 悅司

(74) 代理人 100096150

弁理士 伊藤 孝夫

(74) 代理人 10009955

弁理士 樋口 次郎

(74) 代理人 100111453

弁理士 櫻井 智

最終頁に続く

(54) 【発明の名称】外部接続用クリップを有する半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体装置において、

第1主表面及び前記第1主表面の反対側の第2主表面を有する半導体ダイと、

前記半導体ダイの前記第1主表面に配置された制御電極及び第1主電極と、

前記半導体ダイの前記第2主表面に配置された第2主電極と、

対応する電極に電気的に接続される第1基部、及び、外部部材に電気的に接続するための第1接続部をそれぞれ有する複数の第1導電クリップと、

前記制御電極及び前記第1主電極を覆うように配された保護層と、

前記複数の第1導電クリップの各第1導電クリップの前記第1基部と各電極とを接続する導電性接着素材の層とを備え、

前記各第1導電クリップの前記第1基部は、前記保護層の開口部を通じて、前記導電性接着素材の層によって前記制御電極及び前記第1主電極にそれぞれ電気的に接続されており、

少なくとも、前記制御電極に接続される第1導電クリップの第1基部は、前記制御電極を覆うように形成される前記保護層の開口部よりも大きく形成されており、

前記第2主電極は、前記第2基部、前記第2接続部、および前記第2基部と前記第2接続部とを接続する第2延長部を有する第2導電クリップに接続され、当該第2延長部は、少なくとも前記半導体ダイの第2主表面と前記半導体ダイの前記第1主表面との間に伸びるように形成されており、

10

20

前記第1導電クリップの第1接続部および第2導電クリップの第2接続部は、ともに前記第1主表面の直下に形成されており、

前記各第1導電クリップの第1基部及び第1接続部が、前記半導体ダイの外周より外にはみ出さずに当該外周よりも内側に形成されてなることを特徴とする半導体装置。

**【請求項2】**

前記複数の第1導電クリップは、前記第1接続部と前記第1基部との間隔を空ける第1延長部をそれぞれ備えることを特徴とする請求項1に記載の半導体装置。

**【請求項3】**

各第1導電クリップの前記第1延長部は、実質的に各第1導電クリップの前記第1基部に対して垂直に伸び、

10

各第1導電クリップの前記第1接続部は、実質的に各第1導電クリップの前記第1基部に対して並行であること

を特徴とする請求項2に記載の半導体装置。

**【請求項4】**

前記半導体ダイは、MOSFETであること

を特徴とする請求項1に記載の半導体装置。

**【請求項5】**

前記制御電極に接続される前記第1導電クリップの第1基部と、前記保護層との間に接着の層が設けられており、当該第1基部と半導体ダイとの間の接続が強化されてなることを特徴とする請求項1に記載の半導体装置。

20

**【請求項6】**

前記導電性接着素材の層は、はんだから成ること

を特徴とする請求項1に記載の半導体装置。

**【請求項7】**

前記導電性接着素材は、導電性エポキシから成ること

を特徴とする請求項1に記載の半導体装置。

**【請求項8】**

前記各第1導電クリップは、前記第1基部と前記第1接続部とを繋ぐ第1延長部を備え、

、

前記第1延長部は、各第1基部及び各第1接続部と一体で形成されていること

を特徴とする請求項1に記載の半導体装置。

30

**【請求項9】**

前記第1接続部の少なくとも一つは、バンプであること

を特徴とする請求項1に記載の半導体装置。

**【請求項10】**

前記第1接続部の少なくとも一つは、平坦な接続面を有する円柱であること

を特徴とする請求項1に記載の半導体装置。

**【請求項11】**

前記第1接続部の少なくとも一つは、平坦な接続面を有する一段高い部分であること

を特徴とする請求項1に記載の半導体装置。

40

**【請求項12】**

半導体装置において、

第1主表面及び前記第1主表面の反対側の第2主表面を有する半導体ダイと、

前記半導体ダイの前記第1主表面に配置された第1主電極と、

前記半導体ダイにおける前記第1主表面と反対側の前記第2主表面に配置された第2主電極と、

前記第2主電極と電気的に接続される第2基部、外部部材に電気的に接触するための第2接続部、及び、前記第2基部と前記第2接続部を繋ぎ、前記半導体ダイの第1主表面と前記半導体ダイの第2主表面との間に伸びる第2延長部を備える第2導電クリップと、

前記第1主電極と電気的に接続される第1基部、及び、外部部材に電気的に接触するた

50

めの第1接続部とを備える第1導電クリップと、を備え、

前記第1接続部および第2接続部は、前記第1主表面の直下に形成されており、

前記第1導電クリップの第1基部及び第1接続部が、前記半導体ダイの外周より外にはみ出さずに当該外周よりも内側に形成されており、

保護層が少なくとも一つの電極に配され、

前記保護層は、前記第1導電クリップの一つの第1基部と前記電極の一つとを電気的に接続する導電層を囲んでいること

を特徴とする半導体装置。

#### 【請求項13】

前記半導体ダイは、MOSFETであること

10

を特徴とする請求項12に記載の半導体装置。

#### 【請求項14】

前記制御電極に接続される前記第1導電クリップの第1基部と、前記保護層との間に接着の層が設けられており、当該第1基部と半導体ダイとの間の接続が強化されてなることを特徴とする請求項12に記載の半導体装置。

#### 【請求項15】

前記導電層は、はんだから成ること

を特徴とする請求項12に記載の半導体装置。

#### 【請求項16】

前記導電層は、導電性エポキシから成ること

20

を特徴とする請求項12に記載の半導体装置。

#### 【請求項17】

前記第1導電クリップは、第1基部と第1接続部とを繋ぐ第1延長部を備え、

前記第1延長部は、前記第1基部及び第1接続部と一体で形成されていること、

を特徴とする請求項15に記載の半導体装置。

#### 【発明の詳細な説明】

##### 【関連特許出願】

##### 【0001】

この出願は、マーティン・スタンディング及びハイゼル・ディー・ショフィールドにより2001年3月28日に出願された米国特許出願番号09/819,774「チップスケール表面実装装置及びその製造方法」に関するものである。

30

##### 【背景技術】

##### 【0002】

本発明は、半導体装置に関し、特に外部接続用クリップを有する表面実装半導体装置に関する。

##### 【0003】

電子回路で使用する際、半導体ダイは、基板上の導電パッド等の外部部材に直接接続できる半導体装置を形成するようにパッケージ化される。電子デバイスのパッケージ化には、いくつかの機能がある。電子パッケージの機能の中でも、湿気やその他の環境要素による損傷からの半導体ダイの保護、外部部材との電気的接続、及び、半導体ダイから発生する熱の管理が最も重要である。DIPやSOICのような従来知られたパッケージには、これらの機能が備わっている。多くの場合、これらのパッケージにはリードフレーム構造が使用され、場合によってはパッケージが半導体ダイの4、5倍の大きさとなる。従って、従来の設計手法により半導体ダイのパッケージ化を行なうと、多くの場合、半導体装置が半導体ダイよりもかなり大きくなってしまう。

40

##### 【0004】

電子システムの小型化傾向により、スペースの最大限の利用が余儀なくされる。スペースを最大限に利用する一つの方法としては、装置内の部品の大きさを最小化して部品密度を高める方法がある。部品密度を高めてスペースを最大限に利用する一方で、設計の際に効率的な熱の減少や、例えば接続抵抗による寄生効果の減少などの課題にも取り組ま

50

なければならない。

【発明の開示】

【0005】

本発明に係る半導体装置は、主表面に配置された少なくとも二つの対向する主電極を有する半導体ダイを備える。各電極は、導電クリップに繋がっている。各クリップは、基板上の導電パッド等の外部部材と電気的に接続する接続部と、電極に繋がっている基部とを備える。クリップの接続部は、半導体ダイの一方側に設けられている。この構成を有効にするために、クリップの少なくとも一つには、クリップの基部を接続部に繋ぎ、ダイの主表面の間に伸びる延長部が設けられている。このクリップは、ダイの裏側の電極と外部部材との間に可能な限り最短の経路を提供し、接続そのものに起因するパッケージ内の寄生抵抗とインダクタンスとを減少させる。

10

【0006】

本発明に係る半導体装置の設置面積を減らすために、装置が基板の導電パッドに接続される場合に、クリップの接続部は、半導体ダイの下に直接配されるように向けられても良い。

【0007】

あるいは、延長部を有するクリップの接続部は、ダイの下に配置されている基板の導電パッドに広い空間を提供するために、ダイの下の領域から離れる方向に向けられても良い。

【0008】

20

本発明に係る半導体装置に使用されるクリップの形は、様々であって良い。例えば、第1の実施形態において、各クリップは、延長部によって繋がれ間隔が空けられている基部と接続部とを備える。他の実施形態では、いくつかのクリップは、平坦な基部と、平坦な基部に直接設けられた接続部とを備える。後者のクリップの接続部は、半球状、円柱状または平坦な基部から伸びた一段高い部分でも良い。

【0009】

本発明の他の特徴と利点は、図面を参照した本発明の下記の記載により明らかになる。

【発明を実施するための最良の形態】

【0010】

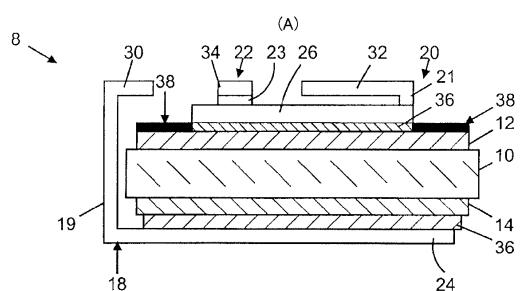

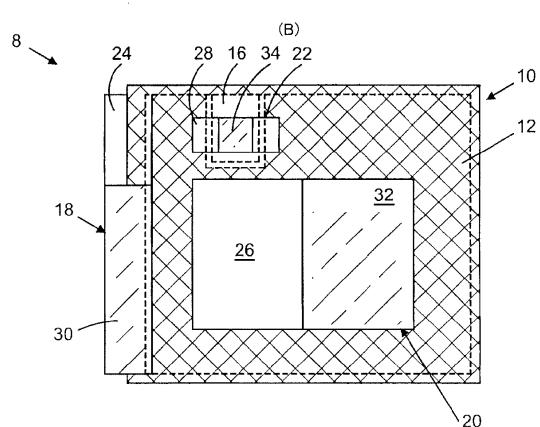

図1A及び1Bを参照すると、本発明に係る半導体装置の第1の実施形態では、半導体ダイ10を備える。好ましい実施形態に係る半導体ダイ10は、パワーMOSFETである。しかしながら、本発明は、パワーMOSFETに限られるものではない。MOSFETの代わりに、IGBTやパワー・ダイオード等の他の電子半導体ダイに適用可能である。

30

【0011】

半導体ダイ10は、互いに対向する二つの主表面を備えている。半導体ダイ10は、第1主表面に取り付けられた第1主電極12と、第2主表面に取り付けられた第2主電極14とを備える。また、半導体ダイ10は、第1主表面に取り付けられた制御電極16を備える。この制御電極16は、第1主電極12から絶縁されている。好ましい実施形態のMOSFETにおいて、制御電極16が従来のゲート電極とされる場合、第1及び第2主電極は、それぞれソースとドレインである。

40

【0012】

制御電極16は、本発明の半導体装置8が電子回路に組み込まれると、第1主電極12と第2主電極14との間を流れる電流を切り替える信号を出力する外部の制御装置から制御信号を受ける。

【0013】

第1の実施形態に係る半導体装置8は、複数のクリップ18、20、22を備える。各クリップは、基部24、26、28と接続部30、32、34とを備える。接続部30、32、34は、外部部材と電気的に接続する機能を有する。基部24、26、28は、はんだや銀を含んだエポキシのような導電性エポキシ等のダイ接着素材36の層によって、

50

それぞれ第2主電極14、第1主電極26及び制御電極16と電気的に接続する。保護層38は、クリップ20、22の基部26、28を電気的に接続させるために設けられた導電性接着素材36の部分を除いて、第1主電極12と制御電極16とを覆っている。

#### 【0014】

また、クリップ18、20、22は、それぞれ、基部24、26、28と接続部30、32、34とを繋ぐ延長部19、21、23を備えている。好ましい実施形態において、延長部19、21、23は、クリップ18、20、22の基部24、26、28の一方端部から垂直に伸びている。接続部30、32、34は、延長部19、21、23によって、間隔が空けられ、基部24、26、28に対してそれぞれ平行になるように構成されるのが好ましい。

10

#### 【0015】

接続部30、32、34は、互いに同一の平面にあり、そして、ダイの一主電極の反対側に配されるのが好ましい。この構成を可能にする本発明の新しい特徴は、半導体ダイ10の第1主表面と第2主表面との間で伸び、そして、基部24と接続部30を繋ぐ延長部19であり、これによって半導体ダイ10の第1主表面及び第2主表面の位置から伸びる電気的に接続するための経路が提供される。この構成は、基板上に半導体装置8の表面実装を可能とする。

#### 【0016】

本発明の他の特徴によると、例えば26、28のような基部は、半導体ダイ10の電極に電気的に接続するために必要な面積より広い面積を有し得る。例えば、制御電極16に電気的に接続されるクリップ22の基部28は、制御電極16に電気的に接続するために必要な面積よりも広い面積を有している。接着の層は、半導体ダイ10の上部へのクリップ22の接続をさらに強力にするように、この余分な領域の下に設けられる。

20

#### 【0017】

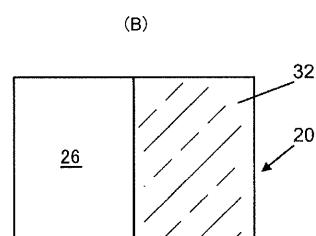

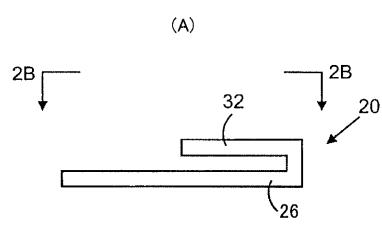

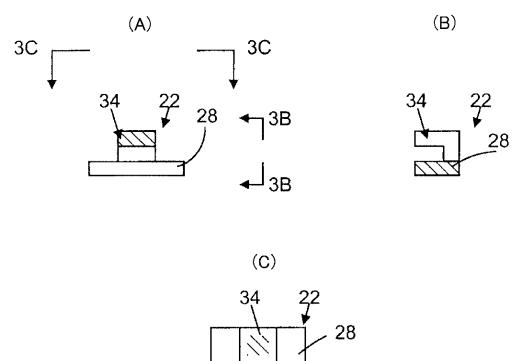

図2A、2B、3A、3B及び3Cを参照すると、第1主電極12及び制御電極16にそれぞれ取り付けられるクリップ20、22は、基部26、28の一方端部から接続部32、34の一方端部へ伸びる延長部21、23によって、接続され間隔が空けられた基部26、28と接続部32、34とをそれぞれ構成するように、銅板のような導電性の金属板を曲げることによって単体で形成される。第1実施形態におけるクリップ18は、ここで記載されている他のクリップ20、22を作る方法と同じ方法で作られても良い。

30

#### 【0018】

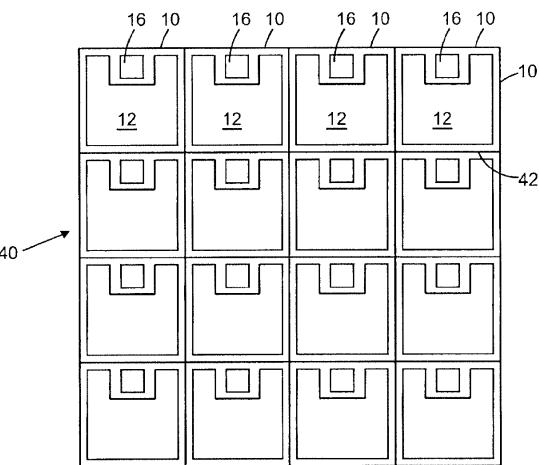

本発明に係る半導体装置は、以下の方法で製造される。図4を参照すると、まず、別個の半導体ダイ10を複数有するシリコンウエハ等の半導体ウエハ40が用意される。ウエハ40における半導体ダイ10は、同質であり、公知の方法によりシリコン基板上に形成された、MOSFETやIGBTやパワー・ダイオード等であっても良い。半導体ダイ10は、ウエハ40の一方端部から反対の端部に及ぶストリート42によって分けられる。各半導体ダイは、少なくとも第1主電極12と制御電極16とを備えている。半導体ダイ10の第2主電極14は、ウエハ8の反対側の面(不図示)に設けられている。電極12、16、14は、はんだ付けが可能であることが好ましい。

#### 【0019】

40

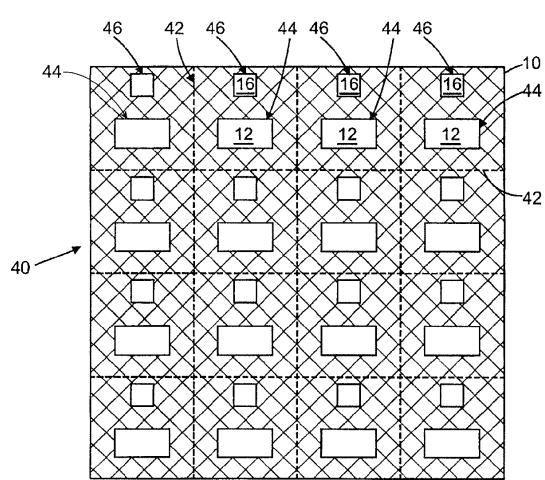

次に、図5を参照すると、第1主電極12及び制御電極16のそれぞれの上に開口部44、46を有する保護層38(図1)が形成される。保護層38は、第1主電極12と制御電極16とこれら電極の間に於ける全ての領域とを覆うウエハ40の上面全体に、ElectraEP2793として知られている材料の如き感光性エポキシの層を堆積させることで、形成される。そして、エポキシを乾燥させ、開口部44、46を形成するために取り除かれる領域が識別、分離されるように、マスクを介して紫外線があてられる。そして、識別された領域が取り除かれ、第1主電極12及び制御電極16の各部分をそれぞれ露出させる開口部44、46が形成される。そして、感光性エポキシは、例えば熱により硬化され、開口部44、46を有する保護層38(図1)が形成される。

#### 【0020】

50

開口部 44、46 は、第 1 主電極 12 及び制御電極 16 と各クリップの各基部との間ににおける良好な電気的な接続を提供するために必要な大きさであればよく、電極の全面に亘る必要はない。さらに、開口部 44、46 は、そこに接続されるクリップの基部の面積と等しい電極の面積を露出させる必要もない。加えて、本発明は、保護層 38（図 1）を作る前記方法に限られるものではなく、開口部 44、46 を持つ保護層 38（図 1）を作るための他の適当な方法を用いることができる。

#### 【 0 0 2 1 】

開口部 44、46 が形成されると、導電性接着素材 36（図 1A）が第 1 主電極 12 及び制御電極 16 の露出部分に堆積される。導電性接着素材 36（図 1A）としてはなんだや導電性エポキシを使用することができる。

10

#### 【 0 0 2 2 】

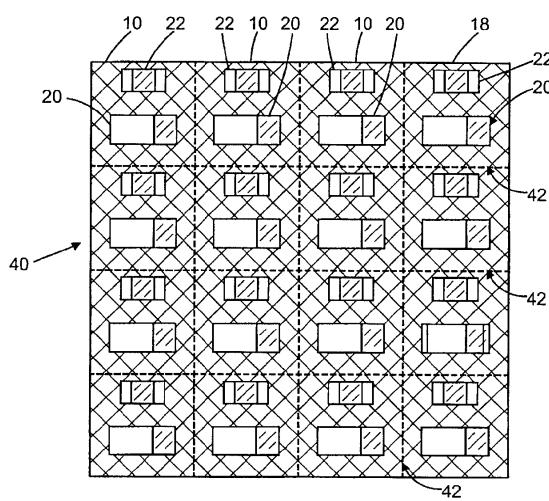

次に、図 6 を参照すると、導電クリップが電極 12、16 の露出部分に配された導電性接着素材 36 の上に据えられる。例えば、図 6 は、本発明の第 1 の実施形態による半導体装置 8 を参照して記載されたクリップ 20、22 を示しており、各クリップの各基部 26、28 は、導電性接着素材 36（図 1A）によって半導体ダイ 10 の第 1 主電極 12 及び制御電極 16 にそれぞれ接続している。導電クリップ（例えばクリップ 20、22）が配置されると、はんだが接着素材として使用される場合にはリフローされ、あるいは、導電性エポキシが導電性接着素材として使用される場合には硬化される。クリップの基部が保護層 38 の開口部 44、46 よりも大きい場合、接着の層は、クリップと半導体ダイとの間における接着の強度をより増加させるべく、開口部 44、46 の外側である基部と、保護層 38 との間に設けられる。また、液体エポキシを、ウエハの他の領域と同様にクリップの基部の少なくとも一部を覆うようにウエハの上に堆積させて、半導体ダイ 10 上における前記クリップのアセンブリの強度を改善させてもよい。その後、ウエハ 40 は、例えばストリート 42 に沿って切ることでサイの目状に切られ、第 1 主電極 12 及び制御電極 16 に接続されている少なくとも一つの導電性クリップを有する個別の半導体ダイ 10 となる。

20

#### 【 0 0 2 3 】

他のクリップ、例えば本発明の第 1 の実施形態に係る半導体装置 8（図 1A）に記載されているクリップ 18 は、はんだや導電性エポキシのような導電性接着素材 36（図 1A）によって半導体ダイ 10 の第 2 主電極 14 に電気的に接続される。これは、個別のダイ 10 をピックアップし、クリップ 18 の基部 24 に第 2 主電極 14 を配置し、はんだや導電性エポキシのような導電性接着素材 36（図 1A）の層に電気的に接続することで達成され得る。再び、はんだが使用された場合にはリフローされ、導電性エポキシが使用された場合には硬化される。

30

#### 【 0 0 2 4 】

代わりに、保護層に開口部が形成された後に、まず、切断してダイに個別化し、その後、クリップが導電性接着素材を使用することによって各ダイの電極に取り付けられる。

#### 【 0 0 2 5 】

クリップ 18、20、22 は、従来のパッケージで使用される銅のストラップやブリッジと同様のフォーマットを有する銅マトリックスリードフレームから切り分けられる。クリップ 18、20、22 は、従来のダイボンディング装置に見られるようなブリッジパンチ及び設置型を使用して適切な位置に配置される。好ましい方法においては、ダイ 10 は、クリップ 18 に配置され、適当な導電性接着素材によりその基部 24 に接続される。導電性接着素材は、リフロー又は硬化され、その後、クリップ 18 は、半導体装置 8 を得るためにストラップからトリムされる。

40

#### 【 0 0 2 6 】

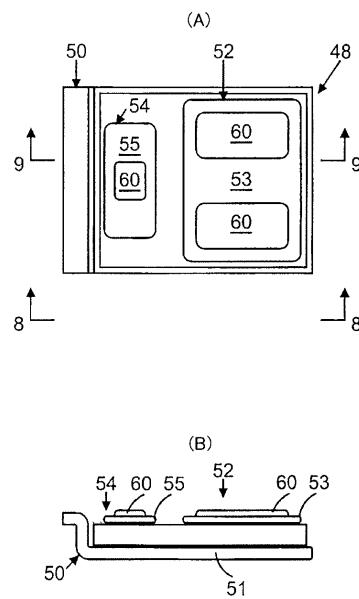

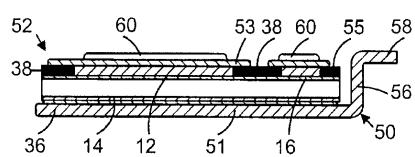

本発明の半導体装置は、様々な形態のクリップを備えるための上記方法により製造される。類似の番号が類似の特徴を結び付ける図 7、8 を参照すると、本発明の第 2 の実施形態に係る半導体装置 48 は、電極に接続されたクリップ 50、52、54 を有する半導体ダイ 10 を備えている。類似の番号が類似の特徴を結び付ける図 9 を参照すると、クリッ

50

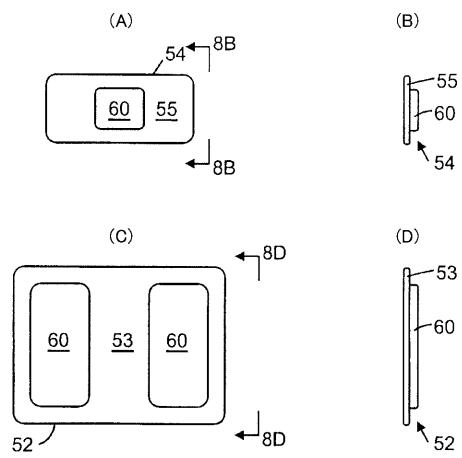

50、52、54は、基部51、53、55をそれぞれ備えている。導電性接着素材36により第2主電極14に接続されるクリップ50は、基部51と接続部58を繋ぐ延長部56を備えている。延長部56は、クリップ50の基部51及び接続部58と一体で形成されている。また、注目すべきは、延長部56が半導体ダイ10における主表面の間に伸びていることである。

#### 【0027】

クリップ52の基部53は、その表面に複数の接続部60が配されている。また、基部55の表面にも接続部60が配されている。接続部60は、各基部53、55のオープンな表面から拡張した一段高い部分である。クリップ52、54の基部53、55は、保護層38の開口部に堆積している導電性接着素材36の層によって、第1主電極12及び制御電極16にそれぞれ電気的に接続されている。クリップ51は、好ましくは、銅から形成され、銀でメッキされる。クリップ50の基部51は、ダイより少し広い面積を有しており、この二つが接着された場合にダイの端部の周囲にフレームが形成される。余分な領域は、接着素材の厚みを増加させ、ダイの端部の周囲にフィレットになる。これは、効果的に、接着素材を制御し、ダイの端から流れるのを防止する。

#### 【0028】

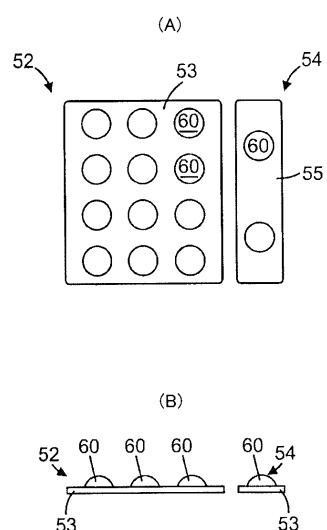

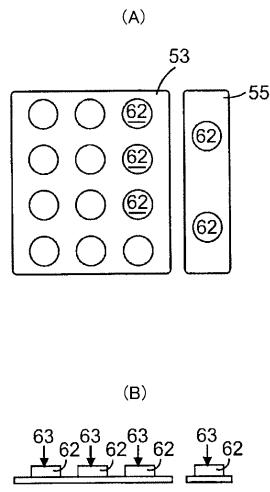

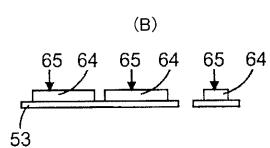

実際に、本発明の様々な実施形態は、クリップの他の形状を使用して、記載された方法により製造することができる。例えば、図10A、10B、11A、11B、12A及び12Bを参照すると、使用されるクリップは、図10A、10Bに示す第2の実施形態で用いられている半球型の接続部60の代わりに、図11A、11Bに示すように平坦な接続面63を有する円柱状の接続部62など様々であってよい。もしくは、接続部60は、図12A、12Bに示すように平坦な接続面65を有する複数の一段高い部分64に代えても良い。

#### 【0029】

ダイの電極に接続されるクリップ52、54における基部53、55の側部は、平坦か少し盛り上がっている。盛り上がった側部は、クリップ50の基部51にある余分な領域と同じように接着素材の流れを制御するのに役立つ。クリップ52、53もまた銅により形成され、銀で仕上げられる。

#### 【0030】

本発明の第2の実施形態は、まず、保護層及び開口部が形成された後にウエハからダイを単体化することで製造される。単体化された各ダイは、銀エポキシなどの適当な導電性接着素材によってクリップ50の基部51に取り付けられる。そして、クリップ52、53は、同じ接着素材又は適当なはんだを用いて取り付けられる。クリップ50は、第2の実施形態に係る半導体装置のリードフレームのベースとして作用する。参照される製造方法によれば、クリップ50が高密度マトリックスの形態をとる一方で、クリップ52、53は、プリッジパンチアセンブリを使用して関連する電極に接着される。

#### 【0031】

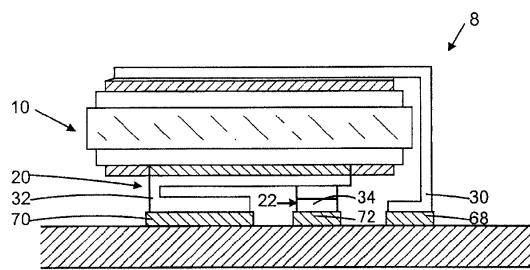

図13を参照すると、半導体装置8が基板66上に表面実装されている状態が示されている。特に、接続部30、32、34は、半導体装置8の電極を電子回路(不図示)内の適当な場所に接続する導電パッド68、70、72と電気的に接続している。

#### 【0032】

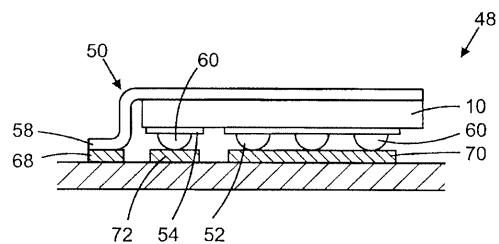

図14を参照すると、第2の実施形態による半導体装置48は、基板66上に表面実装されている。半導体装置8のように、半導体装置48は、クリップ50、52、54の接続部58、60とそれぞれ接続する導電パッド68、70、72を介して電子回路に接続されている表面実装装置である。この構成から、本発明に係る半導体装置8、48が基板に実装された場合、熱は、クリップ18、50の基部24、51を伝わって半導体ダイ10の第2主電極14から放射される。

#### 【0033】

注目すべきは、半導体装置8の接続部30(図13)は、他のクリップ20、22が接続されている半導体ダイ10の主表面の下に該接続部30が位置するような方向に伸びて

10

20

30

40

50

いる。この構成には、半導体装置の設置面積を減らすという追加の利点がある。他方、半導体装置 4 8 の接続部 5 8 (図 1 4) は、他のクリップが取り付けられている半導体ダイ 1 0 の主表面の下の領域から離れた方向へ伸びている。この構成では、半導体装置 4 8 の設置面積が増えることになるけれども、半導体ダイ 1 0 の導電パッド 7 0 、 7 2 のための領域を広くすることができる。また、ダイの第 2 主電極がそれぞれのクリップに取り付けられた場合に、正確なアライメントの必要がないため、製造を単純化することができる。

#### 【 0 0 3 4 】

本発明に係る半導体装置におけるダイの設置面積に対する割合は、90%である。本発明に係る装置の熱放射が改善すると、より高い温度下でも装置を動作させることができるようになる。本発明に係る装置に使われるダイは、0.100 mmまで薄く、従来のパッケージで使用されるダイよりもはるかに薄い。本発明に係る装置は、様々な設置面積で使用できる。また、本発明に係る装置は、装置が組立てられた場合に、様々な基板の間の温度的なミスマッチによるストレスを吸収することができる。これらの特徴により、本発明に係る装置は、従来の装置よりもより厳しい状況で動作し、過酷な状態で使用することができる。

#### 【 0 0 3 5 】

本発明に係る半導体装置を考案するのに様々な形態のクリップが使用されることとは、当業者には明らかであり、従って、ここで示される装置が本発明の範囲を制限することはない。従って、本発明は、特定の実施形態との関係により記載されているが、他の多くの種類や変更、他の使用方法も当業者にとっては明らかである。よって、本発明がこの特定の開示のみに限定されるのではなく、請求項によってのみ定められる。

#### 【 図面の簡単な説明 】

#### 【 0 0 3 6 】

【図 1】図 1 A は、本発明の第 1 の実施形態に係る半導体装置の側面図である。図 1 B は、図 1 A に示す装置の平面図である。

【図 2】図 2 A は、図 1 A に示す装置に使用されるクリップの側面図である。図 2 B は、2 B - 2 B 矢印の方向から見た図 2 A に示すクリップの図である。

【図 3】図 3 A は、図 1 A に示す装置に使用されるクリップの側面図である。図 3 B は、3 B - 3 B 矢印の方向から見た図 3 A に示すクリップの図である。図 3 C は、3 C - 3 C 矢印の方向から見た図 3 A に示すクリップの図である。

【図 4】図 4 は、従来技術に係る、複数の半導体ダイが形成された半導体ウエハを示す図である。

【図 5】図 5 は、半導体ダイの電極部分を露出させる開口部を備える保護層を有する図 4 のウエハを示す図である。

【図 6】図 6 は、半導体ダイの電極部分に取り付けられたクリップを備える図 5 のウエハを示す図である。

【図 7】図 7 A は、本発明の第 2 の実施形態に係る半導体装置の平面図である。図 7 B は、8 - 8 矢印の方向から見た図 7 に示す装置の側面図である。

【図 8】図 8 A 及び 8 B は、それぞれ、本発明の第 2 の実施形態で使用されるクリップの、平面図及び図 8 A の 8 B - 8 B 矢印の方向から見た側面図である。図 8 C 及び 8 D は、それぞれ、本発明の第 2 の実施形態で使用されるクリップの、平面図及び図 8 C の 8 D - 8 D 矢印の方向から見た側面図である。

【図 9】図 9 は、9 - 9 線の方向から見た図 7 に示す装置の縦断面図である。

【図 10】図 10 A 及び 10 B は、それぞれ、本発明の第 2 の実施形態で使用されるクリップの、平面図及び側面図である。

【図 11】図 11 A 及び 11 B は、それぞれ、本発明の第 2 の実施形態で使用可能なクリップの他の例を示す、平面図及び側面図である。

【図 12】図 12 A 及び 12 B は、それぞれ、本発明の第 2 の実施形態で使用可能なクリップの他の例を示す、平面図及び側面図である。

【図 13】図 13 は、基板に取り付けた第 1 の実施形態の半導体装置を示す図である。

10

20

30

40

50

【図14】図14は、基板に取り付けた第2の実施形態の半導体装置を示す図である。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

---

フロントページの続き

(72)発明者 マーティン スタンディング

イギリス国 ケント州 ティエヌ9 1エックスディ トンブリッジ バーデン パーク ロード

19

審査官 市川 篤

(56)参考文献 特開2000-243887(JP,A)

特開平01-161707(JP,A)

特開平02-146757(JP,A)

特開2000-223634(JP,A)

特開昭63-281451(JP,A)

特開2002-076195(JP,A)

特公昭57-039047(JP,B1)

特開平04-159704(JP,A)

特開2002-170916(JP,A)

特開平11-354702(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/60

H01L 23/48