(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

29 May 2008 (29.05.2008)

PCT

(10) International Publication Number

WO 2008/063320 A2(51) International Patent Classification:

G08B 21/00 (2006.01)

(74) Agents: BOLAND, Kevin, J. et al.; W.L. Gore &amp; Associates, Inc., 551 Paper Mill Road, P.O. Box 9206, Newark, DE 19714-9206 (US).

(21) International Application Number:

PCT/US2007/021881

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(22) International Filing Date: 11 October 2007 (11.10.2007)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

11/592,766 3 November 2006 (03.11.2006) US

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, MT, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

(71) Applicant (for all designated States except US): GORE ENTERPRISE HOLDINGS, INC. [US/US]; 551 Paper Mill Road, P.O. Box 9206, Newark, DE 19714-9206 (US).

(72) Inventors; and

(75) Inventors/Applicants (for US only): HUNTER, Steve, B. [GB/GB]; 12 Gameskeeper Road, Kinesswood, Kinross KY13 9JR (GB). VOLTZ, John, A. [US/US]; 408 Uxbridge Way, Hockessin, DE 19707 (US). LEWIS, Brent, W. [US/US]; 305 East Harvest Lane, Middletown, DE 19709 (US). WYLIE, Harold, S. [US/US]; 73 Arbutus Street, Elkton, MD 21921 (US).

## Published:

— without international search report and to be republished upon receipt of that report

(54) Title: TAMPER RESPONDENT SENSOR AND ENCLOSURE

(57) Abstract: A tamper respondent enclosure including (a) a circuit board; (b) an enclosure surrounding the circuit board; (c) a tamper respondent sensor having (i) a substrate with first and second sides; (ii) a first layer of conductive traces on the first side; (d) wherein the tamper respondent sensor is wrapped around the enclosure with at least one overlap region; and (e) wherein only at the at least one overlap region the tamper respondent sensor has a second layer of conductive traces on the second side. Preferably, the substrate is insulating and made of opaque PET, and the first layer is adjacent the enclosure.

WO 2008/063320 A2

## TAMPER RESPONDENT SENSOR AND ENCLOSURE

## FIELD OF THE INVENTION

5 This invention relates to tamper respondent enclosures, and in particular, to a sensor used as a tamper respondent enclosure.

## BACKGROUND OF THE INVENTION

10 Tamper respondent enclosures are used in various applications, including the transport of sensitive information and protecting electronic devices. Typical enclosures are in the form of envelopes and shallow boxes, the walls of which are formed by folding flexible sheets incorporating tamper detection features. As used herein, sheets 15 incorporating tamper detection features are known as "sensors". These sheets may also be wrapped around preexisting boxes or enclosures.

Included in such sheets are layers of flexible material and a matrix of diagonally extending or zig-zag pattern semi-conductive or conductive lines, also known as conductive traces. The lines or traces are printed 20 on thin insulating film. The matrix of lines forms a continuous conductor which is broken if attempts are made to penetrate the film. The sensor matrix is monitored and when a tamper occurs the electrical state of the sensor changes. A detection of a change in state can initiate a signal. This signal can erase information stored within the enclosure, or 25 otherwise protect the information from being discovered.

In known devices, the matrix of semi-conductive or conductive lines or traces on the insulating film is printed on both sides of the film. The lines on one side are disposed in the sections of the film opposite from 30 where the lines are disposed on the opposite side. In this manner, complete coverage of the film is obtained, and it is more difficult to penetrate the film without cutting a line, either on one side of the film or the other.

Typically, the flexible material is a clear insulating film such as 35 PET. In order to further protect and obfuscate the location of the lines of the semi-conductive lines, thereby making it more difficult to circumvent them in an attempt to break through the film to get to the information, known methods include a potting material. This potting material is typically a dark resin that encapsulates the entire film. The dark potting

material provides a mechanical barrier and hides the location of the semi-conductive lines.

5        Although these devices are effective, they are difficult to manufacture. A construction that leads to a more efficient assembly is desired.

## SUMMARY OF THE INVENTION

10       The present invention provides a tamper respondent enclosure including (a) a circuit board; (b) an enclosure surrounding the circuit board; (c) a tamper respondent sensor having (i) a substrate with first and second sides; (ii) a first layer of conductive traces on the first side; (d) wherein the tamper respondent sensor is wrapped around the enclosure with at least one overlap region; and (e) wherein only at the at 15       least one overlap region the tamper respondent sensor has a second layer of conductive traces on the second side. Preferably, the substrate is insulating and made of an opaque film such as PET, and the first layer is adjacent the enclosure.

20       In alternative embodiments, the substrate and enclosure further include an opening for communication between the circuit board and an external device. In exemplary embodiments, the external device is a computer mother board, a connector, and a cable. The circuit board in an alternative embodiment includes a wireless transmitter.

25       In preferred embodiments, the tamper respondent sensor is shaped to allow only two layers at the at least one overlap region, and the second side of said substrate has no exposed conductive traces. Also in a preferred embodiment, the substrate further includes an adhesive disposed over the first layer of conductive traces. The adhesive is preferably a pressure sensitive adhesive (PSA).

30       In another aspect, the present invention provides a tamper respondent sensor including (a) a substrate having a first side and a second side, the substrate adapted to be folded to produce an overlapping portion of the first side with an overlapping portion of the second side; (b) a first layer of conductive traces on the first side; (c) a second layer of conductive traces only at the overlapping portion of the second side, (d) the second side having a region free of conductive traces, (e) the second layer of conductive traces being electrically connected to the first layer of conductive traces. Preferably, the traces

are in an unpredictable pattern. The tamper respondent sensor preferably further includes an input/output (I/O) lead.

5

## DESCRIPTION OF THE DRAWINGS

Figure 1 is a schematic side sectional view of a prior art sensor.

Figure 2A is a schematic side sectional view of a sensor according to an exemplary embodiment of the present invention.

10 Figure 2B is a schematic side sectional view of a sensor according to an exemplary embodiment of the present invention.

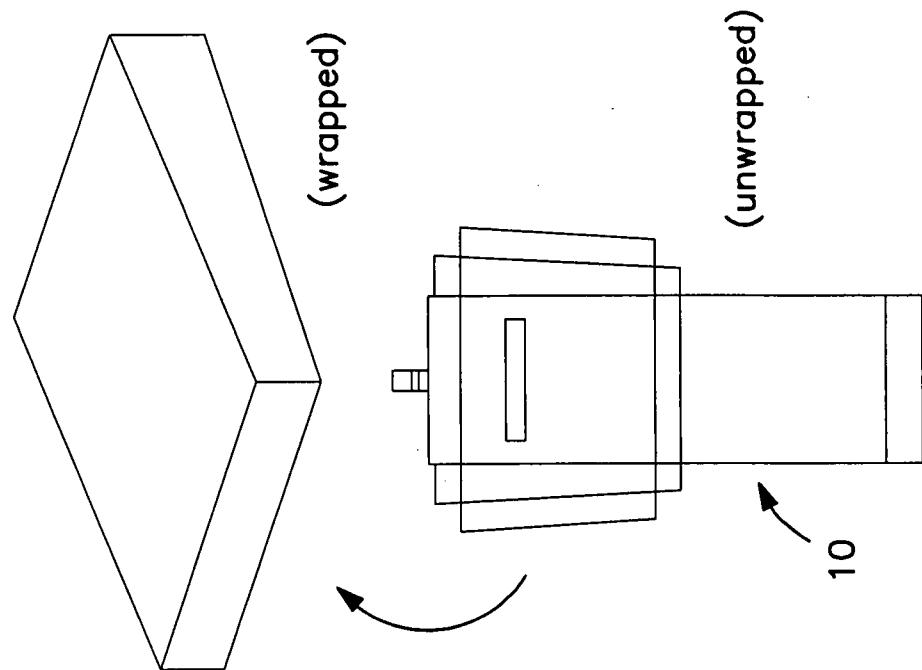

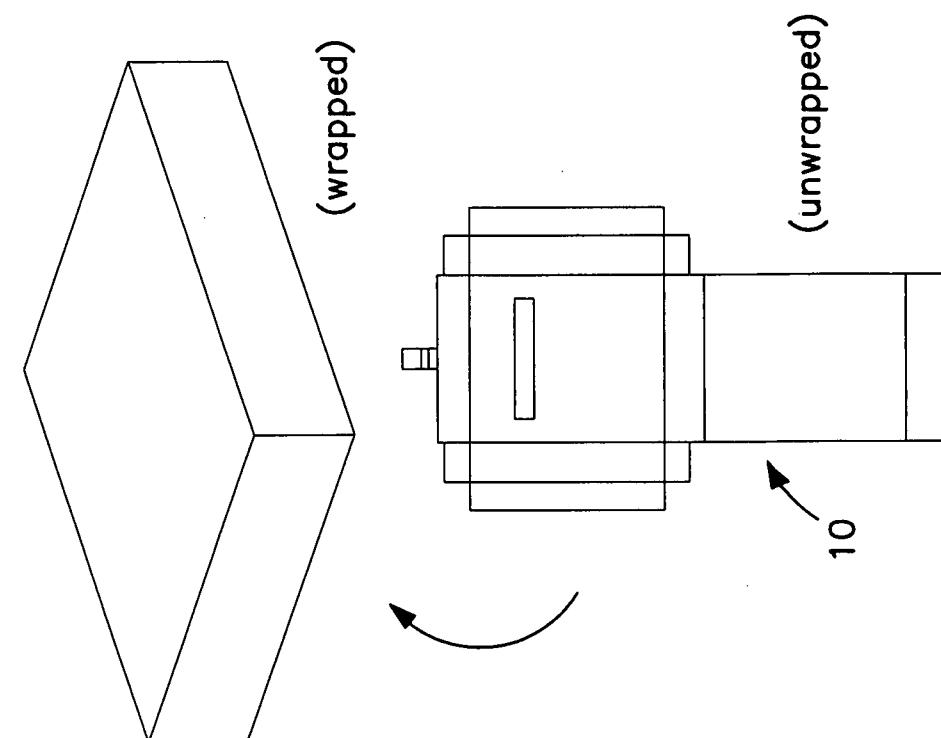

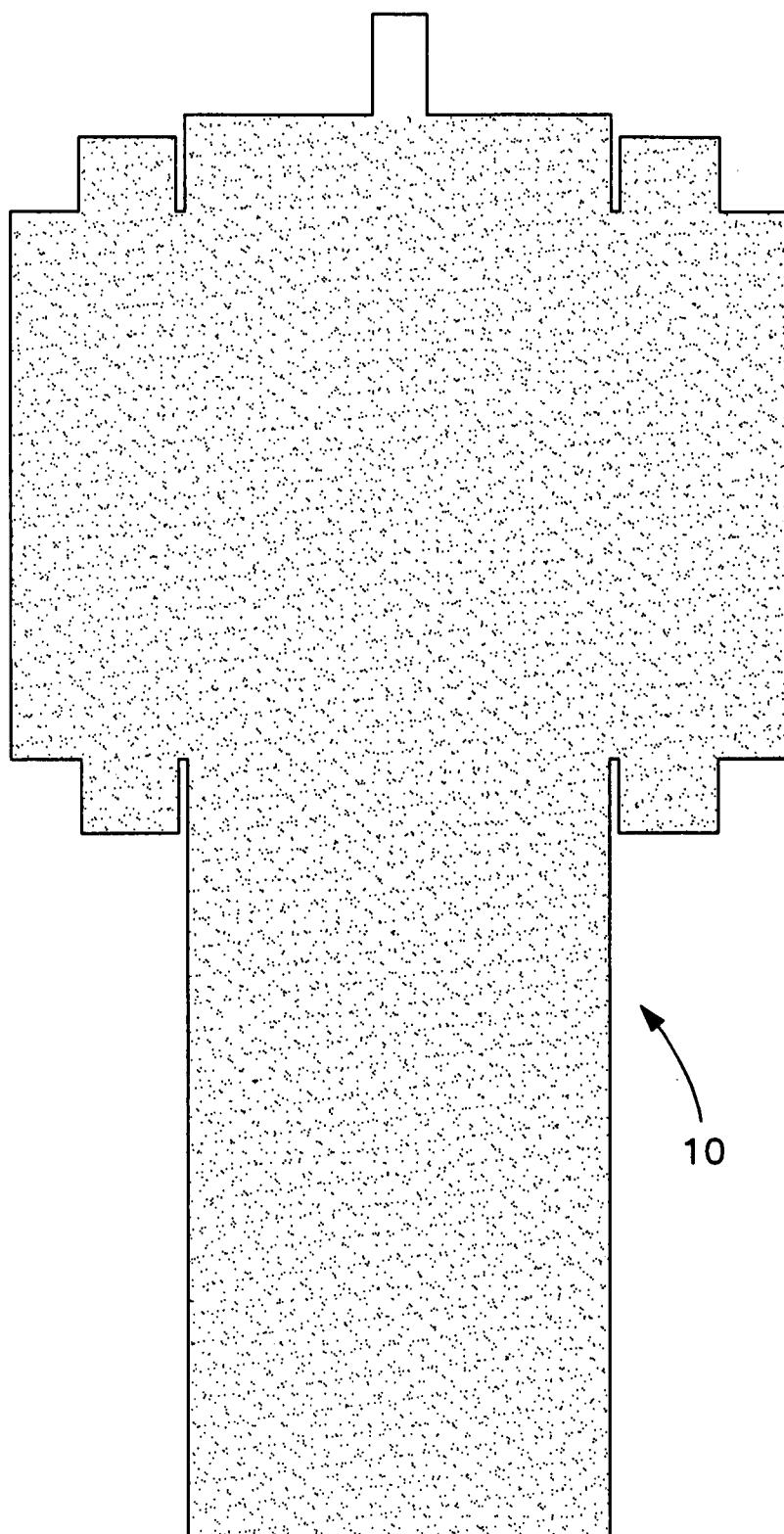

Figure 3A is a schematic showing an exemplary sensor according to the present invention in an unwrapped and a wrapped state.

Figure 3B is a schematic showing an exemplary sensor of the present invention in an unwrapped and a wrapped state.

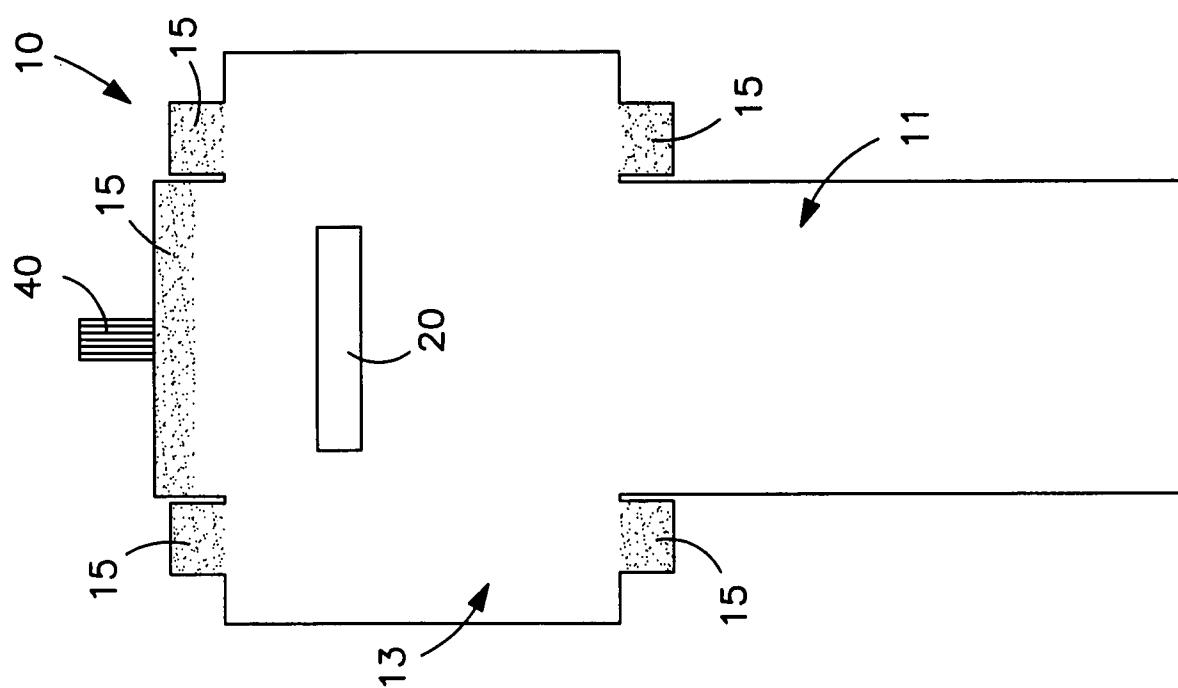

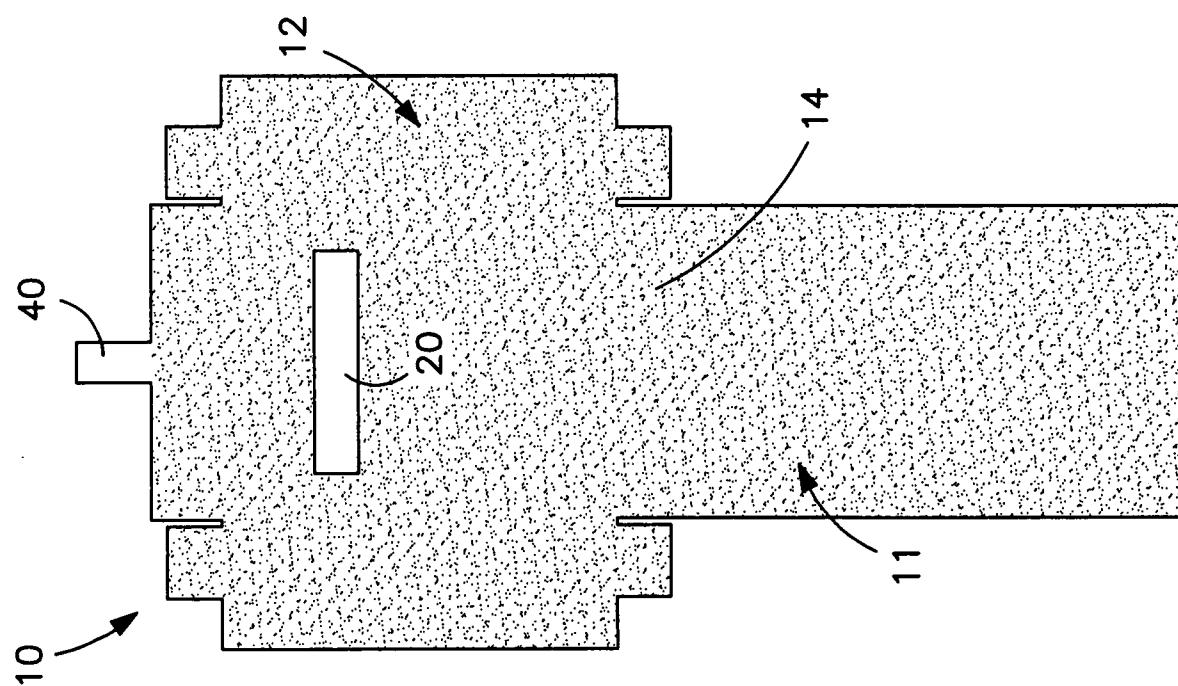

15 Figure 4A is a bottom view of an exemplary sensor according to the present invention.

Figure 4B is a top view of an exemplary sensor according to the present invention.

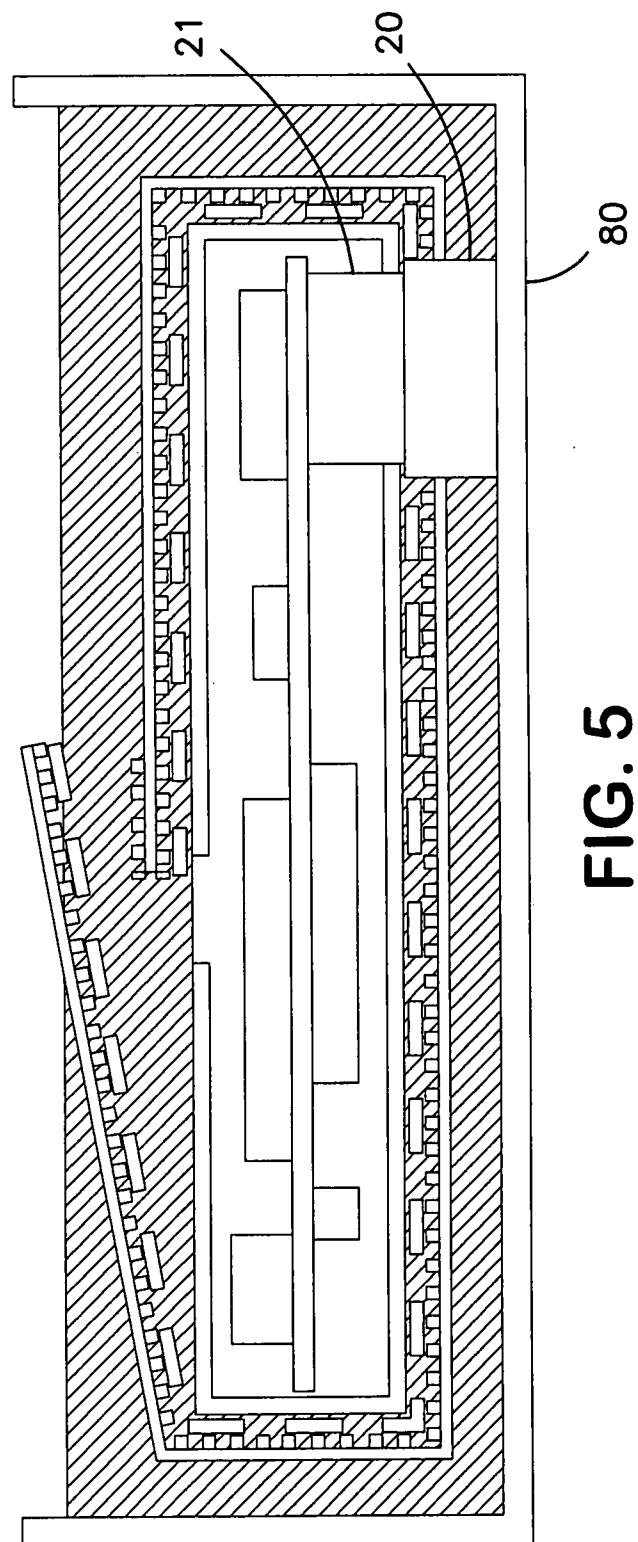

20 Figure 5 is a schematic side sectional view of a sensor according to an exemplary embodiment of the present invention.

Figure 6 is a top view of an exemplary sensor according to the present invention.

25

## DETAILED DESCRIPTION OF THE INVENTION

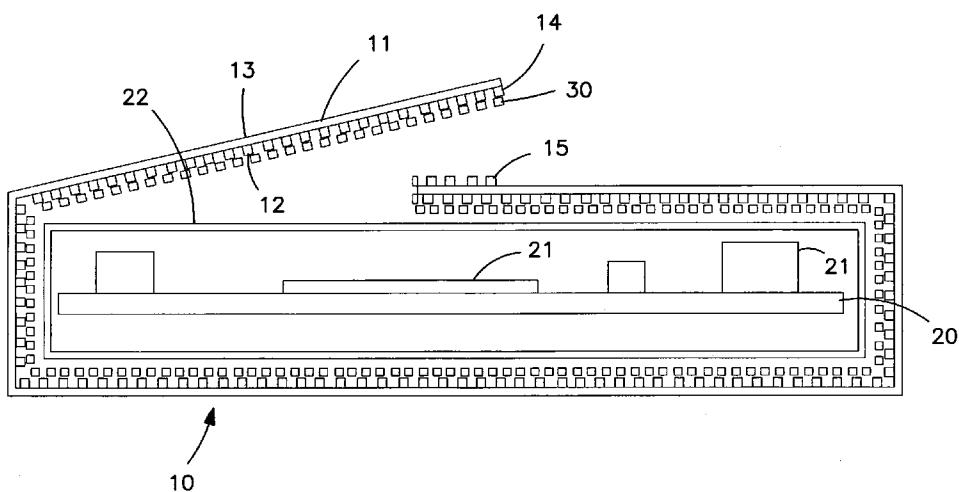

Figure 1 is a schematic diagram of a prior art tamper respondent enclosure. Circuit board 100 has components 101 disposed thereon. Components 101 contain the sensitive information that is desired to be 30 protected. A box or enclosure 102 surrounds circuit board 100 and components 101. Enclosure 102 has a sensor 103 disposed around it. Sensor 103 comprises a clear PET substrate 104. On both sides of PET substrate 104 are disposed printed traces 105. This is a matrix of conductive lines on each side. The lines are disposed in offsetting 35 relation from one side to the other to ensure complete coverage of PET substrate 104. The inside of PET substrate 104 also has a layer of adhesive 106 disposed over the printed trace 105 on that surface. Adhesive layer 106 is a pressure sensitive adhesive (PSA). In this prior

art device, the entire sensor is then encapsulated in an opaque encapsulant or potting material 107. Potting material 107 helps obfuscate printed traces 105. An outer shell 108 surrounds the device. A cable 109 is used to connect components 101 with exterior components 110. Although the top section of sensor 103 is shown to be open, this is for illustration purposes only. In use, the overlapping ends of sensor 103 are secured to one another by adhesive layer 106.

5 Although this device is effective, it is difficult to manufacture. It includes the deposition of printed traces on two sides of the PET substrate and it also includes the potting layer 107.

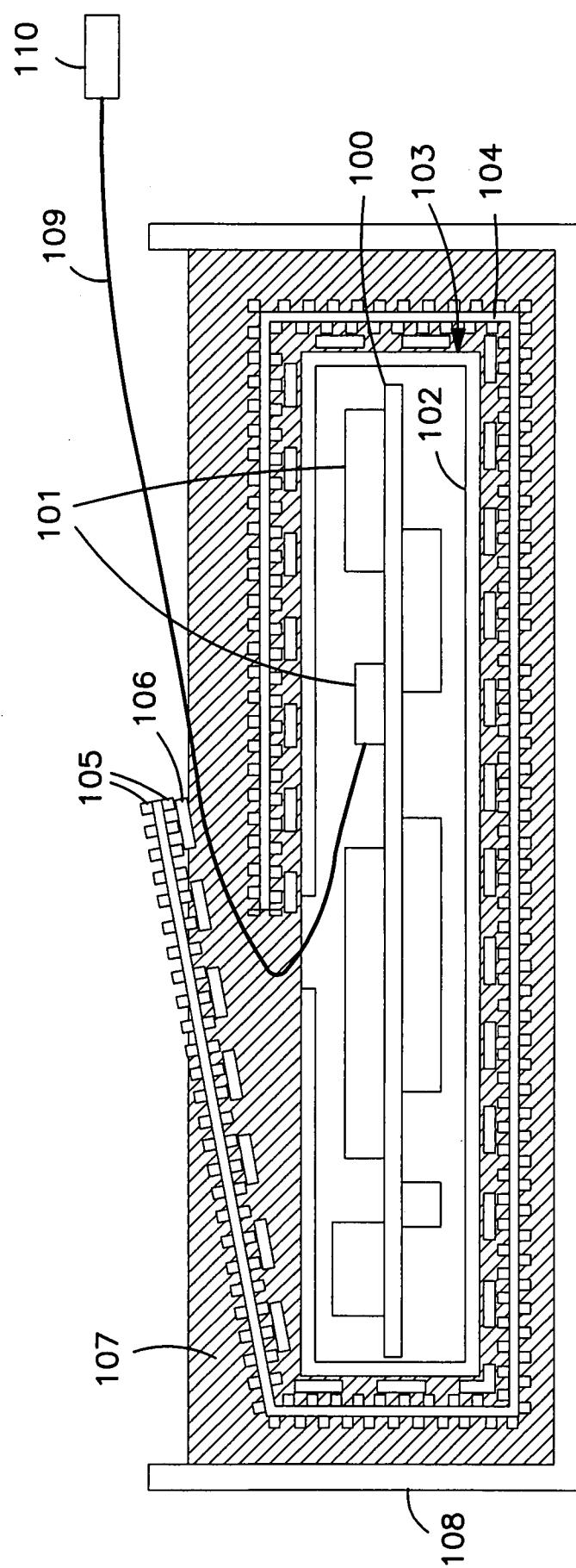

10 Figure 2A is a schematic representation of an exemplary embodiment of the present invention. As shown in Figure 2, a circuit board 20 has components 21 disposed thereon. Components 21 contain sensitive information to be protected. In alternative 15 embodiments, circuit board 20 can include wireless transmitters as components 21. Circuit board 20 and components 21 are enclosed by a box or enclosure 22. Enclosure 22 may be any shape. A rectangular shape is shown in this embodiment, but it may also be trapezoidal, wedge-shaped, or any other shape. Enclosure 22 is encapsulated by 20 tamper respondent sensor 10. In alternative embodiments, tamper respondent sensor 10 may be wrapped around a circuit board without a preexisting box or enclosure, in which case a filler may be used to form a surface over the circuit board to which tamper respondent sensor 10 adheres.

25 Tamper respondent sensor 10 includes a substrate 11. Preferably, substrate 11 an insulating material such as PET. According to this invention, substrate 11 is opaque. By using an opaque PET for substrate 11, it is not necessary to subsequently pot the material in order to obfuscate the printed traces.

30 Substrate 11 has a first side 12 and second side 13. First side 12 is the inside of the substrate as illustrated in Figure 2A. Disposed on this first side 12 is a first layer of conductive traces 14. Preferably, the conductive traces are made of a conductive, non-metallic ink, such as carbon-loaded polymer resin as taught, for example, in U.S. Patent No. 35 5,539,379. Other materials known in the art may be used for the traces.

Substrate 11 is adapted to be folded to produce an overlapping portion of first side 12 with an overlapping portion of second side 13. On second side 13, which is the outer side of substrate 11 in the illustrated

embodiment, a second layer of conductive traces 15 is disposed. Second layer of conductive traces 15 is present, however, only at the overlapping portion of second side 13. That is, second layer of conductive traces 15 is only disposed on that portion of second side 13 where there is an overlap with first side 12. The remainder of second side 13 is a region free of conductive traces. Thus, there are no exposed traces on second side 13.

The traces on second side 13 are electrically connected to the traces on first side 12, for example by a via. Preferably, the vias are located at the overlapping portion. A monitor (not shown) detects the circuit completed by first layer of conductive traces 14 and second layer of conductive traces 15 and monitors the electrical state. If this electrical state changes, indicating that the circuit has been broken, for example by cutting one of the traces, the monitor can trigger a response such as erasing information stored in components 21.

As shown in Figure 2A, the overlap region is open for purposes of illustration. In use, the overlap is mated such that second layer of conductive traces 15 is adhered to first layer of conductive traces 14 by an adhesive layer 30. Adhesive layer 30 is preferably a tackifier, such as a PSA. Adhesive layer 30 is disposed on first side 12 of substrate 11 on the first layer of conductive traces 14. In this manner, once mated, if someone tries to tamper with sensor 10, by lifting substrate 11 at the overlap, adhesive layer 30 will sever either first layer of conductive traces 14 or second layer of conductive traces 15, thereby causing an interruption in the signal and triggering erasure or other protection of information stored in components 21 as described above. There may be one or a plurality of overlap regions of sensor 10 in final use. Preferably there are only two layers of substrate 11 at each overlap region.

As shown in Fig. 2B, a cable 71 is used to connect components inside the device to components outside the device.

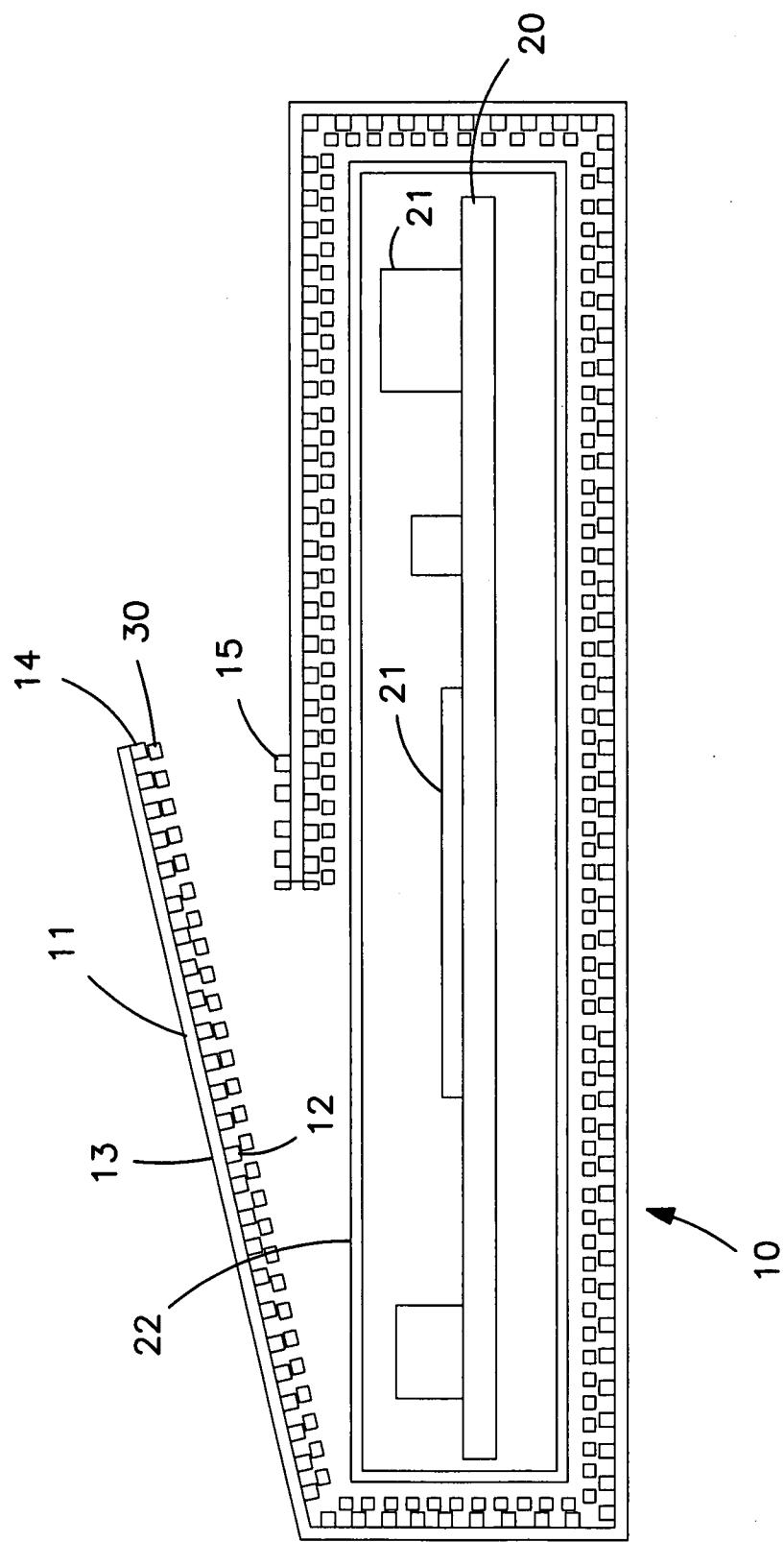

Figure 3A and Figure 3B show alternative embodiments of the present invention. The embodiments represents a sensor 10 for use in wrapping an enclosure of a rectangular shape (Figure 3A) and a wedge shape (Figure 3B). The portion of Figures 3A and 3B labeled "unwrapped" shows sensor 10 in its intermediate form. Once an enclosure is placed on sensor 10, sensor 10 is then wrapped around the enclosure to completely encapsulate it, as illustrated in the portion of the figures labeled "wrapped."

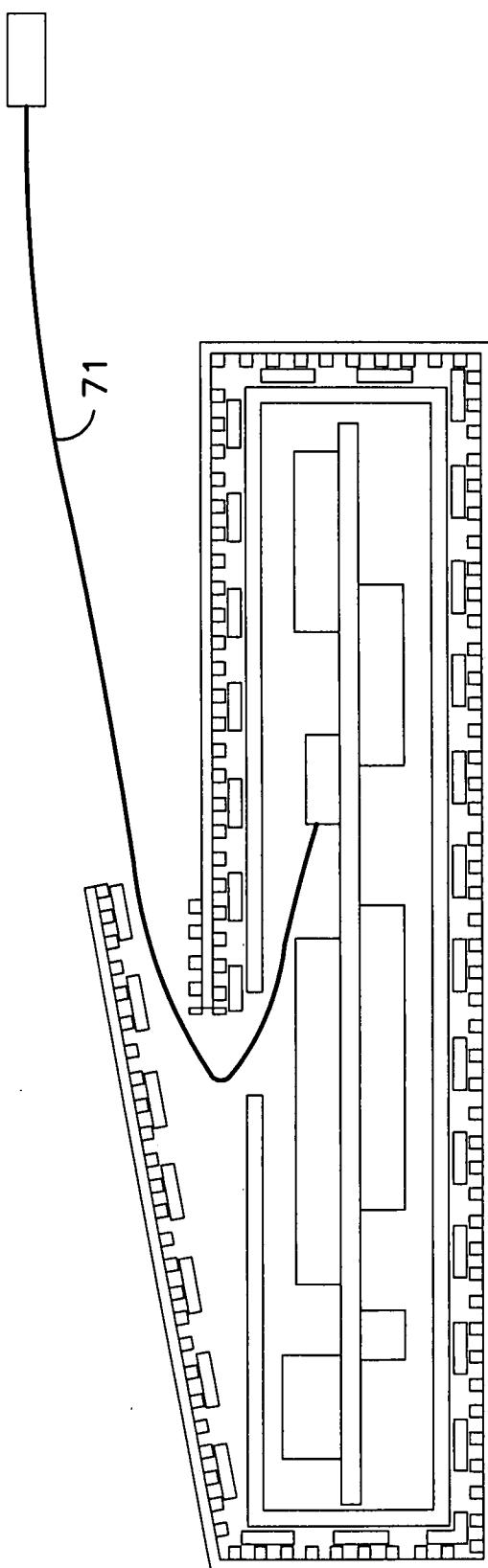

5       Figure 4A is a bottom view of an exemplary sensor 10 according to the present invention. Figure 4B is a top view of sensor 10. As shown in Figures 4A and 4B, sensor 10 includes substrate 11. In the present invention, substrate 11 is an opaque film such as PET. First side 12 of substrate 11 has first layer of conductive traces 14 disposed thereon.

10      In a preferred embodiment of the present invention, traces 14 are disposed in an unpredictable pattern on substrate 11. This is in contrast to diagonal (zig-zag), straight, or sinusoidal wave trace lines known in the art. Because these known patterns repeat at regular intervals, it potentially makes the sensor vulnerable to a jumper attack wherein the attacker can locate two points of the same trace and bypass the trace with a conductive jumper. Potentially, the attacker can then penetrate the sensor without triggering a change in electrical state. By using an unpredictable pattern, it is more difficult to break into sensor 10 because 15 it is difficult to follow a single conductive trace and bypass it with a jumper. In order to make the unpredictable pattern, the trace herein is manually drawn using computer-aided software packages such as PCB-PADS®, from Mentor Graphics, a printed circuit board layout software program.

20      As shown in Figure 4A, a second layer of conductive traces 15 is disposed on the portions of second side 13 of substrate 11 that will overlap with first side 12 as described above. The remainder of second side 13 is a region free of conductive traces. Thus, there are no exposed traces on second side 13 once it is wrapped around an 25 enclosure.

Also shown in Figures 4A and 4B is an opening 20 in sensor 10 which is preferably included in sensor 10 to allow mating of a circuit board 20 with another device external to sensor 10. The external device can be a computer mother board, a connector, or a cable, for example. 30 Fig. 5 illustrates an exemplary embodiment wherein opening 20 allows mating of component 21 to a connector 80. Also shown in Figures 4A and 4B is an I/O lead 40 extending from substrate 11. Fig. 6 is a top view of exemplary sensor 10 without opening 20. This sensor 10 of Fig. 6 would be connected using a cable through the overlap zone as shown 35 in Fig. 2B.

The present invention provides distinctive advantages over the known art. Specifically, employing an unpredictable pattern for the traces makes it more difficult to defeat the device. In addition, using an

opaque PET for substrate 11 obviates the need to pot the sensor. This eliminates a processing step, making production more efficient and cost effective. It also provides natural obfuscation for the conductive traces which may render the use of a second layer of conductive traces over 5 the entire second side 13 of substrate 11 unnecessary. This also eliminates processing steps increasing efficiency and reducing costs. By selectively putting the second layer of conductive traces 15 only at portions of the second side 13 where substrate 11 overlaps, an effective tamper respondent enclosure is produced.

10 In the illustrated embodiments, relatively small overlapping portions are depicted. In alternative embodiments, larger overlapping portions are used, for example covering an entire side of box 22 or furthermore all sides of a box.

15 While particular embodiments of the present invention have been illustrated and described herein, the present invention should not be limited to such illustrations and descriptions. It should be apparent that changes and modifications may be incorporated and embodied as part of the present invention within the scope of the following claims.

The invention claimed is:

1. An article comprising:

- (a) a circuit board;

- (b) a tamper respondent sensor having

- 5 (i) a substrate with first and second sides;

- (ii) a first layer of conductive traces on said first side;

- (c) wherein said tamper respondent sensor is wrapped around said circuit board with at least one overlap region;

- 10 (d) wherein only at said at least one overlap region said tamper respondent sensor has a second layer of conductive traces on said second side.

2. An article as defined in claim 1, wherein said substrate is an opaque insulating film.

- 15 3. An article as defined in claim 1, wherein said substrate is PET.

4. An article as defined in claim 1, wherein said first layer is adjacent the circuit board.

5. An article as defined in claim 1, wherein said substrate and said 20 enclosure further comprises an opening for communication between said circuit board and an external device.

6. An article as defined in claim 5, wherein said external device is a printed circuit board.

7. An article as defined in claim 5, further comprising a connector 25 attached to said circuit board and disposed in said opening.

8. An article as defined in claim 5, further comprising a cable attached to said circuit board and disposed in said opening.

9. An article as defined in claim 1, wherein said circuit board further 30 comprises a wireless transmitter.

10. An article as defined in claim 1, wherein said tamper respondent sensor is shaped such that there are only two layers of substrate at said at least one overlap region.

11. A tamper respondent sensor as defined in claim 1, wherein said 35 second side of said substrate has no exposed conductive traces.

12. A tamper respondent sensor as defined in claim 1, wherein said substrate further comprises an adhesive.

13. A tamper respondent sensor as defined in claim 12, wherein said adhesive is disposed over either said first layer or said second layer of conductive traces 14.

14. A tamper respondent sensor as defined in claim 12, wherein said adhesive is a PSA.

15. A tamper respondent sensor comprising:

- (a) a substrate having a first side and a second side, said substrate adapted to be folded to produce an overlapping portion of said first side with an overlapping portion of said second side;

- (b) a first layer of conductive traces on said first side;

- (c) a second layer of conductive traces only at said overlapping portion of said second side,

- (d) said second side having a region free of conductive traces,

- (e) said second layer of conductive traces electrically connected to said first layer of conductive traces.

16. A tamper respondent sensor as defined in claim 15, wherein said substrate is opaque.

17. A tamper respondent sensor as defined in claim 15, wherein said substrate is insulating.

18. A tamper respondent sensor as defined in claim 15, wherein said substrate is PET.

19. A tamper respondent sensor as defined in claim 15, wherein said substrate further comprises an adhesive.

20. A tamper respondent sensor as defined in claim 19, wherein said adhesive is disposed over said first layer of conductive traces.

21. A tamper respondent sensor as defined in claim 19, wherein said adhesive is a PSA.

22. A tamper respondent sensor as defined in claim 15, further comprising an opening.

23. A tamper respondent sensor as defined in claim 15, wherein said traces are in an unpredictable pattern.

24. A tamper respondent sensor as defined in claim 15 further comprising an I/O lead.

25. A tamper respondent sensor as defined in claim 15 further comprising at least one via through said substrate at said

overlapping portion connecting said first layer of conductive traces to said second layer of conductive traces.

**FIG. 1**

PRIOR ART

**FIG. 2A**

FIG. 2B

**FIG. 3B****FIG. 3A**

**FIG. 5**

**FIG. 6**