(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2016-0130985

(43) 공개일자 2016년11월15일

- (51) 국제특허분류(Int. Cl.)

*H01L 23/373* (2006.01) *H05K 7/20* (2006.01)

- (52) CPC특허분류

*H01L 23/373* (2013.01)

*H05K 7/20427* (2013.01)

- (21) 출원번호 10-2016-7020371

- (22) 출원일자(국제) 2015년02월23일

심사청구일자 없음

- (85) 번역문제출일자 2016년07월26일

- (86) 국제출원번호 PCT/US2015/017043

- (87) 국제공개번호 WO 2015/138110

국제공개일자 2015년09월17일

- (30) 우선권주장

14/202,451 2014년03월10일 미국(US)

- (71) 출원인

더 보잉 컴파니

미국, 일리노이스 60606, 시카고, 100 노스 리버

사이드 플라자

- (72) 발명자

리, 안젤라 더블유.

미국, 워싱턴 98203, 에버렛, 3003 더블유. 캐지

노 로드

헌트, 제프리 에이치.

미국, 캘리포니아 90245, 엘 세간도, 900 엔. 서

펠베다 빌브드.

하우, 와이너 알.

미국, 캘리포니아 90740, 실 비치, 2201 실 비치

빌브드

- (74) 대리인

김윤배, 강철중

전체 청구항 수 : 총 18 항

(54) 발명의 명칭 **그래핀계 열 관리 시스템**

### (57) 요 약

한 측면에서, 열적으로 관리된 전자 부품이 본 명세서에서 설명된다. 일부 구현예로서, 열적으로 관리된 전자 부품은 전자 부품 및 전자 부품의 표면에 배치 된 열 관리 코팅을 포함한다. 열 관리 코팅은 부품의 표면 상에 배치된 그래핀 코팅층을 포함한다. 그래핀 코팅층은 배열된 탄소 나노 입자의 층을 포함할 수 있다. 또한, 열 관리 코팅은 그래핀 코팅층 상에 배치된 배열된 탄소 나노 입자의 층을 추가로 포함할 수 있다. 다른 측면에서, 전자 부품에 대한 열 관리 코팅을 도포하는 방법이 개시된다. 일부 구현예로서, 이러한 방법은 전자 부품의 표면에 그래핀 코팅층을 배치하는 단계를 포함한다. 그래핀 코팅층은 배열된 탄소 나노 입자의 층을 포함할 수 있다. 이러한 방법은 상기 그래핀 코팅층 상에 배열된 탄소 나노 입자의 층을 추가로 배치하는 것을 포함할 수 있다.

### 대 표 도 - 도1

(52) CPC특허분류

*H01L 2924/0002 (2013.01)*

---

## 명세서

### 청구범위

#### 청구항 1

열적으로 관리되는 전자 부품으로서,

상기 전자 부품의 표면에 배치된 열 관리 코팅을 포함하되 상기 열 관리 코팅은 전자 부품의 표면에 배치되는 그래핀 코팅층; 및

상기 그래핀 코팅층에 배치되는 배열된 탄소 나노 입자층을 포함하는 열적으로 관리되는 전자 부품.

#### 청구항 2

제1항에 있어서, 상기 전자 부품의 표면과 상기 열 관리 코팅 사이에 배치된 전기 절연 재료층을 추가로 포함하는 열적으로 관리되는 전자 부품.

#### 청구항 3

제1항에 있어서, 상기 그래핀 코팅층은 1과 30 원자층 사이를 포함하는 열적으로 관리되는 전자 부품.

#### 청구항 4

제1항에 있어서, 상기 그래핀 코팅층은 약 500 nm 이하의 두께를 갖는 열적으로 관리되는 전자 부품.

#### 청구항 5

제1항에 있어서, 상기 탄소 나노 입자는 단일벽 탄소 나노 튜브, 다중벽 탄소 나노 튜브, 폴리린, 헤테로 폴리린, 또는 이들의 조합을 포함하는 열적으로 관리되는 전자 부품.

#### 청구항 6

제1항에 있어서, 배열된 탄소 나노 입자층은 대칭 구조 또는 비대칭 구조를 갖는 열적으로 관리되는 전자 부품.

#### 청구항 7

제1항에 있어서, 상기 배열된 탄소 나노 입자층은 오른쪽 또는 왼쪽 구조를 갖는 열적으로 관리되는 전자 부품.

#### 청구항 8

제1항에 있어서, 상기 열 관리 코팅은 열적으로 관리되는 전자 부품의 전체 중량을 기준으로, 열적으로 관리되는 전자 부품의 약 0.2중량% 이상을 포함하는 열적으로 관리되는 전자 부품.

#### 청구항 9

제1항에 있어서, 상기 열 관리 코팅은 약  $25 \text{ MW/m}^2\text{K}$  이상의 열 전도도를 나타내는 열적으로 관리되는 전자 부품.

#### 청구항 10

전자 부품에 포함되는 열 관리 코팅을 도포하는 방법으로서,

상기 전자 부품의 표면에 그래핀 코팅층을 배치하는 단계; 및

상기 그래핀 코팅층에 배열된 탄소 나노 입자의 층을 배치하는 단계를 포함하는 열 관리 코팅을 도포하는 방법.

#### 청구항 11

제10항에 있어서, 상기 전자 부품의 표면에 그래핀 코팅층을 배치하기 전에 전기 절연 재료층을 상기 전자 부품

에 배치하는 단계를 추가로 포함하는 열 관리 코팅을 도포하는 방법.

### 청구항 12

제10항에 있어서, 상기 탄소 나노 입자는 단일벽 탄소 나노 튜브, 다중벽 탄소 나노 튜브, 풀러린, 헤테로 풀러린, 또는 이들의 조합을 포함하는 열 관리 코팅을 도포하는 방법.

### 청구항 13

제10항에 있어서, 상기 배열된 탄소 나노 입자의 층은 화학 기상 증착을 사용하여 수행하는 열 관리 코팅을 도포하는 방법.

### 청구항 14

제10항에 있어서, 상기 그래핀 코팅층에 상기 배열된 탄소 나노 입자의 층을 배치하기 전에 그래핀 코팅층에 촉매 필름이 배치되는 열 관리 코팅을 도포하는 방법.

### 청구항 15

제14항에 있어서, 상기 촉매 필름은 니켈, 코발트, 철 또는 이들의 조합을 포함하는 열 관리 코팅을 도포하는 방법.

### 청구항 16

제14항에 있어서, 상기 배열된 탄소 나노 입자층의 배치는 상기 촉매 필름으로부터 산기 탄소 나노입자를 성장하는 것을 포함하는 열 관리 코팅을 도포하는 방법.

### 청구항 17

제16항에 있어서, 탄소 나노 입자의 성장시 상기 전자 부품에 DC 또는 AC 전기장을 인가하는 열 관리 코팅을 도포하는 방법.

### 청구항 18

제17항에 있어서, 상기 탄소 나노 입자의 성장시 상기 전자 부품에 자기장을 적용하는 열 관리 코팅을 도포하는 방법.

## 발명의 설명

### 기술 분야

[0001] 본 발명은 전자 부품으로부터, 특히 그래핀계 방열판 및 열관(thermal conduit)으로 에너지를 전도하기 위한 시스템 및 방법에 관한 것이다.

### 배경 기술

[0002] 전자 부품(electronic components) 및 전자 연결부(electronic connections) 또는 커넥터(connectors)들은 열 응력에 일반적으로 민감하다. 또한, 대부분의 전자 부품이나 전자 부품의 하위 요소들은 폐열을 발생한다. 그 결과, 열 응력으로 인한 전자 부품 또는 연결부 또는 커넥터에 대한 일시적인 또는 영구적인 손상을 방지하기 위해서 전자 부품 또는 연결부 또는 커넥터들로부터 열 에너지를 이동(transport)시키는 것이 바람직하다. 이전의 일부 방법에서는 전자 부품으로부터 열 에너지를 흡수하고 전도하기 위해 구리계와 같은 금속계를 사용하였다.

### 발명의 내용

### 해결하려는 과제

[0003] 불행하게도, 이러한 방법들은 과도한 중량의 추가 및/또는 과도한 부피를 차지하는 무겁고 및/또는 부피가 큰

금속계의 사용이 필요할 수 있다. 항공 우주 분야와 같은 많은 분야에서, 중량과 부피의 추가는 바람직하지 않다. 따라서, 전자 부품 및 전자 연결부 또는 커넥터에 대해 열 관리 시스템 및 방법 방법을 개선할 필요가 있다.

## 과제의 해결 수단

- [0004] 한 측면에서, 열적으로 관리된 전자 부품은, 일부 구현예로서, 이전의 열 관리 전자 부품들에 비해 하나 또는 그 이상의 이점을 제공할 수 있다는 것이 본 명세서에 기재되어 있다. 예를 들어, 일부 구현예로서, 본 명세서에서 기재하는 열적으로 관리된 전자 부품은 다른 열적으로 관리된 전자 부품에 비해 부피 및/또는 질량(mass)이 감소하였다. 또한, 본 명세서에서 기재하는 열적으로 관리된 전자 부품은 개선된 방열 및/또는 전도도 (conductance)와 같은 열관 특성을 나타낼 수 있다. 따라서, 일부 구현예로서, 본 명세서에서 기재하는 열적으로 관리된 전자 부품은 부품의 질량 또는 부피의 실질적인 증가 없이 개선된 열 이동 특성(thermal transport characteristic)을 나타낼 수 있다. 참고로, 본 명세서에 "전자 부품은" 전자 부품, 및 전자 부품들로부터, 전자 부품에 대한, 또는 전자 부품들 간의 어떤 전자 커넥터 또는 연결부들을 집합적으로 지칭하는 것이다.

- [0005] 일부 구현예로서, 본 명세서에서 기재하는 열적으로 관리된 전자 부품은 전자 부품의 표면과 열 관리 코팅 사이에 배치된 절연 재료 층을 추가로 포함한다. 일부 구현예로서, 열 관리 코팅은 전자 부품의 표면에 배치된 그래핀 코팅층을 포함한다. 일부 구현예로서, 그래핀 코팅층은 배열된 탄소 나노 입자층을 추가로 포함한다. 또한, 어떤 경우에, 열 관리 코팅은 그래핀 코팅층 위에 배치된 배열된 탄소 나노 입자층을 추가로 포함한다. 그래핀 코팅층은, 일부 구현예로서, 하나 또는 그 이상의 그래핀 시트를 포함한다. 일부 구현예로서, 그래핀 코팅층은 1과 30 원자층 사이를 포함한다. 배열된 탄소 나노 입자층은 일부 구현예로서, 단일벽 탄소 나노튜브(SWNTs), 다중벽 탄소 나노튜브(MWNTs), 폴리린(fullerenes), 헤테로 폴리린(heterofullerenes), 또는 이들의 조합을 포함한다. 또한, 어떤 경우에는, 탄소 나노 입자가 대칭 또는 비대칭 구조로 배열 및 구성될 수 있다. 일부 예에서, 배열된 탄소 나노 입자의 하나 또는 그 이상의 층은 오른쪽(dextral) 또는 왼쪽(sinistral) 구조를 갖는다.

- [0006] 다른 측면으로, 전자 부품에 대해 열 관리 코팅을 도포하는 방법이 본 명세서에 설명되어 있다. 일부 구현예로서, 전자 부품에 대해 열 관리 코팅을 도포하는 방법은 상기 전자 부품의 표면에 그래핀 코팅층을 배치하는 단계를 포함한다. 어떤 경우에는, 그래핀 코팅층은 배열된 탄소 나노 입자층을 포함한다. 또한, 어떤 경우에, 상기 그래핀 코팅층 상에 배열된 탄소 나노 입자층을 추가로 배치하는 단계를 포함한다. 일부 구현예로서, 배열된 탄소 나노 입자층은 화학 기상 증착(CVD) 등의 증착법을 이용하여 증착된다. 또한, 어떤 경우에, 본 명세서에서 기재하는 방법은 배열된 탄소 나노 입자층을 배치하기 전에 그래핀 코팅층에 촉매 막 또는 촉매 입자의 층을 증착하는 단계를 포함한다. 또한, 일부 구현예에서, 전기장 및/또는 자기장이 배열된 탄소 나노 입자층의 성장시에 상기 전자 부품에 적용된다. 또한, 일부의 경우에, 본 명세서에서 기재하는 방법은 전자 부품의 표면에 열 관리 코팅을 배치하기 전에 전자 부품의 표면에 전기 절연 재료 층을 배치하는 단계를 추가로 포함한다.

- [0007] 본 명세서의 측면에 따르면, 열적으로 관리된 전자 부품은 전자 부품의 표면상에 배치된 열 관리 코팅을 포함하여 상기 열 관리 코팅은 전자 부품의 표면상에 배치된 그래핀 코팅층 및 해당 그래핀 코팅층 상에 배치된 배열된 탄소 나노 입자층을 포함한다.

- [0008] 유리하게, 열적으로 관리된 전자 부품은 전자 부품의 표면과 상기 열관리 코팅 사이에 배치된 전기 절연 재료 층을 포함한다.

- [0009] 유리하게, 그래핀 코팅층은 1과 30 원자층 사이를 포함한다.

- [0010] 유리하게, 그래핀 코팅층은 약 500 nm 이하의 두께를 갖는다.

- [0011] 유리직하게, 탄소 나노 입자는 단일벽 탄소 나노튜브, 다중벽 탄소 나노튜브, 폴리린, 헤테로폴리린, 또는 이들의 조합을 포함한다.

- [0012] 유리하게, 배열된 탄소 나노 입자의 층은 대칭 구조를 갖는다.

- [0013] 유리하게, 배열된 탄소 나노 입자의 층은 비대칭 구조를 갖는다.

- [0014] 유리하게, 배열된 탄소 나노 입자의 층은 오른쪽 또는 왼쪽 구조를 갖는다.

- [0015] 유리하게, 열 관리 코팅은 열적으로 관리된 전자 부품의 총 중량에 대하여 열적으로 관리된 전자 부품의 약 0.2 중량% 이하로 포함한다.

- [0016] 유리하게, 열 관리 코팅은 약  $25 \text{ MW/m}^2 \text{ K}$  이상의 열전도도를 나타낸다.

- [0017] 본 명세서의 다른 측면에 따르면, 전자 부품의 표면에 그래핀 코팅층을 배치하는 단계; 및 그래핀 코팅층 상에 배열된 탄소 나노 입자의 층을 배치하는 단계를 포함하는 전자 부품에 대한 열 관리 코팅을 도포하는 방법을 제공한다.

- [0018] 유리하게, 상기 방법은 전자 부품의 표면상에 그래핀 코팅층을 배치하기 전에 전자 부품의 표면 상에 전기 절연 재료층을 배치하는 단계를 추가로 포함한다.

- [0019] 유리하게, 탄소 나노 입자는 단일벽 탄소 나노 튜브, 다중벽 탄소 나노 튜브, 폴리린, 헤테로폴리린, 또는 이들의 조합을 포함한다.

- [0020] 유리하게, 배열된 탄소 나노 입자의 층을 배치하는 단계는 화학 기상 증착을 이용하여 수행된다.

- [0021] 유리하게, 촉매 막은 그래핀 코팅층 상에 배열된 탄소 나노 입자의 층을 배치하기 전에 그래핀 코팅층 상에 증착된다.

- [0022] 바람직하게, 촉매 막은 니켈, 코발트, 철 입자 또는 이들의 조합을 포함한다.

- [0023] 유리하게, 배열된 탄소 나노 입자의 층을 배치하는 단계는 촉매 막에서 탄소 나노 입자를 성장하는 단계를 포함한다.

- [0024] 유리하게, DC 전기장은 탄소 나노 입자의 성장시에 상기 전자 부품에 인가된다.

- [0025] 유리하게, 자기장은 탄소 나노 입자의 성장시에 상기 전자 부품에 인가된다.

- [0026] 임의로 AC 전기장은 탄소 나노 입자의 성장시에 상기 전자 부품에 인가된다.

- [0027] 이를 및 다른 구현에는 다음의 상세한 설명에서 더욱 상세히 설명하기로 한다.

### 도면의 간단한 설명

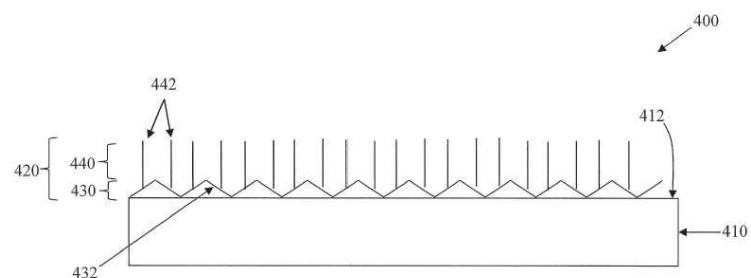

- [0028] 도 1은 본 명세서에서 기재하는 한 구현예에 따른 개략적인 열적으로 관리된 전자 부품의 측면도를 예시한 것이다.

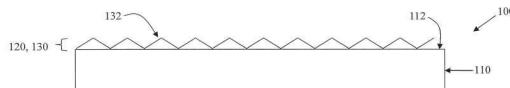

- 도 2는 본 명세서에서 기재하는 한 구현예에 따른 개략적인 열적으로 관리된 전자 부품의 측면도를 예시한 것이다.

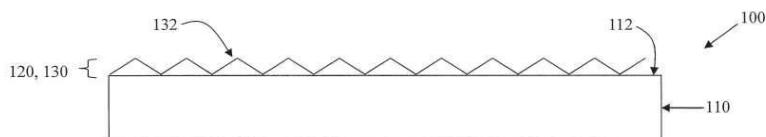

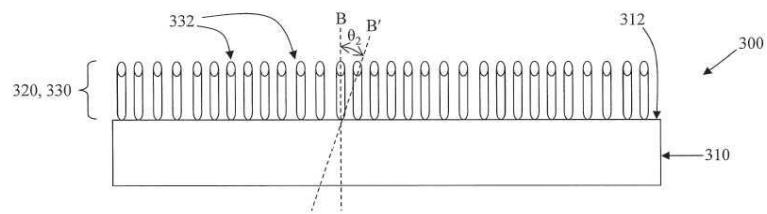

- 도 3은 본 명세서에서 기재하는 한 구현예에 따른 개략적인 열적으로 관리된 전자 부품의 측면도를 예시한 것이다.

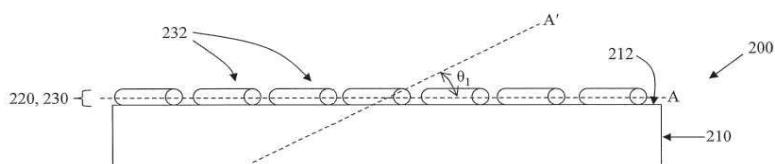

- 도 4는 본 명세서에서 기재하는 한 구현예에 따른 개략적인 열적으로 관리된 전자 부품의 측면도를 예시한 것이다.

### 발명을 실시하기 위한 구체적인 내용

- [0029] 본 명세서에서 기재하는 구현예는 다음의 상세한 설명, 구현예 및 도면을 참조하여 더욱 용이하게 이해할 수 있다. 그러나 본 명세서에서 기재하는 요소, 장치 및 방법은 상세한 설명, 구현예 및 도면들에 제시된 특정 구현 예에 한정되는 것은 아니다. 이를 구현예는 본 발명의 원리를 단지 예시한 것으로 인식되어야 한다. 수많은 변형 및 개조들은 본 발명의 사상 및 범위를 벗어남이 없이 당업자에게 명백할 것이다.

- [0030] 또한, 본 명세서에서 기재하는 모든 범위는 거기에 부분합 된 일부 및 모든 부분 범위를 포함하는 것으로 이해되어야 한다, 예를 들어, "10.0 내지 1.0"은 1.0 또는 그 이상의 최소값에서 시작해서 10.0 또는 그 이하의 최대값에서 끝나는 일부 및 모든 부분 범위, 예를 들어서 1.0 내지 5.3, 또는 4.7 내지 10.0, 또는 3.6 내지 7.9 등을 포함하는 것으로 고려되어야 한다.

- [0031] 본 명세서에서 기재하는 모든 범위는 달리 명시적으로 언급되지 않는 한 범위의 끝점을 포함하는 것으로 간주한다. 예를 들어, "5와 10 사이"의 범위는 일반적으로 종료점 5 및 10을 포함하는 것으로 간주되어야 한다.

- [0032] 또한, 문구 "까지"는 양(amount) 또는 수량(quantity)과 관련하여 사용되는 것으로 그 양은 최소한 검출 가능한 양 또는 수량임을 이해해야 한다. 예를 들어, 특정한 양"까지"의 양으로 존재한다는 재료는 검출 가능한 양으로

부터, 특정한 양을 포함하는 양까지 존재할 수 있다.

### I. 열적으로 관리된 전자 부품

한 측면으로, 열적으로 관리된 전자 부품은 본 명세서에서 설명되어 있다. 일부 구현예로서, 열적으로 관리된 전자 부품은 전자 부품 및 전자 부품의 표면에 배치된 열 관리 코팅을 포함한다. 어떤 경우에는, 열적으로 관리된 전자 부품은 전자 부품의 표면과 열 관리 코팅 사이에 배치된 절연 재료 층을 포함한다. 일부 구현예로서, 열적으로 관리된 전자 부품의 전기 절연 재료 층은 열 관리 코팅과 전자 부품의 표면상에서 노출된 전도성 재료 간의 전기 접촉을 방지할 수 있다. 본 명세서에서 기재하는 열적으로 관리된 전자 부품의 열 관리 코팅은 전자 부품의 표면에 배치된 그래핀 코팅층을 포함한다. 어떤 경우에는, 그래핀 코팅층은 배향 또는 배열된 탄소 나노 입자 층을 포함한다. 또한, 어떤 경우에서, 열 관리 코팅층은 추가로 그래핀 코팅층 상에 배치된 배향 또는 배열된 탄소 나노 입자의 추가 층을 포함한다.

열적으로 관리된 전자 부품의 특정 부품을 참조하면, 본 명세서에서 기재하는 열적으로 관리된 전자 부품은 전자 부품의 표면상에 배치된 그래핀 코팅층을 포함하는 열 관리 코팅을 포함한다. 본 발명의 목적과 모순되지 않는 임의의 그래핀 코팅층이 사용될 수 있다. 본 명세서에서 참고를 목적으로, "그래핀" 코팅층은  $sp^3$ -결합 탄소가 아닌 주요 탄소 성분으로  $sp^2$ -결합 탄소를 포함한다. 일부 구현예로서, 본 명세서에서 기재하는 그래핀 코팅층은  $sp^3$ -하이브리드된 탄소를 포함하지 않거나 실질적으로  $sp^3$ -하이브리드된 탄소를 포함하지 않는다. 예를 들어, 일부 구현예로서, 그래핀 코팅층은 그래핀 코팅층에서 탄소의 총량에 대하여 약 10원자% 이하 또는 약 5원자% 이하의  $sp^3$ -하이브리드된 탄소를 포함한다. 일부 구현예로서, 그래핀 코팅층은 약 2원자% 이하 또는 약 1원자% 이하의  $sp^3$ -하이브리드된 탄소를 포함한다. 또한, 본 명세서에서 기재하는 그래핀 코팅층은 일부 구현예로서, 다이아몬드형 탄소(DLC)를 포함하거나, 구성되거나 본질적으로 구성되지 않는다.

일부 구현예로서, 그래핀 코팅층은 하나 또는 그 이상의 그래핀 시트를 포함, 구성 또는 실질적으로 구성되어 있다. 그래핀 시트는, 일부 구현예로서, 평면한 평면 구조를 갖는 단일 문자 또는 원자층을 포함한다. 본 발명의 목적에 모순되지 않는 임의의 개수의 그래핀 시트가 사용될 수 있다. 일부 구현예로서, 그래핀 코팅층은 복수의 그래핀 시트를 포함한다. 복수의 그래핀 시트는 일부 구현예로서, 적층 또는 층상 구조로 배열될 수 있다. 다른 구현예에서, 그래핀 코팅층은 단일의 그래핀 시트를 포함 또는 구성되어 있다. 따라서, 일부 구현예로서, 본 명세서에서 기재하는 그래핀 코팅층은 하나 또는 그 이상의 원자층을 포함한다. 일부 구현예로서, 그래핀 코팅층은 1과 30 원자층 사이를 포함한다. 일부 구현예로서, 그래핀 코팅층은 1과 20 원자층 또는 1과 10 원자층 사이의 그래핀 층을 포함한다. 일부 구현예로서, 그래핀 코팅층은 1 원자층의 그래핀 층을 포함한다.

도 1은 그래핀 시트를 포함하는 그래핀 코팅층을 포함하는 열 관리 코팅을 포함하는 열적으로 관리된 전자 부품의 측면도를 예시한 것이다. 당업자에 의해 알 수 있는 바와 같이, 도 1에 묘사되어 있는 다양한 요소들은 단지 표시하기 위한 것이며, 반드시 일정한 비율로 도시된 것은 아니다. 도 1의 구현예에서, 열적으로 관리된 전자 부품(100)은 전자 부품(110)과 해당 전자 부품(110)의 표면(112)에 배치된 열 관리 코팅(120)을 포함한다. 열 관리 코팅(120)은 그래핀 시트(132)를 포함하는 그래핀 코팅층(130)을 포함한다. 그래핀 시트(132)는 도 1에서 알칸 사슬과 유사한 선으로 개략적으로 도시되어 있다. 그러나, 당업자에 의해 이해될 수 있는 바와 같이, 이러한 묘사는 단지 설명을 하기 위한 것이다. 또한, 전자 부품(110)도 도 1에 사각형 단면과 편평한 평면 구조를 갖는 것으로 개략적으로 도시되어 있다. 그러나, 다른 구현도 또한 가능하다. 예를 들어, 일부 구현예로서, 전자 부품은, 원형, 타원형 또는 다른 단면 형상을 가질 수 있다. 본 발명의 목적에 모순되지 않는 한 임의의 크기 및 형상이 사용될 수 있다. 이와 유사하게, 일부 구현예로서, 전자 부품(110)의 표면(112)은 볼록한 곡률, 오목한 곡률, 또는 주기적 또는 기복이 많은 곡률을 포함하는 곡률을 가질 수 있다. 일부 구현예로서, 전자 부품(110)의 표면(112)은 변압기(transformer), 저항기(resistor), 콘덴서(capacitor), 인덕터(inductor), 집적회로(integrated circuit) 및/또는 다른 전자 부품과 같은 전자 부품을 포함할 수 있다. 일부 구현예로서, 전자 부품(110)의 표면(112)은 그 표면에 배치된 하나 또는 그 이상의 전자 부분품(electronic subcomponent)을 가질 수 있으며, 텍스처(textured) 또는 요철(irregular) 표면을 만든다. 예를 들어, 어떤 경우에는, 하나 이상의 변압기, 저항기, 콘덴서 및/또는 인덕터가 표면(112) 상에 배치되고, 그래핀 시트(132)가 부분품으로 배치된다. 또한, 일부의 경우에, 중간 전기 절연 재료층(도시되지 않음)이, 표면(112) 상에 배치될 수 있는 하나 또는 그 이상의 전자 부분품을 포함하는 표면(112)과 열 관리 코팅(120) 사이에 배치될 수 있다.

다른 구현예에서, 본 명세서에서 기재하는 그래핀 코팅층은 그래핀 튜브층을 포함, 구성 또는 본질적으로 구성

되어 있다. 본 발명의 목적에 모순되지 않게 임의의 그래핀 투브를 사용할 수 있다. 일부 구현예로서, 그래핀 투브는 단일벽 탄소 나노 투브(SWNTs) 또는 다중벽 탄소 나노 투브(MWNTs)와 같은 탄소 나노 투브(CNTs)를 포함한다. 또한, 그래핀 투브는 본 발명의 목적과 모순되지 않게 임의의 크기를 가질 수 있다. 예를 들어, 일부 구현예로서, 그래핀 투브는 약 500 nm 이하, 약 300 nm 이하, 또는 약 100 nm 이하에서 적어도 하나 치수의 크기를 갖는다. 일부 구현예로서, 그래핀 투브는 약 1 nm와 약 200 nm 사이, 약 1 nm와 약 150 nm 사이 또는 약 5 nm와 약 100 nm 사이에서 적어도 하나 치수의 크기를 갖는다. 일부 구현예로서, 그래핀 투브는 약 5 nm와 약 75 nm 사이, 또는 약 15 nm와 약 60 nm 사이에서 적어도 하나 치수의 크기를 갖는다. 일부 구현예로서, 그래핀 투브는 약 20 nm와 약 30 nm 사이 또는 약 45 nm와 약 55 nm의 사이에서 적어도 하나 치수의 크기를 갖는다. 일부 구현예로서, 그래핀 투브는 약 300 nm 이하, 또는 약 100 nm 이하의 적어도 두개 치수의 크기를 갖는다. 일부 구현예로서, 그래핀 투브는 약 1 nm와 약 200 nm 사이, 약 1 nm와 약 150 nm 사이, 또는 약 5 nm와 약 100 nm의 사이에서 적어도 두개 치수의 크기를 가진다. 일부 구현예로서, 그래핀 투브는 약 5 nm와 약 75 nm의 사이 또는 약 15 nm와 약 60 nm의 사이에서 적어도 두개 치수의 크기를 가진다.

[0039] 또한, 일부 구현예로서, 그래핀 코팅층의 그래핀 투브는 낮은 종횡비를 갖는다. 일부 구현예로서, 그래핀 투브는 약 20 이하 또는 약 10 이하의 종횡비를 갖는다. 일부 구현예로서, 그래핀 투브는 약 2와 약 15 사이 또는 약 3과 약 10 사이의 종횡비를 갖는다. 또한, 약 20 이하의 종횡비를 가지는 그래핀 투브는, 일부 구현예로서 약 5 nm 내지 약 200 nm 또는 약 10 nm 내지 약 100 nm의 범위의 길이를 갖는다.

[0040] 또한, 본 명세서에서 기재하는 그래핀 코팅층의 그래핀 투브는, 일부 구현예로서, 층 상에서 배향되거나 배열될 수 있다. 일부 구현예로서, 하나 이상의 그래핀은 층 상에서 수평 또는 실질적으로 수평으로 배향될 수 있다. 다른 구현예에서, 하나 이상의 그래핀 투브는 층 상에서 수직 또는 실질적으로 수직으로 배향될 수 있다. 또한, 일부 구현예로서, 층 상에서 수직 또는 실질적으로 수직으로 배향된 그래핀 투브는 일렬을 포함해서 배열되거나 실질적으로 배열된 것이다.

[0041] 도 2 및 도 3은 각각 본 명세서에 설명된 일부 구현예에 따른 그래핀 투브 층을 포함하는 그래핀 코팅층을 포함하는 열 관리 코팅을 예시한 것이다. 도 2에 의하면, 열적으로 관리된 전자 부품(200)은 전자 부품(210)과 전자 부품(210)의 표면(212) 상에 배치된 그래핀 코팅층(230)을 포함하는 열 관리 코팅(220)을 포함한다. 또한, 어떤 경우에, 중간 전기 절연층(도시 생략)은 표면(212)과 그래핀 코팅층(230) 사이에 위치할 수 있다. 도 2의 구현예에서, 열적으로 관리된 전자 부품(200)의 그래핀 코팅층(230)은 전자 부품(210)의 표면(212) 상에 수평 또는 실질적으로 수평으로 배향된 복수의 그래핀 투브(232)를 포함한다. 수평 배향은 표면(212)을 기준으로 한다. 본 명세서에서 참고를 목적으로, "수평" 배향은 어떤 배향을 포함하는데, 여기서 그래핀 투브(232)의 장축이 표면(212)에 평행하게 배향된다. 도 2의 구현예에서, 모든 그래핀 투브(232)는 표면(212)에 평행하게 배향된 장축을 갖는 것으로 도시되어 있다. 그러나, 다른 구성도 가능하다. 예를 들어, 일부 구현예에서, 하나 이상의 그래핀 투브는 도 2에서 선 A' 또는 표면(212)에 평행하지 않은 일부 다른 방향에 따라 장축을 가질 수 있다. 본 명세서에서 참고를 목적으로, "실질적으로 수평"의 배향은 그래핀 투브의 장축(A')이 전자 부품(210)의 표면에 평행한 선(A)과 약 45도 각도 이하의 각도( $\theta_1$ )로 형성하는 배향을 포함한다. 일부 구현예로서, 각도( $\theta_1$ )는 약 30도 이하 또는 약 15도 이하이다. 일부 구현예로서, 각도( $\theta_1$ )은 약 0도와 약 30도 사이이다. 일부 구현예로서, 본 명세서에서 기재하는 그래핀 코팅층의 그래핀 투브의 대부분은 수평 또는 실질적으로 수평으로 배향된다. 또한, 일부 구현예는 그래핀 코팅층의 그래핀 투브의 적어도 약 60%, 적어도 약 70%, 적어도 약 80%, 또는 약 90%는 수평 또는 실질적으로 수평으로 배향된다.

[0042] 다른 구현예에서, 그래핀 코팅층의 그래핀 투브는 수직 또는 실질적으로 수직하게 배향될 수 있다. 예를 들어, 도 3과 관련하여, 열 관리 전자 부품(300)은 전자 부품(310)과 전자 부품(310)의 표면(312) 상에 배치된 그래핀 코팅층(330)을 포함하는 열 관리 코팅(320)을 포함한다. 또한, 어떤 경우에는, 중간 절연층(도시하지 않음)은 표면(312)과 그래핀 코팅층(330) 사이에 배치될 수 있다. 도 3의 구현예에서, 열 관리 전자 부품(300)의 그래핀 코팅층(330)은 전자 부품(310)의 표면(312)에 수직 또는 실질적으로 수직하게 배향된 복수의 그래핀 투브(332)를 포함한다. 수직한 배향은 표면(312)을 기준으로 한다. 본 명세서에서 참고를 목적으로, "수직 배향"은 그래핀 투브(332)의 장축이 표면(312)에 수직으로 배향되는 배향을 포함한다. 도 3의 구현예에서, 모든 그래핀 투브(332)는 표면(312)에 수직하게 배향된 장축을 갖는 것으로 도시되어 있다. 그러나, 다른 구성도 가능하다. 예를 들어, 일부 구현예로서, 하나 또는 그 이상의 그래핀 투브는 도 3에서 선 B' 또는 표면(312)에 평행하지 않은 어떤 다른 방향을 따라 장축을 가질 수 있다. 본 명세서에 참고를 목적으로, "실질적으로 수직한" 배향은 어떤 배향을 포함하는데, 여기서, 그래핀 투브의 장축(B')은 전자 부품의 표면에 수직한 선(B)과 약 45도 이하의

각도( $\Theta_2$ )를 형성한다. 일부 구현예로서, 각도( $\Theta_2$ )는 약 30도 이하 또는 약 15도 이하이다. 일부 구현예로서, 각도( $\Theta_2$ )는 약 0도와 약 30도 사이이다. 일부 구현예로서, 본 명세서에서 기재하는 그래핀 코팅층의 그래핀 튜브의 대부분은 수직 또는 실질적으로 수직한 배향을 갖는다. 또한, 본 명세서에서 기재하는 일부 구현예로서, 그래핀 코팅층의 그래핀 튜브의 적어도 약 60%, 적어도 약 70%, 적어도 약 80%, 또는 적어도 약 90%는 수직 또는 실질적으로 수직한 배향을 갖는다.

[0043] 또한, 일부 구현예로서, 본 명세서에서 기재하는 그래핀 코팅층은 수평 또는 실질적으로 수평으로 배향된 단층의 그래핀 튜브 또는 수직 또는 실질적으로 수직으로 배향된 단층의 그래핀 튜브를 포함하는 단층의 그래핀 튜브를 포함, 구성 또는 본질적으로 구성되어 있다.

[0044] 또한, 본 명세서에서 기재하는 그래핀 코팅층은 본 발명의 목적과 모순되지 않게 임의의 두께를 가질 수 있다. 일부 구현예로서, 예를 들면, 그래핀 코팅층은 약 500 nm 이하, 약 300 nm 이하 또는 약 200 nm 이하의 평균 두께를 갖는다. 일부 구현예로서, 그래핀 코팅층은 약 100 nm 이하의 평균 두께를 갖는다. 일부 구현예로서, 그래핀 코팅층은 약 50 nm 이하, 10 nm 이하, 또는 약 5 nm 이하의 평균 두께를 갖는다. 일부 구현예로서, 그래핀 코팅층은 약 3 nm 이하, 약 2 nm 이하, 또는 약 1 nm 이하의 평균 두께를 갖는다. 예를 들어, 일부 구현예로서, 본 명세서에서 기재하는 그래핀 코팅층은 약 1 nm와 약 300 nm의 사이, 약 1 nm와 약 200 nm 사이, 약 1 nm와 약 100 nm 사이, 약 10 nm와 약 300 nm 사이, 약 10 nm와 약 200 nm 사이 또는 약 10 nm와 약 100 nm 사이의 평균 두께를 갖는다. 또한, 일부 구현예로서, 그래핀 코팅층은 약 50 nm와 약 300 nm 사이, 약 50 nm와 약 200 nm 사이, 약 50 nm와 약 100 nm 사이, 또는 약 100 nm와 약 300 nm 사이의 평균 두께를 갖는다. 일부 구현예로서, 그래핀 코팅층은 약 100 nm 이상, 또는 약 300 nm 이상의 평균 두께를 가질 수 있다.

[0045] 또한, 일부 구현예로서, 본 명세서에서 기재하는 그래핀 코팅층은 그래핀 튜브층을 포함하고, 그래핀 코팅층의 평균 두께는 그래핀 튜브의 평균 직경의 약 50배 보다 크지 않다. 일부 구현예로서, 그래핀 코팅층의 평균 두께는 그래핀 튜브의 평균 직경 보다 약 20배 이상 또는 약 10배 이상 보다 크지 않다. 일부 구현예로서, 그래핀 코팅층의 평균 두께는 그래핀 튜브의 평균 직경 보다 약 5배 이상, 약 3배 이상, 약 2배 이상 보다 크지 않다. 다른 구현예에서, 그래핀 코팅층의 평균 두께는 그래핀 튜브의 평균 길이에 비해 약 3배 이상 보다 크지 않다. 일부 구현예로서, 그래핀 코팅층의 평균 두께는 그래핀 튜브의 평균 길이에 비해 약 2배 이상, 약 1.5배 이상 또는 약 1배 이상 보다 크지 않다.

[0046] 일부 구현예로서, 본 명세서에서 기재하는 그래핀 코팅층은 미세 와이어에 의해 연결된 복수의 그래핀 플레이트렛(platelets)들로부터 형성된다. 일부 구현예로서, 복수의 그래핀 플레이트렛은 전자 부품의 표면에 배치될 수 있고, 복수의 그래핀 플레이트렛은 하나 또는 그 이상의 미세 와이어에 의해 연결될 수 있다. 일부 구현예로서, 그래핀 플레이트렛은 전자 부품과 별도로 미리 제조될 수 있고, 이어서 미세 와이어에 의해서 후속 연결을 위해 전자 부품의 표면 상에 배치된다. 또한, 본 발명의 목적과 모순되지 않게 그래핀 플레이트렛은 어떤 크기 또는 형상을 가질 수 있다. 예를 들어, 어떤 경우에 그래핀 플레이트렛은 약 1  $\mu\text{m}$  내지 약 2000  $\mu\text{m}$ 의 폭 또는 직경을 갖는다. 일부 구현예로서, 그래핀 플레이트렛은 약 50  $\mu\text{m}$ 와 약 1800  $\mu\text{m}$  사이, 약 200  $\mu\text{m}$ 와 약 1500  $\mu\text{m}$ 의 사이, 또는 약 400  $\mu\text{m}$ 와 약 1200  $\mu\text{m}$  사이의 폭 또는 직경을 갖는다. 또한, 일부 구현예로서, 그래핀 플레이트렛은 약 1  $\mu\text{m}$ 와 약 1500  $\mu\text{m}$  사이, 약 500  $\mu\text{m}$ 와 약 1300  $\mu\text{m}$  사이, 약 1000  $\mu\text{m}$ 과 약 2000  $\mu\text{m}$  사이, 또는 약 50  $\mu\text{m}$  와 약 1000  $\mu\text{m}$  사이의 폭 또는 직경을 갖는다.

[0047] 또한, 본 명세서에서 기재하는 그래핀 코팅층의 미세 와이어는 본 발명의 목적과 모순되지 않는 임의의 재료로 형성될 수 있다. 예를 들어, 일부 구현예로서, 미세 와이어는 금 나노 입자, 폴리머 미립자 및/또는 이들의 조합물과 같은 금속성 나노 입자로 형성된다. 일부 구현예로서, 미세 와이어는 금과 서브 마이크론 크기의 폴리스티렌 라텍스 미립자의 혼합 혼탁액으로 형성할 수 있다. 또한, 미세 와이어는 본 발명의 목적과 모순되지 않는 어떤 크기 또는 형상을 가질 수 있다. 예를 들어, 일부 구현예로서, 미세 와이어는 약 10 nm와 약 100 nm 사이, 약 10 nm와 약 40 nm 사이, 또는 약 15 nm와 약 50 nm 사이의 직경을 갖는다. 일부 구현예로서, 미세 와이어는 약 1 nm와 약 30 nm 사이, 약 15 nm와 약 30 nm 사이, 또는 약 15 nm와 약 100 nm의 사이의 직경을 갖는다. 또한, 일부 구현예로서, 미세 와이어는 약 15 nm와 약 5 cm 사이, 약 100 nm와 약 5 cm 사이, 약 500 nm와 약 5 cm 사이, 약 1  $\mu\text{m}$ 와 약 5 cm 사이, 또는 약 1 mm와 약 5 cm 사이의 길이를 갖는다. 일부 구현예로서, 미세 와이어는 약 15 nm와 약 1 cm 사이, 약 500 nm와 약 1 cm 사이, 약 1 cm와 약 5 cm 사이, 약 1  $\mu\text{m}$ 와 약 1 cm 사이, 약 1 mm와 약 1 cm 사이, 또는 약 5 mm와 약 3 cm 사이의 길이를 갖는다. 미세 와이어의 형성, 증착 및/또는 배치는 본 발명의 목적과 모순되지 않는 임의의 방법으로 수행할 수 있다. 일부 구현예로서, 예를 들면, 미세 와이어는 또한 이하에서 설명하는대로 유전체 조립 공정에 의해 형성될 수 있다.

[0048]

또한, 본 명세서에서 기재하는 열 관리 코팅의 그래핀 코팅층은 전자 부품의 표면에 배치된다. 일부 구현예로서, 그래핀 코팅층은 전자 부품의 표면에 직접 배치되어 있다. 다른 예에서, 그래핀 코팅층은 그래핀 코팅층과 상기 전자 부품의 표면 사이에 배치된 전기 절연 재료층 상에 배치된다. 또한, 일부 구현예로서, 그래핀 코팅층은 전기 절연 재료층에 또는 전자 부품의 표면에 접합 또는 접착되어 있다. 접합은 일부 구현예에서 화학적 접합을 포함한다. 일부 구현예로서, 접합은 물리적인 접합을 포함한다. 접합은, 일부 구현예에서, 공유 결합, 이온 결합, 수소 결합, 정전기적 상호 작용 및 반 데르 발스 상호 작용 중 하나 또는 그 이상을 포함 또는 구성한다. 일부 구현예로서, 예를 들면, 접합은 반 데르 발스 상호 작용을 포함 또는 구성한다. 일부 구현예로서, 본 명세서에서 기재하는 그래핀 코팅층은, Zong et al., "Direct measurement of graphene adhesion on silicon surface by intercalation of nanoparticles", *J Appl. Phys.*, volume 107, page 026104-1 ~ 026104-3(2007)의 방법에 따라 주사 전자 현미경(SEM)으로 측정했을 때, 전기 절연 재료층 또는 전자 부품의 표면에 적어도 약  $75 \text{ mJ/m}^2$ , 또는 약  $100 \text{ mJ/m}^2$ 의 접착 에너지로 접합 또는 접착한다. 구체적으로, 접착 에너지( $\gamma$ )는 다음 식 (1)으로 주어진다.

$$\gamma = \lambda Eh(w/a)^4 \quad (1)$$

[0049]

위 식에서,  $\lambda$ 는  $1/16$ 와 같은 기하학적 인자이고,  $E$ 는  $0.5 \text{ TPa}$ 이고,  $h$ 는 그래핀 코팅층의 두께이며,  $w$ 는 삽입된 나노 입자의 직경과 같은 중심 블리스터(blister) 변위이고,  $a$ 는 SEM에 의해서 측정된 기포 반경이다. 블리스터는 Zong 등에 교시되어 있는 바와 같이, 코팅층과 기판 사이에 소위 쇄기 입자 또는 삽입된 나노 입자를 배치하는 것에 의해 제공된다. 쇄기 입자는 본 발명의 목적과 모순되지 않는 임의의 적당한 입자를 포함할 수 있다. 일부 구현예로서, 예를 들면, 쇄기 입자는 약  $10 \text{ nm}$ 와 약  $100 \text{ nm}$  사이의 직경을 갖는 금 또는 은 나노 입자를 포함하며, 전자 부품과 측정 목적의 코팅층 사이에 배치되어 있다. 일부 구현예로서, 그래핀 코팅층은 전기 절연 재료층 또는 전자 부품의 표면에 본 명세서에서 기재하는데로 측정했을 때, 적어도 약  $150 \text{ mJ/m}^2$ 의 접착 에너지로 접합 또는 접착된다. 일부 구현예로서, 그래핀 코팅층은 약  $50 \text{ mJ/m}^2$  와 약  $300 \text{ mJ/m}^2$  사이, 또는 약  $100 \text{ mJ/m}^2$  와 약  $200 \text{ mJ/m}^2$  사이의 접착 에너지로 전기 절연 재료층 또는 전자 부품의 표면에 접합 또는 접착된다. 일부 구현예로서, 본 명세서에서 기재하는 그래핀 코팅층은 극단적인 온도, 고습도, 먼지, 전자기 방사선 노출과 같은 불리한 환경 조건에 노출되는 경우 또는 그러한 조건에 대한 노출의 변화 또는 주기에 노출될 때를 포함해서, 시간이 지남에 따라, 전자 부품에서 충간박리(delamination) 또는 다른 분리(detachment)에 대해 대항한다. 또한, 일부 구현예로서, 본 명세서에서 기재하는 그래핀 코팅층은 전자 부품의 전체 표면에 걸쳐 연속적 또는 실질적으로 연속적이다.

[0050]

본 명세서에서 기재하는 열적으로 관리된 전자 부품의 열 관리 코팅은 일부 구현예에서, 그래핀 코팅층 상에 배치된 배향 또는 배열된 탄소 나노 입자층을 추가로 포함한다. 본 발명의 목적과 모순되지 않는 임의의 탄소 나노 입자가 사용될 수 있다. 예를 들어, 일부의 경우에, 본 명세서에서 기재하는 배열된 나노 입자층의 탄소 나노 입자는 단일벽 탄소 나노 튜브 또는 다중벽 탄소 나노 튜브와 같은 이방성(anisotropic) 또는 세장형(elongated) 탄소 나노 입자를 포함한다. 어떤 경우에는 배열된 나노 입자층의 탄소 나노 입자는 그래핀 코팅층에 대한 상술한 기능을 갖는 그래핀 나노 튜브를 포함한다.

[0051]

또한, 일부 구현예로서, 배열된 나노 입자층의 탄소 나노 튜브는 대칭 구조를 갖는다. 다른 경우에, 탄소 나노 튜브는 비대칭 구조를 갖는다. 본 명세서에서 참고를 목적으로, "대칭" 구조를 갖는 탄소 나노 튜브는 회전형, 경면(mirror plane) 및/또는 활주면(glide plane) 대칭을 보인다. 당업자에 의해 알 수 있는 바와 같이, 회전형 대칭은 일반적으로 나노재료 성장 방향( $C_{2v}$  대칭과 같이)에 평행한 축에 대해서  $180^\circ$  회전으로 존재하는 대칭을 의미한다. 경면 대칭은 일반적으로 나노재료 성장 방향에 수직하게 놓여 있는 면을 가로질러서 반사하는 것을 의미한다. 활주면 대칭은 일반적으로 나노재료 성장 방향에 수직하게 놓여 있는 면을 가로질러서 반사하고, 이어서 반사면과 평행 이동하는 것을 말한다. 일부 구현예로서, 본 명세서에서 기재하는 대칭 탄소 나노 튜브는 회전형, 경면 및/또는 활주면 대칭 중 두개 또는 그 이상으로 표현된다. 마찬가지로, 본 명세서에서 참고를 목적으로, "비대칭" 구조를 갖는 탄소 나노 튜브는 비교적 낮은 정도의 회전형, 경면 및/또는 활주면 대칭을 보인다. 어떤 경우에서, 본 명세서에서 기재하는 비대칭 탄소 나노 튜브는 회전형, 경면 및/또는 활주면 대칭이 없거나 또는 이를 중 하나만을 나타낸다.

[0052]

또한, 배열된 나노 입자층의 탄소 나노 튜브는 또한 오른쪽 또는 왼쪽 구조를 가질 수 있다. 본 명세서에서 참고를 목적으로, "오른쪽" 구조를 가지는 탄소 나노 튜브는 오른손 키랄성(right-handed chirality)을 갖는 나노

튜브를 포함한다. 이와 마찬가지로, 본 명세서에서 참고를 목적으로, "왼쪽" 구조를 갖는 탄소 나노 튜브는 왼손 키랄성(left-handed chirality)을 갖는 나노 튜브를 포함한다.

[0054] 또한, 본 명세서에서 참고를 목적으로, "배열된" 탄소 나노 입자층은 모든 또는 실질적으로 모든 탄소 나노 입자가 층 내에서 동일 또는 실질적으로 동일한 방향으로 배향되어 있는 층을 포함한다. 배향은 탄소 나노 튜브의 장축과 같이 탄소 나노 입자의 장축에 비례할 수 있다. 예를 들어, 어떤 경우에, 배열된 탄소 나노 입자는 그래핀 나노 튜브 또는 탄소 나노 튜브를 포함하며, 모든 또는 실질적으로 모든 탄소 나노 튜브는 그래핀 코팅층의 그래핀 나노 튜브에 대해 본 명세서에서 설명한 바와 같이, 수직 또는 실질적으로 수직한 배향을 갖는다. 일부 구현예에서, 배열된 나노 입자층 내에 있는 탄소 나노 튜브의 수직한 또는 실질적으로 수직한 배열은 하층의 그래핀 코팅층을 포함하거나 하나 또는 그 이상의 그래핀 시트로부터 형성될 때 특히 유용할 수 있다. 다른 예에서, 배열된 나노 입자층의 모든 또는 실질적으로 모든 탄소 나노 튜브는 수평 또는 실질적으로 수평한 배향을 갖는다. 일부 구현예로서, 모든 또는 실질적으로 모든 탄소 나노 튜브는 전자 부품의 표면에 대해 약 45도 내지 55도의 배향과 같이 수평한 배향 및 수직한 배향 사이에 있다. 또한, 어떤 경우에, 탄소 나노 입자의 배향의 표준 편차(전자 부품의 표면에 대한 각도 측면에서)는 약 15도 보다, 약 10도 보다 또는 약 5도 보다 크지 않다. 또한, 일부 구현예로서, 본 명세서에서 기재하는 배열된 층의 탄소 나노 튜브의 대부분은 실질적으로 수직 배향과 같이 본 명세서에서 기재하는 배향을 갖는다. 또한, 일부 구현예에서, 배열된 층의 탄소 나노 튜브의 적어도 약 60%, 적어도 약 70%, 적어도 약 80%, 또는 약 90%가 본 명세서에서 기재하는 배향을 갖는다.

[0055] 본 명세서에서 기재하는 배열된 나노 입자의 층은, 일부 구현예에서, 대칭, 비대칭, 오른쪽 또는 왼쪽 구조를 갖는다. 이러한 층에서, 본 명세서에서 참고를 목적으로, 대부분의 탄소 나노 입자는 리사이트 구조(recited structure)를 나타낸다. 예를 들어, 배열된 나노 입자의 대칭층에서, 대부분의 배열된 나노 입자들은 상기에서 설명한 바와 같이, 대칭 구조를 갖는다. 이와 유사하게, 오른쪽 구조를 가지는 배열된 나노 입자의 층에서, 대부분의 배열된 나노 입자들은 상기에서 설명한 바와 같이 오른쪽 구조를 갖는다. 또한, 대칭, 비대칭, 오른쪽 또는 왼쪽 구조를 가지는 층의 일부 구현예에서, 층의 탄소 나노 입자의 적어도 약 60%, 적어도 약 70%, 적어도 약 80%, 또는 적어도 약 90%는 대칭, 비대칭, 오른쪽 또는 왼쪽 구조를 갖는다.

[0056] 도 4는 전자 부품 및 그래핀 코팅층과 해당 그래핀 코팅층에 배치된 배열된 탄소 나노 입자의 층을 포함하는 열 관리 코팅을 포함하는 열적으로 관리된 전자 부품의 측면도를 예시한 것이다. 당업자에 의해 알 수 있는 바와 같이, 도 4에 도시한 여러가지 요소들은 반드시 일정한 비율로 그려진 것은 아니다. 도 4의 구현예에서, 열 관리 전자 부품(400)은 전자 부품(410) 및 열 관리 코팅(420)을 포함한다. 열 관리 코팅(420), 전자 부품(410)의 표면(412) 상에 배치된 그래핀 코팅층(430)을 포함한다. 또한, 어떤 경우에, 중간 전기 절연층(도시 생략)은 표면(412)과 그래핀 코팅층(430) 사이에 배치될 수 있다. 도 4에 도시된 바와 같이, 배열된 탄소 나노 입자층(440)은 그래핀 코팅층(430) 상에 배치된다. 그래핀 코팅층(430)은 그래핀 시트(432)를 포함한다. 배열된 탄소 나노 입자층(440)은 수직으로 배향된 탄소 나노 튜브(442)의 배열을 포함한다. 탄소 나노 튜브(442)는 수직으로 연장되는 선으로 개략적으로 도시되어 있다.

[0057] 본 명세서에서 기재하는 배열된 탄소 나노 입자의 층은 본 발명의 목적과 모순되지 않는 임의의 두께를 가질 수 있다. 일부 구현예로서, 예를 들면, 배열된 탄소 나노 입자의 층은 약 500 nm 이하, 약 300 nm 이하 또는 약 200 nm 이하의 평균 두께를 갖는다. 일부 구현예로서, 배열된 탄소 나노 입자의 층은 약 100 nm 이하 또는 약 50nm 이하의 평균 두께를 갖는다. 어떤 경우에, 본 명세서에서 기재하는 배열된 탄소 나노 입자의 층은 약 1 nm 와 약 300 nm 사이, 약 1 nm와 약 200 nm 사이, 약 1 nm와 약 100 nm 사이, 약 10 nm와 약 300 nm 사이, 약 10 nm와 약 200 nm 사이, 또는 약 10 nm와 약 100 nm 사이의 평균 두께를 가질 수 있다. 또한, 일부 구현예로서, 배열된 탄소 나노 입자의 층은 약 50 nm와 약 300 nm 사이, 약 50 nm와 약 200 nm 사이, 약 50 nm와 약 100 nm 사이, 또는 약 100 nm와 약 300 nm 사이의 평균 두께를 가질 수 있다. 일부 구현예로서, 배열된 탄소 나노 입자의 층은 약 100 nm 이상 또는 약 300 nm 이상의 평균 두께를 가질 수 있다.

[0058] 또한, 본 명세서에서 기재하는 열 관리 코팅은 본 발명의 목적과 모순되지 않는 임의의 전자 부품의 임의의 표면 상에 배치될 수 있다. 예를 들어, 일부의 경우, 표면은 전자 부품의 발열면이다. 또한, 어떤 경우에서, 전자 부품은 전자 부품에 대해, 전자 부품으로부터 또는 전자 부품 간에 접적 회로, 변압기, 저항기, 콘덴서, 인덕터 또는 전기적인 접속부를 포함한다. 일부 구현예로서, 전자 부품은 하나 이상의 전자 접속부 또는 커넥터를 포함할 수 있는 인쇄 회로 기판 등의 회로 기판을 포함한다. 또한, 전자 부품은 본 발명의 목적과 모순되지 않는 임의의 재료로 형성될 수 있다. 예를 들어, 일부 구현예로서, 전자 부품은 구리 박판, 수지 함침 B-스테이지 천, 에폭시, 액체 광 이미지 램프 마스크 잉크 및/또는 건조 필름 광 이미지 램프 마스크와 같은 박판을 포함하거나 그로부터 형성된다. 일부 구현예로서, 전자 부품은 Si, Ge 또는 InP 등의 반도체 재료; 스테인리스 스틸, 금,

은 또는 구리 등의 금속; 및/또는 사파이어,  $\text{SiO}_2$  및  $\text{SiC}$  등의 유전체 재료(dielectric material)를 포함하거나 그로부터 형성된다.

[0059] 본 명세서에서 기재하는 열적으로 관리된 전자 부품은 어떤 경우에, 그래핀 코팅 층과 전자 부품의 표면 사이에 배치된 전기 절연 재료층을 포함한다. 본 발명의 목적과 모순되지 않는 임의의 절연 재료층이 사용될 수 있다. 어떤 경우에, 예를 들면, 절연 재료층은 플라스틱 또는 고무 재료와 같은 폴리머성 재료를 포함하거나 그로부터 형성된다. 다른 경우에, 절연 재료층은 이중층 그래핀(BLG) 또는 그래핀 산화물을 포함하거나 그로부터 형성된다. 일부 구현예로서, 절연 재료층은 이산화 규소 또는 세라믹 등의 무기 재료를 포함하거나 그로부터 형성된다. 다른 전기 절연 재료도 사용될 수 있다.

[0060] 또한, 본 명세서에서 기재하는 절연 재료층은, 본 발명의 목적과 모순되지 않는 임의의 두께를 가질 수 있다. 일부 구현예로서, 예를 들어, 절연 재료층은 약  $10 \mu\text{m}$  이하 또는 약  $1 \mu\text{m}$  이하의 평균 두께를 갖는다. 일부 구현예로서, 절연 재료층은 약  $500 \text{ nm}$  이하의 평균 두께를 갖는다. 일부 구현예로서, 절연 재료층은 약  $100 \text{ nm}$ 와 약  $10 \mu\text{m}$  사이, 약  $500 \text{ nm}$  내지 약  $10 \mu\text{m}$ 의 사이, 또는 약  $100 \text{ nm}$ 와 약  $1 \mu\text{m}$  사이의 평균 두께를 갖는다. 일부 구현예로서, 전기 절연 재료층은 약  $10 \mu\text{m}$  보다 큰 평균 두께를 가질 수 있다.

[0061] 또한, 본 명세서에서 기재하는 열적으로 관리된 전자 부품은 일부 구현예로서, 하나 이상의 바람직한 특성을 발휘할 수 있다. 일부 구현예로서, 예를 들면, 본 명세서에서 기재하는 열적으로 관리된 전자 부품의 열 관리 층은 열적으로 관리된 전자 부품의 전체 중량 또는 질량에 비해서 낮은 중량 또는 질량을 보인다. 예를 들어, 어떤 경우에서, 열 관리 코팅은 열적으로 관리된 전자 부품의 전체 중량을 기준으로, 열적으로 관리된 전자 부품의 약 0.3 중량% 이하, 약 0.2 중량% 이하, 약 0.1 중량% 이하, 약 0.05 중량% 이하, 약 0.01 중량% 이하를 포함한다. 어떤 경우에, 열 관리 코팅은 열적으로 관리된 전자 부품의 전체 중량을 기준으로 열적으로 관리된 전자 부품의 약 0.001 중량%와 약 0.3 중량% 사이, 약 0.001 중량%와 약 0.1 중량% 사이, 약 0.001 중량%와 약 0.01 중량% 사이, 또는 약 0.005 중량%와 약 0.05 중량% 사이를 포함한다. 일부 예에서, 열 관리 코팅은 열적으로 관리된 전자 부품의 총 중량을 기준으로, 열적으로 관리된 전자 부품의 약 0.001 중량% 이하 또는 약 0.3 중량% 이상을 포함한다.

[0062] 또한, 일부 구현예로서, 본 명세서에서 기재하는 열적으로 관리된 전자 부품의 열 관리 코팅은 높은 열 전도도를 보인다. 예를 들어, 일부의 경우에, 열 관리 코팅은 적어도 약  $10 \text{ MW/m}^2\text{K}$ , 적어도 약  $15 \text{ MW/m}^2\text{K}$ , 적어도 약  $20 \text{ MW/m}^2\text{K}$ , 적어도 약  $25 \text{ MW/m}^2\text{K}$ , 적어도 약  $30 \text{ MW/m}^2\text{K}$ , 또는 적어도 약  $35 \text{ MW/m}^2\text{K}$ 의 열 전도도를 보인다. 일부 구현예에서, 본 명세서에서 기재하는 열적으로 관리된 전자 부품의 열 관리 코팅은 약  $10 \text{ MW/m}^2\text{K}$ 와 약  $50 \text{ MW/m}^2\text{K}$  사이, 약  $15 \text{ MW/m}^2\text{K}$ 와 약  $50 \text{ MW/m}^2\text{K}$  사이, 약  $20 \text{ MW/m}^2\text{K}$ 와 약  $50 \text{ MW/m}^2\text{K}$  사이, 약  $25 \text{ MW/m}^2\text{K}$ 와 약  $45 \text{ MW/m}^2\text{K}$  사이, 약  $25 \text{ MW/m}^2\text{K}$ 와 약  $40 \text{ MW/m}^2\text{K}$  사이, 또는 약  $25 \text{ MW/m}^2\text{K}$ 와 약  $30 \text{ MW/m}^2\text{K}$  사이의 열 전도도를 보인다. 본 명세서에서 기재하는 열적으로 관리된 전자 부품의 열 관리 코팅은 약  $30 \text{ MW/m}^2\text{K}$ 와 약  $50 \text{ MW/m}^2\text{K}$  사이의 열 전도도를 나타낸다. 또한, 어떤 경우에, 본 명세서에서 기재하는 열 관리 코팅은 수직(z) 방향과 반대로 코팅의 측방(X, Y) 평면 내에서 한 방향으로 본 명세서에서 기재하는 열 전도도를 나타낸다. 일부 구현예로서, 본 명세서에서 기재하는 열 관리 코팅은 임의의 방향으로 또는 측방 평면 내에서 복수의 방향으로 본 명세서에서 기재하는 열 전도도를 나타낸다. 또한, 본 명세서에서 기재하는 열 전도도는 본 발명의 목적과 모순되지 않는 임의의 방법으로 측정할 수 있다. 예를 들어, 일부 구현예로서, 열 전도도는 화력 리터 컨덕턴스 예컨대 리튬 등으로 기재한 것과 같은 펄스 광열 반사율(PPR: pulse photothermal reflectance) 기법에 의해 측정된다. 이것은 Li et al., "Heat Conduction across Multiwalled Carbon Nanotube/Graphene Hybrid Films," IEEE 2011 13<sup>th</sup> Electronics Packaging Technology Conference, pages 63-66에 기재되어 있다.

[0063] 또한, 일부 구현예로서, 본 명세서에서 기재하는 열적으로 관리된 전자 부품은 본 명세서에서 기재하는 특성의 조합을 나타낼 수 있다. 본 명세서에서 기재하는 열적으로 관리된 전자 부품은 본 발명의 목적에 모순되지 않는 속성과 특성의 어떤 조합을 보인다. 예를 들어, 일부 구현예로서, 열적으로 관리된 전자 부품은 다음과 같은 특성 중 하나 또는 그 이상을 갖는다.

[0064] (1) 적어도 약  $75 \text{ mJ/m}^2$  또는 적어도 약  $100 \text{ mJ/m}^2$ 의 접착 에너지를 가지는 그래핀 코팅층

[0065] (2) 약 30 원자층 이하 또는 약 10 원자층 이하의 그래핀 코팅층 두께

- [0066] (3) 열적으로 관리된 전자 부품의 총 중량에 대해 열적으로 관리된 전자 부품의 0.3중량% 이하를 가지는 열 관리 층 및

- [0067] (4) 약  $25 \text{ MW/m}^2\text{K}$  이상의 열 전도도를 갖는 열 관리 층.

- [0068] II. 열 관리 코팅을 도포하는 방법

- [0069] 또 다른 측면에서, 전자 부품에 대한 열 관리 코팅을 도포하는 방법이 본 명세서에서 설명된다. 일부 구현예로서, 열 관리 코팅을 도포하는 방법은, 전자 부품의 표면에 그래핀 코팅층을 배치하는 단계를 포함한다. 일부 구현예로서, 그래핀 코팅층은 배열된 탄소 나노 입자 층을 포함한다. 또한, 어떤 경우에서, 그래핀 코팅층 상에 배열된 탄소 나노 입자의 층을 추가로 배치하는 단계를 포함한다. 또한, 어떤 경우에, 본 명세서에서 기재하는 방법은 전자 부품의 표면에 절연 재료층을 배치하는 것을 추가로 포함하되 여기서, 전기 절연성 재료층은 표면과 그래핀 코팅층 사이에 배치된다.

- [0070] 방법의 특정 단계를 참조하면, 열 관리 코팅을 도포하는 방법은 전자 부품의 표면에 그래핀 코팅층을 배치하는 단계를 포함할 수 있다. 그래핀 코팅층은 본 발명의 목적에 모순되지 않는 임의의 방법으로 전자 부품의 표면에 배치될 수 있다. 일부 구현예로서, 예를 들어, 그래핀 층을 배치하는 것은 기상 증착법을 사용하여 수행된다. 증착은, 일부 구현예로서, 화학 기상 증착(CVD)을 포함한다. 예를 들어, 일부 구현예로서, CVD는 하나 이상의 그래핀 시트를 포함하는 그래핀 코팅층을 제공하기 위해 사용될 수 있다. 본 발명의 목적과 모순되지 않는 임의의 CVD 방법이 사용될 수 있다. 예를 들어, 일부 구현예로서, 대기압 CVD, 초고진공 CVD법, 열 필라멘트(또는 핫 와이어 또는 촉매) CVD가 사용될 수 있다. 일부 구현예로서, CVD 방법은 하나 이상의 탄소 함유 기체상 반응물로부터 그래핀 층을 배치하는 것을 포함한다. 일부 구현예로서, 기체상 반응물은 탄화수소를 포함한다. 일부 구현예로서, 기체상 반응물은 벤젠, 에탄, 메탄 또는 이들의 조합 또는 혼합물을 포함한다. 또한, 일부 구현예로서, 기체상 반응물은  $\text{H}_2$ 와 같은 담체 가스에 제공된다.

- [0071] 다른 구현예로서, 그래핀 코팅층의 배치는 촉매 기상 증착을 이용하여 수행된다. 예를 들어, 일부 구현예로서, 촉매 증착은 본 명세서에서 기재하는 수직 또는 실질적으로 수직 배향을 갖는 그래핀 튜브의 층을 포함하는 그래핀 코팅층을 제공하기 위해 사용될 수 있다. 본 발명의 목적과 모순되지 않는 임의의 촉매 기상 증착 방법이 사용될 수 있다. 일부 구현예로서, 촉매 기상 증착 방법은 전자 부품의 표면에 금속 촉매 입자를 배치하는 단계를 포함한다. 금속 촉매 입자는, 일부 구현예로서, 동일한 간격 입자들의 질서 있는 배열과 같이 일렬로 전자 부품에 배치될 수 있다. 또한, 금속 촉매 입자는 본 발명의 목적과 모순되지 않는 임의의 크기 및 화학적 조성을 가질 수 있다. 또한, 금속 촉매 입자의 크기는, 일부 구현예로서, 소망의 그래핀 튜브 직경을 얻기 위해 선택된다. 일부 구현예로서, 예컨대, 금속 촉매 입자는 약 1 nm 내지 약 20 nm 또는 약 nm 내지 약 10 nm의 범위의 평균 직경을 갖는다. 일부 구현예로서, 금속 촉매 입자는 약 1 nm 이하의 평균 직경을 갖는다. 또한, 일부 구현예로서, 금속 촉매 입자는 순금속, 금속 합금, 혹은 금속의 혼합물을 포함하는 하나 이상의 전이 금속을 포함한다. 일부 구현예로서, 금속 촉매 입자는 니켈, 코발트, 철, 또는 이들의 조합물을 포함한다. 다른 구현예에서, 금속 촉매 입자는 금 또는 은과 같은 귀금속을 포함한다.

- [0072] 또한, 일부 구현예로서는, 본 명세서에서 기재하는 촉매 기상 증착법은 진공실에 전자 부품을 배치하고, 전자 부품을 가열하는 것을 포함한다. 금속 촉매 입자의 층을 포함하는 전자 부품은, 본 발명의 목적과 모순되지 않는 임의의 온도로 진공실 내에서 가열될 수 있다. 일부 구현예로서, 전자 부품은 약  $600^\circ\text{C}$ 와 약  $800^\circ\text{C}$  사이의 온도로 가열된다. 일부 구현예로서, 전자 부품은 약  $700^\circ\text{C}$ 의 온도로 가열된다.

- [0073] 일부 구현예로서, 촉매 기상 증착 방법은 진공실 내로 하나 이상의 가스를 도입하는 것을 포함하며, 여기서, 적어도 하나의 가스는 탄소를 함유하는 종류를 포함한다. 일부 구현예로서, 아세틸렌 또는 에틸렌 등의 탄소를 함유하는 가스가 암모니아 또는 질소와 같은 공정 가스와 함께 도입된다. 이와 같이, 일부 구현예로서, 그래핀 튜브의 층은 전자 부품 상에 배치된 금속 촉매 입자에서 성장될 수 있다.

- [0074] 또한, 일부 구현예로서, 그래핀 층은 표면 상에 복수의 그래핀 플레이트랫을 배치하고, 하나 이상의 미세 와이어로 플레이트랫을 서로 연결하는 것에 의해 형성된다. 복수의 그래핀 플레이트랫은 미세 와이어 기술에 의한 연결에 모순이 없는 임의의 그래핀 형성 기술에 의해 형성될 수 있다. 예를 들어, 일부 구현예로서, 그래핀 플레이트랫은 조립식 그래핀 시트로 구성된다. 또한, 미세 와이어에 의한 그래핀 플레이트랫의 연결은, 본 발명의 목적과 모순되지 않는 임의의 미세 와이어 기술에 의해 수행될 수 있다.

- [0075] 일부 구현예로서, 복수의 그래핀 플레이트랫을 연결하는 것은 유전 영동법(dielectrophoretic method)에 의해

수행된다. 예를 들어, 표면 상에 배치된 그래핀 플레이트랫과 함께 전자 부품은 본 발명의 목적과 모순되지 않는 임의의 다양한 방식으로 전극들 사이의 거리에서 유전 영동을 실시할 수 있다. 일부 구현예로서, 예를 들어 전극 사이의 거리는 소망하는 미세 와이어의 길이에 따라 약  $1 \mu\text{m}$  내지 약  $1\text{cm}$  이상으로 다양할 수 있다. 전도성과 같은 특정한 속성에 대해 선택된 재료로 형성되는 나노 입자는 전극 위의 챔버 내로 도입될 수 있다. 일부 구현예로서, 나노 입자는 약  $15\text{ nm}$ 와 약  $30\text{ nm}$  사이의 직경을 갖는 금 나노 입자를 포함할 수 있다. 교류 전압이 이중 전기영동실로 적용될 수 있다. 일부 구현예로서, 약  $50\text{ V}$  내지 약  $250\text{ V}$ 의 교류 전압이 약  $50\text{ Hz}$  내지 약  $250\text{ Hz}$ 의 주파수와 함께 전극에 인가될 수 있다. 인가되는 교류 전압은 얇은 금속 섬유의 형성을 초래할 수 있다. 이러한 그래핀 플레이트랫과 같은 탄소를 함유하는 기판의 영역은 플레이트랫의 방향으로의 미세 와이어의 성장을 일으키고 두 전극에 플레이트랫을 연결하는 것과는 달리 균질한 기판 상에 섬(islands)를 형성할 수 있다. 일부 구현예로서, 미세 와이어는 Hermanson et al. "Dielectrophoretic Assembly of Electrically Functional Microwires from Nanoparticle Suspensions," *Science*, vol. 294 (5544), pages 1082-1086 (2001)에 기재된 유전 영동 조립공정에 의해서 형성될 수 있다.

[0076] 다른 구현에서는, 그래핀 층의 배치는 열적 침탄(thermal carburization)를 사용하여 수행된다. 본 발명의 목적과 모순되지 않는 임의의 열적 침탄법이 사용될 수 있다. 일부 구현예로서, 열적 침탄법은 초고전공 또는 불활성 분위기 하의 고온에서 SiC 또는 탄소강 기판 또는 부품과 같이 본 명세서에서 기재하는 탄소를 함유하는 기판 또는 전자 부품을 가열하는 것을 포함한다. 또한, 어떤 경우에는, 열적 침탄법은 탄소를 함유하는 분위기에서 고온으로 본 명세서에서 기재하는 기판이나 전자 부품을 가열하는 단계를 포함한다. 고온은, 어떤 경우에는 약  $1000\text{ }^\circ\text{C}$ 의 온도 이상의 온도를 포함한다. 일부 구현예로서, 고온은, 약  $800\text{ }^\circ\text{C}$  이상 또는  $900\text{ }^\circ\text{C}$  이상일 수 있다. 이론적으로 한정하는 것은 아니지만, 본 명세서에서 기재하는 열적 침탄법 중에 탄소가 풍부한 표면은 남고, 표면으로부터 비탄소 기판 원자는 탈착할 것으로 생각된다. 일부 구현예로서, 열적 침탄은 Van Bommel et al. "LEED and Auger electron observations of the SiC (0001) surface," *Surface Science*, 48(2), pages 463-472 (1975); 또는 Gullapalli et al. "Graphene Growth via Carburization of Stainless Steel and Application in Energy Storage," *Small*, 12, pages 1697-1700 (2011)에 기재된 방법에 따른 방식으로 수행될 수 있다.

[0077] 예를 들어, 일부 구현예로서, 그래핀 층의 배치는 탄소를 함유하는 기판 상에 전자 부분품을 배치한 후에 약  $1000\text{ }^\circ\text{C}$ 의 이상의 온도에서 상기 기판을 열처리하는 것을 포함할 수 있다. 온도와 시간의 증가에 따라, 기판과 전자 부분품에 대해 탄소가 풍부한 코팅은 남겨두고 기판에서의 비탄소 원자는 탈착할 수 있다. 일부 구현예로서, 탄소가 풍부한 코팅은 전자 부품에 배치된 그래핀 층이다. 또한, 일부 구현예로서는, 그래핀 층의 배치는 탄소를 함유하지 않는 기판 상에 전자 부품을 배치하는 것을 포함할 수 있다. 기판과 전자 부분품은 탄소가 풍부한 대기를 함유하는 고온 환경 하에서 배치할 수 있다. 일부 구현예로서, 고온은 약  $950\text{ }^\circ\text{C}$ 의 온도일 수 있다. 또한, 일부 구현예로서, 탄소가 풍부한 분위기는 헥산 또는 다른 탄화수소를 포함 할 수 있다. 이러한 구현에서, 그래핀 코팅층은 전자 부분품과 기판 위에서 형성 될 수 있다.

[0078] 다른 구현에서는, 그래핀 층의 배치는 전자 부품 상에 배치된 산화 흑연(GO)의 박막에 직접 레이저 묘화(laser writing) 또는 레이저 스크라이빙(laser scribing)을 사용하여 수행된다. 본 발명의 목적과 모순되지 않는 임의의 직접 레이저 묘화 또는 스크라이빙 방법이 사용될 수 있다. 일부 구현예로서, 직접 레이저 묘화 또는 스크라이빙 방법은, 고체 상태에서 그래핀 필름을 환원 및 패턴화하기 위해 주변 조건하에서 산화 흑연(GO) 필름의 직접 레이저 조사를 포함한다. 또한, 레이저 강도 및 레이저 조사 처리의 변경은 최종의 레이저 스크라이브 그래핀(LSG)의 전기적 특성을 전환시킬 수 있다. 또한, 레이저 강도(laser intensity), 레이저 주파수(laser frequency), 레이저 펄스 프로필(laser pulsing profile), 펄스 주파수(pulsing frequency), 펄스 둑티 사이클(pulsing duty cycle) 및/또는 산화흑연(GO) 필름의 두께를 변경함으로써, 그래핀 코팅층의 소망하는 두께를 얻을 수 있다. 일부 구현예로서, 직접 레이저 기록은 El-Kady & Kaner, "Scalable fabrication of high-power graphene micro-supercapacitors for flexible and on-chip energy storage," *Nature Communications*, 4, article number 1475, (February 12, 2013); 또는 Strong et al., "Patterning and Electronic Tuning of Laser Scribed Graphene for Flexible All-Carbon Devices," *ACS Nano*, 6(2), 1395-1403 (2012)에 게재된 방법에 부합하는 방식으로 수행할 수 있다.

[0079] 본 명세서에서 기재하는 방법에 의해 제공되는 그래핀 코팅층은 상기의 섹션 I에서 설명한 그래핀 코팅층의 어떤 속성을 가질 수 있다. 예를 들어, 일부 구현예로서, 본 명세서에서 기재하는 방법에 의해 제조된 그래핀 코팅층은 약  $300\text{ nm}$  이하의 두께를 갖는다. 또한, 본 명세서에서 기재하는 그래핀 코팅층의 두께는, 일부 구현예로서, 전자 부품에 코팅층의 중착시 하나 이상의 매개 변수를 변경하여 선택할 수 있다. 예를 들어, 일부 구

현예로서, 상기 코팅층의 두께는 증착 시간을 변경시켜서 선택되며, 여기서, 짧은 증착 시간은 보다 얇은 코팅층을 제공한다. 또한, 증착 시간은, 일부 구현예로서, 전자 부품 상에 배치된 재료의 질량을 결정하기 위해서 준비한 미량 천칭(microbalance)(수정 진동자 미량 천칭 등)에서 얻어진 정보를 이용하여 선택될 수 있다. 일부 구현예로서, 상기 정보는 미량 천칭의 출력에 관한 정보(예를 들면, 전자 부품의 측정된 질량 변경)를 화학 증착 시스템과 같은 증착 장치에 제공하여 피드백 루프(feedback loop)를 형성함으로써 실시간으로 얻어진다.

[0080] 전자 부품에 열 관리 코팅을 도포하는 방법은, 일부 구현예에서, 그래핀 코팅층 상에 배열된 탄소 나노 입자의 층을 배치하는 것을 추가로 포함한다. 배열된 탄소 나노 입자의 층은 본 발명의 목적과 모순되지 않는 임의의 방법으로 전자 부품의 표면 상에 배치될 수 있다. 일부 구현예로서, 예를 들면, 배열된 탄소 나노 입자의 층의 배치는 상기에서 설명한 CVD 법 등의 증착을 이용하여 수행된다. 또한, 배열된 탄소 나노 입자의 층은 배열된 탄소 나노 입자의 층에 대해 상기의 섹션 I에서 설명한 구조 및/또는 특징을 가질 수 있다.

[0081] 어떤 경우에는 배열된 탄소 나노 입자의 층은 하나 이상의 그래핀 시트를 포함하는 그래핀 코팅층의 표면 상에 형성된다. 이러한 일부 구현예로서, 촉매 필름 또는 촉매 입자의 층은 그래핀 코팅층 상에 배열된 탄소 나노 입자의 층을 형성하기 전에 그래핀 코팅층 상에 증착된다. 그 다음에 촉매 필름 또는 촉매 입자의 층은 복수의 배열된 그래핀 튜브를 포함하는 그래핀 코팅층에 대해 상기에서 설명한 바와 같이 탄소 나노 입자를 성장시키는데 사용될 수 있다. 따라서, 어떤 경우에, 본 명세서에서 기재하는 방법에 따라 배열된 탄소 나노 입자의 층을 배치하는 것은 촉매 필름 또는 입자로부터 탄소 나노 입자를 성장시키는 단계를 포함한다.

[0082] 또한, 일부 구현예에서, 자기장 및/또는 전기장이 배열된 탄소 나노 입자의 성장시 전자 부품에 적용할 수 있다. 자기장 및/또는 전기장은 임의의 강도 및/또는 주파수를 가질 수 있고, 본 발명의 목적과 모순되지 않는 임의의 방법으로 도포될 수 있다. 어떤 경우에, 전기장은 직류(DC) 전기장이다. 다른 예에서, 전기장은 교류 전류(AC) 전기장이다. 예를 들어, 일부 구현예로서, 인가되는 DC 전기장은 일정(DC) 장파 관련된 주파수가 없도록(하고, 성장 표면에 대해 인가된 전압을 거리로 나눈 크기를 갖는다. 인가된 전압은, 어떤 경우에, 약 1 볼트(V)와 약 100 V 사이의 범위이고, 거리는 약 1 cm와 약 10 cm 사이의 범위이다. 따라서, 일부 구현예에서, DC 전기장의 크기는 약 1 V/cm와 100 V/cm 사이의 범위 일 수 있다.

[0083] 본 명세서에서 기재하는 전기장의 인가는, 어떤 경우에는, 상기에서 설명한 대칭, 비대칭, 오른쪽 또는 왼쪽 구조와 같은 소망하는 구조를 가지는 층을 제공할 수 있다. 일부 구현예로서, 예를 들면, 비대칭 구조를 가지는 층은 배열된 탄소 나노 입자를 형성하는데 사용되는 탄소를 함유하는 가스의 플라즈마 주파수보다 높은 주파수를 갖는 AC 전기장을 인가하여 CVD 공정에서 형성할 수 있다. 예를 들어, 일부 구현예에서, 인가된 AC 전기장은 약  $10^{15}$  Hz와 약  $10^{17}$  Hz 사이의 주파수와 성장 표면에 대해 인가된 전압을 거리로 나눈 것으로 정의되는 크기를 갖는다. 인가된 전압은, 어떤 경우에, 약 1 V 내지 약 100 V, 그리고 거리 사이의 범위는 약 1 cm 내지 약 100 cm 사이의 범위. 따라서, 일부 구현에서, AC 전기장의 크기가 약 1 V/cm 내지 100 V/cm 사이의 범위 일 수 있다.

[0084] 다른 예시적인 구현예에서, 오른쪽 또는 왼쪽 구조를 갖는 층은 배열된 탄소 나노 입자의 성장시 본 명세서에서 기재하는 DC 전기장 및 자기장 모두를 적용하여 CVD 공정에서 형성될 수 있다. 어떤 경우에, 자기장은 오른쪽 구조를 갖는 층을 제공하기 위해 인가된 전기장과 평행하게 인가된다. 다른 경우에, 자기장은 왼쪽 구조를 갖는 층을 제공하기 위해 인가된 전기장과 평행하지 않게 인가된다. 어떤 경우에, 인가된 자기장은 약 1 Gauss(G) 및 약 100 G 사이의 크기를 가질 수 있다.

[0085] 또한, 어떤 경우에, 본 명세서에서 기재하는 방법은 전자 부품의 표면에 전기 절연성 재료의 층을 증착하는 것을 포함하며, 여기서, 절연 재료층은 표면과 그래핀 코팅층 사이에 위치한다. 전기 절연성 재료층은 본 발명의 목적과 모순되지 않는 임의의 방법으로 전자 부품의 표면 상에 배치될 수 있다. 어떤 경우에는, 예를 들면, 전기 절연층은 딥 코팅(dip coating) 또는 스프레이 코팅(spray coating)에 의해 형성된다. 또한, 본 명세서에서 기재하는 방법에 의해 제공되는 절연 재료층은 상기의 섹션 I에서 설명한 절연 재료층의 어떤 속성을 가질 수 있다.

[0086] 본 명세서에서 기재하는 일부 구현예는 제한하고자 하는 것이 아닌 다음의 실시예에서 추가로 예시하기로 한다.

[0087] 실시예 1

[0088] 열적으로 관리된 전자 부품

[0089] 열적으로 관리된 전자 부품이 다음과 같이 제조한다. CVD 챔버 내에 전자 부품을 배치하고, CVD 증착 조건에 전자 부품을 노출시켜서 편평한 그래핀 시트를 포함하는 그래핀 코팅층을 세정된 전자 부품의 표면에 인가한다. 구체적으로, 대략 101 Torr의 전체 압력에서, 약 100 Torr의 분압 벤젠, 에탄, 메탄의 분위기 및 1 Torr의 분압  $H_2$  하에서 대략 100분 동안 500 °C에서 증착을 수행한다. 얻어진 그래핀 코팅층의 두께는 대략 100 nm 이다. 상기에서 설명한 바와 같이, 보다 얇은 그래핀 코팅층이 증착 시간을 단축시켜서 얻을 수 있고, 두꺼운 그래핀 코팅층은 증착 시간을 늘려서 얻을 수 있다. 또한, 증착 시간은, 상기에서 설명한 바와 같이, 챔버 내에 배치되어 있고 전자 부품 상에 증착된 재료의 질량을 결정하기 위하여 배열되어 있는 미량 천칭으로부터 얻어진 정보를 사용하여 선택할 수 있다.

[0090] 그래핀 코팅층을 배치한 후, 65 nm의 나켈 필름을 측면으로 그래핀 코팅층 상에 배치한다. 플라즈마 강화 CVD(PECVD)를 성장 촉진용 플라즈마 증강제로서 탄소원 및 암모니아로서 아세틸렌을 사용하여 수행한다. 구체적으로, 증착은 표 1에 열거된 성장 조건에서 수행한다(여기서, SCCM은 분당 표준 입방 센티미터를 말하며, A는 암페어이고, V는 전압을 의미하며, W는 와트를 말한다). 얻어진 배열된 탄소 나노 튜브의 층은 대칭 구조를 갖는다.

표 1

| 온도 범위(°C) | $C_2H_2$<br>(SCCM) | $NH_3$<br>(SCCM) | 필라멘트 전류<br>(A) | 플라즈마 강도<br>(A/V/W) | 성장 시간<br>(분) |

|-----------|--------------------|------------------|----------------|--------------------|--------------|

| 600~800   | 40                 | 160              | 7.2            | 0.13/650/90        | 14           |

[0091] 실시예 2

[0092] 열적으로 관리된 전자 부품

[0093] 열적으로 관리된 전자 부품은 다음과 같이 제조한다. 그래핀 코팅층은 실시예 1에 설정한 방법에 의해 전자 부품 상에 배치한다. 배열된 탄소 나노 입자층은 배열된 탄소 나노 입자층의 성장시 약 100 V/cm의 크기를 갖는 DC 전기장을 추가하여, 실시예 1에 설정한 방법에 따라 배치한다. 얻어진 배열된 탄소 나노 입자의 층은 대칭 구조를 갖는다.

[0094] 실시예 3

[0095] 열적으로 관리된 전자 부품

[0096] 열적으로 관리된 전자 부품은 다음과 같이 제조한다. 그래핀 코팅층은 실시예 1에 설정한 방법에 의해 전자 부품 상에 배치한다. 배열된 탄소 나노 입자층은 배열된 탄소 나노 입자층의 성장시 약 1015 Hz의 주파수와 약 100 V/cm의 크기를 갖는 AC 전기장을 추가하여, 실시예 1에 설정한 방법에 따라 배치한다. 얻어진 배열된 탄소 나노 입자의 층은 대칭 구조를 갖는다.

[0097] 실시예 3

[0098] 열적으로 관리된 전자 부품

[0099] 열적으로 관리된 전자 부품은 다음과 같이 제조한다. 그래핀 코팅층은 실시예 1에 설정한 방법에 의해 전자 부품 상에 배치한다. 배열된 탄소 나노 입자층은 배열된 탄소 나노 입자층의 성장시 약 1015 Hz의 주파수와 약 100 V/cm의 크기를 갖는 AC 전기장을 추가하여, 실시예 1에 설정한 방법에 따라 배치한다. 얻어진 배열된 탄소 나노 입자의 층은 대칭 구조를 갖는다.

[0100] 실시예 4

[0101] 열적으로 관리된 전자 부품

[0102] 열적으로 관리된 전자 부품은 다음과 같이 제조한다. 그래핀 코팅층은 실시예 1에 설정한 방법에 의해 전자 부품 상에 배치한다. 배열된 탄소 나노 입자층은 DC 전기장에 평행한 자기장을 추가하여 실시예 2에 설정한 방법에 따라 배치한 결과 나노 재료 성장에 순수 키랄성과 오른쪽 구조를 가지는 탄소 나노 튜브의 층으로 인도한다. 자기장은 약 100 G의 크기를 갖는다.

[0103] 실시예 5

[0105] 열적으로 관리된 전자 부품

[0106] 열적으로 관리된 전자 부품은 다음과 같이 제조한다. 그래핀 코팅층은 실시예 1에 설정한 방법에 의해 전자 부품 상에 배치한다. 배열된 탄소 나노 입자층은 인가된 전기장에 평행하지 않게 자기장을 배열하는 변형을 주어 실시예 4에 설정한 방법에 따라 배치한다. 이러한 방식에서 왼쪽 구조를 가지는 층이 제공된다.

[0107] 본 개시의 다양한 구현예들은 본 발명의 다양한 목적의 달성을 위해 기재한 것이다. 이들 구현예는 본 발명의 원리를 단지 예시한 것으로 인식되어야 한다. 다양한 변형 및 이의 개조들은 본 발명의 사상 및 범위를 벗어남이 없이 당업자에게 명백할 것이다.

### 부호의 설명

[0108] 100,200,300: 열적으로 관리된 전자 부품

110,210,310: 전자 부품

112,212,312: 표면

120,220,320: 열 관리 코팅

130,230,330: 그래핀 코팅층

132: 그래핀 시트

232,332: 그래핀 튜브

### 도면

#### 도면1

#### 도면2

도면3

도면4