(19)

österreichisches

patentamt

(10)

AT 500 259 B1 2007-08-15

(12)

# Patentschrift

(21) Anmeldenummer: A 894/2004

(51) Int. Cl.<sup>8</sup>: H05K 3/40 (2006.01)

(22) Anmeldetag: 2004-05-24

H05K 01/16 (2006.01)

(43) Veröffentlicht am: 2007-08-15

H05K 03/24 (2006.01)

H01L 27/15 (2006.01)

H05B 33/12 (2006.01)

(30) Priorität:

09.09.2003 AT A 1415/03 beansprucht.

(56) Entgegenhaltungen:

US 4827328A US 4839558A

WO 97/03460A1 EP 0854662A2

DE 19715658A1 EP 1087649A2

US 2002/039000A1

(73) Patentanmelder:

AT & S AUSTRIA TECHNOLOGIE &

SYSTEMTECHNIK

AKTIENGESELLSCHAFT

A-8700 LEOBEN-HINTERBERG (AT)

## (54) DÜNNSCHICHTANORDNUNG UND VERFAHREN ZUM HERSTELLEN EINER SOLCHEN DÜNNSCHICHTANORDNUNG

(57) Dünnsschichtanordnung (1) mit einem Substrat (2) und zumindest einem auf dem Substrat in Dünnsschichttechnik aufgebrachten elektronischen Dünnsschichtbauelement (8), wobei auf dem Substrat eine Grundelektrode (4) vorliegt, auf der zum Dünnsschichtbauelement (8) gehörige Dünnsschichten einschließlich einer oberen Deckelektrode (9) angeordnet sind; das Substrat (2) ist durch eine an sich bekannte Leiterplatte mit einem Isoliermaterial-Grundkörper (3) und einer Metallkaschierung als Leiterschicht (5) gebildet, wobei die Leiterschicht (5) die Grundelektrode (4) bildet und hierfür zumindest an der Stelle des Dünnsschichtbauelements (8) geglättet ist, und wobei zwischen der geglätteten, gegebenenfalls verstärkten Leiterschicht (5) und den darüber liegenden Dünnsschichten des Dünnsschichtbauelements (8) eine Kontaktsschicht (18) in Dünnsschichttechnik vorgesehen ist, welche auf der Oberfläche der Grundelektrode (4) physikalisch bzw. chemisch adsorbiert ist.

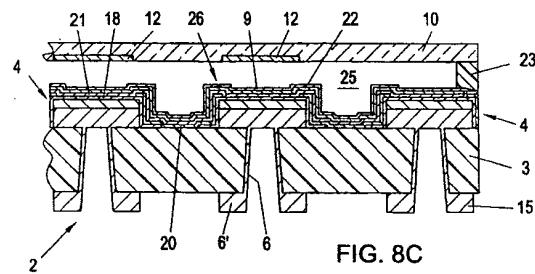

FIG. 8C

Die Erfindung betrifft eine Dünnschichtanordnung mit einem Substrat und zumindest einem auf dem Substrat in Dünnschichttechnik aufgebrachten elektronischen Dünnschichtbauelement, wobei auf dem Substrat eine Grundelektrode vorliegt, auf der zum Dünnschichtbauelement gehörigen Dünnschichten einschließlich einer oberen Deckelektrode angeordnet sind.

- 5 In entsprechender Weise bezieht sich die Erfindung auf ein Verfahren zum Herstellen einer Dünnschichtanordnung mit wenigstens einem elektronischen Dünnschichtbauelement, das in Dünnschichttechnik auf einem Substrat aufgebracht wird.

- 10 Aus der US 4 839 558 A ist eine Anordnung mit Elektrolumineszenz-Elementen auf einem Substrat bekannt, welches als Leiterplatte vorliegen und andere Elektronikkomponenten tragen kann. Die bekannte Elektrolumineszenz-Anordnung ist dabei als Dickschichtstruktur auf dem Substrat aufgebracht, wobei die elektrolumineszierende Schicht auf nach einem Ätzen verbleibenden Kupferkaschierungs-Grundelektroden aufgedruckt wird. Darüber wird eine durchsichtige

- 15 Abdeckung aus Glas mit einer inneren Zinnoxidschicht als Elektrode mit Hilfe eines Adhäsivs angebracht. Eine derartige Struktur hat nicht nur den Nachteil von vergleichsweise großen Abmessungen, insbesondere in Dickenrichtung, sondern auch jenen einer aufwendigen Herstellung.

- 20 Aus der EP 1 087 649 A ist es andererseits bekannt, eine Elektrolumineszenz-Anordnung in Dünnschichttechnik auf einem Substrat und innerhalb einer Verkapselung anzubringen, wobei als aktive Schicht für die Elektrolumineszenz insbesondere eine organische (oder aber auch anorganische) Licht emittierende Schicht angebracht wird. Unterhalb hiervon wird auf dem Substrat eine Grundelektrode beispielsweise durch Niederschlägen aus der Dampfphase angebracht, und über der Licht emittierenden Schicht wird in ähnlicher Weise ein leitendes Material aus der Dampfphase niedergeschlagen, um eine Deckelektrode zu bilden. In Hinblick auf eine matrixartige Anordnung von Elektrolumineszenz-Elementen, für ein Display, werden die Deckelektroden dabei in Zeilenform und die Grundelektroden in Spaltenform angebracht, wogegen die aktiven Elektrolumineszenz-Elemente „punktweise“ vorliegen. In Hinblick auf die Dünnschichttechnik, die hier zur Realisierung der Elektrolumineszenz-Anordnung angewandt wird, wird ein Glassubstrat verwendet, welches mit einer ausreichend glatten Oberfläche vorliegen kann, um die einzelnen Dünnschichten problemlos anbringen zu können, wobei überdies auch die erforderliche Inert-Eigenschaft gegeben ist, d.h. aus dem Glasmaterial diffundieren keine Substanzen in den jeweiligen Dünnschichtaufbau. Ein derartiges Glassubstrat hat jedoch den

- 25 Nachteil, dass es verhältnismäßig aufwendig und teuer in der Herstellung ist, und dass es sich weniger gut zur Montage weiterer elektronischer Bauelemente, insbesondere im Zuge einer miniaturisierten Schaltungsanordnung, eignet.

- 30 Andererseits ist eine klassische Leiterplatte mit einer metallischen Kaschierung, insbesondere

- 35 Kupferkaschierung, auf einem isolierenden bzw. dielektrischen Grundkörper nicht mit Dünnschichttechniken kompatibel.

- 40 Es ist nun Aufgabe der Erfindung, hier Abhilfe zu schaffen und eine Technik vorzusehen, mit der in einfacher und preiswerter Weise Dünnschichtanordnungen ermöglicht werden, ohne dass

- 45 für diese aufwendige Substrate aus Glas benötigt werden. Insbesondere wird mit der Erfindung angestrebt, an sich herkömmliche Leiterplatten einsetzen zu können und in diesen direkt die gewünschten elektronischen Dünnschichtbauelemente, wie insbesondere Elektrolumineszenz-Anordnungen, aber auch andere elektronische Bauelemente, zu integrieren, wobei selbstverständlich zusätzlich auch eine Bestückung mit elektrischen Bauelementen in herkömmlicher

- 50 Weise möglich sein soll.

- 55 Die erfindungsgemäße Dünnschichtanordnung der eingangs angeführten Art ist dadurch gekennzeichnet, dass das Substrat durch eine an sich bekannte Leiterplatte mit einem Isoliermaterial-Grundkörper und einer Metallkaschierung als Leiterschicht gebildet ist, dass die Leiterschicht die Grundelektrode bildet und hierfür zumindest an der Stelle des Dünnschichtbauele-

ments geglättet ist, und dass zwischen der geglätteten, gegebenenfalls verstärkten Leiterschicht und den darüber liegenden Dünnschichten des Dünnschichtbauelements eine Kontaktsschicht in Dünnschichttechnik vorgesehen ist, welche auf der Oberfläche der Grundelektrode physikalisch bzw. chemisch adsorbiert ist.

5 Gemäß der Erfindung wird somit eine herkömmliche Leiterplatte „konditioniert“, um sie mit Dünnschichtsystemen kompatibel zu gestalten. Dabei wird zur Bildung der Grundelektrode die Leiterschicht, also die Metallkaschierung der Leiterplatte, geglättet bzw. poliert, um so eine Basis für einen Dünnschichtaufbau zu schaffen. Die so erhaltene Grundelektrode kann im Bedarfsfall noch chemisch bzw. elektrochemisch verstärkt werden, wobei dann die angesprochene Glättung der Oberfläche der Grundelektrode nach Anbringung einer solchen Verstärkung erfolgt. Die Glättung führt dabei insbesondere zu einer mittleren Oberflächenrauigkeit von maximal 10 nm, bevorzugt maximal 3 nm, wobei sich die entsprechende Rauigkeitsbestimmung auf technologisch relevante Flächen der Größe  $20 \times 20 \mu\text{m}^2$  (Mikrorauigkeit) beschränkt. Unebenheiten größerer lateraler Ausdehnung (Makrorauigkeit) sind in Dünnschicht-technologischer Hinsicht irrelevant. Auf der so erhaltenen mikroskopisch glatten Oberfläche der Grundelektrode ist dann eine Kontaktsschicht vorhanden, die bevorzugt metallisch ist, aber auch eine sonstige anorganische oder organische chemische Schicht oder auch Halbleiterschicht sein kann, und die insbesondere mehrere Funktionen erfüllen kann: Zum Einen dient diese Kontaktsschicht zur 10 Passivierung der Metallkaschierung (Grundelektrode), so dass keine Substanzen aus der Metallkaschierung in den darüber befindlichen Dünnschichtaufbau, z.B. mit organischen Elektrolumineszenzschichten, diffundieren können. Insbesondere ist die Kontaktsschicht zum Anderen eine Kontakt-“Vermittlungs“-Schicht, die den elektrischen Kontakt zwischen den aktiven oder 15 passiven Dünnschichten des Dünnschichtbauelements und der Grundelektrode verbessert und stabilisiert. Weiters ist diese Kontaktsschicht auch eine Haftverbesserungsschicht, die die Haf- 20 tung der Dünnschichtstruktur auf der Grundelektrode stabilisiert und so eine Langzeit-Haftung sicherstellt. Die jeweilige Kontaktsschicht ist naturgemäß abhängig vom jeweils zu integrierenden Dünnschichtbauelement zu wählen, und sie wird im Allgemeinen fotolithografisch strukturiert und mittels üblicher Dünnschichtverfahren, also durch thermisches Verdampfen, durch Kaltka- 25 todenbeschichtung, durch Schleuderbeschichtung usw., aufgebracht. Die Kontaktsschicht besteht beispielsweise aus einem Metall, wie insbesondere aus Aluminium, Gold, Palladium oder Platin etc., es können jedoch zur Bildung der Kontaktsschicht auch leitfähige Suspensionen und Lösungen, z.B. Polyanilin, Polyethylen-Dioxithiophen/Polystyrolsulfonsäure usw., eingesetzt 30 werden. Durch die Glättung der die Grundelektrode bildenden Leiterschicht sowie die Anbrin- 35 gung der Kontaktsschicht wird eine gute Adhäsion der jeweiligen Dünnschichtstruktur sowie ein adäquater elektrischer Kontakt gesichert, so dass es möglich ist, Dünnschichtstrukturen an herkömmlichen Leiterplatten mit dielektrischem Grundkörper und Metallkaschierung zu integrieren. Die Leiterplatten können dabei, wie derzeit zumeist im Einsatz, aus einem Epoxidharz- 40 Grundkörper mit einer doppelseitigen Kupferkaschierung bestehen. Die Kupferkaschierung oder allgemein Metallkaschierung ist an sich vergleichsweise dick und kann mit Vorteil auch als Kühlelement für die jeweilige Dünnschichtstruktur dienen; für diese Kühlfunktion kann die Kupferkaschierung auch entsprechend dick gewählt (oder verstärkt) werden. Es ist aber selbstverständ- 45 lich auch möglich, flexible Leiterplatten, auch „Leiterbahnenfolien“ genannt, zu verwenden, die z.B. einen Isoliermaterial-Grundkörper aus Polyimid, Polyethylennaphthalat oder Polyester aufweisen, wobei wiederum eine Metallkaschierung, z.B. aus Kupfer, als Leiterschicht vorgesehen sein kann.

Es sei erwähnt, dass der vorerwähnte Begriff „elektronisch“ hier in einem breiten Sinn zu verstehen ist und insbesondere auch elektro-optische Systeme bzw. Schichten mit umfassen soll, wie insbesondere Elektrolumineszenz-Anordnungen, wie sie an sich bekannt sind, vgl. außer den beiden eingangs erwähnten Dokumenten US 4 839 558 A und EP 1 087 649 A auch die EP 0 854 662 A. In vergleichbarer Weise sind als „elektronische“ Dünnschichtbauelemente mit der erfindungsgemäßen Technik aber auch beispielsweise Solarzellen, Sensoren, und zwar insbesondere optische Sensoren, aber auch Temperatursensoren und dgl., und weiters derartige elektronische Bauelemente wie Dioden, Transistoren, Feldeffekttransistoren, Leuchtdioden,

Widerstände, Kondensatoren und Schutzelemente (z.B. Überspannungsschutzelemente) denkbar. Diese Dünnschichtbauelemente können jeweils wie an sich bekannt durch eine Verkapselung gegen Umgebungseinflüsse geschützt sein, wobei es weiters insbesondere auch möglich ist, innerhalb der Verkapselung, die ein freies, mit Gas gefülltes Volumen umschließt, Gettermaterialien einzubauen, die Sauerstoff und/oder Wasser im Gasvolumen aufnehmen und so das Dünnschichtbauelement gegen unerwünschte chemische Prozesse schützen. Im Falle einer Elektrolumineszenz-Anordnung oder einer photovoltaischen-Anordnung, aber auch eines optischen Sensors als Dünnschichtbauelement, ist die Verkapselung durchscheinend oder durchsichtig ausgebildet, ebenso wie die Deckelektrode und eine gegebenenfalls unter dieser vorhandene eigene Kontaktsschicht, die wieder - zusätzlich - zur Kontaktvermittlung, Stabilisierung und Passivierung vorgesehen sein kann.

Im Fall einer Elektrolumineszenz-Anordnung kann die Verkapselung in an sich bekannter Weise mit Farbwandler- bzw. Indexanpassungsschichten ausgerüstet sein, die zu den lokalen Grundelektroden bzw. lokalen Dünnschichtbauelementen ausgerichtet sind.

In Hinblick auf den erfindungsgemäß in vorteilhafter Weise ermöglichten Einsatz einer herkömmlichen Leiterplatte als Substrat und die damit gegebenen Möglichkeiten für das Vorsehen der verschiedensten Muster von lokalen Grundelektroden ist es im Fall einer Elektrolumineszenz-Vorrichtung als Dünnschichtbauelement-System von besonderem Vorteil, wenn lokale Grundelektroden, die individuelle Durchkontaktierungen haben, innerhalb einer isolierenden Gitterstruktur auf der Leiterplatte vorliegen und darüber ein flächiges Elektrolumineszenz-Dünnschichtsystem sowie eine flächige oder aber streifen- oder symbolweise strukturierte Deckelektrode angebracht sind. Bei einer solchen Ausbildung kann die jeweilige Dünnschichtstruktur samt Deckelektrode in besonders einfacher Weise integriert werden, ohne dabei an Steuerungsmöglichkeiten für die einzelnen Elektrolumineszenz-Elemente einzubüßen.

Ein weiterer Vorteil der Verwendung einer herkömmlichen Leiterplatte besteht auch darin, dass zur Kontaktierung der Elektroden durch den Leiterplatten-Grundkörper hindurch an sich bekannte sog. Via-Verbindungen vorgesehen werden können. Diese Durchkontaktierungen, insbesondere lasergebohrte Durchkontaktierungen, ergeben wegen ihrer engen, miniaturisierten Anbringung die Möglichkeit einer Integration von Bauelementen, insbesondere optoelektronischen Bauelementen, mit besonders hoher Dichte, so dass beispielsweise Anzeigesysteme mit einer Vielzahl von kleinen, nahe aneinander angebrachten Bildpunkten, d.h. hoch auflösende Anzeigesysteme, erzielt werden können. Denkbar sind aber auch Durchkontaktierungen auf Basis mechanischer Bohrungen oder Plasma-geätzte Verbindungen. Mit Vorteil sind die Durchkontaktierungen zum Anschluss der Grundelektroden direkt unter diesen Grundelektroden vorgesehen; man spricht in diesem Fall von einer sog. Via-In-Electrode(VIE)-Struktur. Es ist aber auch möglich und im Hinblick auf die Kontaktierung der Deckelektroden üblich, Durchkontakteierungen versetzt zu den zugehörigen Elektroden zu positionieren, wobei dann eine horizontale elektrische Verbindung von einem Via-Pad an der Oberseite der Leiterplatte zum Bauelement herzustellen ist. Eine derartige Struktur wird Via-Off-Electrode(VOE)-Struktur genannt.

Bei Anbringung mehrerer Dünnschichtbauelemente auf der Leiterplatte, wie dies in der Regel der Fall sein wird, sind die Bereiche auf der Metallkaschierung der Leiterplatte zwischen den Dünnschichtbauelementen zu entfernen, wobei auch eine zusätzliche Isolierung, beispielsweise aus einem Fotolack, hergestellt und in einem Fotolithografieverfahren lateral strukturiert angebracht wird. Diese Isolierungen umschließen die einzelnen Dünnschichtbauelemente einschließlich ihrer Grundelektroden und isolieren sie so gegeneinander. Dabei ist es auch hier vor Anbringung der Isolierungen zweckmäßig, die von der Metallkaschierung bzw. Leiterschicht freigelegten Bereiche der Leiterplatte durch eine Passivierungsschicht, die mit Hilfe einer herkömmlichen Dünnschichttechnik angebracht wird, zu „verschließen“ und so eine Kontamination des jeweiligen Dünnschichtbauelements durch aus dem Grundkörper der Leiterplatte austretende Substanzen zu verhindern. Diese Passivierungsschicht kann beispielsweise aus Siliziumoxid, aus einem Sol-Gel-System oder einer Epoxidverbindung bestehen. Auch hier ist selbst-

verständlich die jeweilige Passivierungsschicht wieder in Abhängigkeit von der Art der übrigen Materialien, insbesondere des Materials des Grundkörpers der Leiterplatte, auszuwählen, und die Passivierungsschicht wird in der Regel fotolithografisch strukturiert und mittels üblicher Dünnschichtverfahren, wie etwa durch thermisches Verdampfen, durch Schleuderbeschichtung,

5 durch Tintendruckprozesse oder durch Kaltkatodenbeschichtung etc., aufgebracht. Anstatt einer solchen strukturierten, lokalen Aufbringung ist aber auch eine zunächst vollflächige, gleichförmige Aufbringung einer Passivierungsschicht, etwa als Laminat, denkbar, wobei nachträglich eine Strukturierung mit Hilfe fotolithografischer Ätztechniken durchgeführt wird.

10 Wie vorstehend erwähnt ist ein wesentliches Merkmal für die Einsatzmöglichkeit von herkömmlichen Leiterplatten bei den vorliegenden Dünnschichtanordnungen darin zu sehen, dass die Leiterschicht bzw. lokale Grundelektroden, die aus dieser Leiterschicht durch Strukturieren erhalten wurden, zwecks Erzielung einer geringen Oberflächenrauigkeit geglättet werden. Dieses Glätten kann auf vielfältige, an sich übliche Weisen realisiert werden, wobei mechanische, 15 aber auch elektrochemische, chemische und chemisch-mechanische Glättungsverfahren und/oder ein Polieren durch Ionenätzten sowie eine Kombination dieser Verfahren möglich sind. Insbesondere ist es hier denkbar, dass die Leiterschicht durch chemisches Ätzen, beispielsweise mit Schwefelsäure, Salpetersäure oder Chromschwefelsäure, geglättet wird. Andererseits ist es auch vorteilhaft, wenn die Leiterschicht durch Beschuss mit Partikeln einzelner oder mehrerer Atome oder Moleküle, wie z.B. Argon oder Argon-Cluster, geglättet wird.

20 Im Fall der Anbringung einer Verstärkung der lokalen Grundelektroden ist es weiters zweckmäßig, die Leiterplatte zuvor in den übrigen Bereichen vorübergehend fotolithografisch zu passivieren. Die hierfür angebrachte Passivierungsschicht wird nachfolgend, noch vor Anbringen der jeweiligen Dünnschichtbauelemente, insbesondere noch vor Anbringen der Kontaktsschichten, 25 wieder entfernt.

Im Falle einer Strukturierung der Leiterschicht zur Bildung lokaler Grundelektroden ist es im Übrigen auch denkbar, eine Glättung der Leiterschicht noch vor der (insbesondere fotolithografischen) Strukturierung der Leiterschicht durchzuführen.

30 Wie bereits vorstehend erwähnt können im Rahmen der erfindungsgemäßen Technik nicht nur starre Leiterplatten, sondern auch flexible Leiterplatten Anwendung finden. Derzeit werden solche flexible Leiterplatten beispielsweise als mechanisch robuste und platzsparende Verbindungstechnik in vielfältiger Form, etwa als „Flachbandkabel-Ersatz“, eingesetzt, wobei sie nicht nur bewegliche Verbindungen zwischen einzelnen elektrischen Komponenten eines Geräts ermöglichen, sondern auch durch Biegen, Falten und Verwinden eine optimierte Anordnung der Leiterplatte im zur Verfügung stehenden Innenraum eines Gehäuses erlauben. Die Integration von Dünnschichtbauelementen auf derartigen flexiblen Leiterplatten gemäß der hier beschriebenen Technik bietet nun die Möglichkeit, den flexiblen Bereich durch Integration passiver bzw. aktiver Dünnschichtbauelement zu nutzen, ohne dass dies zu einer Versteifung der Leiterplatte - wie etwa im Fall von konventionellen starren, dicken Bauelementen - führen würde. Damit können bewegliche, biegsame und mechanisch robuste Komponenten realisiert werden, und die Leiterplatte wird so wie das Dünnschichtbauelement selbst aufgrund des geringen Volumens und der geringen Masse der Dünnschichtkomponenten im Fall einer mechanischen Belastung in einem wesentlich geringeren Maße beansprucht. Der Einsatz von flexiblen Leiterplatten und in der Folge von flexiblen Dünnschichtanordnungen ist für viele Anwendungen denkbar, wie etwa bei mechanisch besonders belastbaren elastischen Elektronikkomponenten, die Erschütterungen, Beschleunigungen usw. ausgesetzt sind, bei Bauelementen, deren Flexibilität Teil ihrer Funktionalität ist, wie etwa im Fall von Tastaturen oder Sensoren, bei „bestückten“ faltbaren Leiterplatten bis hin zu biegsamen oder gar aufrollbaren Bildschirmen.

40 Auch im Fall von derartigen flexiblen Leiterplatten wird wie vorstehend ausgeführt die Leiterschicht „konditioniert“, um sie mit dem jeweiligen Dünnschichtsystem kompatibel zu machen. Es wird also die Leiterschicht, welche die Grundelektrode des Dünnschichtbauelements bildet,

geglättet bzw. poliert und gegebenenfalls verstärkt; weiters wird die Grundelektrode mit einer Bauelement-adäquaten Kontaktsschicht versehen, welche mit Hilfe eines üblichen Dünnschichtverfahrens, also beispielsweise durch thermisches Verdampfen, durch Kaltkathodenbeschichtung, durch Schleuderbeschichtung usw., aufgebracht werden kann. Grundsätzlich sind im Übrigen sämtliche Dünnschichtverfahren in hervorragender Weise geeignet, flexible Substrate zu beschichten und dabei flexible Strukturen zu bilden, wobei gegebenenfalls Adaptionen im Verfahrensablauf, vor allen Dingen für den Transport der Substrate zwischen einzelnen Prozessstationen, vorzusehen sind. Es bedarf somit keiner Modifikation des Aufbaus des jeweiligen Dünnschichtbauelements, wenn anstatt einer starren Leiterplatte eine flexible Leiterplatte zum Einsatz kommt, und gerade Dünnschichttechniken erlauben eine Ausweitung des Anwendungsspektrums zufolge der Verwendung von flexiblen Leiterplatten bis hin zu aktiven flexiblen Flächengebilden, wobei insgesamt flexible und ultraleichte Dünnschichtanordnungen mit geringsten Ausdehnungen der Bauelemente hergestellt werden können, die starken mechanischen Beanspruchungen, wie Erschütterungen und hohe Beschleunigungen bzw. Verzögerungen, im Weitaus höherem Maß gewachsen sind als vergleichsweise deutlich dicke und schwerere konventionelle Bauelemente. Es können sogar bestückte, faltbare oder aufrollbare Leiterplatten, d.h. Dünnschichtanordnungen, erhalten werden, die eine optimale räumliche Anpassung der Elektronik-Komponenten an das jeweilige Gerät und Gehäuse erlauben. Dabei ist auch eine flexible Passivierung bzw. flexible Verkapselung unproblematisch. Beispielsweise können anstatt einer Verklebung mit starren Gläsern dünne Glaslaminate oder Polymer-Oxid-Verbundschichtsysteme verwendet werden, welche trotz ihrer geringen Dicke einen ausreichenden Schutz gegenüber Eindringen von Gasen oder Feuchte bieten und somit eine Kontamination der jeweiligen Dünnschichtbauelemente wirksam verhindern. Bei geeigneter Wahl und Ausführung des Verkapselungsmaterials in Relation zum flexiblen Leiterplatten-Substrat kann auch eine Anordnung des integrierten Dünnschichtbauelementes genau in der neutralen Ebene der gesamten Anordnung erreicht werden, so dass im Fall einer Biegung des Gesamtsystems im Dünnschichtbauelement selbst, d.h. im Bereich der Grenzschicht: Leiterplatte/Verkapselung wenn überhaupt so nur geringe Zug- und Druckkräfte auftreten.

Die flexible Verkapselungsschicht kann gegebenenfalls vorgefertigt und auf der Leiterplatte angebracht werden, wobei dann beispielsweise eine Adhäsionslage als Haftvermittlungs-Zwischenschicht sowie eine Passivierungslage als Sperrschicht für Feuchte und Luft vorgesehen werden können. Die Verkapselungsschicht kann gegebenenfalls aber auch als Verbundsystem direkt über dem Dünnschichtbauelement aufgebaut werden.

Im Fall von optoelektronisch aktiven Dünnschichtbauelementen bzw. Anzeigesystemen wird auch hier die (flexible) Verkapselung zweckmäßig transparent bzw. transluzent, es kann aber auch die flexible Leiterplatte transparent bzw. transluzent ausgebildet werden, beispielsweise durch Verwendung von Polyethylenterephthalat Polyacryl, oder Polyetherethereketon, wobei diese Basismaterialien mit transparenten bzw. semitransparenten Metallfilmen, Metalllegierungen, leitfähigen Metalloxiden (z.B. Aluminium-dotiertes Zinkoxid, Zinn-dotiertes Indiumoxid usw.), und/oder leitfähigen Suspensionen oder Lösungen (auf Basis von Polyanilin oder Polyethylen-Dioxithiophen/Polystyrolsulfonsäure) versehen werden.

Die Möglichkeit, flexible Leiterplatten mit optoelektronisch aktiven Dünnschichtbauelementen falten oder aufrollen zu können, ist gerade bei Anzeigesystemen von besonderer Bedeutung: Es sind hier elastische, mechanisch robuste und aufrollbare bzw. faltbare Bildschirme ebenso wie aufrollbare bzw. faltbare photovoltaische Zellen denkbar. Vor allem im Bereich von tragbaren elektronischen Geräten, so genannten Hand-helds, sind überdies aufrollbare bzw. faltbare Tastaturen sowie andere Bedienelemente, bei denen Dünnschichtanordnungen mit flexibler Leiterplatte verwendet werden, äußerst vorteilhaft.

Was die Herstellung der Dünnschichtanordnungen mit flexiblen Leiterplatten als Substrat betrifft, so kann hier das so genannte Rolle-zu-Rolle-Verfahren mit besonderem Vorteil angewendet werden. Dabei wird ein flexibles Leiterplatten-Bahnmaterial verwendet, das von einer Rolle

abgewickelt wird, und es wird eine vorgefertigte flexible Verkapselungs-Bahn zugeführt und über dem Dünnschichtbauelement angebracht, wobei die Verkapselungs-Bahn ebenfalls von einer Rolle abgewickelt werden kann. Denkbar ist aber hier selbstverständlich auch, entweder nur die flexible Leiterplatte oder aber nur die flexible Verkapselung als Rollenmaterial vorzusehen.

Während des Glättens bzw. Polierens kann auch eine vorübergehende Verstärkung der flexiblen Leiterplatte vorgesehen werden, wie etwa durch Führen der flexiblen Leiterplatten-Bahn über einen Tisch oder durch vorübergehendes Anordnen einer Trägerfolie auf der Rückseite der zu glättenden flexiblen Leiterplatte, um so eine Versteifung des Substrats während der Glättungs- bzw. Polievorgänge zu gewährleisten. Diese vorübergehende Verstärkung oder Versteifung kann im Verlauf der weiteren Fertigung an einer beliebigen geeigneten Stelle wieder entfernt werden.

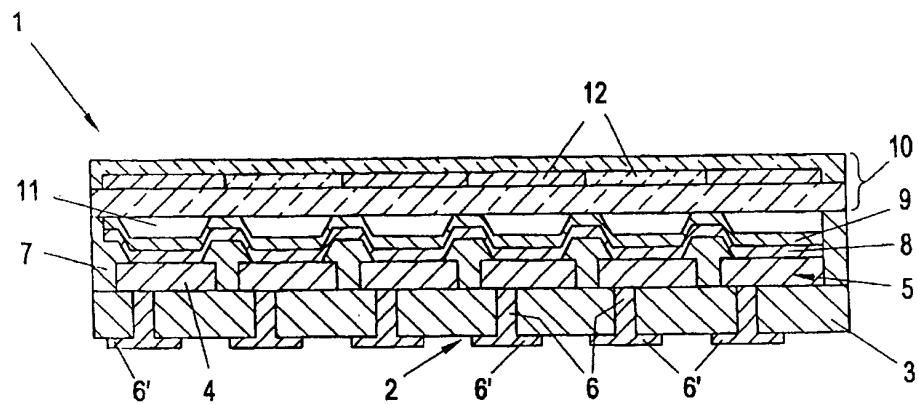

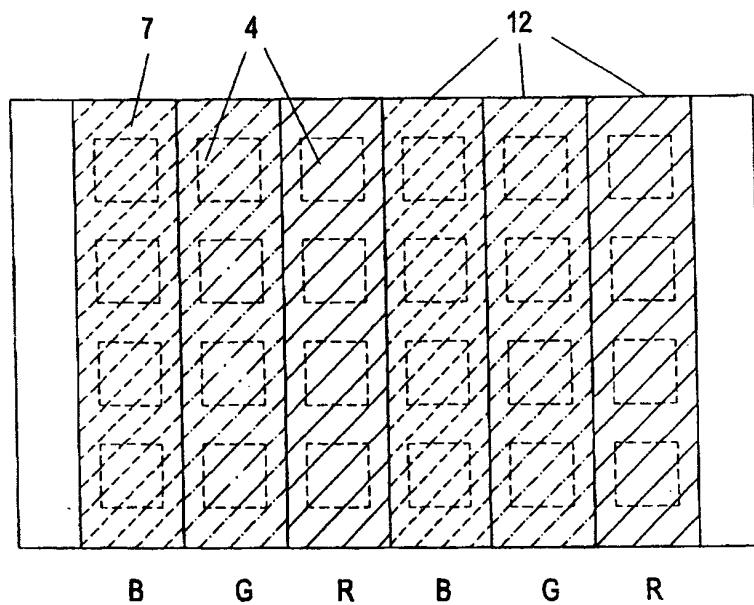

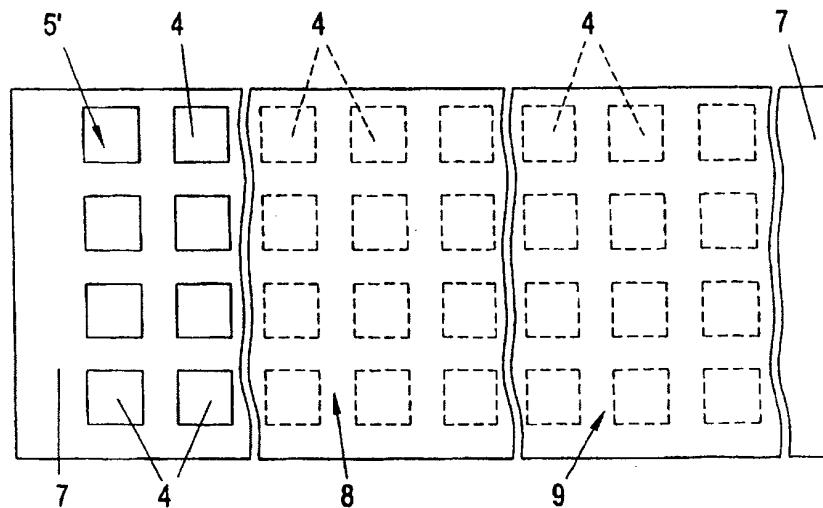

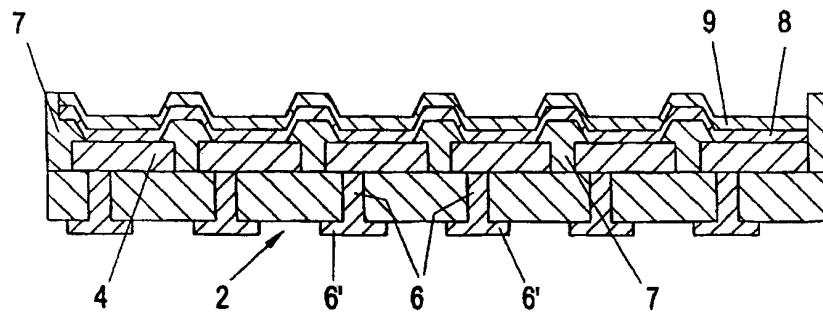

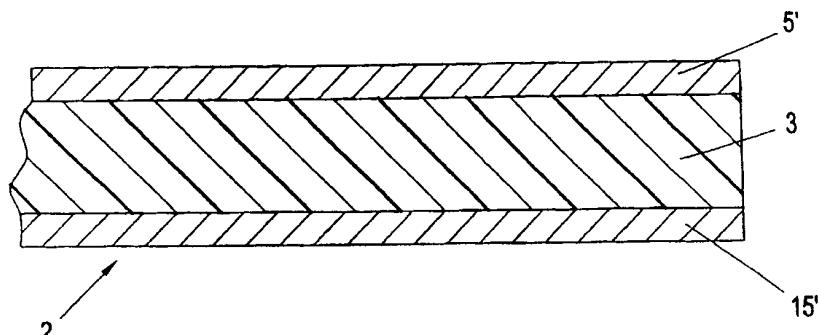

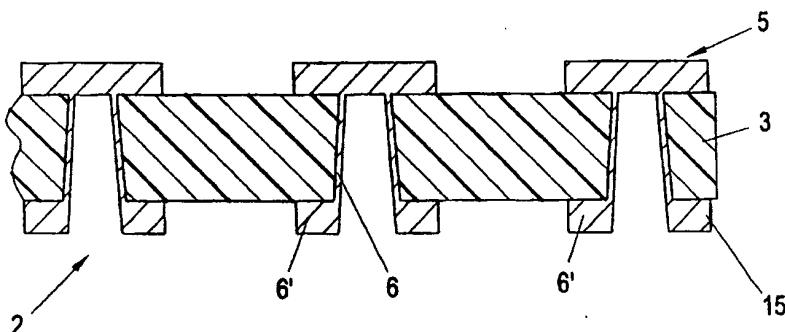

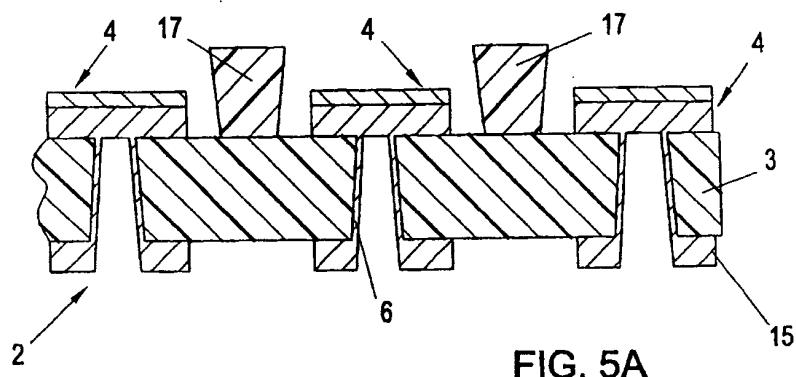

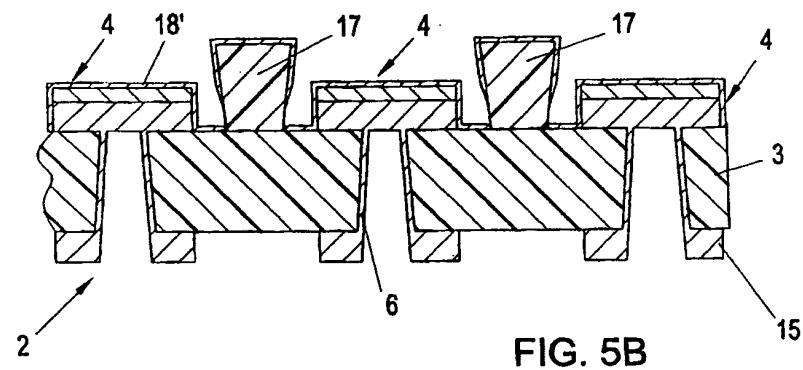

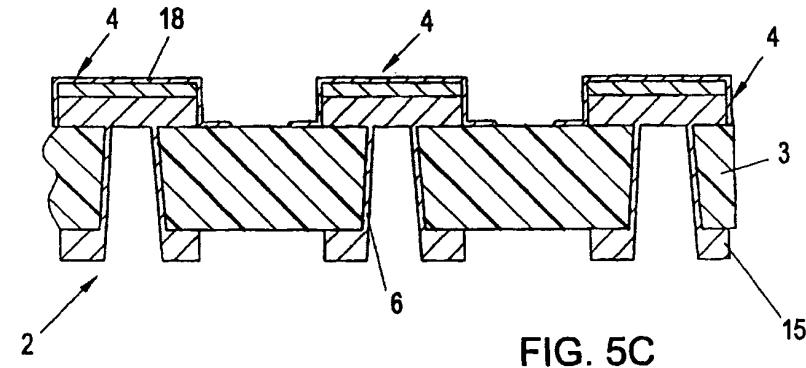

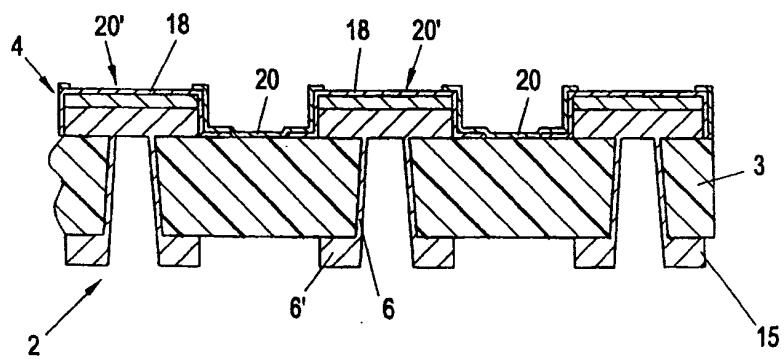

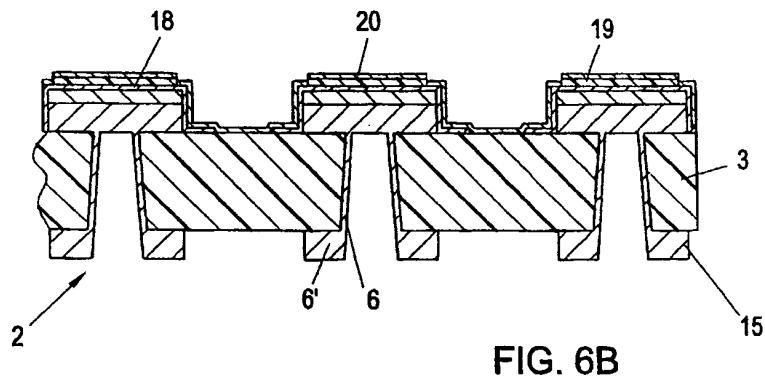

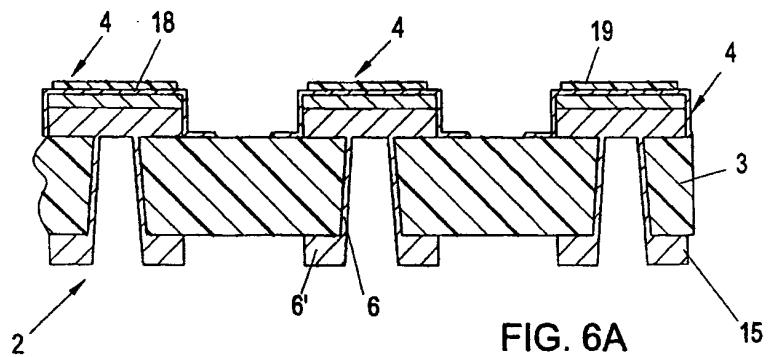

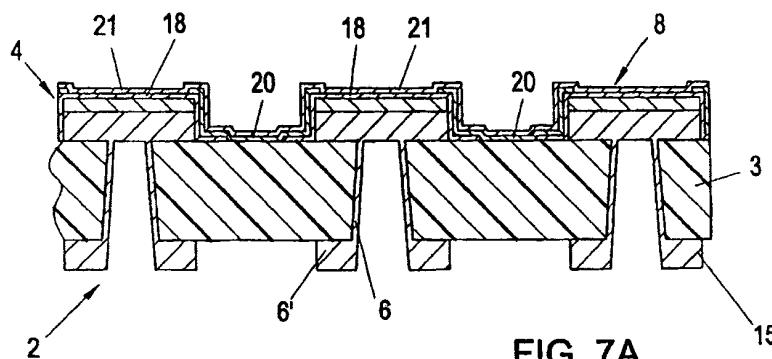

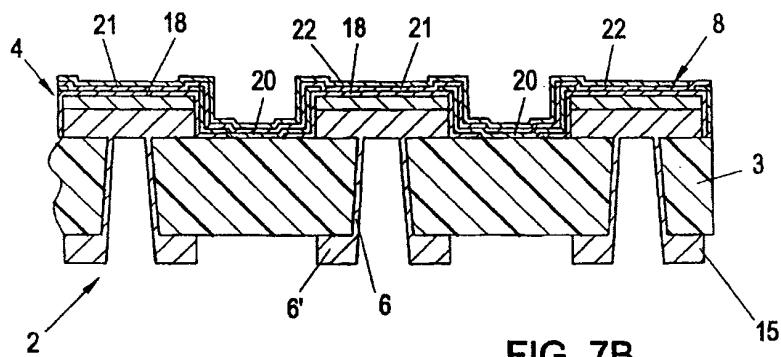

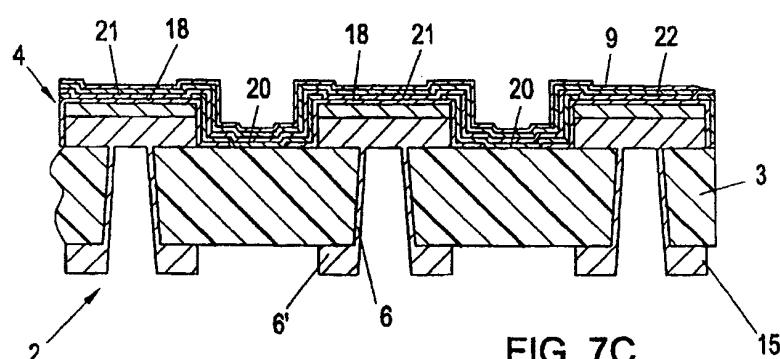

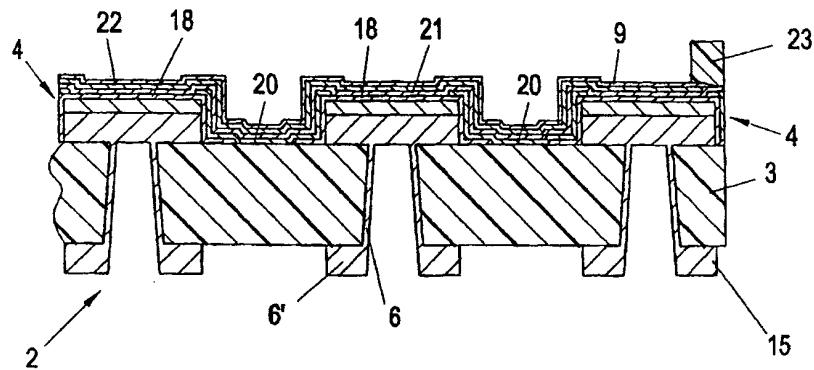

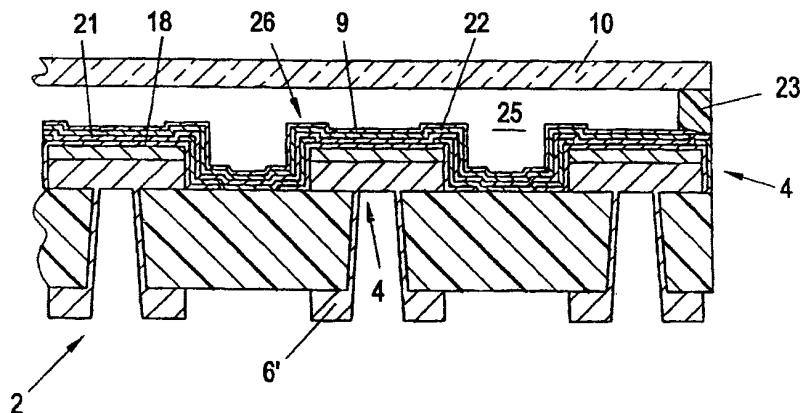

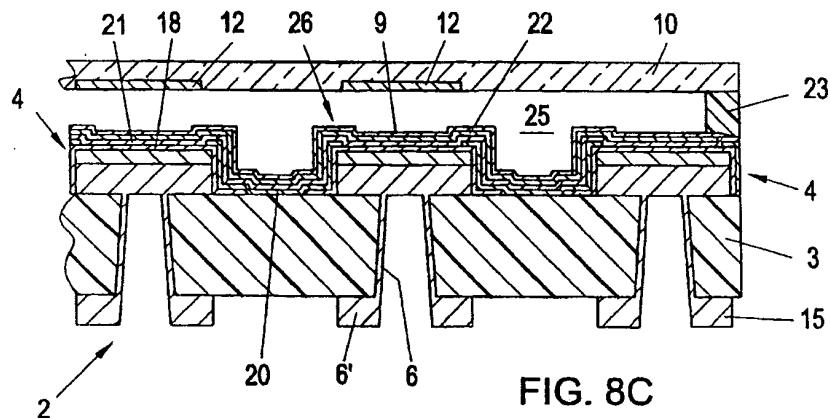

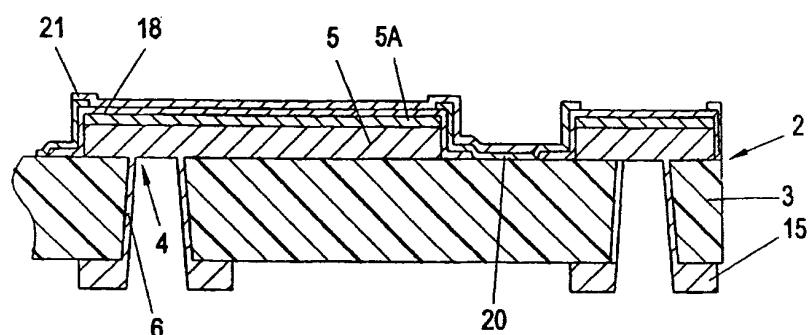

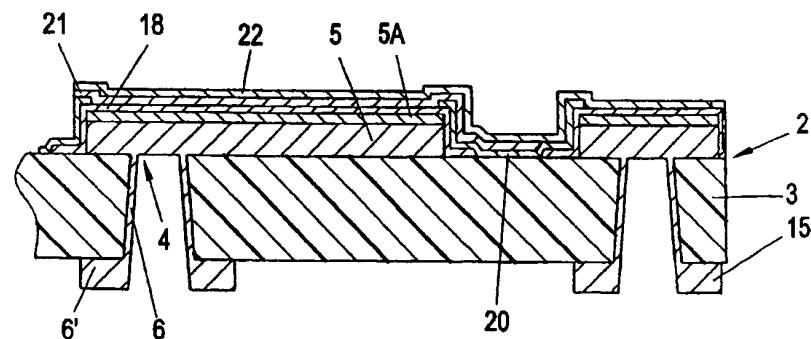

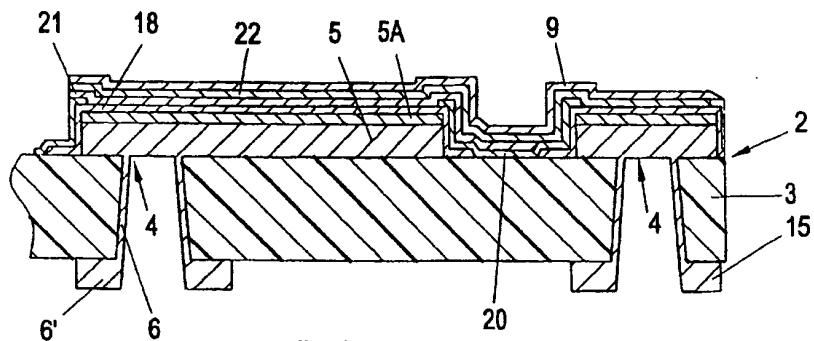

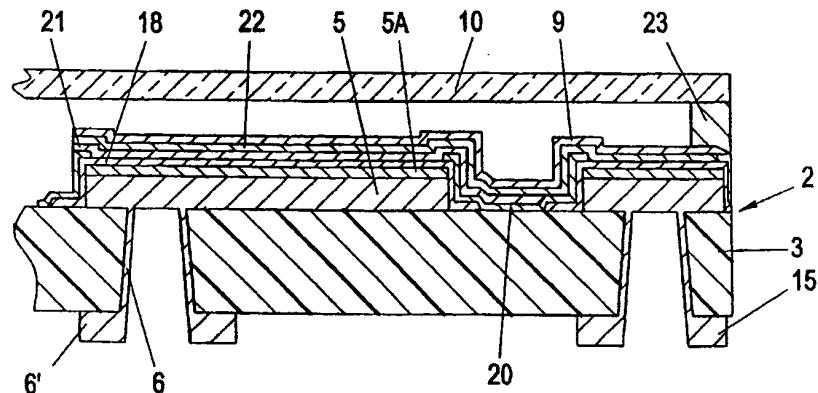

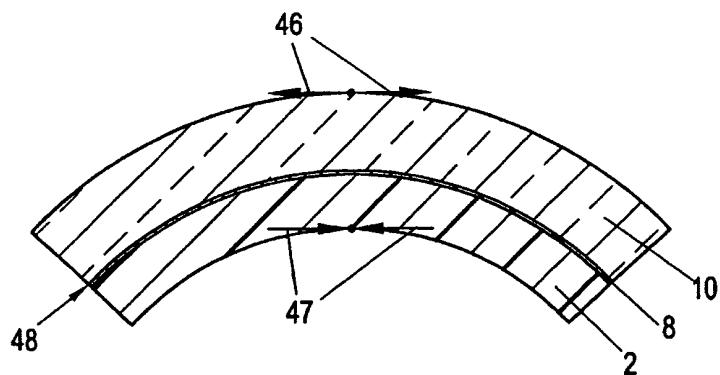

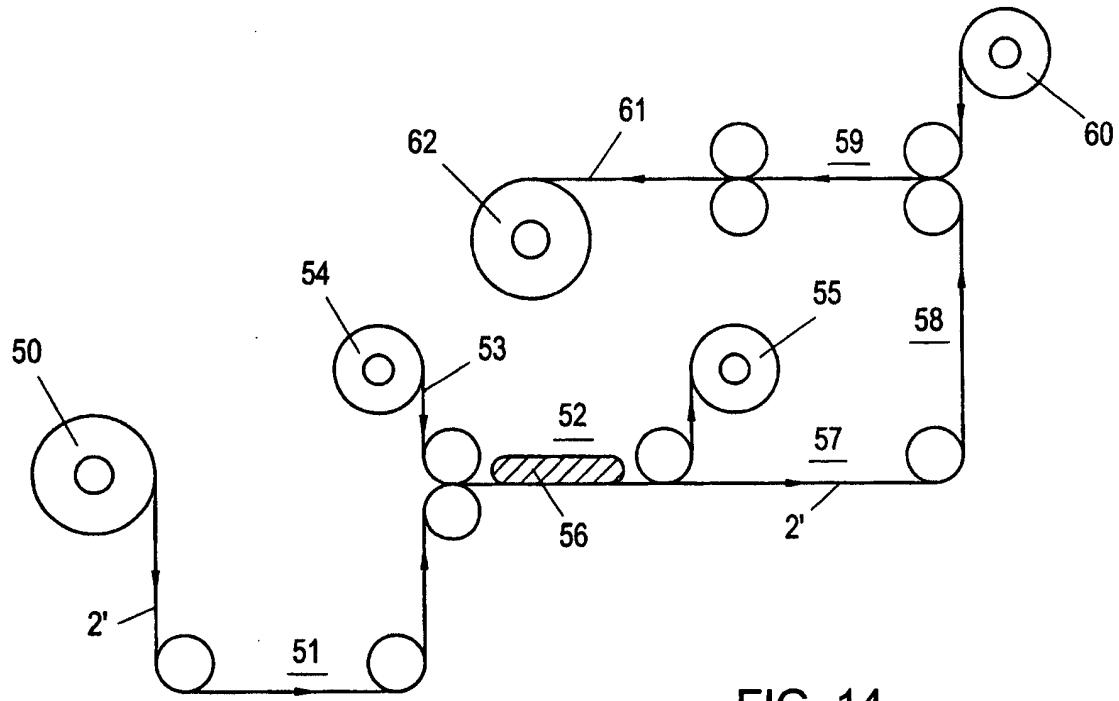

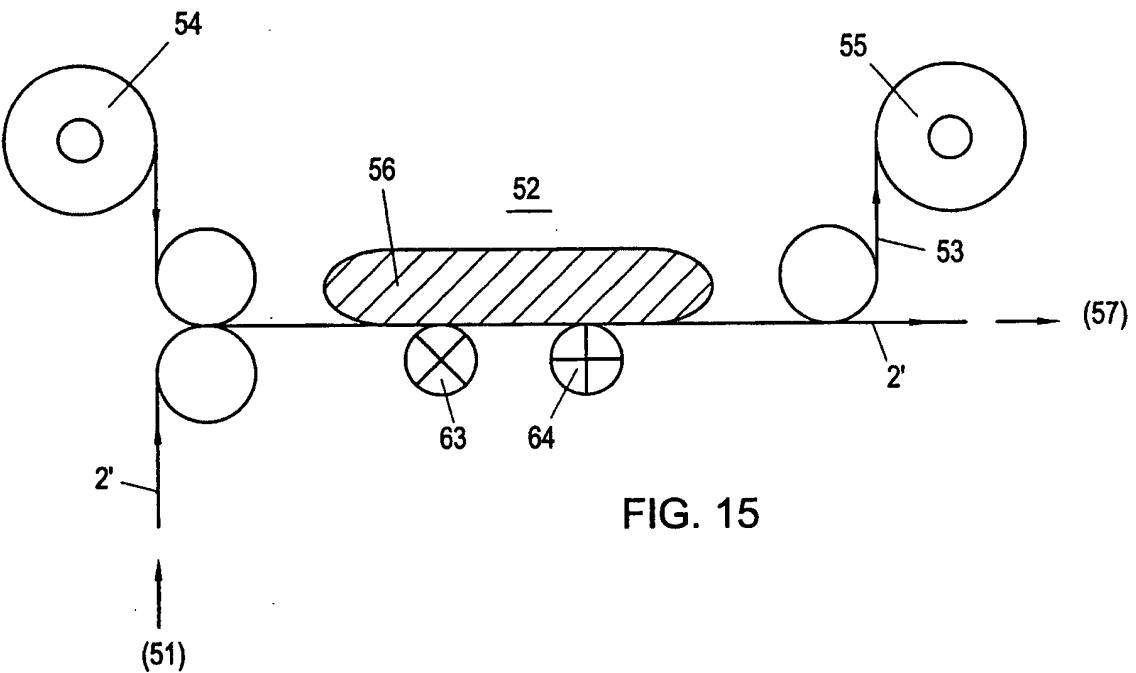

Die Erfindung wird nachfolgend anhand von besonders bevorzugten Ausführungsbeispielen, auf die sie jedoch nicht beschränkt sein soll, und unter Bezugnahme auf die Zeichnung noch weiter erläutert. Dabei zeigen in der Zeichnung im Einzelnen: Die Fig. 1A und 1B in einer schematischen Querschnittsdarstellung bzw. Draufsicht eine Dünnschichtanordnung in Form einer Elektrolumineszenz-Vorrichtung; die Fig. 2A, 2B und 2C in schematischen Draufsichten ähnlich jener von Fig. 1B aufeinanderfolgende Fertigungsschritte dieser Elektrolumineszenz-Vorrichtung; Fig. 2D eine schematische Querschnittsdarstellung ähnlich jener von Fig. 1A, jedoch in der Zwischenstufe nach den Fertigungsschritten gemäß Fig. 2A bis 2C, vor Fertigstellung der Vorrichtung; die Fig. 3 bis 8 mehr im Detail die Herstellung einer solchen Elektrolumineszenz-Vorrichtung ausgehend von einer herkömmlichen Leiterplatte, wobei im Einzelnen in Fig. 3A ein schematischer Querschnitt durch eine solche Leiterplatte gezeigt ist, in Fig. 3B und 3C die Vorbereitung dieser Leiterplatte unter Durchkontaktierung und fotolithografischer Strukturierung ihrer Metallkaschierung, und wobei in Fig. 4A in einer vergleichbaren Querschnittsdarstellung der Zustand nach Anbringung einer Passivierungsschicht an der Substratunterseite als Vorbereitung für die Anbringung einer Grundelektroden-Verstärkung gezeigt ist; in den Fig. 4B und 4C sind Detailschritte zur Anbringung einer Verstärkung der strukturierten Metallkaschierung (Fig. 4B), der Glättung der Elektrodenoberfläche (Fig. 4C), und der Zustand nach Entfernen der Passivierungsschicht (Fig. 4D) gezeigt; in den Fig. 5A bis 5C sind die Anbringung einer Fotolackstruktur zwecks Herstellung lokaler Kontaktsschichten (Fig. 5A), der Aufbau mit einer abgeschiedenen Kontaktsschicht (Fig. 5B) sowie schließlich der Zustand des Substrates samt Grundelektroden und Kontaktsschichten nach Entfernen der temporären Fotolackstruktur (Abrisskante) (Fig. 5C) veranschaulicht; die Fig. 6A, 6B und 6C zeigen aufeinanderfolgende Schritte bei der lokalen, fotolithografisch unterstützten Anbringung einer strukturierten Passivierungsschicht an der Substratoberseite; die Fig. 7A, 7B und 7C zeigen einzelne Schritte bei der Anbringung von optoelektronisch aktiven organischen Schichten (Fig. 7A), einer oberen lichtdurchlässigen Kontaktsschicht (Fig. 7B) und einer oberen lichtdurchlässigen Deckelektrode (Fig. 7C) zwecks Vollständigung des Dünnschichtbauelement-Aufbaus; die Fig. 8A, 8B und 8C schließlich die abschließenden Schritte zur Anbringung einer Verkapselung für die Elektrolumineszenz-Dünnschichtanordnung mit Hilfe eines Klebewulstes (Fig. 8A), auf dem die Verkapselungsschicht angebracht wird (Fig. 8B), und zur Integration lateral strukturierter Farbwandlerschichten (Fig. 8C); die Fig. 9A bis 9D veranschaulichen aufeinanderfolgende Herstellungsschritte zur Fertigung einer photovoltaischen Zelle mit organischem, optoelektronischem Dünnschichtmaterial; die Fig. 10 und 11 zeigen je eine ähnliche schematische Querschnittsdarstellung einer Dünnschichtanordnung mit einer „organischen“ Diode (Fig. 10) bzw. mit einem (Feldeffekt-)Transistor (Fig. 11); Fig. 12 zeigt in einer schematischen Querschnittsdarstellung eine flexible Dünnschichtanordnung, mit einer flexiblen Leiterplatte als Substrat und mit einer flexiblen Verkapselung über dem Dünnschichtbauelement, wobei die Dickenmaße der einzelnen Lagen in ihrer Relation zueinander ungefähr maßstäblich veranschaulicht sind; die Fig. 13A und 13B zeigen eine solche flexible Dünnschichtanordnung in weiter vereinfachter schematischer Querschnittsdarstellung, einmal in unbelastetem Zustand (Fig. 13A) und sodann in einem gebogenen Zustand (Fig. 13B), wobei ersichtlich ist, dass bei Vorsehen des Dünnschichtbauelements in der

neutralen Ebene der Anordnung auf dieses Dünnschichtbauelement keine Zug- bzw. Druckkräfte wirken, wie sie in den äußereren Bereichen der Anordnung wirken; Fig. 14 zeigt ein Schema zur Veranschaulichung der Herstellung einer flexiblen Dünnschichtanordnung in einem Rolle-zu-Rolle-Prozess; und Fig. 15 zeigt ein Detailschema zur Veranschaulichung der Anbringung einer vorübergehenden Versteifung im Zuge eines mechanischen Glättungs- und Polievorganges während der Herstellung der flexiblen Dünnschichtanordnung.

In Fig. 1A ist eine Dünnschichtanordnung in Form einer Elektrolumineszenz-Vorrichtung 1 schematisch in einer Querschnittsdarstellung gezeigt. Diese Elektrolumineszenz-Vorrichtung 1 weist als Substrat eine herkömmliche Leiterplatte 2 mit einem isolierenden Grundkörper 3 auf, auf dem lokale Grundelektroden 4 als verbleibende Teile der strukturierten Metallkaschierung oder Leiterschicht 5 der Leiterplatte 2 vorliegen. Diese Grundelektroden 4 sind über mechanisch oder Laser gebohrte Durchkontaktierungen 6 mit Kontaktstellen 6' an der Substrat-Unterseite verbunden, so dass von der Substratunterseite entsprechende Steuersignale an die Grundelektroden 4 angelegt werden können. Diese Grundelektroden 4 sind beispielhaft aus Fig. 1B als quadratische Flächen erkennbar, und sie sind durch eine in Draufsicht gitterförmige Isolierstruktur 7 voneinander getrennt.

Oberhalb der Grundelektroden 4 und der Isolierstruktur 7 ist insbesondere flächig eine organische Elektrolumineszenz-Dünnschichtstruktur angebracht, die im Prinzip beispielsweise wie in EP 1 087 649 A oder EP 0 854 662 A ausgebildet sein kann, wobei der Inhalt dieser Dokumente durch Bezugnahme hierauf als hier enthalten anzusehen ist.

Über dem organischen Elektroluminesenzschichtsystem 8 befindet sich eine transluzente leitfähige, bevorzugt ebenfalls flächig, gegebenenfalls in Streifenform oder aber auch in Elementform angebrachte Deckelektrode 9. Der gesamte bisher beschriebene Aufbau ist mit Hilfe einer transluzenten Verkapselungsschicht 10, unter Belassung eines Gasvolumens 11 unterhalb hiervon, zur Umgebung hin abgeschlossen, wobei in diese Verkapselungsschicht 10 weiters in an sich bekannter Weise (s. EP 0 854 662 A) Farbwandler- bzw. Indexanpassungsschichten 12 integriert sind.

In der schematischen Draufsicht von Fig. 1B ist ersichtlich, dass diese Farbwandler- bzw. Indexanpassungsschichten 12 streifenförmig, beispielsweise mit den Grundfarben Blau, Grün und Rot, vorliegen (was schematisch durch unterschiedliche Schraffierungen B, G, R in dieser Fig. 1B angedeutet wurde). In Zeilenrichtung (gemäß der Darstellung in Fig. 1B) liegen somit immer drei Farbpunkte Blau, Grün und Rot nebeneinander, und die Ansteuerung dieser Farbpunkte in Zeilenrichtung ebenso wie in Spaltenrichtung erfolgt über die Durchkontaktierungen 6 durch Anlegen von entsprechenden Steuersignalen an die jeweiligen Grundelektroden 4. Die Deckelektrode 9 hingegen kann, wenn sie flächig aufgebracht ist, an einem einheitlichen Potential liegen.

In den Fig. 2A, 2B und 2C sind in schematischen Draufsichten verschiedene Fertigungsstufen bei der Herstellung der eigentlichen Elektrolumineszenz-Vorrichtung (noch ohne Verkapselung) veranschaulicht, wobei das nach diesen Fertigungsschritten erhaltene Zwischenprodukt in Fig. 2D in schematischer Querschnittsdarstellung ersichtlich ist.

Gemäß Fig. 2A liegt bereits eine lateral strukturierte Leiterschicht 5' vor, um so eine Matrix von Grundelektroden 4 zu bilden. Zwischen diesen in Matrix-Form vorliegenden Grundelektroden 4 befindet sich die gitterartige Isolierstruktur 7, die die einzelnen Grundelektroden 4 voneinander trennt. Im nachfolgenden Schritt, vgl. Fig. 2B, wird das organische Elektroluminesenzschichtsystem 8 flächig aufgebracht, s. außer Fig. 2B auch Fig. 2D. Danach wird die lichtdurchlässige Deckelektrode 9 - ebenfalls flächig - abgelagert, wodurch die Anordnung gemäß Fig. 2D erhalten ist. Hierzu ist ergänzend auszuführen, dass vorab die Leiterplatte 2 bereits zur Anfertigung der Laser-Vias 6 samt Kontaktstellen 6' behandelt wurde, bevor die Strukturierung der Leiterschicht 5 zur Bildung der Grundelektroden 4 (s. Fig. 2A) erfolgte.

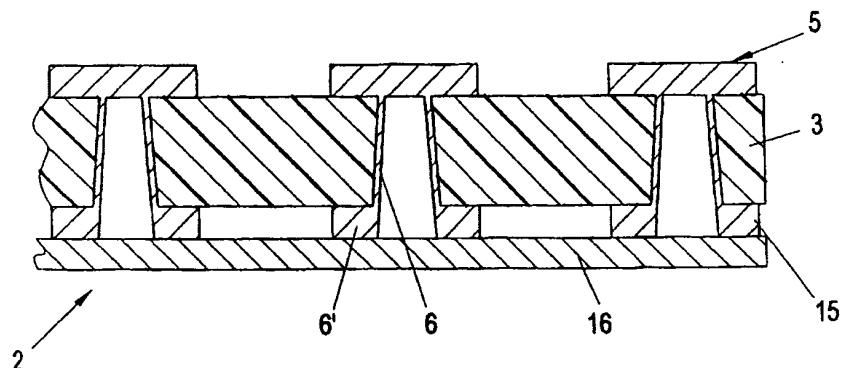

In Fig. 3A ist in einer schematischen Querschnittsdarstellung (in ähnlicher Weise sind alle weiteren Figuren schematische Querschnittsdarstellungen) eine Leiterplatte 2 veranschaulicht, die eine doppelseitige Metallkaschierung 5 (oberseitig) bzw. 15 (unterseitig) auf einem dielektrischen Grundkörper 3, z.B. aus Epoxidharz, aufweist. Die Metallkaschierungen 5, 15 bestehen

5 beispielsweise wie üblich aus Kupfer.

Diese das Substrat der vorliegenden Dünnschichtanordnung bildende Leiterplatte 2 wird so-

dann in einem ersten Schritt mit Durchkontaktierungen 6 versehen, vgl. Fig. 3B, wobei diese

10 Durchkontaktierungen im Hinblick auf die gewünschten eng beisammen liegenden Bildpunkte,

d.h. das hohe Auflösungsvermögen der herzustellenden Elektrolumineszenz-Vorrichtung 1, als

Laserbohrungen mit galvanischer Kupferbeschichtung der Bohrungswände hergestellt werden.

Dabei wird bevorzugt eine derartige Durchkontaktierung oder Laserbohrung 6 unter der jeweils

15 vorzusehenden Grundelekrode 4 hergestellt, um die endgültig erhaltene enge Matrix-

Anordnung der Grundelektronen 4 mit einer entsprechenden Ansteuerungsmöglichkeit von der

Unterseite des Substrates her ausbilden zu können.

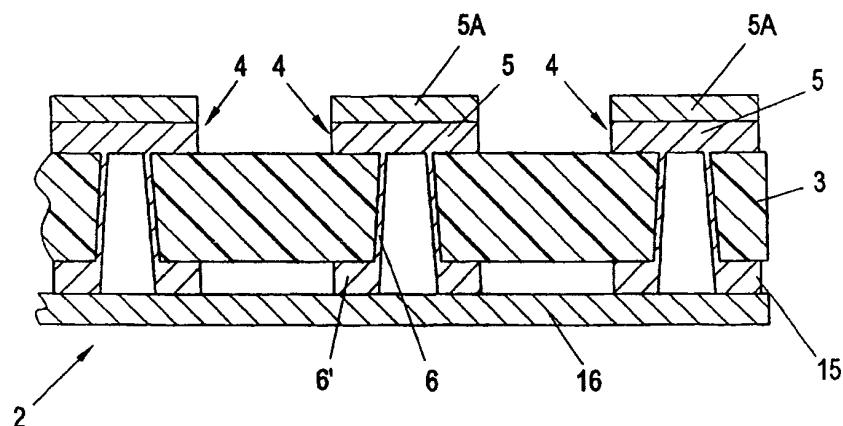

Im nächsten Schritt erfolgt gemäß Fig. 3C eine fotolithografische Strukturierung der Metallka-

schierungen, d.h. der Leiterschichten 5, 15 an der Oberseite und Unterseite des Grundkörpers

20 3 der Leiterplatte 2. Eine derartige Strukturierung ist ebenfalls an sich herkömmlich, so dass die

danach erhaltene Struktur in Fig. 3C ohne die üblichen Zwischenschritte dargestellt werden

kann. Die jeweils erhaltenen Strukturen der oberen Leiterschicht und unteren Leiterschicht sind

zwecks Unterscheidung der vollflächigen Leiterschichten nunmehr anstatt mit 5' bzw. 15' mit 5

bzw. 15 bezeichnet. An der Unterseite bilden dabei die verbleibenden Teile 15 der Leiterschicht

die Kontaktstellen 6'.

25 Als Nächstes wird an der Substratunterseite eine temporäre Passivierungsschicht 16 ange-

bracht, wie aus Fig. 4A ersichtlich ist. Diese temporäre Passivierungsschicht 16 dient dazu,

diese unterseitigen Bereiche der Leiterplatte 2 im Hinblick auf die nachfolgende Anbringung

30 einer chemischen bzw. elektrochemischen Verstärkung der Leiterschicht 5 an den Stellen der

herzustellenden Grundelektronen 4 vorübergehend zu passivieren. Diese Passivierungsschicht

16 kann fotolithografisch, wie an sich bekannt, aufgebracht werden.

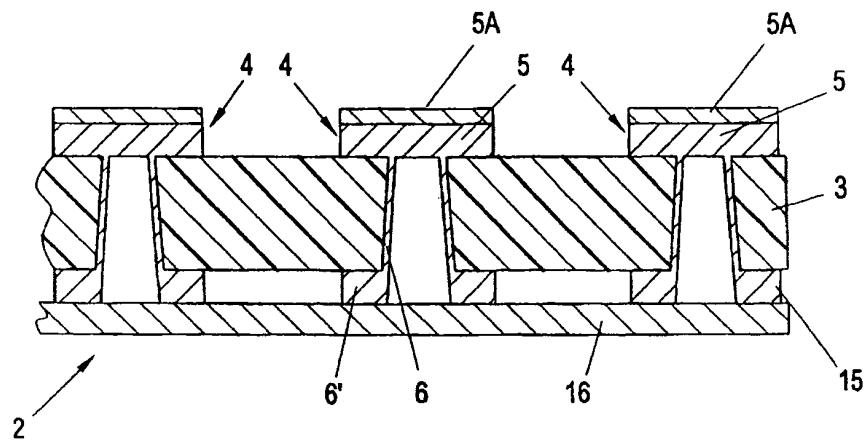

Wie bereits angedeutet erfolgt als nächster Schritt eine chemische bzw. elektrochemische

35 Verstärkung der strukturierten Leiterschicht 5, wobei die Verstärkungslagen in Fig. 4B mit 5A

angegeben sind. Diese metallische Schicht 5A bildet zusammen mit der strukturierten Leiter-

schicht 5 die jeweiligen Grundelektronen 4, beispielsweise in der Matrix-Anordnung gemäß

Fig. 2A. Diese Grundelektronen 4 sind jedoch in dieser Form noch nicht für den Aufbau der

40 gewünschten aktiven oder passiven elektronischen Dünnschichtbauelemente, hier der optoe-

lektronischen EL-Vorrichtung 1, geeignet, da die Oberfläche der Leiterschicht 5 an sich ebenso

wie jene der mit der Verstärkung 5A versehenen Leiterschicht 5 viel zu rau ist. Es wird daher in

einem nächsten Schritt eine Glättung oder ein Polieren der Grundelektronen 4 durchgeführt, um

45 eine niedrige Oberflächenrauigkeit, beispielsweise mit einer mittleren Oberflächenrauigkeit von

maximal 10 nm oder bevorzugt sogar maximal 3 nm zu erreichen. Dieser geglättete Zustand ist

in Fig. 4C dargestellt. Das Glätten oder Polieren kann auf an sich herkömmliche Weise erfolgen,

wie etwa mechanisch, chemisch, elektrochemisch, chemisch-mechanisch sowie durch Ionenätz-

zen. Es können dabei selbstverständlich auch Kombinationen dieser Verfahrenstechniken

eingesetzt werden.

Die herbeizuführende Oberflächenrauigkeit hängt selbstverständlich von der Art der jeweiligen

50 Applikation, d.h. vom jeweils anzubringenden Dünnschichtbauelement ab, so dass auch Abwei-

chungen von den vorgenannten mittleren Rauigkeitswerten denkbar sind.

Zu erwähnen ist auch, dass es nicht unbedingt erforderlich ist, eine metallische Verstärkung 5A

für die Grundelektronen 4 vorzusehen, da auch die Metallkaschierung, d.h. Leiterschicht 5 der

55 Leiterplatte 2, bereits eine ausreichende Dicke aufweisen kann. Weiters ist es im Prinzip auch

denkbar, die Reihenfolge der Strukturierung der Leiterschicht 5 (s. Fig. 3C) und der Glättung der Oberfläche der Leiterschicht (s. Fig. 4C) zu vertauschen, d.h. die Glättung der Leiterschicht 5' insgesamt zuerst vorzunehmen und erst danach die Leiterschicht 5' zur Bildung der Grundelektroden 4, d.h. zur Bildung der strukturierten Leiterschicht 5, entsprechend fotolithografisch zu ätzen.

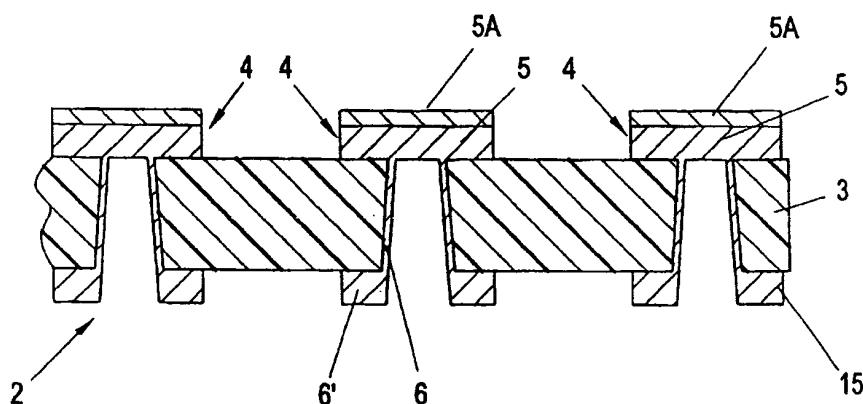

In einem diese Phase der Herstellung abschließenden Schritt wird die untere Passivierungsschicht 16 entfernt, so dass nunmehr die Substratstruktur gemäß Fig. 4D erhalten ist.

10 In der nächsten Phase wird auf der nun geglätteten Grundelektrode 4 eine Kontaktschicht angebracht, wobei als erstes gemäß Fig. 5A eine temporäre Fotolackstruktur in der Art von Abrisskanten 17 in den Zwischenräumen zwischen den Grundelektroden 4 angebracht wird. Darauf wird die gesamte Oberseite der erhaltenen Struktur mit einer Lage 18' aus Kontaktschichtmaterial überzogen, wobei in den unteren Bereichen der Abrisskanten 17 kein Kontaktschichtmaterial erfolgt, so dass in einem nachfolgenden Entfernungsschritt (Ätzschritt) die Abrisskanten 17 entfernt werden können, wobei in den übrigen Bereichen der Oberfläche die gewünschte Kontaktschicht 18 zurückbleibt, vgl. Fig. 5B und 5C.

20 Die Kontaktschicht 18 dient zur elektrischen Kontaktierung der nunmehr aufzubringenden nächsten Schicht des jeweiligen Dünnschichtaufbaus ebenso wie zur Stabilisierung der Haftung dieses Dünnschichtaufbaus auf der Grundelektrode 4 sowie schließlich auch zur Passivierung der Leiterschicht 5 bzw. ihrer Verstärkung 5a, indem durch das Einbringen der Kontaktschicht 18 eine etwaige Kontamination des Dünnschichtsystems durch Interdiffusion von Fremdstoffen aus der Leiterschicht 5 bzw. ihrer Verstärkung 5a unterbunden wird. Das Material für die jeweilige Kontaktschicht 18 ist naturgemäß wiederum abhängig vom jeweiligen anzubringenden Dünnschichtbauelement geeignet zu wählen, und sie besteht beispielsweise aus einem Metall wie Aluminium, Gold, Palladium oder Platin, einer Metalllegierung, Kohlenstoff oder einer halbleitenden Verbindung, kann aber auch aus einer leitfähigen Suspension oder einer Lösung (z.B. Polyanilin, Polyethylen-Dioxithiophen/Polystyrolsulfonsäure) bestehen.

30 Die Kontaktmaterial-Lage 18' kann mittels üblicher Dünnschichtverfahren, wie etwa durch thermisches Verdampfen, Kaltkathodenzerstäubung, Elektronenstrahlverdampfung, Beschichtung mittels Laserpulsen sowie durch Beschichtungsverfahren aus der flüssigen Phase, wie z.B. Tauch-, Sprüh-, Schleuder- und Tintenstrahldruck-Verfahren, aufgebracht werden, wobei auf eine physikalische bzw. chemische Adsorption des Kontaktmaterials auf der Leiterschicht 5 bzw. ihrer Verstärkung 5a zu achten ist; diese physikalische bzw. chemische Adsorption ist für ein Haften bzw. Nicht-Ablösen des Kontaktmaterials auf bzw. von der Leiterschicht 5, 5a von Bedeutung. Im Fall von gleichförmigen Beschichtungsverfahren aus der flüssigen Phase kann die laterale Strukturierung der Kontaktschicht 18 nach der Beschichtung der Leiterplatte 2 beispielsweise mit Trockenätzverfahren erfolgen. Kommen derartige Prozesse zur Anwendung, entfällt die Strukturierung mittels des Abrisskantenverfahrens.

45 Als Nächstes erfolgt nun die Anbringung einer oberen Passivierungsschicht, um die Bereiche zwischen den Grundelektroden 4 samt darüber angebrachten Kontaktschichten 18 zu passivieren und so daran zu hindern, dass über diese Bereiche aus dem Grundkörper 3 der Leiterplatte 2 Substanzen in den noch anzubringenden Dünnschichtaufbau des jeweiligen Dünnschichtbauelements eindringen. Hierfür wird in einem ersten Schritt gemäß Fig. 6A eine neuartige temporäre Fotolackstruktur 19 auf den Kontaktschichten 18 über den Grundelektroden 4 angebracht, und danach wird darüber das Material für die Passivierungsschicht 20 abgeschieden, siehe Fig. 6B. Im Anschluss daran wird über den Grundelektroden 4 die Fotolackschicht samt Passivierungsschicht fotolithografisch entfernt, so dass eine strukturierte Passivierungsschicht 20 nur in den Zwischenzonen, wo das Basismaterial des Isoliergrundkörpers 3 der Leiterplatte 2 freigelegt war, zurückbleibt, s. Fig. 6C. Über Fenster 20' in dieser Passivierungsschicht 20 liegen die Kontaktschichten 18 mit den darunter liegenden Grundelektroden 4 frei. Die Passivierungsschicht 20 ist selbstverständlich nur dann zweckmäßig bzw. anzubringen, wenn die angespro-

- chene Kontamination des spezifischen Dünnschichtaufbaus durch Substanzen, die aus dem dielektrischen Material des Grundkörpers 3 diffundieren können, zu befürchten ist. Wenn eine solche Diffusion von Substanzen nicht zu befürchten ist, kann die Anbringung der Passivierungsschicht 20 auch unterbleiben, es wäre dann aber eine andere Isolierstruktur (7 in Fig. 1A und 1B) zwischen den Grundeletroden 4 anzubringen. Das Material der Passivierungsschicht 20 ist wiederum abhängig von den verwendeten Materialien, insbesondere vom Material des Grundkörpers 3, zu wählen. Wie beschrieben wird sie zweckmäßig fotolithografisch strukturiert (vgl. die Fig. 6A und 6B), und das Material der Passivierungsschicht 20 kann mittels üblicher Dünnschichttechniken, etwa durch thermisches Verdampfen, Kaltkatodenzerstäubung usw., aufgebracht werden, wobei auf eine für das Haften hinreichende physikalische bzw. chemische Adsorption des Passivierungsmaterials auf dem Grundkörper 3 zu achten ist. Als Material für die Passivierungsschicht 20 kann beispielsweise Siliziumoxid, ein Sol-Gel-System oder eine Epoxidverbindung verwendet werden.

- Alternativ zur Technik gemäß den Fig. 6A bis 6C ist es auch denkbar, vorweg eine vollflächige gleichförmige Aufbringung von Passivierungsmaterial, etwa in Form eines Laminats, vorzusehen und diese Passivierungsschicht erst nachträglich fotolithografisch zu strukturieren, um schließlich die Struktur gemäß Fig. 6C zu erhalten.

- Die so erhaltene Anordnung ist nunmehr bereit für die Anbringung der jeweiligen elektronischen Schichten in Dünnschichttechnik, zum Aufbau des gewünschten Dünnschichtbauelementes 8, im vorliegenden Fall einer optoelektronischen aktiven organischen Dünnschichtstruktur; zur Erzielung der Elektrolumineszenz(EL)-Vorrichtung 1 (s. Fig. 1A) werden dabei ein oder mehrere optoelektronisch aktive organische Schichten 21 auf dem vorbereiteten Substrat gemäß Fig. 6C abgeschieden, so dass die Anordnung gemäß Fig. 7A erhalten wird. Wie dabei ersichtlich wird beispielsweise über der gesamten Fläche das organische EL-Material abgelagert, wodurch die Herstellung besonders einfach wird. Ebenso wie dieses (gegebenenfalls mehrlagige) organische EL-Dünnschichtsystem 21 (dessen Dicke einige wenige nm bis einige hundert nm betragen kann) wird nachfolgend auch eine transparente oder transluzente Kontaktsschicht 22, s. Fig. 7B, flächig aufgetragen; auch die nachfolgend angebrachte transparente oder transluzente Deckelektrode 9 wird flächig aufgetragen, s. Fig. 7C. Es ist jedoch abweichend hiervon auch denkbar, die obere Kontaktsschicht 22 sowie die Deckelektrode 9 anstatt vollflächig auch streifenweise oder symbolweise zu strukturieren.

- Als Beispiel für die organischen optoelektronisch aktiven Schichtmaterialien, zur Realisierung der Elektrolumineszenz-Vorrichtung 1, können Poly- und Oligophenyle, Arylamine, Poly- und Oligoazometine genannt werden. Für die transparenten oder transluzenten Kontaktsschichten 22 sowie die Deckelektroden 9 können transparente oder semitransparente Metalle, Metalllegierungen, Halbleiterverbindungen (mit einer Schichtdicke <50 nm), leitfähige Metalloxide (z.B. Aluminium-dotiertes Zinkoxid, Zinn-dotiertes Indiumoxid usw.), leitfähige Sol-Gel-Systeme und/oder leitfähige Suspensionen und Lösungen (auf Basis von Polyanilin, Polyethylen-Dioxithiophen/Polystyrolsulfonsäure) verwendet werden.

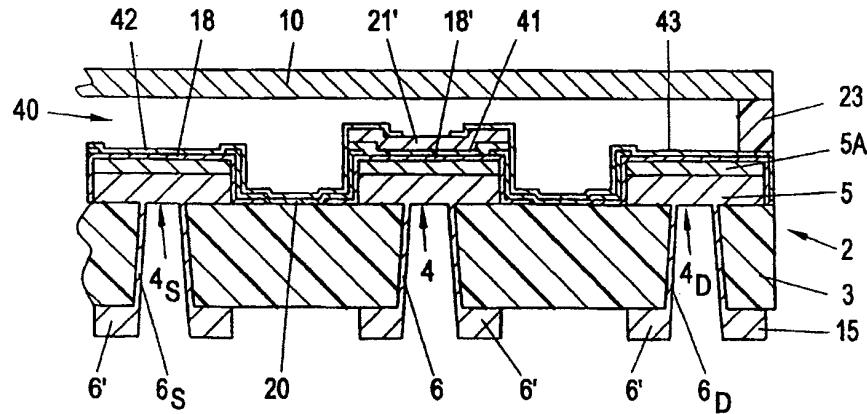

- Abschließend wird die so erhaltene Dünnschichtanordnung (s. Fig. 7C) noch mit einer Schutzabdeckung versehen, wozu als erstes, gemäß Fig. 8A, ein für Gas und Feuchte undurchlässiger Klebewulst 23 randseitig angebracht wird. Über diesem Klebewulst 23 wird anschließend die lichtdurchlässige Verkapselungsschicht 10 angebracht, um die eigentlichen Dünnschichtbauelemente 24 mit den Grundeletroden 4, der Kontaktsschicht 18, der Dünnschichtstruktur 8, der oberen Kontaktsschicht 22 und der Deckelektrode 9 zu verpacken, wobei ein Gasvolumen 25 verbleibt, in dem in an sich herkömmlicher Weise Gettermaterialien für Sauerstoff und/oder Wasser bzw. Feuchtigkeit enthalten sein können.

- Wie sodann in Fig. 8C dargestellt ist, können gewünschtenfalls auch lateral strukturierte Farbwandlerschichten 12 (s. außer Fig. 8C auch Fig. 1A und 1B) in die Verkapselungsschicht 10 über dem Gasvolumen 25 und den einzelnen Dünnschichtbauelementen 24 integriert werden.

Auf diese Weise ist nunmehr die gewünschte Dünnschichtanordnung fertiggestellt, die an den Kontaktstellen 6' mit den erforderlichen Steueranschlüssen versehen werden kann. Zusätzlich können auf der Leiterplatte 2 auch in an sich herkömmlicher und hier nicht näher dargestellter Weise Bauelemente montiert werden, um gewünschte Schaltungsfunktionen zu realisieren.

- 5 In den Fig. 9A bis 9D ist in verschiedenen Herstellungsschritten ein anderes Ausführungsbeispiel veranschaulicht, nämlich eine Dünnschichtanordnung mit einer photovoltaischen Zelle aus einem organischen optoelektronisch aktiven Schichtsystem, wobei die Herstellung im Prinzip sehr ähnlich wie vorstehend anhand der Fig. 3A bis 8C beschrieben erfolgen kann.

- 10 Im Einzelnen wird ähnlich wie in Fig. 7A gezeigt, auf entsprechende Grundelektroden 4, bestehend aus der strukturierten Leiterschicht 5, einer Verstärkung 5A und einer Kontaktschicht 18, das gewünschte optoelektronisch aktive organische Schichtsystem 21 abgeschieden, wonach eine lichtdurchlässige Kontaktschicht 22 (s. Fig. 9B) und darüber eine lichtdurchlässige Deckelektrode 9 (s. Fig. 9C) wiederum flächig abgeschieden werden können. Schließlich kann wiederum in einer Weise wie vorstehend anhand der Fig. 8A und 8B erläutert eine lichtdurchlässige Verkapselungsschicht 10 mit einem randseitigen Gas- und Feuchte-undurchlässigen Klebewulst 23 angebracht werden, wie in Fig. 9D veranschaulicht ist.

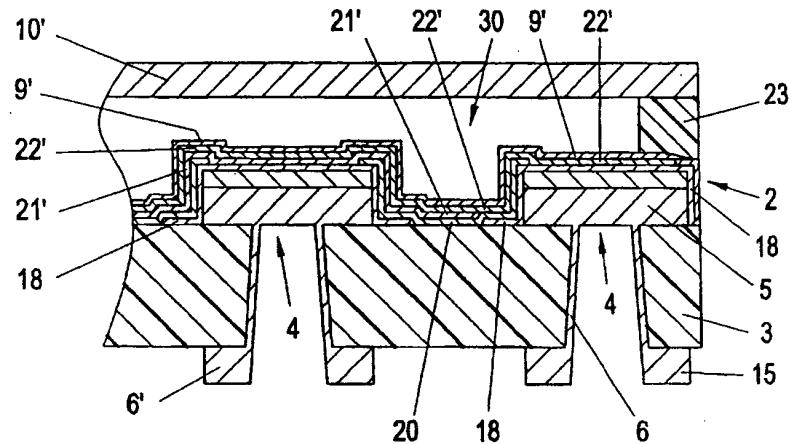

- 15 20 In Fig. 10 ist ein weiteres Ausführungsbeispiel in Form einer auf einer Leiterplatte 2 integrierten organischen Diode 30 veranschaulicht, wobei hier wiederum in vergleichbarer Weise, wie vorstehend erläutert, über einer Grundelektrode 4 mit einer Kontaktschicht 18 ein entsprechendes organisches Dioden-Dünnschichtsystem 21' aufgebracht ist. Darüber befindet sich eine obere Kontaktschicht 22', die hier nicht lichtdurchlässig sein muss, und eine Deckelektrode 9', die ebenfalls nicht lichtdurchlässig zu sein braucht. Zu erkennen sind weiters aus Fig. 10 wiederum die strukturierte untere Metallkaschierung 15 und der Grundkörper 3 der Leiterplatte 2 sowie weiters ein dichter Klebewulst 23 und eine Verkapselungsschicht 10', wobei auch hier eine opake Ausbildung vorliegen kann.

- 25 30 Ähnliches gilt auch für die Transistorstruktur 40 gemäß Fig. 11, wobei wiederum über der Grundelektrode 4, bestehend aus der strukturierten oberen Leiterschicht 5 und einer Verstärkung 5A, eine Kontaktschicht 18' angebracht ist, die beispielsweise den Gate-Kontakt der gebildeten Feldeffektstruktur 40 bildet. Über dieser Kontaktschicht 18' der Transistorstruktur 40 ist eine Isolierschicht 41, beispielsweise aus Aluminiumoxid, angebracht, über der wiederum eine organisch aktive Schicht 21' aufgebracht ist, die einerseits mit einer Source-Kontaktschicht 42 und andererseits mit einer Drain-Kontaktschicht 43 in Verbindung steht. Diese Kontakte werden über seitlich der Transistorstruktur 40 vorhandene Grundelektroden 4<sub>S</sub>, 4<sub>D</sub> bzw. über deren korrespondierende Durchkontaktierungen 6<sub>S</sub>, 6<sub>D</sub> und Kontaktstellen 6' von der Unterseite her kontaktiert.

- 35 40 In ähnlicher Weise können auch andere Dünnschichtbauelemente, und zwar aktive Bauelemente ebenso wie passive Bauelemente, direkt auf dem Leiterplattensubstrat 2 aufgebaut bzw. in dieses integriert werden, wobei wesentlich jeweils die Glättung der strukturierten, gegebenenfalls verstärkten Leiterschicht 5 (bzw. 5A), somit der Grundelektroden 4 oder unterseitigen Elektroden durchzuführen ist. Auf dieser geglätteten oder polierten Grundelektrode wird dann die beschriebene Kontaktschicht zur Herstellung des Kontakts und der stabilen Adhäsion der Dünnschichtaufbauten vorgesehen. Andere an sich herkömmliche Bauelemente, die mit der erfindungsgemäßen Technik auf Leiterplatten integriert werden können, sind beispielsweise Sensoren, wobei im Fall von optischen Sensoren entsprechende lichtdurchlässige obere Kontaktschichten, Elektroden und Verkapselungsschichten vorzusehen sind.

- 45 50

55 Die vorstehend erläuterten Techniken können im Wesentlichen in gleicher Weise bei starren Leiterplatten wie bei flexiblen Leiterplatten angewandt werden. Derartige flexible Leiterplatten 2 haben beispielsweise einen isolierenden Grundkörper 3 aus einer biegsamen Folie aus einem Polyimid, aus Polyethylennapthalat, aus Polyester oder aus Polyetheretherketon, und es kann

in vergleichbarer Weise als Leiterschicht 5 eine Metallkaschierung, insbesondere aus Kupfer, einseitig oder aber beidseitig, vorliegen.

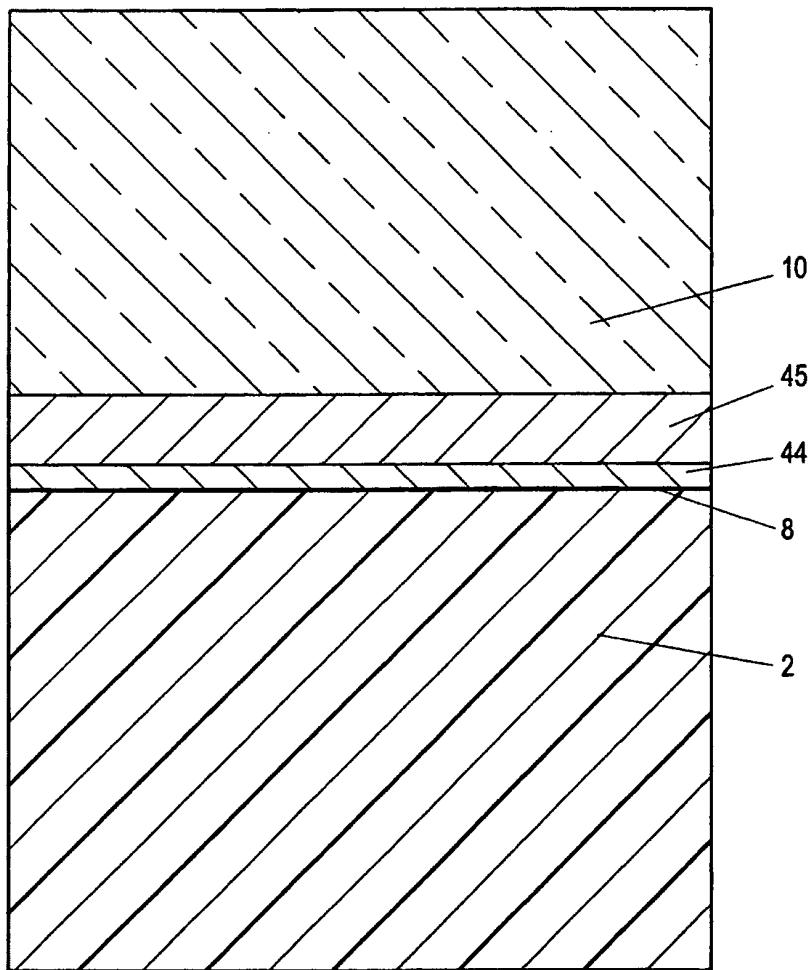

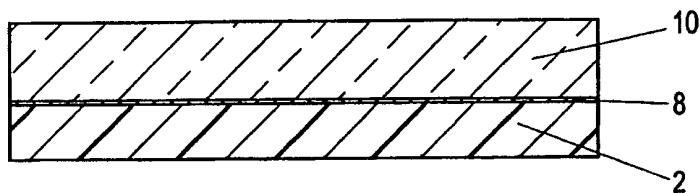

Um schließlich insgesamt eine flexible Gesamtanordnung zu erhalten, sind zwar bei der Anbringung der Dünnschichtstruktur 8 sowie der Kontaktsschichten 18 und der Deckelektroden 9 praktisch keine Abänderungen im Vergleich zu den vorstehend beschriebenen Techniken erforderlich, und insbesondere eignen sich die - extrem dünnen - Dünnschichtsysteme 8 in vorteilhafter Weise für derartige flexible Strukturen, es ist jedoch dann insofern eine Anpassung notwendig, als für die Verkapselung 10 darauf zu achten ist, dass keine starren Gläser aufgeklebt werden, sondern dass biegsame dünne Glaslaminate oder aber Polymer-Oxid-Verbundschichtsysteme oder dergl. flexible Verkapselungslagen 10 eingesetzt werden.

Eine derartige Verkapselungslage 10 aus einem flexiblen Material kann über eine Adhäsions-Zwischenschicht 44 sowie eine als Sperrsicht gegen Feuchte und Luft wirkende Passivierungsschicht 45 auf der flexiblen Leiterplatte 2 bzw. über dem darauf angebrachten Dünnschichtsystem 8 angebracht werden, wie dies schematisch in Fig. 12 dargestellt ist. Bei der Darstellung in Fig. 12 wurde im Übrigen darauf geachtet, die relativen Dickenverhältnisse möglichst maßstäblich zu veranschaulichen, wobei sich auch ergibt, dass das Dünnschichtbauelement 8 in der neutralen Ebene der gesamten flexiblen Dünnschichtanordnung zu liegen kommt. Dies wird je nach Material und Form vor allem der Verkapselungsschicht 10 sowie der flexiblen Leiterplatte 2 ungefähr in der Mittenebene der gesamten Anordnung sein.

Eine solche Dünnschichtanordnung von flexibler Natur ist in Fig. 13A nochmals, noch mehr vereinfacht, dargestellt, und in Fig. 13B ist diese Dünnschichtanordnung in einem gebogenen oder teilweise gefalteten Zustand gezeigt. Dabei wirken im Biegebereich außen auf das Material Zugkräfte ein, wie dies in Fig. 13B mit Pfeilen 46 veranschaulicht ist, wogegen im Biegebereich innen Druckkräfte wirken, die mit Pfeilen 47 in Fig. 13B gezeigt sind. Die neutrale Ebene 48, in der das Dünnschichtsystem 8 bevorzugt angeordnet wird, bleibt bei der Biegung im Wesentlichen kräftefrei, so dass dann, wenn die gesamte Anordnung einer Biegung unterworfen wird, im Dünnschichtbauelement 8 selbst keine Zug- bzw. Druckkräfte auftreten.

In Fig. 14 ist schematisch die Herstellung von Dünnschichtanordnungen mit flexiblen Leiterplatten in einem so genannten Rolle-zu-Rolle-Verfahren gezeigt. Dabei wird ein flexibles, Metallkaschiertes Basismaterial, wie z.B. eine Polyimidfolie mit Kupferkaschierung, als flexible Leiterplatten-Bahn 2' von einer Startrolle ausgehend einer Prozesskammer oder -station 51 zugeführt, wo eine fotolithografische Strukturierung durchgeführt sowie die Verstärkung 5A der Metallkaschierung 5, d.h. Leiterschicht, wie vorstehend beschrieben angebracht wird.

Über Rollen wird das Bahnmaterial 2' dann einer Prozesskammer bzw. -station 52 zugeführt, wo die Metallkaschierung 5, 5A geglättet bzw. poliert wird. Vor dem Eintritt in diese Prozesskammer 52 kann die flexible Leiterplatten-Bahn 2' rückseitig mit Hilfe einer flexible Trägerfolie 53 versteift werden, die von einer Rolle 54 abgewickelt wird. Nach dem Austritt aus der Prozesskammer 52 kann diese eine vorübergehende Versteifung bildende, flexible Trägerfolie 53 auf einer Rolle 55 aufgewickelt werden. Die Trägerfolie 53 kann aber selbstverständlich auch in einer späteren Stufe des Fertigungsprozesses wieder entfernt werden.

Im Zuge des Glättungs- bzw. Polievorganges, kann das Bahnmaterial 2' gegebenenfalls auch über einen ebenen Tisch 56 in der Prozesskammer 52 geführt werden, um so eine besonders wirksame Versteifung bzw. Stützung des Bahnmaterials 2' zu erzielen.

Das Bahnmaterial 2' gelangt sodann in einen Prozessbereich oder in eine Prozesskammer 57, wo die polierte Metallkaschierung 5, 5A veredelt (Kontaktsschicht 18) und passiviert (Passivierungsschicht 20) wird, wie dies vorstehend im Prinzip beispielsweise anhand der Fig. 4 bis 6 erläutert worden ist.

In einer Prozessstation oder -kammer 58 wird dann die Beschichtung der flexiblen Leiterplatte 2 mit den (aktiven oder passiven) Dünnschichten, z.B. 21, mit der oberen, beispielsweise lichtdurchlässigen Kontaktsschicht 22 und mit der das Dünnschichtbauelement abschließenden, gegebenenfalls ebenfalls lichtdurchlässigen Deckelektrode 9 vorgenommen. Die aktiven (oder gegebenenfalls passiven) Dünnschichten können wiederum organische oder anorganische Materialien, wie an sich bekannt, sein.

Schließlich kann die flexible Leiterplatte 2, d.h. das Bahnmaterial 2', in einer Prozessstation 59 mit Verkapselungslagen 10 beschichtet werden, welche bevorzugt als Bahnmaterial von einer Rolle 60 abgerollt, auf die flexible Leiterplatte 2' zugeführt und auflaminiert werden können. Abschließend wird das so erhaltene Bahnmaterial 61, also die flexible Dünnschichtanordnung mit flexibler Leiterplatte und flexibler Verkapselung, auf einer Rolle 62 aufgerollt und für spätere Zuschneid- bzw. Konturierungsschritte bereitgehalten.

Wie bereits vorstehend erwähnt und anhand der Fig. 13A und 13B erläutert, ist es von Vorteil, wenn die Verkapselung 10 so konzipiert wird, dass das Dünnschichtbauelement dann, wenn die Verkapselungslage in der Prozessstation 59 auf die flexible Leiterplatten-Bahn auflaminiert wird, in der neutralen Ebene 48 zu liegen kommt. Dadurch wird beim späteren Biegen des Gesamtsystems das Dünnschichtsystem 8 praktisch keiner mechanischen Beanspruchung unterworfen, so dass Delaminationen und Bruchrisse etc. vermieden werden können.

Fig. 15 veranschaulicht den mechanischen Glättungs- und Polievorgang in der Prozessstation 52 etwas detaillierter, wobei auch schematisch Glättungs- und Polierwalzen oder dergl. 63 bzw. 64 gezeigt sind. Wie erwähnt wird dabei die flexible Leiterplatte 2' auf der Rückseite mit Hilfe einer temporären Trägerfolie 53 verstellt, und sie wird überdies eben über einen Poliertisch 56 geführt, der den Glätt- bzw. Läpp- und Polierwalzen oder -scheiben 63, 64 als Unterlage dient. Die Trägerfolie 53 kann wie erwähnt in Anschluss an diesen Glättungsvorgang sofort wieder entfernt werden, sie kann aber auch zu einem späteren Zeitpunkt von der Leiterplatten-Bahn 2' weg geführt werden.

30

## Patentansprüche:

1. Dünnschichtanordnung mit einem Substrat und zumindest einem auf dem Substrat in Dünnschichttechnik aufgebrachten elektronischen Dünnschichtbauelement, wobei auf dem Substrat eine Grundelektrode vorliegt, auf der zum Dünnschichtbauelement gehörige Dünnschichten einschließlich einer oberen Deckelektrode angeordnet sind, *dadurch gekennzeichnet*, dass das Substrat durch eine an sich bekannte Leiterplatte (2) mit einem Isoliermaterial-Grundkörper (3) und einer Metallkaschierung als Leiterschicht (5) gebildet ist, dass die Leiterschicht (5) die Grundelektrode (4) bildet und hierfür zumindest an der Stelle des Dünnschichtbauelements geglättet ist, und dass zwischen der geglätteten, gegebenenfalls verstärkten Leiterschicht (5) und den darüber liegenden Dünnschichten (21) des Dünnschichtbauelements eine Kontaktsschicht (18) in Dünnschichttechnik vorgesehen ist, welche auf der Oberfläche der Grundelektrode (4) physikalisch bzw. chemisch adsorbiert ist.

2. Dünnschichtanordnung nach Anspruch 1, *dadurch gekennzeichnet*, dass in der Leiterplatte (2) Via-Verbindungen zur elektronischen Kontaktierung der Elektroden durch den Grundkörper (3) der Leiterplatte (2) hindurch vorgesehen sind.

3. Dünnschichtanordnung nach Anspruch 1 oder 2, *dadurch gekennzeichnet*, dass in der Leiterplatte (2) eine Durchkontaktierung (6) zur Grundelektrode (4) direkt unter dieser vorgesehen ist.

4. Dünnschichtanordnung nach einem der Ansprüche 1 bis 3, *dadurch gekennzeichnet*, dass

die geglättete Leiterschicht (5) über Flächenbereiche der Größe  $20 \times 20 \mu\text{m}^2$  eine mittlere Oberflächenrauigkeit von maximal 10 nm, vorzugsweise maximal 3 nm, aufweist.

5. Dünnschichtanordnung nach einem der Ansprüche 1 bis 4, *dadurch gekennzeichnet*, dass auch unter der Deckelektrode (9) eine Kontaktsschicht (22) vorgesehen ist.

6. Dünnschichtanordnung nach einem der Ansprüche 1 bis 5, *dadurch gekennzeichnet*, dass die Kontaktsschicht (18; 22) zugleich eine Passivierungsschicht für die Elektrode bildet.

10. 7. Dünnschichtanordnung nach einem der Ansprüche 1 bis 5, *dadurch gekennzeichnet*, dass die Kontaktsschicht (18; 22) zugleich eine Stabilisierungsschicht für die Haftung zwischen der Elektrode und der benachbarten Dünnschicht bildet.

15. 8. Dünnschichtanordnung nach einem der Ansprüche 1 bis 7, *dadurch gekennzeichnet*, dass die Kontaktsschicht (18; 22) eine metallische Schicht, z.B. aus Aluminium, Gold, Palladium, Platin oder einer Metalllegierung, oder Kohlenstoff oder eine halbleitende Verbindung ist.

20. 9. Dünnschichtanordnung nach einem der Ansprüche 1 bis 7, *dadurch gekennzeichnet*, dass die Kontaktsschicht (18; 22) durch eine leitfähige Suspension oder Lösung, z.B. auf Basis von Polyanilin, Polyethylen-Dioxithiophen/Polystyrolsulfonsäure, gebildet ist.

25. 10. Dünnschichtanordnung nach einem der Ansprüche 1 bis 9, *dadurch gekennzeichnet*, dass auf von der Leiterschicht (5) freigestellten, freiliegenden Bereichen des Grundkörpers (3) eine, Kontamination des jeweiligen Dünnschichtbauelements durch aus dem Grundkörper (3) austretende Substanzen verhindernde Dünnschicht-Passivierungsschicht (20) aufgebracht ist.

30. 11. Dünnschichtanordnung nach Anspruch 10, *dadurch gekennzeichnet*, dass die Passivierungsschicht (20) aus Siliziumoxid, einem Sol-Gel-System oder einer Epoxidverbindung besteht.

35. 12. Dünnschichtanordnung nach einem der Ansprüche 1 bis 11, *dadurch gekennzeichnet*, dass die Deckelektrode (9), gegebenenfalls auch die darunter vorgesehene Kontaktsschicht (22), zumindest transluzent, vorzugsweise transparent ausgebildet ist.

40. 13. Dünnschichtanordnung nach Anspruch 12, *dadurch gekennzeichnet*, dass als Dünnschichtbauelement (24) eine Elektrolumineszenzvorrichtung angeordnet ist.

45. 14. Dünnschichtanordnung nach Anspruch 13, *dadurch gekennzeichnet*, dass lokale Grundelektroden (4), die individuelle Durchkontaktierungen (6) haben, innerhalb einer isolierenden Gitterstruktur auf der Leiterplatte (2) vorliegen und darüber ein flächiges Elektrolumineszenz-Dünnschichtsystem sowie eine flächige oder aber streifen- oder symbolweise strukturierte Deckelektrode (9) angebracht sind.

50. 15. Dünnschichtanordnung nach Anspruch 12, *dadurch gekennzeichnet*, dass als Dünnschichtbauelement eine Leuchtdiode vorgesehen ist.

16. Dünnschichtanordnung nach Anspruch 12, *dadurch gekennzeichnet*, dass als Dünnschichtbauelement eine photovoltaische Anordnung vorgesehen ist.

55. 17. Dünnschichtanordnung nach einem der Ansprüche 1 bis 12, *dadurch gekennzeichnet*, dass als Dünnschichtbauelement ein Sensor, insbesondere ein optischer Sensor oder ein Temperatursensor, vorgesehen ist.

18. Dünnschichtanordnung nach einem der Ansprüche 1 bis 12, *dadurch gekennzeichnet*, dass

- als Dünnschichtbauelement eine Diode (30) vorgesehen ist.

19. Dünnschichtanordnung nach einem der Ansprüche 1 bis 12, *dadurch gekennzeichnet*, dass als Dünnschichtbauelement ein Transistor, insbesondere ein Feldeffekttransistor (40), vorgesehen ist.

- 5 20. Dünnschichtanordnung nach einem der Ansprüche 1 bis 12, *dadurch gekennzeichnet*, dass als Dünnschichtbauelement ein Überspannungsschutzelement vorgesehen ist.

- 10 21. Dünnschichtanordnung nach einem der Ansprüche 1 bis 12, *dadurch gekennzeichnet*, dass als Dünnschichtbauelement ein Widerstand und/oder ein Kondensator vorgesehen ist.

- 15 22. Dünnschichtanordnung nach einem der Ansprüche 1 bis 21, *dadurch gekennzeichnet*, dass dem Dünnschichtbauelement eine Verkapselung (10) zugeordnet ist.

23. Dünnschichtanordnung nach Anspruch 22, *dadurch gekennzeichnet*, dass die Verkapselung (10) transluzent oder transparent ausgebildet ist.

- 20 24. Dünnschichtanordnung nach Anspruch 22 oder 23, *dadurch gekennzeichnet*, dass innerhalb der Verkapselung (10) ein abgeschlossenes Gasvolumen (11) vorliegt.

- 25 25. Dünnschichtanordnung nach Anspruch 23 oder 24, *dadurch gekennzeichnet*, dass die Verkapselung Farbwandler- bzw. Indexanpassungsschichten (12) in Ausrichtung zu den lokalen Grundelektroden trägt.

26. Dünnschichtanordnung nach einem der Ansprüche 1 bis 25, *dadurch gekennzeichnet*, dass die Leiterplatte (2) eine an sich bekannte flexible Leiterplatte ist.

- 30 27. Dünnschichtanordnung nach Anspruch 26, *dadurch gekennzeichnet*, dass das Dünnschichtbauelement eine flexible Struktur hat.

28. Dünnschichtanordnung nach Anspruch 26 oder 27, soweit abhängig von einem der Ansprüche 22 bis 25, *dadurch gekennzeichnet*, dass die Verkapselung (10) flexibel ist, z.B. aus einem dünnen Glaslaminat oder einem Polymer-Oxid-Verbundschichtsystem besteht.

- 35 29. Dünnschichtanordnung nach Anspruch 28, *dadurch gekennzeichnet*, dass die Verkapselung (10) über eine Haftvermittlungsschicht (44) über dem Dünnschichtbauelement (8) angebracht ist.

- 30 30. Dünnschichtanordnung nach Anspruch 28 oder 29, *dadurch gekennzeichnet*, dass die Verkapselung (10) über eine als Sperrsicht für Feuchte und Luft dienende Passivierungsslage (45) über dem Dünnschichtbauelement (8), gegebenenfalls über der Haftvermittlungsschicht (44), angebracht ist.

- 40 31. Dünnschichtanordnung nach einem der Ansprüche 28 bis 30, *dadurch gekennzeichnet*, dass das Dünnschichtbauelement (8) in der neutralen Ebene (48) zwischen der flexiblen Leiterplatte (2) und der flexiblen Verkapselung (10) angebracht ist.

- 45 32. Dünnschichtanordnung nach einem der Ansprüche 26 bis 31, *dadurch gekennzeichnet*, dass die flexible Leiterplatte (2) transparent oder transluzent ist.

- 50 33. Dünnschichtanordnung nach einem der Ansprüche 26 bis 32, gekennzeichnet durch eine Ausbildung als aufrollbares bzw. faltbares Bahnmaterial (61).

- 55 34. Verfahren zum Herstellen einer Dünnschichtanordnung mit wenigstens einem elektroni-

schen Dünnschichtbauelement, das in Dünnschichttechnik auf einem Substrat aufgebracht wird, *dadurch gekennzeichnet*, dass als Substrat eine Leiterplatte mit einem Isoliermaterial-Grundkörper und einer Metallkaschierung als Leiterschicht verwendet wird, dass die Leiterschicht zumindest lokal, gegebenenfalls nach Anbringung einer Verstärkung, geglättet wird, um zumindest eine Grundelektrode für das Dünnschichtbauelement zu bilden, und dass auf der Grundelektrode eine Kontaktsschicht in Dünnschichttechnik angebracht wird, bevor darüber das übrige Dünnschichtbauelement angebracht wird.

5           35. Verfahren nach Anspruch 34, *dadurch gekennzeichnet*, dass die Leiterschicht durch ein mechanisches Verfahren, wie z.B. Läppen, Schleifen oder Polieren, geglättet wird.

10          36. Verfahren nach Anspruch 34, *dadurch gekennzeichnet*, dass die Leiterschicht durch elektrochemisches Polieren geglättet wird.

15          37. Verfahren nach Anspruch 34, *dadurch gekennzeichnet*, dass die Leiterschicht durch chemisch-mechanisches Polieren geglättet wird.

20          38. Verfahren nach Anspruch 34, *dadurch gekennzeichnet*, dass die Leiterschicht durch chemisches Ätzen, beispielsweise mit Schwefelsäure, Salpetersäure oder Chromschwefelsäure, geglättet wird.

25          39. Verfahren nach Anspruch 34, *dadurch gekennzeichnet*, dass die Leiterschicht durch Ionenätzten geglättet wird.

30          40. Verfahren nach Anspruch 34, *dadurch gekennzeichnet*, dass die Leiterschicht durch Beschuss mit Partikeln einzelner oder mehrerer Atome oder Moleküle, wie z.B. Argon oder Argon-Cluster, geglättet wird.

35          41. Verfahren nach einem der Ansprüche 34 bis 40, *dadurch gekennzeichnet*, dass die Leiterschicht über Flächenbereiche der Größe  $20 \times 20 \mu\text{m}^2$  bis zu einer mittleren Oberflächenrauigkeit von maximal 10 nm, vorzugsweise maximal 3 nm, geglättet wird.

40          42. Verfahren nach einem der Ansprüche 34 bis 41, *dadurch gekennzeichnet*, dass die Leiterschicht elektrochemisch verstärkt wird.

45          43. Verfahren nach einem der Ansprüche 34 bis 42, *dadurch gekennzeichnet*, dass die Leiterplatte vor einem lokalen Verstärken der Leiterschicht in den übrigen Bereichen vorübergehend fotolithografisch passiviert wird.

50          44. Verfahren nach einem der Ansprüche 34 bis 43, *dadurch gekennzeichnet*, dass von der Leiterschicht freigelegte Bereiche des Grundkörpers vor dem Anbringen des übrigen Dünnschichtbauelements fotolithografisch unterstützt in Dünnschichttechnik passiviert wird.

55          45. Verfahren nach Anspruch 43 oder 44, *dadurch gekennzeichnet*, dass eine Passivierungsschicht durch thermisches Verdampfen aufgebracht wird.

46. Verfahren nach Anspruch 43 oder 44, *dadurch gekennzeichnet*, dass eine Passivierungsschicht durch Kaltkatodenbeschichtung aufgebracht wird.

50          47. Verfahren nach einem der Ansprüche 34 bis 46, *dadurch gekennzeichnet*, dass als Substrat eine flexible Leiterplatte verwendet wird.

55          48. Verfahren nach Anspruch 47, *dadurch gekennzeichnet*, dass die flexible Leiterplatte vorübergehend, zumindest während des Glättens, durch eine Versteifungslage und/oder durch Führen über einen Tisch gestützt wird.

49. Verfahren nach Anspruch 47 oder 48, *dadurch gekennzeichnet*, dass eine flexible Leiterplatten-Bahn verwendet wird, die von einer Rolle abgewickelt wird.

50. Verfahren nach einem der Ansprüche 47 bis 49, *dadurch gekennzeichnet*, dass eine vorgefertigte flexible Verkapselungs-Bahn über der mit dem Dünnschichtbauelement versehenen flexiblen Leiterbahn angebracht wird.

51. Verfahren nach Anspruch 50, *dadurch gekennzeichnet*, dass die Verkapselungs-Bahn von einer Rolle abgewickelt wird.

10

## Hiezu 16 Blatt Zeichnungen

15

20

25

30

35

40

45

50

55

FIG. 1A

FIG. 1B

FIG. 2A

FIG. 2B

FIG. 2C

FIG. 2D

Int. Cl.<sup>8</sup>: **H05K 3/40** (2006.01)

**H05K 01/16** (2006.01)

**H05K 03/24** (2006.01)

**H01L 27/15** (2006.01)

**H05B 33/12** (2006.01)

FIG. 3A

FIG. 3B

FIG. 3C

FIG. 4A

FIG. 4B

FIG. 4C

FIG. 4D

Int. Cl.<sup>8</sup>: **H05K 3/40** (2006.01)

**H05K 01/16** (2006.01)

**H05K 03/24** (2006.01)

**H01L 27/15** (2006.01)

**H05B 33/12** (2006.01)

FIG. 5A

FIG. 5B

FIG. 5C

Int. Cl.<sup>8</sup>: **H05K 3/40** (2006.01)

**H05K 01/16** (2006.01)

**H05K 03/24** (2006.01)

**H01L 27/15** (2006.01)

**H05B 33/12** (2006.01)

FIG. 7A

FIG. 7B

FIG. 7C

FIG. 8A

FIG. 8B

FIG. 8C

FIG. 9A

FIG. 9B

FIG. 9C

FIG. 9D

FIG. 10

FIG. 11

FIG. 12

FIG. 13A

FIG. 13B

Blatt: 1 5

Int. Cl.<sup>8</sup>: H05K 3/40 (2006.01)

H05K 01/16 (2006.01)

H05K 03/24 (2006.01)

H01L 27/15 (2006.01)

H05B 33/12 (2006.01)

FIG. 14

Blatt: 1 6

Int. Cl.<sup>8</sup>: H05K 3/40 (2006.01)

H05K 01/16 (2006.01)

H05K 03/24 (2006.01)

H01L 27/15 (2006.01)

H05B 33/12 (2006.01)

FIG. 15