(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4762522号

(P4762522)

(45) 発行日 平成23年8月31日(2011.8.31)

(24) 登録日 平成23年6月17日(2011.6.17)

(51) Int.Cl.

F 1

|              |           |            |      |

|--------------|-----------|------------|------|

| HO1L 29/786  | (2006.01) | HO1L 29/78 | 618B |

| HO1L 29/78   | (2006.01) | HO1L 29/78 | 626A |

| HO1L 21/336  | (2006.01) | HO1L 29/78 | 301B |

| HO1L 21/8234 | (2006.01) | HO1L 29/78 | 301X |

| HO1L 27/088  | (2006.01) | HO1L 29/78 | 301Y |

請求項の数 13 (全 22 頁) 最終頁に続く

(21) 出願番号

特願2004-312684 (P2004-312684)

(22) 出願日

平成16年10月27日 (2004.10.27)

(65) 公開番号

特開2005-159332 (P2005-159332A)

(43) 公開日

平成17年6月16日 (2005.6.16)

審査請求日

平成19年10月10日 (2007.10.10)

(31) 優先権主張番号

特願2003-368159 (P2003-368159)

(32) 優先日

平成15年10月28日 (2003.10.28)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(74) 代理人 100116159

弁理士 玉城 信一

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 根本 幸恵

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 宮澤 尚之

最終頁に続く

(54) 【発明の名称】 半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項1】

基板上に形成した導電性を有する第1の領域上に接して、選択的に金属元素を含む領域を形成し、

前記金属元素を含む領域上に接して、半導体を呈する極細炭素繊維を前記金属元素を含む領域を触媒として前記基板に対して垂直方向に形成し、

前記極細炭素繊維の間を充填する部材を形成し、

前記極細炭素繊維を包囲するゲート絶縁膜を形成し、

前記ゲート絶縁膜に接するゲート電極を形成し、

前記極細炭素繊維と接続する導電性を有する第2の領域を前記極細炭素繊維上に形成することを特徴とする半導体装置の作製方法。 10

## 【請求項2】

基板上に形成した導電性を有する第1の領域上に接して、選択的に金属元素を含む領域を形成し、

前記金属元素を含む領域上に接して、半導体を呈する極細炭素繊維を前記金属元素を含む領域を触媒として前記基板に対して垂直方向に形成した後、半導体材料を形成し、

前記半導体材料に、レーザ光を照射して前記極細炭素繊維の間を半導体材料で充填し、

前記半導体材料の一部を除去した後、

前記極細炭素繊維を包囲するゲート絶縁膜を形成し、

前記ゲート絶縁膜に接するゲート電極を形成し、

10

20

前記極細炭素纖維と接続する導電性を有する第2の領域を前記極細炭素纖維上に形成することを特徴とする半導体装置の作製方法。

**【請求項3】**

基板上に形成した導電性を有する第1の領域上に、第1の絶縁膜を介してゲート電極を筒状に形成し、

前記ゲート電極の内表面を覆う第2の絶縁膜を形成し、

前記第2絶縁膜の一部を除去して、前記導電性を有する第1の領域を露出した後、該導電性を有する第1の領域上に接して、金属元素を含む領域を前記第2の絶縁膜内に形成し、

前記金属元素を含む領域上に接して、半導体を呈する極細炭素纖維を前記金属元素を含む領域を触媒として前記基板に対して垂直方向に形成し、

前記極細炭素纖維の間を充填する部材を形成した後、前記極細炭素纖維に接続する導電性を有する第2の領域を前記極細炭素纖維上に形成することを特徴とする半導体装置の作製方法。

**【請求項4】**

請求項1又は請求項3において、

前記極細炭素纖維の間を充填する部材は、半導体材料で形成されることを特徴とする半導体装置の作製方法。

**【請求項5】**

請求項1又は請求項3において、

前記極細炭素纖維の間を充填する部材は、絶縁材料で形成されることを特徴とする半導体装置の作製方法。

**【請求項6】**

請求項1又は請求項3において、

前記極細炭素纖維の間を充填する部材は、液滴吐出法で形成されることを特徴とする半導体装置の作製方法。

**【請求項7】**

請求項5において、

前記絶縁材料は、比誘電率が4以下の低誘電率材料であることを特徴とする半導体装置の作製方法。

20

**【請求項8】**

請求項2において、

前記レーザ光は、連続発振のレーザから照射されるレーザ光であることを特徴とする半導体装置の作製方法。

30

**【請求項9】**

請求項1乃至請求項8のいずれか一項において、

前記極細炭素纖維の領域は、チャネル形成領域であることを特徴とする半導体装置の作製方法。

**【請求項10】**

請求項1乃至請求項9のいずれか一項において、

前記金属元素を含む領域は、基板面に対して傾斜することを特徴とする半導体装置の作製方法。

40

**【請求項11】**

請求項1乃至請求項10のいずれか一項において、

前記金属元素は、ニッケル、鉄、コバルト、白金、ゲルマニウム、チタン、又はパラジウムから選ばれた元素、または前記元素を主成分とする合金材料若しくは化合物であることを特徴とする半導体装置の作製方法。

**【請求項12】**

請求項1乃至請求項11のいずれか一項において、

前記導電性を有する第1の領域及び前記導電性を有する第2の領域は、ソース領域及び

50

ドレイン領域であることを特徴とする半導体装置の作製方法。

【請求項 1 3】

請求項 1 乃至請求項 1 2 のいずれか一項において、

前記極細炭素纖維は、グラファイトナノファイバ、カーボンナノファイバ、カーボンナノチューブ、チューブ状グラファイト、カーボンナノコーン、又はコーン状グラファイトであることを特徴とする半導体装置の作製方法。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、微細構造の半導体素子、及び微細構造の半導体素子で形成される半導体装置を作製する方法に関する。 10

【背景技術】

【0 0 0 2】

近年、半導体装置を含む電気器具（ビデオカメラ、デジタルカメラ、プロジェクター、パーソナルコンピュータ、モバイルコンピュータ、携帯電話または電子書籍等）の小型化、軽量化、コストの低減に対する要求は高まるばかりである。電気器具を小型化、軽量化しても性能が落ちないことはユーザーにとって当然の要求であり、電気器具には今以上の性能が要求され続ける。なお、電気器具の機能や性能を決定するのは、システムを構成する L S I ( Large Scale Integrated Circuit の略) の特性や、電気器具の表示部における表示装置の特性である。そこで、L S I 等の半導体装置に関する微細化、高集積化や、表示装置の高輝度、高精細化に関する研究開発がさかんに進められている。これは、微細度や集積度が向上することにより、ひとつのチップに搭載できる機能が多くなるため、上記したような電気器具の小型化、軽量化、高性能化の要求を満たすためである。また、表示装置においては、画素数が増えることで高精細な画像表示が可能となる。 20

【0 0 0 3】

また、例えば、ひとつのチップに M P U 、メモリ、 I / O インターフェースなどひとつのシステム（機能回路）を構成する回路がモノリシックに搭載され、高速化、高信頼性、低消費電力化が可能なシステムオンチップが提案されている。また、前述したようなシステム（機能回路）を薄膜トランジスタ（以下、 T F T と示す。）で形成して、表示パネルと同一基板上に形成（搭載）されたシステムオンパネルが提案されている。これらを実現するために、高集積化の技術開発が続いている。また、前述したようなシステム（機能回路）を T F T で形成するためには、スイッチング速度の早い T F T を作製する必要がある。このため、 T F T の半導体領域の結晶性を高めると共に、 T F T 素子の微細化が益々必要とされており、半導体素子の各部分のサイズ（配線幅、チャネル幅、コンタクトホールの直径等）を縮小する試みがなされている。 30

【発明の開示】

【発明が解決しようとする課題】

【0 0 0 4】

しかしながら、微細化において、レジストマスクを形成する為の露光工程のアライメント精度、縮小投影露光による加工技術の精度、レジストの現像後形成されたレジストマスクの仕上り寸法、コンタクトホールを開口するために層間絶縁膜をエッチングするときの横方向のエッチング量等を精密に制御しなければならず、微細構造の半導体素子を有する半導体装置の製造を著しく困難なものとしている。 40

【0 0 0 5】

また、半導体装置の応答速度を高速にするために、半導体素子の各部分のサイズ（配線幅、チャネル幅、コンタクトホールの直径等）を縮小すると、短チャネル効果によって閾値電圧が高くなってしまい、信頼性が低下するという問題がある。

【0 0 0 6】

以上のことから、本発明では、高速化及び高集積化が可能な半導体素子、及びそれ 50

が高集積された半導体装置、並びにこれらの作製方法を提供する。

【課題を解決するための手段】

【0007】

本発明の一は、基板の厚さ方向に積層されたソース領域、チャネル形成領域、及びドレイン領域と、絶縁膜を介して前記チャネル形成領域と重畳するゲート電極とを有し、前記チャネル形成領域は、極細炭素纖維で形成されている半導体装置である。

【0008】

また、本発明の一は、基板表面上に半導体素子が形成される半導体装置であつて、前記半導体素子は、前記基板表面の垂直方向に接して積層されるソース領域、チャネル形成領域、及びドレイン領域と、前記チャネル形成領域の側面に形成されるゲート絶縁膜と、前記ゲート絶縁膜を介して前記チャネル形成領域の反対側に形成されるゲート電極とを有し、前記チャネル形成領域は、極細炭素纖維で形成されている。10

【0009】

前記極細炭素纖維は、前記極細炭素纖維を充填する部材で包囲されており、その材料は、絶縁材料又は半導体材料で形成されている。

【0010】

なお、前記極細炭素纖維を充填する部材が絶縁材料で形成されている場合は、ゲート絶縁膜としても機能する。

【0011】

前記チャネル形成領域は、一本の極細炭素纖維又は複数の極細炭素纖維で形成されている。20

【0012】

前記ソース領域又はドレイン領域と、前記極細炭素纖維との間には、金属元素を含む領域が形成されている。

【0013】

この金属元素を含む領域は、ニッケル、鉄、コバルト、白金、ゲルマニウム、チタン、パラジウム、又は亜鉛から選ばれた元素、若しくは前記元素を主成分とする合金材料若しくは化合物である。

【0014】

前記ゲート電極は、前記チャネル形成領域を囲繞している。この場合、複数のチャネル形成領域を一つのゲート電極で覆つても良い。30

【0015】

前記ゲート電極は、前記チャネル形成領域の一部を重畳している。この場合、複数のゲート電極で、チャネル形成領域を重畳してもよい。

【0016】

基板としては、単結晶シリコン基板または化合物半導体基板、若しくはガラス、石英、プラスチック、アルミナ、セラミック、又は絶縁膜が表面に形成された導電部材で形成されている。

【0017】

前記極細炭素纖維は、グラファイトナノファイバ、カーボンナノファイバ、カーボンナノチューブ、チューブ状グラファイト、カーボンナノコーン、又はコーン状グラファイトである。40

【0018】

また、本発明の一は、導電性を有する第1の領域上に、選択的に金属元素を含む領域を形成し、前記金属元素を含む領域上に極細炭素纖維を形成し、前記極細炭素纖維を包囲する絶縁膜を形成し、前記極細炭素纖維を包囲する絶縁膜に接するゲート電極を形成し、前記極細炭素纖維と接続する導電性を有する第2の領域を形成する半導体装置の作製方法である。

【0019】

また、導電性を有する第1の領域上に、第1の絶縁膜を介してゲート電極を形成し、前50

記ゲート電極の表面を覆う第2の絶縁膜を形成し、前記第1の絶縁膜の一部を除去して、前記導電性を有する第1の領域を露出した後、該導電性を有する第1の領域上に金属元素を有する領域を形成し、前記金属元素を有する領域上に極細炭素纖維を形成し、前記極細炭素纖維の間を充填する部材を形成した後、前記極細炭素纖維に接続する導電性を有する第2の領域を形成する半導体装置の作製方法である。

#### 【0020】

また、導電性を有する第1の領域上に、選択的に金属元素を含む領域を形成し、前記金属元素を含む領域上に極細炭素纖維を形成した後、半導体膜を成膜し、前記半導体膜に、レーザ光を照射して前記極細炭素纖維の間を半導体材料で形成される部材で充填し、前記半導体材料で形成される部材の一部を除去した後、前記極細炭素纖維を包囲する絶縁膜を形成し、前記極細炭素纖維を包囲する絶縁膜に接するゲート電極を形成し、前記極細炭素纖維と接続する導電性を有する第2の領域を形成する半導体装置の作製方法である。10

#### 【0021】

また、導電性を有する第1の領域上に、第1の絶縁膜を介してゲート電極を形成し、前記ゲート電極の表面を覆う第2の絶縁膜を形成し、前記第1の絶縁膜の一部を除去して、前記導電性を有する第1の領域を露出した後、該導電性を有する第1の領域上に金属元素を有する領域を形成し、前記金属元素を有する領域上に極細炭素纖維を形成した後、半導体膜を成膜し、前記半導体膜にレーザ光を照射して、前記極細炭素纖維の間を半導体材料で形成される部材で充填した後、前記半導体膜の一部を除去し、前記半導体膜及び前記ゲート電極上に第3の絶縁膜を形成し、前記第3の絶縁膜の一部を除去して前記極細炭素纖維を露出した後、導電性を有する第2の領域を形成する半導体装置の作製方法である。20

#### 【0022】

前記レーザ光は、連続発振のレーザから照射されるレーザ光である。代表的な連続発振のレーザは、Nd : YAGレーザ、Nd : YVO<sub>4</sub>レーザ、Nd : YLFレーザ、Nd : YA

IO<sub>3</sub>レーザ、ガラスレーザー、ルビーレーザー、アレキサンドライドレーザー、またはTi : サファイアレーザーである。

#### 【0023】

前記導電性を有する第1の領域及び前記導電性を有する第2の領域は、ソース領域及びドレイン領域である。30

#### 【0024】

前記極細炭素纖維は、グラファイトナノファイバ、カーボンナノファイバ、カーボンナノチューブ、チューブ状グラファイト、カーボンナノコーン、又はコーン状グラファイト。

#### 【0025】

CNTとしては、単層又は多層のものがあるか、ここではどちらを用いることもできる。

#### 【発明の効果】

#### 【0026】

極細炭素纖維は、半導体を呈する。このため、極細炭素纖維を用いた半導体素子は、電界効果トランジスタと同様に、パリスティック伝導を示す。また、極細炭素纖維は、ナノ単位であって微細であり、且つ安定性を有している。さらに、本発明の半導体素子は、基板表面に対して縦方向に積層されている。このため、微細、かつスイッチング速度が速い半導体素子を形成することができる。また、半導体素子が微細であるため、高集積された半導体装置を作製することができる。40

#### 【発明を実施するための最良の形態】

#### 【0027】

以下、発明を実施するための最良の形態について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は本実施の形態の記載内容に限定して解釈されるものではない。50

また、各図面において共通の部分は同じ符号を付して詳しい説明を省略する。

**【0028】**

(第1実施形態)

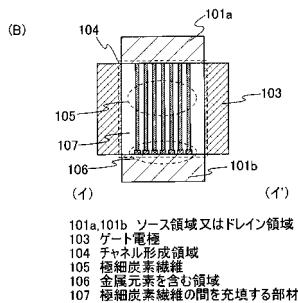

**【0029】**

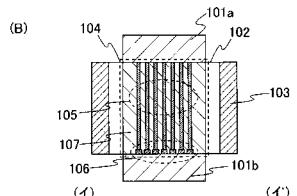

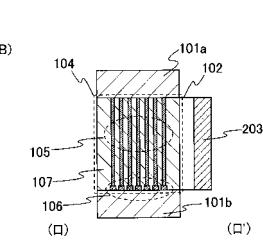

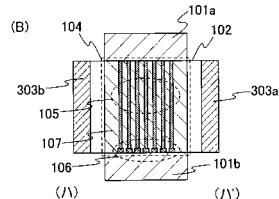

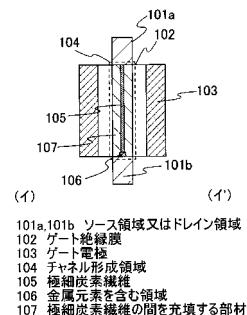

本発明の半導体素子の一実施形態を、図1を用いて説明する。本実施形態では、ゲート電極がチャネル形成領域を囲繞(包囲)している。

**【0030】**

図1(A)は、半導体素子を模式的に示す斜視図である。半導体素子は、ソース領域及びドレイン領域101a、101bと、ソース領域及びドレイン領域の間に形成されているチャネル形成領域(図示しない。)と、少なくともチャネル形成領域を覆うゲート絶縁膜102と、ゲート絶縁膜102を介してチャネル形成領域を囲繞するゲート電極103などで形成されている。

10

**【0031】**

図1(B)は、図1(A)の(イ)-(イ')を示す断面図である。ソース領域及びドレイン領域101a、101bの間に、チャネル形成領域104が形成されており、該チャネル形成領域は、ゲート絶縁膜102を介してゲート電極103に囲繞(包囲)されている。

**【0032】**

極細炭素繊維105の間には、極細炭素繊維の間を充填する部材107が形成されている。この代表例としては、絶縁材料または半導体材料で形成される。

20

**【0033】**

なお、極細炭素繊維の間を充填する部材107が、絶縁材料で形成されている場合、図12に示すようにゲート絶縁膜102を設けず、極細炭素繊維の間を充填する材料に接してゲート電極103を設けても良い。この場合、半導体素子を形成するための工程数を削減することができ、スループットを向上させることができる。

**【0034】**

極細炭素繊維の間を充填する部材107が半導体材料で形成されている場合、極細炭素繊維及びその間を充填する部材がチャネル形成領域104である。一方、極細炭素繊維の間を充填する部材が、絶縁材料で形成されている場合、チャネル形成領域104は、極細炭素繊維である。このとき、絶縁材料を、アクリル、ベンゾシクロブテン、パリレン、フレア、ポリイミド、シロキサンポリマー等の低誘電率材料(好ましくは、比誘電率が4以下の材料)を用いると、極細炭素繊維の間に生じる寄生容量を低減することができ、低消費電力及び高速動作化が可能である。

30

**【0035】**

極細炭素繊維は、ソース領域又はドレイン領域の一方上に選択的に形成された金属元素を有する領域106上に形成されており、且つソース領域又はドレイン領域の他方と接続している。金属元素を有する領域106は、金属元素で形成される領域、又は金属元素化合物で形成される領域である。本実施形態において、金属元素を有する領域106は、ニッケル元素、鉄元素、コバルト元素、白金元素、ゲルマニウム元素、チタン元素、パラジウム元素、又は亜鉛元素、若しくはこれらの元素の化合物で形成される。化合物としては、珪化物、酸化物等が挙げられる。

40

**【0036】**

なお、図13に示すように、一本の極細炭素繊維105でチャネル形成領域104を形成してもよい。この場合、より微細な半導体素子を形成することができ、高集積された半導体装置を作製することができる。

**【0037】**

ソース領域又はドレイン領域101a、101bは、導電材料で形成することができる。導電材料としては、アルミニウム、チタン、金、白金、又はタングステンの金属材料やこれらを含む合金の一種若しくは複数種を組み合わせて形成する。また、導電性を有する半導体、代表的にはp型またはn型を呈する結晶性半導体膜又は単結晶半導体基板の一部

50

であっても良い。

**【0038】**

ソース領域又はドレイン領域 101a、101b は、アルミニウム、チタン、金、白金、又はタングステンの金属材料を、スパッタリング法、蒸着法、又は CVD 法によって成膜した後、フォトリソグラフィーを行うことにより形成する。また、半導体基板に n 型または p 型を付与する不純物を、任意の領域に添加して形成する。さらには、ソース領域又はドレイン領域 101b が、絶縁性を有する基板上に形成される場合、絶縁性を有する基板上に n 型または p 型を呈する半導体膜を成膜し、公知のフォトリソグラフィー工程により所望の形状にエッチングする。又は、絶縁性を有する基板上に半導体膜を成膜し、該半導体膜に n 型又は p 型を付与する不純物元素を添加するし、公知のフォトリソグラフィー工程により、所望の形状にエッチングする。10

**【0039】**

なお、ソース領域又はドレイン領域 101a、101b は、図 14 に示すソース領域又はドレイン領域 111a、111b のように、極細炭素繊維 105 又は金属元素を有する領域 106 と接する面が、基板面に対して一定の傾斜を有する構造としても良い。この場合、極細炭素繊維の端部も、基板面に対して傾斜を有して配列している。

**【0040】**

本実施形態においては、ソース領域、ドレイン領域 101a、101b、及びチャネル形成領域 104 を円柱状として示したが、この構造に限定されるものではない。例えば、三角柱、四角柱、多角柱等の角柱構造で形成することもできる。さらには、ソース領域、ドレイン領域、チャネル形成領域の断面構造が異なるものでもよい。20

**【0041】**

本実施形態で示す半導体素子は、極細炭素繊維をチャネル形成領域に有し、かつ基板表面に対して縦方向に積層されている。このため、微細で、且つスイッチング速度が速い半導体素子である。

**【0042】**

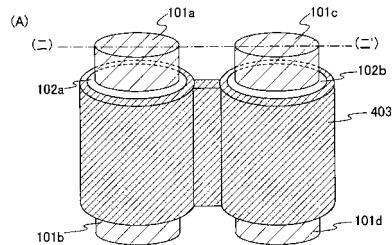

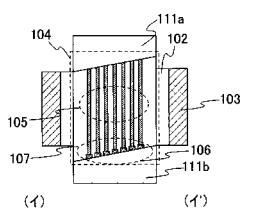

(第 2 実施形態)

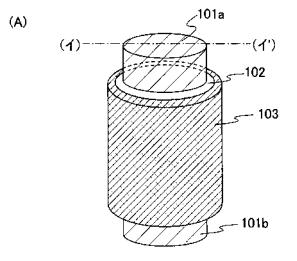

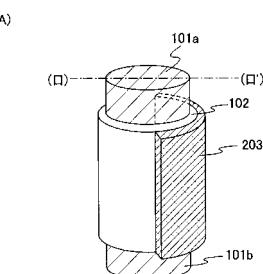

本実施形態では、実施形態 1 とは異なる構造の半導体素子を、図 2 を用いて示す。なお、図 1 と同様の部位に関しては、同じ符号を用いて説明し、各部位の詳細な説明を省略する。30

**【0043】**

図 2 (A) は、本実施形態の半導体素子を模式的に示す斜視図である。半導体素子は、ソース領域及びドレイン領域 101a、101b と、ソース領域及びドレイン領域の間に形成されているチャネル形成領域(図示しない。)と、少なくともチャネル形成領域を覆うゲート絶縁膜 102、ゲート絶縁膜 102 を介してチャネル形成領域の一部を重畳する一つのゲート電極 203 で形成されている。

**【0044】**

ゲート電極がチャネル形成領域を重畳する割合は、任意にすることができる。

**【0045】**

図 2 (B) は、図 2 (A) の (口) - (口') を示す断面図である。ソース領域及びドレイン領域の間に、チャネル形成領域 104 が形成されており、該チャネル形成領域は、ゲート絶縁膜 102 を介してゲート電極 203 に重畳されている。40

**【0046】**

極細炭素繊維 105 の間には、第 1 実施形態と同様に、極細炭素繊維の間を充填する部材が形成されている。この代表例としては、絶縁材料または半導体材料で形成される。

**【0047】**

極細炭素繊維の間を充填する部材 107 が半導体材料で形成されている場合、極細炭素繊維 105 及びその間を充填する部材 107 がチャネル形成領域である。一方、極細炭素繊維の間を充填する部材 107 が、絶縁材料で形成されている場合、チャネル形成領域は、極細炭素繊維 105 である。50

**【 0 0 4 8 】**

また、極細炭素纖維 105 は、第1実施形態と同様に、ソース領域又はドレイン領域の一方上に選択的に形成された金属元素を有する領域上に形成されており、且つソース領域又はドレイン領域の他方と接続している。

**【 0 0 4 9 】**

本実施形態で示す半導体素子は、極細炭素纖維をチャネル形成領域に有し、かつ基板表面に対して縦方向に積層されている。このため、微細で、且つスイッチング速度が速い半導体素子である。

**【 0 0 5 0 】**

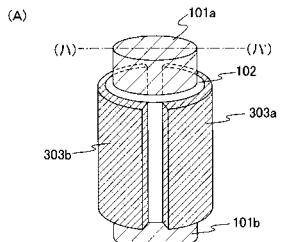

(第3実施形態)

10

本実施形態では、第1実施形態及び第2実施形態とは異なる構造の半導体素子を、図3を用いて示す。なお、図1と同様の部位に関しては、同じ符号を用いて説明し、各部位の詳細な説明を省略する。

**【 0 0 5 1 】**

図3(A)は、本実施形態の半導体素子を模式的に示す斜視図である。半導体素子は、ソース領域及びドレイン領域 101a、101b と、ソース領域及びドレイン領域の間に形成されているチャネル形成領域(図示しない。)と、少なくともチャネル形成領域を覆うゲート絶縁膜 102、ゲート絶縁膜 102 を介してチャネル形成領域の一部を重畳する複数のゲート電極 303a、303b で形成されている。本実施形態では、2つのゲート電極で形成されている。

20

**【 0 0 5 2 】**

ゲート電極がチャネル形成領域を重畳する割合、及び各ゲート電極の距離は、任意にすることができる。

**【 0 0 5 3 】**

図3(B)は、図3(A)の(ハ)-(ハ')を示す断面図である。ソース領域及びドレイン領域 101a、101b の間に、チャネル形成領域 104 が形成されており、該チャネル形成領域は、ゲート絶縁膜 102 を介して二つのゲート電極 303a、303b に重畳されている。

**【 0 0 5 4 】**

極細炭素纖維 105 の間には、実施形態1と同様に、極細炭素纖維の間を充填する部材が形成されている。この代表例としては、絶縁材料または半導体材料で形成される。

30

**【 0 0 5 5 】**

極細炭素纖維の間を充填する部材 107 が半導体材料で形成されている場合、極細炭素纖維 105 及びその間を充填する部材 107 がチャネル形成領域である。一方、極細炭素纖維の間を充填する部材 107 が、絶縁材料で形成されている場合、チャネル形成領域は、極細炭素纖維 105 である。

**【 0 0 5 6 】**

また、第1実施形態と同様に、極細炭素纖維 105 は、ソース領域又はドレイン領域の一方上に選択的に形成された金属元素を有する領域上に形成されており、且つソース領域又はドレイン領域の他方と接続している。

40

**【 0 0 5 7 】**

本実施形態で示す半導体素子は、極細炭素纖維をチャネル形成領域に有し、かつ基板表面に対して縦方向に積層されている。このため、微細で、且つスイッチング速度が速い半導体素子である。

**【 0 0 5 8 】**

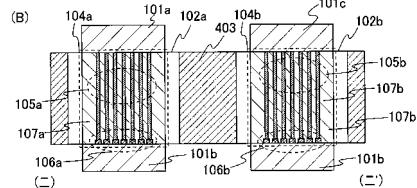

(第4実施形態)

本実施形態では、第1実施形態乃至第3実施形態とは異なる構造の半導体素子を、図4を用いて示す。なお、図1と同様の部位に関しては、同じ符号を用いて説明し、各部位の詳細な説明を省略する。

**【 0 0 5 9 】**

50

図4(A)は、本実施形態の半導体素子を模式的に示す斜視図である。半導体素子は、ソース領域及びドレイン領域101a～101dと、ソース領域及びドレイン領域の間に形成されているチャネル形成領域(図示しない。)と、チャネル形成領域を覆うゲート絶縁膜102a、102b、ゲート絶縁膜102a、102bを介してチャネル形成領域を囲繞するゲート電極403で形成されている。本実施形態では、1つのゲート電極403が2つのチャネル形成領域を囲繞している。

#### 【0060】

なお、本実施形態では、ゲート電極403は、チャネル形成領域104a、104bをそれぞれ囲繞しているが、この構造に限定されず、2つのチャネル形成領域104a、104bの一部ずつを重畠してもよい。

10

#### 【0061】

図4(B)は、図4(A)の(ハ)～(ハ')を示す断面図である。ソース領域及びドレイン領域の間(101aと101bの間、101cと101dの間)に、チャネル形成領域104a、104bが形成されており、該チャネル形成領域は、ゲート絶縁膜102a、102bを介してゲート電極403に囲繞されている。

#### 【0062】

極細炭素繊維105a、105bの間には、第1実施形態と同様に、極細炭素繊維の間を充填する部材が形成されている。この代表例としては、絶縁材料または半導体材料で形成される。

20

#### 【0063】

極細炭素繊維の間を充填する部材107が半導体材料で形成されている場合、極細炭素繊維105a、105b及びその間を充填する部材107a、107bがチャネル形成領域である。一方、極細炭素繊維の間を充填する部材107a、107bが、絶縁材料で形成されている場合、チャネル形成領域は、極細炭素繊維105a、105bである。

#### 【0064】

また、第1実施形態と同様に、極細炭素繊維105a、105bは、ソース領域又はドレイン領域の一方上に選択的に形成された金属元素を有する領域上に形成されており、且つソース領域又はドレイン領域の他方と接続している。

#### 【0065】

本実施形態で示す半導体素子は、極細炭素繊維をチャネル形成領域に有し、かつ基板表面に対して縦方向に積層されている。このため、微細で、且つスイッチング速度が速い半導体素子である。

30

#### 【0066】

##### (第5実施形態)

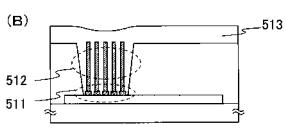

本実施形態では、第1実施形態乃至第4実施形態に示される半導体素子の作製方法について図5を用いて説明する。本実施形態では、第1実施形態で示される半導体素子の作製方法を示すが、第2実施形態乃至第4実施形態に示される半導体素子それぞれに適応することができる。

#### 【0067】

本実施形態では、基板として絶縁性を有する基板、代表的には、ガラス、石英、セラミック、又はプラスチックを用いる。ガラス基板としては、アルミニノホウケイ酸ガラス、バリウムホウケイ酸ガラス、アルミニシリケートガラスなどの無アルカリガラス基板が使用される。さらには、表面に絶縁膜を形成したシリコン基板やステンレス基板などの半導電性または導電性基板も適用可能である。

40

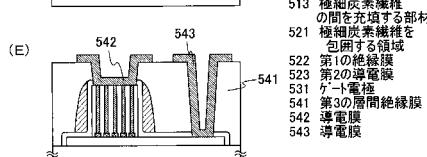

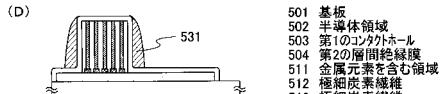

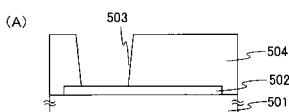

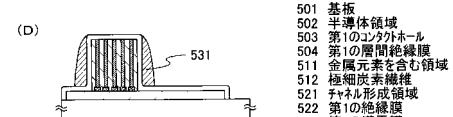

#### 【0068】

図5(A)に示すように、基板501上に所望の形状を有する半導体領域502を形成し、その上に第1の層間絶縁膜を形成する。半導体領域502は、ソース領域又はドレイン領域の一方である。

#### 【0069】

ここでは、半導体領域502は、基板上にリン(P)又はボロン(B)を含む結晶性半

50

導体膜を成膜し、フォトリソグラフィー工程により形成したレジストマスクを用いて、所望の形状にエッチングする。

#### 【0070】

第1の層間絶縁膜は、無機材料（酸化シリコン、窒化シリコン、酸化窒化シリコンなど）、又は有機材料（ポリイミド、アクリル、ポリアミド、ポリイミドアミド、ベンゾシクロブテン、またはシロキサンポリマー）を主成分とする原料を用いて層を形成する。

#### 【0071】

次に、第1の層間絶縁膜の一部上に、フォトリソグラフィー工程によりレジストマスク（図示しない。）を形成する。この後、ドライエッ칭法、ウェットエッ칭法等の公知の手法を用いて層間絶縁膜の一部を除去して、コンタクトホール503を有する第2の層間絶縁膜504を形成するとともに、半導体領域502の一部を露出する。10

#### 【0072】

次に、図5(B)に示すように、露出された半導体領域の表面に、選択的に金属元素を有する領域511を形成する。金属元素を有する領域は、少なくとも半導体領域に第1の導電膜を成膜し、リフトオフ法、エッ칭法等により第1の導電膜の一部を除去して、半導体領域上に縞状の金属元素を含む領域221を形成する。また、マスクを用いて成膜して金属元素を含む領域を形成することができる。さらには、第1の導電膜を半導体領域上に成膜した後、所定の温度で加熱して、半導体領域の表面に金属化合物（金属珪化物、金属窒化物、金属酸化物等）を形成することができる。第1の導電膜の代表例は、ニッケル元素、鉄元素、コバルト元素、白金元素、ゲルマニウム元素、チタン元素、パラジウム元素、又は亜鉛元素、若しくはこれらの元素の合金、更には化合物で形成される膜が挙げられる。20

#### 【0073】

次に、金属元素を含む領域511を触媒として極細炭素纖維512を形成する。形成方法としては、アルコールを原料ガスに用いた触媒CVD法、メタン、エチレン、またはアセチレン等の炭化水素を含む雰囲気で100～1100度、好ましくは400～650度に加熱する熱CVD法、同様の炭化水素を用い、0.1～10 torrの減圧下で形成するプラズマCVD法等がある。プラズマCVD法では、基板側に負の電圧を印加することにより、極細炭素纖維は基板に対して垂直方向に成長する。また、大気圧雰囲気で、炭化水素を原料として、パルス電圧を印加するプラズマCVD法によって、CNTを形成することもできる。30

#### 【0074】

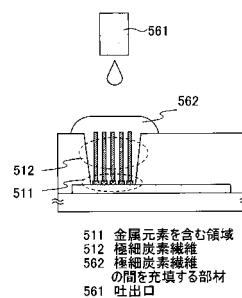

次に、極細炭素纖維の間を充填する部材513を形成する。極細炭素纖維の間を充填する部材513としては、半導体材料で形成されるもの、又は絶縁材料で形成されるものとをあげることができる。本実施形態では、絶縁材料を用いて極細炭素纖維の間を充填する部材を形成する。絶縁材料は、塗布可能な材料、代表例としては、ポリイミド樹脂、アクリル樹脂、シロキサン構造を含む樹脂、又は有機SOG(Spin on Glass)、無機SOG(Spin on Glass)等に代表される塗布シリコン酸化膜が挙げられる。無機SOGとしては、PSG(Phosphosilicate Glass)、BSG(Borosilicate Glass)、BPSG(Boronophosphosilicate Glass)、シリケート系SOG、アルコキシリケート系SOG、ポリシラザン系SOGが挙げられる。有機SOGとしては、ポリメチルシロキサンに代表される、Si-C<sub>4</sub>H<sub>9</sub>結合を有するシリコン酸化膜が挙げられる。これらを、スピンドルコートにて塗布することにより、極細炭素纖維の間を充填する。40

#### 【0075】

なお、極細炭素纖維の間を充填する部材513を図15に示すように、液滴吐出法によって、吐出口561からコンタクトホールに極細炭素纖維の間を充填する部材の材料を吐出してもよい。562は、液滴吐出法により形成した極細炭素纖維の間を充填する部材である。この方法により、所望の領域にのみ、材料を吐出することが可能であり、材料の削減、及びコスト削減を図ることができる。50

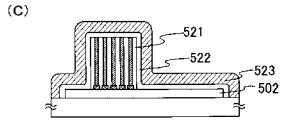

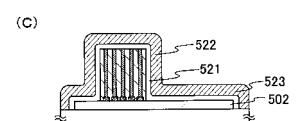

## 【0076】

次に、図5(C)に示すように、極細炭素纖維の間を充填する部材513の表面をエッティングして、極細炭素纖維512を露出させると共に、層間絶縁膜504の一部又は全部を異方性エッティングして、図5(C)の521に示すような、極細炭素纖維及びそれを包囲する領域521を形成する。なお、極細炭素纖維を包囲する領域は、極細炭素纖維の間を充填する部材の一部である。

## 【0077】

次に、極細炭素纖維及びそれを包囲する領域521を覆うように第2の絶縁膜を成膜する。該第2の絶縁膜は、後のゲート絶縁膜となる。第2の絶縁膜は、プラズマCVD法またはスパッタ法を用い、シリコンを含む絶縁膜の単層または積層構造の絶縁膜を形成する。なお、極細炭素纖維の間を充填する部材513及び第2の層間絶縁膜のエッティング条件により、極細炭素纖維及び半導体領域が絶縁膜で覆われている場合、該第2の絶縁膜を形成する必要はない。10

## 【0078】

次に、第2の絶縁膜上に、第2の導電膜523を成膜する。第2の導電膜の材料としては、単層構造又は多層構造とすることができます。ゲート電極の材料としては、タンタル(Ta)、タンゲステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ネオジム(Nd)から選ばれた元素、またはこれらの元素を主成分とする合金材料若しくは化合物材料で形成することができる。また、銀銅パラジウム合金(AgPdCu合金)を用いてもよい。さらには、リン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜を用いてもよい。20

## 【0079】

次に、図5(D)に示すように、第2の導電膜を所望の形状にエッティングして、ゲート電極531を形成する。例えば、マスクを用いず異方性エッティングを行うことにより、第1実施形態に示すような、チャネル形成領域を囲繞するゲート電極を形成することができる。また、所望の領域にマスクを用いることにより、第2実施形態乃至第4実施形態に示されるような、チャネル形成領域の一部を重畠するゲート電極を形成することができる。

## 【0080】

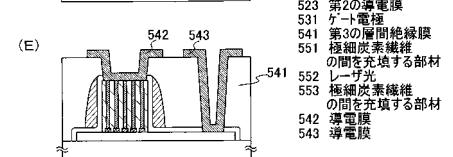

次に、図5(E)に示されるように、第3の層間絶縁膜541を形成した後、第3の層間絶縁膜の一部をエッティングしてコンタクトホールを形成すると共に、チャネル形成領域である極細炭素纖維512、及び半導体領域502をそれぞれ一部露出する。つぎに、チャネル形成領域及び半導体領域に接続する導電膜542、543を形成する。本実施形態においては、チャネル形成領域及び半導体領域に接続する導電性としては、導電性を有する結晶性半導体膜を成膜し、所望の形状にエッティングする。チャネル形成領域に接続される結晶性半導体膜は、ドレイン領域又はソース領域の他方となる。なお、本実施形態のように、チャネル形成領域に接続する導電膜と半導体領域に接続する導電膜とを、同一の層間絶縁膜上に形成しているが、この構造に限られず、異なる層で形成してもよい。30

## 【0081】

本実施形態で示す半導体素子は、極細炭素纖維をチャネル形成領域に有し、かつ基板表面に対して縦方向に積層されている。このため、微細で、且つスイッチング速度が速い半導体素子を作製することができる。40

## 【0082】

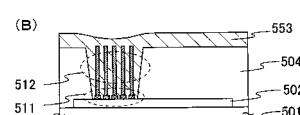

## (第6実施形態)

本実施形態では、第1実施形態乃至第4実施形態に示される半導体素子の作製方法について図6を用いて説明する。本実施形態では、第5実施形態において、極細炭素纖維の間を充填する部材として、半導体膜を用いた例を示す。

## 【0083】

図6(A)に示すように、第5実施形態の工程により、半導体領域502上に形成されたコンタクトホール内に極細炭素纖維512を形成する。

## 【0084】

10

20

30

40

50

次に、極細炭素繊維の間を充填する部材 551 を形成する。本実施形態では、極細炭素繊維の間を充填する部材 551 を、半導体材料を用いて極細炭素繊維の間を充填する部材を形成する。半導体材料の代表例としては、非晶質半導体膜又は結晶性半導体膜がある。プラズマ CVD 法、スパッタリング法により、非晶質又は結晶質の半導体膜を基板上に成膜、該半導体膜に連続発振のレーザから射出されるレーザ光 552 を照射して溶融させる。

#### 【0085】

連続発振のレーザとしては、Nd : YAG レーザ、Nd : YVO<sub>4</sub> レーザ、Nd : YLF レーザ、Nd : YAlO<sub>3</sub> レーザ、ガラスレーザー、ルビーレーザー、アレキサンドライトレーザー、または Ti : サファイアレーザー等を適宜用いることができる。

10

#### 【0086】

この結果、図 6 (B) の 553 で示されるような極細炭素繊維の間を充填する部材を形成することができる。なお、溶融した非晶質半導体膜は、極細炭素繊維の間で結晶化される。

#### 【0087】

この後、図 6 (C) ~ (E) に示すように、第 5 実施形態と同様の工程により、ゲート絶縁膜となる第 2 の絶縁膜 522、ゲート電極 531、及び導電膜 542、543、第 3 の層間絶縁膜 541 を形成する。

#### 【0088】

なお、本実施形態において、基板として絶縁性を有する基板の代わりに、単結晶半導体基板を用いることもできる。この場合、半導体領域 502 は、半導体基板の一部に不純物元素をドーピングして形成すれば良い。

20

#### 【0089】

また、極細炭素繊維の間を充填する部材 513 として絶縁材料で形成されるものを示したが、半導体材料で形成してもよい。この場合、第 1 の絶縁膜 522 は必須となる。

#### 【0090】

本実施形態で示す半導体素子は、極細炭素繊維をチャネル形成領域に有し、かつ基板表面に対して縦方向に積層されている。このため、微細で、且つスイッチング速度が速い半導体素子を作製することができる。

#### 【0091】

30

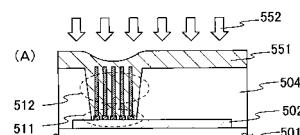

#### (第 7 実施形態)

本実施形態では、第 1 実施形態乃至第 4 実施形態に示される半導体素子の作製工程として、第 5 実施形態又は第 6 実施形態とは異なる工程を示す。本実施形態では、基板として、シリコン単結晶等の半導体材料又は半導体化合物の単結晶基板を用いた例を示す。なお、本実施形態は、ガラス基板等の絶縁表面を有する基板にも適応することができる。

#### 【0092】

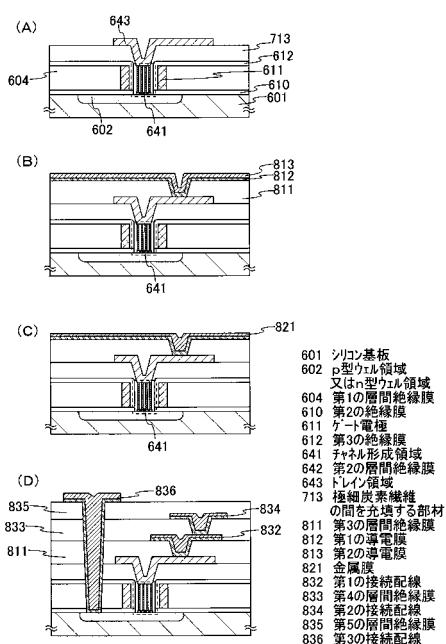

図 7 (A) に示すように、シリコン基板 601 に p 型を付与する不純物又は n 型を付与する不純物をドーピングして p 型ウェル領域又は n 型ウェル領域 602 を形成する。なお、基板として絶縁表面を有する基板、代表的には、ガラス、石英、セラミック、又はプラスチック、若しくは、表面に絶縁膜を形成したシリコン基板やステンレス基板などの半導電性または導電性基板を用いた場合は、第 5 実施形態又は第 6 実施形態に示すように、所望の形状であって、かつ導電性を有する半導体膜を形成する。

40

#### 【0093】

次に、基板表面に第 1 の絶縁膜 603 を形成する。第 1 の絶縁膜としては、プラズマ CVD 法またはスパッタリング法、熱酸化法等を用い、シリコンを含む絶縁膜の単層または積層構造の絶縁膜を形成する。

#### 【0094】

なお、第 1 の絶縁膜 603 は、p 型ウェル領域又は n 型ウェル領域 602 と後に形成されるゲート電極 611 とを絶縁するために設ける。

#### 【0095】

50

次に、第1の絶縁膜上に、第1の層間絶縁膜を形成する。層間絶縁膜としては、第5実施形態に示す第1の層間絶縁膜と同様の材料及び作製方法を適宜用いる。次に、層間絶縁膜の一部をエッティングして、コンタクトホールが形成された層間絶縁膜604を形成すると共に、第1の絶縁膜603を露出する。

#### 【0096】

次に、コンタクトホール内に第1の導電膜605を形成する。この後、第1の導電膜としては、第5実施形態の第2の導電膜523と同様の材料及び作製方法にて作製することができる。

#### 【0097】

次に、図7(B)に示すように、第1の導電膜の一部をエッティングしてゲート電極611を形成する。本実施形態においては、異方性エッティングを用いることにより第1実施形態で示されるような、チャネル形成領域を囲繞するゲート電極を形成することができる。また、エッティングする領域により、第2実施形態乃至第4実施形態に示されるようなゲート電極を適宜形成することができる。さらには、第1の導電膜を成膜する際に、マスクを用いて形成することにより、エッティング工程を経ずとも、所望の形状を有するゲート電極を形成することができる。

#### 【0098】

次に、少なくともゲート電極の露出部に第2の絶縁膜612を形成する。第2の絶縁膜の形成方法としては、第5実施形態の第2の絶縁膜と同様の手法により形成することができる。また、第2の絶縁膜も第5実施形態の第2の絶縁膜と同様の材料及び手法を用いて形成する。この後、第2の絶縁膜において、p型ウェル領域、又はn型ウェル領域と接する第2の絶縁膜の部分を、ドライエッティング又はウェットエッティングにより除去し、図6(C)に示されるようなゲート絶縁膜621を形成する。

#### 【0099】

なお、ゲート電極として、アルミニウム、タンタル、チタン等を用いて形成すると、上記の工程によりゲート絶縁膜を形成する代わりに、ゲート電極の表面を陽極酸化法又はプラズマ酸化法によりゲート絶縁膜621を形成することもできる。この工程の場合、p型ウェル領域、又はn型ウェル領域と接する第2の絶縁膜が形成されないため、工程を削減することが可能となる。

#### 【0100】

次に、第5実施形態と同様の工程により、半導体領域の表面に金属元素を含む領域511を形成した後、該領域上に極細炭素繊維512を形成する。

#### 【0101】

次に、図7(D)に示すように、第5実施形態と同様に、極細炭素繊維の間を充填する部材513を形成する。本実施形態では、極細炭素繊維の間を充填する部材513は、絶縁材料又は半導体材料で形成することができる。

#### 【0102】

次に、図7(E)に示すように、極細炭素繊維の間を充填する部材513の表面をエッティングして、極細炭素繊維の表面を露出すると共に、チャネル形成領域641を形成する。この工程は、公知のウェットエッティング法、ドライエッティング法、C P M (Chemical-Mechanical Polishing : 化学的・機械的ポリッシング)法等を用いることができる。なお、チャネル形成領域641は、極細炭素繊維512と半導体材料で形成される領域である。

#### 【0103】

次に、第2の層間絶縁膜を形成した後、該第2の層間絶縁膜の一部をエッティングしてコンタクトホールが形成された第3の層間絶縁膜642を形成すると共に、チャネル形成領域641の一部を露出する。次に、チャネル形成領域に接続するドレイン領域643を形成する。

#### 【0104】

本実施形態で示す半導体素子は、極細炭素繊維をチャネル形成領域に有し、かつ基板表

10

20

30

40

50

面に対して縦方向に積層されている。このため、微細で、且つスイッチング速度が速い半導体素子を作製することができる。

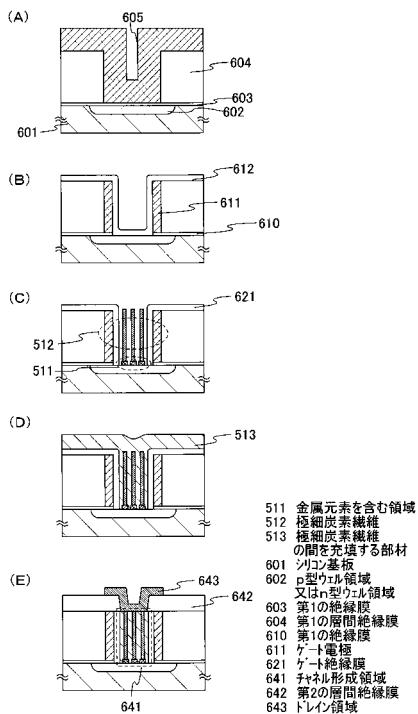

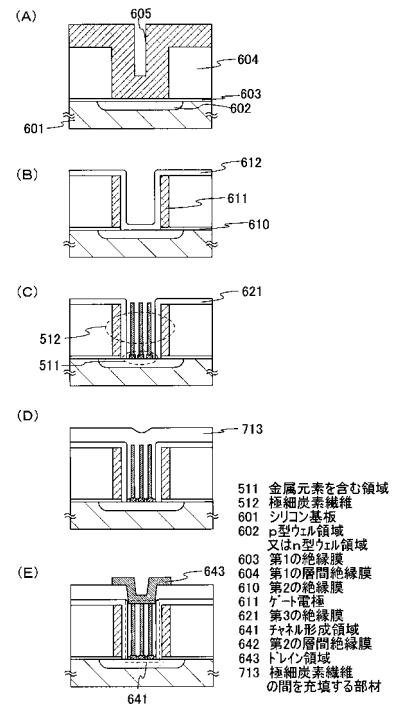

#### 【0105】

##### (第8実施形態)

本実施形態では、第1実施形態乃至第4実施形態に示される半導体素子の作製工程として、第7実施形態において、極細炭素纖維の間を充填する材料として絶縁膜を用いた構造の作製工程を示す。

#### 【0106】

図8(A)～図8(C)に示すように、第7実施形態と同様の工程により、601シリコン基板上に極細炭素纖維512、ゲート絶縁膜621、ゲート電極611を形成する。

10

#### 【0107】

次に、図8(D)に示すように、極細炭素纖維の間に極細炭素纖維の間を充填する部材713を形成する。本実施形態においては、極細炭素纖維の間を充填する部材としては、絶縁膜を形成する。絶縁膜の材料及びその形成方法は、第5実施形態の極細炭素纖維の間を充填する部材513と同様のものを適応することができる。なお、本実施形態においては、極細炭素纖維の間を充填する部材は、絶縁膜であるため、第2の層間絶縁膜としても機能する。このため、第1の層間絶縁膜及び第3の絶縁膜上に、一定の膜厚を有して形成する。

#### 【0108】

次に、図8(E)に示すように、極細炭素纖維の間を充填する部材の一部をドライエッティング法、又はウェットエッティング法等の公知の手法によりエッティングして、コンタクトホールを形成すると共に、極細炭素纖維の一部を露出する。

20

#### 【0109】

次に、チャネル形成領域641である極細炭素纖維に接続するドレン領域643を形成する。

#### 【0110】

本実施形態で示す半導体素子は、極細炭素纖維をチャネル形成領域に有し、かつ基板表面に対して縦方向に積層されている。このため、微細で、且つスイッチング速度が速い半導体素子を作製することができる。

#### 【実施例1】

30

#### 【0111】

本実施例では、第1実施形態乃至第4実施形態に示される、基板膜厚方向にソース領域、チャネル形成領域、ドレン形成領域が積層され、かつチャネル形成領域が極細炭素纖維で形成させる半導体素子が、多層配線構造を有する半導体装置の例について、図9に示す。

#### 【0112】

図9(A)に示すように、第5実施形態乃至第8実施形態に示す工程によって、基板上に基板の膜厚方向にソース領域、チャネル形成領域、ドレン形成領域が積層され、かつチャネル形成領域が極細炭素纖維で形成される半導体素子を形成する。本実施形態においては、第8実施形態で示させる工程を適応し、601シリコン基板上にp型ウェル領域又はn型ウェル領域602、該半導体領域に接続するチャネル形成領域641、該チャネル形成領域を包囲し、且つゲート絶縁膜として機能する第3の絶縁膜612、第3の絶縁膜を介してチャネル形成領域を囲繞するゲート電極611、チャネル形成領域と接続するドレン領域643を形成する。なお、ゲート電極611とp型ウェル領域又はn型ウェル領域602との間を絶縁する第2の絶縁膜610、第2の絶縁膜上であって且つゲート電極の側面に形成されている第1の層間絶縁膜604、第1の層間絶縁膜上に形成される第3の絶縁膜612、第3の絶縁膜上に形成され且つ極細炭素纖維の間を充填する部材713がそれぞれ形成されている。

40

#### 【0113】

次に、図9(B)に示すように、第2の層間絶縁膜として機能する極細炭素纖維の間を

50

充填する部材 713 及びドレン領域 643 上に第 3 の層間絶縁膜 811 を形成する。第 3 の層間絶縁膜としては、第 1 の層間絶縁膜 407 と同様の材料を用いて形成することができる。次に、第 3 の層間絶縁膜の一部をエッチングして、コンタクト孔を開口した後、第 1 の導電膜 812 及び第 2 の導電膜 813 を成膜する。第 1 の導電膜 812 としては、プロッキング効果を有する導電性材料によって形成する。第 1 の導電膜の代表例としては、Ti、TiN、TiW、Ta、TaN、WSix で形成される膜が挙げられる。第 2 の導電膜 813 としては、リフローが可能な金属材料膜 706 を成膜する。ここではアルミニウムを主成分とする合金、代表的には AlGe 膜を形成する。また、本実施例では、2 層構造の導電膜を成膜したが、これに限らず単層の導電膜、又は 3 層以上の導電膜でもよい。

10

#### 【0114】

次に、図 9 (C) に示すように、350 ~ 400 の熱処理を行って第 2 の導電膜をリフローさせて凹凸を緩和する。ここで、凹凸が緩和された金属膜 821 が形成される。第 1 の導電膜及び第 2 の導電膜を所望の形状にエッチングして、図 9 (D) に示す第 1 の接続配線 832 を形成する。

#### 【0115】

なお、第 2 の導電膜として、アルミニウムを含む合金の代わりに、銅で形成される膜を形成し、ダマシン法により接続配線を形成しても良い。銅で形成される配線は、低抵抗であり、且つ平坦性を有するため、多層配線を可能とすることで、さらなる素子の高集積化が可能である。

20

#### 【0116】

次に、層間絶縁膜の形成と、コンタクトホールの形成と、金属材料膜の形成と、リフロー処理と、エッチング処理とを同様に繰り返して、第 4 の層間絶縁膜 833、第 5 の層間絶縁膜 835、第 2 の接続配線 834、第 3 の接続配線 836 を形成する。

#### 【0117】

また、本実施例では、単結晶半導体基板上に形成された半導体素子を有する多層構造の半導体装置を示したが、これに限らず、ガラス基板等の絶縁表面を有する基板を用いた FET を有する半導体装置に適応することもできる。

#### 【0118】

本実施例で示す半導体素子は、極細炭素纖維をチャネル形成領域に有し、かつ基板表面に対して縦方向に積層されている。このため、微細で、且つスイッチング速度が速い半導体素子を作製することができる。また、多層配線構造を有しているため、さらなる素子の高集積化が可能である。

30

#### 【実施例 2】

#### 【0119】

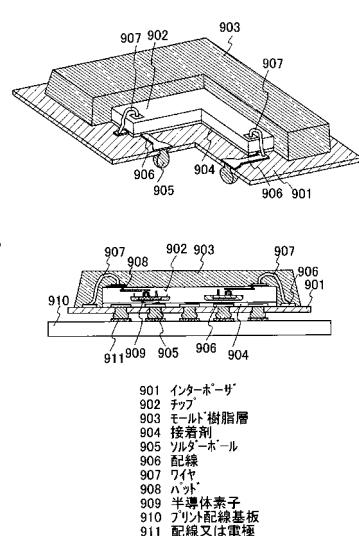

本実施例では、本発明を用いて形成する半導体素子を有する半導体装置の一例であるパッケージについて図 10 を用いて説明する。図 10 (A) に、ワイヤーボンディング法でチップがインターポーザに接続されている、パッケージの断面構造を表す斜視図を示す。901 はインターポーザ、902 はチップ、903 はモールド樹脂層に相当する。チップ 902 はインターポーザ 901 上に、マウント用の接着剤 904 によりマウントされている。

40

#### 【0120】

また図 10 (A) に示すインターポーザ 901 は、ソルダーボール 905 が設けられたボールグリッドアレイ型である。ソルダーボール 905 は、インターポーザ 901 のチップ 902 がマウントされている側とは反対の側に設けられている。そしてインターポーザ 901 に設けられた配線 906 は、インターポーザ 901 に設けられたコンタクト孔を介して、ソルダーボール 905 と電気的に接続している。

#### 【0121】

なお本実施例では、チップ 902 とソルダーボール 905 との電気的な接続をするための配線 906 を、インターポーザ 901 のチップがマウントされている面上に設けている

50

が、本発明で用いるインターポーザはこれに限定されない。例えば、インターポーザの内部において配線が多層化されて設けられていても良い。

#### 【0122】

図10(A)では、チップ902と配線906とが、ワイヤ907によって電気的に接続されている。図10(B)に、図10(A)に示したパッケージの断面図を示す。チップ902には第1実施形態乃至第4実施形態で示される半導体素子909が設けられており、またチップ902のインターポーザ901が設けられている側とは反対側に、パッド908が設けられている。パッド908は該半導体素子909と電気的に接続されている。そしてパッド908は、インターポーザ901に設けられた配線906と、ワイヤ907によって接続されている。

10

#### 【0123】

910はプリント配線基板の一部に相当し、911はプリント配線基板910に設けられた配線または電極に相当する。配線906はソルダーボール905を介して、プリント配線基板910に設けられた配線または電極911に接続される。なおソルダーボール905と、配線または電極911との接続は、熱圧着や、超音波による振動を加えた熱圧着等様々な方法を用いることができる。なお、アンダーフィルで圧着後のソルダーボール間の隙間を埋めるようにし、接続部分の機械的強度や、パッケージで発生した熱の拡散などの効率を高めるようにしても良い。アンダーフィルは必ずしも用いる必要はないが、インターポーザとチップの熱膨張係数のミスマッチから生ずる応力により、接続不良が起こるのを防ぐことができる。超音波を加えて圧着する場合、単に熱圧着する場合に比べて接続不良を抑えることができる。

20

#### 【0124】

なお、本実施例においては、チップがワイヤーボンディング法によってインターポーザに接続されているパッケージを示したがこれに限られない。フリップチップ法を用いてこれらを接続しても良い。この場合、接続するべきパッドの数が増加しても、ワイヤーボンディング法に比べて、比較的パッド間のピッチを広く確保することができるので、端子数の多いチップの接続に向いている。

#### 【0125】

また、パッケージ内においてチップを積層してもよい。この場合、一つのパッケージ内に複数のチップを設けることができるため、パッケージ全体の大きさを抑えることができるというメリットを有している。

30

#### 【0126】

さらには、複数のパッケージを積層してもよい。この構造では、パッケージごとに電気的な検査を行い、良品だけを選別してから積層することができるので、歩留りを高めることができるというメリットを有している。

#### 【0127】

本発明により、歩留まり高く高集積化された半導体装置を作製することができる。

#### 【実施例3】

#### 【0128】

本実施例では、本発明を用いて形成する半導体素子を有する半導体装置の一例である表示装置について説明する。

40

#### 【0129】

本発明を用いて形成する半導体素子を、液晶表示装置、有機発光素子に代表される発光素子を各画素に備えた発光装置、DMD(Digital Micromirror Device)、PDP(Plasma Display Panel)、FED(Field Emission Display)等の表示装置の駆動を制御する各種回路に用いることができる。

#### 【0130】

本実施例で示す半導体素子は、極細炭素繊維をチャネル形成領域に有し、かつ基板表面に対して縦方向に積層されている。このため、スイッチング速度が速い半導体素子が高集

50

積された半導体装置である。

【実施例 4】

【0131】

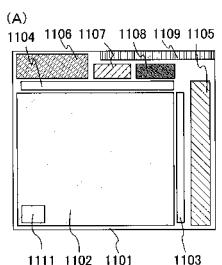

本発明を実施して得た半導体装置を組み込むことによって様々な電子機器を作製することができる。電子機器としては、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、オーディオコンポ等)、ノート型パーソナルコンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDigital Versatile Disc(DVD)等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置)などが挙げられる。電子機器の1つであるカーナビゲーションを例に挙げ、本発明の素子が実際に電子機器に実装されている様子を図11(A)に示す。

【0132】

図11(A)に示すナビゲーションシステムの表示部のモジュールは、基板上に画素部1102、画素部の表示を制御する走査線駆動回路1103、信号線駆動回路1104、コントロール回路1105、オーディオ用回路1106、映像信号処理回路1107、SRAM1108等が設けられている。本実施例では、基板1101はガラス基板である。

【0133】

また、FPC1109によって、外部に設けられているプリント配線基板と接続されている。

20

【0134】

図11(B)には、基板1001上に形成された各回路のブロック図を示す。なお、画素部1102に液晶素子が形成される場合の回路について説明する。画素部1102は、階調電源1111を有する。画素部1102の周囲には、走査線駆動回路1103と、信号線駆動回路1104とが設けられている。なお、画素部1102は、発光素子、DMD素子、電界放出素子等を用いてもよい。

【0135】

コントロール回路1105は、CPU1112、CPU用インターフェース(I/F)1113、CPUが使用するスタック・変数用SRAMとして機能するWRAM1114、プログラムと画像データが格納されているマスクROMとして機能するPROM1115、PROMとWRAMのアドレス・データバスのインターフェース及びWRAM用アドレスの一部をデコードしてオーディオ用回路を制御する信号を作製する機能を有するメモリーコントローラ1116、を有している。

30

【0136】

オーディオ用回路1106は、音声データが格納されているマスクROMとして機能するオーディオROM1121、オーディオ用回路のクロック信号を作製したり、カウンタを使ってオーディオROMのアドレスを作製する機能を有するオーディオコントローラ1122、デジタル音声データからアナログ波形を作製したり、アナログ波形を増幅する機能を有するアンプ1123を有する。

40

【0137】

映像信号処理回路1107は、画像データの色情報を格納するSRAMとして機能するCRAM1131を有する。

【0138】

さらに、画像の座標情報や画像一行分の画像情報を格納するSRAM1108が設けられている。

【0139】

これら機能を有する各回路は、プリント基板(図示しない)に設けられた電源回路からの電源が、FPC1109を介して供給される。

【0140】

50

また、FPC1109を介して、外部に設けられたキーボードからの入力信号、メモリ、クロック、スピーカー、電源等の信号を入出力する。

#### 【0141】

本発明で作製される半導体素子は、微細且つ高速度動作が可能であるため、図11(A)に示される各回路の半導体素子の作製に本発明を適応することにより、高精細な表示を有し、且つ応答の少ないナビゲーションシステムを作製することが可能である。

#### 【図面の簡単な説明】

#### 【0142】

【図1】本発明に係る半導体素子を説明する断面図。

10

【図2】本発明に係る半導体素子を説明する断面図。

【図3】本発明に係る半導体素子を説明する断面図。

【図4】本発明に係る半導体素子を説明する断面図。

【図5】本発明に係る半導体素子の作製工程を説明する断面図。

【図6】本発明に係る半導体素子の作製工程を説明する断面図。

【図7】本発明に係る半導体素子の作製工程を説明する断面図。

【図8】本発明に係る半導体素子の作製工程を説明する断面図。

【図9】本発明に係る半導体装置の作製工程を説明する断面図。

【図10】本発明に係る半導体装置の作製工程を説明する断面図。

【図11】本発明に係る電子機器を説明する断面図。

20

【図12】本発明に係る半導体素子を説明する断面図。

【図13】本発明に係る半導体素子を説明する断面図。

【図14】本発明に係る半導体素子を説明する断面図。

【図15】本発明に係る半導体素子の作製工程を説明する断面図。

【図1】

101a,101b ソース領域又はドレイン領域

102 ゲート絶縁膜

103 ゲート電極

104 チャネル形成領域

105 極細炭素繊維

106 金属元素を含む領域

107 極細炭素繊維の間を充填する部材

【図2】

101a,101b ソース領域又はドレイン領域

102 ゲート絶縁膜

203 ゲート電極

104 チャネル形成領域

105 極細炭素繊維

106 金属元素を含む領域

107 極細炭素繊維の間を充填する部材

【図3】

101a,101b ソース領域又はドレイン領域

102 ゲート絶縁膜

303a,303b ゲート電極

104 チャネル形成領域

105 極細炭素繊維

106 金属元素を含む領域

107 極細炭素繊維の間を充填する部材

【図4】

101a～101d ソース領域又はドレイン領域

102a,102b ゲート絶縁膜

403 ゲート電極

104a,104b チャネル形成領域

105a,105b 極細炭素繊維

106a,106b 金属元素を含む領域

107a,107b 極細炭素繊維の間を充填する部材

【図5】

501 基板

502 半導体領域

503 第1のコンタクトホール

504 第2の層間絶縁膜

511 金属元素を含む領域

512 極細炭素繊維

513 極細炭素繊維の間を充填する部材

521 極細炭素繊維を包埋する領域

522 第1の絶縁膜

523 第2の導電膜

531 ゲート電極

541 第3の層間絶縁膜

542 保護膜

543 導電膜

【図6】

501 基板

502 半導体領域

503 第1のコンタクトホール

504 第2の層間絶縁膜

511 金属元素を含む領域

512 極細炭素繊維

521 チャネル形成領域

522 第10の絶縁膜

523 第20導電膜

531 ゲート電極

541 第30層間絶縁膜

551 極細炭素繊維の間を充填する部材

レーザ光

553 極細炭素繊維の間を充填する部材

542 保護膜

543 導電膜

【図7】

【図8】

【図9】

【図10】

【 义 1 1 】

This diagram illustrates the internal structure of the main board assembly. It features a central vertical bus bar with various components connected to it. Labels indicate the following components and their connections:

- (B) 1104 1106 1121 1122 1123

- 1107

- 1131

- 1108

- 1112

- 1113

- 1114

- 1115

- 1116

- 1105

- 1111 1102 1101 1103

- 1101 基板

- 1102 画素部

- 1103 走査線駆動回路

- 1104 信号線駆動回路

- 1105 コントロール回路

- 1106 オーディオ用回路

- 1107 映像信号処理回路

- 1108 SRAM

- 1109 FPC

- 1111 障害電源

- 1112 フレーム

- 1113 レンズ

- 1114 WRAM

- 1115 PROM

- 1116 メモリコントローラ

- 1121 オーディオROM

- 1122 オーディオコントローラ

- 1123 アップ

- 1131 CRAM

( 12 )

【 図 1 3 】

【习题 1-4】

- 111a,111b ソース領域又はドレン領域

- 102 ゲート絶縁膜

- 103 ゲート電極

- 104 チャネル形成領域

- 105 極細炭素繊維

- 106 金属元素を含む領域

- 107 極細炭素繊維の間を充填する部材

【习题 15】

---

フロントページの続き

| (51)Int.Cl.            | F I               |

|------------------------|-------------------|

| H 01 L 29/06 (2006.01) | H 01 L 27/08 102B |

| H 01 L 29/12 (2006.01) | H 01 L 27/08 102E |

|                        | H 01 L 29/06 601B |

|                        | H 01 L 29/06 601N |

|                        | H 01 L 29/78 652T |

|                        | H 01 L 29/78 653B |

|                        | H 01 L 29/78 653D |

(56)参考文献 特開2002-110977(JP,A)

特開2003-086796(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 29 / 78 - 29 / 786

H 01 L 29 / 00 - 29 / 38

H 01 L 27 / 06 - 27 / 092

H 01 L 21 / 336

J S T P l u s ( J D r e a m I I )