(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3655175号

(P3655175)

(45) 発行日 平成17年6月2日(2005.6.2)

(24) 登録日 平成17年3月11日(2005.3.11)

(51) Int.C1.<sup>7</sup>

F 1

H01L 27/105

H01L 27/10 444B

H01L 21/336

H01L 29/78 652N

H01L 29/78

H01L 29/78 653A

H01L 29/78 653C

H01L 29/78 656Z

請求項の数 5 (全 25 頁) 最終頁に続く

(21) 出願番号

特願2000-199935 (P2000-199935)

(22) 出願日

平成12年6月30日 (2000.6.30)

(65) 公開番号

特開2002-26279 (P2002-26279A)

(43) 公開日

平成14年1月25日 (2002.1.25)

審査請求日

平成15年10月20日 (2003.10.20)

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100075683

弁理士 竹花 喜久男

(74) 代理人 100084515

弁理士 宇治 弘

(72) 発明者 川久保 隆

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝 研究開発センター内

審査官 國島 明弘

最終頁に続く

(54) 【発明の名称】半導体記憶装置の製造方法

(57) 【特許請求の範囲】

【請求項1】

基板の一主面に設けられた単結晶半導体層の面に第1の不純物領域を形成し、縦型電界効果トランジスタの一方のソースまたはドレインのいずれかを形成する工程と、

前記第1の不純物領域上に下部キャパシタ電極層、強誘電体膜および上部キャパシタ電極からなる積層膜をこの順序でエピタキシャル成長する工程と、

前記下部キャパシタ電極層、強誘電体膜および上部キャパシタ電極を所要の形状にパターニングし、複数のキャパシタを形成する工程と、

前記複数のキャパシタ下の単結晶半導体層を残して前記単結晶半導体層を選択的に除去し、複数のキャパシタ下に単結晶半導体柱状部を形成する工程と、

前記複数の柱状部の側壁にゲート絶縁膜を形成して前記柱状部をチャネル部とし、前記柱状部のそれぞれの下部に隣接する位置の前記単結晶半導体層に第2の不純物領域を形成して他方のソースまたはドレイン領域とした縦型電界効果トランジスタを形成する工程と、

を具備してなる半導体記憶装置の製造方法。

【請求項2】

前記複数の単結晶半導体柱状部の形成工程は、

ピット線の延長方向に相互に隣接する単結晶半導体柱状部間の間隔は、ワード線の延長方向に相互に隣接する単結晶半導体柱状部間の間隔よりも大きく設定する工程を含み、前記ワード線は前記ピット線と実質的に直角に交差することを特徴とする請求項1記載の半導

体記憶装置の製造方法。

【請求項 3】

前記積層膜をエピタキシャル成長する前に、第1の不純物層にバリア層を生成する工程を含むことを特徴とする請求項1記載の半導体記憶装置の製造方法。

【請求項 4】

複数のキャパシタを形成後、複数のキャパシタのそれぞれの側壁に層間絶縁膜を形成する工程を含むことを特徴とする請求項1記載の半導体記憶装置の製造方法。

【請求項 5】

複数の縦型電界効果トランジスタの形成工程は、複数のキャパシタとともに複数の縦型電界効果トランジスタを自己整合的に形成する工程を含むことを特徴とする請求項1記載の半導体記憶装置の製造方法。 10

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、半導体記憶装置の製造方法に関する。

【0002】

【従来の技術】

最近、記憶媒体として強誘電体膜をキャパシタに用い、スイッチング素子として電界効果トランジスタを用いた記憶装置（強誘電体メモリ）の開発が行われてあり、一部にはすでに実用化されている。強誘電体メモリは、電圧を切った状態でも、強誘電体が自発分極により電位差を発生させその状態を保っている現象を利用した不揮発性メモリであり、電源を落とした後も記憶内容が失われないという特徴がある。しかも強誘電体膜の膜厚が十部薄い場合には自発分極の反転が速く、DRAM並みに高速の書き込み、読み出しが可能であるなどの特徴を持つ。 20

【0003】

このような特徴をもつ強誘電体メモリであるが、一般に強誘電体膜として使用されている  $Pb(Zr, Ti)_O_3$  や  $SrBi_2Ta_2O_7$  は低融点金属である鉛やビスマスを主成分として含むために不安定であり、薄膜化が難しい、シリコンプロセス中で劣化してしまう、などの問題点を抱えており、強誘電体メモリ本来の実力を発揮できていない。

【0004】

これに対して強誘電体膜である  $BaTiO_3$  は熱力学的に安定で、薄膜化が可能で、シリコンプロセス中でも劣化しないという特徴がある。しかしながらキュリー温度が低いために強誘電特性が一定でないなど十分ではない。 30

【0005】

これに対して  $BaTiO_3$  を下地に対してエピタキシャル成長させ、かつ下地との格子不整合を利用して歪を導入した場合に、非常に良い強誘電特性が得られる。すなわち、強誘電体材料系として安定な  $BaTiO_3$  を使用し、下地に対してエピタキシャル成長させたエピタキシャル・キャパシタが作成できれば、理想的な強誘電体メモリが実現できる。

【0006】

一方DRAMなどに用いられる主にシリコン酸化膜等の常誘電体膜を有するキャパシタの場合には、結晶構造は単結晶でなくても十分なキャパシタ特性を達成できる。したがってDRAMでは半導体基板表面に形成されたトランジスタ上に層間絶縁膜を形成し、この層間絶縁膜上に直接常誘電体キャパシタを形成できるので多層構造化が容易にできる。したがってDRAMは容易に高集積化が可能となる。 40

【0007】

しかしながら強誘電体メモリに用いるエピタキシャル・キャパシタの場合には非晶質からなる層間絶縁膜上に直接エピタキシャル成長することはできず、何らかの方法で下地に単結晶Si表面を利用することが必須である。例えばトランジスタが形成された面と同じ単結晶Si基板表面内にエピタキシャル・キャパシタを形成しメモリセルを構成することができる。もちろんこの場合1ビットのスペースは多層構造とする場合よりも2倍以上占め 50

ることとなり、更なる高集積化には向いていない。

【0008】

以上の点に鑑みて、強誘電体メモリを多層化し、高集積化する提案がいくつかなされている。

【0009】

その一つとして、予めトランジスタを形成したSi基板上にトランジスタを覆う層間絶縁膜を形成し、トランジスタのソース電極或いはドレイン電極の一方の電極上に開口部（コンタクトホール）を形成し、この開口部内に気相からの選択エピタキシャル成長或いは非晶質からの固相エピタキシャル成長により単結晶Siストレージノードを形成する。次に、この単結晶Siストレージノード上にエピタキシャル成長によりエピタキシャル・キャパシタを作成する方法（特開平8-139292号公報）が提案されている。

10

【0010】

この方法によりエピタキシャル・キャパシタを多層化できるので、トランジスタとキャパシタを同一Si基板平面上に形成するよりは集積化に適する。しかしながら更に高集積化させる場合には、トランジスタのソース電極或いはドレイン電極の一方の電極上に形成するコンタクトホールを細く形成しなければならず、コンタクトホールの深さと幅のアスペクト比が大きくなり、この中にシリコンを一つの単結晶状に形成するのが困難になるという問題が懸念される。

【0011】

これを回避するために、成長温度を高温にするほど選択性が高まるというシリコンの選択成長の特性を利用して、より高温成長させて単結晶シリコンを形成することが考えられる。しかしながらトランジスタの耐熱性から基板温度を750から800程度以上には上げられず単結晶シリコンを形成するにも限界がある。このような観点から、高いアスペクト比で単結晶Siストレージノードを選択エピタキシャル成長させるための成長条件は非常に狭く一つのメモリデバイスの中に数十メガ個以上の数のプラグを作製する際の歩留まりを考慮すると解決すべき技術課題が大きいと予想される。

20

【0012】

また他の作成法としてエピタキシャル・キャパシタを形成した第一のシリコン基板とトランジスタを形成した第二のシリコン基板を貼り合せる方法（特開平11-74477号公報）が提案されている。しかしながら基板を貼り合わせる際に伴うトランジスタやエピタキシャル・キャパシタに与える衝撃や、基板を再研磨する場合の精度の問題、各ビット間の特性がばらつく問題などを考慮するとやはり解決すべき技術課題が大きい。

30

【0013】

【発明が解決しようとする課題】

本発明者らは、上記問題に鑑み、強誘電体メモリの多層化を行なうにあたり、基板表面に対して垂直方向の導通が得られるように延在するチャネル層を持つ縦型電界効果トランジスタに着目した。

【0014】

縦型電界効果トランジスタとは、半導体基板上に形成された半導体の柱状部に対して下からソース又はドレインの内の何れか一方として機能する下部ソースドレイン領域、半導体層、ソース又はドレインの内の一方に対し他方として機能する上部ソースドレイン領域が形成され、半導体層の側面にゲート絶縁膜を介してゲート電極が形成されたものである。この縦型電界効果トランジスタは上部ソースドレイン領域から下部ソースドレイン領域或いは下部ソースドレイン領域から上部ソースドレイン領域、すなわち半導体基板に対して垂直方向に電流が流れるチャネル部がある。

40

【0015】

このような縦型電界効果トランジスタにおいては単結晶半導体からなる上部ソースドレイン領域が半導体基板の上面に位置しており、この上部ソースドレイン領域の単結晶表面を下地層としてエピタキシャル・キャパシタを形成することで強誘電体メモリの多層化を達成できると考えられる。

50

## 【0016】

しかもこの方法は、最小加工寸法を  $F$  とするとメモリセルサイズは最小のクロスポイントセルである  $4F^2$  まで縮小可能であるというメリットもある。そのときのエピタキシャル・キャパシタの面積は  $F^2$  となりもっとも高い集積化を達成できる。

## 【0017】

そこで実際に半導体基板に縦型電界効果トランジスタを作成し、単結晶シリコンを表面に有する上部ソースドレイン領域上に、フォトリソグラフィ技術を用いてエピタキシャル・キャパシタを作成し、強誘電体メモリを作成してみた。

## 【0018】

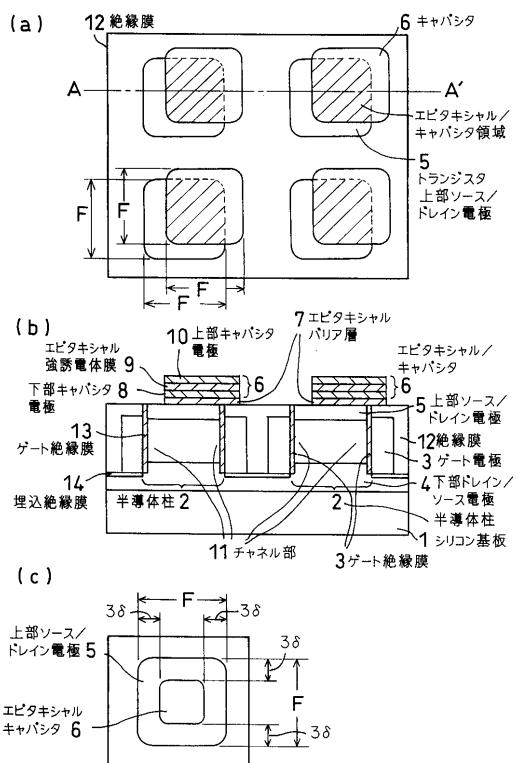

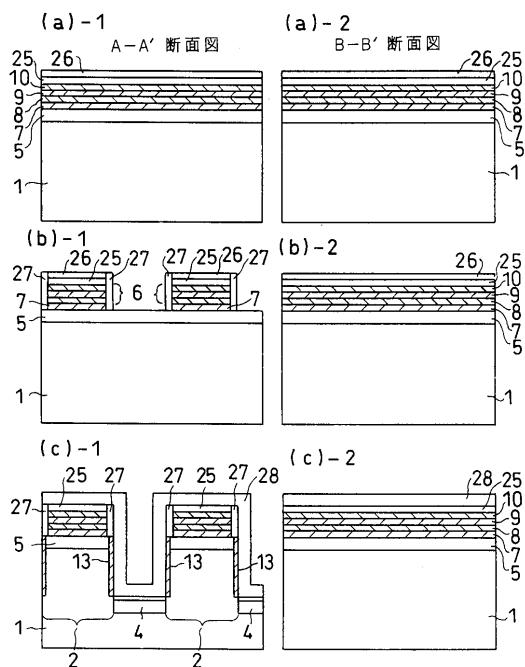

図1に、この強誘電体メモリの縦型電界効果トランジスタとエピタキシャル・キャパシタの位置関係を示す。図1(a)は平面図、図1(b)は図1(a)平面図のA-A'断面の断面図である。

## 【0019】

図1(a)(b)に示すように、この強誘電体メモリは、Si基板1上に、半導体の柱状部2が形成されている。この柱状部2の側面にはゲート絶縁膜13を介してゲート電極3が形成されている。柱状部2とゲート絶縁膜13の界面付近には、Si基板1に対して垂直方向の導通が得られるように延在するチャネル部11が形成されている。柱状部2上には、ソース又はドレインの内の何れか一方として機能する上部ソースドレイン領域5が形成されている。また柱状部2の下には、ソース又はドレインの一方に対して他方として機能する下部ソースドレイン領域4が形成されている。ゲート電極3と下部ソースドレイン領域4は埋め込み絶縁膜14(シリコン酸化膜)によって電気的に隔離されている。これらの構造によって縦型電界効果トランジスタを構成している。この縦型電界効果トランジスタは層間絶縁膜12(非晶質)により埋め込まれている。

## 【0020】

単結晶シリコンを表面に有する上部ソースドレイン領域5上には、バリア層7がエピタキシャル成長している。このバリア層7上には、下部キャパシタ電極層8、強誘電体膜9及び上部キャパシタ電極層10からなるエピタキシャル・キャパシタ6がエピタキシャル成長している。

## 【0021】

この強誘電体メモリを作成するにあたって、非晶質の層間絶縁膜12に囲まれた  $F^2$  の面積の上部ソースドレイン領域5上に、 $F^2$  の面積のエピタキシャル・キャパシタ6を最大合わせ誤差3で形成した場合、上部ソースドレイン領域5のパターンとエピタキシャル・キャパシタ6のパターンが重なるのは図1(a)中にハッチングで示した領域のみである。それ以外のキャパシタ6のパターンが上部ソースドレイン領域5に重ならない部分は、非晶質の層間絶縁膜12上に形成されることとなる。非晶質の層間絶縁膜12上に形成されたキャパシタ6は下部キャパシタ電極層7、強誘電体膜9及び上部キャパシタ電極層10がエピタキシャル成長せず多結晶化してしまう。

## 【0022】

したがってキャパシタ特性は優れたエピタキシャル・キャパシタ特性(上部ソースドレイン領域4と重なっている領域)と劣った多結晶キャパシタ特性(非晶質層間絶縁膜12上に形成された領域)の混じったものとなり、残留分極値が小さくリーク電流が大きくなる問題が生じた。

## 【0023】

上記問題に鑑み、図1(c)に示すように、前後左右の最大合わせ誤差を考慮してキャパシタ面積を上部ソースドレイン領域5よりも十分小さくして、エピタキシャル成長したエピタキシャル・キャパシタ6を作成した場合、キャパシタ面積は  $(F - 2 \times 3)^2$  のとなる。この場合3が30%程度であることを考慮すると、本来  $F^2$  の面積を利用できるのが、わずか20%程度しか利用できず極めて面積利用効率の悪いものであった。

## 【0024】

本発明は上記の問題点を解決するためになされたものであり、縦型電界効果型トランジ

10

20

40

50

スタの上部ソースドレイン領域上にエピタキシャル・キャパシタを自己整合的に形成することが可能な半導体記憶装置の製造方法を提供することを目的とする。

【0025】

【課題を解決するための手段】

上記目的を達成するために、第1の発明は、一主面に単結晶半導体層を有する基板と、前記基板上に形成され、前記一主面に対して垂直方向の導通が得られるように延在するチャネル部と、

前記チャネル部の導通方向に沿う側表面に形成されたゲート絶縁膜、及びこのゲート絶縁膜を介して形成されたゲート電極と、

前記チャネル部上に前記単結晶半導体層の表面を有するように形成され、ソース又はドレインの内の何れか一方として機能する一方領域と、

前記チャネル部下に形成され、前記ソース又はドレインの一方に対し他方として機能する他方領域と、

前記一方領域の前記単結晶半導体層の表面上にエピタキシャル成長された、下部キャパシタ電極層、強誘電体膜及び上部キャパシタ電極層を備えるキャパシタとを具備することを特徴とする半導体記憶装置を提供する。

【0026】

前記キャパシタの側壁に、これを被服するキャパシタ絶縁側壁とを具備することが好ましい。

【0027】

エピタキシャル・キャパシタをマスクとして下地の単結晶半導体層をエッチングする際、エピタキシャル・キャパシタの側壁に絶縁膜側壁を設けることでエッチングによる欠陥発生を防止できる。

【0028】

また、前記一方領域と前記下部キャパシタ電極層間にエピタキシャル成長されたバリア層が形成されていることが好ましい。

【0029】

上部ソースドレイン領域上に、この上部ソースドレイン領域表面を酸化させないように酸素をブロックするためのバリア層を形成することで、絶縁体化することを防ぐと共に、キャパシタがエピタキシャル成長しやすくすることができる。バリア層としては導電性の立方晶系のものが好ましい。

【0030】

第2の発明は、一主面に単結晶半導体層を有する基板と、

前記基板上に選択的に形成され、一主面に対して垂直方向に導通するチャネル部となるよう柱状にされた複数の半導体柱状部と、

前記柱状部の側面に形成されたゲート絶縁膜と、

前記柱状部の側面に前記ゲート絶縁膜を介して形成されたゲート電極と、

前記柱状部の頂部に形成されたソース又はドレインの内の何れか一方として機能する一方領域と、

前記柱状部の基板側に形成され、前記ソース又はドレインの一方に対し他方として機能する他方領域と、

前記一方領域場に形成された、前記柱状部の頂部平面形状と一致する形状の下部キャパシタ電極層、強誘電体膜及び上部キャパシタ電極層とを具備することを特徴とする半導体記憶装置を提供する。

【0031】

第3の発明は、一主面に単結晶半導体層を有する基板の前記単結晶半導体層の表面上に、下部キャパシタ電極層、誘電体膜及び上部キャパシタ電極層をこの順にエピタキシャル成長する工程と、

前記下部キャパシタ電極層、誘電体膜及び上部キャパシタ電極層を所望の形状にパターニングしてキャパシタを形成する工程と、

10

20

30

40

50

前記キャパシタ下の前記単結晶半導体層を残すように前記単結晶半導体層を選択的に除去することにより前記キャパシタ下に半導体の柱状部を形成する工程と、

前記柱状部の側壁にゲート絶縁膜及び、このゲート絶縁膜を介するゲート電極を形成し、前記柱状部の側壁部分をチャネル部とした縦型電界効果トランジスタを形成する工程とを具備することを特徴とする半導体記憶装置の製造方法を提供する。

## 【0032】

本発明では、先ず単結晶半導体層表面上に、強誘電体キャパシタをエピタキシャル成長させて、所望のキャパシタ特性を有するエピタキシャル・キャパシタを形成し、このエピタキシャル・キャパシタをマスクとして単結晶半導体層をエッチングして半導体の柱状部を形成し、この柱状部の側面にチャネル部を具備する縦型電界効果トランジスタを形成している。このようにすると縦型電界効果トランジスタの上部ソースドレイン領域とエピタキシャル・キャパシタとが自己整合的に位置合わせできるので、高集積化された半導体メモリを作成できる。

## 【0033】

前記単結晶半導体層の表面には予め前記縦型電界効果トランジスタの上部ソース又はドレイン領域となる半導体層が形成されていることが好ましい。

## 【0034】

第4の発明は、一主面に単結晶半導体層を有する基板上に、前記基板の一主面に対して垂直方向に導通するチャネル部となる半導体の柱状部を形成する工程と、

前記柱状部の側面にゲート絶縁膜を形成する工程と、

前記柱状部の側面に前記ゲート絶縁膜を介してゲート電極を形成する工程と、

前記柱状部の頂部にソース又はドレインの内の何れか一方として機能する一方領域を形成する工程と、

前記柱状部の前記基板側に前記ソース又はドレインの一方に対し他方として機能する他方領域を形成する工程と、

前記一方領域の単結晶半導体面を核としてエピタキシャル半導体層をエピタキシャル成長する工程と、

前記半導体層上に、下部キャパシタ電極層、誘電体膜及び上部キャパシタ電極層をこの順にエピタキシャル成長する工程と、

少なくとも前記下部キャパシタ電極層及び前記エピタキシャル半導体層を一括してパターニングする工程とを具備することを特徴とする半導体記憶装置の製造方法を提供する。

## 【0035】

本発明は、縦型電界効果トランジスタにおける上部ソースドレイン領域の表面の単結晶部を核としてエピタキシャル半導体層をエピタキシャル成長させている。このときエピタキシャル半導体層は横方向にもエピタキシャル成長させることで、上部ソースドレイン領域よりも横方向に広がりを持ってエピタキシャル成長膜が形成できる。このエピタキシャル半導体層を下地膜としてエピタキシャル・キャパシタを形成することでパターニングの際に少々の合わせ誤差があっても十分な大きさのエピタキシャル・キャパシタを形成できる。

## 【0036】

第3、第4の発明において、前記誘電体膜が強誘電体膜であることが好ましい。

## 【0037】

ここで第3の発明では、最初に個々のエピタキシャル・キャパシタを単結晶が表面に出ている半導体基板上に作成した後に、このエピタキシャル・キャパシタをマスクとして、半導体基板をパターニングし半導体柱を形成する。次にこの半導体柱に縦型電界効果トランジスタを作成することによって、上部のエピタキシャル・キャパシタと下部の縦型電界効果トランジスタを自己整合的に形成することが可能となる。したがって  $F^2$  の面積を持つ縦型電界効果トランジスタ上に、同じく  $F^2$  の面積を持つエピタキシャル・キャパシタを形成できるので強誘電体メモリの高集積化が可能となる。

## 【0038】

10

20

30

40

50

また、第4の発明では、最初に半導体基板上に、縦型電界効果トランジスタを作成し非晶質絶縁膜で埋め込む。次に縦型電界効果トランジスタの上部ソースドレイン領域の単結晶面を表出し、これを核（シード層）として基板全面をエピタキシャル単結晶半導体層で覆う。次にこのエピタキシャル単結晶半導体層上にエピタキシャル成長させたエピタキシャル・キャパシタの層構造を形成し、少なくともエピタキシャル下部キャパシタ電極層と前記エピタキシャル単結晶半導体層を同一のパターンで一括して加工してセルノードを分離絶縁する。こうすることで層間絶縁膜上にもエピタキシャル・キャパシタを形成することが可能となり、一括パターニングによる合わせずれが生じても、 $F^2$ の面積を持つエピタキシャル・キャパシタを縦型電界効果トランジスタの上に作成することが可能となる。

【0039】

10

なお、縦型電界効果トランジスタの作成方法として、第3の発明ではエピタキシャル・キャパシタをマスクとして半導体の柱状部をパターニングしたあと、縦型電界効果トランジスタを作成しているので、このパターニングされた半導体の柱状部に縦型電界効果トランジスタを作成する方法に限られるが、第4の発明では、柱状部を形成した後にエピタキシャル・キャパシタを形成しているので、柱状部はパターニングして形成するほかに、選択エピタキシャル成長して形成してもよい。

【0040】

また、第3の発明では、エピタキシャル・キャパシタをマスクとして半導体の柱状部をパターニングし縦型電界効果トランジスタを形成できるので、リソグラフィー工程数が削減される効果も奏する。

20

【0041】

また、本発明に使用されるエピタキシャル・キャパシタの誘電体膜としてキャパシタ特性が安定で、エピタキシャル成長が容易な $BaTiO_3$ を主成分とする強誘電体膜が望ましい。さらに上部キャパシタ電極層及び下部キャパシタ電極層に、この強誘電体膜と同じペロブスカイト構造を持つ導電性の酸化物例えば $SrRuO_3$ や $Sr(Ti, Nb)O_3$ などの単結晶膜を使用し、電極の格子定数と強誘電体膜の格子定数の差を利用して人工的に歪ませたエピタキシャル歪格子誘電体膜を使用することが望ましい。

【0042】

この場合、 $BaTiO_3$ 系のエピタキシャル歪格子誘電体膜は、残留分極量が $80\mu C/cm^2$ 以上、動作電圧が1V以下という非常に優れた強誘電体キャパシタを縦型電界効果トランジスタに対して自己整合的に作成することができる。

30

【0043】

また、本発明において、 $(Ba, Sr)TiO_3$ 系のエピタキシャル歪格子誘電体膜の常誘電体（Sr、Baの組成比を選ぶことによって常誘電体化させることが可能）を使用することにより、DRAMに使用されるキャパシタの常誘電体膜として用いることができる。この場合比誘電率が1000以上、酸化膜の換算膜厚にして0.1nm以下と非常に優れた常誘電体キャパシタを縦型電界効果トランジスタに自己整合的に作成することも可能となる。

【0044】

【発明の実施の形態】

以下、本発明の好ましい実施形態について図面を参照して説明する。

40

【0045】

(実施形態1)

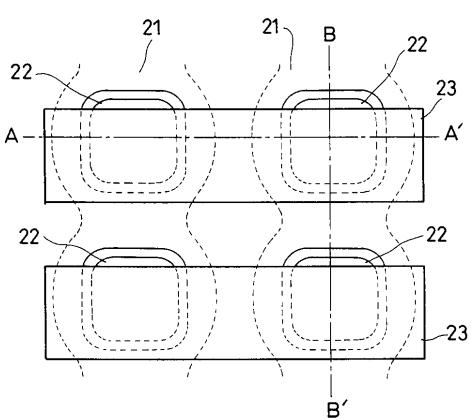

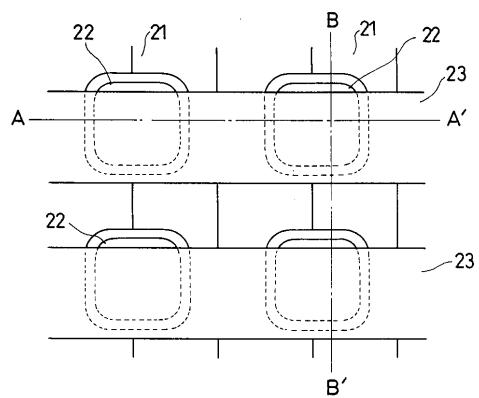

図2は、本発明の実施形態1にかかる半導体記憶装置の平面図である。ここでは強誘電体キャパシタと縦型電界効果型トランジスタを使用したメモリセルを $2 \times 2$ 個分のみ示した。

【0046】

図2中、21はワード線、23は、ワード線21に直交するビット線である。ワード線21とビット線23の交差する位置には、強誘電体エピタキシャル・キャパシタ22及びその下に縦型電界効果トランジスタが形成されている。

【0047】

50

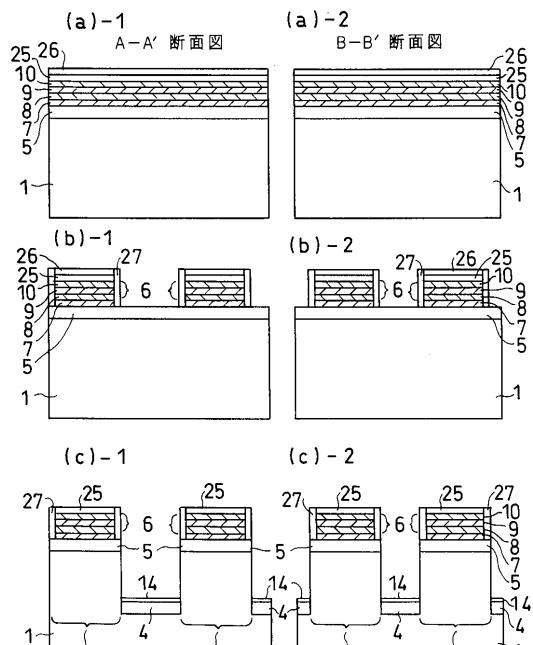

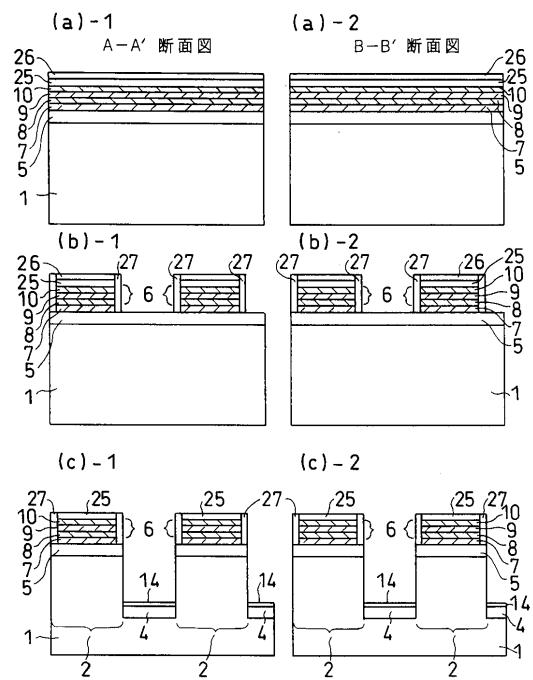

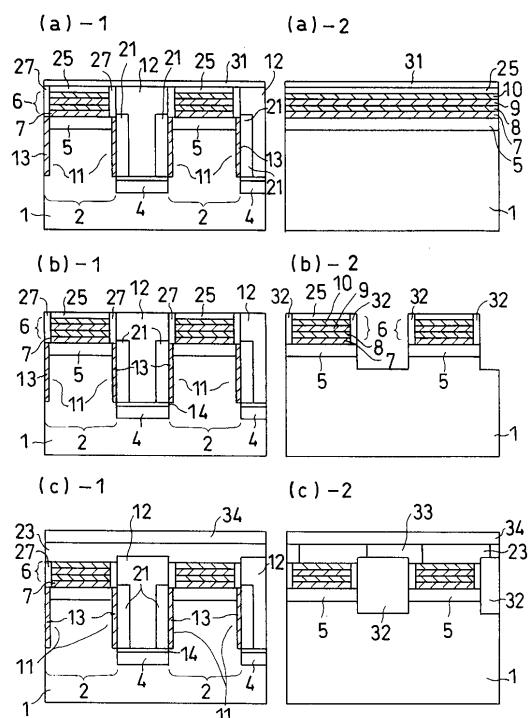

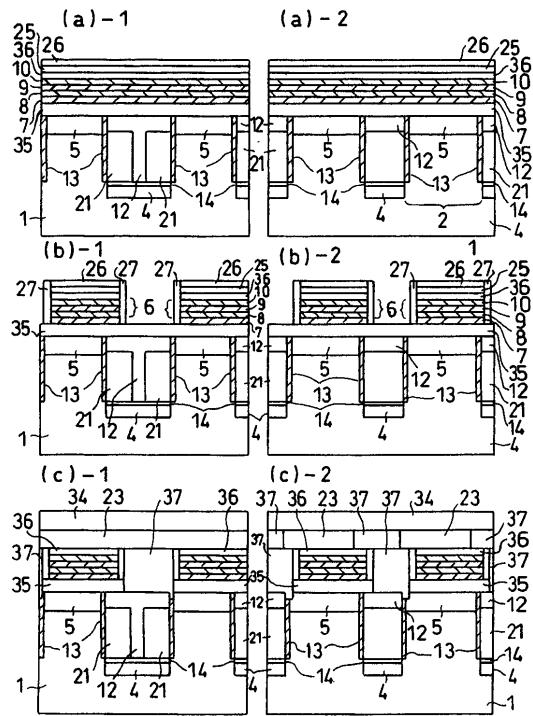

次に、図3、図4を用いてこの半導体記憶装置の製造方法を説明する。図3、図4の(a)-1、(b)-1、(c)-1は図2中A-A'断面図、図3、図4の(a)-2、(b)-2、(c)-2は図2中B-B'断面図である。

#### 【0048】

先ず、図3(a)-1、(a)-2に示すように、第2導電型の不純物領域5(後に縦型電界効果トランジスタの上部ソースドレイン領域になる)を予め表面に形成した第1導電型のシリコン単結晶基板1をフッ酸でエッティングした後、ただちに脱気した超々純水で洗浄して表面を水素ターミネーションする。次に、この第2導電型の不純物領域5上に $(\text{Ti}_{0.9}, \text{Al}_{0.1})\text{N}$ からなるバリア層7、 $\text{SrRuO}_3$ からなる下部キャパシタ電極層8、 $\text{BaTiO}_3$ からなる強誘電体膜9、 $\text{SrRuO}_3$ からなる上部キャパシタ電極層10を順にスパッタ法によりエピタキシャル成長する。基板温度はすべて600である。次に、上部キャパシタ電極層10上に酸化膜25及び窒化膜26を化学的気相成長法(CVD法)により成膜する。

#### 【0049】

次に、図3(b)-1、(b)-2に示すように、リソグラフィー及び反応性イオンエッティングによりバリア層7、下部キャパシタ電極層8、強誘電体膜9、上部キャパシタ電極層10、酸化膜25、窒化膜26を半導体基板1上の不純物領域5までパターニングし、個々のエピタキシャル・キャパシタ6を形成する。

#### 【0050】

次に、酸化膜をCVD法により成膜した後、窒化膜26及び半導体基板1上の不純物領域5を停止層として異方性エッティングしエピタキシャル・キャパシタ6の側壁に酸化膜キャパシタ側壁27を形成する。

#### 【0051】

次に、図3(c)-1、(c)-2に示すように、個々のエピタキシャル・キャパシタ6が含まれる酸化膜25及び酸化膜キャパシタ側壁27をマスクとしてシリコン基板1をエッティングし、半導体の柱状部2を形成する。このとき窒化膜26もいっしょにエッティングされる。酸化膜キャパシタ側壁27によってエッティング時にエピタキシャル・キャパシタに与える影響を抑えることができる。

#### 【0052】

次に、エピタキシャル・キャパシタ6が含まれる酸化膜25及び酸化膜キャパシタ側壁27をマスクとしイオンインプランテーション及び熱処理による活性化を行なって第2導電型の不純物拡散層4(後に縦型電界効果トランジスタの下部ソースドレイン領域になる)を形成し、さらにこの不純物拡散層4上に埋め込み絶縁膜14(シリコン酸化膜)を形成する。

#### 【0053】

次に、図4(a)-1、(a)-2に示すように、酸素雰囲気中或いは水蒸気雰囲気中で、1050、急速熱酸化(RTO)により、半導体の柱状部2のシリコンが表出している側壁に犠牲酸化膜を形成し、フッ酸でエッティングして除去することによりトランジスタのチャネル層となる表面に存在した加工損傷層を除去した後、改めて800におけるボックス酸化によりゲート絶縁膜13を形成する。次にCVD法により第2導電型の半導体層28をこのシリコン基板1上に一様に作成する。

#### 【0054】

次に、図4(b)-1、(b)-2に示すように、異方性エッティングにより第2導電型半導体層28をエッチバックしてワード線21(縦型電界効果トランジスタのゲート電極)を作成する。

#### 【0055】

なおこのとき図4(b)-1に示すA-A'断面はメモリセル間の間隔が最小加工寸法Fよりやや広く作成してあるためにワード線21とワード線21が分離される。一方図4(b)-2に示すB-B'断面のワード線21はメモリセル間の間隔を最小加工寸法Fで作成してあるために半導体の柱状部2間の溝が完全に埋め込まれワード線21が連続して形成されている。

10

20

30

40

50

## 【0056】

次に、基板全面に窒化膜からなる層間絶縁膜12を埋め込み平坦化する。

## 【0057】

ここまで工程でシリコン基板1表面の第2導電型不純物層5(上部ソースドレイン領域)、半導体の柱状部2の下部に形成された第2導電型不純物拡散層4(下部ソースドレイン領域3)、半導体の柱状部2の側壁にゲート絶縁膜13を介して形成されたゲート電極21からなる縦型電界効果トランジスタが形成されることになる。この縦型電界効果トランジスタにおける半導体の柱状部2の側面にはシリコン基板1に対して垂直方向に延在したチャネル部11が形成される。なお埋め込み絶縁膜14はゲート電極21と下部ソースドレイン領域4を電気的に分離するためのものである。

10

## 【0058】

次に、図4(c)-1、(c)-2に示すように、この基板上にCVD法により酸化膜29を成膜し、リソグラフィーによりピット線23形成用のマスクを形成し、窒化膜12をストッパーとして酸化膜25及び酸化膜27の一部を選択エッチングして、エピタキシャル・キャパシタ6の上部キャパシタ電極層10を露出する。

## 【0059】

次に、スパッタによりピット線23を埋め込み、平坦化後にさらに酸化膜30を形成する。

## 【0060】

このようにして、シリコン基板1面に対して垂直方向に延在するチャネル部11と、このチャネル部11にゲート絶縁膜13を介して形成されたゲート電極21と、前記チャネル部11の上下にそれぞれ形成された上部ソースドレイン領域電極5及び下部ソースドレイン領域4を具備する縦型電界効果トランジスタと、前記縦型電界効果トランジスタの上部ソースドレイン領域5上にエピタキシャル成長した下部キャパシタ電極層8、強誘電体膜9及び上部キャパシタ電極層10を有するエピタキシャル・キャパシタ6とを具備する強誘電体メモリを作成できる。

20

## 【0061】

また、この実施形態1で示したように、1回のリソグラフィー工程によりエピタキシャル・キャパシタと縦型電界効果トランジスタとが自己整合したメモリセルを形成することができる。さらに1回のリソグラフィー工程によってメモリセルとピット線を接続することができる。

30

## 【0062】

本実施例では、一主面に単結晶半導体層を有する基板として、シリコン単結晶を表面に有するシリコン単結晶基板を用いた。もちろんシリコン基板上に絶縁膜を介してシリコン単結晶層が形成されているいわゆるSOI基板を用いても良い。

## 【0063】

## (実施形態2)

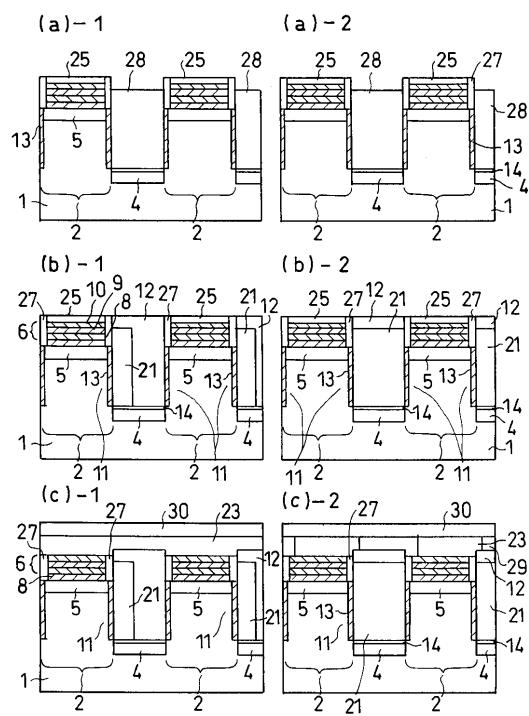

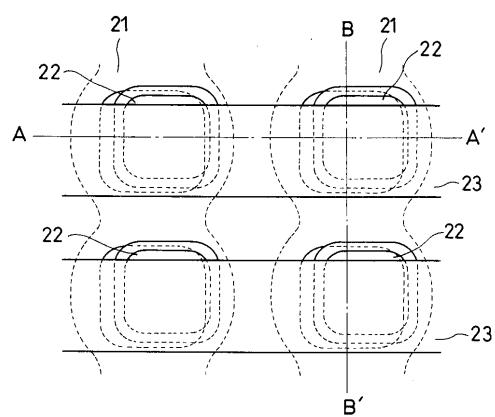

図5は、本発明の実施形態2にかかる半導体記憶装置の平面図である。ここでは強誘電体キャパシタと縦型電界効果型トランジスタを使用したメモリセルを $2 \times 2$ 個分のみ示した。実施形態1との違いは、ワード線21が縦型電界効果トランジスタの右側を半周囲で形成している点である。

40

## 【0064】

図5中、21はワード線、23は、ワード線21に直交するピット線である。ワード線21とピット線23の交差する位置には、強誘電体エピタキシャル・キャパシタ22及びその下に縦型電界効果トランジスタが形成されている。

## 【0065】

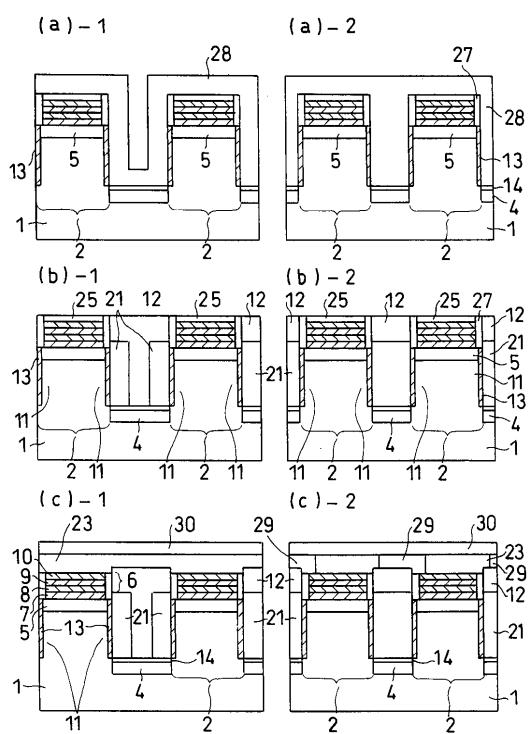

次に、図6、図7を用いてこの半導体記憶装置の製造方法を説明する。図6、図7の(a)-1、(b)-1、(c)-1は図5中A-A'断面図、図6、図7の(a)-2、(b)-2、(c)-2は図5中B-B'断面図である。

## 【0066】

50

先ず、図6(a)-1、(a)-2に示すように、第2導電型の不純物領域5(後に縦型電界効果トランジスタの上部ソースドレイン領域になる)を予め表面に形成した第1導電型のシリコン単結晶基板1をフッ酸でエッティングした後、ただちに脱気した超々純水で洗浄して表面を水素ターミネーションする。次に、この第2導電型の不純物領域5上に $(\text{Ti}_{0.9}, \text{Al}_{0.1})\text{N}$ からなるバリア層7、 $\text{SrRuO}_3$ からなる下部キャパシタ電極層8、 $\text{BaTiO}_3$ からなる強誘電体膜9、 $\text{SrRuO}_3$ からなる上部キャパシタ電極層10を順にスパッタ法によりエピタキシャル成長する。基板温度はすべて600である。次に、上部キャパシタ電極層10上に酸化膜25及び窒化膜26をCVD法により成膜する。

#### 【0067】

次に、図6(b)-1、(b)-2に示すように、リソグラフィー及び反応性イオンエッティングによりバリア層7、下部キャパシタ電極層8、強誘電体膜9、上部キャパシタ電極層10、酸化膜25、窒化膜26を半導体基板1上の不純物領域5までパターニングし、個々のエピタキシャル・キャパシタ6を形成する。

#### 【0068】

次に、酸化膜をCVD法により成膜した後、窒化膜26及び半導体基板1上の不純物領域5を停止層として異方性エッティングしエピタキシャル・キャパシタ6の側壁に酸化膜キャパシタ側壁27を形成する。

#### 【0069】

次に、図6(c)-1、(c)-2に示すように、個々のエピタキシャル・キャパシタ6が含まれる酸化膜25及び酸化膜キャパシタ側壁27をマスクとして半導体基板1をエッティングし、半導体柱2を形成する。このとき窒化膜26もいっしょにエッティングされる。酸化膜キャパシタ側壁27によってエッティング時にエピタキシャル・キャパシタに与える影響を抑えることができる。

#### 【0070】

次にエピタキシャル・キャパシタ6が含まれる酸化膜25及び酸化膜キャパシタ側壁27をマスクとしてイオンインプランテーション及び熱処理による活性化を行なって第2導電型の不純物拡散層4(後に縦型電界効果トランジスタの下部ソースドレイン領域になる)を形成し、さらにこの不純物拡散層4上に埋め込み絶縁層14(シリコン酸化膜)を形成する。

#### 【0071】

次に、図7(a)-1、(a)-2に示すように、酸素雰囲気中或いは水蒸気雰囲気中で、1050、RTOにより、半導体柱2のシリコンが表出している側壁に犠牲酸化膜を形成し、フッ酸でエッティングして除去することによりトランジスタのチャネル層が形成される表面に存在した加工損傷層を除去した後、改めて800におけるボックス酸化によりゲート絶縁膜13を形成する。次にCVD法により第2導電型の半導体層28をこのシリコン基板1上に一様に作成する。

#### 【0072】

次に、図7(b)に示すように、フォトリソグラフィ工程によりワード線形成用のマスクを形成し、酸化膜25及び酸化キャパシタ側壁27をエッティングストッパーとして第2導電型の半導体層28をエッチバックしてワード線21(縦型電界効果トランジスタのゲート電極)を作成する。

#### 【0073】

次に、基板全面に窒化膜からなる層間絶縁膜12を埋め込み平坦化する。

ここまで工程でシリコン基板1表面の第2導電型不純物層5(上部ソースドレイン領域)、半導体柱2の下部に形成された第2導電型不純物拡散層4(下部ソースドレイン領域)、半導体の柱状部2の側壁にゲート絶縁膜13を介して形成されたゲート電極21からなる縦型電界効果トランジスタが形成されたことになる。この縦型電界効果トランジスタの半導体における柱状部2の側面にはシリコン基板1に対して垂直方向に延在するチャネル部11が形成される。なお埋め込み絶縁膜14はゲート電極21と下部ソースドレイン領域4を電気的に分離するためのものである。

10

20

30

40

50

## 【0074】

本実施形態では図7(b)-1のA-A'断面図及び図5に示すように半導体の柱状部2の右側壁面のみにゲート電極21が形成されているので、チャネル部11は柱状部2の右側面のみに形成される。

## 【0075】

次に、図7(c)-1、(c)-2に示すように、この基板上にCVD法により酸化膜29を成膜し、リソグラフィーによりビット線23形成用のマスクを形成し、窒化膜12をストップバーとして酸化膜25及び酸化膜キャパシタ側壁27の一部を選択エッチングして、エピタキシャル・キャパシタ6の上部キャパシタ電極層10を露出する。

## 【0076】

次に、スパッタによりビット線23を埋め込み、平坦化後にさらに酸化膜保護層30を形成する。

## 【0077】

このようにして、シリコン基板1の面に対して垂直方向に延在するチャネル部11と、このチャネル部11にゲート絶縁膜13を介して形成されたゲート電極21と、前記チャネル部11の上下にそれぞれ形成された上部ソースドレイン領域電極5及び下部ソースドレイン領域4を具備する縦型電界効果トランジスタと、前記縦型電界効果トランジスタの上部ソースドレイン領域5上にエピタキシャル成長した下部キャパシタ電極層8、強誘電体膜9及び上部キャパシタ電極層10を具備するキャパシタ6とを具備する強誘電体メモリを作成できる。

## 【0078】

また、この実施形態2で示したように、2回のリソグラフィー工程によりエピタキシャル・キャパシタと縦型電界効果トランジスタとが自己整合したメモリセルを形成することができる。さらに1回のリソグラフィー工程によってメモリセルとビット線を接続することができる。

## 【0079】

## (実施形態3)

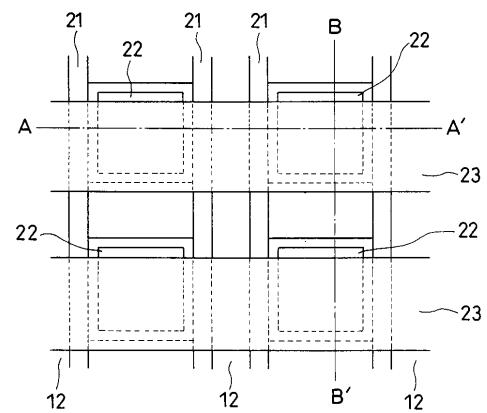

図8は、本発明の実施形態3にかかる半導体記憶装置の平面図である。ここでは強誘電体キャパシタと縦型電界効果型トランジスタを使用したメモリセルを2×2個分のみ示した。実施形態1との違いは、ワード線21が半導体柱2の左右側壁に選択エッチングにより残されたものである。

## 【0080】

図8中、21はワード線、23は、ワード線21に直交するビット線である。ワード線21とビット線23の交差する位置には、強誘電体エピタキシャル・キャパシタ22及びその下に縦型電界効果トランジスタが形成されている。12は層間絶縁膜である。

## 【0081】

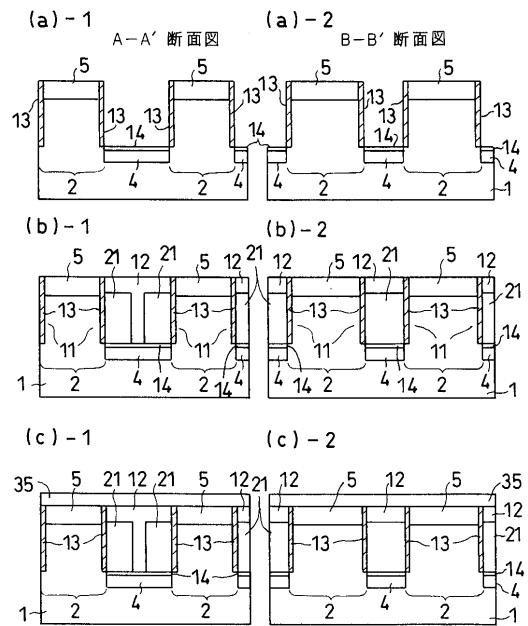

次に、図9、図10を用いてこの半導体記憶装置の製造方法を説明する。図9、図10の(a)-1、(b)-1、(c)-1は図8中A-A'断面図、図9、図10の(a)-2、(b)-2、(c)-2は図8中B-B'断面図である。

まず、図9(a)-1、(a)-2に示すように、第2導電型の不純物領域5(後に縦型電界効果トランジスタの上部ソースドレイン領域になる)を予め表面に形成した第1導電型のシリコン単結晶基板1をフッ酸でエッチングした後、ただちに脱気した超々純水で洗浄して表面を水素ターミネーションする。次に、この第2導電型の不純物領域5上に $(\text{Ti}_{0.9}, \text{Al}_{0.1})\text{N}$ からなるバリア層7、 $\text{SrRuO}_3$ からなる下部キャパシタ電極層8、 $\text{BaTiO}_3$ からなる強誘電体膜9、 $\text{SrRuO}_3$ からなる上部キャパシタ電極層10を順にスパッタ法によりエピタキシャル成長する。基板温度はすべて600である。次に、上部キャパシタ電極層10上に酸化膜25及び窒化膜26をCVD法により成膜する。

## 【0082】

次に、図9(b)-1、(b)-2に示すように、リソグラフィー及び反応性イオンエッチングによりバリア層7、下部キャパシタ電極層8、強誘電体膜9、上部キャパシタ電極層10、酸

10

20

30

40

50

化膜 25、窒化膜 26 を半導体基板 1 上の不純物領域 5 までパターニングし、個々のエピタキシャル・キャパシタ 6 を形成する。このとき図 9 (b)-1 の A - A' 断面のほうだけ、すなわちワード線 21 方向に残るようにエッチングした。

【 0083 】

次に、酸化膜をCVD法により成膜した後、窒化膜 26 及び半導体基板 1 上の不純物領域 5 を停止層として異方性エッチングしエピタキシャル・キャパシタ 6 の側壁に酸化膜キャパシタ側壁 27 を形成する。

【 0084 】

次に、図 9 (c)-1、(c)-2 に示すように、個々のエピタキシャル・キャパシタ 6 が含まれる酸化膜 25 及び酸化膜キャパシタ側壁 27 をマスクとしてシリコン基板 1 をエッチングし、半導体の柱状部 2 を形成する。このとき窒化膜 26 もいっしょにエッチングされる。酸化膜キャパシタ側壁 27 によってエッチング時にエピタキシャル・キャパシタに与える影響を抑えることができる。

【 0085 】

次にエピタキシャル・キャパシタ 6 が含まれる酸化膜 25 及び酸化膜キャパシタ側壁 27 をマスクとしイオンインプランテーション及び熱処理による活性化を行なって第2導電型の不純物拡散層 4（後に縦型電界効果トランジスタの下部ソースドレイン領域になる）を形成し、さらにこの不純物拡散層 4 上に埋め込み絶縁膜 14（シリコン酸化膜）を形成する。

【 0086 】

次に、酸素雰囲気中或いは水蒸気雰囲気中で、1050℃、RTOにより、半導体の柱状部 2 の Si が表出している側壁に犠牲酸化膜を形成し、フッ酸でエッチングして除去することによりトランジスタのチャネル層表面に存在した加工損傷層を除去した後、改めて 800℃ におけるボックス酸化によりゲート絶縁膜 13 を形成した。次にCVD法により第2導電型の半導体層 28 をこの半導体基板 1 上に一様に形成する。

【 0087 】

次に、図 10 (a)-1、(a)-2 に示すように、酸化膜 25 及び酸化膜キャパシタ側壁 27 をストッパーとして第2導電型の半導体層 28 を異方選択エッチングしてワード線 21（縦型電界効果トランジスタのゲート電極）を作成する。

次に、シリコン基板 1 全面に窒化膜からなる層間絶縁膜 12 を埋め込み平坦化し、窒化膜 31 をさらにCVD法により成膜した。

ここまで工程でシリコン基板 1 表面の第2導電型不純物層 5（上部ソースドレイン領域）、半導体の柱状部 2 の下部に形成された第2導電型不純物拡散層 4（下部ソースドレイン領域）、半導体の柱状部 2 の側壁にゲート絶縁膜 13 を介して形成されたゲート電極 21 からなる縦型電界効果トランジスタが形成されることになる。この縦型電界効果トランジスタにおける半導体の柱状部 2 の側面には半導体基板 1 に対して垂直方向の導通が得られるチャネル部 11 が形成される。なお埋め込み絶縁膜 14 はゲート電極 21 と下部ソースドレイン領域 4 を電気的に分離するためのものである。

【 0088 】

次に、図 10 (b)-1 の B - B' 断面図に示すように、リソグラフィー及び反応性イオンエッチングによりエピタキシャル・キャパシタ 6 をビット線 23 方向に沿って不純物領域 5 までエッチングする。さらに酸化膜をCVD法により成膜した後、異方性エッチングにより窒化膜 31 及び半導体基板 1 上の不純物領域 5 を停止層として、酸化膜キャパシタ側壁 32 を形成する。このとき窒化膜 31 もエッチングされる。酸化膜キャパシタ側壁 27 によってエッチング時にエピタキシャル・キャパシタに与える影響を抑えることができる。

【 0089 】

次に、エピタキシャル・キャパシタ 6 上に残された酸化膜 25 及び酸化膜キャパシタ側壁 27、32 をマスクとして、半導体基板 1 をエッチングして、ビット線 23 方向のトレンチを形成し、セルノードを分離する。

【 0090 】

10

20

30

40

50

次に、図10(c)-1、(c)-2に示すように、CVD法により窒化膜32を埋め込み平坦化する。次にCVD法により酸化膜33を成膜する。次にリソグラフィーによりビット線23形成用のマスクを形成し、窒化膜32及び窒化膜12をストッパーとして酸化膜25の全部、酸化膜キャパシタ側壁27、32、酸化膜33の一部をエッチングしエピタキシャル・キャパシタ6の上部キャパシタ電極層10を露出する。

【0091】

さらにスパッタによりビット線23を埋め込み平坦化後、窒化膜34を形成する。および第4の酸化膜24の選択エッチングを行なってキャパシタの上部電極14を露出した。さらにスパッタによりビット線31を埋め込み、平坦化後にさらに第5の窒化膜29を形成した。

上述した工程により2回のリソグラフィー工程により $4F^2$ のメモリセル面積および $F^2$ のキャパシタ面積を持ち完全に自己整合した強誘電体キャパシタと縦形電界効果型トランジスタからなるメモリセルを形成することができた。さらに1回のリソグラフィー工程によってメモリセルとビット線を接続することができた。

【0092】

(実施形態4)

図11は、本発明の実施形態4にかかる半導体記憶装置の平面図である。ここでは強誘電体キャパシタと縦形電界効果トランジスタを使用したメモリセルを $2 \times 2$ 個分のみ示した。本実施形態では最初に半導体基板上に、縦型電界効果トランジスタを作成し非晶質絶縁膜で埋め込む。次に縦型電界効果トランジスタの単結晶上部ソースドレイン領域を表出し、これを核(シード層)として基板全面を単結晶半導体層で覆う。次にこの単結晶半導体層上にエピタキシャル成長させたエピタキシャル・キャパシタの層構造を形成し、少なくともエピタキシャル下部キャパシタ電極層と前記単結晶半導体層を同一のパターンで一括して加工してセルノードを分離絶縁するものである。

【0093】

図11中、21はワード線、23は、ワード線21に直交するビット線である。ワード線21とビット線23の交差する位置には、強誘電体エピタキシャル・キャパシタ22及びその下に縦型電界効果トランジスタが形成されている。

【0094】

次に、図12、図13を用いてこの半導体記憶装置の製造方法を説明する。図12、図13の(a)-1、(b)-1、(c)-1は図11中A-A'断面図、図12、図13の(a)-2、(b)-2、(c)-2は図11中B-B'断面図である。

【0095】

先ず、図12(a)-1、(a)-2に示すように、第1導電型のシリコン単結晶基板1をリソグラフィー及び反応性イオンエッチングによりパターニングして、半導体の柱状部2を形成する。次に、イオンインプランテーション及び熱処理による活性化を行なって、半導体の柱状部2上に第2導電型の不純物拡散層5(後に縦型電界効果トランジスタの上部ソースドレイン領域になる)を、半導体の柱状部2間に第2導電型の不純物拡散層4(後に縦型電界効果トランジスタの下部ソースドレイン領域になる)を同時に自己整合的に形成する。

【0096】

次に、半導体の柱状部2間に不純物拡散層4上に、埋め込み絶縁膜14(シリコン酸化膜)を形成する。

【0097】

次に、酸素雰囲気中或いは水蒸気雰囲気中で、1050、RTOにより、半導体柱2のシリコンが表出している側壁に犠牲酸化膜を形成し、フッ酸でエッチングして除去することによりトランジスタのチャネル層が形成される表面に存在した加工損傷層を除去した後、改めて800におけるボックス酸化によりゲート絶縁膜13を形成した。

【0098】

次に図12(b)-1、(b)-2に示すように、CVD法により第2導電型の半導体層をこの半導体基板1上に一様に形成する。異方性エッチングによりこの半導体層をエッチバックしてワ

10

20

30

40

50

ド線 2 1 (後に縦型電界効果トランジスタのゲート電極になる)を作成する。

【 0 0 9 9 】

なおこのとき図 1 2 (b)-1に示す A - A' 断面はメモリセル間の間隔が最小加工寸法 F よりやや広く作成してあるためにワード線 2 1 とワード線 2 1 が分離される。一方図 1 2 (b)-2に示す B - B' 断面のワード線 2 1 はメモリセル間の間隔を最小加工寸法 F で作成してあるために半導体の柱状部 2 間の溝が完全に埋め込まれワード線 2 1 が連続して形成されている。次に層間絶縁膜 1 2 (酸化膜)により半導体の柱状部 2 を埋め込み平坦化する。

【 0 1 0 0 】

ここまで工程で、半導体の柱状部 2 上に形成された第2導電型不純物拡散層 5 (上部ソースドレイン領域)、半導体の柱状部 2 間に形成された第2導電型不純物拡散層 4 (下部ソースドレイン領域)、半導体柱 2 側壁に形成されたゲート絶縁膜 1 3 、半導体の柱状部 2 の側面に延在するチャネル部 1 1 からなる縦形電界効果型トランジスタが形成されたことになる。

【 0 1 0 1 】

次に、図 1 2 (c)-1、(c)-2に示すように、上部ソースドレイン領域 5 の表面をフッ酸でエッティングした後に、ただちに脱気した超々純水で洗浄して表面を水素ターミネーションする。次に、シリコン基板 1 全面に第 2 導電型の非晶質シリコン層を形成し、500 の熱処理により、上部ソースドレイン領域 5 のシリコン単結晶面を核(シード層)として、上部ソースドレイン領域 5 と非晶質シリコン層との界面から、この非晶質シリコン層を固相エピタキシャル成長させて単結晶シリコン層 3 5 を作成し平坦化する。

【 0 1 0 2 】

次に、図 1 3 (a)-1、(a)-2に示すように、単結晶シリコン層 3 5 の表面をフッ酸でエッティングした後に、ただちに脱気した超々純水で洗浄して表面を水素ターミネーションする。次に、この単結晶シリコン層 3 5 上に  $(\text{Ti}_{0.9}, \text{Al}_{0.1})\text{N}$  からなる下部バリア層 7 、  $\text{SrRuO}_3$  からなる下部キャパシタ電極層 8 、  $\text{BaTiO}_3$  からなる強誘電体膜 9 、  $\text{SrRuO}_3$  からなる上部キャパシタ電極層 1 0 、  $(\text{Ti}_{0.9}, \text{Al}_{0.1})\text{N}$  からなる上部バリア層 3 6 を順にスパッタ法によりエピタキシャル成長する。基板温度はすべて 600 である。次に、上部バリア層 3 6 上に酸化膜 2 5 及び窒化膜 2 6 をCVD法により成膜する。

【 0 1 0 3 】

次に、図 1 3 (b)-1、(b)-2に示すように、リソグラフィー及び反応性イオンエッティングにより下部バリア層 7 、下部キャパシタ電極層 8 、強誘電体膜 9 、上部キャパシタ電極層 1 0 、上部バリア層 3 6 、酸化膜 2 5 、窒化膜 2 6 を半導体基板 1 上の単結晶シリコン層 3 5 までパターニングし、個々のエピタキシャル・キャパシタ 6 を形成する。

【 0 1 0 4 】

さらに酸化膜をCVD法により成膜した後、窒化膜 2 6 及び単結晶シリコン層 3 5 を停止層として異方性エッティングにより、酸化膜キャパシタ側壁を形成する。

【 0 1 0 5 】

次に、図 1 3 (c)-1、(c)-2に示すように、個々のエピタキシャル・キャパシタ 6 が含まれる酸化膜 2 5 及び酸化膜キャパシタ側壁 2 7 をマスクとして単結晶シリコン層 3 5 を選択的にエッティングし、下部キャパシタ電極層 8 、下部バリア層 7 、単結晶シリコン層 1 6 及び上部ソースドレイン領域 5 からなるセルノードを分離絶縁する。このとき窒化膜 2 6 もいっしょにエッティングされる。

【 0 1 0 6 】

次に、CVD法に酸化膜 3 7 を成膜し、化学的機械的研磨法 (CMP) により  $(\text{Ti}, \text{Al})\text{N}$  上部バリア層 3 6 をストッパーとしてこの面が表面に出るまで研磨し平坦化する。次に、CVD法により窒化膜 3 7 を成膜し、リソグラフィーによりビット線形成用のマスクを形成し、酸化膜 3 6 をストッパーとして窒化膜 3 7 を選択エッティングする。さらにスパッタによりビット線 2 3 を埋め込み、平坦化する。さらに窒化膜 3 4 を形成し保護膜とした。

【 0 1 0 7 】

上述した工程では、2回のリソグラフィー工程により自己整合した強誘電体キャパシタと

10

20

30

40

50

縦形電界効果型トランジスタからなるメモリセルを形成することができる。さらに1回のリソグラフィー工程によってメモリセルとビット線を接続することができる。

【0108】

(実施形態5)

実施形態1から実施形態4では、強誘電体キャパシタの強誘電体膜として $\text{BaTiO}_3$ 系のエピタキシャル歪格子誘電体膜を使用し、メモリセル面積がおよそ $4 \text{ F}^2$ 、キャパシタ面積が $\text{F}^2$ の半導体メモリを作成した。

【0109】

この場合でも、加工技術の進展に連れて、例えば加工寸法 $F$ が $0.1 \mu\text{m}$ 以下になった場合はメモリセルに必要な蓄積電荷量が足りなくなる恐れがある。具体的には安定な読み出しを保証するためのメモリセルに必要な電荷量が $20 \text{ fC}$ であると仮定すると、 $80 \mu\text{C}/\text{cm}^2$ の残留分極値を持つ強誘電体キャパシタを使用しても $0.1 \mu\text{m}^2$ のキャパシタ面積では $8 \text{ fC}$ にしかならず安定な読み出し動作ができなくなる恐れがある。

10

【0110】

そこで、本実施形態では、実施形態1から実施形態4に示したメモリセルを用いて、加工寸法 $F$ が $0.1 \mu\text{m}$ 以下になった場合でも安定動作可能な強誘電体メモリの回路構成について説明する。

【0111】

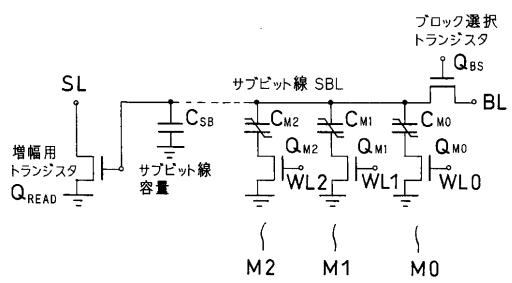

図14は、このような強誘電体メモリの回路図である。

【0112】

20

各メモリセル $M_0$ 、 $M_1$ 、 $M_2$ は、強誘電体キャパシタ $C_{M0}$ 、 $C_{M1}$ 、 $C_{M2}$ の下部電極が縦形電界効果トランジスタ $Q_{r0}$ 、 $Q_{r1}$ 、 $Q_{r2}$ と接続され、上部キャパシタ電極層がサブビット線 $SBL$ に接続されている。サブビット線 $SBL$ の一端は増幅用トランジスタ $Q_{READ}$ のゲート電極に接続されている。増幅用トランジスタ $Q_{READ}$ の出力を読み出し線 $SL$ に接続する。

【0113】

このようなサブブロックを後で説明する図15のようにマトリックス状に並べて半導体メモリを構成する。こうすることで、サブビット線 $SBL$ にぶらさがるメモリセルの個数を少なくできるので、サブブロック化しない通常のビット線の容量よりもはるかに小さくなり、各メモリセルの $M_0$ 、 $M_1$ 、 $M_2$ の蓄積電荷は、増幅用トランジスタ $Q_{READ}$ がONになった後に読み出し線 $SL$ を通して読み取る。

30

【0114】

したがって各メモリセル $M_0$ 、 $M_1$ 、 $M_2$ に要求される蓄積電荷量がはるかに小さくても、サブビット線 $SBL$ に接続するメモリセル数が少ないので、増幅用トランジスタ $Q_{READ}$ によって読み出し可能となる。

【0115】

また逆に各メモリセル $M_0$ 、 $M_1$ 、 $M_2$ の蓄積電荷量に応じてサブビット線 $SBL$ に接続するメモリセル数を調節することにより、最適なサブビット線容量に調節することで最適な呼び出し信号を得ることが可能である。

【0116】

40

また、増幅用トランジスタ $Q_{READ}$ の構造としては、各メモリセル $M_0$ 、 $M_1$ 、 $M_2$ に使用した縦形電界効果トランジスタを使用するとメモリセルプロセスやメモリセルレイアウトの点で最適である。

【0117】

このように実施形態1から実施形態4で説明した $\text{BaTiO}_3$ 系のエピタキシャル歪格子誘電体膜を使用した強誘電体キャパシタと縦形電界効果トランジスタを接続したメモリセルを、本実施形態で説明したサブビット線 $SBL$ と増幅用トランジスタ $Q_{READ}$ を使用したメモリ回路を使用することで、初めて $4 \text{ Gb} \sim 16 \text{ Gb}$ の超高集積半導体記憶装置の作成が初めて可能になる。

【0118】

50

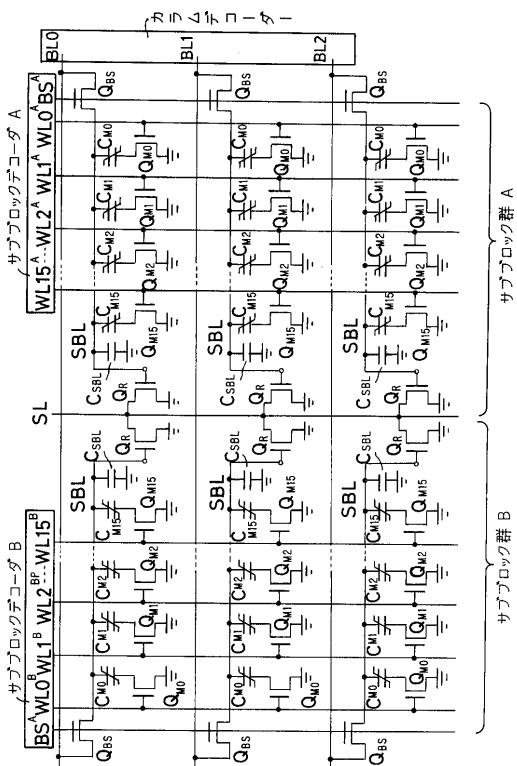

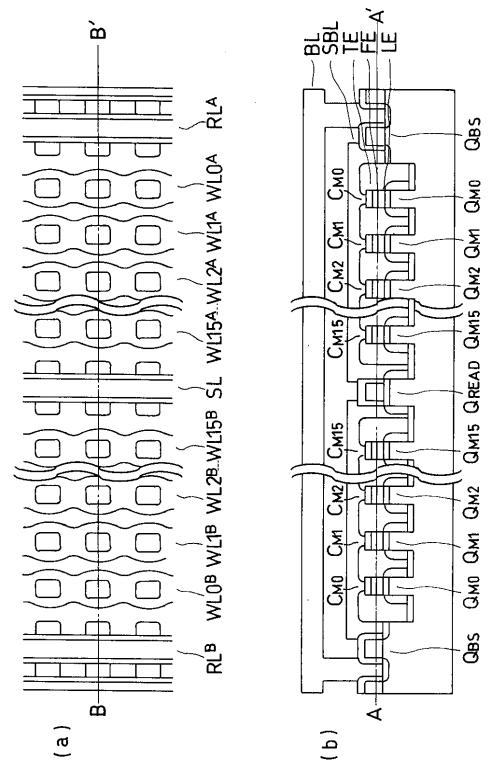

図15は、図14で説明したメモリセルのサブブロックを6個マトリックス上に配置した強誘電メモリ回路図である。

【0119】

図15に示すように、複数個の縦型電界効果トランジスタ $Q_{M0}, Q_{M1}, Q_{M2}, \dots, Q_{M15}$ と、これら縦型電解トランジスタ $Q_{M0}, Q_{M1}, Q_{M2}, \dots, Q_{M15}$ の上部ソースドレイン領域に下部キャパシタ電極層が接続された複数個の強誘電体キャパシタ $C_{M0}, C_{M1}, C_{M2}, C_{M3}, \dots, C_{M15}$ とからなるメモリセルがサブビット線SBLに接続されたサブブロックがマトリックス状に接続されている。

【0120】

各縦型電界効果トランジスタ $Q_{M0}, Q_{M1}, Q_{M2}, \dots, Q_{M15}$ の下部ソースドレイン領域はプレート電極に接続され接地されている。各強誘電体キャパシタ $C_{M0}, C_{M1}, C_{M2}, \dots, C_{M15}$ の上部キャパシタ電極層はそれぞれのブロックのサブビット線SBLに接続されている。

【0121】

ここで各メモリセルは実施形態1から実施形態4で説明したように、各強誘電体キャパシタ $C_{M0}, C_{M1}, C_{M2}, \dots, C_{M15}$ が、それぞれエピタキシャル成長された下部キャパシタ電極層、強誘電体膜、上部キャパシタ電極層から構成され、それぞれ縦型電界効果トランジスタ上に自己整合的に形成されたものである。

【0122】

またここでは、各サブビット線SBLに16個のメモリセルが接続されている場合を説明しているが、強誘電体キャパシタの残留分極値に応じてサブビット線に接続するメモリセル数を適宜増減できるのは言うまでもない。

【0123】

それぞれのサブビット線SBLの一端はそれぞれ増幅用トランジスタ $Q_R$ のゲート電極に接続されている。各増幅用トランジスタ $Q_R$ の下部ソースドレイン領域はプレート電極に接続され接地されている。上部ソースドレイン領域は読み出し線SBLに接続されている。ここでサブビット線SBLには補助容量 $C_{SBL}$ が接続されている。

【0124】

また、それぞれのサブビット線SBLの他端はサブブロック選択用トランジスタ $Q_{BS}$ の一方のソースドレイン電極に接続されており、サブブロック選択用トランジスタ $Q_{BS}$ の他方のソースドレイン電極はビット線BBLに接続されている。

【0125】

そしてそれぞれのサブビット線SBLに接続されたメモリセル列を複数個マトリックス状に配置し、1個の読み出し線SBLを中心として右にサブブロック群[A]、左にサブブロック群Bとして、2個に対称配列している。

【0126】

サブブロック群Aのサブブロックに属する縦型電界効果トランジスタ $Q_{M0}, Q_{M1}, Q_{M2}, \dots, Q_{M15}$ の各ゲート電極にはワード線 $WL0^A, WL1^A, WL2^A, \dots, WL15^A$ が接続されている。また、サブブロック群Bのサブブロックに属する縦型電界効果トランジスタ $Q_{M0}, Q_{M1}, Q_{M2}, \dots, Q_{M15}$ の各ゲート電極にはワード線 $WL0^B, WL1^B, WL2^B, \dots, WL15^B$ が接続されている。

【0127】

また、それぞれのサブブロック群Aの選択用トランジスタ $Q_{BS}$ の各ゲート電極にはサブブロック選択線 $BS^A$ が接続され、サブブロック群Bの選択用トランジスタ $Q_{BS}$ の各ゲート電極にはサブブロック選択線 $BS^B$ が接続されている。

【0128】

サブブロック群Aに属する各ワード線 $WL0^A, WL1^A, WL2^A, \dots, WL15^A$ は、ローデコーダAに接続されている。また、サブブロック群Bに属する各ワード線 $WL0^B, WL1^B, WL2^B, \dots, WL15^B$ は、ローデコーダBに接続されている。また、それぞれのサブブロック群に属するサブブロックの対称配置されたサブブロックのサブブロック選択用トランジスタ $Q_B$

10

20

30

40

50

<sub>s</sub>のソースドレイン電極は共通のピット線BL0, BL1, …に接続され、カラムデコーダに接続されている。

【0129】

このような接続関係にある強誘電体メモリにおいて、サブブロック群Aに属するピット線B<sub>L<sub>x</sub></sub> (x=0, 1)とワード線WL<sub>y<sup>A</sup></sub> (y=0, 1, 2, …, 15)の交点で示される座標 (X, Y) メモリセルを選択する場合について説明する。

【0130】

先ずBS<sup>A</sup>のワード線を“1(ハイレベル)”としてサブブロック選択用トランジスタQ<sub>BS</sub>をオンにし、次にワード線WL<sub>y<sup>A</sup></sub>を“1(ハイレベル)”としてY座標のメモリセルの縦型電界効果トランジスタQ<sub>My</sub>をオンにする。次に、電位一定(例えば1/2V<sub>CC</sub>)のプレート電極PEに10対してピット線BL<sub>x</sub>に電位を加えることで座標 (X, Y) に位置するメモリセルを選択できる。

【0131】

同様にサブブロックBに属するピット線BL<sub>x</sub> (x=0, 1)とワード線WL<sub>y<sup>B</sup></sub> (y=0, 1, 2, …, 15)の交点で示される所望の記憶セルを選択する場合について説明する。

【0132】

先ずBS<sup>B</sup>のワード線を“1(ハイレベル)”としてサブブロック選択トランジスタQ<sub>BS</sub>をオンにし、次にワード線WL<sub>y<sup>B</sup></sub>を“1(ハイレベル)”として選択用トランジスタQ<sub>My</sub>をオンにする。次に、電位一定(例えば1/2V<sub>CC</sub>)のプレート電極PEに対してピット線BL<sub>x</sub>に電位を加えることで座標 (X, Y) に位置するメモリセルを選択できる。20

【0133】

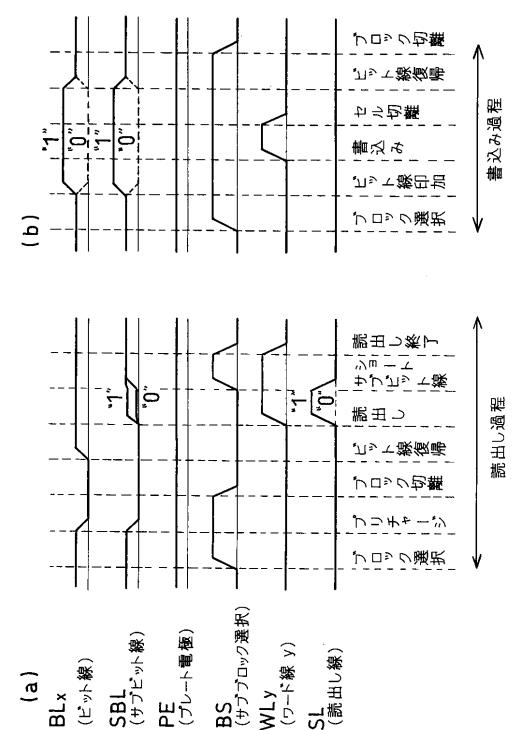

図16に示すタイミングチャートに基づいて、図15で説明した強誘電体メモリの読み出し/書き込み手順を説明する。

【0134】

先ず、図16(a)に示すように、読み出し時には、サブブロック選択用ワード線BSをオンにし、サブブロック選択用トランジスタQ<sub>BS</sub>をオンにする。次に、ピット線BL<sub>x</sub>に一定の電圧を与え、サブピット線SBLに読み出し電圧を加える。次に、サブブロック選択用トランジスタQ<sub>BS</sub>をオフにして、サブピット線SBLをフローティング状態にしてプリチャージを行なう。次に、ピット線BL<sub>x</sub>を復帰させる。

【0135】

次に、ワード線WL<sub>y</sub>を選択することにより、ワード線WL<sub>y</sub>に接続する縦型電界効果トランジスタQ<sub>My</sub>をオン状態にする。こうして縦型電界効果トランジスタQ<sub>My</sub>に接続された記憶用強誘電体キャパシタC<sub>My</sub>にプリチャージされたサブピット線SBLが電気的に接続される。そしてプリチャージされた電圧を記憶用強誘電体キャパシタC<sub>My</sub>に加えて反転させる。このとき記憶用強誘電体キャパシタC<sub>My</sub>にあらかじめ記憶させてあった分極方向の違いにより、サブピット線SBLはハイかローの異なる電位を示す。これを1か0として増幅用トランジスタQ<sub>READ</sub>で読み出して読み出し線SLに出力する。最後にワード線WL<sub>y</sub>を切る。このようにして座標 (X, Y) のメモリセルの情報を読み出すことができる。次にサブブロック選択用ワード線BSがオンとなりサブピット線がショートされる。次に、サブブロック選択用ワード線BS及びワード線WL<sub>y</sub>が切られて読み出し終了となる。40

【0136】

次に、図16(b)を用いて、書き込み時について説明する。

【0137】

先ず、サブブロック選択用ワード線BSをオンにし、サブブロック選択用トランジスタQ<sub>BS</sub>をオンにする。次に、ピット線BLを記憶させたい方法(1か0)により、メモリセルの強誘電体膜を極性反転させるに必要な電圧を引火することによって、サブピット線SBLに書き込み電圧を印加する。次に、ワード線WL<sub>y</sub>を選択することにより、ワード線WL<sub>y</sub>に接続する縦型電界効果トランジスタQ<sub>My</sub>をオン状態にする。こうして強誘電体キャパシタC<sub>My</sub>とサブピット線SBLが電気的に接続され、情報に応じた電圧が印加されて、強誘電体の極性が決定される。次にワード線WL<sub>y</sub>が切られてセルが切り離される。次に、ピット線が復帰さ50

れる。次に、サブブロック選択用ワード線BSが切られてブロックが切り離されて書き込み終了となる。

【0138】

図17は図15で説明した強誘電体メモリの平面図及び断面図である。

【0139】

図17(a)は、図17(b)のA-A'で切った平面図、図17(b)は図18(a)のB-B'で切った断面図を示す。それぞれの記号は図15に用いた記号と同一である。

【0140】

ビット線BLに接続された1個のブロック内にサブブロックが2個設置され、各サブブロック内には16個のメモリセル、サブブロック選択用トランジスタQ<sub>BS</sub>及び増幅用トランジスタQ<sub>READ</sub>が含まれる。

【0141】

また、各選択用トランジスタQ<sub>M0</sub>, Q<sub>M1</sub>, Q<sub>M2</sub>, ……, Q<sub>M15</sub>は縦形電界効果型トランジスタである。各選択用トランジスタQ<sub>M0</sub>, Q<sub>M1</sub>, Q<sub>M2</sub>, ……, Q<sub>M15</sub>の上部ソースドレイン領域上には下部キャパシタ電極層LE、強誘電体膜FE及び上部キャパシタ電極層TEからなる強誘電体キャパシタC<sub>M0</sub>, C<sub>M1</sub>, C<sub>M2</sub>, ……, C<sub>M15</sub>が形成されている。またサブビット線SBLの一端が接続されている増幅用トランジスタQ<sub>READ</sub>も縦形電界効果型トランジスタでありサブビット線SBLの他端に接続されているサブブロック選択用トランジスタQ<sub>BS</sub>は通常の平面型電界効果型トランジスタである。

【0142】

本実施形態では、メモリセルのワード線方向の幅は2Fでビット線方向の長さは2.3Fであるから面積は4.6F<sup>2</sup>ブロックあたりの記憶セル以外の領域は16F<sup>2</sup>であるからメモリセル1個当たり(4.6+16/32)F<sup>2</sup>になる。

【0143】

また、本実施形態では強誘電体キャパシタとして60?C/cm<sup>2</sup>の残留分極を持つものを使用したため各サブビット線に8個の記憶セルを接続しても安定に動作することが分かった。したがって1個当たり5.1F<sup>2</sup>の寸法になった。

【0144】

このような回路構成により非常に高集積化された不揮発性メモリの動作が確認できた。

【0145】

【発明の効果】

以上詳述したように本発明によれば縦形トランジスタの上部ソースドレイン領域上にエピタキシャル・キャパシタを自己整合的に作成することができるため、両者の面積がほぼ一致し最小4F<sup>2</sup>の面積のメモリセルを作成することが可能になる。

【図面の簡単な説明】

【図1】 縦形電界効果型トランジスタを基板上に形成後、フォトリソグラフィによりエピタキシャル強誘電体キャパシタを形成した強誘電体メモリを説明するもので(a)は平面図、(b)は(a)のA-A'線に沿う断面図、(c)は平面図。

【図2】 本発明の実施形態1に係る強誘電体メモリセルの平面図。

【図3】 本発明の実施形態1に係る強誘電体メモリセルの工程を説明する断面図で、(a)-1, (b)-1, (c)-1は図2のA-A'線に沿う断面図、(a)-2, (b)-2, (c)-2は図2のB-B'線に沿う断面図。

【図4】 本発明の実施形態1に係る強誘電体メモリセルの工程を説明する断面図で、(a)-1, (b)-1, (c)-1は図2のA-A'線に沿う断面図、(a)-2, (b)-2, (c)-2は図2のB-B'線に沿う断面図。

【図5】 本発明の実施形態2に係る強誘電体メモリセルの平面図。

【図6】 本発明の実施形態2に係る強誘電体メモリセルの工程を説明する断面図で、(a)-1, (b)-1, (c)-1は図5のA-A'線に沿う断面図、(a)-2, (b)-2, (c)-2は図5のB-B'線に沿う断面図。

【図7】 本発明の実施形態2に係る強誘電体メモリセルの工程を説明する断面図で、(a)

10

20

30

40

50

) -1, (b) -1, (c) -1 は図 5 の A - A' 線に沿う断面図、(a) -2, (b) -2, (c) -2 は図 5 の B - B' 線に沿う断面図。

【図 8】 本発明の実施形態 3 に係る強誘電体メモリセルの平面図。

【図 9】 本発明の実施形態 3 に係る強誘電体メモリセルの工程を説明する断面図で、(a) -1, (b) -1, (c) -1 は図 8 の A - A' 線に沿う断面図、(a) -2, (b) -2, (c) -2 は図 8 の B - B' 線に沿う断面図。

【図 10】 本発明の実施形態 3 に係る強誘電体メモリセルの工程を説明する断面図で、(a) -1, (b) -1, (c) -1 は図 8 の A - A' 線に沿う断面図、(a) -2, (b) -2, (c) -2 は図 8 の B - B' 線に沿う断面図。

【図 11】 本発明の実施形態 4 に係る強誘電体メモリセルの平面図。

10

【図 12】 本発明の実施形態 4 に係る強誘電体メモリセルの工程を説明する断面図で、(a) -1, (b) -1, (c) -1 は図 11 の A - A' 線に沿う断面図、(a) -2, (b) -2, (c) -2 は図 11 の B - B' 線に沿う断面図。

【図 13】 本発明の実施形態 4 に係る強誘電体メモリセルの工程を説明する断面図で、(a) -1, (b) -1, (c) -1 は図 11 の A - A' 線に沿う断面図、(a) -2, (b) -2, (c) -2 は図 11 の B - B' 線に沿う断面図。

【図 14】 本発明の実施形態 5 に係る強誘電体メモリセルのサブプロック回路図。

【図 15】 本発明の実施形態 5 に係る強誘電体メモリセルをマトリックス状に配置した回路図。

【図 16】 本発明の実施形態 5 に係る強誘電体メモリの読み出し / 書き込みシーケンスを示すタイミングチャート。

20

【図 17】 本発明の実施形態 5 に係る強誘電体メモリの平面図及び断面図で (a) は (b) における A - A' 線に添って切り取った平面図、(b) は (a) における B - B' 線に沿って切り取った断面図。

【符号の説明】

- 1 . . . 半導体基板

- 2 . . . 半導体の柱状部

- 3 . . . ゲート電極

- 4 . . . 下部ソースドレイン領域

- 5 . . . 上部ソースドレイン領域

- 6 . . . エピタキシャル・キャパシタ

- 7 . . . バリア層

- 8 . . . 下部キャパシタ電極層

- 9 . . . 強誘電体膜

- 10 . . . 上部キャパシタ電極層

- 11 . . . チャネル部

- 12 . . . 層間絶縁膜

- 13 . . . ゲート絶縁膜

- 14 . . . 埋め込み絶縁膜

- 21 . . . ワード線

- 22 . . . エピタキシャル・キャパシタ領域

- 23 . . . ビット線

- 25 . . . 酸化膜

- 26 . . . 窒化膜

- 27 . . . キャパシタ側壁

30

40

【 図 1 】

【 図 2 】

【 四 3 】

【 図 4 】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

---

フロントページの続き

(51)Int.Cl.<sup>7</sup>

F I

H 0 1 L 29/78 6 5 8 G

(56)参考文献 特開平11-220103(JP, A)

特開平11-135757(JP, A)

特開平11-074477(JP, A)

特開平10-270652(JP, A)

特開平10-209404(JP, A)

(58)調査した分野(Int.Cl.<sup>7</sup>, DB名)

H01L 27/105

H01L 21/336

H01L 29/78 652

H01L 29/78 653

H01L 29/78 656